## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## **User's Manual**

# V850E1

**32-Bit Microprocessor Core**

**Architecture**

Document No. U14559EJ3V1UM00 (3rd edition) Date Published February 2004 N CP(K)

### [MEMO]

#### NOTES FOR CMOS DEVICES —

#### (1) VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN).

#### (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

#### (3) PRECAUTION AGAINST ESD

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

#### (4) STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

These commodities, technology or software, must be exported in accordance with the export administration regulations of the exporting country. Diversion contrary to the law of that country is prohibited.

- The information in this document is current as of February, 2004. The information is subject to

change without notice. For actual design-in, refer to the latest publications of NEC Electronics data

sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not

all products and/or types are available in every country. Please check with an NEC Electronics sales

representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative

purposes in semiconductor product operation and application examples. The incorporation of these

circuits, software and information in the design of a customer's equipment shall be done under the full

responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by

customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

- The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

#### (Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

M8E 02.11-1

### **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC Electronics product in your application, please contact the NEC Electronics office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- · Ordering information

- · Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- · Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### [GLOBAL SUPPORT]

http://www.necel.com/en/support/support.html

### NEC Electronics America, Inc. (U.S.) NEC Electronics (Europe) GmbH NEC Electronics Hong Kong Ltd.

Santa Clara, California Tel: 408-588-6000 800-366-9782

Duesseldorf, Germany Tel: 0211-65030

#### • Sucursal en España

Madrid, Spain Tel: 091-504 27 87

#### • Succursale Française

Vélizy-Villacoublay, France Tel: 01-30-675800

#### Filiale Italiana

Milano, Italy Tel: 02-66 75 41

#### • Branch The Netherlands

Eindhoven. The Netherlands Tel: 040-2445845

#### Tyskland Filial

Taeby, Sweden Tel: 08-63 80 820

#### United Kingdom Branch

Milton Keynes, UK Tel: 01908-691-133

Hong Kong Tel: 2886-9318

#### **NEC Electronics Hong Kong Ltd.**

Seoul Branch Seoul, Korea Tel: 02-558-3737

#### NEC Electronics Shanghai Ltd.

Shanghai, P.R. China Tel: 021-5888-5400

#### **NEC Electronics Taiwan Ltd.**

Taipei, Taiwan Tel: 02-2719-2377

#### **NEC Electronics Singapore Pte. Ltd.**

Novena Square, Singapore Tel: 6253-8311

J04.1

#### **PREFACE**

**Target Readers**

This manual is intended for users who wish to understand the functions of the V850E1 CPU core for designing application systems using the V850E1 CPU core.

**Purpose**

This manual is intended to give users an understanding of the architecture of the V850E1 CPU core described in the **Organization** below.

Organization

This manual contains the following information.

- Register set

- Data types

- · Instruction format and instruction set

- · Interrupts and exceptions

- Pipeline

#### **How to Use This Manual**

It is assumed that the reader of this manual has general knowledge in the fields of electrical engineering, logic circuits, and microcontrollers.

To learn about the hardware functions,

→ Read Hardware User's Manual of each product.

To learn about the functions of a specific instruction in detail,

→ Read CHAPTER 5 INSTRUCTIONS.

The mark ★ shows major revised points.

#### **Product Types**

This manual explains the products divided into types.

Before reading this manual, check the corresponding product type.

| Product Type                                      | Product Name                |  |  |  |  |  |  |  |

|---------------------------------------------------|-----------------------------|--|--|--|--|--|--|--|

| Type A                                            | NU85E CPU core              |  |  |  |  |  |  |  |

| Type B NU85ET CPU core                            |                             |  |  |  |  |  |  |  |

| Type C                                            | NB85E, NB85ET CPU core      |  |  |  |  |  |  |  |

| Type D V850E/IA1, V850E/IA2, V850E/MA1, V850E/SV2 |                             |  |  |  |  |  |  |  |

| Type E V850E/IA3, V850E/IA4, V850E/MA3            |                             |  |  |  |  |  |  |  |

| Type F                                            | Type F V850E/MA2, V850E/ME2 |  |  |  |  |  |  |  |

**Conventions** Data significance: Higher digits on the left and lower digits on the right

Active low representation:  $\times \times \times B$  (B is appended to pin or signal name)

Note: Footnote for item marked with Note in the text

Caution: Information requiring particular attention

$\begin{tabular}{ll} \textbf{Remark}: & Supplementary information} \\ \textbf{Numerical representation:} & Binary ... \times \times \times \text{ or } \times \times \times \times B \\ \end{tabular}$

Decimal ... ××××

Hexadecimal ... ××××H

Prefix indicating the power of 2 (address space, memory capacity):

K (Kilo):  $2^{10} = 1,024$ M (Mega):  $2^{20} = 1,024^2$ G (Giga):  $2^{30} = 1,024^3$

### **CONTENTS**

| CHAP. | TER 1  | GENERAL                                                     | 12 |

|-------|--------|-------------------------------------------------------------|----|

| 1.1   | Featu  | ıres                                                        | 13 |

| 1.2   | Interr | nal Configuration                                           | 14 |

| СПУБ. | TED 2  | REGISTER SET                                                | 15 |

|       |        |                                                             |    |

| 2.1   | _      | ram Registers                                               |    |

| 2.2   | -      | em Registers                                                |    |

|       | 2.2.1  | Interrupt status saving registers (EIPC, EIPSW)             |    |

|       | 2.2.2  | NMI status saving registers (FEPC, FEPSW)                   |    |

|       | 2.2.3  | Exception cause register (ECR)                              |    |

|       | 2.2.4  | Program status word (PSW)                                   |    |

|       | 2.2.5  | CALLT caller status saving registers (CTPC, CTPSW)          |    |

|       | 2.2.6  | Exception/debug trap status saving registers (DBPC, DBPSW)  |    |

|       | 2.2.7  | CALLT base pointer (CTBP)                                   |    |

|       | 2.2.8  | Debug interface register (DIR)                              |    |

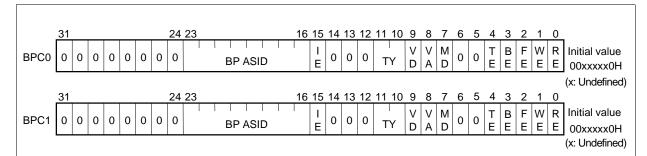

|       | 2.2.9  | Breakpoint control registers 0 and 1 (BPC0, BPC1)           |    |

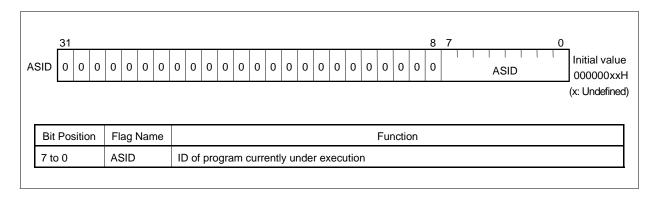

|       |        | Program ID register (ASID)                                  |    |

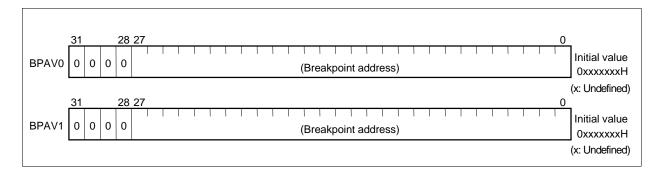

|       |        | Breakpoint address setting registers 0 and 1 (BPAV0, BPAV1) |    |

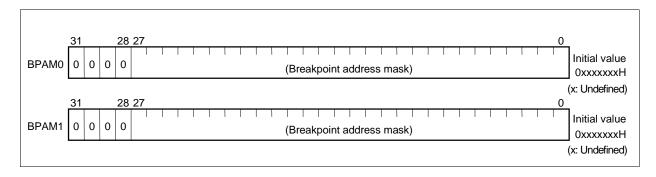

|       |        | Breakpoint address mask registers 0 and 1 (BPAM0, BPAM1)    |    |

|       |        | Breakpoint data setting registers 0 and 1 (BPDV0, BPDV1)    |    |

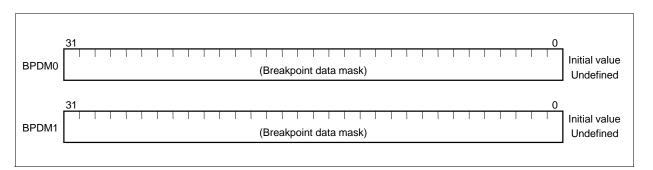

|       | 2.2.14 | Breakpoint data mask registers 0 and 1 (BPDM0, BPDM1)       | 32 |

|       |        |                                                             |    |

| CHAP  |        | DATA TYPES                                                  |    |

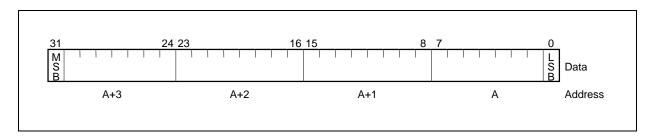

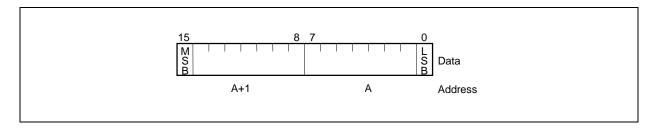

| 3.1   |        | Format                                                      |    |

| 3.2   | Data   | Representation                                              | 35 |

|       | 3.2.1  | Integer                                                     | 35 |

|       | 3.2.2  | Unsigned integer                                            | 35 |

|       | 3.2.3  | Bit                                                         | 35 |

| 3.3   | Data   | Alignment                                                   | 36 |

| CHAP  | TER 4  | ADDRESS SPACE                                               | 37 |

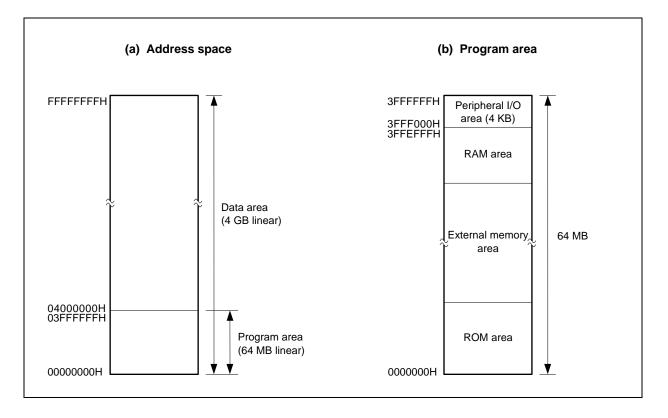

| 4.1   | Memo   | ory Map                                                     | 38 |

| 4.2   | Addre  | essing Mode                                                 | 39 |

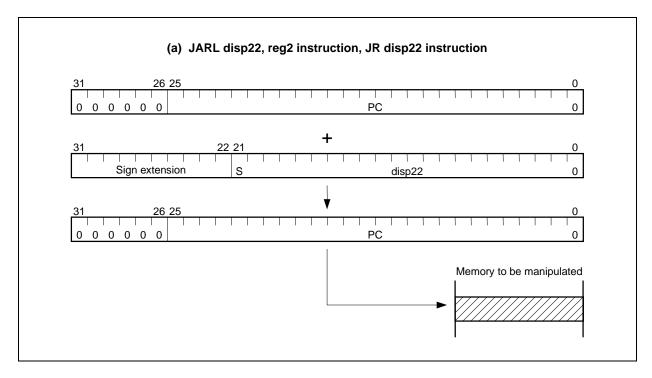

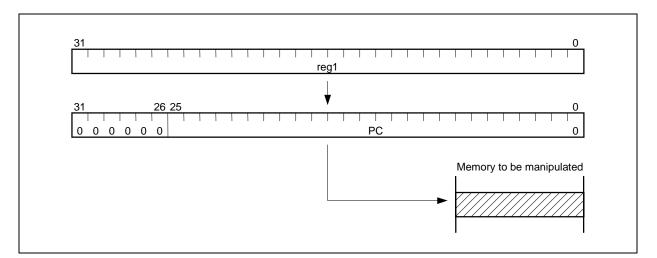

|       | 4.2.1  | Instruction address                                         | 39 |

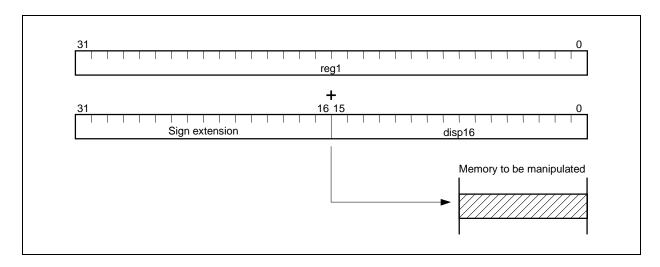

|       | 4.2.2  | Operand address                                             | 41 |

| CHAP  | TER 5  | INSTRUCTIONS                                                | 43 |

| 5.1   |        | uction Format                                               |    |

| 5.2   |        | ne of Instructions                                          |    |

| 5.3   |        | uction Set                                                  |    |

|       |        |                                                             |    |

|       |        |                                                             |    |

|       |        |                                                             |    |

|       |        |                                                             |    |

|       |        |                                                             |    |

| Bcond   | 57  |

|---------|-----|

| BSH     | 59  |

| BSW     | 60  |

| CALLT   | 61  |

| CLR1    | 62  |

| CMOV    | 63  |

| CMP     | 64  |

| CTRET   | 65  |

| DBRET   |     |

| DBTRAP  |     |

| DI      |     |

| DISPOSE |     |

| DIV     |     |

| DIVH    |     |

| DIVHU   |     |

| DIVU    |     |

|         |     |

| El      |     |

| HALT    |     |

| HSW     |     |

| JARL    |     |

| JMP     |     |

| JR      |     |

| LD.B    |     |

| LD.BU   | 83  |

| LD.H    | 84  |

| LD.HU   | 86  |

| LD.W    | 88  |

| LDSR    | 90  |

| MOV     | 91  |

| MOVEA   | 92  |

| MOVHI   |     |

| MUL     |     |

| MULH    |     |

| MULHI   |     |

| MULU    |     |

| NOP     |     |

| NOT     |     |

| NOT1    |     |

|         |     |

| OR      |     |

| ORI     |     |

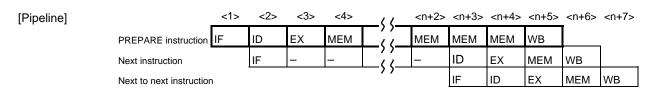

| PREPARE |     |

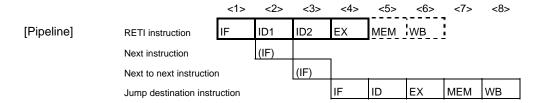

| RETI    |     |

| SAR     |     |

| SASF    |     |

| SATADD  |     |

| SATSUB  |     |

| SATSUBI | 113 |

| SATSUBR | 111 |

|            | SET1                                                  | 115 |

|------------|-------------------------------------------------------|-----|

|            | SETF                                                  | 116 |

|            | SHL                                                   | 118 |

|            | SHR                                                   | 119 |

|            | SLD.B                                                 | 120 |

|            | SLD.BU                                                | 121 |

|            | SLD.H                                                 | 122 |

|            | SLD.HU                                                | 124 |

|            | SLD.W                                                 | 126 |

|            | SST.B                                                 | 128 |

|            | SST.H                                                 | 129 |

|            | SST.W                                                 | 131 |

|            | ST.B                                                  | 133 |

|            | ST.H                                                  | 134 |

|            | ST.W                                                  | 136 |

|            | STSR                                                  | 138 |

|            | SUB                                                   | 139 |

|            | SUBR                                                  | 140 |

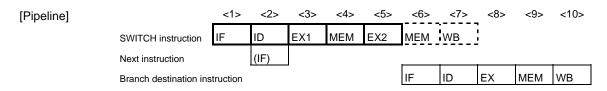

|            | SWITCH                                                | 141 |

|            | SXB                                                   | 142 |

|            | SXH                                                   | 143 |

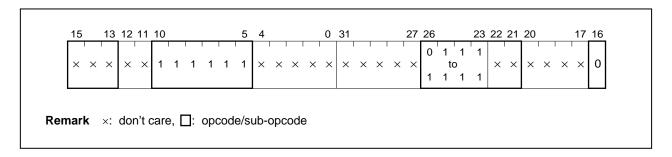

|            | TRAP                                                  | 144 |

|            | TST                                                   | 145 |

|            | TST1                                                  | 146 |

|            | XOR                                                   |     |

|            | XORI                                                  | 148 |

|            | ZXB                                                   | 149 |

|            | ZXH                                                   | 150 |

| 5.4        | Number of Instruction Execution Clock Cycles          |     |

|            |                                                       |     |

| CHAP       | TER 6 INTERRUPTS AND EXCEPTIONS                       | 155 |

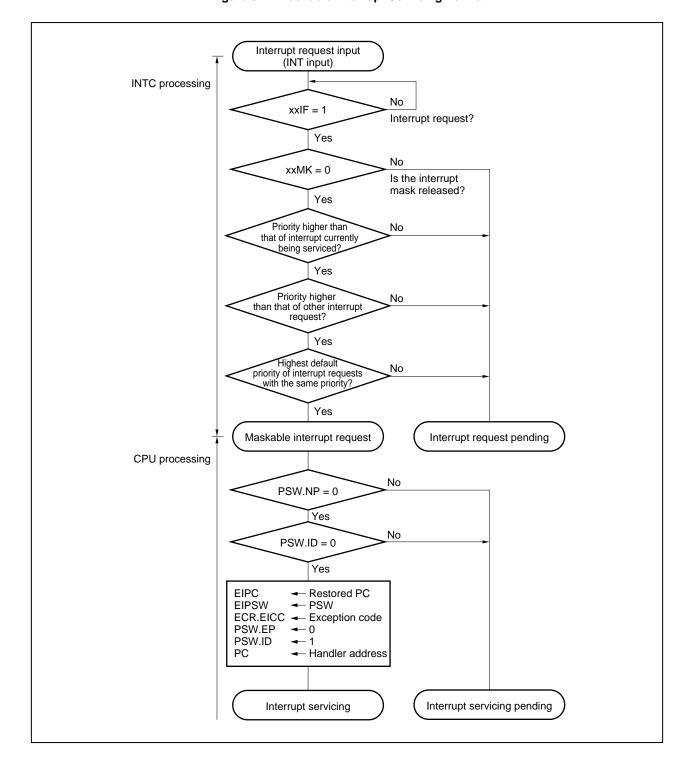

| 6.1        | Interrupt Servicing                                   | 156 |

|            | 6.1.1 Maskable interrupts                             | 156 |

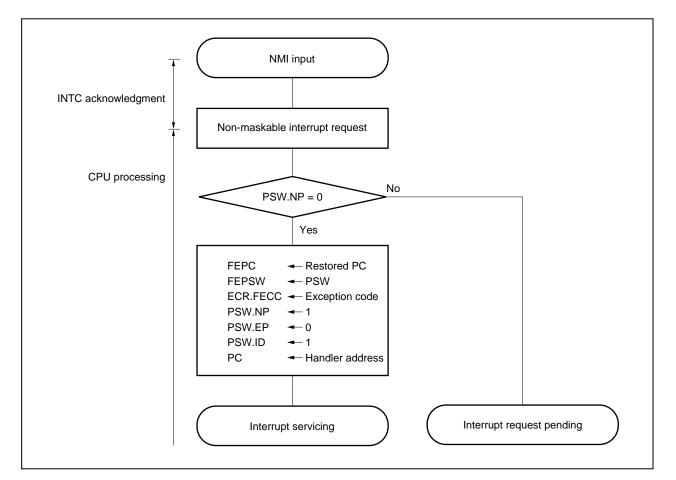

|            | 6.1.2 Non-maskable interrupts                         | 158 |

| 6.2        | Exception Processing                                  | 159 |

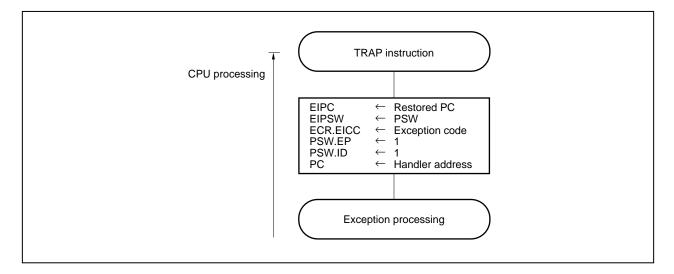

|            | 6.2.1 Software exceptions                             | 159 |

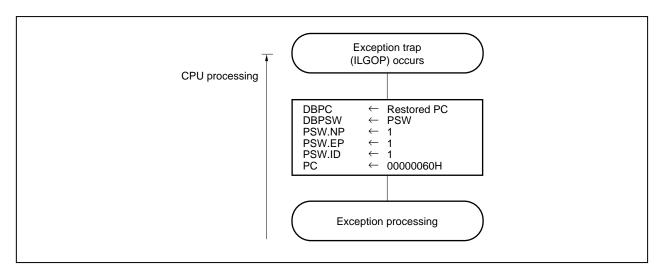

|            | 6.2.2 Exception trap                                  | 160 |

|            | 6.2.3 Debug trap                                      | 161 |

| 6.3        | Restoring from Interrupt/Exception Processing         | 162 |

|            | 6.3.1 Restoring from interrupt and software exception | 162 |

|            | 6.3.2 Restoring from exception trap and debug trap    | 163 |

| CHAP.      | TER 7 RESET                                           | 164 |

|            |                                                       |     |

| 7.1<br>7.2 | Register Status After Reset                           |     |

| 1.2        | Starting Up                                           | 100 |

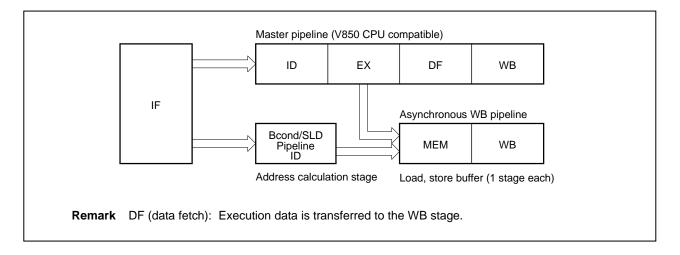

| CHAP       | TER 8 PIPELINE                                        | 166 |

|            |                                                       |     |

| 8.1        | Features                                              |     |

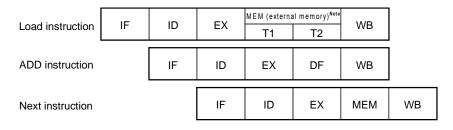

|   |             | 8.1.1  | Non-blocking load/store                                            | 168  |

|---|-------------|--------|--------------------------------------------------------------------|------|

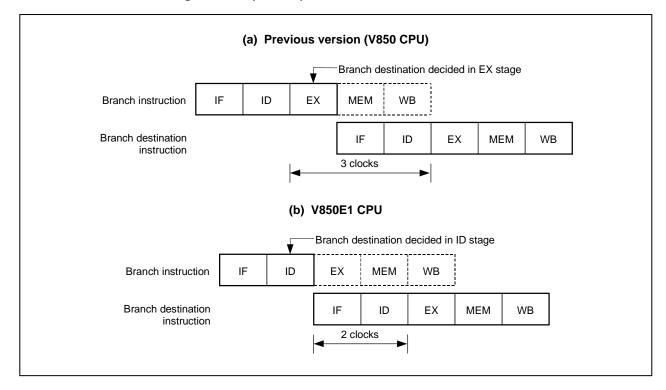

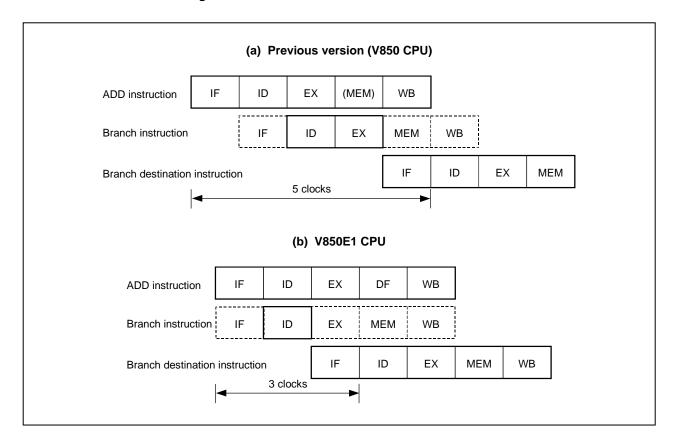

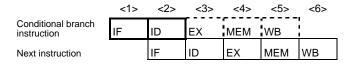

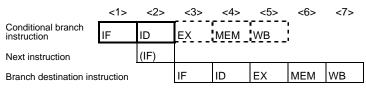

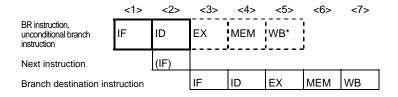

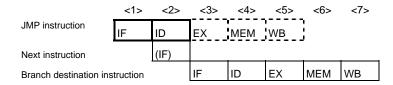

|   |             | 8.1.2  | 2-clock branch                                                     |      |

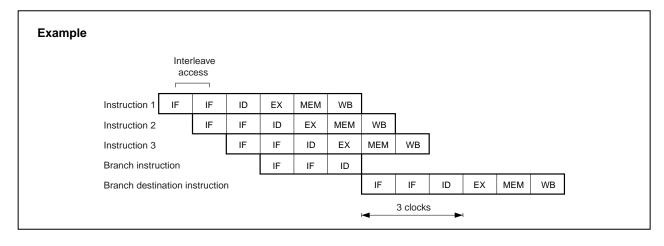

|   |             | 8.1.3  |                                                                    |      |

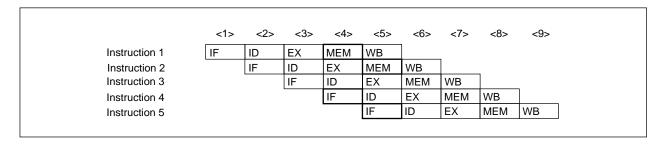

|   | 8.2         |        | ine Flow During Execution of Instructions                          |      |

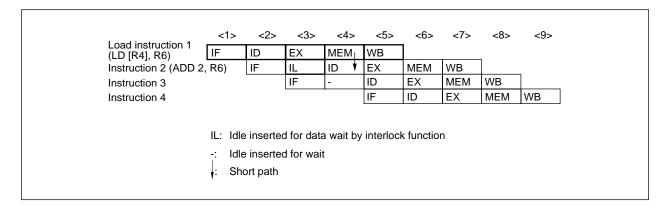

|   | <b>0.</b> _ | 8.2.1  | Load instructions                                                  |      |

|   |             | 8.2.2  | Store instructions                                                 |      |

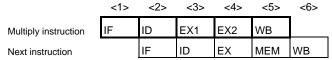

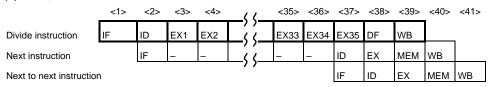

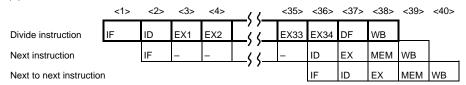

|   |             | 8.2.3  | Multiply instructions                                              |      |

|   |             | 8.2.4  | Arithmetic operation instructions                                  |      |

|   |             | 8.2.5  | Saturated operation instructions                                   |      |

|   |             | 8.2.6  | Logical operation instructions                                     |      |

|   |             | 8.2.7  | Branch instructions                                                |      |

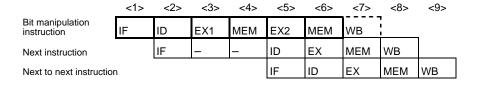

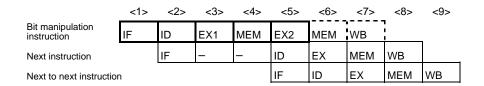

|   |             | 8.2.8  | Bit manipulation instructions                                      |      |

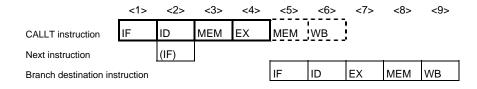

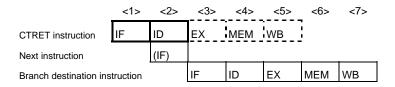

|   |             | 8.2.9  | Special instructions                                               |      |

|   |             |        | Debug function instructions                                        |      |

|   | 8.3         |        | ine Disorder                                                       |      |

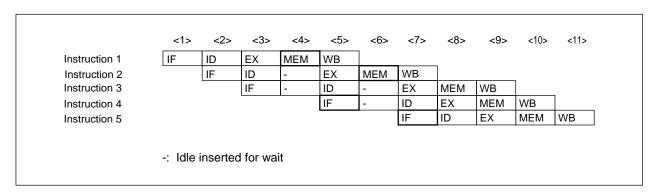

|   |             | 8.3.1  | Alignment hazard                                                   |      |

|   |             | 8.3.2  | Referencing execution result of load instruction                   |      |

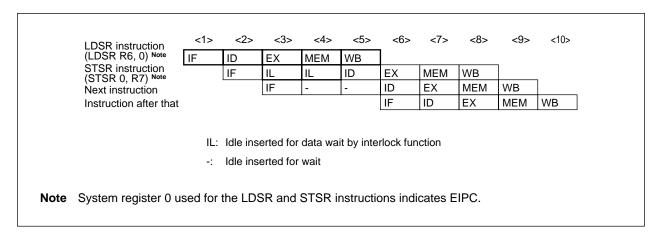

|   |             | 8.3.3  | Referencing execution result of multiply instruction               |      |

|   |             | 8.3.4  | Referencing execution result of LDSR instruction for EIPC and FEPC |      |

|   |             | 8.3.5  | Cautions when creating programs                                    |      |

|   | 8.4         | Addit  | ional Items Related to Pipeline                                    |      |

|   |             | 8.4.1  | Harvard architecture                                               | 186  |

|   |             | 8.4.2  | Short path                                                         |      |

|   |             |        |                                                                    |      |

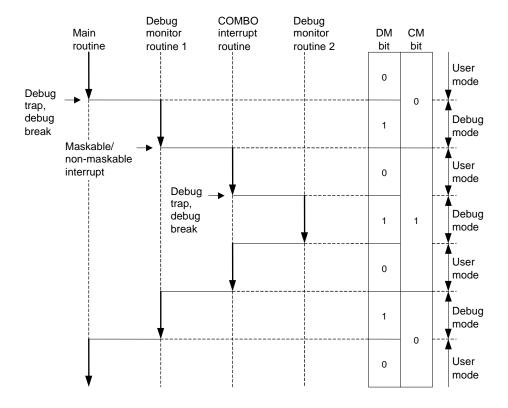

| ۲ | CHAP        |        | SHIFTING TO DEBUG MODE                                             |      |

|   | 9.1         |        | to Shift to Debug Mode                                             |      |

|   | 9.2         | Cauti  | ons                                                                | 195  |

| _ | A DDE       | NDIY / | A NOTES                                                            | 107  |

| • |             |        |                                                                    |      |

|   | A.1         |        | iction on Conflict Between sld Instruction and Interrupt request   |      |

|   |             |        | Description                                                        |      |

|   |             | A.1.2  | Countermeasure                                                     | 197  |

|   | ADDE        | NDIV E | INSTRUCTION LIST                                                   | 100  |

|   | APPEI       | NDIA E | S INSTRUCTION LIST                                                 | 190  |

|   | ADDE        | NDIV ( | INSTRUCTION OPCODE MAP                                             | 212  |

|   | APPEI       | ADIX ( | NSTRUCTION OFCODE WAF                                              | 212  |

|   | ADDE        | NDIV F | D DIFFERENCES WITH ARCHITECTURE OF V850 CPU                        | 247  |

|   | APPEI       | NDIX L | DIFFERENCES WITH ARCHITECTURE OF VOOU CPU                          | 217  |

|   | ADDE        | NDIV E | INSTRUCTIONS ADDED FOR V850E1 CPU COMPARED WITH V850 CPU           | 240  |

|   | APPEI       | אטוא ב | INSTRUCTIONS ADDED FOR V650ET CPU COMPARED WITH V650 CPU           | 219  |

|   | ADDE        | NDIV E | - INDEX                                                            | 221  |

|   | AFFEI       | ADIV L | INDLA                                                              | ∠∠ I |

|   | \ DDE!      | NDIY 1 | REVISION HISTORY                                                   | 224  |

| τ |             |        |                                                                    |      |

|   |             |        | Revisions in This Edition                                          |      |

|   | G.2         | Histo  | ry of Revisions up to This Edition                                 | 225  |

#### **CHAPTER 1 GENERAL**

Real-time control systems are used in a wide range of applications, including:

- office equipment such as HDDs (Hard Disk Drives), PPCs (Plain Paper Copiers), printers, and facsimiles,

- automobile electronics such as engine control systems and ABSs (Antilock Braking Systems), and

- factory automation equipment such as NC (Numerical Control) machine tools and various controllers.

The great majority of these systems conventionally employ 8-bit or 16-bit microcontrollers. However, the performance level of these microcontrollers has become inadequate in recent years as control operations have risen in complexity, leading to the development of increasingly complicated instruction sets and hardware design. As a result, the need has arisen for a new generation of microcontrollers operable at much higher frequencies to achieve an acceptable level of performance under today's more demanding requirements.

The V850 Series of microcontrollers was developed to satisfy this need. This series uses RISC architecture that can provide maximum performance with simpler hardware, allowing users to obtain a performance approximately 15 times higher than that of the existing 78K/III Series and 78K/IV Series of CISC single-chip microcontrollers at a lower total cost.

In addition to the basic instructions of conventional RISC CPUs, the V850 Series is provided with special instructions such as saturation, bit manipulation, and multiply/divide (executed by a hardware multiplier) instructions, which are especially suited to digital servo control systems. Moreover, instruction formats are designed for maximum compiler coding efficiency, allowing the reduction of object code sizes.

The V850E1 CPU is a 32-bit RISC CPU core for ASIC, newly developed as the CPU core central to system LSI in the current age of system-on-a-chip. This core includes not only the control functions of the V850 CPU, the CPU core incorporated in the V850 Series, but also supports data processing through its enhanced external bus interface performance, and the addition of features such as C language switch statement processing, table lookup branching, stack frame creation/deletion, data conversion, and other high-level language supporting instructions.

In addition, because the instruction codes are upwardly compatible with the V850 CPU at the object code level, the software resources of systems that incorporate the V850 CPU can be used unchanged.

#### 1.1 Features

- (1) High-performance 32-bit architecture for embedded control

- Number of instructions: 83

- 32-bit general-purpose registers: 32

- · Load/store instructions in long/short format

- 3-operand instruction

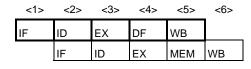

- 5-stage pipeline of 1 clock cycle per stage

- Hardware interlock on register/flag hazards

- Memory space Program space: 64 MB linear

Data space: 4 GB linear

- (2) Special instructions

- · Saturation operation instructions

- · Bit manipulation instructions

- Multiply instructions (On-chip hardware multiplier executing multiplication in 1 clock)

16 bits  $\times$  16 bits  $\rightarrow$  32 bits

32 bits  $\times$  32 bits  $\rightarrow$  32 bits or 64 bits

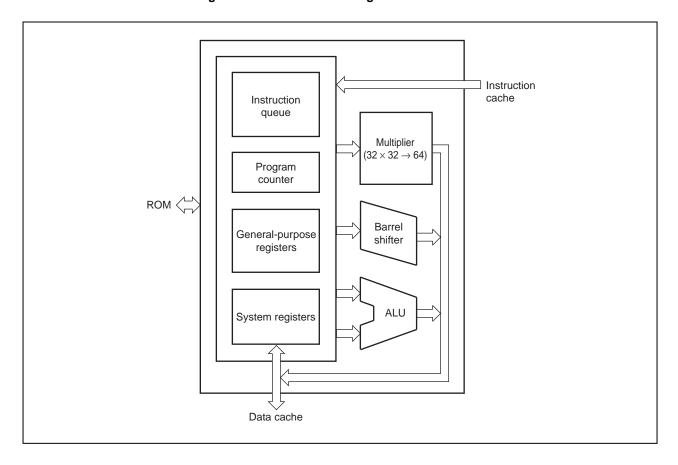

#### 1.2 Internal Configuration

The V850E1 CPU executes almost all instructions such as address calculation, arithmetic and logical operation, and data transfer in one clock by using a 5-stage pipeline.

It contains dedicated hardware such as a multiplier (32  $\times$  32 bits) and a barrel shifter (32 bits/clock) to execute complicated instructions at high speeds.

Figure 1-1 shows the internal block diagram.

Figure 1-1. Internal Block Diagram of V850E1 CPU

#### **CHAPTER 2 REGISTER SET**

The registers can be classified into two types: program registers that can be used for general programming, and system registers that can control the execution environment. All the registers are 32 bits wide.

Figure 2-1. Registers

| (a) Program registers            | (b) System registers                                |       |

|----------------------------------|-----------------------------------------------------|-------|

| r0 (Zero register)               | 31 0 EIPC (Interrupt status saving register)        |       |

| r1 (Assembler-reserved register) | EIPSW (Interrupt status saving register)            |       |

| r2                               |                                                     |       |

| r3 (Stack pointer (SP))          | FEPC (NMI status saving register)                   |       |

| r4 (Global pointer (GP))         | FEPSW (NMI status saving register)                  |       |

| r5 (Text pointer (TP))           |                                                     |       |

| r6                               | ECR (Exception cause register)                      |       |

| r7                               | PSW (Program status word)                           |       |

| r8                               | ( region contact ( )                                |       |

| r9                               | CTPC (CALLT caller status saving register)          |       |

| r10                              | CTPSW (CALLT caller status saving register)         |       |

| r11                              |                                                     |       |

| r12                              | DBPC (Exception/debug trap status saving register)  |       |

| r13                              | DBPSW (Exception/debug trap status saving register) |       |

| r14                              | CTBP (CALLT base pointer)                           |       |

| r15                              |                                                     | 2     |

| r16                              | DIR (Debug interface register)                      |       |

| r17                              |                                                     |       |

| r18                              | BPC0 (Breakpoint control register 0)                |       |

| r19                              | BPC1 (Breakpoint control register 1)                |       |

| r20                              | ASID (Program ID register)                          |       |

| r21                              |                                                     |       |

| r22                              | BPAV0 (Breakpoint address setting register 0)       |       |

| r23                              | BPAV1 (Breakpoint address setting register 1)       | Not   |

| r24                              | BPAM0 (Breakpoint address mask register 0)          |       |

| r25                              | BPAM1 (Breakpoint address mask register 1)          |       |

| r26                              | DDD/(0 (D                                           |       |

| r27                              | BPDV0 (Breakpoint data setting register 0)          |       |

| r28                              | BPDV1 (Breakpoint data setting register 1)          |       |

| r29                              | BPDM0 (Breakpoint data mask register 0)             |       |

| r30 (Element pointer (EP))       | BPDM1 (Breakpoint data mask register 1)             | J     |

| r31 (Link pointer (LP))          | Note These registers are reserved for               |       |

|                                  | debug function. They can only be use                | ed in |

| PC (Program counter)             | type A or B products. They cannot                   | t be  |

\*

#### 2.1 Program Registers

The program registers include general-purpose registers (r0 to r31) and a program counter (PC).

**Table 2-1. Program Registers**

| Program Registers | Name      | Function                                                                          | Description                                                                                     |  |  |  |  |  |  |  |

|-------------------|-----------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| General-purpose   | r0        | Zero register                                                                     | Always holds 0.                                                                                 |  |  |  |  |  |  |  |

| registers         | r1        | Assembler-reserved register                                                       | Used as working register for address generation.                                                |  |  |  |  |  |  |  |

|                   | r2        | Address/data variable register (when the real-time OS to be used is not using r2) |                                                                                                 |  |  |  |  |  |  |  |

|                   | r3        | Stack pointer (SP)                                                                | Used for stack frame generation when function is called.                                        |  |  |  |  |  |  |  |

|                   | r4        | Global pointer (GP)                                                               | Used to access global variable in data area.                                                    |  |  |  |  |  |  |  |

|                   | r5        | Text pointer (TP)                                                                 | Used as register for pointing to start address of text area (area where program code is placed) |  |  |  |  |  |  |  |

|                   | r6 to r29 | Address/data variable registers                                                   |                                                                                                 |  |  |  |  |  |  |  |

|                   | r30       | Element pointer (EP)                                                              | Used as base pointer for address generation when memory is accessed.                            |  |  |  |  |  |  |  |

|                   | r31       | Link pointer (LP)                                                                 | Used when compiler calls function.                                                              |  |  |  |  |  |  |  |

| Program counter   | PC        | Holds instruction address during program execution.                               |                                                                                                 |  |  |  |  |  |  |  |

Remark For detailed descriptions of r1, r3 to r5, and r31 used by an assembler or C compiler, refer to the CA850 (C Compiler Package) Assembly Language User's Manual.

#### **★** (1) General-purpose registers (r0 to r31)

Thirty-two general-purpose registers, r0 to r31, are provided. All these registers can be used for data variables or address variables.

However, care must be exercised as follows in using the r0 to r5, r30, and r31 registers.

#### (a) r0, r30

r0 and r30 are implicitly used by instructions.

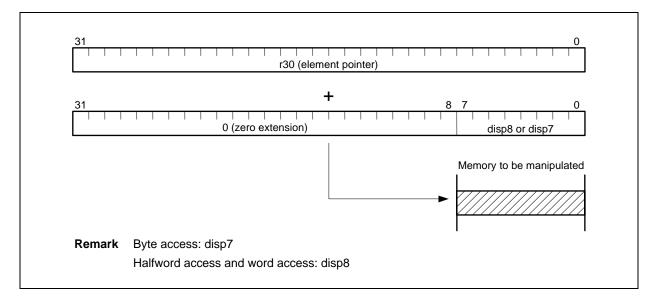

r0 is a register that always holds 0, and is used for operations using 0 and offset 0 addressing. r30 is used as a base pointer when accessing memory using the SLD and SST instructions.

#### (b) r1, r3 to r5, r31

r1, r3 to r5, and r31 are implicitly used by the assembler and C compiler.

Before using these registers, therefore, their contents must be saved so that they are not lost. The contents must be restored to the registers after the registers have been used.

#### (c) r2

r2 is sometimes used by a real-time OS. When the real-time OS to be used is not using r2, r2 can be used as an address variable register or a data variable register.

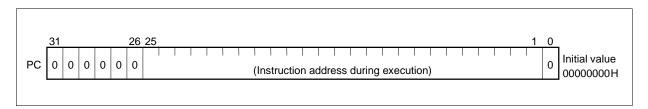

### (2) Program counter (PC)

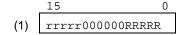

This register holds an instruction address during program execution. The lower 26 bits of this register are valid, and bits 31 to 26 are reserved for future function expansion (fixed to 0). If a carry occurs from bit 25 to bit 26, it is ignored. Bit 0 is always fixed to 0 so that execution cannot branch to an odd address.

Figure 2-2. Program Counter (PC)

### 2.2 System Registers

The system registers control the CPU status and hold information on interrupts.

System registers can be read or written by specifying the relevant system register number from the following list using a system register load/store instruction (LDSR or STSR instruction).

Table 2-2. System Register Numbers

| Register | Register Name                                                                                 | Operand S           | Specifiability      |

|----------|-----------------------------------------------------------------------------------------------|---------------------|---------------------|

| No.      |                                                                                               | LDSR<br>Instruction | STSR<br>Instruction |

| 0        | Interrupt status saving register (EIPC)                                                       | 0                   | 0                   |

| 1        | Interrupt status saving register (EIPSW)                                                      | 0                   | 0                   |

| 2        | NMI status saving register (FEPC)                                                             | 0                   | 0                   |

| 3        | NMI status saving register (FEPSW)                                                            | 0                   | 0                   |

| 4        | Exception cause register (ECR)                                                                | ×                   | 0                   |

| 5        | Program status word (PSW)                                                                     | 0                   | 0                   |

| 6 to 15  | (Numbers reserved for future function expansion (operation cannot be guaranteed if accessed)) | ×                   | ×                   |

| 16       | CALLT caller status saving register (CTPC)                                                    | 0                   | 0                   |

| 17       | CALLT caller status saving register (CTPSW)                                                   | 0                   | 0                   |

| 18       | Exception/debug trap status saving register (DBPC)                                            | 0                   | O <sup>Note 1</sup> |

| 19       | Exception/debug trap status saving register (DBPSW)                                           | 0                   | O <sup>Note 1</sup> |

| 20       | CALLT base pointer (CTBP)                                                                     | 0                   | 0                   |

| 21       | Debug interface register (DIR)                                                                | O <sup>Note 1</sup> | 0                   |

| 22       | Breakpoint control registers 0 and 1 (BPC0, BPC1) <sup>Note 2</sup>                           | O <sup>Note 1</sup> | O <sup>Note 1</sup> |

| 23       | Program ID register (ASID)                                                                    | 0                   | 0                   |

| 24       | Breakpoint address setting registers 0 and 1 (BPAV0, BPAV1) <sup>Note 2</sup>                 | O <sup>Note 1</sup> | O <sup>Note 1</sup> |

| 25       | Breakpoint address mask registers 0 and 1 (BPAM0, BPAM1) <sup>Note 2</sup>                    | O <sup>Note 1</sup> | O <sup>Note 1</sup> |

| 26       | Breakpoint data setting registers 0 and 1 (BPDV0, BPDV1) <sup>Note 2</sup>                    | O <sup>Note 1</sup> | O <sup>Note 1</sup> |

| 27       | Breakpoint data mask registers 0 and 1 (BPDM0, BPDM1) <sup>Note 2</sup>                       | O <sup>Note 1</sup> | O <sup>Note 1</sup> |

| 28 to 31 | (Numbers reserved for future function expansion (operation cannot be guaranteed if accessed)) | ×                   | ×                   |

- **Notes 1.** These registers can be accessed only in the debug mode of type A and B products. Accessing these registers in other product types is prohibited. If they are accessed, the operation is not guaranteed.

- 2. The actual register to be accessed is specified by the DIR.CS bit.

Caution When returning using the RETI instruction after setting bit 0 of EIPC, FEPC, or CTPC to 1 using the LDSR instruction and servicing an interrupt, the value of bit 0 is ignored (because bit 0 of the PC is fixed to 0). Therefore, be sure to set an even number (bit 0 = 0) when setting a value to EIPC, FEPC, or CTPC.

Remark O: Accessible

x: Inaccessible

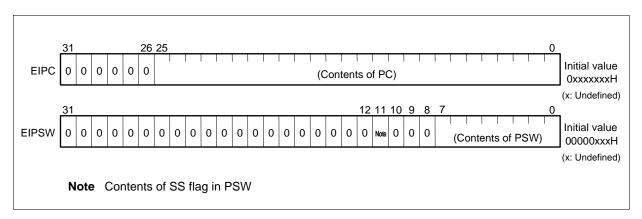

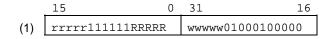

#### 2.2.1 Interrupt status saving registers (EIPC, EIPSW)

Two interrupt status saving registers are provided: EIPC and EIPSW.

If a software exception or maskable interrupt occurs, the contents of the program counter (PC) are saved to EIPC, and the contents of the program status word (PSW) are saved to EIPSW (if a non-maskable interrupt (NMI) occurs, the contents are saved to the NMI status saving registers (FEPC, FEPSW)).

Except for some instructions, the address of the instruction next to the one being executed when the software exception or maskable interrupt occurs is saved to EIPC (see **Table 6-1 Interrupt/Exception Codes**).

The current value of the PSW is saved to EIPSW.

Because only one pair of interrupt status saving registers is provided, the contents of these registers must be saved by program when multiple interrupt servicing is enabled.

Bits 31 to 26 of EIPC and bits 31 to 12 and 10 to 8 of EIPSW are reserved for future function expansion (fixed to 0).

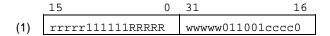

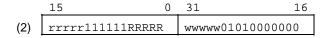

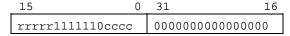

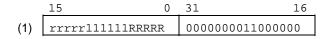

Figure 2-3. Interrupt Status Saving Registers (EIPC, EIPSW)

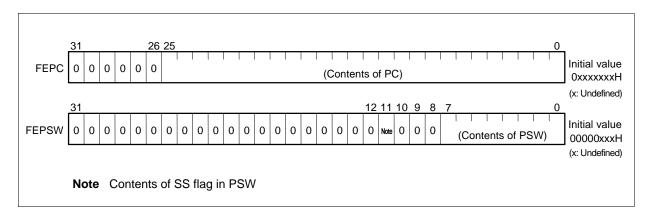

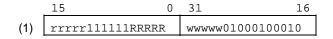

#### 2.2.2 NMI status saving registers (FEPC, FEPSW)

Two NMI status saving registers are provided: FEPC and FEPSW.

If a non-maskable interrupt (NMI) occurs, the contents of the program counter (PC) are saved to FEPC, and the contents of the program status word (PSW) are saved to FEPSW.

Except for some instructions, the address of the instruction next to the one being executed when the NMI occurs is saved to FEPC (see **Table 6-1 Interrupt/Exception Codes**).

The current value of the PSW is saved to FEPSW.

Because only one pair of NMI status saving registers is provided, the contents of these registers must be saved by program when multiple interrupt servicing is enabled.

Bits 31 to 26 of FEPC and bits 31 to 12 and 10 to 8 of FEPSW are reserved for future function expansion (fixed to 0).

Figure 2-4. NMI Status Saving Registers (FEPC, FEPSW)

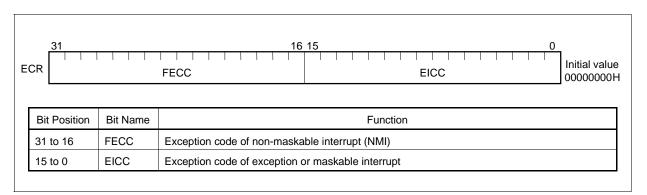

#### 2.2.3 Exception cause register (ECR)

The exception cause register (ECR) holds the cause information when an exception or interrupt occurs. The ECR holds an exception code which identifies each interrupt source (see **Table 6-1 Interrupt/Exception Codes**). This is a read-only register, and therefore no data can be written to it by using the LDSR instruction.

Figure 2-5. Exception Cause Register (ECR)

#### 2.2.4 Program status word (PSW)

The program status word (PSW) is a collection of flags that indicate the status of the program (result of instruction execution) and the status of the CPU.

If the contents of the bits in this register are modified by the LDSR instruction, the PSW will assume the new value immediately after the LDSR instruction has been executed. Setting the ID flag to 1, however, will disable interrupt requests even while the LDSR instruction is being executed.

Bits 31 to 12 and 10 to 8 are reserved for future function expansion (fixed to 0).

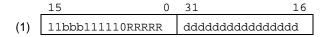

Figure 2-6. Program Status Word (PSW) (1/2)

| Γ                                                                                                                                                                                                                                                                                 | 31 |                                                                                                                 | _ |    |                 | <u> </u>                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Т                                                                                                                                                                                                                                                          | Τ    |      |      |      |     |     |     |   |    |        |       | 12  | 11     |     | 0  | 9  | 8  | 7<br>N | 6<br>E |     |     | 4           | 3<br>C | 2 | 1 | Ť | ٦., | itial ' | (alı |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----------------------------------------------------------------------------------------------------------------|---|----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-----|-----|-----|---|----|--------|-------|-----|--------|-----|----|----|----|--------|--------|-----|-----|-------------|--------|---|---|---|-----|---------|------|

| SW [                                                                                                                                                                                                                                                                              | 0  | 0                                                                                                               | 0 | 0  | 0               | 0                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                          | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0 | (  | 0      | 0     | 0   | S<br>S | (   | 0  | 0  | 0  | P      |        |     | b   | S<br>A<br>T | Υ      | ٧ | S | Z | 1   | 0000    |      |

| Bit Position Flag Name Function                                                                                                                                                                                                                                                   |    |                                                                                                                 |   |    |                 |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                            |      |      |      |      |     |     |     |   |    |        |       |     |        |     |    |    |    |        |        |     |     |             |        |   |   |   |     |         |      |

| Operates with single-step execution when this flag is set to 1 (debug trap occurs each time instruction is executed).  This flag is cleared to 0 when branching to the interrupt servicing routine.  When the SE bit of the DIR register is 0, this flag is not set (fixed to 0). |    |                                                                                                                 |   |    |                 |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                            |      | me   |      |      |     |     |     |   |    |        |       |     |        |     |    |    |    |        |        |     |     |             |        |   |   |   |     |         |      |

| 7 NP Indicates that non-maskable interrupt (NMI) servicing is in progress. This flag is set to 1 when an NMI request is acknowledged, and multiple interrupt servicing is disabled.  0: NMI servicing is not in progress  1: NMI servicing is in progress                         |    |                                                                                                                 |   |    |                 |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                            |      |      |      |      |     |     |     |   |    |        |       |     |        |     |    |    |    |        |        |     |     |             |        |   |   |   |     |         |      |

| 6                                                                                                                                                                                                                                                                                 |    |                                                                                                                 |   | EF | 0               |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Indicates that exception processing is in progress. This flag is set to 1 when an exception occurs. Even when this bit is set, interrupt requests can be acknowledged.  0: Exception processing is not in progress  1: Exception processing is in progress |      |      |      |      |     |     |     |   |    |        |       |     |        |     |    |    |    |        |        |     |     |             |        |   |   |   |     |         |      |

| 5                                                                                                                                                                                                                                                                                 |    |                                                                                                                 |   | ID |                 |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | (                                                                                                                                                                                                                                                          | 0: I | nter | rupt | s ei | nab | led | (EI | ) | in | nterru | ıpt r | equ | ies    | t c | an | be | ac | kno    | OW     | led | lge | d.          |        |   |   |   |     |         |      |

| 4                                                                                                                                                                                                                                                                                 |    |                                                                                                                 |   | SA | ΑΤ <sup>Ν</sup> | ote                                                                                                                                       | 1: Interrupts disabled (DI)  Indicates that an overflow has occurred in a saturated operation and the result is saturated. This is a cumulative flag. When the result is saturated, the flag is set to 1 and is not cleared to 0 even if the next result is not saturated. To clear this flag to 0, use the LDSR instruction. This flag is neither set to 1 nor cleared to 0 by execution of an arithmetic operation instruction.  0: Not saturated  1: Saturated |                                                                                                                                                                                                                                                            |      |      |      |      |     |     |     |   |    |        |       |     |        |     |    |    |    |        |        |     |     |             |        |   |   |   |     |         |      |

| 3                                                                                                                                                                                                                                                                                 |    |                                                                                                                 |   | C, | Y               | Indicates whether a carry or borrow occurred as a result of the operation.  0: Carry or borrow did not occur  1: Carry or borrow occurred |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                            |      |      |      |      |     |     |     |   |    |        |       |     |        |     |    |    |    |        |        |     |     |             |        |   |   |   |     |         |      |

| 2                                                                                                                                                                                                                                                                                 |    | OV <sup>Note</sup> Indicates whether overflow occurred as a result of the operation.  0: Overflow did not occur |   |    |                 |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                            |      |      |      |      |     |     |     |   |    |        |       |     |        |     |    |    |    |        |        |     |     |             |        |   |   |   |     |         |      |

**Note** Can only be used in type A or B products. Cannot be used in other product types.

1: Overflow occurred

\*

Figure 2-6. Program Status Word (PSW) (2/2)

| Bit Position | Flag Name         | Function                                                                                                         |

|--------------|-------------------|------------------------------------------------------------------------------------------------------------------|

| 1            | S <sup>Note</sup> | Indicates whether the result of the operation is negative.  0: Result is positive or zero  1: Result is negative |

| 0            | Z                 | Indicates whether the result of the operation is zero.  0: Result is not zero  1: Result is zero                 |

**Note** In the case of saturate instructions, the SAT, S, and OV flags will be set according to the result of the operation as shown in the table below. Note that the SAT flag is set to 1 only when the OV flag has been set to 1 during a saturated operation.

| Status of Operation                    |                        | Status of Flag | Operation Result of Saturation |                  |  |  |  |  |  |

|----------------------------------------|------------------------|----------------|--------------------------------|------------------|--|--|--|--|--|

| Result                                 | SAT                    | OV             | S                              | Processing       |  |  |  |  |  |

| Maximum positive value is exceeded     | 1                      | 1              | 0                              | 7FFFFFFH         |  |  |  |  |  |

| Maximum negative value is exceeded     | 1                      | 1              | 1                              | 80000000H        |  |  |  |  |  |

| Positive (Not exceeding maximum value) | Holds the value before | 0              | 0                              | Operation result |  |  |  |  |  |

| Negative (Not exceeding maximum value) | operation              |                | 1                              |                  |  |  |  |  |  |

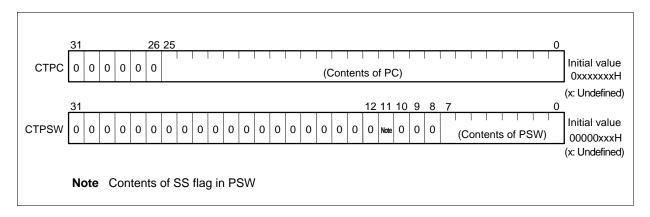

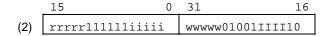

#### 2.2.5 CALLT caller status saving registers (CTPC, CTPSW)

Two CALLT caller status saving registers are provided: CTPC and CTPSW.

If a CALLT instruction is executed, the contents of the program counter (PC) are saved to CTPC, and the contents of the program status word (PSW) are saved to CTPSW.

The contents saved to CTPC are the address of the instruction next to the CALLT instruction.

The current value of the PSW is saved to CTPSW.

Bits 31 to 26 of CTPC and bits 31 to 12 and 10 to 8 of CTPSW are reserved for future function expansion (fixed to 0).

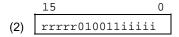

Figure 2-7. CALLT Caller Status Saving Registers (CTPC, CTPSW)

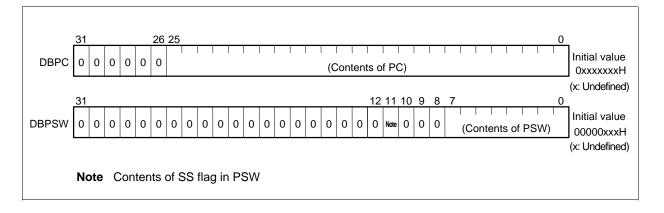

#### 2.2.6 Exception/debug trap status saving registers (DBPC, DBPSW)

Two exception/debug trap status saving registers are provided: DBPC and DBPSW.

★ When an exception trap, debug trap<sup>Note</sup>, or debug break occurs or during a single-step operation, the contents of the program counter (PC) are saved to DBPC, and the contents of the program status word (PSW) are saved to DBPSW. The contents to be saved to DBPC are as follows.

Table 2-3. Contents to Be Saved to DBPC

| Cause f                         | or Saving                 | Contents Saved to DBPC                                                                                              |  |  |  |  |  |  |

|---------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Occurrence of exception trap    |                           | Address of the instruction next to the instruction that caused an exception trap                                    |  |  |  |  |  |  |

| Occurrence of debug trap        |                           | Address of the instruction next to the instruction that caused a debug trap                                         |  |  |  |  |  |  |

| Occurrence of debug break       | Execution trap            | Address of the instruction that caused a break                                                                      |  |  |  |  |  |  |

|                                 | Misalign access exception |                                                                                                                     |  |  |  |  |  |  |

|                                 | Alignment error exception |                                                                                                                     |  |  |  |  |  |  |

|                                 | Access trap               | Address of the instruction next to the instruction that caused a break                                              |  |  |  |  |  |  |

| Single-step operation execution | on                        | Address of the instruction to be executed next (instruction executed when restoring from the debug monitor routine) |  |  |  |  |  |  |

Remark For details of causes for saving, refer to CHAPTER 9 SHIFTING TO DEBUG MODE.

The current value of the PSW is saved to DBPSW.

\* Reading from this register is enabled only in debug mode (DIR.DM bit = 1) (writing to this register is always enabled). If this register is read in user mode (DM bit = 0), an undefined value is read.

Bits 31 to 26 of DBPC and bits 31 to 12 and 10 to 8 of DBPSW are reserved for future function expansion (fixed to 0).

★ Note Type C products do not support a debug trap.

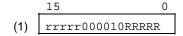

Figure 2-8. Exception/Debug Trap Status Saving Registers (DBPC, DBPSW)

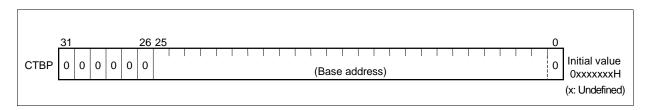

### 2.2.7 CALLT base pointer (CTBP)

The CALLT base pointer (CTBP) is used to specify a table address and to generate a target address (bit 0 is fixed to 0).

Bits 31 to 26 are reserved for future function expansion (fixed to 0).

Figure 2-9. CALLT Base Pointer (CTBP)

#### 2.2.8 Debug interface register (DIR)

The debug interface register (DIR) controls the debug function and indicates the debug function status.

The values of the bits in this register can be changed by using the LDSR instruction. Changed values become valid immediately after the execution of this instruction is complete.

This register can only be written in the debug mode (DM bit = 1) (except for bits 3 and 1) but can always be read.

Bits 14 to 8, 6 to 4, 2, and 1 are undefined in the user mode (DM bit = 0).

Bits 31 to 15 and 7 are reserved for future function expansion (fixed to 0).

★ Caution Use of the debug interface register (DIR) is possible only in type A and B products, not in other product types.

Figure 2-10. Debug Interface Register (DIR) (1/3)

|              |    | 31 |   |   |   |       |     |    |   |   |   |   |   |   |   |   |   | 15 | 14     | 13     | 12     | 11     | 10     | 9  | 8      | 7 | 6      | 5      | 4      | 3      | 2      | 1_ | 0 | _                          |

|--------------|----|----|---|---|---|-------|-----|----|---|---|---|---|---|---|---|---|---|----|--------|--------|--------|--------|--------|----|--------|---|--------|--------|--------|--------|--------|----|---|----------------------------|

| D            | IR | 0  | 0 | 0 | 0 | 0     | 0   | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | S<br>Q | R<br>E | C<br>S | C<br>E | M<br>A |    | S<br>E | 0 | I<br>N | T<br>1 | T<br>0 | C<br>M | M<br>T |    |   | Initial value<br>00000040H |

| Bit Position |    |    |   |   | Е | Bit N | lam | ne |   |   |   |   |   |   |   |   |   |    |        |        |        | Fur    | nctic  | on |        |   |        |        |        |        |        |    |   |                            |

|              |    |    |   |   |   |       |     |    |   |   |   |   |   |   |   |   |   |    |        |        |        |        |        |    |        |   |        |        |        |        |        |    |   |                            |

SQ<sup>Notes 1, 2</sup> 14 Sets sequential break mode (sets a break if a break occurs for channel 0 and channel 1 in that 0: Normal break mode 1: Sequential break mode RE<sup>Notes 1, 2</sup> 13 Sets range break mode (sets a break only when a break occurs for channels 0 and 1 simultaneously). 0: Normal break mode 1: Range break mode CSNote 2 12 Sets break register bank. 0: Select bank 0 register (channel 0 control register) 1: Select bank 1 register (channel 1 control register) 11 CE Enables/disables COMBO interrupt. 0: COMBO interrupt disabled 1: COMBO interrupt enabled 10 MA Enables/disables misalign access exception detection. 0: Misalign access exception detection disabled 1: Misalign access exception detection enabled 9 ΑE Enables/disables alignment error exception detection. 0: Alignment error exception detection disabled 1: Alignment error exception detection enabled

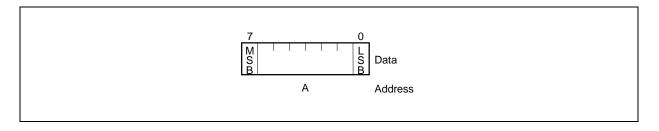

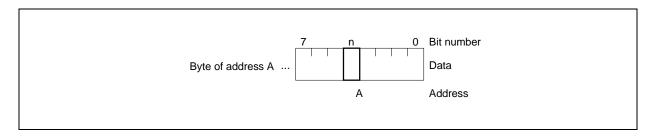

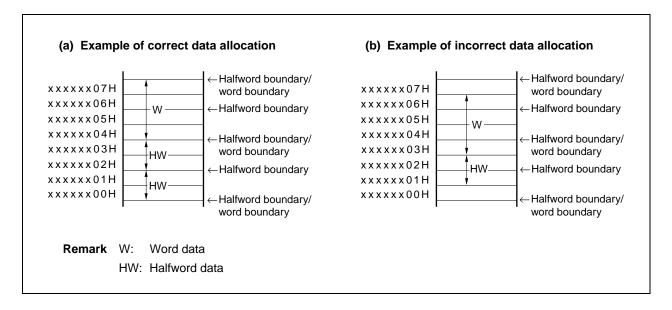

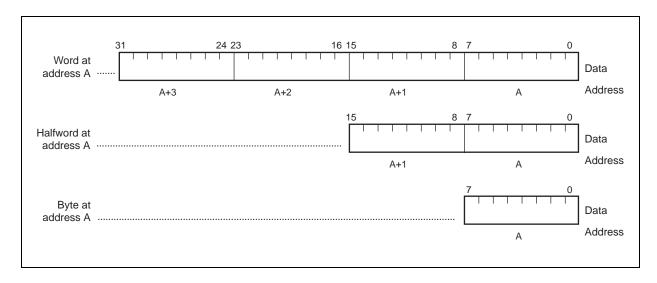

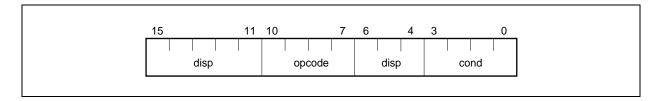

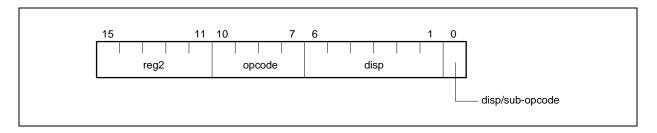

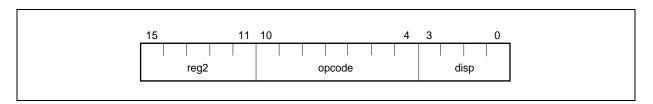

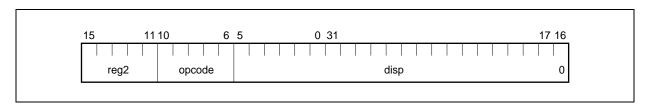

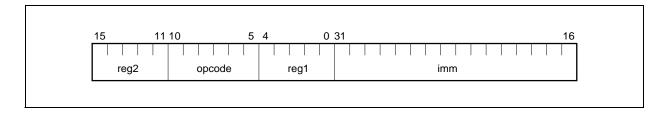

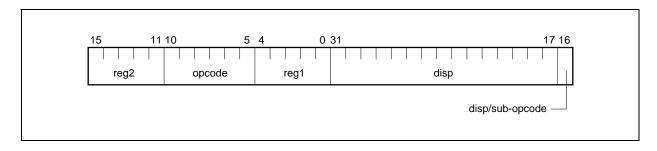

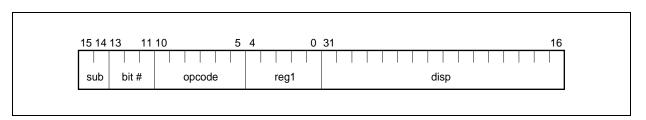

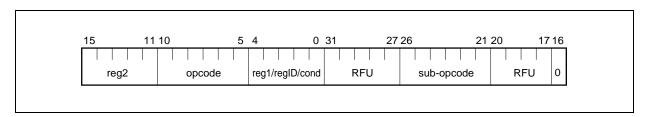

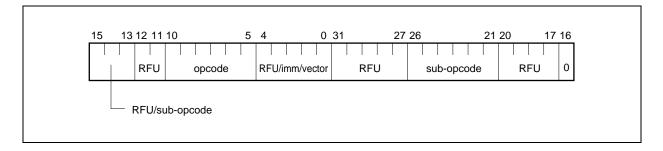

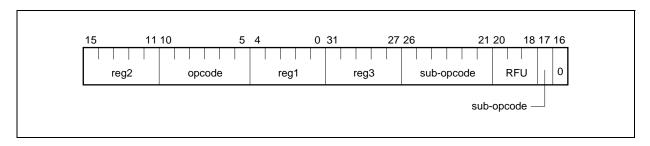

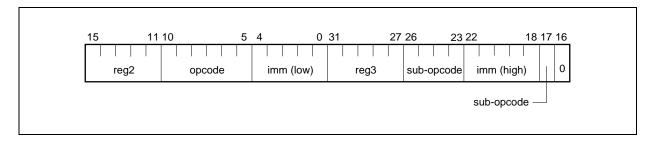

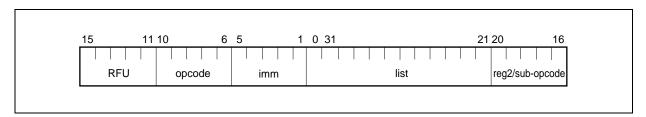

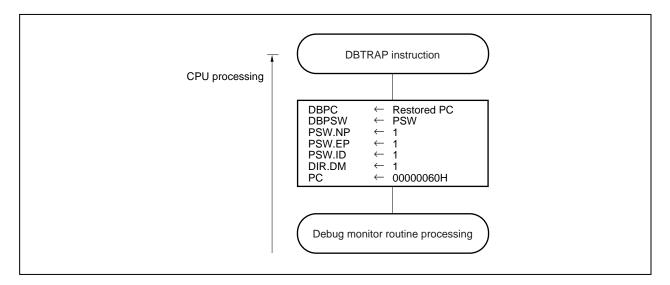

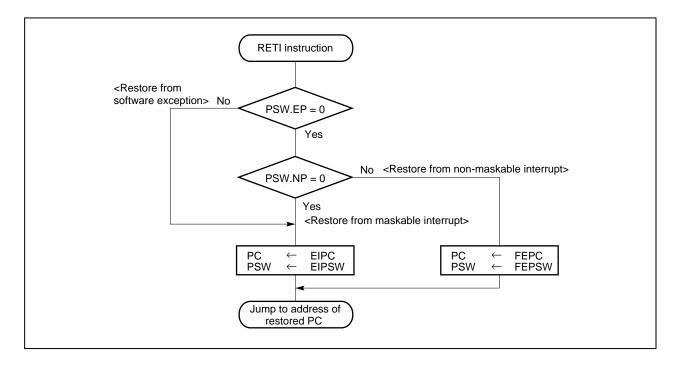

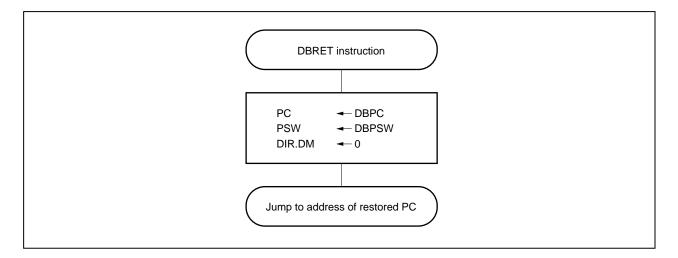

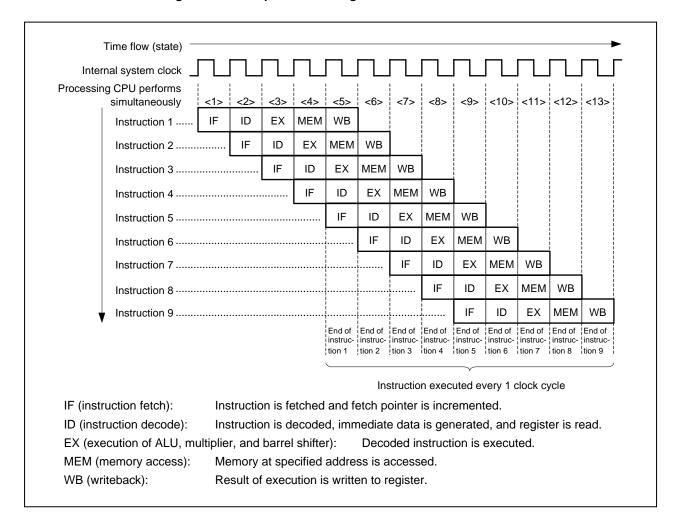

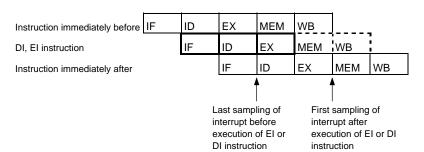

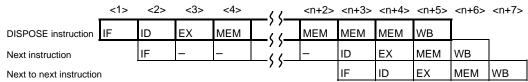

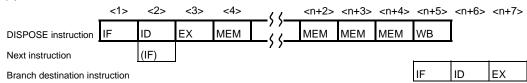

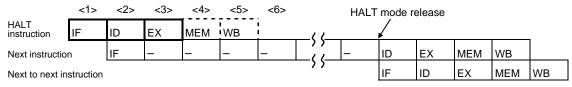

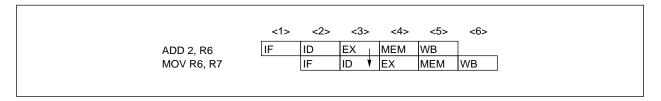

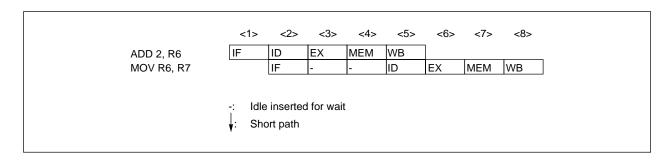

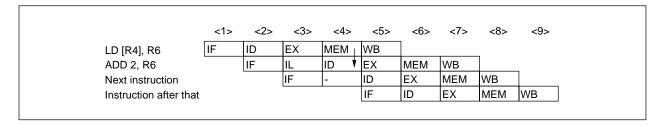

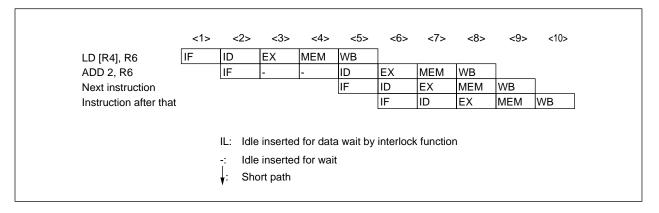

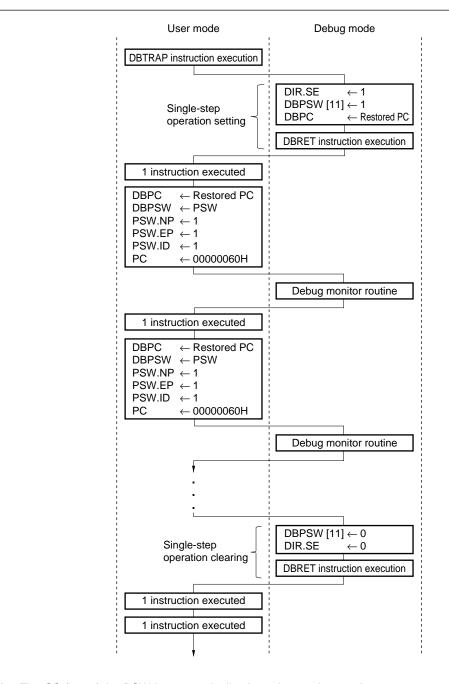

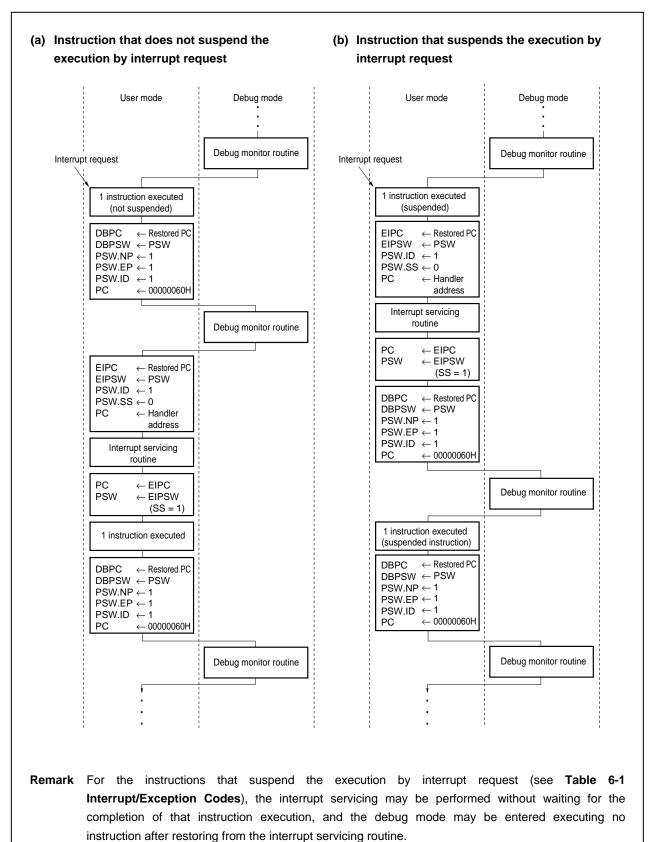

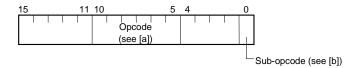

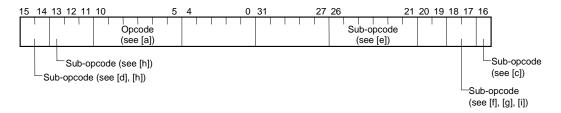

**Notes 1.** Always set either the SQ or RE bit to 1 or clear both bits to 0. If both bits are set to 1, the operation cannot be guaranteed.