# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

**User's Manual**

# **μPD77210 Family**

# **Digital Signal Processor**

Architecture

μ**PD77210** μ**PD77213**

Document No. U15807EJ2V0UM00 (2nd edition) Date Published May 2002 N CP(K)

© NEC Corporation 2002 Printed in Japan [MEMO]

#### **①** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

### **②** HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

# **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

The export of this product from Japan is regulated by the Japanese government. To export this product may be prohibited without governmental license, the need for which must be judged by the customer. The export or re-export of this product from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

License not needed:  $\mu$ PD77210F1-DA2,  $\mu$ PD77210GJ-8EN The customer must judge the need for license:  $\mu$ PD77213F1-xxx-DA2,  $\mu$ PD77213GJ-xxx-8EN

- The information in this document is current as of May, 2002. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data books, etc., for the most up-to-date specifications of NEC semiconductor products. Not all products and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this document.

- NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC semiconductor products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customers

agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize

risks of damage to property or injury (including death) to persons arising from defects in NEC

semiconductor products, customers must incorporate sufficient safety measures in their design, such as

redundancy, fire-containment, and anti-failure features.

- NEC semiconductor products are classified into the following three quality grades:

"Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor products

developed based on a customer-designated "quality assurance program" for a specific application. The

recommended applications of a semiconductor product depend on its quality grade, as indicated below.

Customers must check the quality grade of each semiconductor product before using it in a particular

application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC's data sheets or data books, etc. If customers wish to use NEC semiconductor products in applications not intended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingness to support a given application.

(Note)

- (1) "NEC" as used in this statement means NEC Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC semiconductor products" means any semiconductor product developed or manufactured by or for NEC (as defined above).

M8E 00.4

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- Ordering information

- Product release schedule

- Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### NEC Electronics Inc. (U.S.)

Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

#### NEC do Brasil S.A.

Electron Devices Division Guarulhos-SP, Brasil Tel: 11-6462-6810 Fax: 11-6462-6829

#### NEC Electronics (Europe) GmbH

Duesseldorf, Germany Tel: 0211-65 03 01 Fax: 0211-65 03 327

- Sucursal en España Madrid, Spain Tel: 091-504 27 87 Fax: 091-504 28 60

- Succursale Française Vélizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

- Filiale Italiana Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

- Branch The Netherlands Eindhoven, The Netherlands Tel: 040-244 58 45 Fax: 040-244 45 80

- Branch Sweden Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388

- United Kingdom Branch Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

#### NEC Electronics Hong Kong Ltd. Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

NEC Electronics Hong Kong Ltd. Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

#### NEC Electronics Shanghai, Ltd.

Shanghai, P.R. China Tel: 021-6841-1138 Fax: 021-6841-1137

#### **NEC Electronics Taiwan Ltd.**

Taipei, Taiwan Tel: 02-2719-2377 Fax: 02-2719-5951

#### NEC Electronics Singapore Pte. Ltd.

Novena Square, Singapore Tel: 253-8311 Fax: 250-3583

J02.4

#### INTRODUCTION

| Target Readers             | This manual is intended for users who understand the functions of $\mu$ PD77210 Family devices and who design application systems (hardware and software) using these products.                                                                                                                                                                                                                                                            |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | The $\mu$ PD77210 Family is the general name for the $\mu$ PD77210 and $\mu$ PD77213 devices. Unless functional differences are otherwise specified, the descriptions in this manual apply to all $\mu$ PD77210 Family devices. Particular product names are specified when functional differences exist.                                                                                                                                  |

| Purpose                    | This manual's purpose is to help the user understand the hardware and software functions of the $\mu$ PD77210 Family devices, as listed below, and to serve as a reference for development of hardware and software in systems using these devices.                                                                                                                                                                                        |

| Organization               | <ul> <li>This manual consists of the following chapters:</li> <li>CHAPTER 1 GENERAL</li> <li>CHAPTER 2 PIN FUNCTIONS</li> <li>CHAPTER 3 USE METHODS</li> <li>CHAPTER 4 ARCHITECTURE</li> <li>CHAPTER 5 PERIPHERALS</li> <li>CHAPTER 6 BOOT FUNCTIONS</li> <li>APPENDIX A INDEX</li> </ul>                                                                                                                                                  |

| How to Read<br>This Manual | This manual assumes that the reader has general knowledge of electricity, logic circuits, and microcomputers.<br>• For a general understanding of $\mu$ PD77210 Family basic functions:                                                                                                                                                                                                                                                    |

|                            | <ul> <li>→ Start reading this manual from CHAPTER 1 GENERAL.</li> <li>For hardware engineers and software engineers:</li> <li>→ Read this manual from CHAPTER 1 GENERAL to CHAPTER 6 BOOT FUNCTIONS.<br/>The device's various internal function blocks are described in CHAPTER 4<br/>ARCHITECTURE. The functions related to peripherals such as interfaces, timers, and<br/>interrupts are described in CHAPTER 5 PERIPHERALS.</li> </ul> |

|                            | <ul> <li>For others who will use this as a reference manual:         <ul> <li>→ Refer to the index at the end of the manual. Use the terms in the index as keywords for searching.</li> </ul> </li> </ul>                                                                                                                                                                                                                                  |

|                            | • <b>CHAPTER 3 USE METHODS</b> describes the overall use of $\mu$ PD77210 Family devices, from power-on to execution of user programs. Be sure to read this chapter before using a $\mu$ PD77210 Family device.                                                                                                                                                                                                                            |

|                            | <ul> <li>For description of the instruction language used in μPD77210 Family devices, see the μPD77016 Family Architecture User's Manual.</li> </ul>                                                                                                                                                                                                                                                                                       |

| Conventions | Data significance:         | Higher digits on the left and lower digits on the right                             |

|-------------|----------------------------|-------------------------------------------------------------------------------------|

|             | Active low representation: | $\overline{\times\!\!\times\!\!\times\!\!\times}$ (pin or signal name is overlined) |

|             | Note:                      | Footnote for item marked with Note in the text                                      |

|             | Caution:                   | Information requiring particular attention                                          |

|             | Remark:                    | Supplemental information                                                            |

|             | Numeric notation:          | Binary XXXX or ObXXXX                                                               |

|             |                            | Decimal xxxx                                                                        |

|             |                            | Hexadecimal 0x××××                                                                  |

**Related Documents:** The related documents listed below may include preliminary versions. However, preliminary versions are not marked as such.

#### Documents Related to µPD77210

| Document Name | Pamphlet | Data Sheet | User's Manual |              | Application Note |

|---------------|----------|------------|---------------|--------------|------------------|

| Part Number   |          |            | Architecture  | Instructions | Basic Software   |

| μ PD77210     | U12395E  | U15203E    | This manual   | U13116E      | U11958E          |

| μ PD77213     |          |            |               |              |                  |

#### **Documents Related to Development Tools**

| Document Name            | Document No.       |         |

|--------------------------|--------------------|---------|

| RX77016 User's Manual    | Function           | U14397E |

|                          | Configuration Tool | U14404E |

| RX77016 Application Note | HOST API           | U14371E |

#### **Documents Related to Middleware**

| Document Name               | Document No. |

|-----------------------------|--------------|

| μSAP77016-B01 User's Manual | U13130E      |

| μSAP77016-B03 User's Manual | U13373E      |

| μSAP77016-B04 User's Manual | U13955E      |

| μSAP77016-B05 User's Manual | U14497E      |

| μSAP77016-B06 User's Manual | U15165E      |

| μSAP77016-B07 User's Manual | U15134E      |

| μSAP77016-B08 User's Manual | U15152E      |

| μSAP77016-B11 User's Manual | U15683E      |

Caution The related documents listed above are subject to change without notice. Be sure to use the latest version of each document for designing.

#### CONTENTS

| СНАР | PTER 1 GENERAL                                             |    |

|------|------------------------------------------------------------|----|

| 1.1  | Comparison with $\mu$ PD77111 Family                       |    |

|      | 1.1.1 High-speed operation                                 | 17 |

|      | 1.1.2 Low power consumption                                |    |

|      | 1.1.3 Expanded peripheral functions                        |    |

| 1.2  | Features                                                   |    |

|      | 1.2.1 DSP core kernel                                      |    |

|      | 1.2.2 Peripheral block                                     |    |

|      | 1.2.3 Ordering information                                 |    |

| СНАР | PTER 2 PIN FUNCTIONS                                       |    |

| 2.1  | Pin Connection                                             |    |

|      | 2.1.1 161-pin plastic fine pitch BGA ( $10 \times 10$ )    |    |

|      | 2.1.2 144-pin plastic LQFP (fine pitch) ( $20 \times 20$ ) |    |

| 2.2  | Pin Configuration                                          |    |

| 2.3  | Pin Functions                                              |    |

| 2.4  | Connection of Unused Pins                                  | 35 |

| СНАР | TER 3 USE METHODS                                          |    |

| 3.1  | From Power-on to Program Execution                         |    |

|      | 3.1.1 Power-on                                             |    |

|      | 3.1.2 Reset                                                |    |

|      | 3.1.3 Boot                                                 |    |

|      | 3.1.4 Program execution                                    |    |

| 3.2  | Standby Mode                                               |    |

| 3.3  | Clock Settings After Boot Operation                        |    |

| СНАР | PTER 4 ARCHITECTURE                                        |    |

| 4.1  | Overall Block Configuration                                |    |

| 4.2  | Buses                                                      |    |

|      | 4.2.1 Main bus                                             |    |

|      | 4.2.2 Data bus                                             |    |

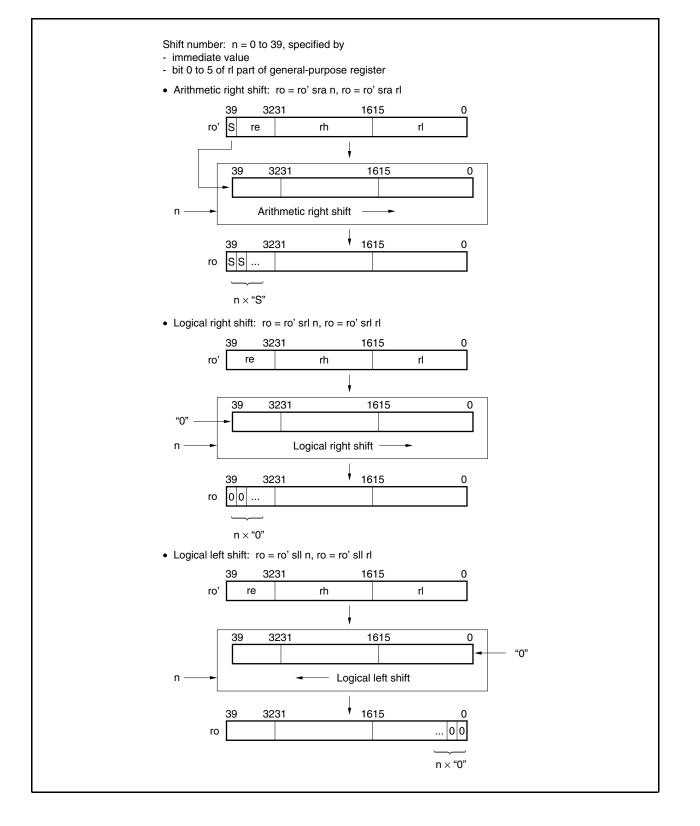

|      | 4.2.3 Peripheral $\leftrightarrow$ memory transfer bus     |    |

| 4.3  | System Control Units                                       |    |

|      | 4.3.1 Clock generator                                      |    |

|      | 4.3.2 Reset function                                       |    |

|      | 4.3.3 Pipeline architecture                                |    |

|      | 4.3.4 Standby functions                                    |    |

| 4.4  | Program Control Unit                                       |    |

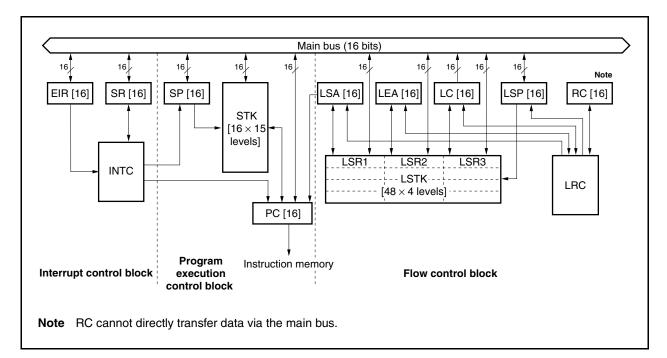

|      | 4.4.1 Block configuration                                  |    |

|      | 4.4.2 Program execution control block                      |    |

|      | 4.4.3 Flow control block                                   |    |

|      | 4.4.4  | Interrupts                                                                     | 77  |

|------|--------|--------------------------------------------------------------------------------|-----|

|      | 4.4.5  | Error status register (ESR)                                                    | 89  |

| 4.5  | Data / | Addressing Unit                                                                | 90  |

|      | 4.5.1  | Block configuration                                                            | 90  |

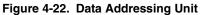

|      | 4.5.2  | Data memory space                                                              | 90  |

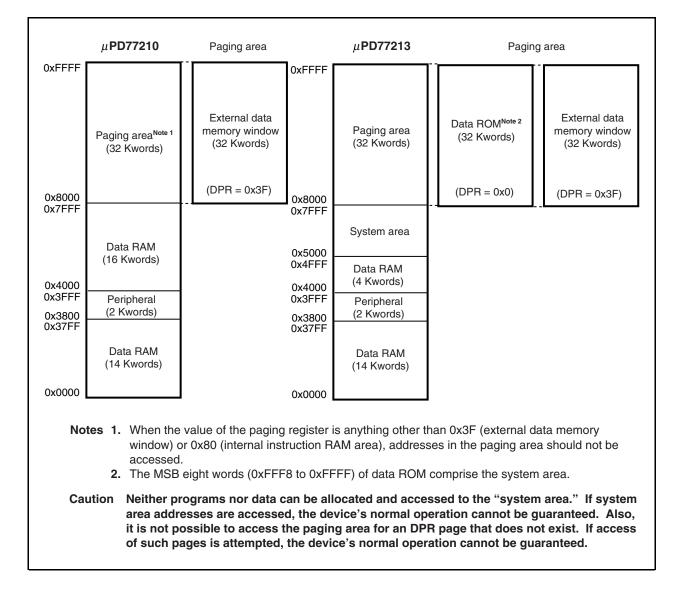

|      | 4.5.3  | Instruction memory aliasing                                                    | 94  |

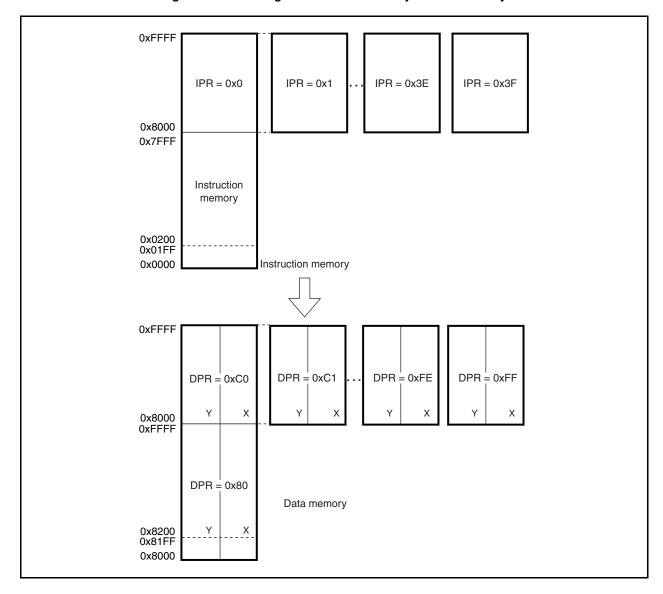

|      | 4.5.4  | External data memory map                                                       | 95  |

|      | 4.5.5  | Addressing mode                                                                | 97  |

| 4.6  | Opera  | tion Unit                                                                      | 108 |

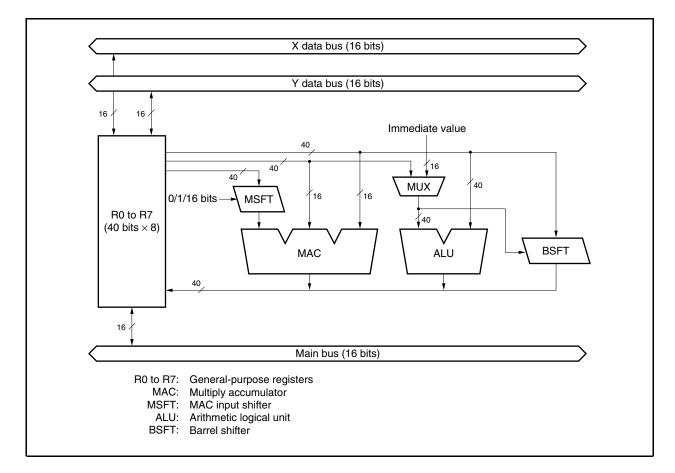

|      | 4.6.1  | Block configuration                                                            | 109 |

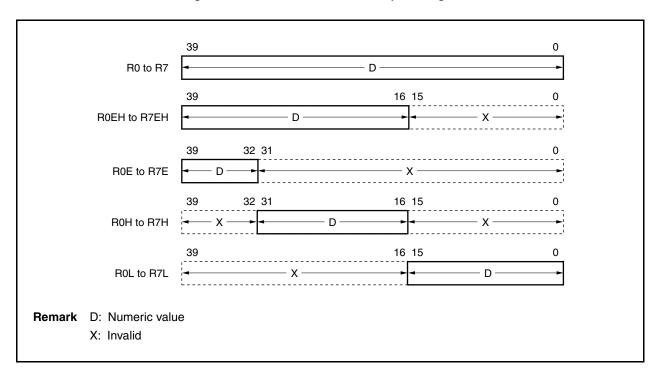

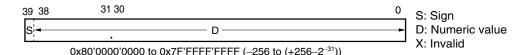

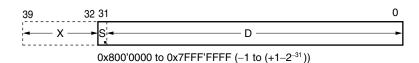

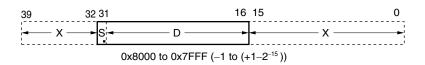

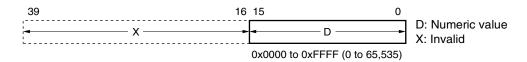

|      | 4.6.2  | General-purpose registers and data formats                                     | 109 |

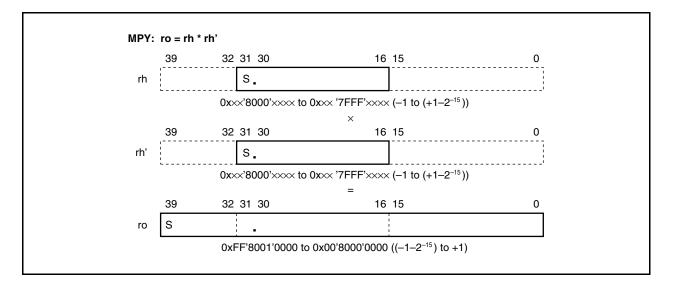

|      | 4.6.3  | Operation functions of multiply accumulator (MAC) and MAC input shifter (MSFT) | 113 |

|      | 4.6.4  | Operation functions of arithmetic and logic unit (ALU)                         | 121 |

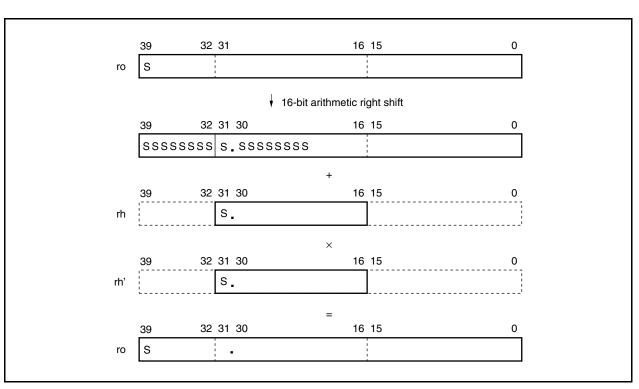

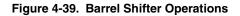

|      | 4.6.5  | Operation functions of barrel shifter (BSFT)                                   | 123 |

| СНАР | TER :  | 5 PERIPHERALS                                                                  | 125 |

| 5.1  | Block  | Configuration                                                                  | 126 |

| 5.2  | Peripl | neral Registers                                                                | 127 |

| 5.3  | Time   | Division Multiplexing (TDM) Serial Interface (TSIO)                            | 130 |

|      | 5.3.1  | TDM serial interface pins                                                      |     |

|      | 5.3.2  | TDM serial interface registers                                                 | 132 |

|      | 5.3.3  | Timing of TDM serial interface                                                 |     |

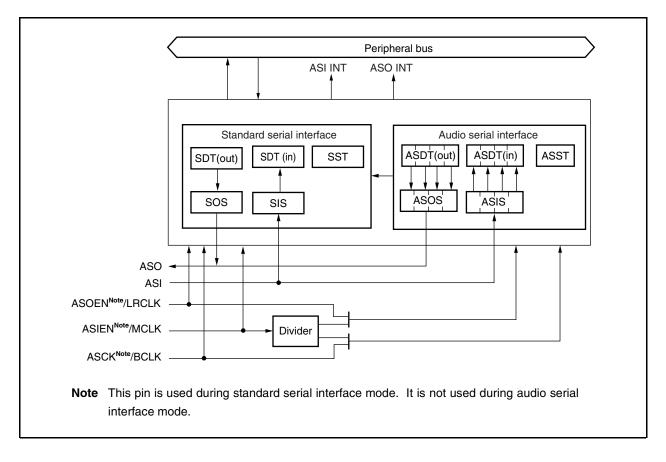

| 5.4  | Audio  | Serial Interface (ASIO)                                                        | 139 |

|      | 5.4.1  | Audio serial interface pins                                                    |     |

|      | 5.4.2  | Audio serial interface registers                                               |     |

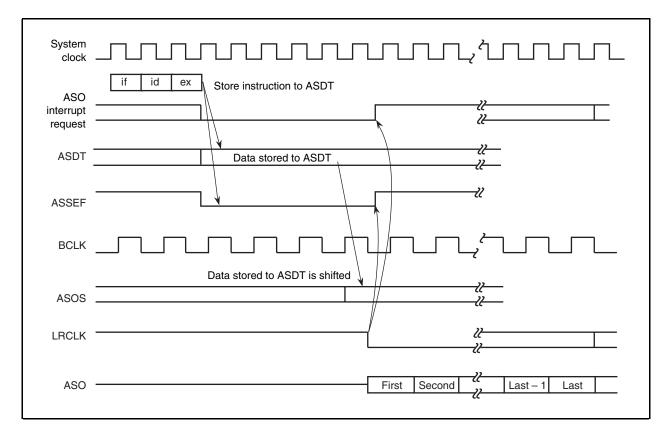

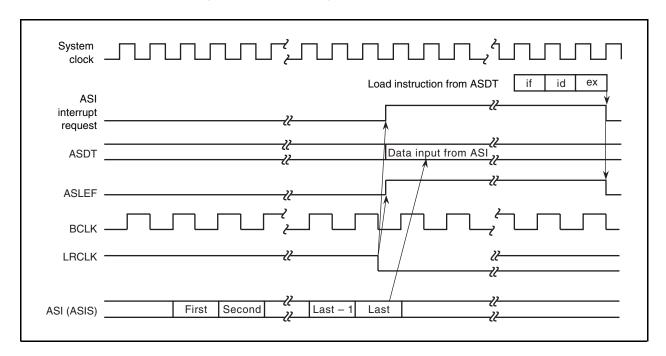

|      | 5.4.3  | Timing of audio serial interface                                               |     |

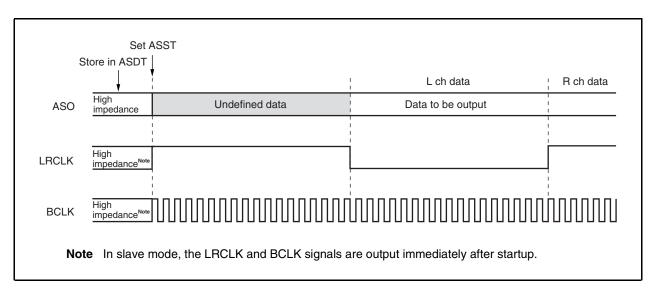

|      | 5.4.4  | Precautions on ASIO during startup                                             | 147 |

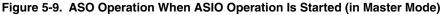

| 5.5  | Stand  | ard Serial Interface (SIO)                                                     | 148 |

|      | 5.5.1  | Standard serial interface pins                                                 |     |

|      | 5.5.2  | Standard serial interface registers                                            |     |

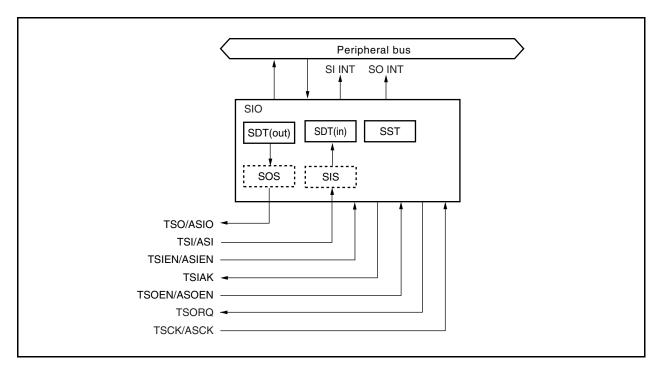

|      | 5.5.3  | Timing of serial interface                                                     | 153 |

|      | 5.5.4  | Precautions on SIO during startup                                              | 161 |

| 5.6  | Host I | nterface (HIO)                                                                 | 162 |

|      | 5.6.1  | Host interface pins                                                            | 163 |

|      | 5.6.2  | Host interface registers                                                       | 164 |

|      | 5.6.3  | Host interface registers from perspective of host                              | 166 |

|      | 5.6.4  | Timing of host interface                                                       | 167 |

| 5.7  | Exteri | nal Data Memory Interface (MIO)                                                | 172 |

|      | 5.7.1  | Memory interface pins                                                          | 174 |

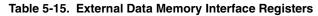

|      | 5.7.2  | External data memory interface registers                                       | 174 |

|      | 5.7.3  | Direct access                                                                  | 180 |

|      | 5.7.4  | DMA access                                                                     | 181 |

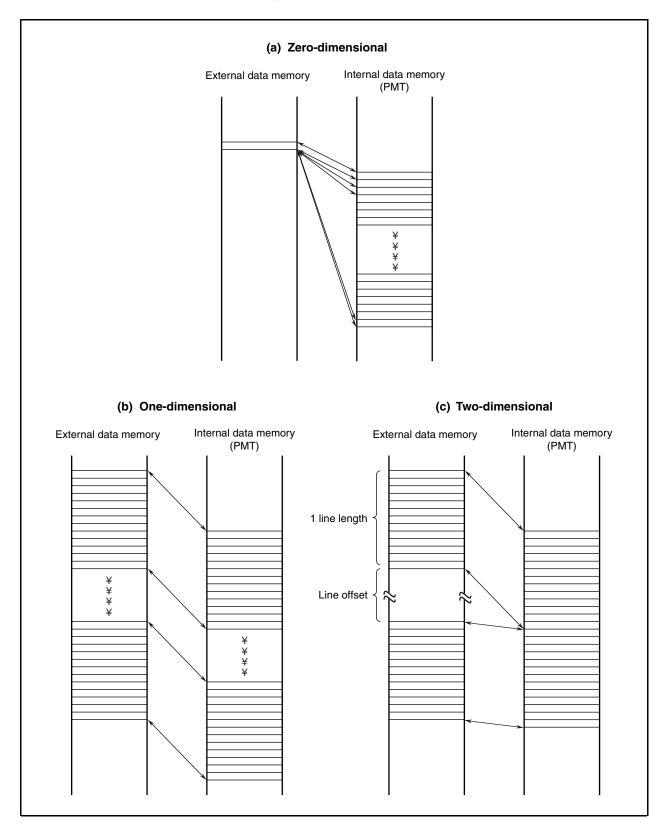

|      | 5.7.5  | Direct access timing                                                           | 183 |

|      | 5.7.6  | DMA access timing                                                              | 184 |

|      | 5.7.7  | Timing of memory access                                                        | 185 |

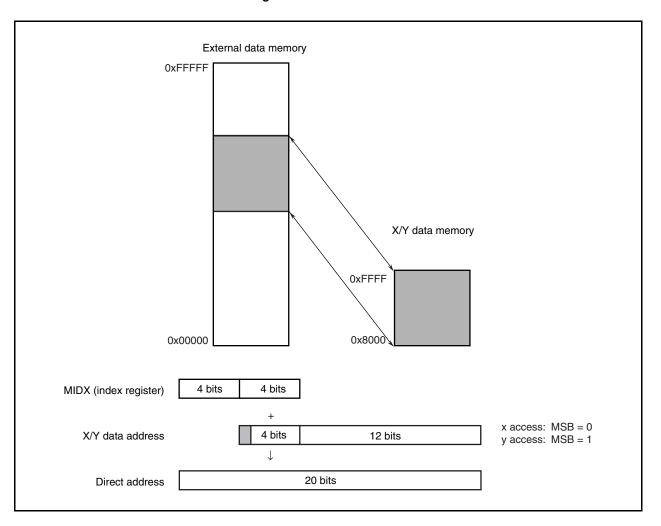

| 5.8  | Peripł | neral $\leftrightarrow$ Memory Transfer (PMT)                                  | 187 |

|      | 5.8.1   | PMT registers                                                     | 189 |

|------|---------|-------------------------------------------------------------------|-----|

|      | 5.8.2   | PMT operation modes                                               | 191 |

|      | 5.8.3   | PMT transfer steps                                                | 192 |

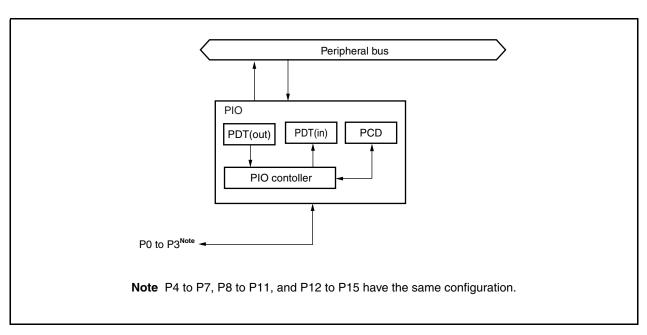

| 5.9  | Genera  | al-Purpose I/O Port (PIO)                                         | 193 |

|      | 5.9.1   | General-purpose I/O port pins                                     | 193 |

|      | 5.9.2   | General-purpose I/O port registers                                | 194 |

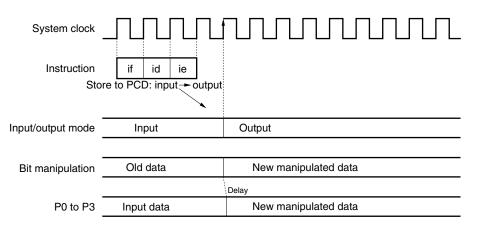

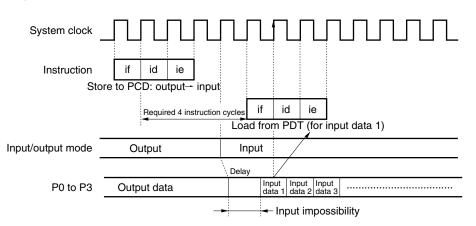

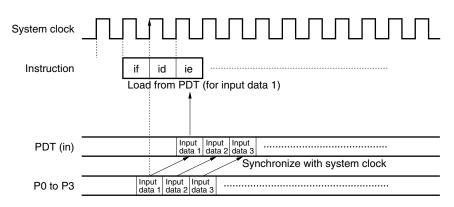

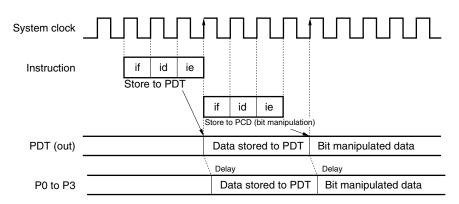

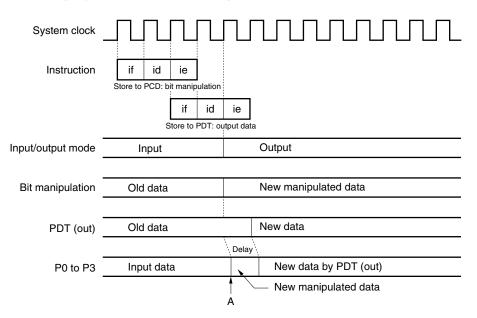

|      | 5.9.3   | Timing of general-purpose I/O port                                | 196 |

|      | 5.9.4   | Example of port programming                                       | 200 |

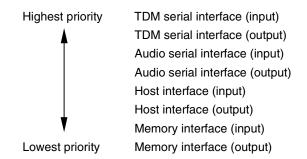

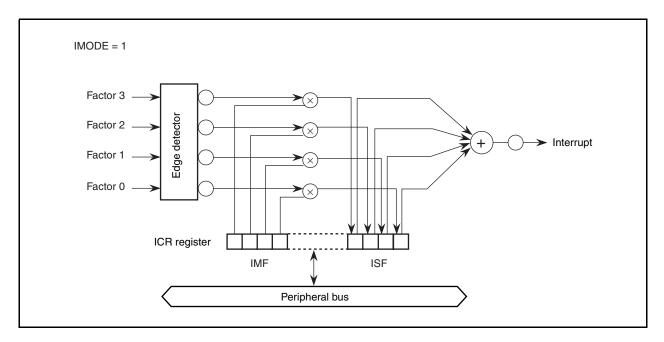

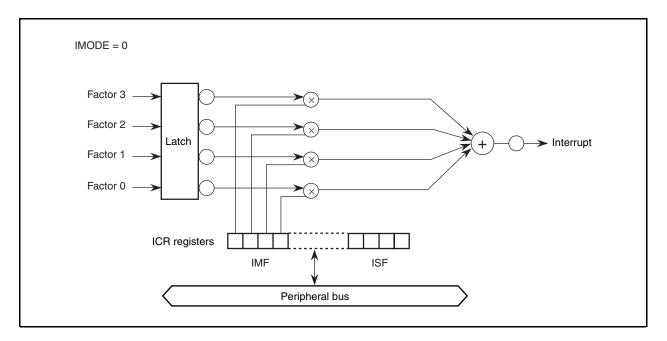

| 5.10 | Interru | pt Controller (INTC)                                              | 201 |

|      | 5.10.1  | Interrupt controller's registers                                  | 202 |

|      | 5.10.2  | Operation modes of interrupt controller                           | 203 |

|      | 5.10.3  | Interrupt table                                                   | 204 |

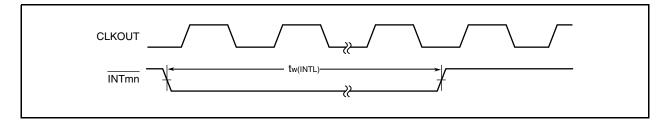

|      | 5.10.4  | Hardware conditions during interrupt from external interrupt pins | 205 |

|      | 5.10.5  | Interrupt-related precautions                                     | 206 |

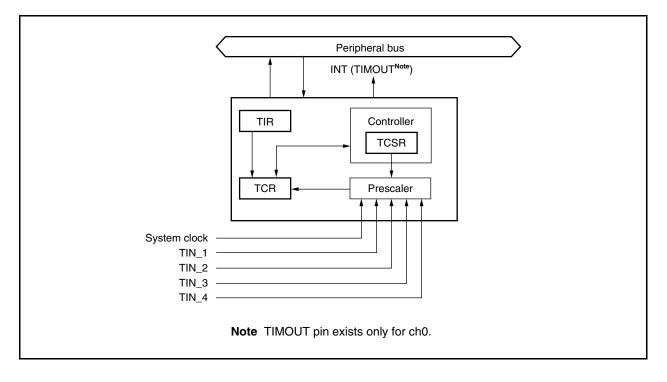

| 5.11 | Timer   | (TIM)                                                             | 209 |

|      | 5.11.1  | Timer pins                                                        | 210 |

|      | 5.11.2  | Timer registers                                                   | 210 |

|      | 5.11.3  | Operation of timer                                                | 212 |

|      | 5.11.4  | Precautions on use of timer                                       | 212 |

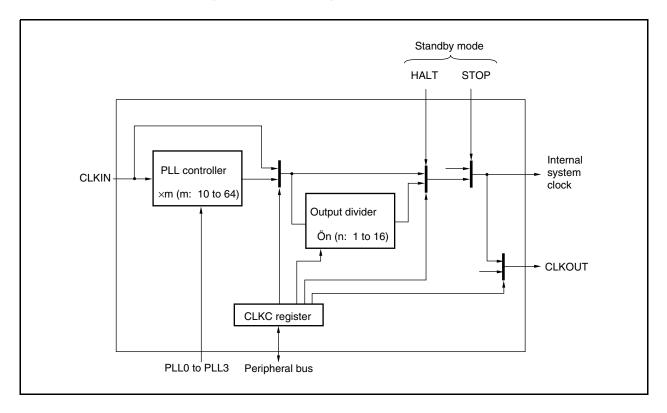

| 5.12 | Clock   | Controller (CLKC)                                                 | 213 |

|      | 5.12.1  | Clock controller's register                                       | 214 |

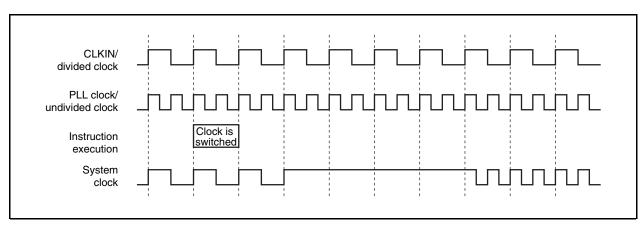

|      | 5.12.2  | Timing of clock switching                                         | 216 |

|      | 5.12.3  | Precaution points on clock control                                | 217 |

| 5.13 | Instruc | ction Memory Correction Function (IMC)                            | 221 |

|      | 5.13.1  | Registers for instruction memory correction function              | 221 |

|      | 5.13.2  | Operation of instruction correction function                      | 222 |

| 5.14 | Paging  | g Function                                                        | 222 |

|      | 5.14.1  | Registers for paging function                                     | 223 |

|      | 5.14.2  | Operation of paging function                                      | 223 |

| 5.15 | Periph  | eral STOP Mode                                                    | 224 |

|      | 5.15.1  | Peripheral STOP mode register                                     | 224 |

|      | 5.15.2  | Operation of peripheral STOP mode                                 | 225 |

| 5.16 | Debug   | Interface (IEIO)                                                  | 225 |

|      | 5.16.1  | JTAG port                                                         | 225 |

|      | 5.16.2  | Debug interface pins                                              | 226 |

|      | 5.16.3  | Boundary scan test function                                       | 226 |

|      | 5.16.4  | Debug function (in-circuit emulator function)                     | 227 |

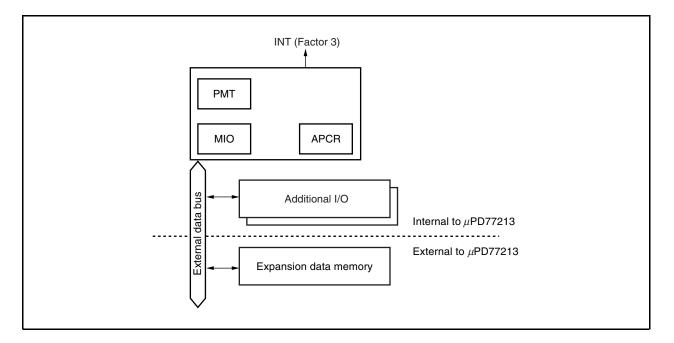

| 5.17 | Expan   | sion Interfaces (Additional I/O)                                  | 228 |

|      | 5.17.1  | Expansion interface register                                      | 229 |

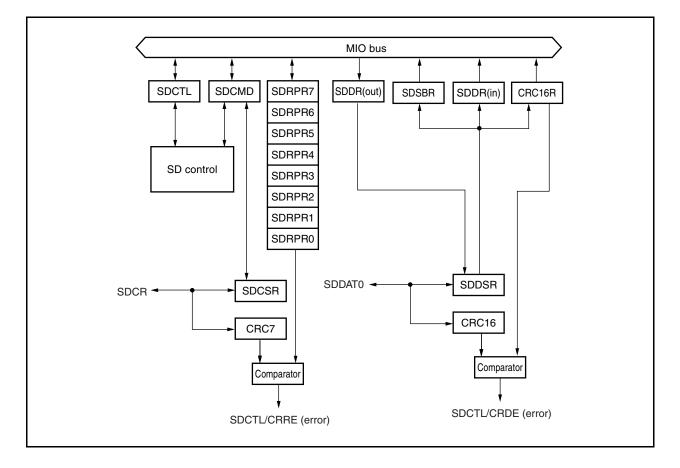

| 5.18 | SD Ca   | rd Interface (SDCIF)                                              | 230 |

|      | 5.18.1  | SD card interface pins                                            | 231 |

|      | 5.18.2  | SD card interface registers                                       | 232 |

|      | 5.18.3  | CRC (Cyclic Redundancy Codes) circuit                             | 237 |

|      | 5.18.4  | Operation of SD card interface                                    | 238 |

|      |         |                                                                   |     |

| СНАР | TER 6   | BOOT FUNCTIONS                                                    | 240 |

|      |         |                                                                   |     |

| 6.1  | Initial | Reset Boot                | 240 |

|------|---------|---------------------------|-----|

|      | 6.1.1   | Boot mode specification   | 240 |

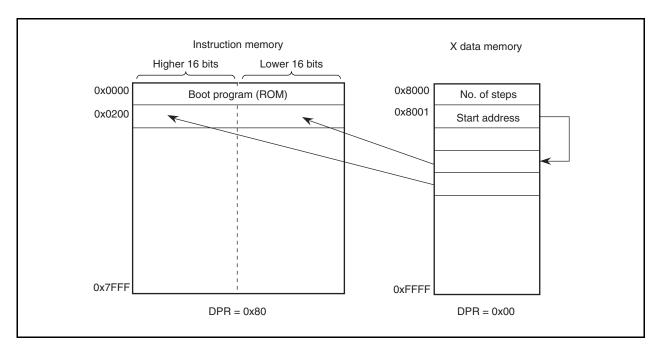

|      | 6.1.2   | X memory boot             | 241 |

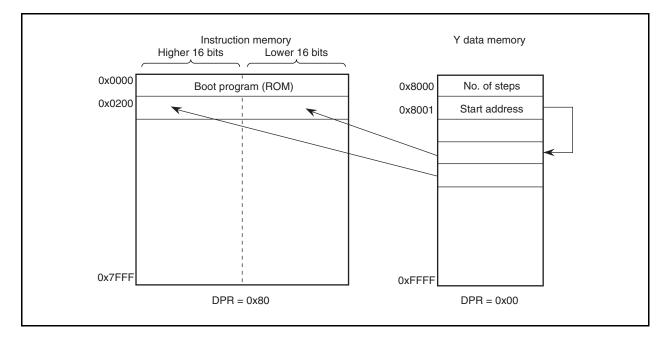

|      | 6.1.3   | Y memory boot             | 242 |

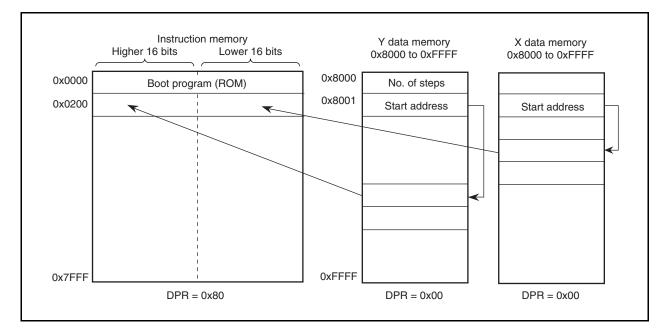

|      | 6.1.4   | XY memory boot            | 243 |

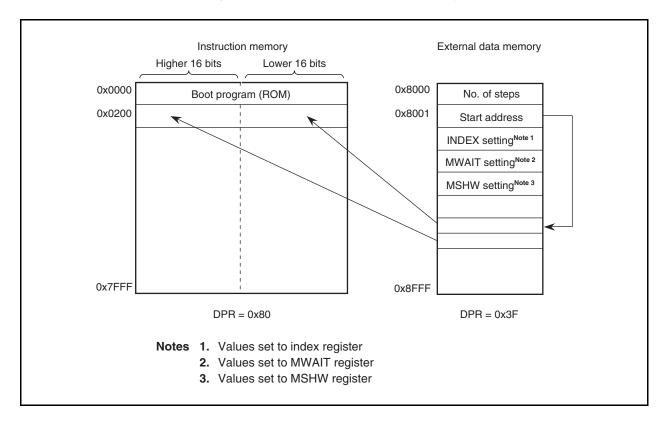

|      | 6.1.5   | External data memory boot | 244 |

|      | 6.1.6   | Host boot                 | 245 |

|      | 6.1.7   | Serial boot               |     |

|      | 6.1.8   | Non-boot                  |     |

| 6.2  | Initial | Reset Boot and PLL        | 248 |

| 6.3  | Reboo   | ot                        | 249 |

| APPE | NDIX    | A INDEX                   | 250 |

| A.1  | Termi   | nology Index              | 250 |

| A.2  | Regis   | ter Index                 |     |

|      | A.2.1   | Register name order       |     |

|      | A.2.2   | Register symbol order     | 256 |

# LIST OF FIGURES (1/3)

| Figure       | No. Title                                                            | Page |

|--------------|----------------------------------------------------------------------|------|

| 0.4          |                                                                      | 00   |

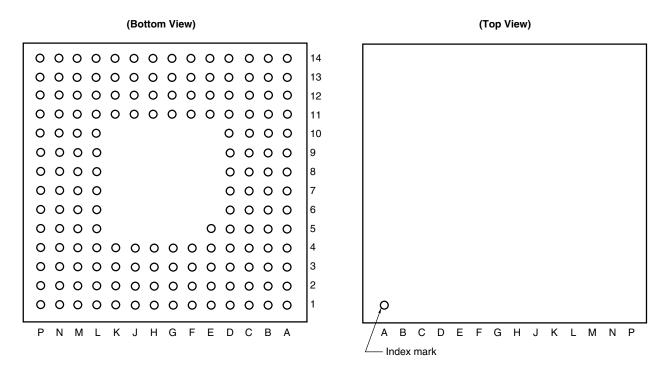

| 2-1          | 161-Pin Plastic Fine Pitch BGA                                       |      |

| 2-2          | 144-Pin Plastic LQFP                                                 |      |

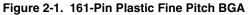

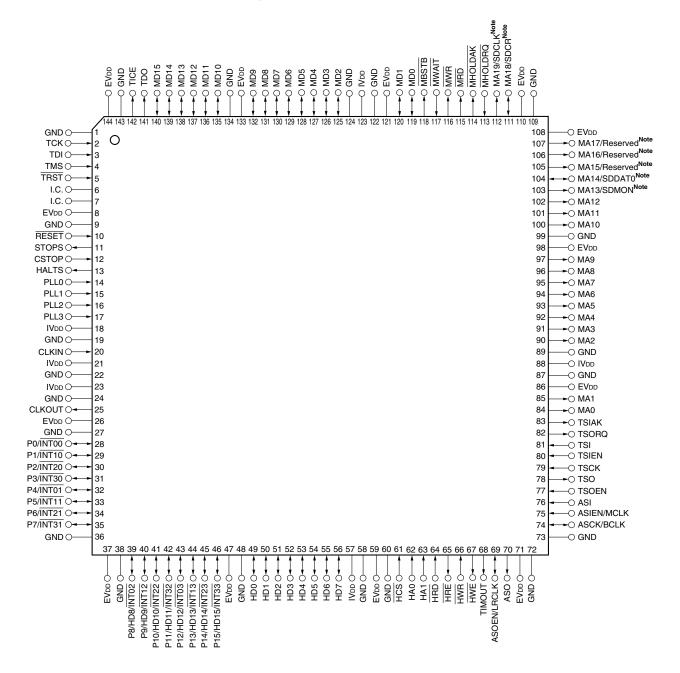

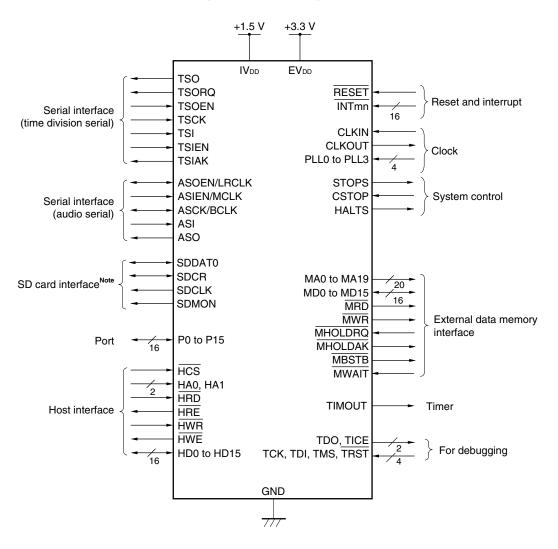

| 2-3          | Pin Configuration                                                    |      |

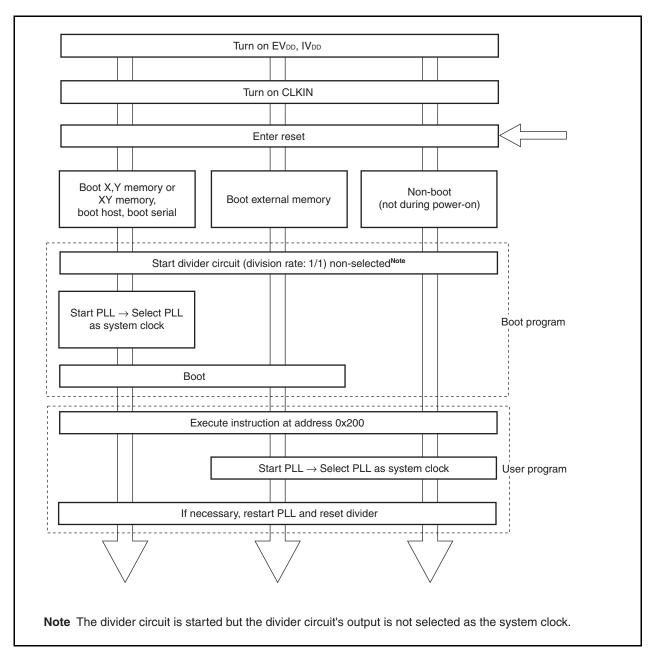

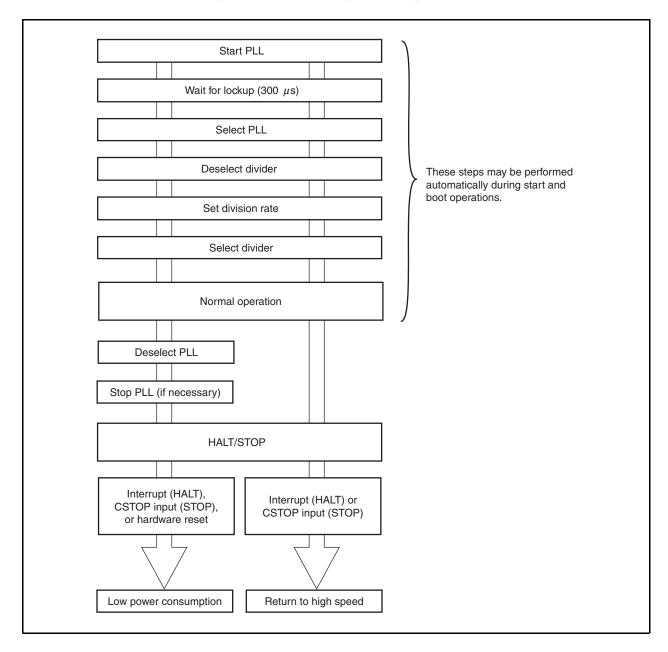

| 3-1          | From Power-On to User Program Execution                              |      |

| 3-2          | From Starting to Stopping the PLL                                    | 40   |

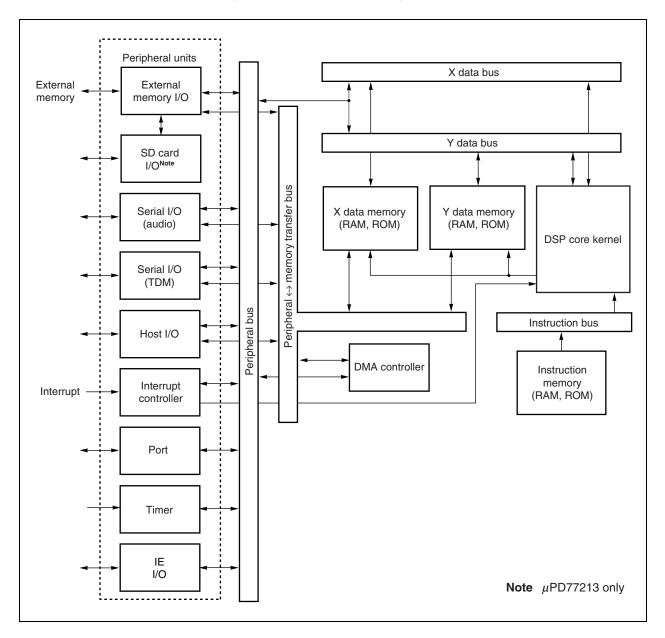

| 4-1          | Overall Block Configuration                                          | 40   |

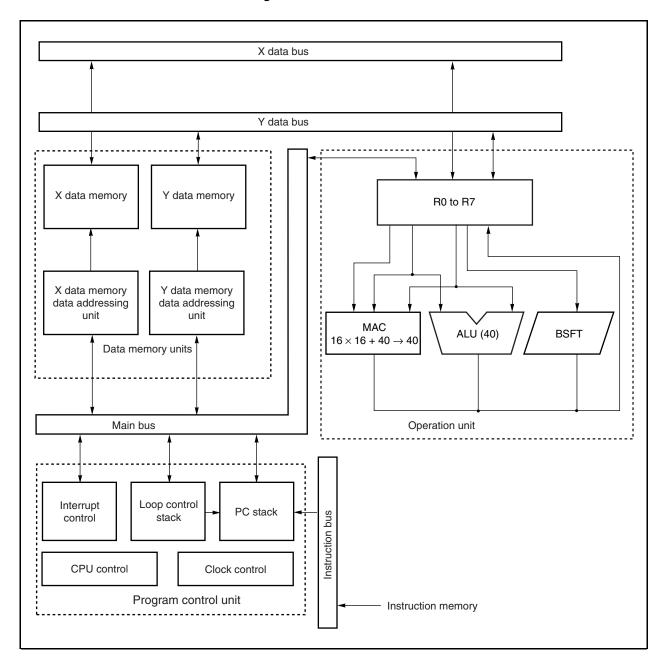

| 4-2          | DSP Core Kernel                                                      |      |

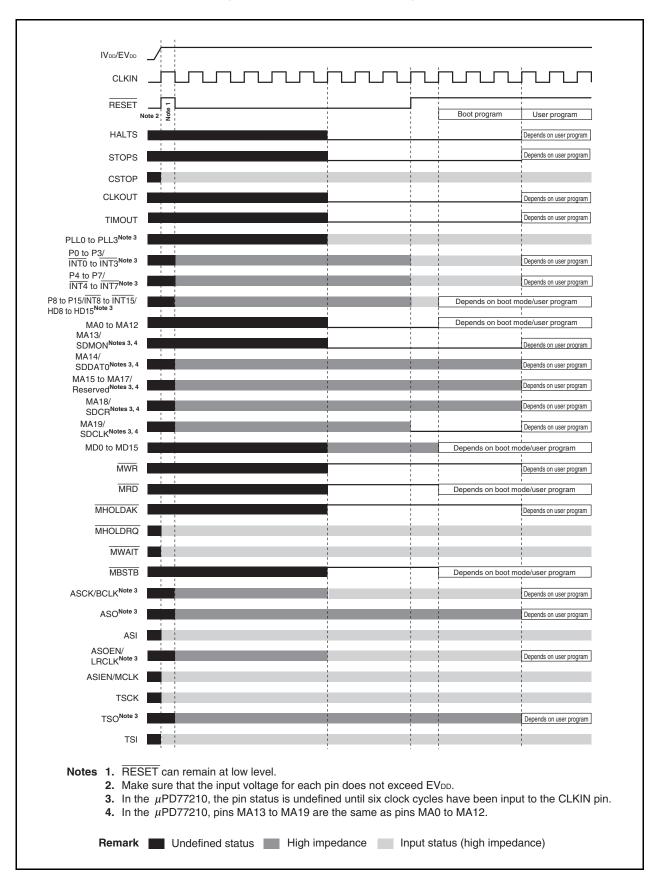

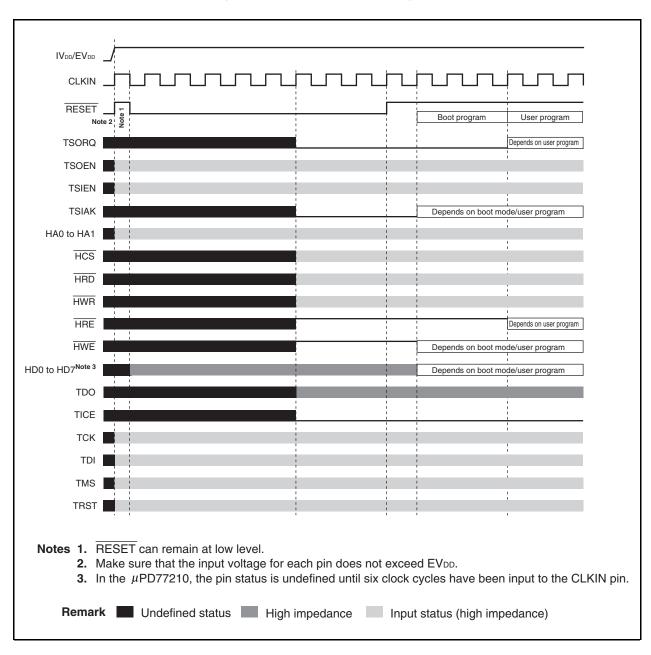

| 4-3          | Reset Operation Timing                                               |      |

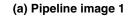

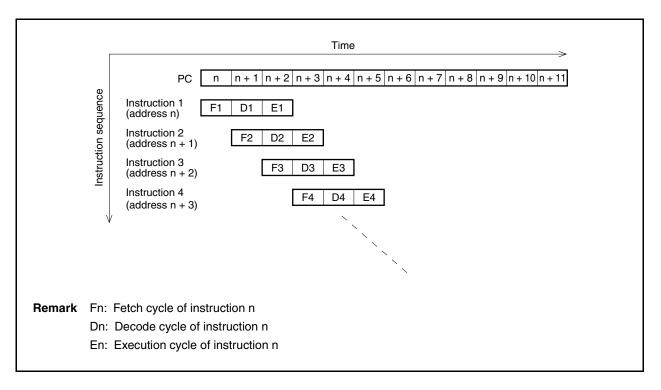

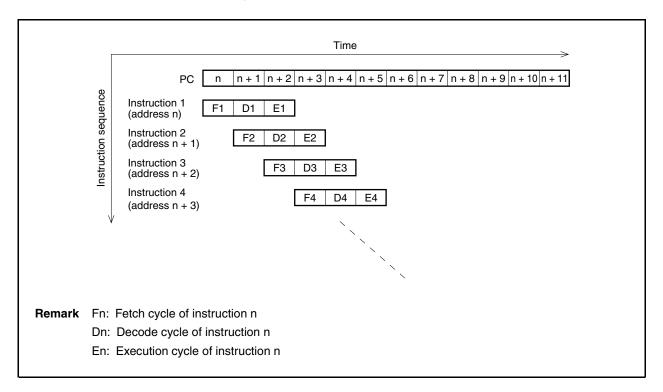

| 4-4          | Pipeline Image                                                       |      |

| 4-5          | Program Control Unit                                                 |      |

| 4-6          | Instruction Memory Map                                               |      |

| 4-7          | Normal Operation of PC                                               |      |

| 4-8          | Timing of Unconditional Immediate Jump                               |      |

| 4-9          | Timing of Unconditional Indirect Jump                                |      |

| 4-10         | Timing of Conditional Immediate Jump (Condition Satisfied: Branch)   |      |

| 4-11         | Timing of Conditional Immediate Jump (Condition Not Satisfied: Pass) |      |

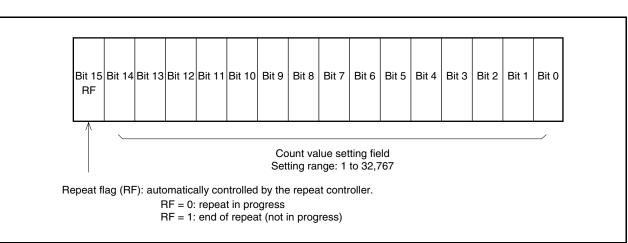

| 4-12         | Format of RC                                                         |      |

| 4-12         | Example of Repeat Instruction (Repetition of 2 Times)                |      |

| 4-14         | Repeat Execution Timing (Repetition of 2 Times)                      |      |

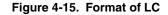

| 4-15         | Format of LC                                                         |      |

| 4-16         | Loop Execution Timing (Example of 2 Loops Operation)                 |      |

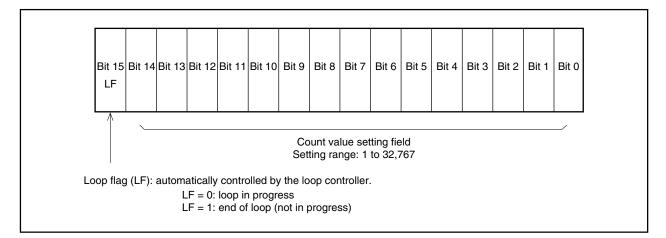

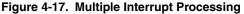

| 4-17         | Multiple Interrupt Processing                                        |      |

| 4-17         | Interrupt Acknowledging Timing                                       |      |

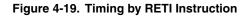

| 4-10         | Timing by RETI Instruction                                           |      |

| 4-19         | Interrupt Delay Timing (One-Cycle Delay)                             |      |

| 4-20<br>4-21 | Interrupt Delay Timing (One-Cycle Delay)                             |      |

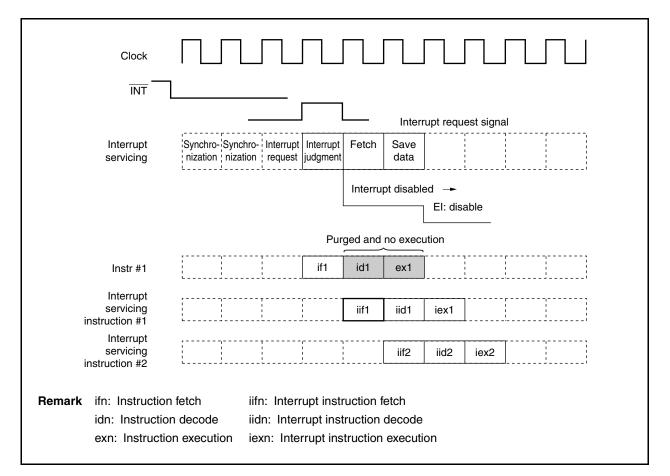

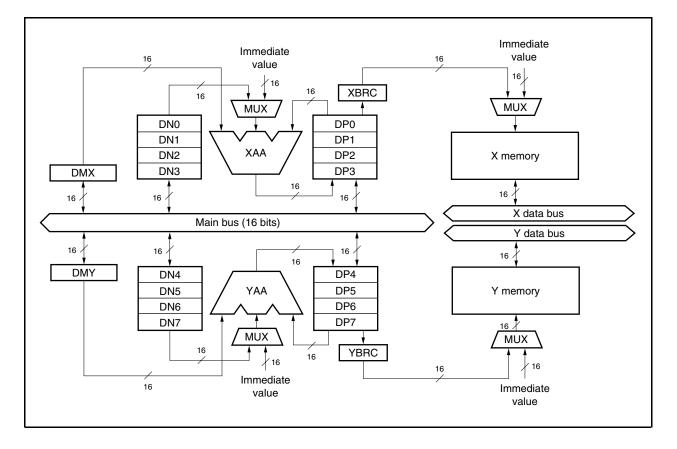

| 4-21         | Data Addressing Unit                                                 |      |

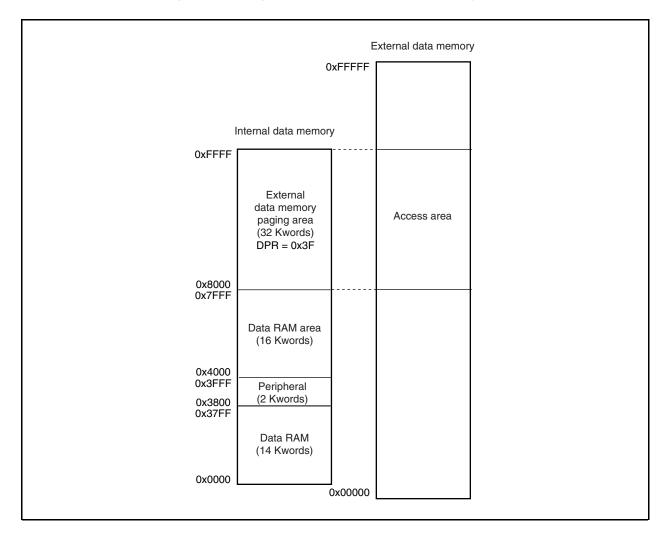

| 4-22         | Data Memory Map                                                      |      |

| 4-23         | Aliasing of Instruction Memory as Data Memory                        |      |

| 4-24<br>4-25 | Image of Access to External Data Memory Map                          |      |

| 4-25<br>4-26 |                                                                      |      |

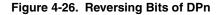

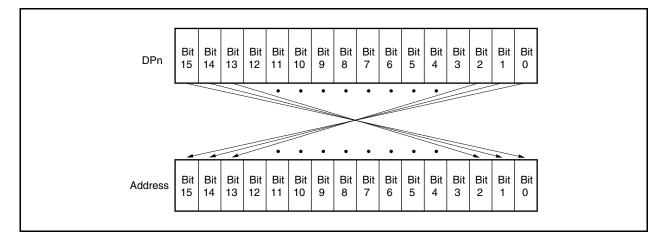

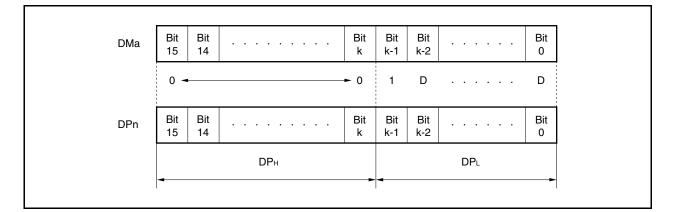

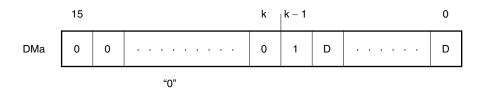

| 4-20<br>4-27 | Reversing Bits of DPn<br>Division of DPn                             |      |

|              |                                                                      |      |

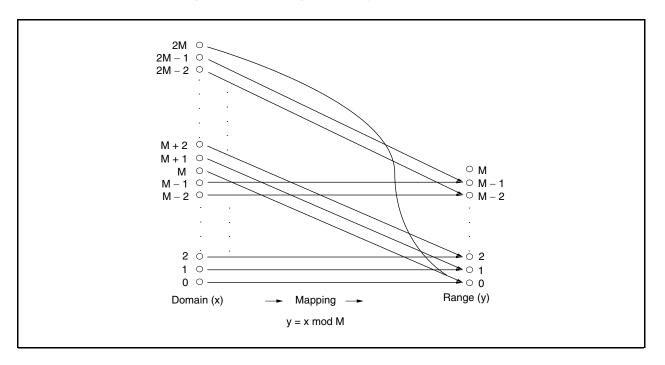

| 4-28<br>4-29 | Mapping of Ordinary Modulo Operation                                 |      |

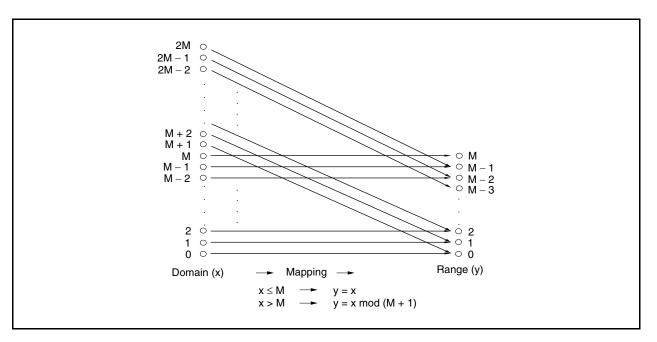

|              | Mapping of Modulo Adjustment                                         |      |

| 4-30         | Operation Unit                                                       |      |

| 4-31         | Formats of General-Purpose Registers                                 |      |

| 4-32         | Data Exchange Between General-Purpose Registers and Data Memory      |      |

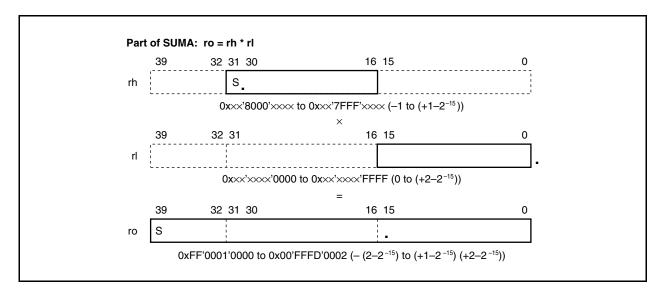

| 4-33         | Signed-Signed Multiply                                               |      |

| 4-34         | Signed-Unsigned Multiply                                             |      |

| 4-35         | Unsigned-Unsigned Multiply                                           |      |

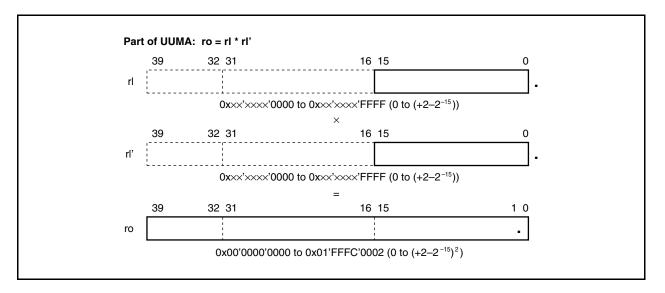

| 4-36         | Accumulative Multiplication                                          |      |

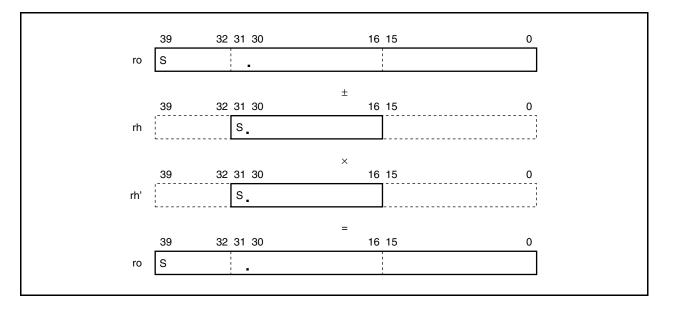

| 4-37         | 1-Bit Shift Accumulative Multiplication                              | 119  |

| Figure | No. Title                                                                                     | Page |

|--------|-----------------------------------------------------------------------------------------------|------|

| 4.00   |                                                                                               | 100  |

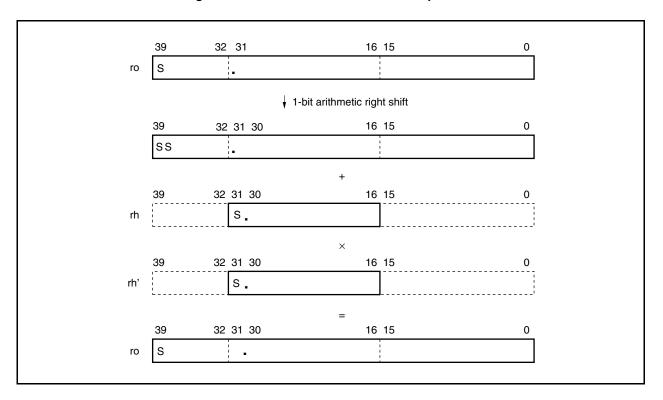

| 4-38   | 16-Bit Shift Accumulative Multiplication                                                      |      |

| 4-39   | Barrel Shifter Operations                                                                     | 124  |

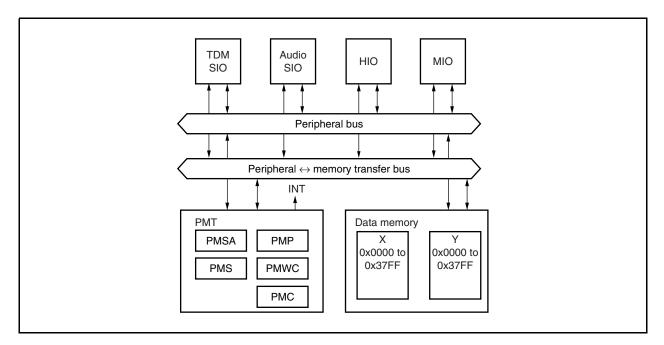

| 5-1    | Peripheral Units                                                                              |      |

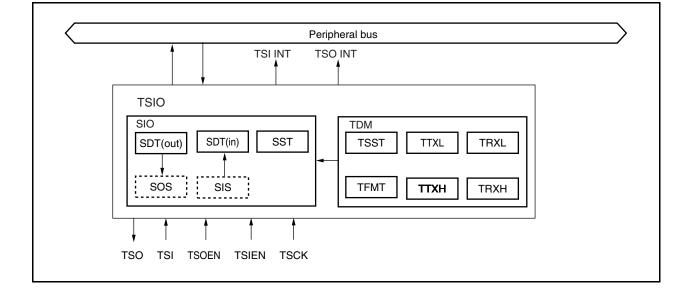

| 5-2    | Block Diagram of TDM Serial Interface                                                         | 130  |

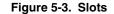

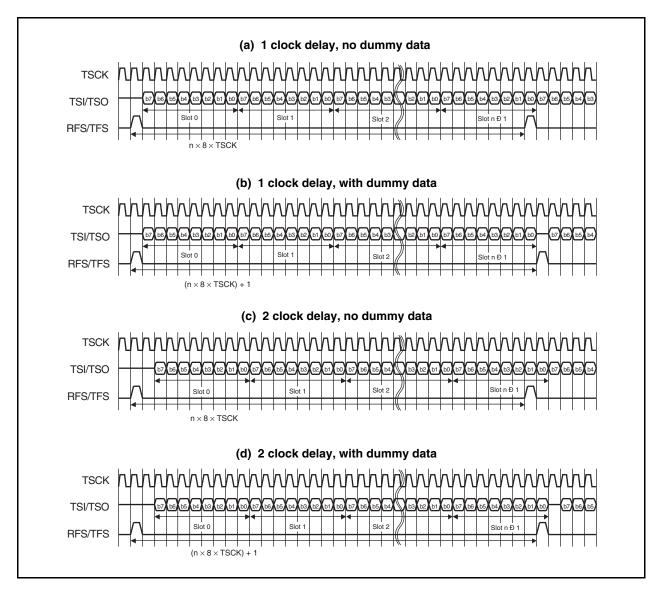

| 5-3    | Slots                                                                                         | 137  |

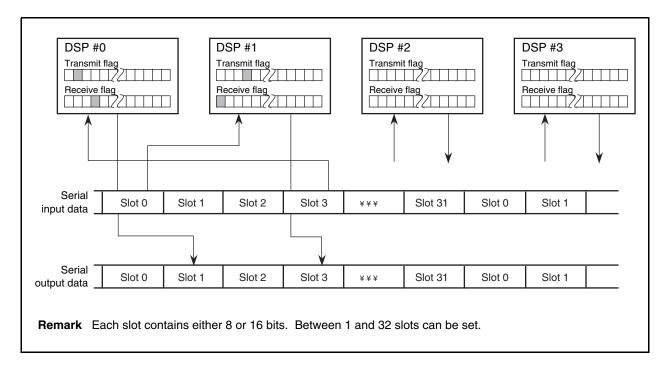

| 5-4    | Expanded Slots                                                                                | 137  |

| 5-5    | Timing of TDM Serial Interface                                                                | 138  |

| 5-6    | Block Diagram of Audio Serial Interface                                                       | 140  |

| 5-7    | Output Timing of Audio Serial Interface                                                       | 145  |

| 5-8    | Input Timing of Audio Serial Interface                                                        | 146  |

| 5-9    | ASO Operation When ASIO Operation Is Started (in Master Mode)                                 | 147  |

| 5-10   | Block Diagram of Standard Serial Interface                                                    | 148  |

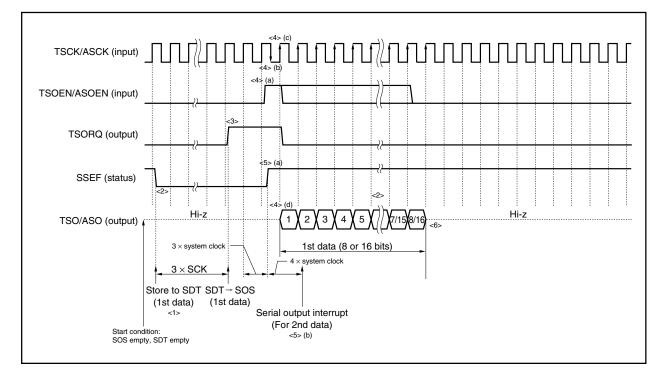

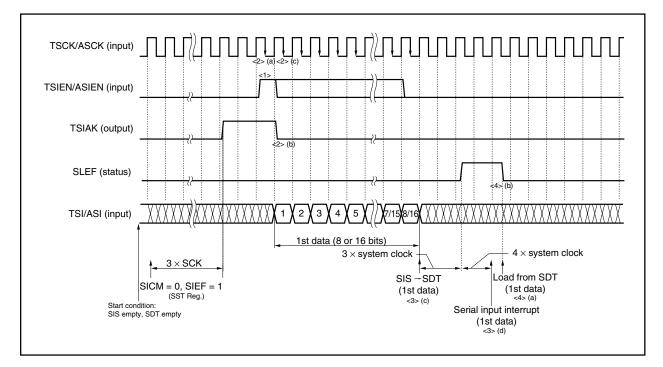

| 5-11   | Serial Interface Output Timing                                                                | 154  |

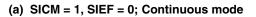

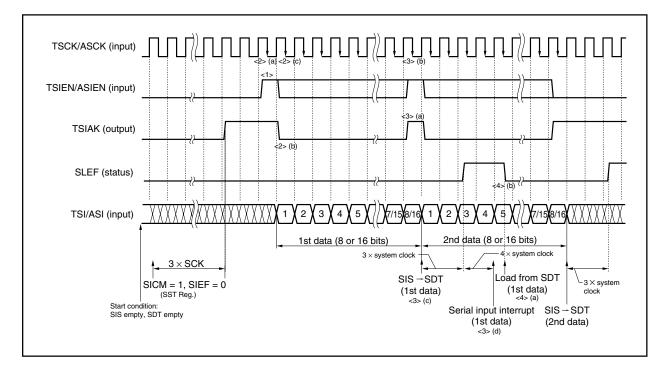

| 5-12   | Serial Interface Input Timing                                                                 | 156  |

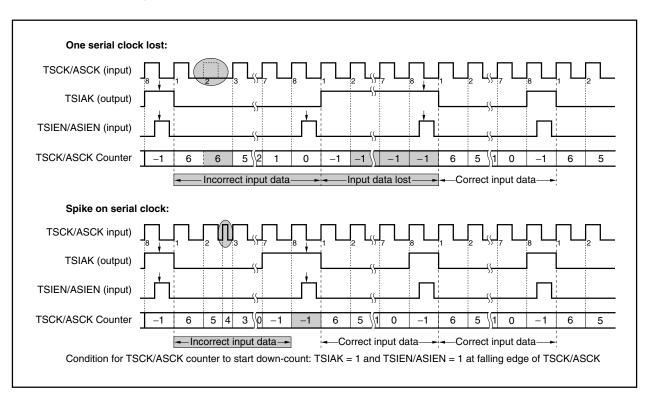

| 5-13   | Serial Interfaces - Operation of the Serial Clock Counter                                     | 157  |

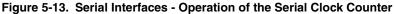

| 5-14   | Block Diagram of Host Interface                                                               | 162  |

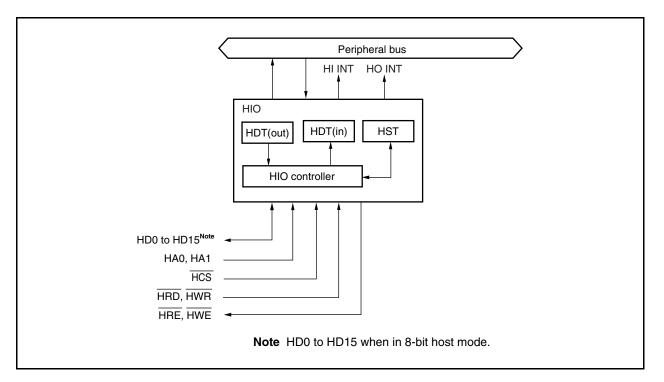

| 5-15   | Host Read Sequence ( $\mu$ PD77210 Family $\rightarrow$ Host): HDT Write Without Wait         | 167  |

| 5-16   | Host Write Sequence ( $\mu$ PD77210 Family $\leftarrow$ Host): HDT Read Without Wait          | 168  |

| 5-17   | Block Diagram of External Data Memory Interface                                               | 173  |

| 5-18   | Direct Access                                                                                 |      |

| 5-19   | DMA Access                                                                                    |      |

| 5-20   | Direct Access Timing                                                                          |      |

| 5-21   | DMA Access Timing                                                                             |      |

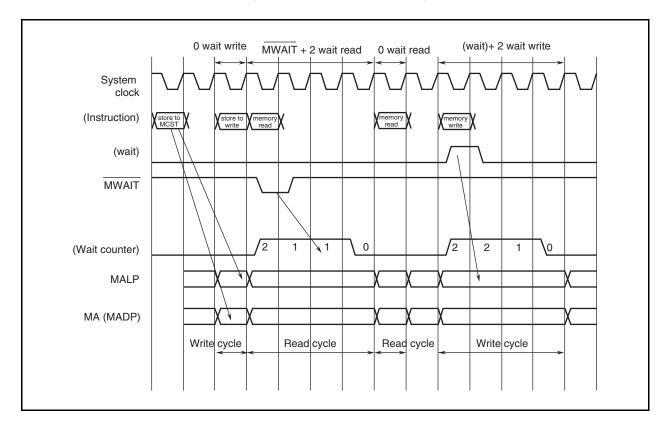

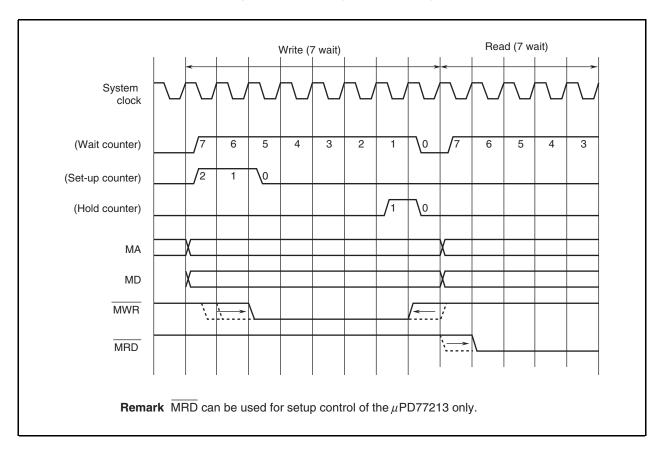

| 5-22   | Memory Access Timing                                                                          |      |

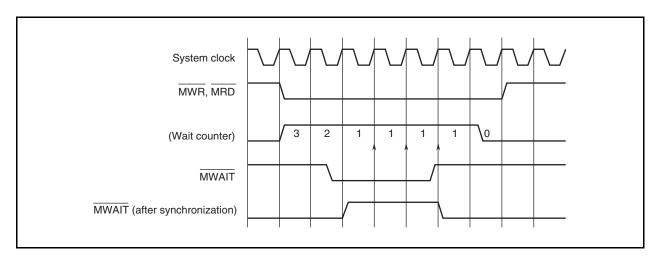

| 5-23   | Insertion of Access Wait Cycles via MWAIT Pin                                                 |      |

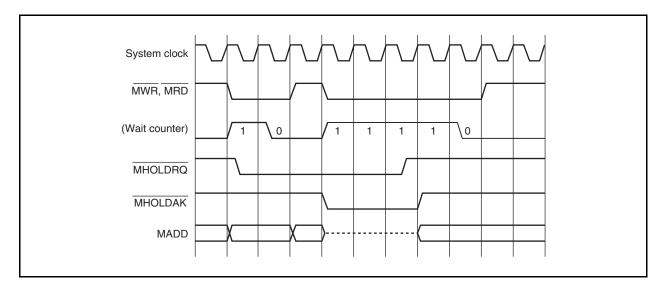

| 5-24   | Bus Arbitration                                                                               |      |

| 5-25   | Block Diagram of PMT Controller                                                               |      |

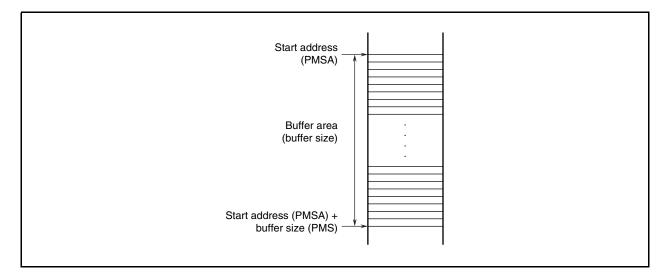

| 5-26   | PMT Settings                                                                                  | 191  |

| 5-27   | Block Diagram of General-Purpose I/O Port                                                     | 193  |

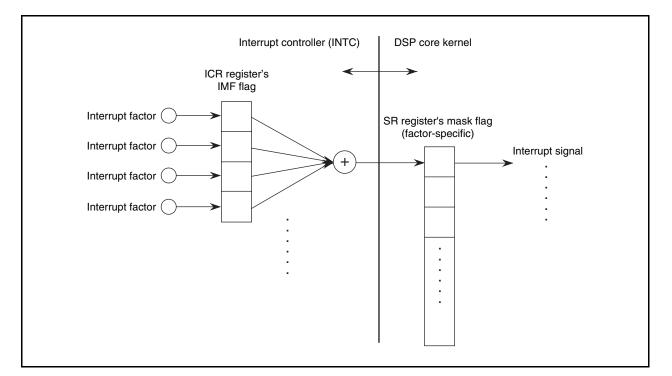

| 5-28   | Interrupt Controller in Stamp Mode                                                            | 203  |

| 5-29   | Interrupt Controller in Mask Mode                                                             | 204  |

| 5-30   | External Interrupt Timing                                                                     | 205  |

| 5-31   | Relationship Between Two Types of Mask Flags                                                  | 206  |

| 5-32   | fint Instruction Use Example: When Using an Audio Serial Input Interrupt While in 32-Bit Mode | 207  |

| 5-33   | Block Diagram of Timer (1 Channel)                                                            | 210  |

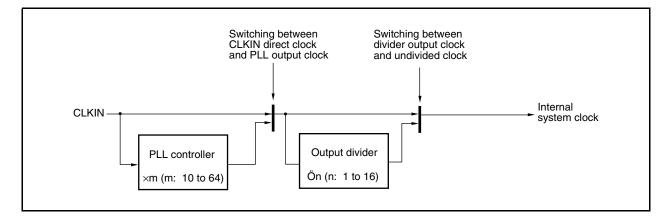

| 5-34   | Block Diagram of Clock Controller                                                             | 213  |

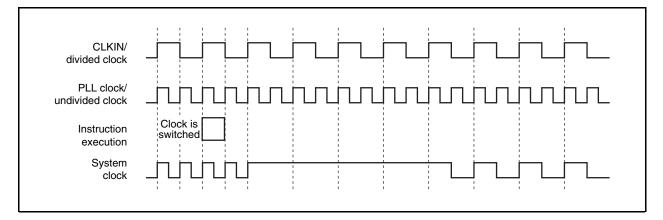

| 5-35   | Timing of Clock Switching                                                                     | 216  |

| 5-36   | Clock Switching                                                                               | 217  |

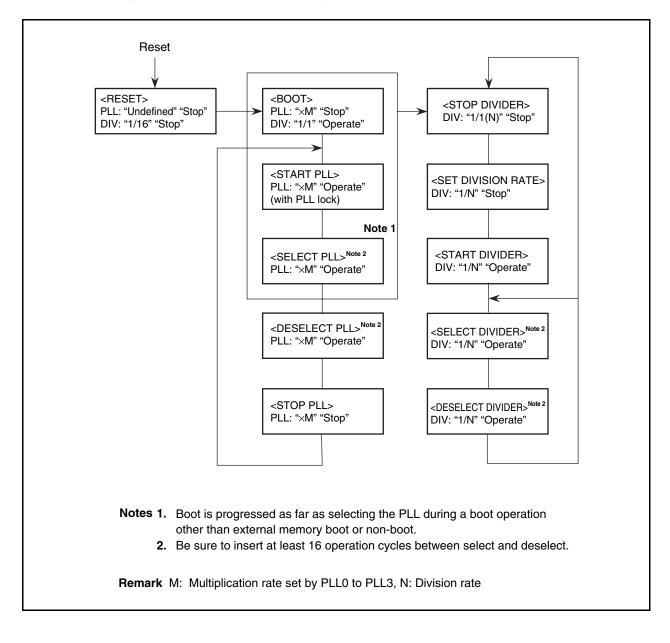

| 5-37   | State Transitions During PLL Operations and Divider Operations                                | 218  |

| 5-38   | Example of PLL Settings                                                                       | 219  |

| 5-39   | Example of Divider Settings                                                                   | 219  |

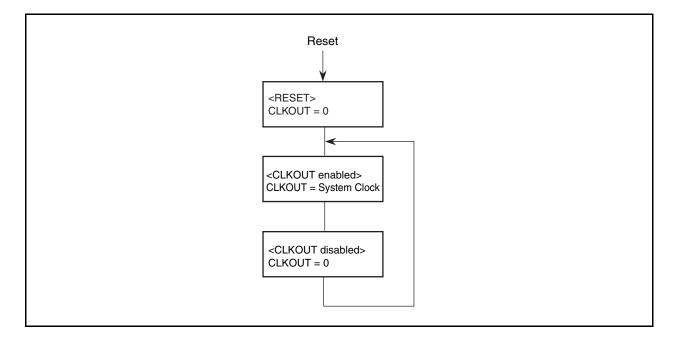

| 5-40   | State Transition of Clock Monitor Output                                                      | 220  |

| 5-41   | Clock Monitor Output Setting Example                                                          | 220  |

|        |                                                                                               |      |

# LIST OF FIGURES (2/3)

# LIST OF FIGURES (3/3)

| Figure I | No. Title                            | Page |

|----------|--------------------------------------|------|

|          |                                      |      |

| 5-42     | Example of POWC Register Settings    |      |

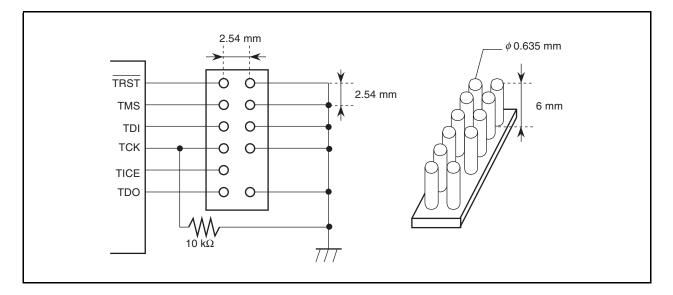

| 5-43     | JTAG Pin Handling                    |      |

| 5-44     | Block Diagram of Expansion Interface |      |

| 5-45     | Block Diagram of SD Card Interface   | 230  |

|          |                                      |      |

| 6-1      | Boot from X Memory                   |      |

| 6-2      | Boot from Y Memory                   |      |

| 6-3      | Boot from X Memory and Y Memory      |      |

| 6-4      | Boot from External Data Memory       |      |

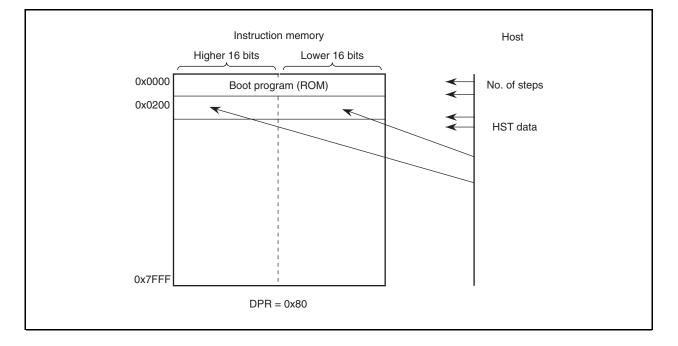

| 6-5      | Host Boot Operation                  |      |

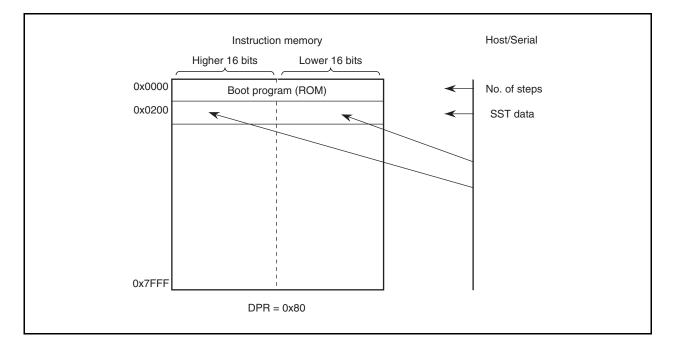

| 6-6      | Serial Boot Operation                |      |

|          |                                      |      |

# LIST OF TABLES (1/2)

| Table I | No. Title                                                       | Page |

|---------|-----------------------------------------------------------------|------|

| 1-1     | Features of $\mu$ PD77210 Family Devices                        | 20   |

| 2-1     | Connection of Functional Pins                                   |      |

| 2-2     | Connection of Non-Functional pin                                |      |

| 4-1     | Registers Connected to Main Bus                                 | 45   |

| 4-2     | Functional Block and Bus                                        | 45   |

| 4-3     | Registers and Memories Connected to X Data Bus                  | 46   |

| 4-4     | Registers and Memories Connected to Y Data Bus                  | 47   |

| 4-5     | PLL Multiplication Rate Settings                                | 49   |

| 4-6     | PLL Lock Range Settings                                         | 50   |

| 4-7     | CPU Registers to Be Initialized and Their Initial Values        | 52   |

| 4-8     | Peripheral Registers to Be Initialized and Their Initial Values | 53   |

| 4-9     | Pins to Be Initialized and Their Initial Values                 | 53   |

| 4-10    | Status of Pins During HALT Mode                                 | 57   |

| 4-11    | Internal Instruction Memory Capacity                            | 60   |

| 4-12    | Classification of Branch Instructions                           | 65   |

| 4-13    | Interrupt Vector Table                                          |      |

| 4-14    | ROM and RAM Capacity                                            | 92   |

| 4-15    | External Data Memory Capacity                                   |      |

| 4-16    | Conditions for Simultaneous Access to X and Y Memories          | 93   |

| 4-17    | Modifying Data Pointers                                         |      |

| 4-18    | Formats of General-Purpose Registers                            | 110  |

| 4-19    | Accumulative Multiplication Function                            | 117  |

| 5-1     | Memory Mapping of Peripheral Registers                          | 127  |

| 5-2     | TDM Serial Interface Registers                                  | 131  |

| 5-3     | Bit Configuration of TSST                                       | 133  |

| 5-4     | Bit Configuration of SST1                                       | 134  |

| 5-5     | Combination of SICM and SIEF Bits                               | 135  |

| 5-6     | Bit Configuration of TFMT                                       |      |

| 5-7     | Audio Serial Interface Registers                                | 140  |

| 5-8     | Bit Configuration of ASST                                       | 143  |

| 5-9     | Standard Serial Interface Registers                             | 148  |

| 5-10    | Bit Configuration of SST                                        | 151  |

| 5-11    | Combination of SICM Bits and SIEF Bits                          |      |

| 5-12    | Host Interface Registers                                        |      |

| 5-13    | Bit Configuration of HST                                        | 164  |

| 5-14    | Selection of Registers for Host Interface                       |      |

| 5-15    | External Data Memory Interface Registers                        | 173  |

| 5-16    | Bit Configuration of MSHW                                       | 177  |

| 5-17    | Bit Configuration of MWAIT                                      | 178  |

| 5-18    | Bit Configuration of MCST                                       | 179  |

| 5-19    | PMT Registers                                                   |      |

# LIST OF TABLES (2/2)

| Table N | No. Title                                            | Page |

|---------|------------------------------------------------------|------|

|         |                                                      |      |

| 5-20    | PMT Transfer Channels and Target Peripherals         |      |

| 5-21    | Bit Configuration of PMC                             |      |

| 5-22    | Registers of General-Purpose I/O Port                | 193  |

| 5-23    | Bit Configuration of PCD                             |      |

| 5-24    | Interrupt Controller's Registers                     | 201  |

| 5-25    | Bit Configuration of ICR                             |      |

| 5-26    | Interrupt Table                                      |      |

| 5-27    | Timer Registers                                      |      |

| 5-28    | Bit Configuration of TCSR                            |      |

| 5-29    | Timer Clock Sources (TCSR Bits 5 to 3)               |      |

| 5-30    | Clock Controller's Register                          |      |

| 5-31    | Bit Configuration of CLKC                            |      |

| 5-32    | Registers for Instruction Memory Correction Function | 221  |

| 5-33    | Bit Configuration of CEFR                            |      |

| 5-34    | Registers for Paging Function                        |      |

| 5-35    | DPR Settings and Target Area                         |      |

| 5-36    | Peripheral STOP Mode Register                        |      |

| 5-37    | Bit Configuration of POWC                            |      |

| 5-38    | Test Instructions                                    |      |

| 5-39    | Expansion Interface Register                         |      |

| 5-40    | Bit Configuration of APCR                            |      |

| 5-41    | SD Card Interface Registers                          |      |

| 5-42    | Bit Configuration of SDCMD_IDX                       |      |

| 5-43    | Bit Configuration of SDCTL                           |      |

| 5-44    | Configuration of SDRPR Register                      |      |

| 5-45    | Bit Configuration of $\mu$ PD77213's APCR Register   |      |

| 6-1     | Initial Reset Boot Mode                              |      |

| 6-2     | PLL's Lock Range                                     |      |

| 6-3     | Boot Modes and PLL                                   |      |

| 6-4     | Reboot Entry Addresses and Parameters                |      |

#### **CHAPTER 1 GENERAL**

The  $\mu$ PD77210 Family, which is the successor to the  $\mu$ PD77111 Family, is the general name used for the 16-bit fixed decimal digital signal processors (DSPs)  $\mu$ PD77210 and  $\mu$ PD77213.

Features such as high speed and low power consumption make these devices suitable not only for voice processing in various mobile application sets but also for processing of signals from all types of media including music and video.

#### 1.1 Comparison with $\mu$ PD77111 Family

Because  $\mu$ PD77210 Family devices employ a 0.13- $\mu$ m process, they achieve twice the execution speed of  $\mu$ PD77111 Family devices while consuming only half the power. The  $\mu$ PD77210 Family also feature expanded peripheral functions.

#### 1.1.1 High-speed operation

The maximum operating frequency has been raised to the range of 120 MHz (in the  $\mu$ PD77213) to 160 MHz (in the  $\mu$ PD77210). This makes it possible to implement a multi-channel speech codec or speech/video codec on a single chip.

#### 1.1.2 Low power consumption

The current consumption during execution of MAC operations (parallel load/store) and NOP operations is 0.35 mA/MHz. The operating voltage is 1.5 V (1.6 V when the  $\mu$ PD77210 operates between 120 and 160 MHz).

#### 1.1.3 Expanded peripheral functions

The range of peripheral functions provided in  $\mu$ PD77111 Family devices has been expanded in  $\mu$ PD77210 Family devices. The expanded functions and additional peripherals found in  $\mu$ PD77210 Family devices include the following.

- 8-/16-bit host interface (expanded function: supports 16-bit bus)

- General-purpose I/O ports (expanded function: up to 16 ports can be used)

- On-chip 8-channel DMA function (new)

- Time division multiplexing (TDM) serial interface (new)

- 32-/64-bit audio serial interface (new)

- 16-bit timer (new)

- SD (Secure Digital) card interface<sup>Note</sup>

**Note** *µ*PD77213 only

**Remark** The  $\mu$ PD77111 Family is the general name for the  $\mu$ PD77110, 77111, 77112, 77113A, 77114, and 77115.

#### 1.2 Features

The  $\mu$ PD77210 Family is compatible with the  $\mu$ PD77111 Family's operations and instruction set. The  $\mu$ PD77210 Family also maintains binary level compatibility with the  $\mu$ PD77111 Family's software and middleware (except for parts that depend on the memory configuration and peripheral configuration).

#### 1.2.1 DSP core kernel

Functions

- Parallel processing using dual load/store

- Hardware loop

- Execution of conditional instructions

- Execution of product sum operation in one instruction cycle

- On-chip JTAG-compliant functions

#### Programming

- 16 bits × 16 bits + 40 bits = 40-bit multiply accumulator

- Eight 40-bit general-purpose registers

- Eight data memory pointer registers (four each for the X and Y memory spaces)

- 12 levels of interrupts (four factors are assigned to each level for expanded interrupt factors)

- 3-operand instructions (trinomial operations)

- No pipeline at execution stage

Memory space (space from perspective DSP core kernel) Note

- Instruction memory 32-bit width × 16-bit words

- X data memory 16-bit width × 16-bit words

- Y data memory 16-bit width × 16-bit words

Note Not all of the logically available space has been implemented.

#### 1.2.2 Peripheral block

Functions

- 8-channel DMA function

- Peripheral memory transfer (PMT) function

- 1 Mword × 16 bits SRAM interface

- Time division multiplexing (TDM) serial interface (TSIO)

- Audio serial interface (ASIO)

- 8-/16-bit host interface (HIO)

- General-purpose I/O port (PIO)

- 16-bit timer

- Expanded interrupt functions

- Peripheral circuit standby function

- Instruction correction function

- Memory space expansion function (paging function)

- PLL multiplication and division control functions

- SD card interface (µPD77213 only)

Memory space (space from paging function) Note

- Instruction memory 32-bit width  $\times$  16-bit words  $\times$  64 pages

- X data memory 16-bit width × 16-bit words × 64 pages

- Y data memory 16-bit width × 16-bit words × 64 pages

- DMA data memory 16-bit width × 16-bit words

- External data memory 16-bit width  $\times$  20-bit words

Note Not all of the logically available space has been implemented.

|                             |                         | μPD77210                                                                                        | μPD77213                                                                                                                                                                                                                                                                        |  |  |

|-----------------------------|-------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Instruction cycle           |                         | 6.25 ns                                                                                         | 8.33 ns                                                                                                                                                                                                                                                                         |  |  |

| Operating clock frequency   | r (maximum)             | 160 MHz 120 MHz                                                                                 |                                                                                                                                                                                                                                                                                 |  |  |

| Clock circuit               | PLL multiplier circuit  | × 10 to 32 (×2 steps), × 40 to 64 (×8 steps)                                                    |                                                                                                                                                                                                                                                                                 |  |  |

|                             | Divider output          | ÷ integer of 1 to 16                                                                            |                                                                                                                                                                                                                                                                                 |  |  |

| Parallel instruction execut | ion                     | operations and parallel load/store ins<br>parallel load/store instructions, regist              | Trinomial operations and parallel load/store instructions, binomial operations and parallel load/store instructions, monomial operations and parallel load/store instructions, register-to-register transfers and conditional instructions, branch and conditional instructions |  |  |

| Hardware loop               |                         | Nesting is possible up to four levels.                                                          |                                                                                                                                                                                                                                                                                 |  |  |

| Conditional instructions    |                         | Conditional operations, conditional tr<br>are enabled by combining independent<br>instructions. | -                                                                                                                                                                                                                                                                               |  |  |

| Multiply accumulator        |                         | 16 bits $\times$ 16 bits + 40 bits $\rightarrow$ 40 bits                                        |                                                                                                                                                                                                                                                                                 |  |  |

| Accumulator                 |                         | 40-bit I/O (binomial operations and n                                                           | nonomial operations)                                                                                                                                                                                                                                                            |  |  |

| General-purpose registers   | 3                       | Eight 40-bit registers                                                                          |                                                                                                                                                                                                                                                                                 |  |  |

| Data memory pointers        |                         | Eight: four each for X memory space                                                             | e and Y memory space                                                                                                                                                                                                                                                            |  |  |

| Interrupts                  |                         | 12 vectors (up to four levels of factor                                                         | s per vector)                                                                                                                                                                                                                                                                   |  |  |

| Three-stage pipeline cont   | rol                     | Instruction fetch, instruction decode,                                                          | instruction execution                                                                                                                                                                                                                                                           |  |  |

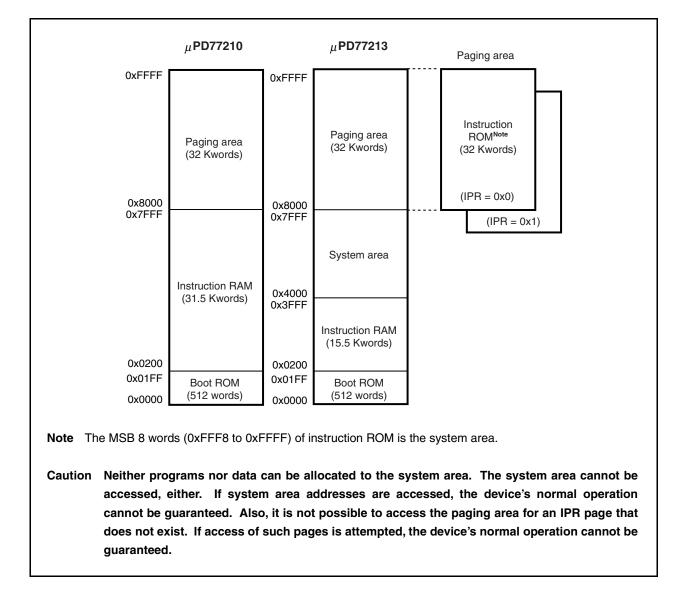

| Instruction memory          | System ROM              | 512 words (for boot function)                                                                   |                                                                                                                                                                                                                                                                                 |  |  |

|                             | Internal RAM            | 31.5 Kwords                                                                                     | 15.5 Kwords                                                                                                                                                                                                                                                                     |  |  |

|                             | Internal ROM            | None                                                                                            | 64 Kwords                                                                                                                                                                                                                                                                       |  |  |

|                             | External area           | None                                                                                            |                                                                                                                                                                                                                                                                                 |  |  |

| Data memory                 | X internal RAM          | 30 Kwords                                                                                       | 18 Kwords                                                                                                                                                                                                                                                                       |  |  |

|                             | X internal ROM          | None                                                                                            | 32 Kwords                                                                                                                                                                                                                                                                       |  |  |

|                             | Y internal RAM          | 30 Kwords                                                                                       | 18 Kwords                                                                                                                                                                                                                                                                       |  |  |

|                             | Y internal ROM          | None                                                                                            | 32 Kwords                                                                                                                                                                                                                                                                       |  |  |

|                             | External area (X and Y) | 1 Mword                                                                                         | 1 Mword (8 Kwords when using SD card)                                                                                                                                                                                                                                           |  |  |

| Serial interface            |                         | Audio serial (× 1)                                                                              |                                                                                                                                                                                                                                                                                 |  |  |

|                             |                         | TDM serial (× 1)                                                                                |                                                                                                                                                                                                                                                                                 |  |  |

|                             |                         | Standard serial (× 2) (shared as aud                                                            | io/TDM)                                                                                                                                                                                                                                                                         |  |  |

| Host interface              |                         | 8-bit/16-bit parallel                                                                           |                                                                                                                                                                                                                                                                                 |  |  |

| General-purpose I/O ports   | 3                       | Up to 16                                                                                        |                                                                                                                                                                                                                                                                                 |  |  |

| Timer                       |                         | Two-channel (16-bit resolution)                                                                 |                                                                                                                                                                                                                                                                                 |  |  |

| Memory card interface       |                         | None                                                                                            | SD card (1 bit)                                                                                                                                                                                                                                                                 |  |  |

| DMA transfer function       |                         | 8 channels, between peripherals and internal data RAM                                           |                                                                                                                                                                                                                                                                                 |  |  |

| Power supply                | DSP core                | 1.425 to 1.65 V, 1.55 to 1.65 V (when 120 and 160 MHz)                                          | the $\mu$ PD77210 operates between                                                                                                                                                                                                                                              |  |  |

|                             | External I/O            | 2.7 to 3.6 V                                                                                    |                                                                                                                                                                                                                                                                                 |  |  |

| Standby modes               |                         | By HALT instruction or STOP instruction                                                         |                                                                                                                                                                                                                                                                                 |  |  |

| Package                     |                         | 144-pin LQFP, 161-pin FBGA                                                                      |                                                                                                                                                                                                                                                                                 |  |  |

| Other                       |                         | Debug function (JTAG)                                                                           |                                                                                                                                                                                                                                                                                 |  |  |

## Table 1-1. Features of $\mu$ PD77210 Family Devices

#### 1.2.3 Ordering information

| Part Number        | Package                                            |  |

|--------------------|----------------------------------------------------|--|

| μPD77210F1-DA2     | 161-pin plastic fine pitch BGA (10 $	imes$ 10)     |  |

| μPD77210GJ-8EN     | 144-pin plastic LQFP (fine pitch) (20 $\times$ 20) |  |

| μPD77213F1-×××-DA2 | 161-pin plastic fine pitch BGA (10 $	imes$ 10)     |  |

| μPD77213GJ-×××-8EN | 144-pin plastic LQFP (fine pitch) (20 $	imes$ 20)  |  |

### **CHAPTER 2 PIN FUNCTIONS**

This chapter describes the pin connections and pin functions of the  $\mu$ PD77210 Family. The pin names are shown below.

| ASCK:        | Audio serial clock input/output   | MWAIT:        | External data memory access wait      |

|--------------|-----------------------------------|---------------|---------------------------------------|

| ASI:         | Audio serial data input           |               | input                                 |

| ASIEN:       | Audio serial input enable         | NC:           | Non-connection                        |

| ASO:         | Audio serial data output          | P0 to P15:    | Port                                  |

| ASOEN:       | Audio serial output enable        | PLL0 to PLL3: | PLL multiple rate set                 |

| BCLK:        | Bit Clock input/output            | Reserved:     | Reserved                              |

| CLKIN:       | Clock input                       | RESET:        | Reset                                 |

| CLKOUT:      | Clock output                      | SDCLK:        | SD card clock output                  |

| CSTOP:       | Clear stop mode                   | SDCR:         | SD card command output/response       |

| EVDD:        | Power supply for I/O pins         |               | input                                 |

| GND:         | Ground                            | SDDAT0:       | SD card data input                    |

| HALTS:       | Halt status signal output         | SDMON:        | SD card access monitor output         |

| HD0 to HD15: | Host data bus                     | STOPS:        | Stop status signal output             |

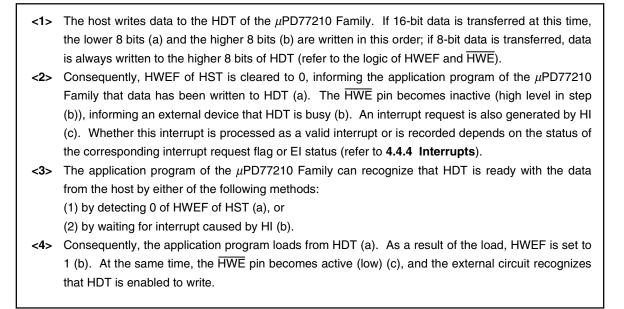

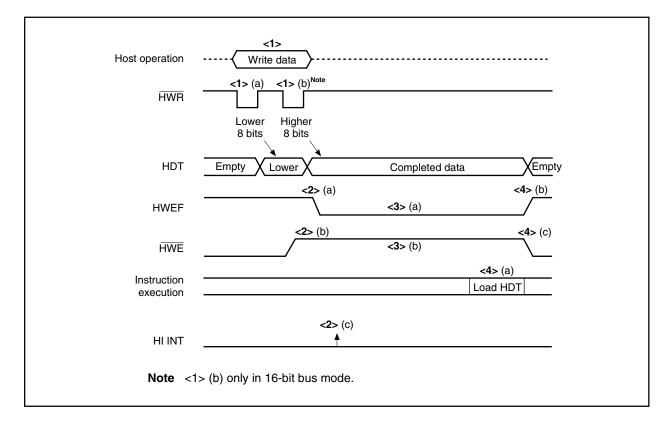

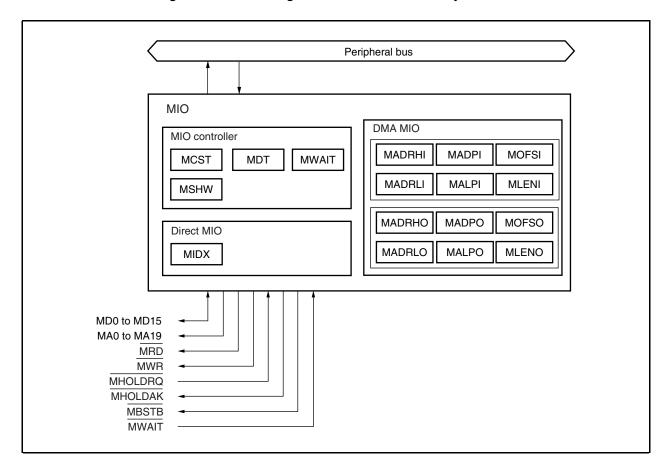

| HCS:         | Host chip select                  | TCK:          | Test clock input                      |