### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for written consent of Renesas Electronics. Further, you may not use any Renesas Electronics shall not be in any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics atta abooks, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU ROHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## Regarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: http://www.renesas.com

Renesas Technology Corp. Customer Support Dept. April 1, 2003

#### Cautions

Keep safety first in your circuit designs!

Renesas Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate

measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

Notes regarding these materials

- 1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation or a third party.

- 2. Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

# SH7729R CPU Board HS7729RSTC01H

User's Manual

Renesas Electronics

Rev.1.0 2001.08

### Cautions

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

## **IMPORTANT INFORMATION**

### **READ FIRST**

### • READ this user's manual before using this CPU board.

### • KEEP the user's manual handy for future reference.

### Do not attempt to use the CPU board until you fully understand its mechanism.

### CPU Board:

Throughout this document, the term "CPU board" shall be defined as the following products produced only by Hitachi, Ltd. excluding all subsidiary products.

- CPU board

- Serial cable

- AC power adapter

- AC power cable

The user system or a host computer is not included in this definition.

### Purpose of the CPU Board:

This CPU board is a software and hardware development tool for systems employing the Hitachi microcomputer SH7729R. Simple debugging functions such as debugging, performance evaluation, and development of the user system including the SH7729R are enabled by connecting the CPU board to a host computer. In addition, expansion boards can be installed in the slots; therefore, memory and I/O can be expanded. However, this CPU board must not be installed in user products to be used as part of the user products; it is limited to debugging and evaluation of user systems. This CPU board must only be used for the above purpose.

### Limited Applications:

This CPU board is not authorized for use in MEDICAL, atomic energy, aeronautical or space technology applications without consent of the appropriate officer of a Hitachi sales company. Such use includes, but is not limited to, use in life support systems. Buyers of this CPU board must notify the relevant Hitachi sales offices before planning to use the product in such applications.

### **Improvement Policy:**

Hitachi, Ltd. (including its subsidiaries, hereafter collectively referred to as Hitachi) pursues a policy of continuing improvement in design, performance, and safety of the CPU board. Hitachi reserves the right to change, wholly or partially, the specifications, design, user's manual, and other documentation at any time without notice.

### Target User of the CPU Board:

This CPU board should only be used by those who have carefully read and thoroughly understood the information and restrictions contained in the user's manual. Do not attempt to use the CPU board until you fully understand its mechanism.

It is highly recommended that first-time users be instructed by users that are well versed in the operation of the CPU board.

## LIMITED WARRANTY

Hitachi warrants its CPU boards to be manufactured in accordance with published specifications and free from defects in material and/or workmanship. Hitachi, at its option, will repair or replace any CPU boards returned intact to the factory, transportation charges prepaid, which Hitachi, upon inspection, determine to be defective in material and/or workmanship. The foregoing shall constitute the sole remedy for any breach of Hitachi's warranty. See the Hitachi warranty booklet for details on the warranty period. This warranty extends only to you, the original Purchaser. It is not transferable to anyone who subsequently purchases the CPU board from you. Hitachi is not liable for any claim made by a third party or made by you for a third party.

### DISCLAIMER

HITACHI MAKES NO WARRANTIES, EITHER EXPRESS OR IMPLIED, ORAL OR WRITTEN, EXCEPT AS PROVIDED HEREIN, INCLUDING WITHOUT LIMITATION THEREOF. WARRANTIES AS TO MARKETABILITY. MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE OR USE. OR AGAINST INFRINGEMENT OF ANY PATENT. IN NO EVENT SHALL HITACHI BE LIABLE FOR ANY DIRECT, INCIDENTAL OR CONSEQUENTIAL DAMAGES OF ANY NATURE, OR LOSSES OR EXPENSES RESULTING FROM ANY DEFECTIVE CPU BOARD, THE USE OF ANY CPU BOARD, OR ITS DOCUMENTATION, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. EXCEPT AS EXPRESSLY STATED OTHERWISE IN THIS WARRANTY, THIS CPU BOARD IS SOLD "AS IS ", AND YOU MUST ASSUME ALL RISK FOR THE USE AND RESULTS OBTAINED FROM THE CPU BOARD.

#### State Law:

Some states do not allow the exclusion or limitation of implied warranties or liability for incidental or consequential damages, so the above limitation or exclusion may not apply to you. This warranty gives you specific legal rights, and you may have other rights which may vary from state to state.

### The Warranty is Void in the Following Cases:

Hitachi shall have no liability or legal responsibility for any problems caused by misuse, abuse, misapplication, neglect, improper handling, installation, repair or modifications of the CPU board without Hitachi's prior written consent or any problems caused by the user system.

### All Rights Reserved:

This user's manual and CPU board are copyrighted and all rights are reserved by Hitachi. No part of this user's manual, all or part, may be reproduced or duplicated in any form, in hard-copy or machine-readable form, by any means available without Hitachi's prior written consent.

### Other Important Things to Keep in Mind:

- 1. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 2. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi.

#### Figures:

Some figures in this user's manual may show items different from your actual system.

#### Limited Anticipation of Danger:

Hitachi cannot anticipate every possible circumstance that might involve a potential hazard. The warnings in this user's manual and on the CPU board are therefore not all inclusive. Therefore, you must use the CPU board safely at your own risk.

## **SAFETY PAGE**

### **READ FIRST**

- READ this user's manual before using this CPU board.

- KEEP the user's manual handy for future reference.

Do not attempt to use the CPU board until you fully understand its mechanism.

### **DEFINITION OF SIGNAL WORDS**

This is the safety alert symbol. It is used to alert you to potential personal injury hazards. Obey all safety messages that follow this symbol to avoid possible injury or death.

**DANGER** indicates an imminently hazardous situation which, if not avoided, will result in death or serious injury.

**WARNING** indicates a potentially hazardous situation which, if not avoided, could result in death or serious injury.

**CAUTION** indicates a potentially hazardous situation which, if not avoided, may result in minor or moderate injury.

**CAUTION** used without the safety alert symbol indicates a potentially hazardous situation which, if not avoided, may result in property damage.

NOTE emphasizes essential information.

##

Observe the precautions listed below. Failure to do so will result in a FIRE HAZARD and will damage the user system and the CPU board or will result in PERSONAL INJURY. The USER PROGRAM will be LOST.

- 1. Always satisfy the power supply conditions which are described in the manual. Ensure that there are no short circuits between VCC and GND. Do not apply voltage that is outside the guaranteed range.

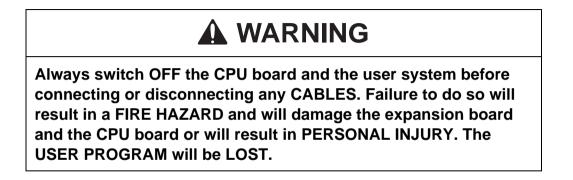

- 2. Always switch OFF the CPU board and the user system before connecting or disconnecting any CABLES, CONNECTORS, or JUMPERS.

- 3. When turning on the CPU board or the user system, take care that conductive material does not touch the CPU board or the user system.

- 4. Check that the pin numbers on the connectors of the CPU board and those on the user system are correctly aligned before connecting the CPU board and the user system.

### Preface

Thank you for purchasing the CPU board for Hitachi's SH7729R microcomputer.

The CPU board is an efficient development tool for software and hardware of systems based on Hitachi's SH7729R microcomputer.

This manual describes the SH7729R CPU board (model number HS7729RSTC01H). Hereafter, this product will be referred to as "the CPU board."

This manual explains the functions and method of operation of these CPU boards.

Section 1, Overview, describes the hardware system configuration and explains environment settings to enable board use.

Section 2, Preparation before Use, explains procedures for using the CPU boards, HDI installation, various connections, and the power supply specifications.

Section 3, Tutorial, introduces the major HDI features while demonstrating methods for loading and debugging a C language program.

Section 4, Descriptions of Windows, describes each of the windows used in the HDI.

Section 5, CPU Board Specifications, explains the specifications of the CPU boards, the memory map, interfaces with external equipment, and CPU board initialization.

Section 6, Notes and Troubleshooting, explains important information regarding use and gives suggestions for troubleshooting.

Section 7, Creation of User Interrupt Handlers, explains how to create an original interrupt handler routine.

Please read this manual completely in order to gain a thorough understanding of this product's functions and performance.

The text appearing in the various windows of the HDI may differ from those appearing in this manual depending on the language of the OS being used. The figures appearing in this manual are for the English version of  $Microsoft^{\circ}$  Windows<sup> $\circ$ </sup> 98.

Related Manuals

- SH7729R Hardware Manual

- SH3, SH3E, SH3-DSP Programming Manual

- SH Series Cross Assembler User's Manual

- H Series Linkage Editor User's Manual

- H Series Librarian User's Manual

- SuperH RISC Engine C/C++ Compiler User's Manual

- SH Series Simulator/Debugger User's Manual

- Hitachi Debugging Interface User's Manual (available in the CD-ROM supplied with this CPU board)

- Hitachi Embedded Workshop User's Manual

When connecting an E10A emulator to the CPU board, the following manual should also be read.

• SH7729R E10A Emulator User's Manual

## Note: Microsoft<sup>®</sup> and Windows<sup>®</sup> are registered trademarks of Microsoft Corporation in the United States and/or other countries.

### Contents

| Prefa |                                         | i   |

|-------|-----------------------------------------|-----|

| Secti | on 1 Overview                           | 1   |

| 1.1   | Features                                | 1   |

| 1.2   | System Configuration                    | 2   |

| 1.3   | Warnings                                | 3   |

| 1.4   | Components                              | 4   |

| 1.5   | CD-R Contents                           | 5   |

| 1.6   | Environmental Conditions                | 6   |

| Secti | on 2 Preparation before Use             | 7   |

| 2.1   | CPU Board Preparation                   | 7   |

| 2.2   | HDI Installation                        | 8   |

| 2.3   | HDI Uninstallation                      | 9   |

| 2.4   | Connecting Cables                       | 10  |

| 2.5   | Connecting the User Expansion Board     | 13  |

| 2.6   | Connecting the PCMCIA Card              | 14  |

| 2.7   | Switches                                | 15  |

| 2.8   | Jumpers                                 | 16  |

| 2.9   | Power Supply                            | 19  |

|       | 2.9.1 Power-Supply Specifications       | 19  |

|       | 2.9.2 Connecting the Power Supply Cable | .20 |

| Secti | on 3 Tutorial                           | 23  |

| 3.1   | Introduction                            |     |

| 3.2   | Running the HDI                         |     |

| 3.3   | [HDI] Window                            |     |

| 3.4   | Setting up the CPU Board                |     |

| 3.5   | Setting the [Monitor Setup] Dialog Box  |     |

| 3.6   | Downloading the Tutorial Program        |     |

| 5.0   | 3.6.1 Downloading the Tutorial Program  |     |

|       | 3.6.2 Displaying the Source Program     |     |

| 3.7   | Setting the Software Breakpoint         |     |

| 3.8   | Setting Registers                       |     |

| 3.9   | Executing the Program                   |     |

| 3.10  | Reviewing Breakpoints                   |     |

| 3.11  | Viewing Memory                          |     |

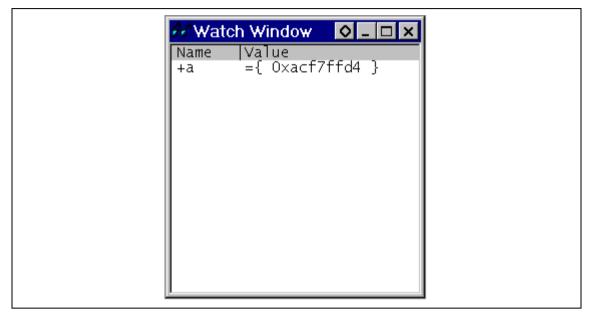

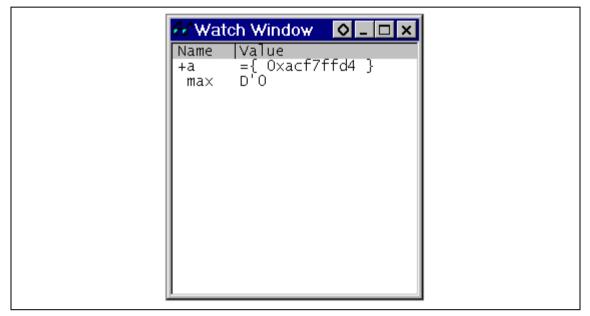

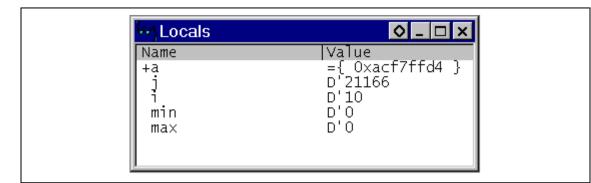

| 3.12  | Watching Variables                      |     |

| 3.13  | Stepping Through a Program              |     |

|       | 3.13.1 Executing [Step In] Command      |     |

|       | 3.13.2 Executing [Step Out] Command     |     |

|       | 3.13.3                    | Executing [Step Over] Command                                               | 48  |

|-------|---------------------------|-----------------------------------------------------------------------------|-----|

| 3.14  |                           |                                                                             |     |

| 3.15  |                           |                                                                             |     |

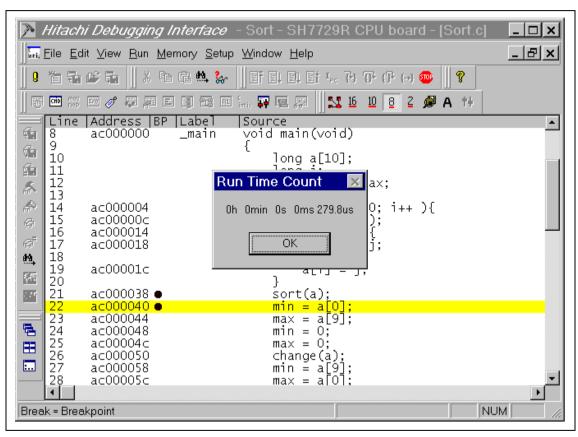

| 3.16  | Run Time Count Function55 |                                                                             |     |

| 3.17  |                           |                                                                             |     |

| 3.18  | -                         | Next?                                                                       |     |

|       |                           |                                                                             |     |

| Secti | on 4                      | Descriptions of Windows                                                     | 63  |

| 4.1   | HDI W                     | /indows                                                                     |     |

| 4.2   | Descrip                   | otions of Each Window                                                       | 56  |

|       | 4.2.1                     | [Monitor Setup] Dialog Box                                                  | 66  |

|       | 4.2.3                     | [Add/Edit Breakpoint] Dialog Box                                            | 70  |

|       | 4.2.4                     | [System Status] Window                                                      |     |

|       | 4.2.5                     | [Run Time Count Condition] Dialog Box                                       |     |

|       | 4.2.6                     | [Cache Control] Dialog Box                                                  |     |

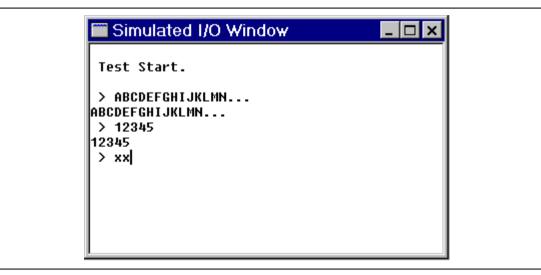

|       | 4.2.7                     | [Simulated I/O Window] Window                                               |     |

|       | 4.2.8                     | [Command Line] Window                                                       |     |

|       |                           |                                                                             |     |

| Secti | on 5 (                    | CPU Board Specifications                                                    | 77  |

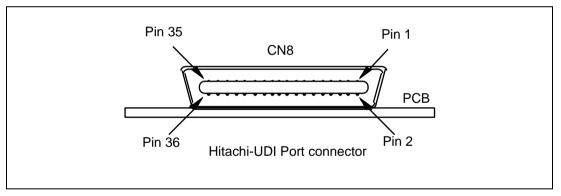

| 5.1   |                           | Diagram                                                                     |     |

| 5.2   |                           | cations                                                                     |     |

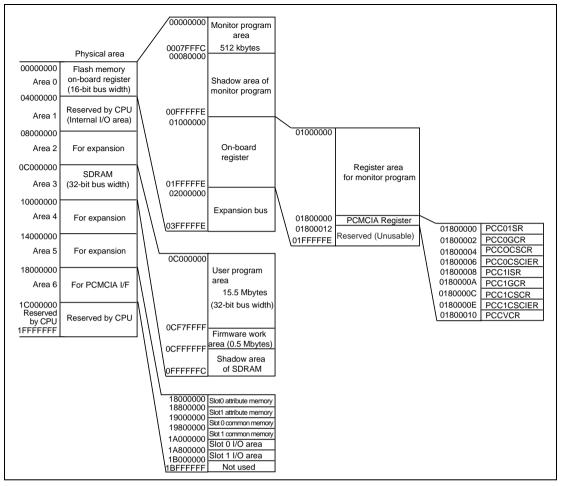

| 5.3   | -                         | у Мар                                                                       |     |

| 5.4   |                           | al Interface                                                                |     |

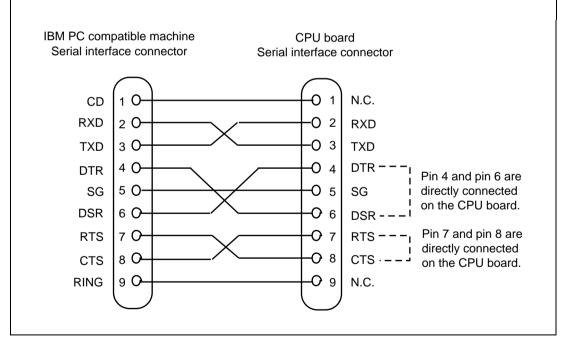

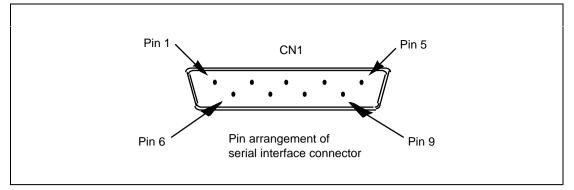

|       | 5.4.1                     | Serial Interface                                                            | 82  |

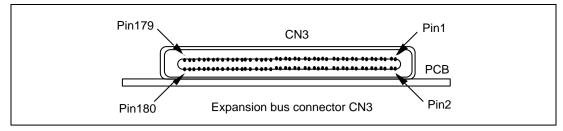

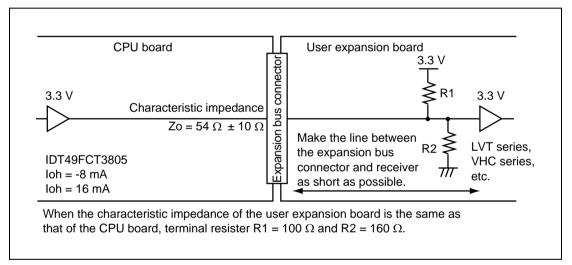

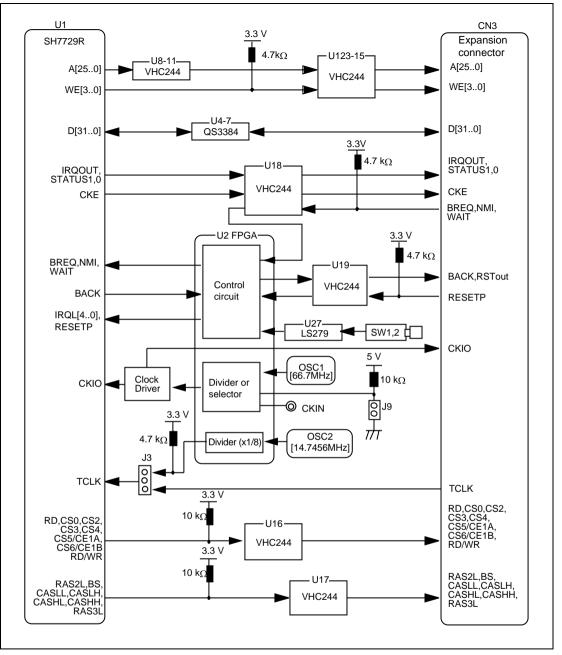

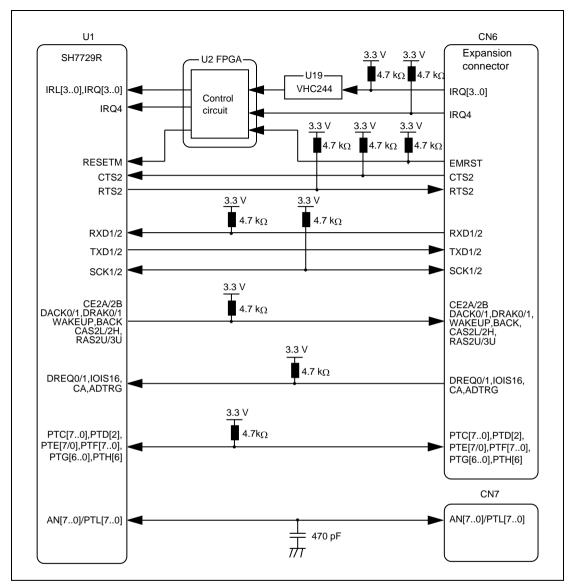

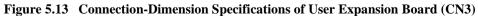

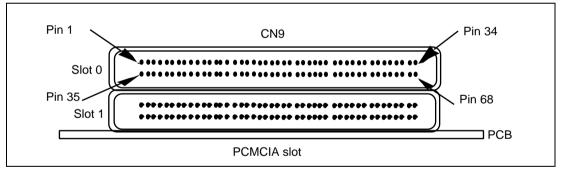

|       | 5.4.2                     | User Expansion Board Interface                                              |     |

|       | 5.4.3                     | PCMCIA Interface                                                            |     |

|       | 5.4.4                     | E10A Emulator Interface                                                     |     |

| 5.5   | Parts L                   | ayout                                                                       |     |

| 5.6   |                           | zation                                                                      |     |

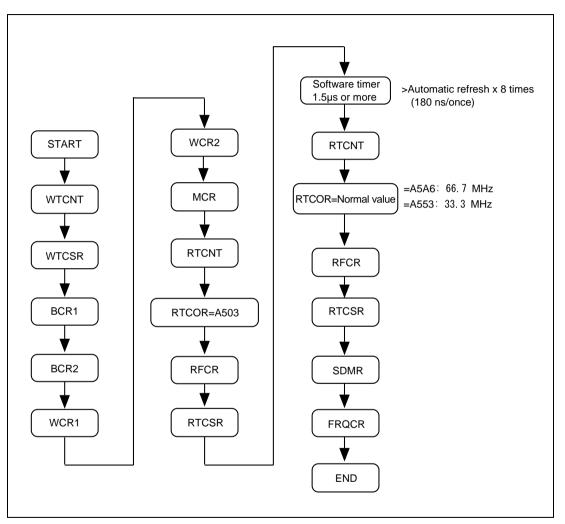

|       | 5.6.1                     | Initializing Resources                                                      |     |

|       | 5.6.2                     | Procedure for Making Initial Settings of the CPU Bus State Controller (BSC) |     |

|       | 5.6.3                     | Initial Settings of CPU Bus State Controller (BSC)                          |     |

|       |                           |                                                                             |     |

| Secti | on 6 1                    | Notes and Troubleshooting                                                   | 125 |

| 6.1   | Notes                     | ~                                                                           | 125 |

| 6.2   | Trouble                   | eshooting                                                                   | 133 |

|       |                           | -                                                                           |     |

| Secti | on 7 (                    | Creation of User Interrupt Handlers                                         | 135 |

| 7.1   | Creatio                   | n of User Interrupt Handlers                                                | 135 |

| 7.2   | User Pr                   | rogram Using SCI                                                            | 137 |

|       | 7.2.1                     | Creation of SCI Driver                                                      | 137 |

|       | 7.2.2                     | SCI-Related Register Settings                                               | 138 |

| 7.3   | Sample                    | Program                                                                     |     |

### Section 1 Overview

### 1.1 Features

The SH7729R CPU board (hereafter, referred to as the CPU board) supports the evaluation of the functions and performance of the Hitachi SH7729R microcomputer, and the development and evaluation of systems that incorporate the SH7729R.

The features of this CPU board are as follows:

• Supports user expansion boards

Has an expansion bus connector for I/O of signals conforming to the SH7729R external bus specifications, to which expansion boards developed by the user to increase memory and I/O can be connected and evaluated.

- Supports the maximum operating frequency Allows evaluation at 200 MHz (internal operating frequency), which is the maximum frequency of the SH7729R.

- Interface

For interfacing with IBM PC compatible as the host computer, a serial interface (that conforms to RS-232C) (one channel) is provided. The Hitachi Debugging Interface (HDI) is also provided as host interface software.

• Enables user-program evaluation

Up to 15.5 Mbytes of a user program can be loaded by serial interface into the user memory and be evaluated.

• Support for PCMCIA

PCMCIA interface hardware is provided as standard equipment, so that user programs can be employed in PCMCIA evaluations.

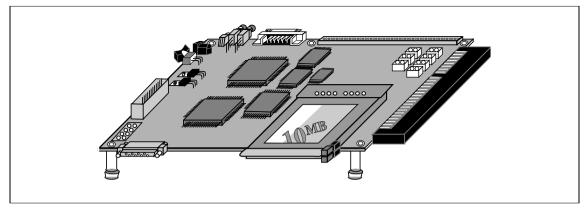

Figure 1.1 CPU Board, External View

Note: IBM PC is a registered trademark of International Business Machines Corporation in the United States.

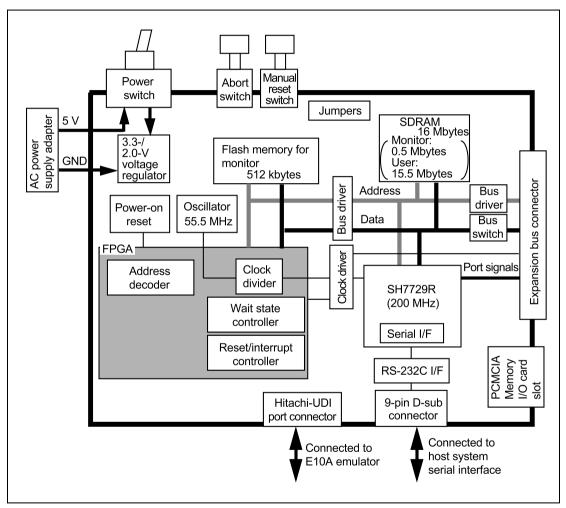

### **1.2** System Configuration

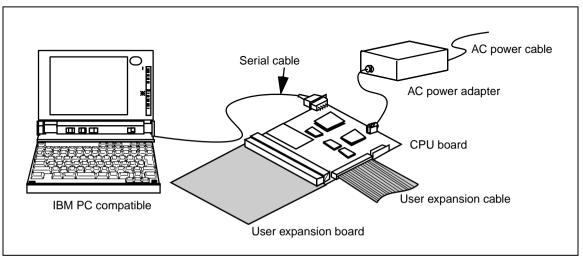

The system configuration of the CPU board is shown in figure 1.2.

The following items are required to use the CPU board.

- IBM PC compatible machine: One for the monitor command input and output.

- One serial interface cable: Use the provided cable.

- One AC power supply adapter: Use the provided adapter.

- One AC power supply cable: Use the provided power cable.

Figure 1.2 CPU Board System Configuration

# CAUTION

### READ the following warnings before using the CPU board. Incorrect operation will damage the user system and the CPU board. The USER PROGRAM will be LOST.

- 1. Check all components against the component list after unpacking the CPU board.

- 2. Never place heavy objects on the CPU board.

- 3. Protect the CPU board from excessive impacts and stresses. For details, refer to section 1.6, Environmental Conditions.

- 4. Do not connect any cable or connector other than specified ones to the CPU board.

- 5. When moving the host computer or user expansion board, take care not to vibrate or damage the CPU board.

- 6. After connecting the cable, check that it is connected correctly. For details, refer to section 2, Preparation before Use.

- 7. Supply power to the connected equipment after connecting all cables. Cables must not be connected or removed while the power is on.

### 1.4 Components

Table 1.1 lists the components of the CPU board. Check all components after unpacking.

#### View Quantity Remarks Item CPU board 1 One printed circuit board AC power 1 supply adapter 1 AC power ſĿ supply cable Serial 1 communication cable Jumper pin 1 CD-R\* 1 One CD-R; Model number 0 HS7729RSTC01SR Notes on Usage 2 One Japanese version of SH7729R and one English version; Notes on CPU Board Japanese: Usage HS7729RSTC01HJ-P, English: HS7729RSTC01HE-P

### Table 1.1 CPU Board Component List

Note: Refer to section 1.5, CD-R Contents.

### 1.5 CD-R Contents

The supplied CD-R includes software and user's manuals for the SH7729R CPU board as listed in table 1.2.

| Directory          | File Name          | Contents                                        | Remarks                                                    |

|--------------------|--------------------|-------------------------------------------------|------------------------------------------------------------|

| \setup             | setup.exe          | HDI installer                                   |                                                            |

| \Manuals\Japanese  | HS7729RSTC01HJ.pdf | SH7729R CPU Board<br>User's Manual              | PDF document in<br>Japanese<br>Type No.:<br>HS7729RSTC01HJ |

| \Manuals\Japanese  | HS6400DIIW5SJ.pdf  | Hitachi Debugging<br>Interface User's<br>Manual | PDF document in<br>Japanese<br>Type No.:<br>HS6400DIIW5SJ  |

| \Manuals\English   | HS7729RSTC01HE.pdf | SH7729R CPU Board<br>User's Manual              | PDF document in<br>English<br>Type No.:<br>HS7729RSTC01HE  |

| \Manuals\English   | HS6400DIIW5SE.pdf  | Hitachi Debugging<br>Interface User's<br>Manual | PDF document in<br>English<br>Type No.:<br>HS6400DIIW5SE   |

| \Pdf_read\Japanese | Ar40jpn.exe        | Acrobat <sup>®</sup> Reader<br>installer        | Japanese version                                           |

| \Pdf_read\Englsih  | Ar40eng.exe        | Acrobat <sup>®</sup> Reader<br>installer        | English version                                            |

### Table 1.2CD-R Contents

Note: To read a PDF document, use the Acrobat<sup>®</sup> Reader.

# CAUTION

Observe the conditions listed in tables 1.3 and 1.4 when using the CPU board. Failure to do so will damage the user system and the CPU board. The USER PROGRAM will be LOST.

### Table 1.3 Environmental Conditions

| ltem          | Specifications                                                                             |  |  |

|---------------|--------------------------------------------------------------------------------------------|--|--|

| Temperature   | Operating: +10°C to +35°C<br>Storage: -10°C to +50°C                                       |  |  |

| Humidity      | Operating: 35% RH to 80% RH, no condensation<br>Storage: 35% RH to 80% RH, no condensation |  |  |

| Vibration     | Operating:2.45 m/s² max.Storage:4.9 m/s² max.Transportation:14.7 m/s² max.                 |  |  |

| Ambient gases | There must be no corrosive gases present                                                   |  |  |

#### Table 1.4 Operating Environments

| ltem                          | Description                                                                                                                                            |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host computer                 | Built-in Pentium or higher-performance CPU (200 MHz or higher recommended); IBM PC or compatible machine.                                              |

| OS                            | Windows <sup>®</sup> 95, Windows <sup>®</sup> 98, or Windows NT <sup>®</sup>                                                                           |

| Minimum memory capacity       | 32 Mbytes or more (double of the load module size recommended)                                                                                         |

| Hard-disk capacity            | Installation disk capacity: 5 Mbytes or more. (Prepare an area at least double the memory capacity (four-times or more recommended) as the swap area.) |

| CD-ROM drive                  | Required to install the HDI.                                                                                                                           |

| Pointing device such as mouse | Connectable to the host computer; compatible with Windows <sup>®</sup> 95, Windows <sup>®</sup> 98, and Windows NT <sup>®</sup> .                      |

| Power supply                  | Input: 100 to 240 VAC, 50/60 Hz, 0.9 A max.                                                                                                            |

| (for AC power supply adapter) | Output: +5.0 VDC, 6.0 A max.                                                                                                                           |

### 2.1 CPU Board Preparation

##

READ the reference sections shaded in figure 2.1 before using the CPU board product. Incorrect operation will damage the user system and the CPU board. The USER PROGRAM will be LOST.

Unpack the CPU board and prepare it for use as shown in figure 2.1:

|                                                                                                                                                                                                   | Reference           |                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------|

| Unpack the CPU board.                                                                                                                                                                             | -                   | ]                                 |

| Check the components against the component list.                                                                                                                                                  | Component list      |                                   |

| Turn on the host computer.                                                                                                                                                                        |                     | Procedure                         |

| Install the HDI.                                                                                                                                                                                  | Section 2.2         | when the CPU board is used first. |

| Turn off the host computer.                                                                                                                                                                       |                     |                                   |

| Connect the CPU board to the host<br>computer and AC power supply adapter,<br>and when necessary to a PCMCIA<br>card or user expansion board. Also be<br>sure to set the jumper on the CPU board. | Sections 2.4 to 2.9 |                                   |

| Turn on the host computer.                                                                                                                                                                        |                     | Procedure<br>when the CPU         |

| Turn on the CPU board.                                                                                                                                                                            | Section 3           | board is used for second time     |

| Start the HDI.                                                                                                                                                                                    |                     | or later.                         |

Figure 2.1 CPU Board Preparation Flow Chart

### 2.2 HDI Installation

An example of installing the HDI on an IBM PC compatible machine is described in this section.

Start [setup.EXE] in the \SETUP directory of the CD-R. If any other application is running, close it before starting the HDI installer.

### Figure 2.2 [setup.EXE] Icon

This runs the HDI installer. A dialog box will first prompt you to select a language for the installation process. Select a language then continue according to the instructions displayed by the installer.

Note: Under Windows NT<sup>@</sup>4.0, install the HDI in the administrator mode.

**HDI Installation Directory:** The default directory for installing the HDI depends on whether the Hitachi Embedded Workshop (HEW) has been installed in the host computer, as shown in table 2.1

Table 2.1

Default Installation Directory

| HEW Program                                            | Default Installation Directory |

|--------------------------------------------------------|--------------------------------|

| HEW has not been installed                             | C:\HDI5_CB\7729R               |

| HEW has been installed<br>(in this example, in C:\HEW) | C:\HEW\HDI5\CB\7729R           |

**Backup File:** If another version of HDI has already been installed, a message "The HDI.INI file has already existed. Can it be overwritten?" will be displayed. Clicking [Yes] will make a backup of the existing file in the Backup directory of the installation directory.

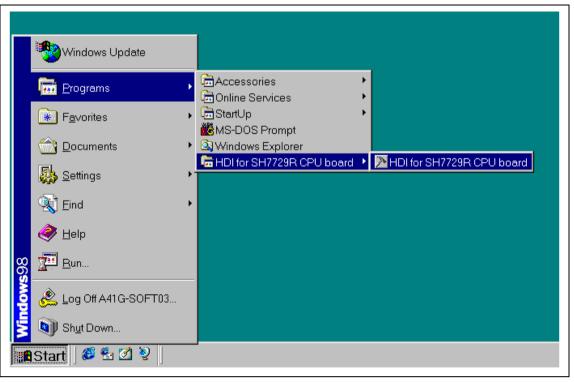

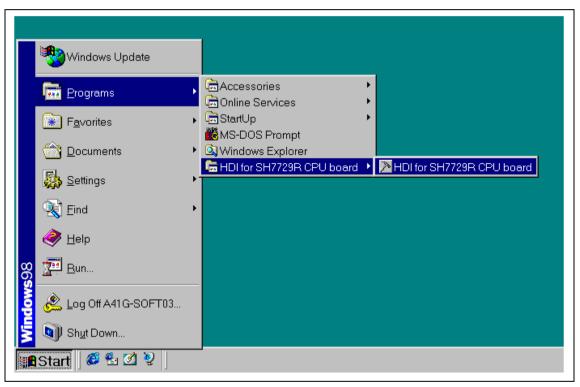

When installation is complete, [HDI for SH7729R CPU board] can be selected from the start menu.

Figure 2.3 Start Menu

### 2.3 HDI Uninstallation

Uninstall the HDI for the SH7729R CPU board as follows:

- 1. Select [Settings] from the Start menu, then select [Control Panel].

- 2. Select [Add/Remove Programs].

- 3. Select [HDI for SH7729R CPU board] from the application list, then click [Add/Remove].

- 4. A confirmation message will be displayed, and the uninstallation procedure will start.

### 2.4 Connecting Cables

This section shows how to connect interface cables to the CPU board.

##

Always switch OFF the CPU board and the user system before connecting or disconnecting any CABLES, CONNECTORS, or JUMPERS. Failure to do so will result in a FIRE HAZARD and will damage the user system and the CPU board or will result in PERSONAL INJURY. The USER PROGRAM will be LOST.

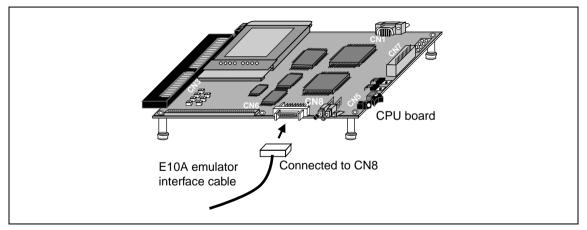

Figure 2.4 E10A Emulator Interface Cable Connection

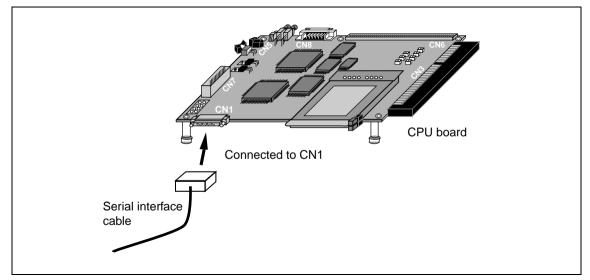

Figure 2.5 Serial Interface Cable Connection

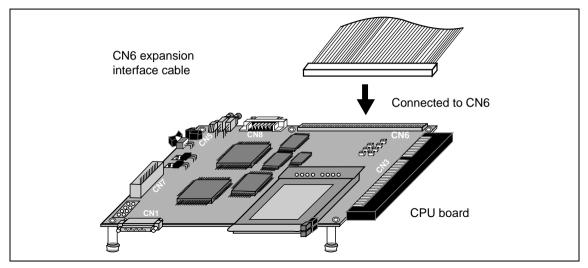

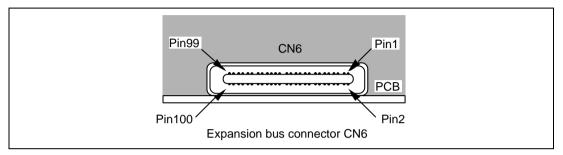

Figure 2.6 CN6 Expansion Interface Cable Connection

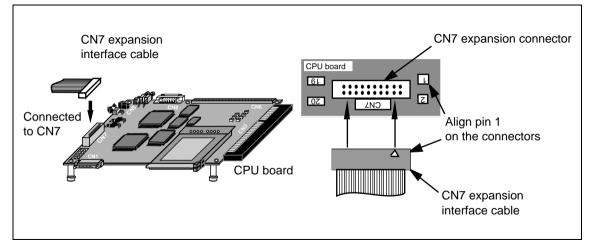

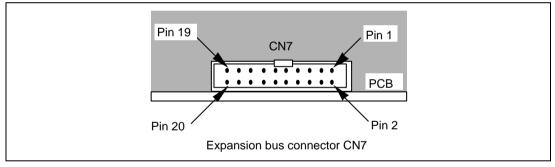

Figure 2.7 CN7 Expansion Interface Cable Connection

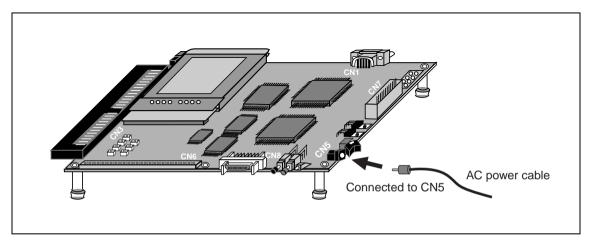

Figure 2.8 AC Power Supply Cable Connection

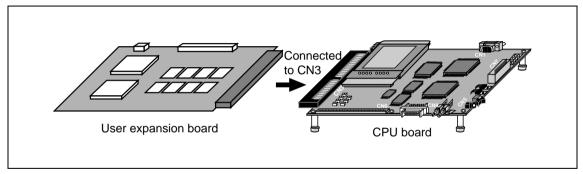

### 2.5 Connecting the User Expansion Board

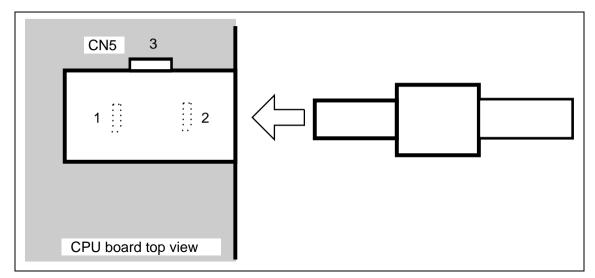

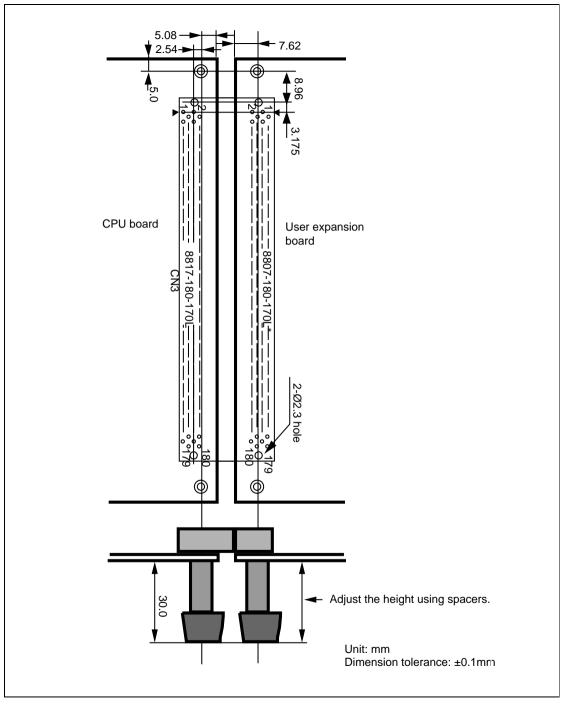

Figure 2.9 shows how to connect the user expansion board.

##

Always switch OFF the CPU board and the user system before connecting or disconnecting any CABLES, CONNECTORS, or JUMPERS. Failure to do so will result in a FIRE HAZARD and will damage the user system and the CPU board or will result in PERSONAL INJURY. The USER PROGRAM will be LOST.

Figure 2.9 User Expansion Board Connection

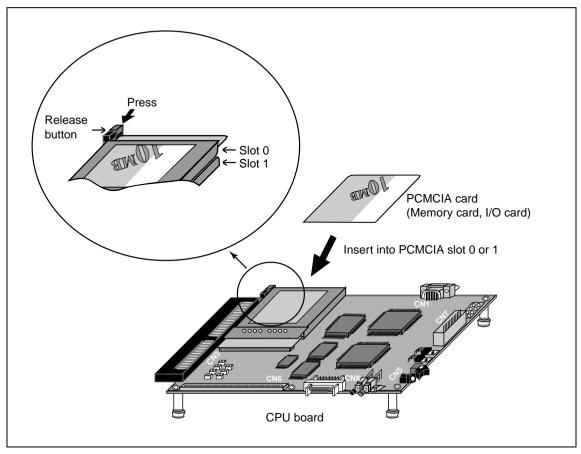

### 2.6 Connecting the PCMCIA Card

Figure 2.10 shows how to connect the PCMCIA card.

Figure 2.10 PCMCIA Card Connection

To use a PCMCIA card (memory card, I/O card), insert the PCMCIA card into slot 0 or slot 1. To remove the PCMCIA card, press the release button in the direction of the arrow.

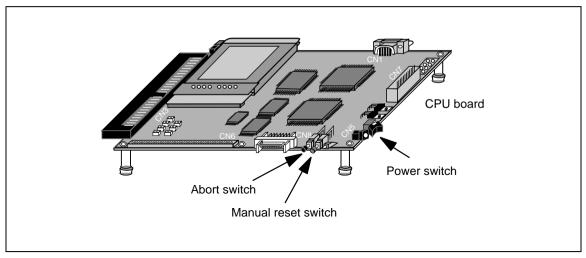

### 2.7 Switches

Table 2.2 lists the switches used in the CPU board and figure 2.11 shows where the three switches are located (on the CPU board).

| Switch                 | Symbol | Туре                   | Function                                                                                                                                                   |

|------------------------|--------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Manual reset<br>switch | SW1    | Push button<br>(Red)   | Forcibly initializes the system. Use this switch when<br>the system does not operate correctly, for example,<br>when the user program goes out of control. |

| Abort switch           | SW2    | Push button<br>(Black) | Forcibly terminates command execution. Aborts user<br>program execution and returns the system to<br>firmware command input wait state.                    |

| Power supply switch    | SW3    | Rocker switch          | Turns on and off the 5 V power supplied to the CPU board.                                                                                                  |

| Table 2.2 | Switch Specifications |

|-----------|-----------------------|

|-----------|-----------------------|

Note If the power supply is turned on while pressing the manual reset switch, the CPU board and HDI will not be started. Please do not operate the manual reset switch while turning on the power.

Figure 2.11 Switch Location

##

Always switch OFF the CPU board and the user system before connecting or disconnecting any CABLES, CONNECTORS, or JUMPERS. Failure to do so will result in a FIRE HAZARD and will damage the user system and the CPU board or will result in PERSONAL INJURY. The USER PROGRAM will be LOST.

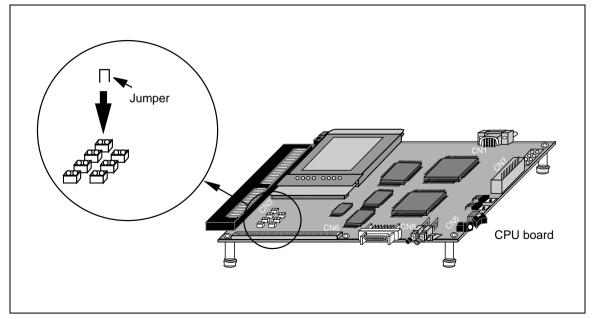

Table 2.3 lists the jumpers on the CPU board and figure 2.12 shows how to insert a jumper pin.

#### Symbol Function Setting Description J1 Selects endian Closed Big endian (default at shipment) Open Little endian For test Be sure to open this jumper.\*2 J2 Open .J3 Selects timer clock External clock TCLK (CN3-158 pin) 1-2 closed 2-3 closed On-board clock (1.8432 MHz) (default at shipment) J4 Not mounted J5 Not mounted J6 Not mounted J7 Selects host computer Closed 115200 bit/s\*3 (default at shipment) interface baud rate Open 57600 bit/s J8 Not mounted J9 Selects bus frequency\*1 J9 J10 J10 Closed Closed 66.7 MHz (default at shipment) Closed Open 33.3 MHz Closed Forbidden Open Open Open Forbidden Enables E10A emulator J11 Closed For use of the emulator Open Emulator not used (default at shipment) J12 Not mounted

#### Table 2.3 Jumper Settings

J13

Not mounted

The same frequency is supplied to the CPU, bus clock, and expansion connectors, but the Notes: 1. CPU internal operating clock always operates at 200 MHz.

2. If jumper J2 is closed, the monitor program will be corrupted. Be sure to open J2.

3. When the bus frequency is set to 33.3 MHz, the CPU board cannot be interfaced with the host computer at 115200 bit/s; set the baud rate to 57600 bit/s.

Figure 2.12 Jumper Insertion

### 2.9 **Power Supply**

#### 2.9.1 **Power-Supply Specifications**

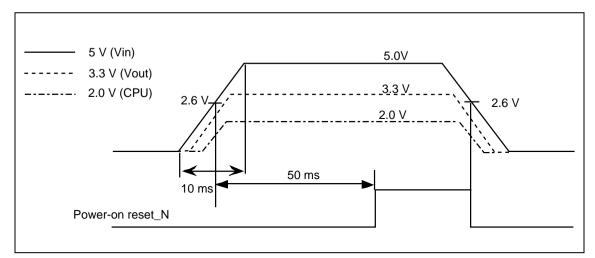

Figure 2.13 shows the power-supply specifications.

Figure 2.13 Power-Supply Specifications

Power should always be supplied to the CPU board using the provided AC power supply adapter and AC power supply cable. The method of connection is shown in figure 2.14.

Observe the precautions listed below. Failure to do so will result in a FIRE HAZARD and will damage the user system and the CPU board or will result in PERSONAL INJURY. The USER PROGRAM will be LOST.

1. Always use the provided AC power supply adapter.

2. Always switch OFF the CPU board and the user system before connecting or disconnecting any CABLES, CONNECTORS, or JUMPERS.

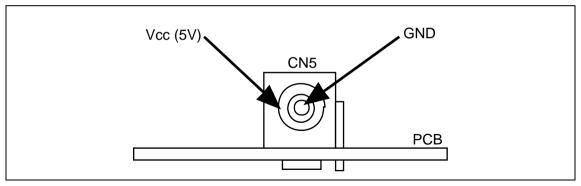

Figure 2.14 Front View of Power Supply Connector

Figure 2.15 AC Power Supply Cable Connection

# Section 3 Tutorial

### 3.1 Introduction

The following describes the main functions of the HDI by using a tutorial program.

The tutorial program is based on the C program that sorts ten random data items in ascending or descending order.

The tutorial program is included in the sort.c file. The compiled load module is provided in the SYSROF format and is included in the sort.abs file.

The tutorial program is automatically installed when the HDI is installed.

Table 3.1 lists the tutorial program configuration.

#### Table 3.1Tutorial Program Configuration

| Item                        | Contents                              |

|-----------------------------|---------------------------------------|

| Tutorial file (load module) | (install directory)\tutorial\sort.abs |

| Tutorial file (source file) | (install directory)\tutorial\sort.c   |

For the operating environment, use the RAM area starting from address H'AC000000. The MMU function is not used.

- Notes: 1. sort.abs operates in big endian. sort.abs must be recompiled to operate in little endian.

- 2. The work space for this tutorial program was created using Version 1.1 (Release 4) of Hitachi Embedded Workshop (HEW).

Hitachi SH C/C++ compiler version 5.1B Hitachi SH IM OptLinker version 1.1B

## 3.2 Running the HDI

To run the HDI, select the [HDI for SH7729R CPU board] from the [Start] menu.

#### Figure 3.1 [Start] Menu

The [HDI] window will open, then the [Select Session] dialog box will appear. Check that the setting shown in figure 3.2 is complete, and click the [OK] button.

| Select Session                                                         | ×                   |

|------------------------------------------------------------------------|---------------------|

| <ul> <li>Create a new session on</li> <li>SH7729R CPU board</li> </ul> | OK<br>E <u>x</u> it |

| © <u>P</u> revious session file:                                       | Browse              |

Figure 3.2 [Select Session] Dialog Box

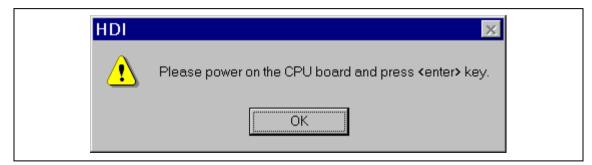

The message box shown in figure 3.3 will appear. Check that the CPU board power is turned on, and click the [OK] button.

Figure 3.3 Power Supply Confirmation Message Box

When Link up appears on the status bar, HDI startup is completed.

If Link up does not appear, check the items listed in table 3.2.

#### Table 3.2 Check Items When HDI Cannot Be Initiated

| Check Item                                                                                     | Reference in this Manual |

|------------------------------------------------------------------------------------------------|--------------------------|

| Check that the power monitoring LED (LED1) on the CPU board is turned on                       | Section 5.5              |

| Check that the host computer and the CPU board are correctly connected through a serial cable. | Sections 2.4 and 5.4.1   |

| Check that the port and baud rate are set correctly in the [Monitor Setup] dialog box.         | Sections 3.5 and 4.2.1   |

| Check that the jumper pins are correctly inserted into the jumpers<br>on the CPU board.        | Section 2.8              |

|   | 🦻 Hita                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | achi Debugging Interface - Sort - SH7729R CPU board 📃 🗆 🗙                     |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| 0 | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | dit ⊻iew <u>R</u> un <u>M</u> emory <u>S</u> etup <u>W</u> indow <u>H</u> elp |

| 0 | j 0 🎘 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | \$2 \$2 \$2 \$2 \$2 \$2 \$2 \$2 \$2 \$2 \$2 \$2 \$2 \$                        |

| 0 | @ @ ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 🗱 📨 🛷 💭 📰 🗐 🕾 📾 📷, 🐺 🖼 💭 🔰 🗓 💈 🖉 A 👫                                          |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Sort.c                                                                        |

|   | WB 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ine Address BP Label Source                                                   |

| 3 | A 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | long i:                                                                       |

|   | <ul> <li>♣</li> <li>↓</li> <li>↓</li></ul> | 5 ac000014 if(j < 0){<br>7 ac000018 j = -j;                                   |

|   | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ac00001c a[i] = j;                                                            |

|   | 20<br>21<br>22<br>23<br>24<br>25<br>24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4 a⊂000048 min = 0:                                                           |

| 4 | For Help, j                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | press F1                                                                      |

Figure 3.4 [HDI] Window

The key functions of the HDI are described in section 4, Descriptions of Windows. Numbers in figure 3.4 indicate the following:

- 1. Menu bar: Gives the user access to the HDI commands for using the HDI debugger.

- 2. Toolbar: Provides convenient buttons as shortcuts for the most frequently used menu commands.

- 3. Program window: Displays the source program being debugged.

- 4. Status bar: Displays the status of the CPU board, and progress information about downloading.

- 5. [Help] button: Activates on-line help about any features of the HDI user interface.

### 3.4 Setting up the CPU Board

The following conditions can be set up on the CPU board before downloading the program:

- Connection method

- I/O definition file

- Options on program load

The following describes how to set up the CPU board for the tutorial programs.

### 3.5 Setting the [Monitor Setup] Dialog Box

• Select [Configure Platform...] from the [Setup] menu to set configuration. The [Monitor Setup] dialog box is displayed.

| ľ | Monitor Setup               |                        | ×            |

|---|-----------------------------|------------------------|--------------|

|   | - Target Monitor Comm       | ms Settings            | OK           |

|   | Comms Port:                 | СОМ1: 💌                | Cancel       |

|   | Baud Rate:                  | 115200 💌               | <u>H</u> elp |

|   | 1/0 definition file:        | SH7729R                | Browse       |

|   | Download with v             | erify                  |              |

|   | 🔲 D <u>e</u> lete breakpoin | its when program is re | loaded       |

|   | □ <u>R</u> eset CPU when    | n program has been de  | ownloaded    |

Figure 3.5 [Monitor Setup] Dialog Box

Set options as follows:

| Option                                            | Default   | Value                                                                                                                                                                                                             |

|---------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Comms Port:                                       | COM1:     | Select from among COM1, COM2, COM3, or COM4 as the host computer serial port.                                                                                                                                     |

| Baud Rate:                                        | 115200    | Sets the serial baud rate. Select either 57600 bit/s or 115200 bit/s, to match the setting of jumper J7. Connection is not possible at any other setting.                                                         |

| I/O definition file                               | SH7729R   | Sets the I/O register definition file. The SH7729R definition file is set as default On selecting a file, the [I/O Registers] window (accessed from the [View] menu) can be used to display register information. |

| Download with verify                              | _         | The CPU board does not support this function (this box cannot be selected).                                                                                                                                       |

| Delete breakpoints<br>when program is<br>reloaded | Unchecked | When this box is checked, all breakpoints are deleted when a program is reloaded.                                                                                                                                 |

| Reset CPU when<br>program has been<br>downloaded  | Unchecked | When this box is checked, registers are initialized* when a program is loaded. No reset signal is input to the CPU board.                                                                                         |

#### Table 3.3 Setting the [Monitor Setup] Dialog Box

Note: Only the program counter and status register and VBR are initialized (PC = H'AC000000 and SR = H'600010E0 The value of VBR depends on the endian).

- Click the [OK] button.

- Notes: 1. The I/O register definition file can be selected in this dialog box. Be sure to select a file within the HDI installation directory. Otherwise, the I/O register window will not operate correctly.

- 2. The name of the I/O register definition file can consist of up to nine characters. This number does not include the file name's extension.

### **3.6 Downloading the Tutorial Program**

### 3.6.1 Downloading the Tutorial Program

Download the object program to be debugged.

• Select [Load Program...] from the [File] menu. The [Load Program] dialog box is displayed. Enter the offset and file name in the [Offset] edit box and [File name] list box as shown in figure 3.6 and click the [Open] button.

Figure 3.6 [Load Program] Dialog Box

When the file has been loaded, the following message box displays information about the memory areas that have been filled with the program code.

| HDI | X                                                                                                              |

|-----|----------------------------------------------------------------------------------------------------------------|

| •   | Module name: C:\HDI5_CB\7729r\tutorial\Sort.abs<br>Areas loaded:<br>AC000000 - AC0001AD<br>AC0001B0 - AC0001BB |

|     | OK                                                                                                             |

Figure 3.7 [HDI] Message Box

• Click the [OK] button to continue.

#### 3.6.2 Displaying the Source Program

The HDI allows the user to debug a program at the source level.

- Select [Source...] from the [View] menu. The [Open] dialog box is displayed.

- Select the C source file that corresponds to the object file the user has loaded.

| Open               |          |   |       |          | ? ×                  |

|--------------------|----------|---|-------|----------|----------------------|

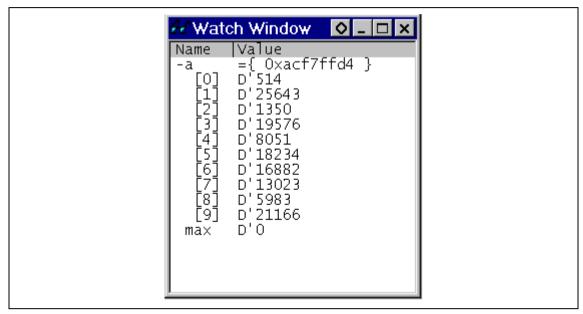

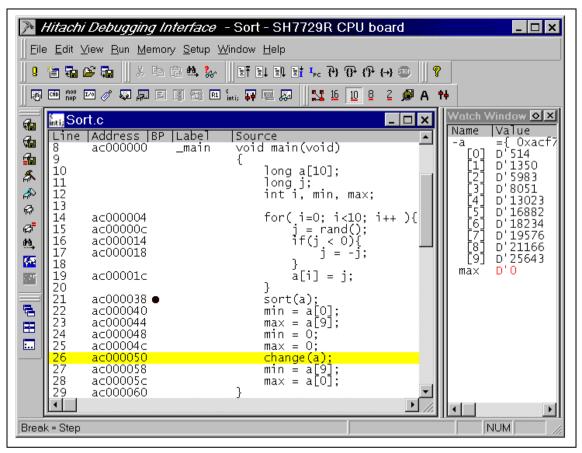

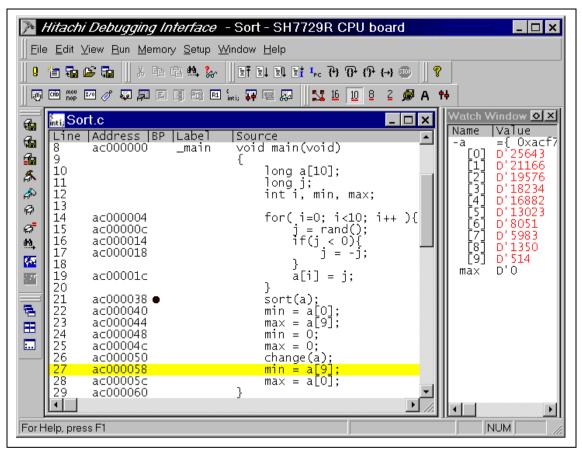

| Look jn: 🔤         | tutorial | • | - 🖻 💆 | <b>e</b> | 8-8-<br>0-0-<br>8-8- |