# R0K572390

SH7239 CPU ボード ユーザーズマニュアル

ルネサスマイクロコンピュータ SuperH<sup>™</sup> RISC engine ファミリ∕SH7239 シリーズ

Rev.1.00

本資料に記載の全ての情報は本資料発行時点のものであり、ルネサス エレクトロニクスは、 予告なしに、本資料に記載した製品または仕様を変更することがあります。 ルネサス エレクトロニクスのホームページなどにより公開される最新情報をご確認ください。

### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネサス エレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

#### WEEE Directive

Renesas development tools and products are directly covered by the European Union's Waste Electrical and Electronic Equipment, (WEEE), Directive 2002/96/EC.

As a result, this equipment, including all accessories, must not be disposed of as household waste but through your locally recognised recycling or disposal schemes.

As part of our commitment to environmental responsibility Renesas also offers to take back the equipment and has implemented a Tools Product Recycling Program for customers in Europe. This allows you to return equipment to Renesas for disposal through our approved Producer Compliance Scheme.

To register for the program, click here "http://www.renesas.com/weee".

# このマニュアルの使い方

### 1. 目的と対象者

このマニュアルは、本 CPU ボードの機能と操作仕様をユーザに理解していただくためのマニュアルです。本 CPU ボードを使用するユーザを対象にしています。このマニュアルを使用するには、電気回路、論理回路、マイクロコンピュータに関する基本的な知識が必要です。

このマニュアルは、大きく分類すると、製品の概要、機能仕様、操作仕様で構成されています。

本 CPU ボードは、注意事項を十分確認の上、使用してください。注意事項は、各章の本文中に記載しています。

改訂記録は旧版の記載内容に対して訂正または追加した主な箇所をまとめたものです。改訂内容すべてを記載したもので はありません。詳細は、このマニュアルの本文でご確認ください。

SH7239 CPU ボード R0K572390 では次のドキュメントを用意しています。

| ドキュメントの種類    | 記載内容              | 資料名             | 資料番号        |

|--------------|-------------------|-----------------|-------------|

| ユーザーズマニュアル   | 機能仕様(搭載デバイス、メモリマッ | SH7239 CPU ボード  | 本ユーザーズマニュアル |

|              | プ、電気的特性等)と操作仕様(コネ | R0K572390 ユーザーズ |             |

|              | クタ、スイッチ類)の説明      | マニュアル           |             |

| インストレーションマニュ | ハードウェアおよびソフトウェアの  | SH7239 CPU ボード  | R20UT0298JJ |

| アル           | セットアップ方法の説明       | R0K572390 インストレ |             |

|              |                   | ーションマニュアル       |             |

SH7239 グループでは次のドキュメントを用意しています。ドキュメントは最新版を使用してください。最新版はルネサス エレクトロニクスホームページに掲載されています。

| ドキュメントの種類                | 記載内容                                                                | 資料名                           | 資料番号        |

|--------------------------|---------------------------------------------------------------------|-------------------------------|-------------|

| ユーザーズマニュアル<br>ハードウェア編    | ハードウェアの仕様(ピン配置、メモリマップ、周辺機能の仕様、電気的特性、タイミング)と動作説明<br>※周辺機能の使用方法はアプリケー |                               | R01UH0086JJ |

|                          | ションノートを参照してください。                                                    |                               |             |

| ソフトウェアマニュアル              | CPU・命令セットの説明                                                        | SH-2A、SH2A-FPU<br>ソフトウェアマニュアル | RJJ09B0086  |

| アプリケーションノート              | 応用例、参考プログラムなど                                                       | ルネサス エレクトロニク                  | スホームページに掲載さ |

| RENESAS TECHNICAL UPDATE | 製品の仕様、ドキュメント等に関する 速報                                                | れています。                        |             |

## 2. 略語および略称の説明

| 略語/略称 | 英語名                                          | 日本語名                       |

|-------|----------------------------------------------|----------------------------|

| ACIA  | Asynchronous Communication Interface Adapter | 調歩同期式通信アダプタ                |

| bps   | bits per second                              | 転送速度を表す単位、ビット/秒            |

| CRC   | Cyclic Redundancy Check                      | 巡回冗長検査                     |

| DMA   | Direct Memory Access                         | CPUの命令を介さずに直接データ転送を行う方式    |

| DMAC  | Direct Memory Access Controller              | DMA を行うコントローラ              |

| GSM   | Global System for Mobile Communications      | FDD-TDMA の第二世代携帯電話の方式      |

| Hi-Z  | High Impedance                               | 回路が電気的に接続されていない状態          |

| IEBus | Inter Equipment bus                          | _                          |

| I/O   | Input/Output                                 | 入出力                        |

| IrDA  | Infrared Data Association                    | 赤外線通信の業界団体または規格            |

| LSB   | Least Significant Bit                        | 最下位ビット                     |

| MSB   | Most Significant Bit                         | 最上位ビット                     |

| NC    | Non-Connection                               | 未接続                        |

| PLL   | Phase Locked Loop                            | 位相同期回路                     |

| PWM   | Pulse Width Modulation                       | パルス幅変調                     |

| SFR   | Special Function Registers                   | 周辺機能を制御するためのレジスタ           |

| SIM   | Subscriber Identity Module                   | ISO/IEC 7816 規定の接触型 IC カード |

| UART  | Universal Asynchronous Receiver/Transmitter  | 調歩同期式シリアルインタフェース           |

| VCO   | Voltage Controlled Oscillator                | 電圧制御発振器                    |

すべての商標および登録商標は、それぞれの所有者に帰属します。

# 目次

| 1. | 概要.   |                                  | 1-1  |

|----|-------|----------------------------------|------|

|    | 1.1   | 概要                               | 1-1  |

|    | 1.2   | 構成                               | 1-2  |

|    | 1.3   | 外部仕様                             | 1-3  |

|    | 1.4   | 外観                               | 1-4  |

|    | 1.5   | ブロック図                            | 1-5  |

|    | 1.6   | 部品配置図                            | 1-6  |

|    | 1.7   | メモリ配置図                           | 1-8  |

|    | 1.8   | 絶対最大定格                           | 1-10 |

|    | 1.9   | 動作条件                             | 1-10 |

| 2. | 機能    | ±様                               | 2-1  |

| ,  | 2.1   | 機能概略                             | 2-1  |

| ,  | 2.2   | CPU                              | 2-2  |

|    | 2.3   | 外付けメモリ                           | 2-3  |

|    | 2.3.1 | SRAM                             | 2-3  |

|    | 2.3.2 | EEPROM                           | 2-5  |

| Ź  | 2.4   | シリアルポートインタフェース                   | 2-6  |

| ź  | 2.5   | 入出力ポート                           | 2-7  |

| ,  | 2.6   | RCANインタフェース                      | 2-11 |

| ,  | 2.7   | LCDインタフェース                       | 2-12 |

|    | 2.8   | H-UDIインタフェース                     |      |

|    | 2.9   | スイッチ、ジャンパ                        |      |

|    | 2.10  | LED、ポテンショメータ                     |      |

|    | 2.11  | 電源モジュール                          |      |

|    |       | クロックモジュール                        |      |

|    | 2.13  | リセットモジュール                        | 2-18 |

| 3. | 操作值   | ±様                               | 3-1  |

| í  | 3.1   | コネクタ概略                           | 3-1  |

|    | 3.1.1 | アプリケーションヘッダ(JA1、JA2、JA3、JA5、JA6) | 3-2  |

|    | 3.1.2 | コモンリングコネクタ(J1、J2、J3、J4)          | 3-9  |

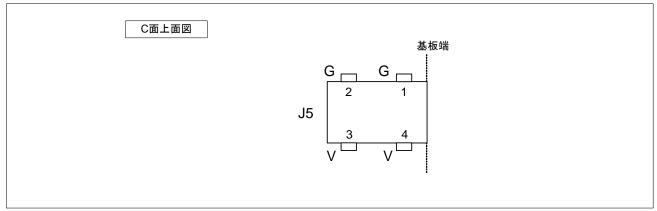

|    | 3.1.3 | DC 電源ジャック(J5)                    | 3-12 |

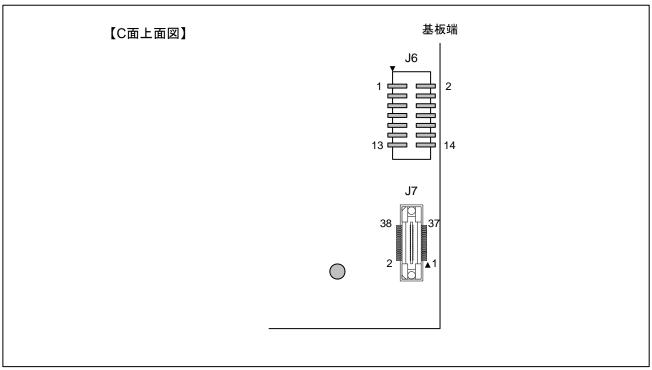

|    | 3.1.4 | H-UDI ポートコネクタ(J6、J7)             | 3-13 |

| 1寸球 RU   | IK5/239U 按統凶            |      |

|----------|-------------------------|------|

| /+43 D.0 | )K572390 接続図            |      |

| 3.3      | 外形寸法                    | 3-23 |

| 3.2.4    | LED                     |      |

| 3.2.3    | ポテンショメータ                | _    |

| 3.2.2    | スイッチ                    | 3-21 |

| 3.2.1    | ジャンパ (JP1、JP2、JP3)      | 3-20 |

| 3.2      | 操作系部品の概要                | 3-19 |

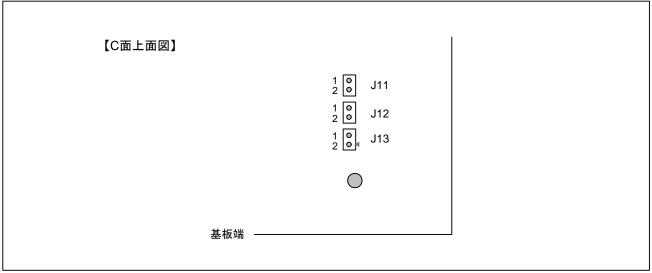

| 3.1.8    | 外部電源供給コネクタ(J11、J12、J13) | 3-18 |

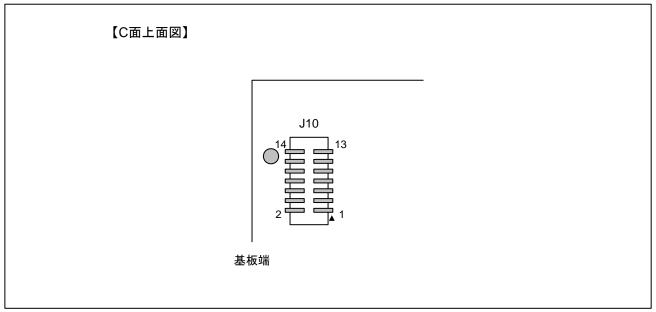

| 3.1.7    | LCD インタフェースコネクタ (J10)   | 3-17 |

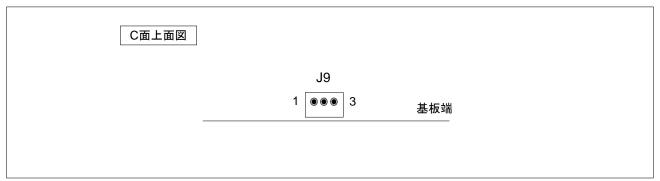

| 3.1.6    | RCAN ポートコネクタ(J9)        | 3-16 |

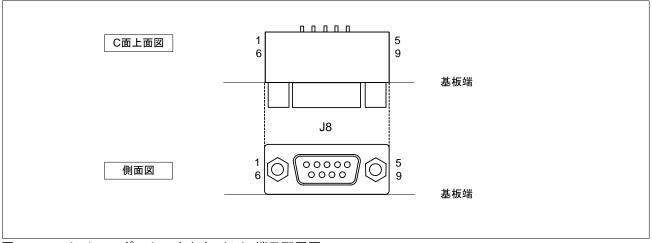

| 3.1.5    | シリアルポートコネクタ(J8)         | 3-15 |

### 1. 概要

### 1.1 概要

R0K572390は、ルネサスエレクトロニクス製シングルチップ RISC マイクロコンピュータSH7239の機能・性能評価及び、アプリケーションソフトウェアの開発・評価を行なうための CPU ボードです。SH7239の製品展開にあわせて以下の2種類がラインアップされています。

- R0K572390C000BR: SH7239A搭載(3.3V、160MHz動作)

- R0K572390C020BR: SH7239B搭載(5.0V、100MHz動作)

SH7239の内蔵周辺機能の端子は、コモンリングコネクタおよびアプリケーションヘッダに接続されており、計測機器を用いた周辺デバイスとのタイミング評価や、開発用途に合わせた拡張ボードの開発が可能です。また、ルネサスエレクトロニクス製オンチップエミュレータ E10A-USB の接続が可能です。

### 1.2 構成

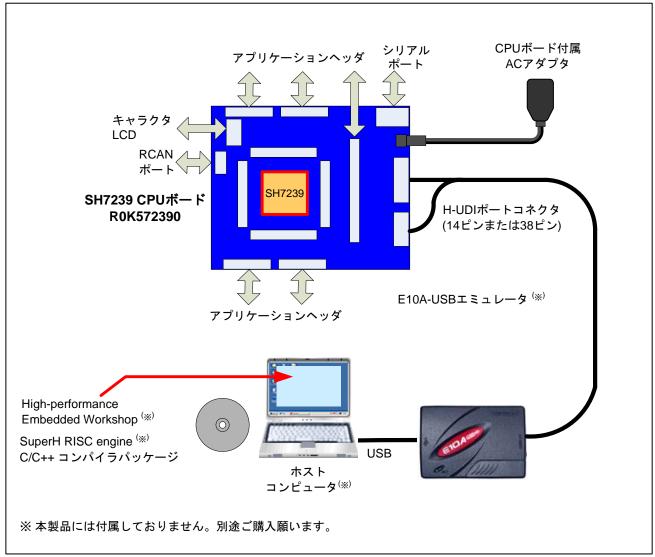

図 1.1にR0K572390を用いたシステム構成例を示します。

図1.1 R0K572390を用いたシステム構成例

### 1.3 外部仕様

表 1.1にR0K572390の外部仕様一覧を示します。

### 表1.1 R0K572390外部仕様一覧

| 項目           | 内容                                                          |

|--------------|-------------------------------------------------------------|

| CPU          | SH7239A <sup>*1</sup> またはSH7239B <sup>*2</sup>              |

|              | • 入力(XIN)クロック:10MHz <sup>*1</sup> または 12.5MHz <sup>*2</sup> |

|              | • CPU クロック:最大 160MHz <sup>*1</sup> または 100MHz <sup>*2</sup> |

|              | • 周辺クロック:最大 40MHz <sup>*1</sup> または 50MHz <sup>*2</sup>     |

|              | <ul><li>内蔵メモリ</li></ul>                                     |

|              | フラッシュメモリ:512K バイト                                           |

|              | RAM: 64K バイト                                                |

|              | FLD(データ格納用フラッシュメモリ): 32K バイト                                |

| メモリ          | • EEPROM: 64K バイト (SPI インタフェース)                             |

|              | • SRAM: 64K バイト(8 ビットバス幅×2)(未実装) <sup>*3</sup>              |

| コネクタ         | • コモンリングコネクタ(CPU の全信号)(未実装)                                 |

|              | • アプリケーションヘッダ(バス、I/O、VCC、GND) (未実装)                         |

|              | • シリアルポートコネクタ(D-sub 9 ピン)                                   |

|              | • RCAN ポートコネクタ(3 ピン、ピンヘッダ)                                  |

|              | • LCD インタフェースコネクタ(14 ピン)                                    |

|              | • H-UDI ポートコネクタ(14 ピン)                                      |

|              | • H-UDI ポートコネクタ(38 ピン)                                      |

| LED、ポテンショメータ | • 電源用 LED: 1                                                |

|              | • ブートモード用 LED : 1                                           |

|              | • ユーザ用 LED : 4                                              |

|              | • ポテンショメータ(10kΩ):1                                          |

| スイッチ、ジャンパ    | • リセットスイッチ:1                                                |

|              | • ユーザスイッチ:3(NMI、IRQ3 またはADTRG、IRQ4)                         |

|              | • モード設定用ディップスイッチ:1(2極)                                      |

|              | • 電源選択用ジャンパ:1 (未実装) *4                                      |

|              | • RCAN 信号接続用ジャンパ: 1 (未実装)                                   |

|              | ADTRG信号接続用ジャンパ: 1 (未実装)                                     |

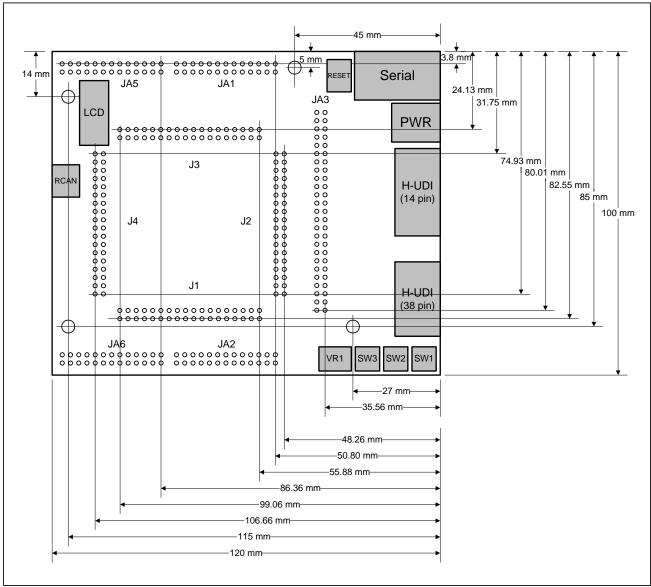

| 基板仕様         | • 寸法:100mm×120mm                                            |

|              | • 実装形態:4層 両面実装                                              |

|              | • 基板構成:1枚                                                   |

- 【注】\*1 R0K572390C000BR の場合です。

- \*2 R0K572390C020BR の場合です。

- \*3 R0K572390C000BR のみユーザが実装することができます。

- \*4 電源電圧は、R0K572390C000BR では 3.3V に、R0K572390C020BR では 5V に固定されます。

#### 外観 1.4

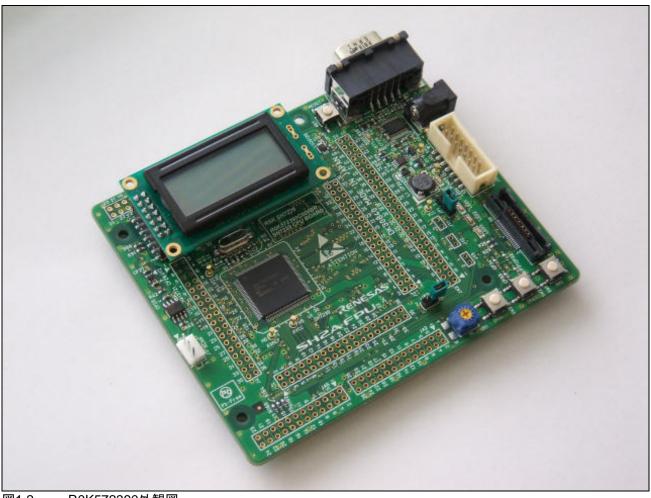

図 1.2にR0K572390の外観を示します。

R0K572390外観図 図1.2

### 1.5 ブロック図

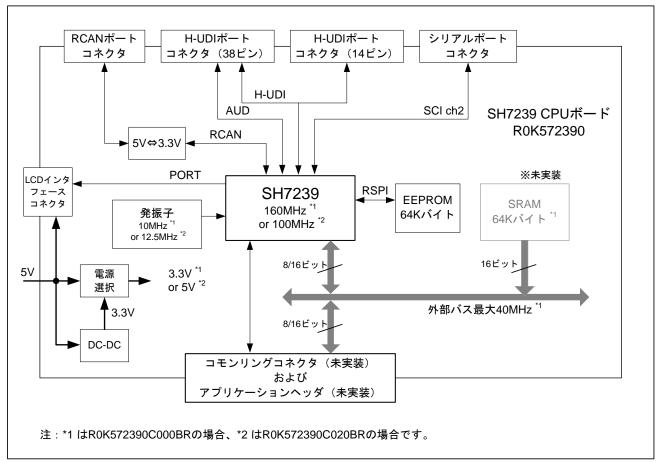

図 1.3にR0K572390のブロック図を示します。

図1.3 R0K572390ブロック図

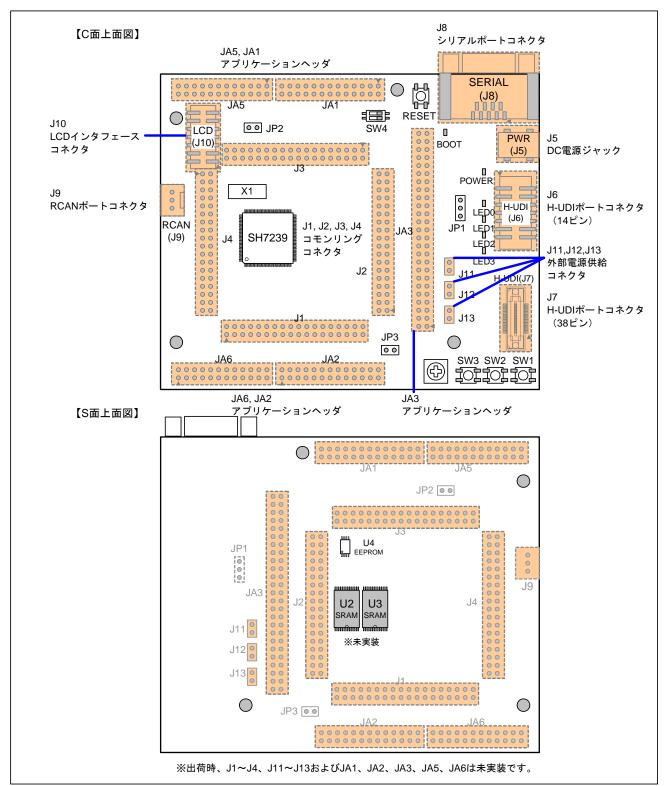

### 1.6 部品配置図

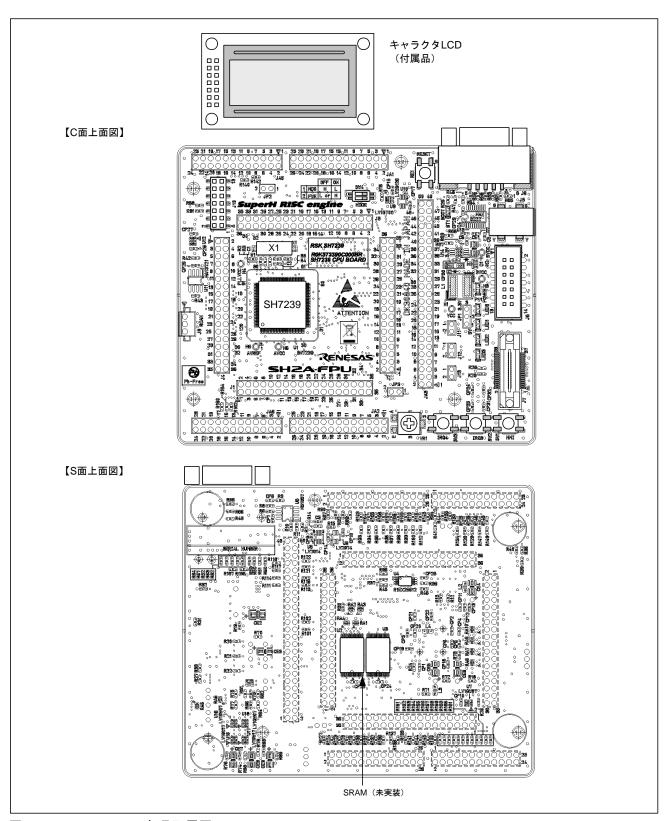

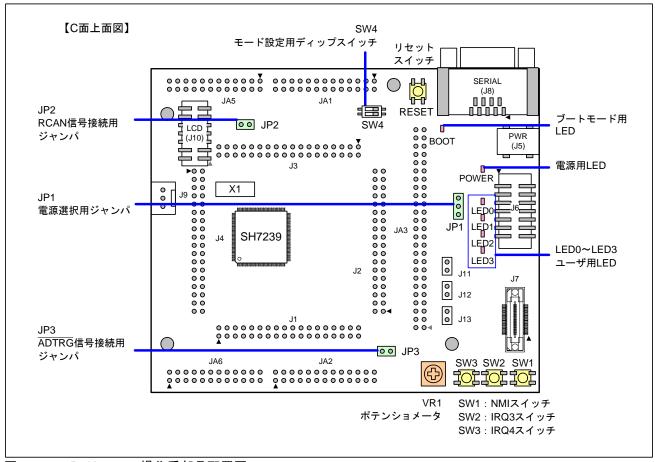

図 1.4にR0K572390の部品配置図を示します。

図1.4 R0K572390部品配置図

表 1.2にR0K572390の主な実装部品一覧を示します。

表1.2 R0K572390の主な実装部品一覧

| 部品番号          | 部品名称                 | 型名、メーカ                                                          | 未実装品推奨型名等                                  |

|---------------|----------------------|-----------------------------------------------------------------|--------------------------------------------|

| U1            | CPU                  | SH7239A *1 (ルネサス)                                               |                                            |

|               |                      | SH7239B *2 (ルネサス)                                               |                                            |

| U2, U3        | SRAM                 | 未実装 *3                                                          | M5M5256DVP-70G(ルネサス)                       |

| U4            | EEPROM               | R1EX25512ATA00A(ルネサス)                                           |                                            |

| U13           | RS-232C トランシーバ       | MAX3222CPWR (TI)                                                |                                            |

| U11           | RCAN トランシーバ          | HA13721RPJE(ルネサス)                                               |                                            |

| U14           | 3.3V レギュレータ          | LM2738-YMY 550kHz (NS)                                          |                                            |

| U6            | リセットIC               | M51957BFP(ルネサス)                                                 |                                            |

| X1            | 発振子 (水晶)             | CXZ49GFB10000H0PESZZ *1<br>CXZ49GFB12500H0PESZZ *2<br>(京セラキンセキ) |                                            |

| J1~J4         | コモンリングコネクタ           | 未実装                                                             | 18 ピン×2 列ピンヘッダ                             |

| JA1, JA2      | アプリケーションヘッダ          | 未実装                                                             | 13 ピン×2 列ピンヘッダ                             |

| JA3           | アプリケーションヘッダ          | 未実装                                                             | 25 ピン×2 列ピンヘッダ                             |

| JA5, JA6      | アプリケーションヘッダ          | 未実装                                                             | 12 ピン×2 列ピンヘッダ                             |

| J5            | DC 電源ジャック            | KLDX-SMT2-0202-A (Kycon)                                        |                                            |

| J6            | H-UDI ポートコネクタ(14 ピン) | HTST-107-01-T-DV (Samtec)                                       |                                            |

| J7            | H-UDI ポートコネクタ(38 ピン) | 2-5767004-2                                                     |                                            |

|               |                      | (タイコエレクトロニクスアンプ)                                                |                                            |

| J8            | シリアルポートコネクタ          | 154188 (ERNI)                                                   |                                            |

| J9            | RCAN ポートコネクタ         | B3P-SHF-1AA(LF)(SN)(日圧)                                         |                                            |

| J10           | LCD インタフェースコネクタ      | SSM-107-LM-DV-P-TR (Samtec)                                     |                                            |

| J11           | 外部電源供給コネクタ           | 未実装                                                             | A2-2PA-2.54DSA (ヒロセ)                       |

| J12           | 外部電源供給コネクタ           | 未実装                                                             | A2-2PA-2.54DSA (ヒロセ)                       |

| J13           | 外部電源供給コネクタ           | 未実装                                                             | A2-2PA-2.54DSA (ヒロセ)                       |

| POWER         | 電源用 LED              | 緑色                                                              |                                            |

| BOOT          | ブートモード用 LED          | 橙色                                                              |                                            |

| LED0~<br>LED3 | ユーザ用 LED             | 緑色、橙色、赤色、赤色                                                     |                                            |

| VR1           | ポテンショメータ             | CT-6ETV10KΩ(日本電産コパル)                                            |                                            |

| RESET         | リセットスイッチ             | B3S-1000 (オムロン)                                                 |                                            |

| SW1           | NMI スイッチ             | B3S-1000 (オムロン)                                                 |                                            |

| SW2, SW3      | IRQ3, IRQ4 スイッチ      | B3S-1000 (オムロン)                                                 |                                            |

|               | モード設定用ディップスイッチ       | A6HF-2102 (オムロン)                                                |                                            |

| SW4           | (2 極)                |                                                                 |                                            |

| SW4<br>JP1    | (2極)<br>電源選択用ジャンパ    | <br>  未実装 <sup>*4</sup>                                         | 2.54mm ピッチ 3 極ピンヘッダ                        |

|               |                      | 未実装 <sup>*4</sup><br>未実装                                        | 2.54mm ピッチ 3 極ピンヘッダ<br>2.54mm ピッチ 2 極ピンヘッダ |

- 【注】\*1 R0K572390C000BR の場合です。

- \*2 R0K572390C020BR の場合です。

- \*3 R0K572390C000BR の場合のみユーザが実装することができます。

- \*4 R0K572390C000BR では 3.3V 側に、R0K572390C020BR では 5V 側に固定されます。

### 1.7 メモリ配置図

図 1.5、図 1.6にR0K572390でのSH7239のメモリ配置を示します。

| SI                                        | H7239論理空間 MCUモード3               |                                           | R0K572390メモリ配置            |

|-------------------------------------------|---------------------------------|-------------------------------------------|---------------------------|

| H'0000 0000                               | (シングルチップモード)<br>内蔵ROM (512Kバイト) | н'0000 0000                               | 内蔵ROM (512Kバイト)           |

| н'0008 0000                               | 予約領域                            | н'0008 0000                               | 予約領域                      |

| н'0040 2000                               | FCUファーム領域 (8Kバイト)               | н'0040 2000                               | FCUファーム領域 (8Kバイト)         |

| H'0040 4000                               |                                 | H'0040 4000                               |                           |

|                                           | 予約領域                            |                                           | 予約領域                      |

| H'800F FFFF<br>H'8010 0000<br>H'8010 8000 | データフラッシュ (32Kバイト)<br>予約領域       | H'800F FFFF<br>H'8010 0000<br>H'8010 8000 | データフラッシュ (32Kバイト)<br>予約領域 |

| H'80FF 7FFF<br>H'80FF 8000                | FOLIDAM (OK & C.L.)             | H'80FF 7FFF<br>H'80FF 8000                |                           |

| H'80FF A000                               | FCURAM (8Kバイト)<br>予約領域          | H'80FF A000                               | FCURAM (8Kバイト)<br>予約領域    |

| H'FFF7 FFFF<br>H'FFF8 0000                | 内蔵RAM (32Kバイト)                  | H'FFF7 FFFF<br>H'FFF8 0000                | 内蔵RAM (32Kバイト)            |

| H'FFF8 8000                               | 予約領域                            | H'FFF8 8000                               | 予約領域                      |

| H'FFF9 0000                               | 内蔵RAM (32Kバイト)                  | H'FFF9 0000                               | 内蔵RAM (32Kバイト)            |

| H'FFF9 8000                               | 予約領域                            | H'FFF9 8000                               | 予約領域                      |

| H'FFFD FFFF                               | ሆሉ ነ የ                          | H'FFFD FFFF                               |                           |

| H'FFFE 0000                               |                                 | H'FFFE 0000                               |                           |

| 11 11111 0000                             |                                 |                                           |                           |

| H'FFFF FFFF                               | 周辺I/O                           | H'FFFF FFFF                               | 周辺I/O                     |

図1.5 SH7239メモリ配置 (MCU モード 3)

| н.0000 0000                | (内蔵ROM有効モード)<br>内蔵ROM (512Kバイト) | н'0000 0000                | 内蔵ROM (512Kバイト)                   |

|----------------------------|---------------------------------|----------------------------|-----------------------------------|

| н'0008 0000                | 内蔵ROM (512Kハイト)           予約領域  | н'0008 0000                | - <u>内蔵ROM (512K/ハイト)</u><br>予約領域 |

| н'0040 2000                | FCUファーム領域 (8Kバイト)               | н'0040 2000                | FCUファーム領域 (8Kバイト)                 |

| H'0040 4000                | 予約領域                            | H'0040 4000                | 予約領域                              |

| н'0200 0000                |                                 | н'0200 0000                | SRAM (64Kバイト) *1                  |

| H'0220 0000                | CS0空間                           | H'0201 0000<br>H'0220 0000 | 未使用領域                             |

| H'0420 0000                | 予約領域                            | H'0400 0000                | 予約領域 予約領域                         |

| 11 0400 0000               | CS1空間                           | 11 0400 0000               | 未使用領域                             |

| H'0420 0000                |                                 | н'0420 0000                |                                   |

|                            | 予約領域                            |                            | 予約領域                              |

|                            | 7 4512 2                        | _                          | 7 1212 2                          |

| H'0BFF FFFF<br>H'0C00 0000 | CCOTT BI                        | H'0BFF FFFF<br>H'0C00 0000 | +                                 |

| H'0C20 0000                | CS3空間                           | H'0C20 0000                | 未使用領域<br>                         |

| H'1000 0000                | 予約領域                            | H'1000 0000                | 予約領域 予約領域                         |

| 11 1000 0000               | CS4空間                           | 11 1000 0000               | 未使用領域                             |

| н'1020 0000                | 予約領域                            | н'1020 0000                | 予約領域                              |

| H'1400 0000                | CS5空間                           | H'1400 0000                | 未使用領域                             |

| H'1420 0000                | 予約領域                            | H'1420 0000                | 予約領域                              |

| н'1800 0000                |                                 | н'1800 0000                |                                   |

| H'1820 0000                | CS6空間                           | H'1820 0000                | 未使用領域<br>—————————————————————    |

|                            | 予約領域                            |                            | 予約領域                              |

| H'800F FFFF<br>H'8010 0000 | データフラッシュ (32Kバイト)               | H'800F FFFF<br>H'8010 0000 | <br>データフラッシュ (32Kバイト              |

| н'8010 8000                | 7-37777 (3210 17 17)            | н'8010 8000                | ) — \$ 2 7 9 2 ± (32K) (4   1     |

|                            | 予約領域                            |                            | 予約領域                              |

| H'80FF 7FFF<br>H'80FF 8000 | FCURAM (8Kバイト)                  | H'80FF 7FFF<br>H'80FF 8000 | FCURAM (8Kバイト)                    |

| H'80FF A000                | 1 CORAW (BRO 14)                | H'80FF A000                | T COTO TIVI (OTO T   1 )          |

|                            |                                 |                            |                                   |

|                            | 予約領域                            |                            | 予約領域                              |

|                            |                                 |                            |                                   |

| H'FFF7 FFFF<br>H'FFF8 0000 |                                 | H'FFF7 FFFF<br>H'FFF8 0000 |                                   |

|                            | 内蔵RAM (32Kバイト)                  |                            | 内蔵RAM (32Kバイト)                    |

| H'FFF8 8000                | 予約領域                            | H'FFF8 8000                | 予約領域                              |

| H'FFF9 0000<br>H'FFF9 8000 | 内蔵RAM (32Kバイト)                  | H'FFF9 0000<br>H'FFF9 8000 | 内蔵RAM (32Kバイト)                    |

| 11 1119 6000               |                                 | 11 222 3000                |                                   |

|                            | 予約領域                            |                            | 予約領域                              |

|                            | 3 4.3 150.50                    |                            | 1 4.7 KY.SA                       |

| H'FFFD FFFF<br>H'FFFE 0000 |                                 | H'FFFD FFFF                |                                   |

| H'FFFE 0000                | E TUO                           | H'FFFE 0000                | ELITI/O                           |

|                            | 周辺I/O                           |                            | 周辺I/O                             |

図1.6 SH7239メモリ配置(MCUモード 2、R0K572390C000BR のみ設定可能)

### 1.8 絶対最大定格

表 1.3にR0K572390の絶対最大定格を示します。

### 表1.3 R0K572390の絶対最大定格

| 記号               | 項目           | 定格値        | 備考                |

|------------------|--------------|------------|-------------------|

| 5VCC             | 5V 系電源電圧     | -0.3V~6.0V | VSS 基準            |

| 3VCC *1          | 3.3V 系電源電圧   | −0.3V~4.0V | VSS 基準            |

| AVCC             | 5V 系アナログ電源電圧 | -0.3V~6.0V | AVSS 基準           |

| T <sub>opr</sub> | 動作周囲温度 *2    | 0°C~50°C   | 結露なきこと、腐蝕性ガス環境は不可 |

| T <sub>stg</sub> | 保存周囲温度 *2    | −10°C~60°C | 結露なきこと、腐蝕性ガス環境は不可 |

<sup>【</sup>注】\*1 外部電源供給コネクタから直接 3.3V 系電源を供給する場合の規格です。

### 1.9 動作条件

表 1.4にR0K572390の動作条件を示します。

### 表1.4 R0K572390の動作条件

| 記号               | 項目           | 定格値         | 備考                          |

|------------------|--------------|-------------|-----------------------------|

| 5VCC             | 5V 系電源電圧     | 4.75V~5.25V | VSS 基準                      |

| 3VCC *1          | 3.3V 系電源電圧   | 3.15V~3.45V | VSS 基準                      |

| AVCC             | 5V 系アナログ電源電圧 | 4.75V~5.25V | AVSS 基準                     |

| _                | 最大消費電流       | 1A 以下       | 5V 系電源(アナログ含む)、3.3V 系電源の合計値 |

| T <sub>opr</sub> | 動作周囲温度 *2    | 0°C~50°C    | 結露なきこと、腐蝕性ガス環境は不可           |

<sup>【</sup>注】\*1 外部電源供給コネクタから直接 3.3V 系電源を供給する場合の規格です。

<sup>\*2</sup> 周囲温度とはボードに限りなく近い部分の空気の温度のことを言います。

<sup>\*2</sup> 周囲温度とはボードに限りなく近い部分の空気の温度のことを言います。

## 2. 機能仕様

### 2.1 機能概略

R0K572390は、表 2.1に示す機能を有しています。

表2.1 R0K572390機能モジュール一覧

| 項番   | 機能             | 内容                                                          |

|------|----------------|-------------------------------------------------------------|

| 2.2  | CPU            | SH7239A <sup>*1</sup> またはSH7239B <sup>*2</sup>              |

|      |                | • 入力(XIN)クロック:10MHz <sup>*1</sup> または 12.5MHz <sup>*2</sup> |

|      |                | • CPU クロック:最大 160MHz <sup>*1</sup> または 100MHz <sup>*2</sup> |

|      |                | • 周辺クロック:最大 40MHz <sup>*1</sup> または 50MHz <sup>*2</sup>     |

|      |                | • 内蔵メモリ フラッシュメモリ: 512K バイト                                  |

|      |                | RAM : 64K バイト                                               |

|      |                | FLD(データ格納用フラッシュメモリ):32K バイト                                 |

| 2.3  | 外付けメモリ         | 以下のメモリを搭載                                                   |

|      |                | • EEPROM: 64K バイト (SPI インタフェース)                             |

|      |                | • SRAM : 64K バイト(8 ビットバス幅×2、 未実装) <sup>*3</sup>             |

| 2.4  | シリアルポートインタフェース | SH7239の SCI Ch2 をシリアルポートコネクタに接続                             |

| 2.5  | 入出力ポート         | SH7239の全信号をコモンリングコネクタに、バスおよび入出力ポート等を                        |

|      |                | アプリケーションヘッダに接続                                              |

| 2.6  | RCANインタフェース    | SH7239の RCAN 端子を RCAN トランシーバ経由で RCAN ポートコネクタ                |

|      |                | に接続                                                         |

| 2.7  | LCDインタフェース     | キャラクタ LCD インタフェース                                           |

| 2.8  | H-UDIインタフェース   | SH7239の H-UDI/AUD 端子を H-UDI ポートコネクタ(14 ピン、38 ピン)            |

|      |                | に接続、E10A-USB を用いたデバッグが可能 <sup>*4</sup>                      |

| 2.9  | スイッチ、ジャンパ      | 以下のスイッチ、ジャンパを搭載                                             |

|      |                | • リセットスイッチ                                                  |

|      |                | • ユーザスイッチ:3(NMI、IRQ3 またはADTRG、IRQ4 端子に接続)                   |

|      |                | • モード設定用ディップスイッチ:1(2極)                                      |

|      |                | • 電源選択用ジャンパ:1 (未実装)                                         |

|      |                | - RCAN 信号接続用ジャンパ: 1 (未実装)                                   |

|      |                | • ADTRG信号接続用ジャンパ:1       (未実装)                              |

| 2.10 | LED、ポテンショメータ   | 以下の LED およびポテンショメータを実装                                      |

|      |                | • 電源用 LED: 1                                                |

|      |                | • ブートモード用 LED : 1                                           |

|      |                | • ユーザ用 LED : 4                                              |

| 0.44 | <b>高海エン</b>    | <ul><li>ポテンショメータ(10kΩ):1</li></ul>                          |

| 2.11 | 電源モジュール        | ROK572390のシステム電源制御                                          |

| 2.12 | クロックモジュール      | クロック源:水晶発振子 10MHz *1 または 12.5MHz *2                         |

| 2.13 | リセットモジュール<br>  | - ROK572390に実装されているデバイスのリセット制御                              |

|      | +              | • リセットスイッチとユーザスイッチ SW1 を用いたブートモード制御                         |

| -    | 操作仕様           | コネクタ、スイッチ、LED、ポテンショメータの詳細は、第3章で説明しま                         |

|      |                | す。                                                          |

- 【注】\*1 R0K572390C000BR の場合です。

- \*2 R0K572390C020BR の場合です。

- \*3 R0K572390C000BR のみユーザが実装することができます。

- \*4 アプリケーションヘッダでアドレス A16~A20、AHを使用する場合、H-UDIポートコネクタは使用できません。

### 2.2 CPU

R0K572390は、製品展開ごとにそれぞれ以下のマイクロコンピュータを搭載しています。

- R0K572390C000BR: SH7239A(3.3V、CPUクロック最大160MHz/周辺クロック最大40MHz動作)

- R0K572390C020BR: SH7239B(5.0V、CPUクロック最大100MHz/周辺クロック最大50MHz動作)

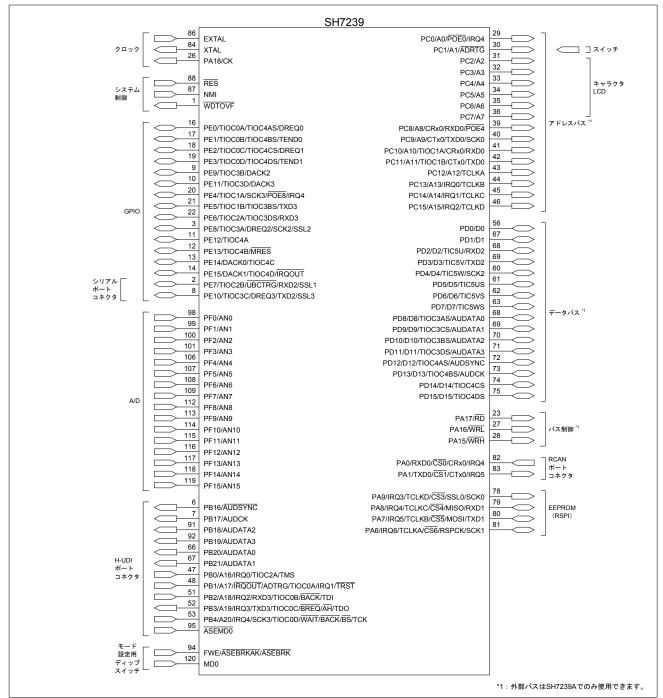

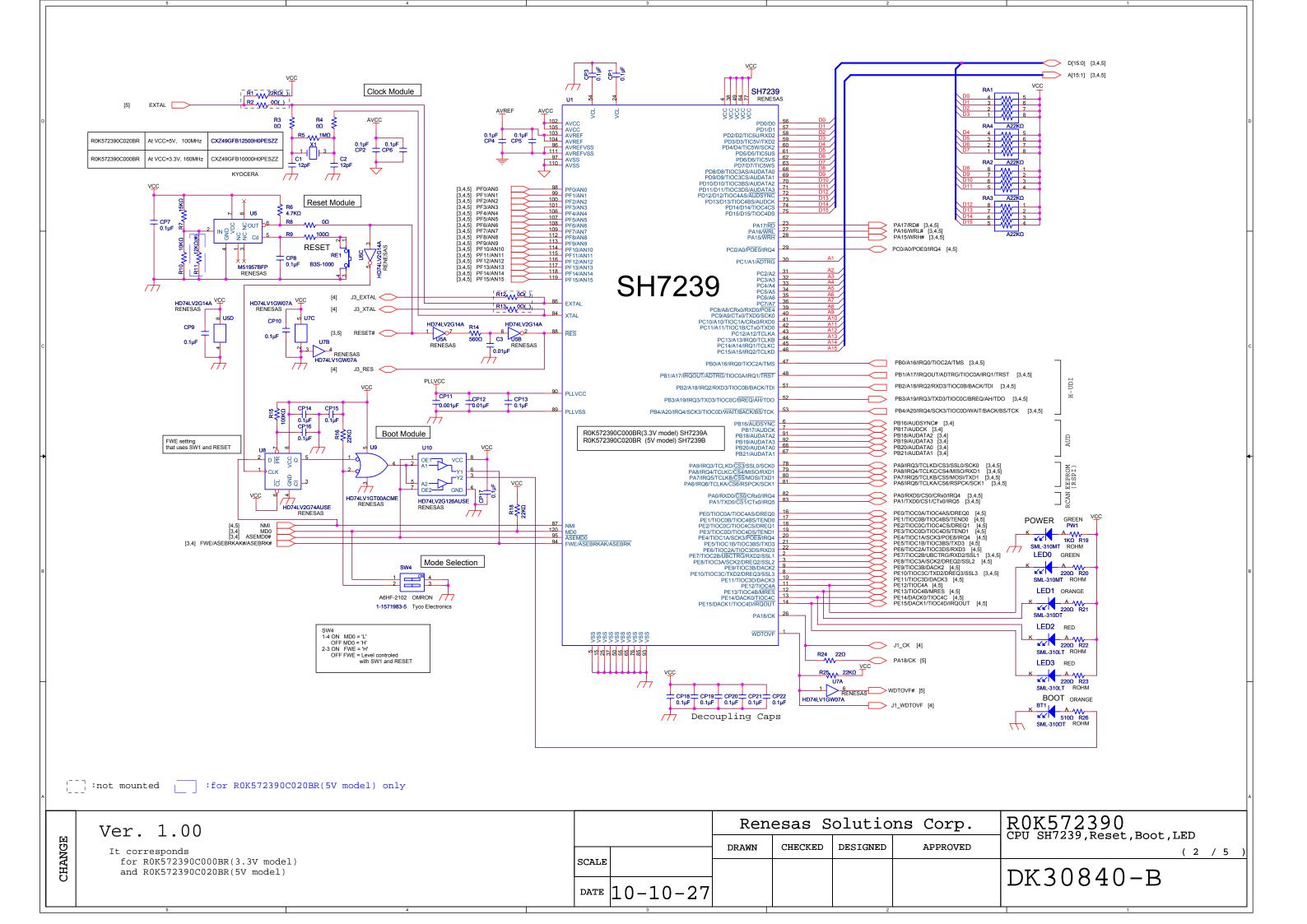

SH7239A、SH7239B は、512K バイトのフラッシュメモリ、32K バイトの FLD、64K バイトの RAM を内蔵しており、データ処理、機器制御等の多様な応用分野に対応することのできるマイクロコンピュータです。図 2.1にR0K572390におけるSH7239ブロック図を示します。

図2.1 SH7239ブロック図

### 2.3 外付けメモリ

### 2.3.1 SRAM

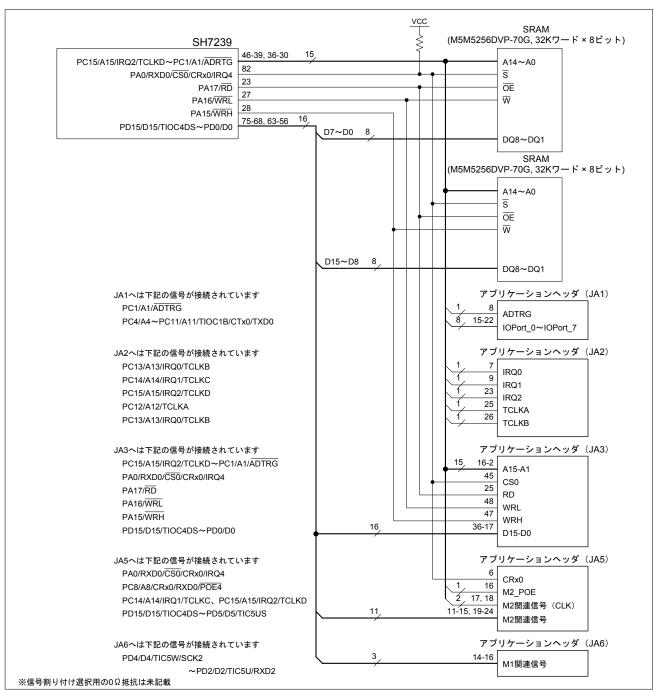

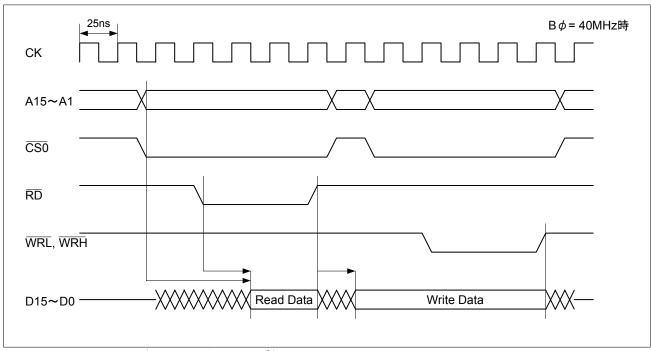

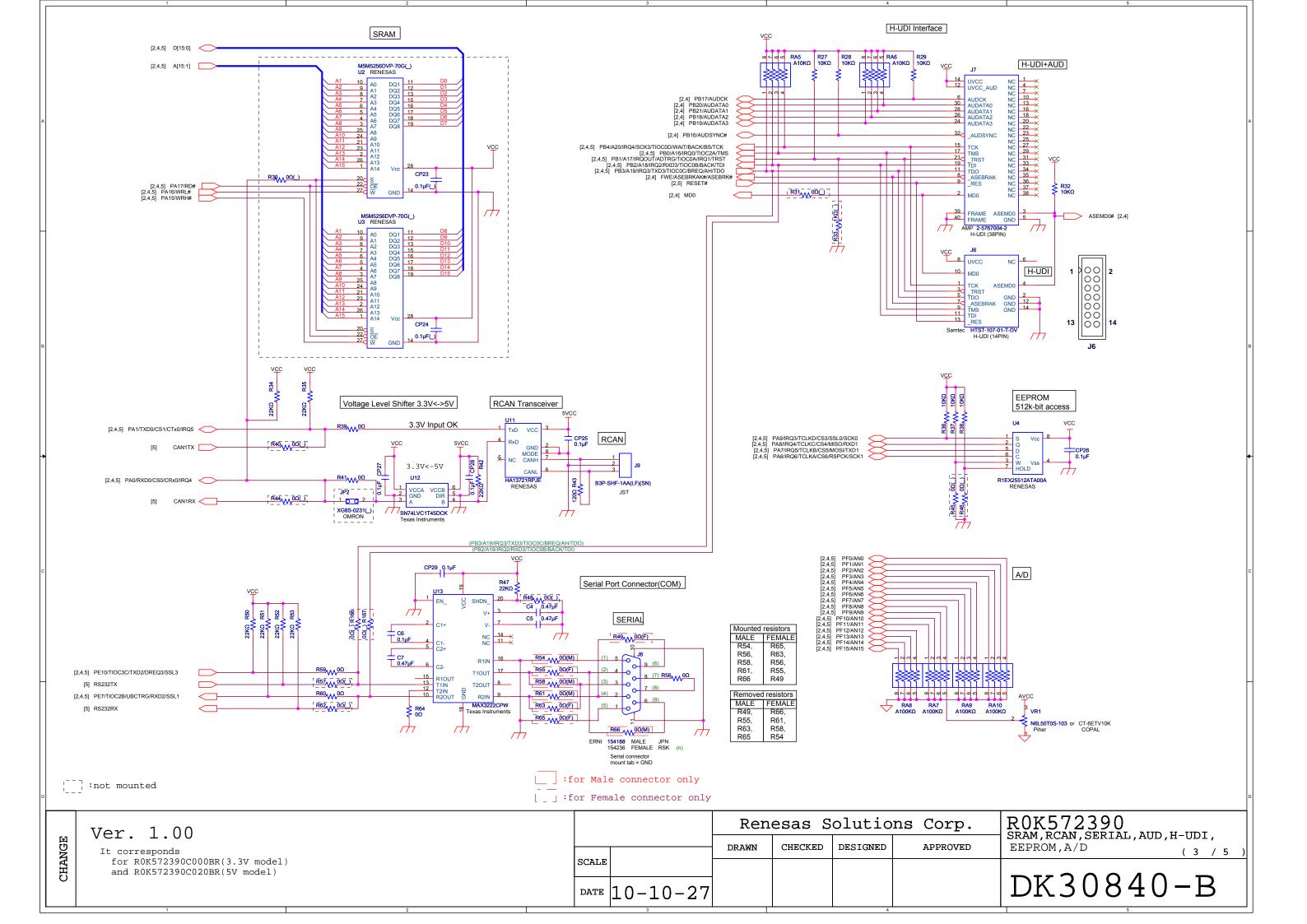

R0K572390には、64K バイトの SRAM(32K ワード×8 ビット×2 個)を実装することができます(出荷時未実装)。SRAM の制御は、SH7239に内蔵されたバスステートコントローラの $\overline{\text{CS0}}$ により行います。

本 SRAM は、SH7239A を MCU モード 2 に設定した場合のみ使用できます。また、SRAM 制御に使用する $\overline{\text{CSO}}$  は RCAN の CRx0 と共用のため、RCAN 機能と SRAM を同時に使用することはできません。SRAM 使用時は、信号接続先を切り替えるために抵抗 R41 を取り外し、出荷時未実装の抵抗 R30 を取り付けてください。

図 2.2にSH7239とSRAMの接続回路構成を示します。

図2.2 SRAM 接続回路構成

図2.3 SRAM リード/ライトタイミング例

### 表2.2 バスステートコントローラ設定例(SRAM リード・ライト)

| ユーザ領域        | 対象デバイス                   | バスステートコントローラ設定                                                              |

|--------------|--------------------------|-----------------------------------------------------------------------------|

| ユーザ領域<br>CS0 | 対象デバイス<br>M5M5256DVP-70G | バスステートコントローラ設定  CS0 空間バスコントロールレジスタ(CS0BCR): 推奨設定値:H'0240 0400 ・サイクル間アイドル指定: |

|              |                          | SW[1:0] = B'01 ; 1.5 サイクル                                                   |

|              |                          | WR[3:0] = B'0010;2 サイクル<br>・外部ウェイトマスク指定:<br>WM = B'1;外部ウェイト入力無視             |

|              |                          | ・RD、WRxxネゲート→アドレス、CSOネゲート遅延サイクル数:<br>HW[1:0] = B'00; 0.5 サイクル               |

### 2.3.2 EEPROM

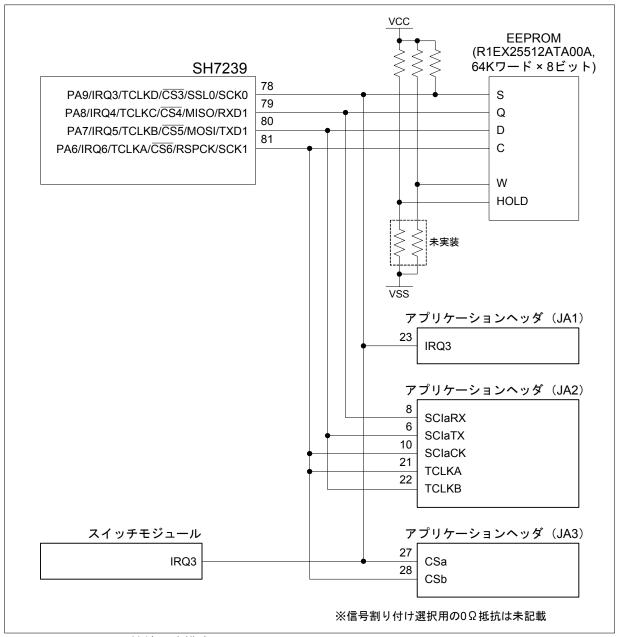

R0K572390には、64K バイトの EEPROM(64K ワード×8 ビット×1 個)を実装しています。EEPROM の制御は、SH7239に内蔵されたルネサスシリアルペリフェラルインタフェースにより行います。

本 EEPROM の制御に使用する各端子は、ユーザスイッチ SW2、アプリケーションヘッダ(JA1、JA2 および JA3)にも SCI Ch1 関連端子、MTU2 関連端子、および IRQ3、 $\overline{\text{CS3}}$ および $\overline{\text{CS6}}$ 信号として接続されており、重複して使用することはできないため、注意してください。

図 2.4にSH7239とEEPROMの接続回路構成を示します。

図2.4 EEPROM 接続回路構成

#### シリアルポートインタフェース 2.4

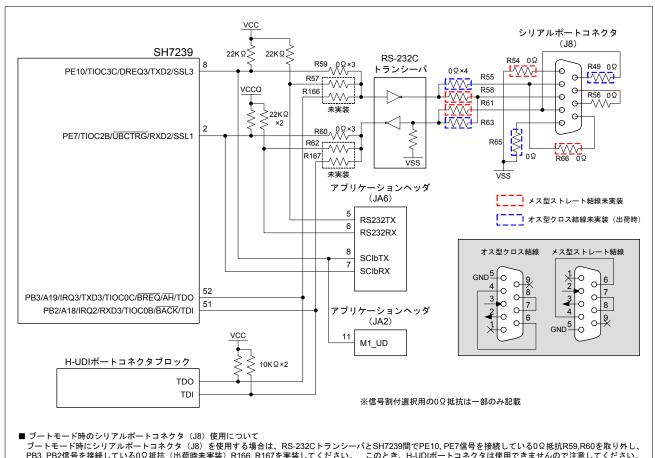

R0K572390では、SH7239の SCI Ch2 が RS-232C トランシーバ経由でシリアルポートコネクタ (J8) に接続さ れています。また、SH7239の SCI Ch2 は、アプリケーションヘッダ(JA6)の7ピン、8ピンおよびアプリケ ーションヘッダ (JA2) の11 ピン (TIOC3C として使用) にも接続されています。さらに、アプリケーション ヘッダ(JA6)の5ピン、6ピンをRS-232Cトランシーバ経由でシリアルポートコネクタ(J8)に接続するこ ともできます。この場合、接続先選択に使用している 0Ω抵抗を付け替えてください。ただし、SH7239の SCI Ch2 をシリアルポートとして使用する場合は、アプリケーションヘッダと重複して使用できません。

ブートモード等でシリアルポートコネクタ(J8)を使用したい場合は、RS-232CトランシーバとSH7239間 で PE10、PE7 信号を接続している  $0\Omega$ 抵抗 R59、R60 を取り外し、PB3、PB2 信号を接続している  $0\Omega$ 抵抗(出 荷時未実装) R166、R167を取り付けてください。この場合、H-UDIポートコネクタは使用できないため、注 意してください。

図 2.5に、R0K572390におけるシリアルポートブロック図を示します。

- ブートモード時にシリアルボーニホック(J8)を使用する場合は、RS-232CトランシーバとSH7239間でPE10, PE7信号を接続している0Ω抵抗R59,R60を取り外し、 PB3, PB2信号を接続している0Ω抵抗(出荷時未実装)R166, R167を実装してください。 このとき、H-UDIポートコネクタは使用できませんので注意してください。

図2.5 シリアルポートブロック図

### 2.5 入出力ポート

R0K572390では、SH7239の全ての信号がコモンリングコネクタに接続されています。また、ほとんどの入出 力ポートがアプリケーションヘッダにも接続されています。表 2.3~表 2.6に入出力ポート機能表を示します。 また一部の入出力ポートは、ボード上のデバイス、各 I/O コネクタやスイッチ、LED などにも接続されてい ますが、これらの信号接続については第3章 操作仕様で説明していますのでそちらを参照してください。

表2.3 入出力ポート機能表 (1/4)

|    | SH7239                      | コモ | ンリン | グコネ | ・クタ | アプリケーションヘッダ |      |      |      |       |               |  |

|----|-----------------------------|----|-----|-----|-----|-------------|------|------|------|-------|---------------|--|

| 番号 | 端子名                         | J1 | J2  | J3  | J4  | JA1         | JA2  | JA3  | JA5  | JA6   | 使用機能          |  |

| 1  | WDTOVF                      | 1  |     |     |     |             | [5]  |      |      |       | WDTOVF        |  |

| 2  | PE7/TIOC2B/UBCTRG/RXD2/SSL1 | 2  |     |     |     |             |      |      |      | (7)   | RXD2          |  |

| 3  | PE8/TIOC3A/SCK2/DREQ2/SSL2  | 3  |     |     |     |             |      |      |      | (10), | SCK2, TIOC3A  |  |

|    |                             |    |     |     |     |             |      |      |      | [13]  |               |  |

| 4  | VCC                         | 4  |     |     |     |             |      |      |      |       |               |  |

| 5  | VSS                         | 5  |     |     |     |             |      |      |      |       |               |  |

| 6  | PB16/AUDSYNC                | 6  |     |     |     |             |      |      |      |       |               |  |

| 7  | PB17/AUDCK                  | 7  |     |     |     |             |      |      |      |       |               |  |

| 8  | PE10/TIOC3C/TXD2/DREQ3/SSL3 | 8  |     |     |     |             | [11] |      |      | (8)   | TIOC3C, TXD2  |  |

| 9  | PE9/TIOC3B/DACK2            | 9  |     |     |     |             | 13   |      |      |       | TIOC3B        |  |

| 10 | PE11/TIOC3D/DACK3           | 10 |     |     |     |             | 14   |      |      |       | TIOC3D        |  |

| 11 | PE12/TIOC4A                 | 11 |     |     |     |             | 15   |      |      |       | TIOC4A        |  |

| 12 | PE13/TIOC4B/MRES            | 12 |     |     |     |             | 17   |      |      |       | TIOC4B        |  |

| 13 | PE14/DACK0/TIOC4C           | 13 |     |     |     |             | [16] |      |      | (2)   | TIOC4C, DACK0 |  |

| 14 | PE15/DACK1/TIOC4D/IRQOUT    | 14 |     |     |     |             | 18   |      |      |       | TIOC4D        |  |

| 15 | VSS                         | 15 |     |     |     |             |      |      |      |       |               |  |

| 16 | PE0/TIOC0A/TIOC4AS/DREQ0    | 16 |     |     |     | (23)        | (7)  |      |      | (1)   | TIOC0A, DREQ0 |  |

| 17 | PE1/TIOC0B/TIOC4BS/TEND0    | 17 |     |     |     |             | (9)  |      | (9)  | (3)   | TIOC0B, TEND0 |  |

| 18 | PE2/TIOC0C/TIOC4CS/DREQ1    | 18 |     |     |     |             | (23) |      | (10) |       | TIOC0C        |  |

| 19 | PE3/TIOC0D/TIOC4DS/TEND1    | 19 |     |     |     |             |      |      | (14) | [16]  | TIOCOD        |  |

| 20 | PE4/TIOC1A/SCK3/POE8/IRQ4   | 20 |     |     |     |             | (23) |      | [9], | (11), | TIOC1A, IRQ4, |  |

|    |                             |    |     |     |     |             |      |      | (12) | (14)  | SCK3          |  |

| 21 | PE5/TIOC1B/TIOC3BS/TXD3     | 21 |     |     |     |             | [19] |      |      | (9)   | TIOC1B, TXD3  |  |

| 22 | PE6/TIOC2A/TIOC3DS/RXD3     | 22 |     |     |     |             | [20] |      | (13) | (12)  | TIOC2A, RXD3  |  |

|    |                             |    |     |     |     |             |      |      |      | (15)  |               |  |

| 23 | PA17/RD                     | 23 |     |     |     |             |      | 25   |      |       | RD            |  |

| 24 | VCL                         |    |     |     |     |             |      |      |      |       |               |  |

| 25 | VSS                         | 25 |     |     |     |             |      |      |      |       |               |  |

| 26 | PA18/CK                     | 26 |     |     |     |             |      | [44] |      |       | СК            |  |

| 27 | PA16/WRL                    | 27 |     |     |     |             |      | 48   |      |       | WRL           |  |

| 28 | PA15/WRH                    | 28 |     |     |     |             |      | 47   |      |       | WRH           |  |

| 29 | PC0/A0/POE0/IRQ4            | 29 |     |     |     |             | 24   | 1    |      |       | POE0, A0      |  |

| 30 | PC1/A1/ADTRG                | 30 |     |     |     | 8           |      | 2    |      |       | ADTRG, A1     |  |

<sup>【</sup>注】 []: デバイスや  $0\Omega$ 抵抗(実装)を経由して CPU 端子に接続されている信号です。

<sup>():</sup>  $0\Omega$ 抵抗(未実装)を経由して CPU 端子に接続されている信号です。各信号を使用するコネクタ、端子にあわせて  $0\Omega$ 抵抗を付け替えてください。このとき、信号が競合しないよう注意してください。

表2.4 入出力ポート機能表(2/4)

|    | SH7239                                    | コモ | ンリン | グコネ | ヘクタ | アプリケーションヘッダ |            |               |      |      |                      |  |  |

|----|-------------------------------------------|----|-----|-----|-----|-------------|------------|---------------|------|------|----------------------|--|--|

| 番号 | 端子名                                       | J1 | J2  | J3  | J4  | JA1         | JA2        | JA3           | JA5  | JA6  | 使用機能                 |  |  |

| 31 | PC2/A2                                    |    | 1   |     |     |             |            | 3             |      |      | A2                   |  |  |

| 32 | PC3/A3                                    |    | 2   |     |     |             |            | 4             |      |      | A3                   |  |  |

| 33 | PC4/A4                                    |    | 3   |     |     | (15)        |            | 5             |      |      | PC4, A4              |  |  |

| 34 | PC5/A5                                    |    | 4   |     |     | (16)        |            | 6             |      |      | PC5, A5              |  |  |

| 35 | PC6/A6                                    |    | 5   |     |     | (17)        |            | 7             |      |      | PC6, A6              |  |  |

| 36 | PC7/A7                                    |    | 6   |     |     | (18)        |            | 8             |      |      | PC7, A7              |  |  |

| 37 | VSS                                       |    | 7   |     |     |             |            |               |      |      |                      |  |  |

| 38 | VCC                                       |    | 8   |     |     |             |            |               |      |      |                      |  |  |

| 39 | PC8/A8/CRx0/RXD0/POE4                     |    | 9   |     |     | (19)        |            | 9             | 16   |      | PC8, A8, POE4        |  |  |

| 40 | PC9/A9/CTx0/TXD0/SCK0                     |    | 10  |     |     | (20)        |            | 10            |      |      | PC9, A9              |  |  |

| 41 | PC10/A10/TIOC1A/CRx0/RXD0                 |    | 11  |     |     | (21)        |            | 11            |      |      | PC10, A10            |  |  |

| 42 | PC11/A11/TIOC1B/CTx0/TXD0                 |    | 12  |     |     | (22)        |            | 12            |      |      | PC11, A11            |  |  |

| 43 | PC12/A12/TCLKA                            |    | 13  |     |     |             | 25         | 13            |      |      | TCLKA, A12           |  |  |

| 44 | PC13/A13/IRQ0/TCLKB                       |    | 14  |     |     |             | [7],<br>26 | 14            |      |      | IRQ0, TCLKB,<br>A13, |  |  |

| 45 | PC14/A14/IRQ1/TCLKC                       |    | 15  |     |     |             | [9]        | 15            | (17) |      | IRQ1, A14,<br>TCLKC  |  |  |

| 46 | PC15/A15/IRQ2/TCLKD                       |    | 16  |     |     |             | [23]       | 16            | (18) |      | IRQ2, A15,<br>TCLKD  |  |  |

| 47 | PB0/A16/IRQ0/TIOC2A/TMS                   |    | 17  |     |     |             |            | (37)          |      |      | A16                  |  |  |

| 48 | PB1/A17/IRQOUT/ADTRG/TIOC0A/IRQ1/TRST     |    | 18  |     |     |             |            | (38)          |      |      | A17                  |  |  |

| 49 | vcc                                       |    | 19  |     |     |             |            |               |      |      |                      |  |  |

| 50 | VSS                                       |    | 20  |     |     |             |            |               |      |      |                      |  |  |

| 51 | PB2/A18/IRQ2/RXD3/TIOC0B/BACK/TDI         |    | 21  |     |     |             |            | (39)          |      |      | A18                  |  |  |

| 52 | PB3/A19/IRQ3/TXD3/TIOC0C/BREQ/AH/TDO      |    | 22  |     |     |             |            | (40),<br>(46) |      |      | A19, AH              |  |  |

| 53 | PB4/A20/IRQ4/SCK3/TIOC0D/WAIT/BACK/BS/TCK |    | 23  |     |     |             |            | (45)          |      |      | A20                  |  |  |

| 54 | VCL                                       |    |     |     |     |             |            |               |      |      |                      |  |  |

| 55 | VSS                                       |    | 25  |     |     |             |            |               |      |      |                      |  |  |

| 56 | PD0/D0                                    |    | 26  |     |     |             |            | 17            |      |      | D0                   |  |  |

| 57 | PD1/D1                                    |    | 27  |     |     |             |            | 18            |      |      | D1                   |  |  |

| 58 | PD2/D2/TIC5U/RXD2                         |    | 28  |     |     |             |            | 19            |      | [14] | D2, TIC5U            |  |  |

| 59 | PD3/D3/TIC5V/TXD2                         |    | 29  |     |     |             |            | 20            |      | [15] | D3, TIC5V            |  |  |

| 60 | PD4/D4/TIC5W/SCK2                         |    | 30  |     |     |             |            | 21            |      | [16] | D4, TIC5W            |  |  |

<sup>【</sup>注】 []: デバイスや 0  $\Omega$ 抵抗(実装)を経由して CPU 端子に接続されている信号です。

<sup>():</sup>  $0\Omega$ 抵抗(未実装)を経由して CPU 端子に接続されている信号です。各信号を使用するコネクタ、端子にあわせて  $0\Omega$ 抵抗を付け替えてください。このとき、信号が競合しないよう注意してください。

表2.5 入出力ポート機能表(3/4)

| SH7239 |                               |    | ンリン | グコネ  | ヘクタ | アプリケーションヘッダ |               |      |              |     |                 |  |  |

|--------|-------------------------------|----|-----|------|-----|-------------|---------------|------|--------------|-----|-----------------|--|--|

| 番号     | 端子名                           | J1 | J2  | J3   | J4  | JA1         | JA2           | JA3  | JA5          | JA6 | 使用機能            |  |  |

| 61     | PD5/D5/TIC5US                 |    |     | 1    |     |             |               | 22   | [12]         |     | D5, TIC5US      |  |  |

| 62     | PD6/D6/TIC5VS                 |    |     | 2    |     |             |               | 23   | [13]         |     | D6, TIC5VS      |  |  |

| 63     | PD7/D7/TIC5WS                 |    |     | 3    |     |             |               | 24   | [14]         |     | D7, TIC5WS      |  |  |

| 64     | VCC                           |    |     | 4    |     |             |               |      |              |     |                 |  |  |

| 65     | VSS                           |    |     | 5    |     |             |               |      |              |     |                 |  |  |

| 66     | PB20/AUDATA0                  |    |     | 6    |     |             |               |      |              |     |                 |  |  |

| 67     | PB21/AUDATA1                  |    |     | 7    |     |             |               |      |              |     |                 |  |  |

| 68     | PD8/D8/TIOC3AS/AUDATA0        |    |     | 8    |     |             |               | 29   | [15]         |     | D8, TIOC3AS     |  |  |

| 69     | PD9/D9/TIOC3CS/AUDATA1        |    |     | 9    |     |             |               | 30   | (11)         |     | D9, TIOC3CS     |  |  |

| 70     | PD10/D10/TIOC3BS/AUDATA2      |    |     | 10   |     |             |               | 31   | 19           |     | D10, TIOC3BS    |  |  |

| 71     | PD11/D11/TIOC3DS/AUDATA3      |    |     | 11   |     |             |               | 32   | 20           |     | D11, TIOC3DS    |  |  |

| 72     | PD12/D12/TIOC4AS/AUDSYNC      |    |     | 12   |     |             |               | 33   | 21           |     | D12, TIOC4AS    |  |  |

| 73     | PD13/D13/TIOC4BS/AUDCK        |    |     | 13   |     |             |               | 34   | 23           |     | D13, TIOC4BS    |  |  |

| 74     | PD14/D14/TIOC4CS              |    |     | 14   |     |             |               | 35   | 22           |     | D14, TIOC4CS    |  |  |

| 75     | PD15/D15/TIOC4DS              |    |     | 15   |     |             |               | 36   | 24           |     | D15, TIOC4DS    |  |  |

| 76     | VSS                           |    |     | 16   |     |             |               |      |              |     |                 |  |  |

| 77     | VCC                           |    |     | 17   |     |             |               |      |              |     |                 |  |  |

| 78     | PA9/IRQ3/TCLKD/CS3/SSL0/SCK0  |    |     | 18   |     | [23]        |               | (27) |              |     | IRQ3, CS3       |  |  |

| 79     | PA8/IRQ4/TCLKC/CS4/MISO/RXD1  |    |     | 19   |     |             | 8             |      |              |     | RXD1            |  |  |

| 80     | PA7/IRQ5/TCLKB/CS5/MOSI/TXD1  |    |     | 20   |     |             | (6),<br>[22]  |      |              |     | TXD1, TCLKB     |  |  |

| 81     | PA6/IRQ6/TCLKA/CS6/RSPCK/SCK1 |    |     | 21   |     |             | (10),<br>[21] | (28) |              |     | SCLK1,TCLKA,CS6 |  |  |

| 82     | PA0/RXD0/CS0/CRx0/IRQ4        |    |     | 22   |     |             |               | (45) | (6)          |     | CS0, CRx0       |  |  |

| 83     | PA1/TXD0/CS1/CTx0/IRQ5        |    |     | 23   |     |             |               |      | (5),<br>[10] |     | CTx0, IRQ5      |  |  |

| 84     | XTAL                          |    |     | (24) |     |             |               |      |              |     |                 |  |  |

| 85     | VSS                           |    |     | 25   |     |             |               |      |              |     |                 |  |  |

| 86     | EXTAL                         |    |     | (26) |     |             | (2)           |      |              |     | EXTAL           |  |  |

| 87     | NMI                           |    |     | 27   |     |             | 3             |      |              |     | NMI             |  |  |

| 88     | RES                           |    |     | 28   |     |             | [1]           |      |              |     | RES             |  |  |

| 89     | PLLVSS                        |    |     |      |     |             |               |      |              |     |                 |  |  |

| 90     | PLLVCC                        |    |     |      |     |             |               |      |              |     |                 |  |  |

<sup>【</sup>注】 []: デバイスや 0  $\Omega$  抵抗 (実装) を経由して CPU 端子に接続されている信号です。

<sup>():</sup>  $0\Omega$ 抵抗(未実装)を経由して CPU 端子に接続されている信号です。各信号を使用するコネクタ、端子にあわせて  $0\Omega$ 抵抗を付け替えてください。このとき、信号が競合しないよう注意してください。

表2.6 入出力ポート機能表(4/4)

| SH7239 |                     |    | ンリン | グコネ | ・クタ | アプリケーションヘッダ |     |     |     |     |       |  |

|--------|---------------------|----|-----|-----|-----|-------------|-----|-----|-----|-----|-------|--|

| 番号     | 端子名                 | J1 | J2  | J3  | J4  | JA1         | JA2 | JA3 | JA5 | JA6 | 使用機能  |  |

| 91     | PB18/AUDATA2        |    |     |     | 1   |             |     |     |     |     |       |  |

| 92     | PB19/AUDATA3        |    |     |     | 2   |             |     |     |     |     |       |  |

| 93     | VSS                 |    |     |     | 3   |             |     |     |     |     |       |  |

| 94     | FWE/ASEBRKAK/ASEBRK |    |     |     | 4   |             |     |     |     |     |       |  |

| 95     | ASEMD0              |    |     |     | 5   |             |     |     |     |     |       |  |

| 96     | AVREFVSS            |    |     |     | 6   |             |     |     |     |     |       |  |

| 97     | AVSS                |    |     |     | 7   | 6           |     |     |     |     | AVSS  |  |

| 98     | PF0/AN0             |    |     |     | 8   | 9           |     |     |     |     | AN0   |  |

| 99     | PF1/AN1             |    |     |     | 9   | 10          |     |     |     |     | AN1   |  |

| 100    | PF2/AN2             |    |     |     | 10  | 11          |     |     |     |     | AN2   |  |

| 101    | PF3/AN3             |    |     |     | 11  | 12          |     |     |     |     | AN3   |  |

| 102    | AVCC                |    |     |     | 12  | 5           |     |     |     |     | AVCC  |  |

| 103    | AVREF               |    |     |     | 13  | 7           |     |     |     |     | AVREF |  |

| 104    | AVREF               |    |     |     | 14  |             |     |     |     |     |       |  |

| 105    | AVCC                |    |     |     | 15  |             |     |     |     |     |       |  |

| 106    | PF4/AN4             |    |     |     | 16  |             |     |     | 1   |     | AN4   |  |

| 107    | PF5/AN5             |    |     |     | 17  |             |     |     | 2   |     | AN5   |  |

| 108    | PF6/AN6             |    |     |     | 18  |             |     |     | 3   |     | AN6   |  |

| 109    | PF7/AN7             |    |     |     | 19  |             |     |     | 4   |     | AN7   |  |

| 110    | AVSS                |    |     |     | 20  |             |     |     |     |     |       |  |

| 111    | AVREFVSS            |    |     |     | 21  |             |     |     |     |     |       |  |

| 112    | PF8/AN8             |    |     |     | 22  | [15]        |     |     |     |     | PF8   |  |

| 113    | PF9/AN9             |    |     |     | 23  | [16]        |     |     |     |     | PF9   |  |

| 114    | PF10/AN10           |    |     |     | 24  | [17]        |     |     |     |     | PF10  |  |

| 115    | PF11/AN11           |    |     |     | 25  | [18]        |     |     |     |     | PF11  |  |

| 116    | PF12/AN12           |    |     |     | 26  | [19]        |     |     |     |     | PF12  |  |

| 117    | PF13/AN13           |    |     |     | 27  | [20]        |     |     |     |     | PF13  |  |

| 118    | PF14/AN14           |    |     |     | 28  | [21]        |     |     |     |     | PF14  |  |

| 119    | PF15/AN15           |    |     |     | 29  | [22]        |     |     |     |     | PF15  |  |

| 120    | MD0                 |    |     |     | 30  |             |     |     |     |     |       |  |

【注】 []: デバイスや 0  $\Omega$  抵抗(実装)を経由して CPU 端子に接続されている信号です。

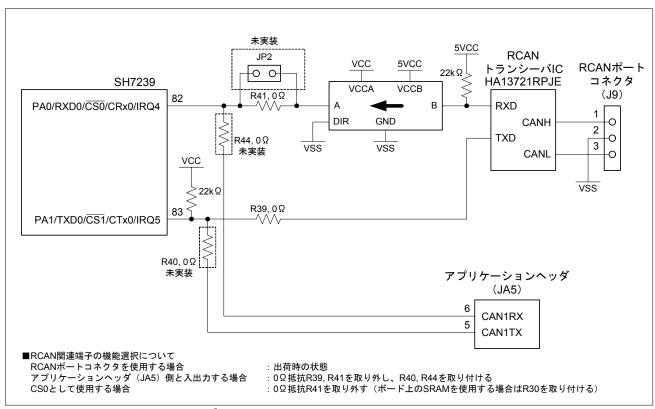

### 2.6 RCAN インタフェース

ROK572390では、RCAN ポートコネクタ(J9、3 ピンコネクタ)を実装しており、SH7239の CTx0 は  $0\Omega$ 抵抗と RCAN トランシーバ IC を介して、CRx0 は  $0\Omega$ 抵抗とレベルシフタおよび RCAN トランシーバ IC を経由して接続されています。CTx0、CRx0 はアプリケーションヘッダ(JA5)にも接続されており、選択して使用することができます。アプリケーションヘッダ(JA5)側を使用する場合は、接続先選択に使用している  $0\Omega$ 抵抗を付け替えてください。RCAN ポートコネクタとアプリケーションヘッダ側の CAN 信号を重複して使用することはできません。

SH7239の PA0/RXD0/ $\overline{CS0}$ /CRx0/IRQ4 端子は $\overline{CS0}$ の機能としても使用されており、 $0\Omega$ 抵抗の付け替えで選択します。CRx0 として RCAN ポートコネクタを使用する場合は、出荷時の状態のままで使用してください。 $\overline{CS0}$  の機能として使用する場合は、必ず  $0\Omega$ 抵抗 R41 を取り外してください。この場合、RCAN ポートコネクタ (J9) は使用できません。

$0\Omega$ 抵抗 R41 を取り付けたままで PA0/RXD0/ $\overline{\text{CSO}}$ /CRx0/IRQ4 端子を出力端子に設定しないように注意してください。

図 2.6にRCANインタフェースブロック図を示します。

図2.6 RCAN インタフェースブロック図

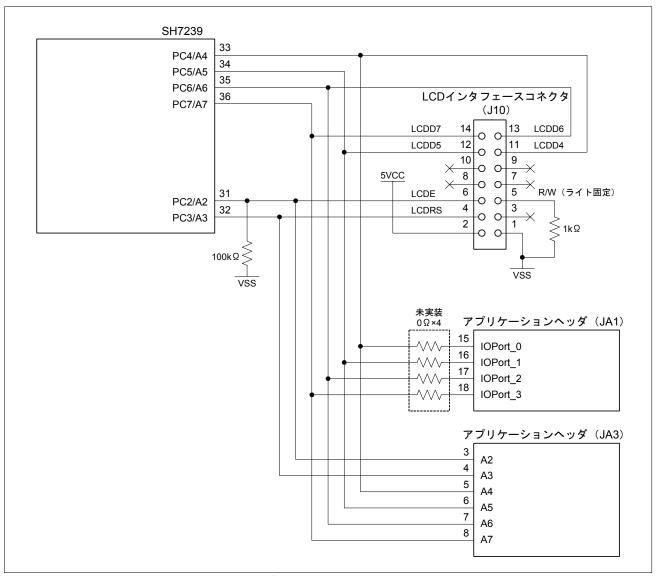

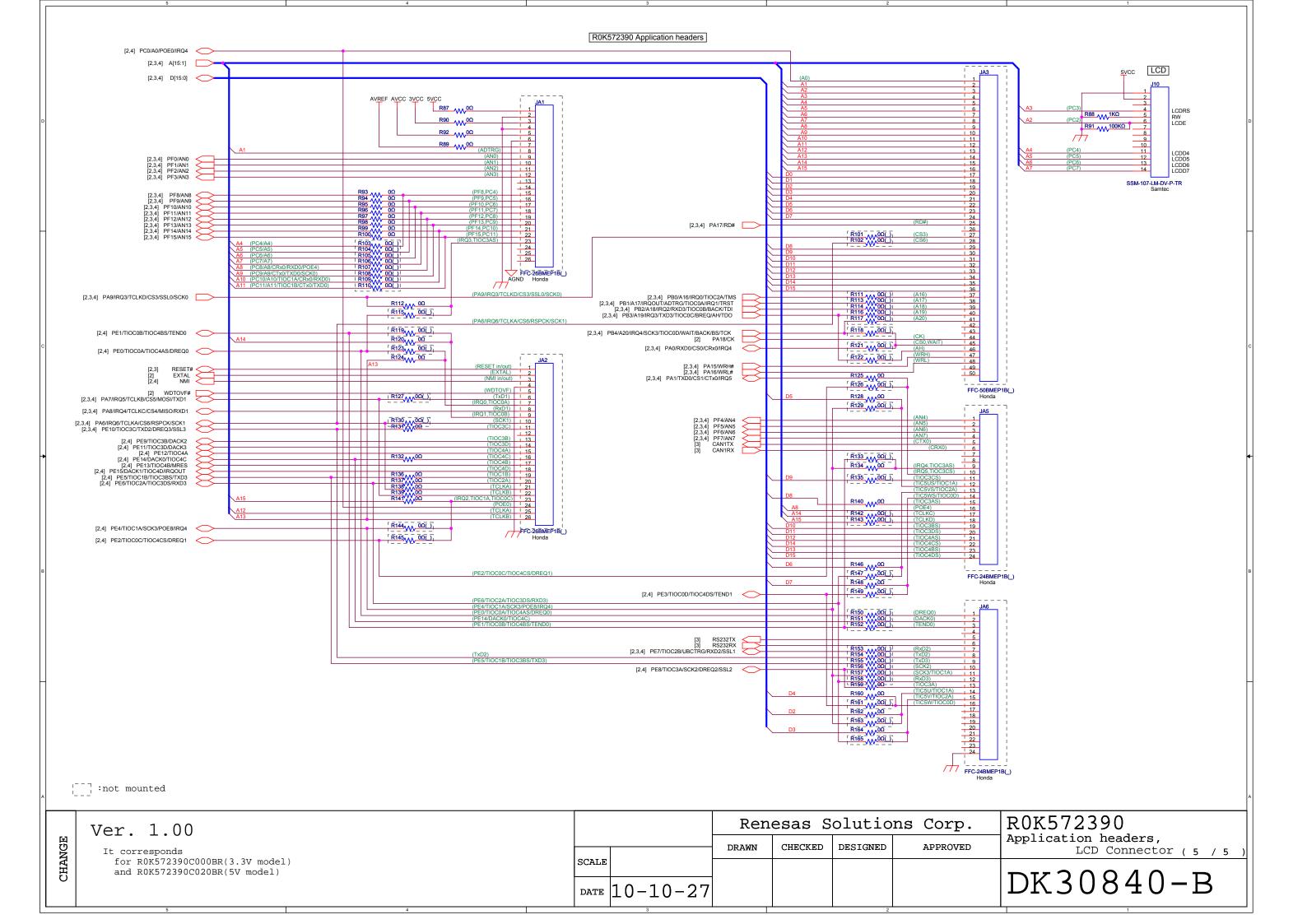

### 2.7 LCD インタフェース

R0K572390では、14 ピンのキャラクタ LCD インタフェース用コネクタ(J10)を実装しています。 キャラクタ LCD の制御にはSH7239の PC2~PC7 を使用しますが、これらの端子はボード上の SRAM(未実 装)へのアドレスとしても使用されています。またアプリケーションヘッダ(JA1、JA3)にも接続されており、 キャラクタ LCD と SRAM およびアプリケーションヘッダ側の各信号を重複して使用することはできません。 図 2.7にキャラクタLCDインタフェースブロック図を示します。

図2.7 キャラクタ LCD インタフェースブロック図

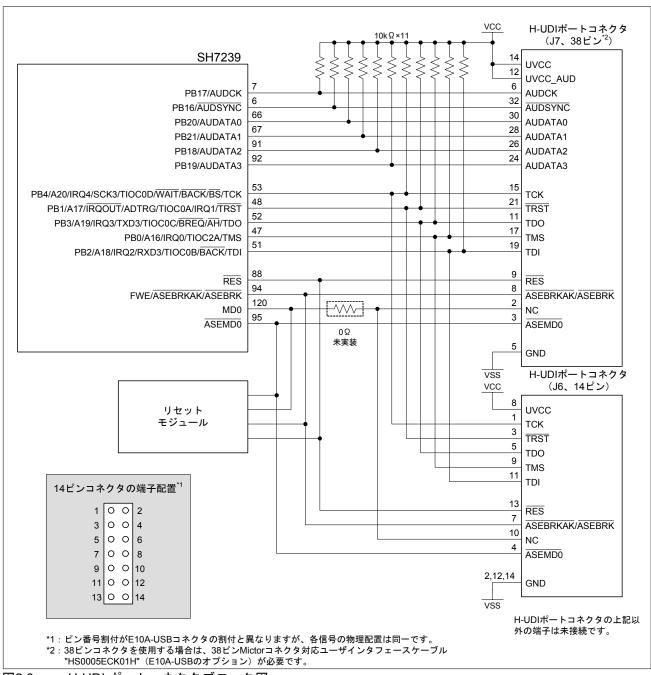

### 2.8 H-UDI インタフェース

R0K572390には、エミュレータ接続用の H-UDI ポートコネクタ(J6、J7)を実装しており、E10A-USB エミュレータと接続することができます。

SH7239の FWE/ASEBRKAK/ASEBRK端子は、リセットモジュールで、リセットスイッチとユーザスイッチ SW1 (NMI) を用いた FWE 信号論理生成、およびASEMD0信号を用いた FWE 信号とASEBRKAK/ASEBRK信号機能の切り替えが行われます。

R0K572390では、H-UDI 関連信号のうち JTAG 関連信号(TCK、 $\overline{\text{TRST}}$ 、TMS、TDO、TDI)は、ブートモード時を除き他の機能としては使用できません。

図 2.8にH-UDIポートコネクタブロック図を示します。

図2.8 H-UDIポートコネクタブロック図

### 2.9 スイッチ、ジャンパ

R0K572390では、リセット生成、NMI および IRQ 割り込み入力、ADTRG入力のためプッシュスイッチと動作モード設定用のディップスイッチを実装しています。

プッシュスイッチのうちリセットスイッチとユーザスイッチSW1 (NMI) は、SH7239のプログラミングモード関連設定にも使用します。リセットスイッチ回路とモード設定用ディップスイッチは 2.13 リセットモジュールで説明しています。そちらを参照してください。

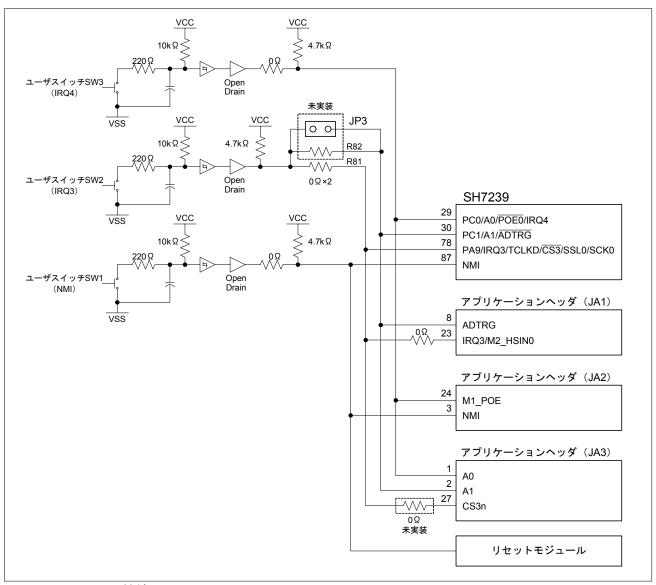

ユーザスイッチ SW2(IRQ3)は $\overline{ADTRG}$ 入力としても使用できるよう  $0\Omega$ 抵抗 R82(未実装)およびジャンパ(JP3、未実装)を経由し PC1/A1/ $\overline{ADTRG}$ 端子に接続されています。 $\overline{ADTRG}$ 入力として使用する場合は R82を取り付けてください。R82を取り付けた状態で PC1/A1/ $\overline{ADTRG}$ を出力に設定しないように注意してください。またR0K572390には電源選択、RCAN 信号接続用のジャンパがあります。これらのジャンパについては、第3章機能仕様で説明していますので、そちらを参照してください。

図 2.9に割り込み入力関連のスイッチ接続図を示します。

図2.9 スイッチ接続図

### 2.10 LED、ポテンショメータ

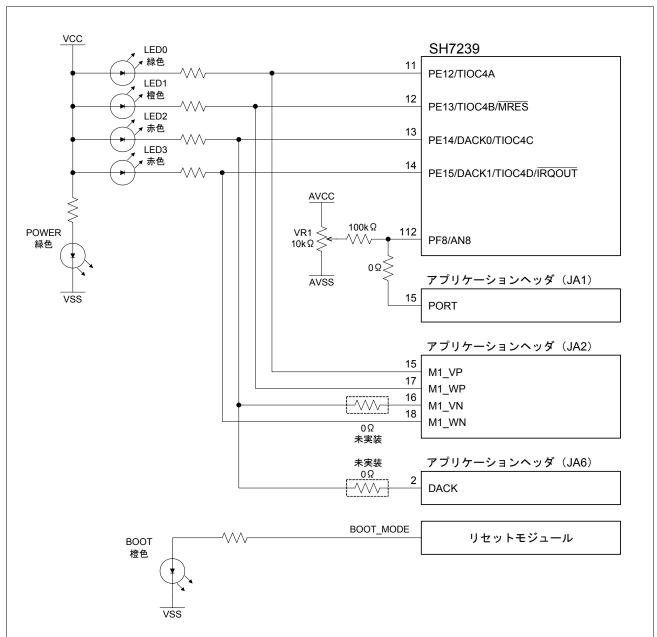

R0K572390は、電源用 LED (POWER)、ブートモード用 LED (BOOT) およびユーザ用 LED4 個 (LED0~LED3) を実装しています。POWER は電源 ON を示し、BOOT はブートモード (FWE="H") であることを示します。ユーザ用 LED はSH7239の PE12~PE15 で制御します。

またR0K572390はポテンショメータを搭載しており、A/D 変換器の AN8 に接続されています。 図 2.10にLEDおよびポテンショメータの接続図を示します。

図2.10 LED およびポテンショメータ

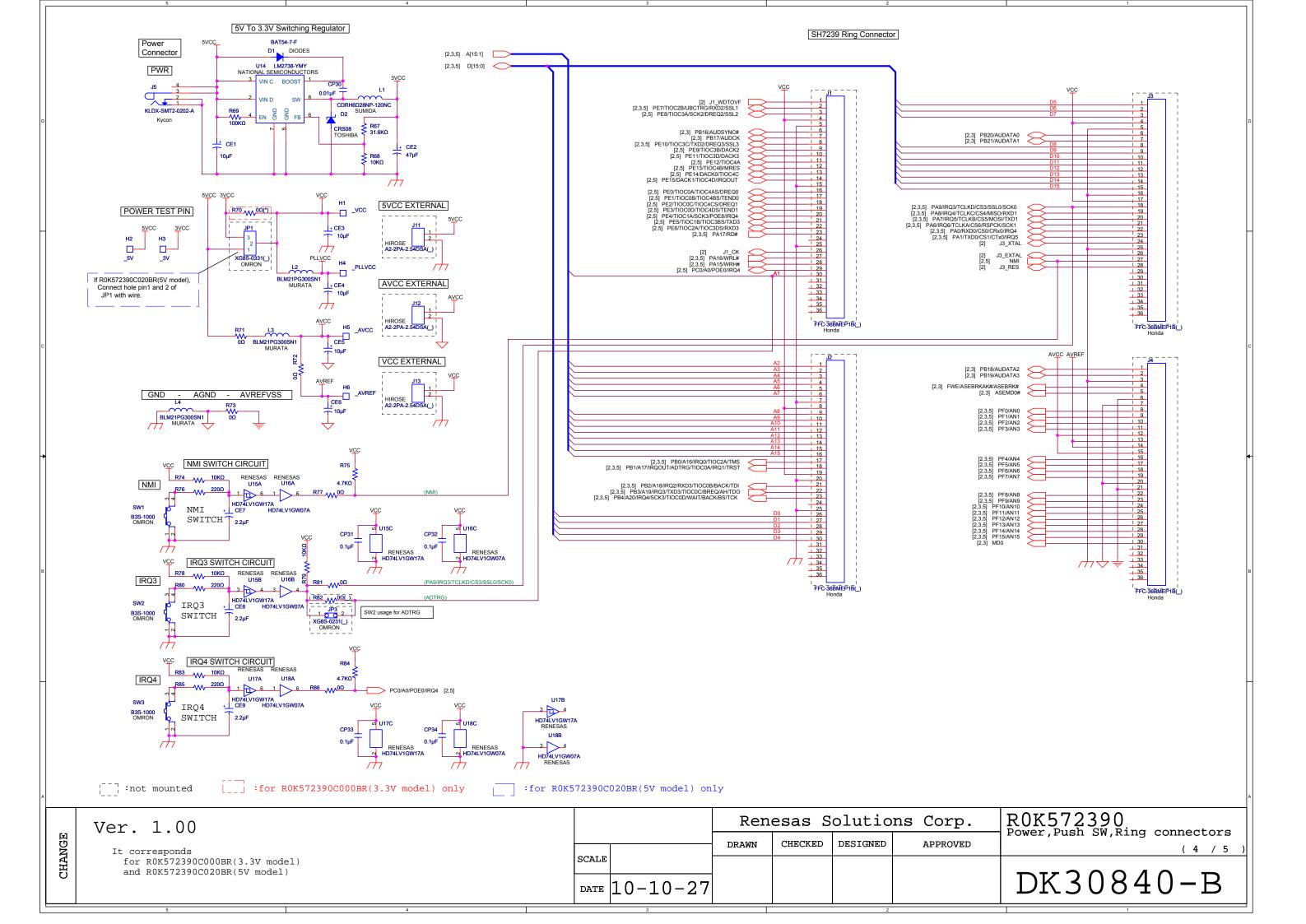

### 2.11 電源モジュール

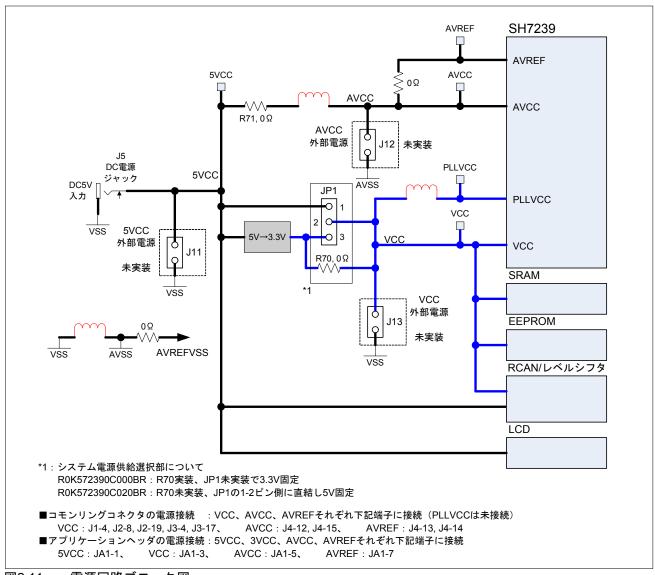

R0K572390では、5V電源をボードに入力し、レギュレータを用いて 3.3V の電圧を生成しています。出力電圧可変タイプのレギュレータを使用しているため、抵抗値を変更することにより任意の電圧値を生成することが可能です。

電源選択ジャンパJP1 は出荷時未実装であり、SH7239A を搭載したR0K572390C000BR では、VCC は 3.3V に固定されます。またSH7239B を搭載したR0K572390C020BR では、VCC は 5V に固定されます。

DC 安定化電源から外部電源供給コネクタ(J11)経由で 5V 電源を供給することも可能です。またSH7239のシステム電源(VCC)、アナログ電源(AVCC)も個別に外部電源から供給することができます。このときシステム電源は外部電源供給コネクタ(J13)経由、アナログ電源は外部電源供給コネクタ(J12)経由で供給します。アナログ電源を個別に供給する場合は、5V 電源とアナログ電源をつないでいる  $0\Omega$ 抵抗 R71 を取り外してください。外部電源供給コネクタ J11~J13 は出荷時未実装です。

図 2.11に、R0K572390の電源回路ブロック図を示します。

注意: R0K572390を動作させる場合は、必ず DC 電源ジャック (J5) または各外部電源供給コネクタ (J11~J13) から電源を供給してください。

図2.11 電源回路ブロック図

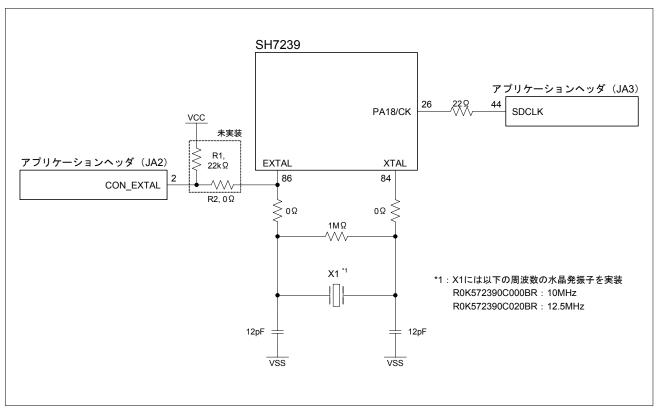

### 2.12 クロックモジュール

R0K572390では、搭載するマイコンに応じてSH7239の XTAL と EXTAL 端子に 10MHz または 12.5MHz の水 晶発振子を接続しています。

● R0K572390C000BR: 10MHzの水晶発振子を接続● R0K572390C020BR: 12.5MHzの水晶発振子を接続

EXTAL 端子にアプリケーションヘッダ(JA2)からクロックを入力することも可能です。この場合、X1の水晶発振子を取り外し、出荷時未実装の $0\Omega$ 抵抗 R2を取り付けてください。また、必要に応じてプルアップ用抵抗 R1も取り付けてください。

図 2.12に、R0K572390のクロックモジュール図を示します。

図2.12 クロックモジュール図

### 2.13 リセットモジュール

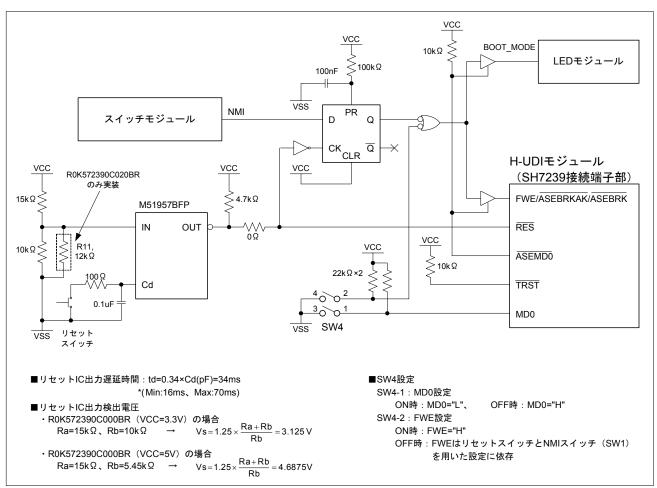

R0K572390のリセットモジュールでは、パワーオンリセット、リセットスイッチによるRES信号を生成しています。また、モード設定用ディップスイッチ(SW4)、リセットスイッチ、ユーザスイッチ SW1(NMI)とフリップフロップを用いたSH7239のブートモード制御(FWE 信号制御)、およびASEMD0信号を用いた FWE/ASEBRKAK/ASEBRK信号機能の制御も行っています。

ブートモード制御方法および FWE/ASEBRKAK/ASEBRK信号機能制御の詳細については第3章 操作仕様の 3.2.2 項を参照してください。

図 2.13に、R0K572390のリセットモジュール図を示します。

図2.13 リセットモジュール図

## 3. 操作仕様

#### 3.1 コネクタ概略

図 3.1にR0K572390コネクタ配置図を示します。

図3.1 R0K572390コネクタ配置図

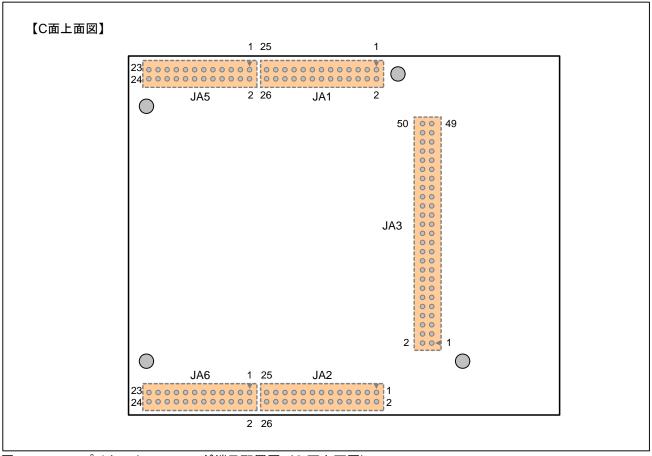

## 3.1.1 アプリケーションヘッダ (JA1、JA2、JA3、JA5、JA6)

R0K572390には、SH7239の入出力端子を接続したアプリケーションヘッダ実装用のスルーホール (JA1、JA2、JA3、JA5、JA6) を設けています。スルーホールに標準 MIL コネクタを実装して、拡張基板等と接続して使用することができます。

図 3.2にアプリケーションヘッダ端子配置図(C面上面図)を示します。

図3.2 アプリケーションヘッダ端子配置図(C面上面図)

表 3.1にアプリケーションヘッダ (JA1) 端子一覧を示します。

表3.1 アプリケーションヘッダ (JA1) 端子一覧

| Pin No. | 接続信号名                            | 使用機能   |

|---------|----------------------------------|--------|

| 1       | 5VCC <sup>*1</sup>               | 5VCC   |

| 2       | GND                              | GND    |

| 3       | 3VCC <sup>*1</sup>               | 3VCC   |

| 4       | GND                              | GND    |

| 5       | AVCC *1                          | AVCC   |

| 6       | AGND                             | AGND   |

| 7       | AVREF *1                         | AVREF  |

| 8       | PC1/A1/ADTRG                     | ADTRG  |

| 9       | PF0/AN0                          | AN0    |

| 10      | PF1/AN1                          | AN1    |

| 11      | PF2/AN2                          | AN2    |

| 12      | PF3/AN3                          | AN3    |

| 13      | NC                               | -      |

| 14      | NC                               | -      |

| 45      | PF8/AN8, *1                      | PF8,   |

| 15      | PC4/A4 *2                        | PC4    |

| 16      | PF9/AN9, <sup>*1</sup>           | PF9,   |

|         | PC5/A5 *2                        | PC5    |

| 17      | PF10/AN10, *1                    | PF10,  |

| 17      | PC6/A6 *2                        | PC6    |

| 18      | PF11/AN11, *1                    | PF11,  |

|         | PC7/A7 *2                        | PC7    |

| 19      | PF12/AN12, *1                    | PF12,  |

| 13      | PC8/A8/CRx0/RXD0/POE4 *2         | PC8    |

| 20      | PF13/AN13, *1                    | PF13,  |

|         | PC9/A9/CTx0/TXD0/SCK0 *2         | PC9    |

| 21      | PF14/AN14, *1                    | PF14,  |

|         | PC10/A10/TIOC1A/CRx0/RXD0 *2     | PC10   |

| 22      | PF15/AN15, *1                    | PF15,  |

|         | PC11/A11/TIOC1B/CTx0/TXD0 *2     | PC11   |

| 23      | PA9/IRQ3/TCLKD/CS3/SSL0/SCK0, *1 | IRQ3,  |

|         | PE0/TIOC0A/TIOC4AS/DREQ0 *2      | TIOC0A |

| 24      | NC                               | -      |

| 25      | NC                               | -      |

| 26      | NC                               | -      |

【注】 \*1:0 $\Omega$ 抵抗(出荷時実装)を経由して接続されています。

\*2:0Ω抵抗(出荷時未実装)を経由して接続されています。

表 3.2にアプリケーションヘッダ (JA2) 端子一覧を示します。

表3.2 アプリケーションヘッダ (JA2) 端子一覧

| Pin No. | 接続信号名                            | 使用機能    |

|---------|----------------------------------|---------|

| 1       | RESET                            |         |

| 2       | EXTAL *2                         | EXTAL   |

| 3       | NMI                              | NMI     |

| 4       | GND                              | GND     |

| 5       | WDTOVF *1                        | WDTOVF  |

| 6       | PA7/IRQ5/TCLKB/CS5/MOSI/TXD1 *2  | TXD1    |

| 7       | PC13/A13/IRQ0/TCLKB, *1          | IRQ0,   |

| ,       | PE0/TIOC0A/TIOC4AS/DREQ0 *2      | TIOC0A  |

| 8       | PA8/IRQ4/TCLKC/CS4/MISO/RXD1     | RXD1    |

| 9       | PC14/A14/IRQ1/TCLKC, *1          | IRQ1,   |

| 9       | PE1/TIOC0B/TIOC4BS/TEND0 *2      | TIOC0B  |

| 10      | PA6/IRQ6/TCLKA/CS6/RSPCK/SCK1 *2 | SCK1    |

| 11      | PE10/TIOC3C/TXD2/DREQ3/SSL3 *1   | TIOC3C  |

| 12      | NC                               | -       |

| 13      | PE9/TIOC3B/DACK2                 | TIOC3B  |

| 14      | PE11/TIOC3D/DACK3                | TIOC3D  |

| 15      | PE12/TIOC4A                      | TIOC4A  |

| 16      | PE14/DACK0/TIOC4C *1             | TIOC4C  |

| 17      | PE13/TIOC4B/MRES                 | TIOC4B  |

| 18      | PE15/DACK1/TIOC4D/IRQOUT         | TIOC4D  |

| 19      | PE5/TIOC1B/TIOC3BS/TXD3 *1       | TIOC1B  |

| 20      | PE6/TIOC2A/TIOC3DS/RXD3 *1       | TIOC2A  |

| 21      | PA6/IRQ6/TCLKA/CS6/RSPCK/SCK1 *1 | TCLKA   |

| 22      | PA7/IRQ5/TCLKB/CS5/MOSI/TXD1 *1  | TCLKB   |

|         | PC15/A15/IRQ2/TCLKD, *1          | IRQ2,   |

| 23      | PE4/TIOC1A/SCK3/POE8/IRQ4, *2    | TIOC1A, |

|         | PE2/TIOC0C/TIOC4CS/DREQ1 *2      | TIOC0C  |

| 24      | PC0/A0/POE0/IRQ4                 | POE0    |

| 25      | PC12/A12/TCLKA                   | TCLKA   |

| 26      | PC13/A13/IRQ0/TCLKB              | TCLKB   |

【注】 \*1:0 $\Omega$ 抵抗(出荷時実装)を経由して接続されています。 \*2:0 $\Omega$ 抵抗(出荷時未実装)を経由して接続されています。

表 3.3および表 3.4にアプリケーションヘッダ (JA3) 端子一覧を示します。

表3.3 アプリケーションヘッダ (JA3) 端子一覧 (1)

| Pin No. | 接続信号名                            | 使用機能 |

|---------|----------------------------------|------|

| 1       | PC0/A0/POE0/IRQ4                 | A0   |

| 2       | PC1/A1/ADTRG                     | A1   |

| 3       | PC2/A2                           | A2   |

| 4       | PC3/A3                           | A3   |

| 5       | PC4/A4                           | A4   |

| 6       | PC5/A5                           | A5   |

| 7       | PC6/A6                           | A6   |

| 8       | PC7/A7                           | A7   |

| 9       | PC8/A8/CRx0/RXD0/POE4            | A8   |

| 10      | PC9/A9/CTx0/TXD0/SCK0            | A9   |

| 11      | PC10/A10/TIOC1A/CRx0/RXD0        | A10  |

| 12      | PC11/A11/TIOC1B/CTx0/TXD0        | A11  |

| 13      | PC12/A12/TCLKA                   | A12  |

| 14      | PC13/A13/IRQ0/TCLKB              | A13  |

| 15      | PC14/A14/IRQ1/TCLKC              | A14  |

| 16      | PC15/A15/IRQ2/TCLKD              | A15  |

| 17      | PD0/D0                           | D0   |

| 18      | PD1/D1                           | D1   |

| 19      | PD2/D2/TIC5U/RXD2                | D2   |

| 20      | PD3/D3/TIC5V/TXD2                | D3   |

| 21      | PD4/D4/TIC5W/SCK2                | D4   |

| 22      | PD5/D5/TIC5US                    | D5   |

| 23      | PD6/D6/TIC5VS                    | D6   |

| 24      | PD7/D7/TIC5WS                    | D7   |

| 25      | PA17/RD                          | RD   |

| 26      | NC                               | -    |

| 27      | PA9/IRQ3/TCLKD/CS3/SSL0/SCK0 *1  | CS3  |

| 28      | PA6/IRQ6/TCLKA/CS6/RSPCK/SCK1 *1 | CS6  |

| 29      | PD8/D8/TIOC3AS/AUDATA0           | D8   |

| 30      | PD9/D9/TIOC3CS/AUDATA1           | D9   |

| 31      | PD10/D10/TIOC3BS/AUDATA2         | D10  |

| 32      | PD11/D11/TIOC3DS/AUDATA3         | D11  |

| 33      | PD12/D12/TIOC4AS/AUDSYNC         | D12  |

| 34      | PD13/D13/TIOC4BS/AUDCK           | D13  |

| 35      | PD14/D14/TIOC4CS                 | D14  |

| 36      | PD15/D15/TIOC4DS                 | D15  |

【注】 \*1:0Ω抵抗(出荷時未実装)を経由して接続されています。

表3.4 アプリケーションヘッダ (JA3) 端子一覧 (2)

| Pin No. | 接続信号名                                        | 使用機能 |

|---------|----------------------------------------------|------|

| 37      | PB0/A16/IRQ0/TIOC2A/TMS *3                   | A16  |

| 38      | PB1/A17/IRQOUT/ADTRG/TIOC0A/IRQ1/TRST *3     | A17  |

| 39      | PB2/A18/IRQ2/RXD3/TIOC0B/BACK/TDI *3         | A18  |

| 40      | PB3/A19/IRQ3/TXD3/TIOC0C/BREQ/AH/TDO *3      | A19  |

| 41      | PB4/A20/IRQ4/SCK3/TIOC0D/WAIT/BACK/BS/TCK *3 | A20  |

| 42      | NC                                           | -    |

| 43      | NC                                           | -    |

| 44      | PA18/CK                                      | СК   |

| 45      | PA0/RXD0/CS0/CRx0/IRQ4, *2                   | CS0, |

| 45      | PB4/A20/IRQ4/SCK3/TIOC0D/WAIT/BACK/BS/TCK *3 | WAIT |

| 46      | PB3/A19/IRQ3/TXD3/TIOC0C/BREQ/AH/TDO *3      | ĀH   |

| 47      | PA15/WRH                                     | WRH  |

| 48      | PA16/WRL                                     | WRL  |

| 49      | NC                                           | -    |

| 50      | NC                                           | -    |

【注】\*1:0Ω抵抗(出荷時実装)を経由して接続されています。

\*2:0Ω抵抗(出荷時未実装)を経由して接続されています。

\*3:0 $\Omega$ 抵抗(出荷時未実装)を経由して接続されており、H-UDIの JTAG 信号とマルチプレクスされているため、エミュレータ接続時は使用できません。

表 3.5にアプリケーションヘッダ (JA5) 端子一覧を示します。

表3.5 アプリケーションヘッダ (JA5) 端子一覧

| Pin No. | 接続信号名                         | 使用機能         |

|---------|-------------------------------|--------------|

| 1       | PF4/AN4                       | AN4          |

| 2       | PF5/AN5                       | AN5          |

| 3       | PF6/AN6                       | AN6          |

| 4       | PF7/AN7                       | AN7          |

| 5       | PA1/TXD0/CS1/CTx0/IRQ5 *2     | CTx0         |

| 6       | PA0/RXD0/CS0/CRx0/IRQ4 *2     | CRx0         |

| 7       | NC                            | -            |

| 8       | NC                            | -            |

| 9       | PE4/TIOC1A/SCK3/POE8/IRQ4, *1 | IRQ4, TIOC1A |

|         | PE1/TIOC0B/TIOC4BS/TEND0 *2   | TIOC0B       |

| 10      | PA1/TXD0/CS1/CTx0/IRQ5, *1    | IRQ5,        |

|         | PE2/TIOC0C/TIOC4CS/DREQ1 *2   | TIOC0O       |

| 11      | PD9/D9/TIOC3CS/AUDATA1 *2     | TIOC3CS      |

| 12      | PD5/D5/TIC5US, *1             | TIC5US,      |

|         | PE4/TIOC1A/SCK3/POE8/IRQ4, *2 | TIOC1A       |

| 13      | PD6/D6/TIC5VS, *1             | TIC5VS,      |

|         | PE6/TIOC2A/TIOC3DS/RXD3 *2    | TIOC2A       |

| 14      | PD7/D7/TIC5WS, *1             | TIC5WS,      |

|         | PE3/TIOC0D/TIOC4DS/TEND1 *2   | TIOC0D       |

| 15      | PD8/D8/TIOC3AS/AUDATA0 *1     | TIOC3AS      |

| 16      | PC8/A8/CRx0/RXD0/POE4         | POE4         |

| 17      | PC14/A14/IRQ1/TCLKC *2        | TCLKC        |

| 18      | PC15/A15/IRQ2/TCLKD *2        | TCLKD        |

| 19      | PD10/D10/TIOC3BS/AUDATA2      | TIOC3BS      |

| 20      | PD11/D11/TIOC3DS/AUDATA3      | TIOC3DS      |

| 21      | PD12/D12/TIOC4AS/AUDSYNC      | TIOC4AS      |

| 22      | PD14/D14/TIOC4CS              | TIOC4CS      |

| 23      | PD13/D13/TIOC4BS/AUDCK        | TIOC4BS      |

| 24      | PD15/D15/TIOC4DS              | TIOC4DS      |

【注】\*1:0Ω抵抗(出荷時実装)を経由して接続されています。

\*2:0Ω抵抗(出荷時未実装)を経由して接続されています。

表 3.6にアプリケーションヘッダ (JA6) 端子一覧を示します。

表3.6 アプリケーションヘッダ (JA6) 端子一覧

| Pin No. | 接続信号名                          | 使用機能    |

|---------|--------------------------------|---------|

| 1       | PE0/TIOC0A/TIOC4AS/DREQ0 *2    | DREQ0   |

| 2       | PE14/DACK0/TIOC4C *2           | DACK0   |

| 3       | PE1/TIOC0B/TIOC4BS/TEND0 *2    | TEND0   |

| 4       | NC                             | -       |

| 5       | -                              | RS232TX |

| 6       | -                              | RS232RX |

| 7       | PE7/TIOC2B/UBCTRG/RXD2/SSL1 *2 | RXD2    |

| 8       | PE10/TIOC3C/TXD2/DREQ3/SSL3 *2 | TXD2    |

| 9       | PE5/TIOC1B/TIOC3BS/TXD3 *2     | TXD3    |

| 10      | PE8/TIOC3A/SCK2/DREQ2/SSL2 *2  | SCK2    |

| 11      | PE4/TIOC1A/SCK3/POE8/IRQ4 *2   | SCK3    |

| 12      | PE6/TIOC2A/TIOC3DS/RXD3 *2     | RXD3    |

| 13      | PE8/TIOC3A/SCK2/DREQ2/SSL2 *1  | TIOC3A  |

| 14      | PD2/D2/TIC5U/RXD2, *1          | TIC5U,  |

|         | PE4/TIOC1A/SCK3/POE8/IRQ4 *2   | TIOC1A  |

| 15      | PD3/D3/TIC5V/TXD2, *1          | TIC5V,  |

|         | PE6/TIOC2A/TIOC3DS/RXD3 *2     | TIOC2A  |

| 16      | PD4/D4/TIC5W/SCK2, *1          | TIC5W,  |

|         | PE3/TIOC0D/TIOC4DS/TEND1 *2    | TIOC0D  |

| 17      | NC                             | -       |

| 18      | NC                             | -       |

| 19      | NC                             | -       |

| 20      | NC                             | -       |

| 21      | NC                             | -       |

| 22      | NC                             | -       |

| 23      | NC                             | -       |

| 24      | -                              | VSS     |

【注】 \*1:0 $\Omega$ 抵抗(出荷時実装)を経由して接続されています。

\*2:0Ω抵抗(出荷時未実装)を経由して接続されています。

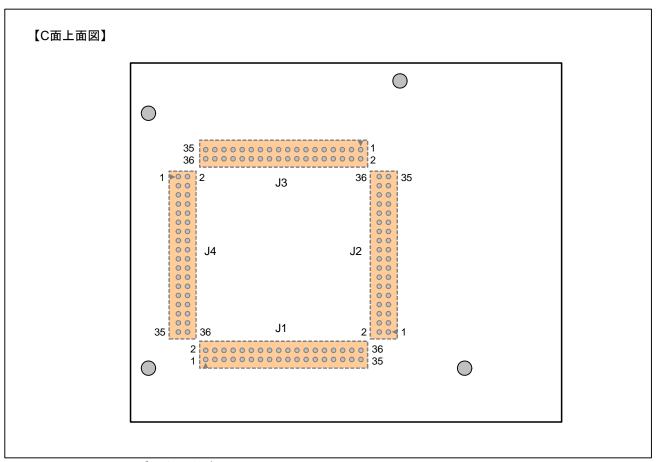

## 3.1.2 コモンリングコネクタ (J1、J2、J3、J4)

R0K572390には、SH7239の全信号を接続したコモンリングコネクタ実装用のスルーホール (J1、J2、J3、J4) を設けています。スルーホールには標準 MIL コネクタを接続することができ、SH7239各信号のモニタリング 等に利用できます。

図 3.3にコモンリングコネクタ端子配置図を、表 3.7~表 3.10に各コネクタの端子一覧を示します。

図3.3 コモンリングコネクタ端子配置図(C面上面図)

## 表3.7 コモンリングコネクタ (J1) 端子一覧

| Pin No. | 信号名                        | Pin No. | 信号名                         |

|---------|----------------------------|---------|-----------------------------|

| 1       | WDTOVF                     | 2       | PE7/TIOC2B/UBCTRG/RXD2/SSL1 |

| 3       | PE8/TIOC3A/SCK2/DREQ2/SSL2 | 4       | VCC                         |

| 5       | VSS                        | 6       | PB16/AUDSYNC                |

| 7       | PB17/AUDCK                 | 8       | PE10/TIOC3C/TXD2/DREQ3/SSL3 |

| 9       | PE9/TIOC3B/DACK2           | 10      | PE11/TIOC3D/DACK3           |

| 11      | PE12/TIOC4A                | 12      | PE13/TIOC4B/MRES            |

| 13      | PE14/DACK0/TIOC4C          | 14      | PE15/DACK1/TIOC4D/IRQOUT    |

| 15      | VSS                        | 16      | PE0/TIOC0A/TIOC4AS/DREQ0    |

| 17      | PE1/TIOC0B/TIOC4BS/TEND0   | 18      | PE2/TIOC0C/TIOC4CS/DREQ1    |

| 19      | PE3/TIOC0D/TIOC4DS/TEND1   | 20      | PE4/TIOC1A/SCK3/POE8/IRQ4   |

| 21      | PE5/TIOC1B/TIOC3BS/TXD3    | 22      | PE6/TIOC2A/TIOC3DS/RXD3     |

| 23      | PA17/RD                    | 24      | NC                          |

| 25      | VSS                        | 26      | PA18/CK                     |

| 27      | PA16/WRL                   | 28      | PA15/WRH                    |

| 29      | PC0/A0/POE0/IRQ4           | 30      | PC1/A1/ADTRG                |

| 31      | NC                         | 32      | NC                          |

| 33      | NC                         | 34      | NC                          |

| 35      | NC                         | 36      | NC                          |

## 表3.8 コモンリングコネクタ (J2) 端子一覧

| Pin No. | 信号名                                       | Pin No. | 信号名                                   |

|---------|-------------------------------------------|---------|---------------------------------------|

| 1       | PC2/A2                                    | 2       | PC3/A3                                |

| 3       | PC4/A4                                    | 4       | PC5/A5                                |

| 5       | PC6/A6                                    | 6       | PC7/A7                                |

| 7       | VSS                                       | 8       | VCC                                   |

| 9       | PC8/A8/CRx0/RXD0/POE4                     | 10      | PC9/A9/CTx0/TXD0/SCK0                 |

| 11      | PC10/A10/TIOC1A/CRx0/RXD0                 | 12      | PC11/A11/TIOC1B/CTx0/TXD0             |

| 13      | PC12/A12/TCLKA                            | 14      | PC13/A13/IRQ0/TCLKB                   |

| 15      | PC14/A14/IRQ1/TCLKC                       | 16      | PC15/A15/IRQ2/TCLKD                   |

| 17      | PB0/A16/IRQ0/TIOC2A/TMS                   | 18      | PB1/A17/IRQOUT/ADTRG/TIOC0A/IRQ1/TRST |

| 19      | VCC                                       | 20      | VSS                                   |

| 21      | PB2/A18/IRQ2/RXD3/TIOC0B/BACK/TDI         | 22      | PB3/A19/IRQ3/TXD3/TIOC0C/BREQ/AH/TDO  |

| 23      | PB4/A20/IRQ4/SCK3/TIOC0D/WAIT/BACK/BS/TCK | 24      | NC                                    |

| 25      | VSS                                       | 26      | PD0/D0                                |

| 27      | PD1/D1                                    | 28      | PD2/D2/TIC5U/RXD2                     |

| 29      | PD3/D3/TIC5V/TXD2                         | 30      | PD4/D4/TIC5W/SCK2                     |

| 31      | NC                                        | 32      | NC                                    |

| 33      | NC                                        | 34      | NC                                    |

| 35      | NC                                        | 36      | NC                                    |

表3.9 コモンリングコネクタ (J3) 端子一覧

| Pin No. | 信号名                           | Pin No. | 信号名                          |

|---------|-------------------------------|---------|------------------------------|

| 1       | PD5/D5/TIC5US                 | 2       | PD6/D6/TIC5VS                |

| 3       | PD7/D7/TIC5WS                 | 4       | VCC                          |

| 5       | VSS                           | 6       | PB20/AUDATA0                 |

| 7       | PB21/AUDATA1                  | 8       | PD8/D8/TIOC3AS/AUDATA0       |

| 9       | PD9/D9/TIOC3CS/AUDATA1        | 10      | PD10/D10/TIOC3BS/AUDATA2     |

| 11      | PD11/D11/TIOC3DS/AUDATA3      | 12      | PD12/D12/TIOC4AS/AUDSYNC     |

| 13      | PD13/D13/TIOC4BS/AUDCK        | 14      | PD14/D14/TIOC4CS             |

| 15      | PD15/D15/TIOC4DS              | 16      | VSS                          |

| 17      | VCC                           | 18      | PA9/IRQ3/TCLKD/CS3/SSL0/SCK0 |

| 19      | PA8/IRQ4/TCLKC/CS4/MISO/RXD1  | 20      | PA7/IRQ5/TCLKB/CS5/MOSI/TXD1 |

| 21      | PA6/IRQ6/TCLKA/CS6/RSPCK/SCK1 | 22      | PA0/RXD0/CS0/CRx0/IRQ4       |

| 23      | PA1/TXD0/CS1/CTx0/IRQ5        | 24      | XTAL *1                      |

| 25      | VSS                           | 26      | EXTAL*1                      |

| 27      | NMI                           | 28      | RES                          |

| 29      | NC                            | 30      | NC                           |

| 31      | NC                            | 32      | NC                           |

| 33      | NC                            | 34      | NC                           |

| 35      | NC                            | 36      | NC                           |

【注】\*1:0Ω抵抗(出荷時未実装)を経由して接続されています。

表3.10 コモンリングコネクタ (J4) 端子一覧

| Pin No. | 信号名          | Pin No. | 信号名                 |

|---------|--------------|---------|---------------------|

| 1       | PB18/AUDATA2 | 2       | PB19/AUDATA3        |