# **RAJ306000** Series

## User's Manual: Hardware

General purpose Motor control IC

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

Renesas Electronics www.renesas.com

Rev.2.02 Mar. 2021

### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other disputes involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawing, chart, program, algorithm, application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics products.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (space and undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. When using the Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat radiation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions or failure or accident arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please ensure to implement safety measures to guard them against the possibility of bodily injury, injury or damage caused by fire, and social damage in the event of failure or malfunction of Renesas Electronics products, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures by your own responsibility as warranty for your products/system. Because the evaluation of microcomputer software alone is very difficult and not practical, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please investigate applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive carefully and sufficiently and use Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall not use Renesas Electronics products or technologies for (1) any purpose relating to the development, design, manufacture, use, stockpiling, etc., of weapons of mass destruction, such as nuclear weapons, chemical weapons, or biological weapons, or missiles (including unmanned aerial vehicles (UAVs)) for delivering such weapons, (2) any purpose relating to the development, design, manufacture, or use of conventional weapons, or (3) any other purpose of disturbing international peace and security, and you shall not sell, export, lease, transfer, or release Renesas Electronics products or technologies to any third party whether directly or indirectly with knowledge or reason to know that the third party or any other party will engage in the activities described above. When exporting, selling, transferring, etc., Renesas Electronics products or technologies, you shall comply with any applicable export control laws and regulations promulgated and administered by the governments of the countries asserting jurisdiction over the parties or transactions.

- 10. Please acknowledge and agree that you shall bear all the losses and damages which are incurred from the misuse or violation of the terms and conditions described in this document, including this notice, and hold Renesas Electronics harmless, if such misuse or violation results from your resale or making Renesas Electronics products available any third party.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

### General Precautions in the Handling of Microprocessing Unit and Microcontroller Unit Products

The following usage notes are applicable to all Microprocessing unit and Microcontroller unit products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

### 1. Handling of Unused Pins

Handle unused pins in accordance with the directions given under Handling of Unused Pins in the manual.

The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

Prohibition of Access to Reserved Addresses Access to reserved addresses is prohibited. The reserved addresses are provided for the possible future expansion of functions. Do not access

these addresses; the correct operation of LSI is not guaranteed if they are accessed.

4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

5. Differences between Products

Before changing from one product to another, i.e. to a product with a different part number, confirm that the change will not lead to problems.

The characteristics of Microprocessing unit or Microcontroller unit products in the same group but having a different part number may differ in terms of the internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a system-evaluation test for the given product.

### How to Use This Manual

- Readers This manual is intended for user engineers who wish to understand the functions of the RL78/G1F and design and develop application systems and programs for these devices. The target products are as follows.

- 64-pin: RAJ3060xx (xx = 01,10)

- Purpose This manual is intended to give users an understanding of the functions described in the Organization below.

- Organization The RAJ306000 series manual is separated into three parts: this manual, RL78/G1F hardware Manual and the software edition. This manual explains the function unique to RAJ306000 series. For detailed usage of the RL78/G1F microcomputer, refer to the RL78 / G1F User's Manual Hardware(R01UH0516E) and "Technical Update" on RL78/G1F. (common to the RL78 family).

| RAJ306000 SeriesRL78/G1FUser's ManualUser's ManualHardwareHardware(This Manual) |                          | RL78 Family<br>User's Manual<br>Software |

|---------------------------------------------------------------------------------|--------------------------|------------------------------------------|

| About RAJ36000                                                                  | About RL78/G1F           | CPU functions                            |

| Pin functions                                                                   | Pin functions            | Instruction set                          |

| Internal block functions                                                        | Internal block functions | Explanation of each instruction          |

- Pre-Driver function

- How to use RL78/G1F

- Interrupts

- Other on-chip peripheral functions

- Electrical specifications

### How to Read This Manual

It is assumed that the readers of this manual have general knowledge of electrical engineering, logic circuits, and microcontrollers.

•To gain a general understanding of functions:

$\rightarrow$  Read this manual in the order of the **CONTENTS**. The mark "<R>" shows major revised points. The revised points can be easily searched by copying an "<R>" in the PDF file and specifying it in the "Find what:" field.

- •How to interpret the register format:

- •To know details of the RL78/G1F Microcontroller instructions:

- → Refer to the separate document RL78 Family User's Manual Software(R01US0015E).

### Conventions

| Data significance: Higher digits | Higher digits on the left and lower digits on the right     |  |  |  |  |

|----------------------------------|-------------------------------------------------------------|--|--|--|--|

| Active low representations:      | $\overrightarrow{xxx}$ (overscore over pin and signal name) |  |  |  |  |

| Note:                            | Footnote for item marked with Note in the text              |  |  |  |  |

| Caution:                         | Information requiring particular attention                  |  |  |  |  |

| Remark:                          | Supplementary information                                   |  |  |  |  |

| Numerical representations:       | Binary ····×××× or ××××B                                    |  |  |  |  |

|                                  | Decimal xxxx                                                |  |  |  |  |

|                                  | Hexadecimal xxxxHor 0xxxxx                                  |  |  |  |  |

### **Related Documents**

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

Documents Related to Devices

| Document Name                                                      | Document No. |

|--------------------------------------------------------------------|--------------|

| RAJ306000 Series User's Manual Hardware                            | This manual  |

| RL78/G1F User's Manual Hardware                                    | R01UH0516E   |

| RL78 Family User's Manual Software                                 | R01US0015E   |

| Data sheet RAJ306001, RAJ306010 (General-Purpose Motor Control IC) | R18DS0034E   |

### Documents Related to Flash Memory Programming (User's Manual)

|       | Document No.                                                 |            |  |  |  |

|-------|--------------------------------------------------------------|------------|--|--|--|

| PG-FF | PG-FP5 Flash Memory Programmer                               |            |  |  |  |

|       | RL78, 78K, V850, RX100, RX200, RX600 (Except RX64x), R8C, SH |            |  |  |  |

|       | Common                                                       |            |  |  |  |

|       | Setup Manual                                                 | R20UT0930E |  |  |  |

#### Caution The related documents listed above are subject to change without notice. Be sure to use the latest version

of each document when designing. Other Documents

| Document Name                        | Document No. |

|--------------------------------------|--------------|

| Renesas Microcontrollers RL78 Family | R01CP0003E   |

| Semiconductor Package Mount Manual   | R50ZZ0003E   |

| Semiconductor Reliability Handbook   | R51ZZ0001E   |

Caution The related documents listed above are subject to change without notice. Be sure to use the latest version of each document when designing.

All trademarks and registered trademarks are the property of their respective owners.

EEPROM is a trademark of Renesas Electronics Corporation.

SuperFlash is a registered trademark of Silicon Storage Technology, Inc. in several countries including the United States and Japan.

### CONTENTS

| CONTENTS                                                              | 1  |

|-----------------------------------------------------------------------|----|

| CHAPTER 1 Outline                                                     | 1  |

| 1.1 Features                                                          |    |

| 1.2 Pin Configuration (Top View)                                      |    |

| 1.3 Recommended circuit                                               |    |

| 1.3.1 Power supply                                                    | 6  |

| 1.3.2 Reset function                                                  | 7  |

| 1.3.3 Charge-pump                                                     |    |

| 1.4 Recommended drive waveform                                        | 9  |

| 1.5 How to select the external MOSFET                                 |    |

| CHAPTER 2 Pre-Driver                                                  | 11 |

| 2.1 Terminal configuration of Pre-Driver.                             |    |

| 2.1.1 The terminal connection of Pre-Driver                           |    |

| 2.1.2 Pre-Driver terminal table                                       |    |

| 2.2 System clock of Pre-Driver                                        |    |

| 2.3 Communication format                                              |    |

| 2.4 Pre-Driver register                                               |    |

| 2.4.1 Power Save Control Register (PS_ALL)                            |    |

| 2.4.2 Power Save Control Setting Register by function (PS)            |    |

| 2.4.3 Software Reset Register (SW_RESET)                              |    |

| 2.4.4 ADC Selector Register (ADC_SEL)                                 |    |

| 2.4.5 U/V/W Phase Motor Control Signal Select Register (SELSIG_U/V/W) |    |

| 2.4.6 Hall Signal Processing Setting Register (HALL_SIG)              |    |

| 2.4.7 ALARM Status Register1 (ALMSTS1)                                |    |

| 2.4.8 ALARM Operation Setting Register1 (ALMOPE1)                     |    |

| 2.4.9 ALARM Pin Output Setting Register1 (ALMOUT1)                    |    |

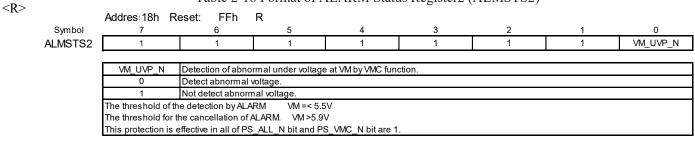

| 2.4.10 ALARM Status Register2 (ALMSTS2)                               |    |

| 2.4.11 Current Sense Setting Register2 (CS_SET2)                      |    |

| 2.4.12 ALARM Pin Output Setting Register2 (ALMOUT2)                   |    |

| 2.4.13 Error Detection Wait Time Setting Register (ERROR_WAIT)        |    |

| 2.4.14 Current Sense Setting Register1 (CS_SET1)                      |    |

| 2.4.15 Hall IC Threshold Adjustment Register (HAIC_TH)                |    |

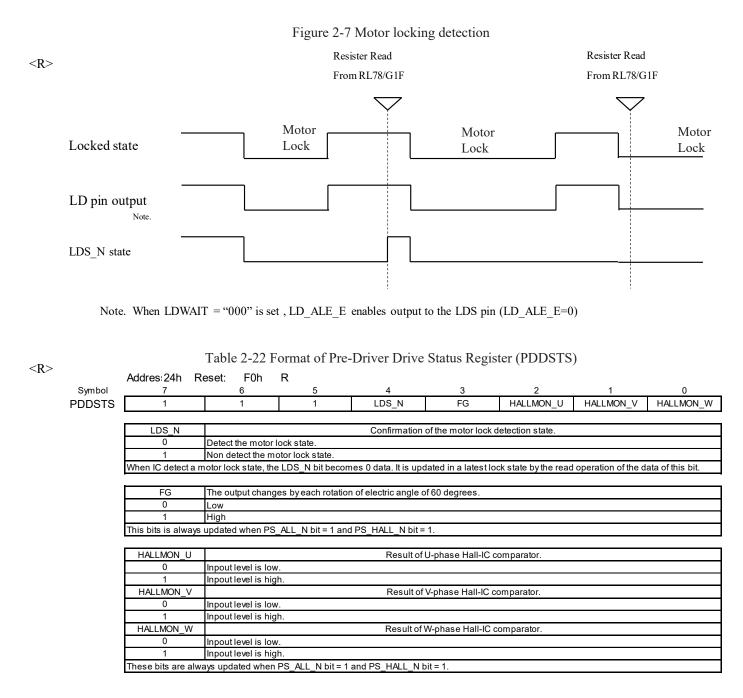

| 2.4.16 Pre-Driver Drive Status Register (PDDSTS)                       |    |

|------------------------------------------------------------------------|----|

| 2.4.17 LD Judgment Wait Time Register (LD_WAIT)                        |    |

| 2.4.18 Motor Drive Control Setting Register (DRIVE_SET)                |    |

| 2.4.19 High Side Output Current Capability Setting Register (IDRCNT_H) |    |

| 2.4.20 Pch Slew Rate Setting Register (TRCNT_P)                        |    |

| 2.4.21 Charge Pump Setting Register 1 (CPSET1)                         |    |

| 2.4.22 Charge Pump Setting Register2 (CPSET2)                          |    |

| 2.4.23 Charge Pump Trimming Register (CP_TRIM)                         |    |

| 2.4.24 5V Regulator Voltage Setting Register (VREG5_TRIM)              |    |

| 2.4.25 Current Sense AMP Trimming Register (CSAMP_TRIM)                |    |

| 2.4.26 ALARM Raw Status Monitor Register1 (ALMRAW1)                    |    |

| 2.4.27 TOIN Pin Monitor Register (TOIN_MONI)                           |    |

| 2.4.28 WHO_AM_I register (WHO_AM_I)                                    |    |

| 2.4.29 Trimming Protect Register (TRIM_PT)                             |    |

| 2.4.30 Trimming Data Enable Register (TRIM_EN)                         |    |

| 2.4.31 High Accuracy BGR Temperature Correction Register (BGR_TRIM)    |    |

| 2.4.32 BUFFAMP Absolute Value Correction Register (BFAMP_TRIM)         |    |

| 2.5 Pre-Driver Function (Setting / Usage)                              |    |

| 2.5.1 Pre-Drive Block                                                  |    |

| 2.5.2 5V Regulator Block                                               |    |

| 2.5.3 Hall IC Comparator Block                                         |    |

| 2.5.4 Error Detection Block                                            |    |

| 2.5.5 CS AMP Block                                                     |    |

| 2.5.6 Charge Pump Block                                                |    |

| 2.5.7 Commutation Block                                                |    |

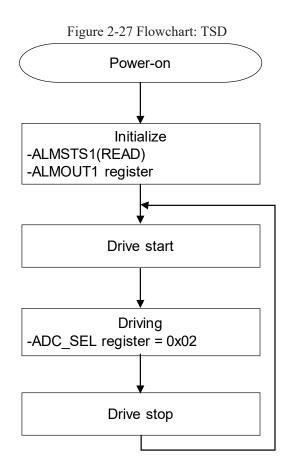

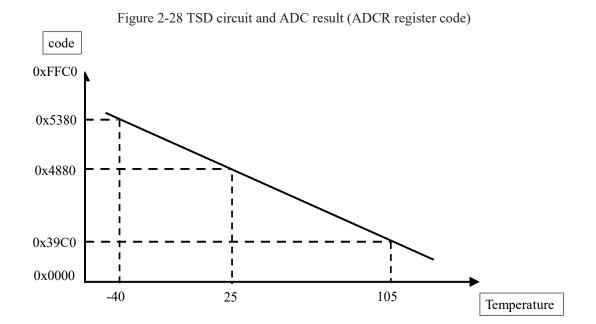

| 2.5.8 TSD (Thermal Shut Down) Block                                    |    |

| 2.5.9 Voltage Monitor (VMC) Block                                      |    |

| 2.5.10 BEMF Amp Block                                                  |    |

| 2.5.11 Trimming Register Block                                         |    |

| CHAPTER 3 RL78/G1F                                                     | 64 |

| 3.1 Outline of RL78/G1F built in RAJ306000 series                      |    |

| 3.2 Register setting of RL78/G1F for using RAJ306000 Series            |    |

| 3.3 Restriction of RL78/G1F                                            |    |

| 3.3.1 PIN FUNCTIONS                                                    |    |

| 3.3.2 CLOCK GENERATOR                                                  |    |

| 3.3.3 TIMER ARRAY UNIT                                                 |    |

| 3.3.4 TIMER RJ                                                         |    |

| 3.3.5 TIMER RD                                               |  |

|--------------------------------------------------------------|--|

| 3.3.6 TIMER RG                                               |  |

| 3.3.7 REAL-TIME CLOCK                                        |  |

| 3.3.8 12-BIT INTERVAL TIMER                                  |  |

| 3.3.9 CLOCK OUTPUT/BUZZER OUTPUT CONTROLLER                  |  |

| 3.3.10 WATCHDOG TIMER                                        |  |

| 3.3.11 A/D CONVERTER                                         |  |

| 3.3.12 D/A CONVERTER                                         |  |

| 3.3.13 COMPARATOR (CMP)                                      |  |

| 3.3.14 PROGRAMMABLE GAIN AMPLIFIER (PGA)                     |  |

| 3.3.15 SERIAL ARRAY UNIT (SAU)                               |  |

| 3.3.16 IrDA                                                  |  |

| 3.3.17 DATA TRANSFER CONTROLLER (DTC)                        |  |

| 3.3.18 EVENT LINK CONTROLLER (ELC)                           |  |

| 3.3.19 INTERRUPT FUNCTIONS                                   |  |

| 3.3.20 KEY INTERRUPT FUNCTION                                |  |

| 3.3.21 POWER-ON-RESET CIRCUIT                                |  |

| 3.3.22 OPTION BYTE                                           |  |

| 3.3.23 FLASH MEMORY                                          |  |

| CHAPTER 4 Sequence Example                                   |  |

| 4.1 Start-up Sequence                                        |  |

| 4.1.1 Built-in 5V regulator                                  |  |

| 4.2 Stop Sequence                                            |  |

| 4.2.1 STOP mode                                              |  |

| 4.2.2 SNOOZE mode                                            |  |

| CHAPTER 5 Attention to use                                   |  |

| 5.1 Operation in high temperature                            |  |

| APPENDIX A REVISION HISTORY                                  |  |

| A. 1 Major Revisions in This Edition (REV.2.02) from REV2.00 |  |

| A. 2 Major Revisions in REV.2.00 from REV1.06                |  |

| A. 3 Revision History of Preceding Editions                  |  |

|                                                              |  |

### CHAPTER 1 Outline

### 1.1 Features

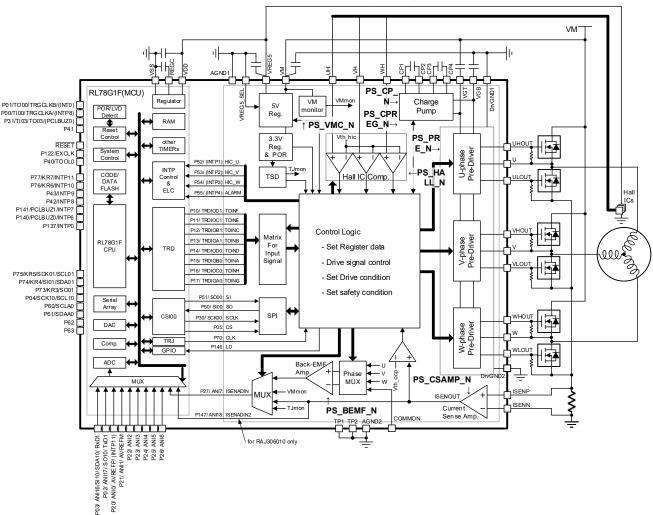

RAJ306000 series is a general-purpose Motor control IC consists of RL78/G1F and Pre-Driver.

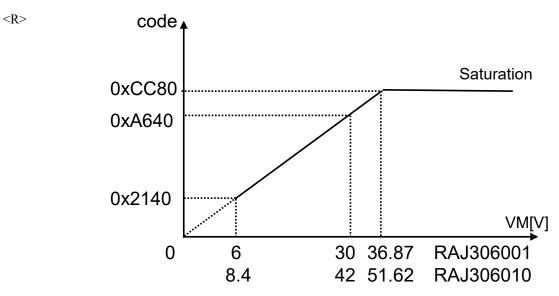

<R>

- RL78/G1F (R5F11BLEGFB)-powered

- Code-Flash 64KB

- Data-Flash 4KB

- RAM 5.5KB

- Possible to drive three phase Brushless DC motors

- Supports sensor [Hall based] and sensor-less control

- Dead time adjustment function.

- Adjustable gate drive current.

- Operating voltage: (Using double boost function of charge-pump

- 6V to 30V for RAJ306001

- 6V to 42V for RAJ306010

- Built in 5V regulator.

- Drive possible Nch MOSFET

- Peak gate drive current is 500mA.

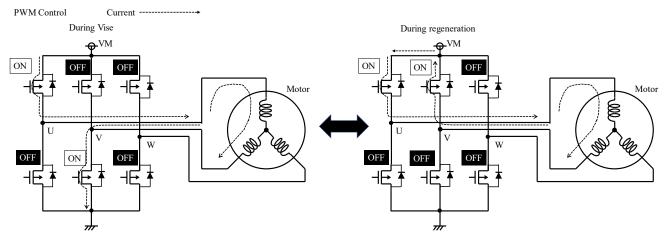

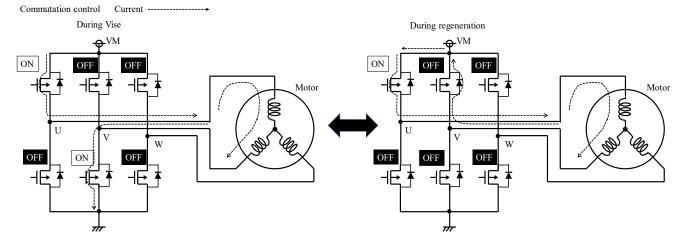

- Driving mode is selectable. (PWM control or commutation control)

- Support safety function

- The installed MCU (RL78/G1F) corresponds to IEC60730 safety standards.

- Over temperature protection (Thermal Shutdown)

- Over current protection (CS AMP, Built in 5V regulator)

- Under-voltage detection (VM, charge-pump)

- Over-voltage detection (Built in 5V regulator, charge-pump)

- Motor lock detection

- Hall IC comparator

- Adjustable input threshold voltage.

- Adjustable input hysteresis voltage.

- Various measurement circuit.

- VM voltage

- Chip temperature (Pre-Driver)

- Motor current

- Back-EMF voltage

### 1.2 Pin Configuration (Top View)

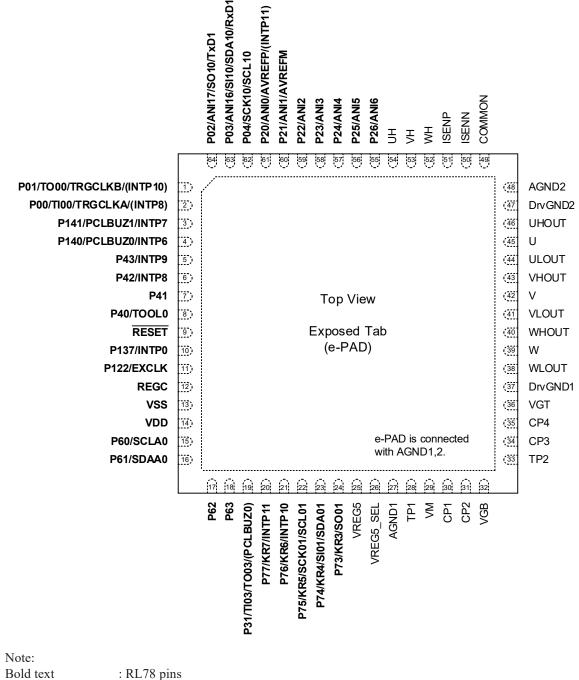

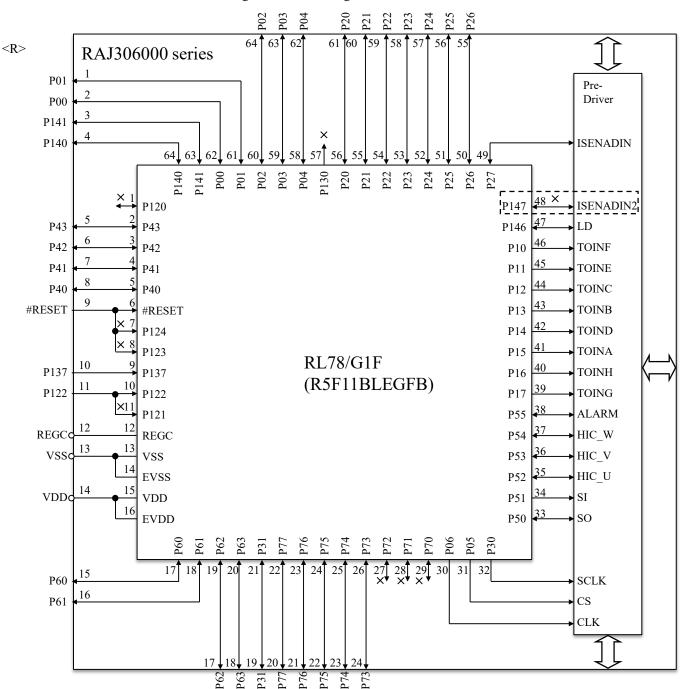

Figure 1-1 shows the pin configuration diagram.

Table 1-1, Table 1-2, and Table 1-3 show the pin configuration table of RAJ306000 series.

<R>

Figure 1-1 Pin configuration diagram

Bold text : RL78 pins Normal-face font : Pre-driver pins

#### PIN Initial IN/OUT or RL78 or I/O level Function Pre-Driver Power/GND Condition Number Name Main Function : GPIO Input Port P01 VDD I/O 1 Alternate Function : TO00/TRGCLKB/(INTP10) Main Function : GPIO 2 P00 VDD I/O Input port Alternate Function : TI00/TRGCLKA/(INTP8) Main Function : GPIO 3 P141 VDD I/O Input port Alternate Function : PCLBUZ1/INTP7 Main Function:GPIO 4 P140 VDD I/O Input port Alternate Function:PCLBUZ0/INTP6 Main Function:GPIO 5 P43 VDD I/O Input port Alternate Function:INTP9 Main Function:GPIO 6 P42 VDD I/O Input port Alternate Function:INTP8 7 P41 VDD GPIO I/O Input port Main Function:GPIO 8 P40 VDD I/O Input port Alternate Function:TOOL0 9 VDD -Input port Reset pin RESET Main Function:GPI 10 P137 VDD INPUT Input port Alternate Function:INTP0 Main Function : GPI INPUT P122 VDD 11 Input port Alternate Function : EXCLK REGC VDD 12 -Regulator output RL78 13 VSS VDD GND Ground potential for RL78/G1F pin. 14 VDD VDD Power Positive power supply for RL78/G1F pin. Main Function : GPIO P60 VDD I/O 15 Input port Alternate Function : SCLA0 Main Function : GPIO P61 VDD I/O 16 Input port Alternate Function : SDAA0 17 P62 VDD I/O Input port GPIO 18 P63 VDD I/O Input port GPIO Main Function : GPIO 19 P31 VDD I/O Input port Alternate Function :TI03/TO03/(PCLBUZ0) Main Function : GPIO P77 VDD I/O 20 Input port Alternate Function : KR7/INTP11 Main Function · GPIO 21 P76 VDD I/O Input port Alternate Function : KR6/INTP10 Main Function : GPIO 22 VDD I/O P75 Input port Alternate Function : KR5/SCK01/SCL01 Main Function : GPIO 23 P74 VDD I/O Input port Alternate Function : KR4/SI01/SDA01 Main Function:GPIO 24 P73 VDD I/O Input port Alternate Function:KR3/SO01

Table 1-1 Terminal table (1/3)

### **CHAPTER 1 Outline**

| Table 1-2 Terminal table (2/3) |        |                                                         |           |                        |                      |                                                                                                                           |

|--------------------------------|--------|---------------------------------------------------------|-----------|------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------|

| RL78 or<br>Pre-Driver          | Number | PIN<br>Name                                             | I/O level | IN/OUT or<br>Power/GND | Initial<br>Condition | Function                                                                                                                  |

|                                |        | Function of VREG5 pin is depends on VREG5_SEL pin level |           |                        |                      |                                                                                                                           |

|                                | 26     | VREG5_SEL                                               | VDD       | IN                     | IN                   | VREG5_SEL=GND:Built-in 5V regulator is selected. (Output 5V)<br>VREG5_SEL=5V:External 5V regulator is selected (Input 5V) |

|                                | 27     | AGND1                                                   | GND       | GND                    | GND                  | Ground potential for analog and logic circuits of Pre-Driver.                                                             |

|                                | 28     | TP1                                                     | VDD       | IN                     | IN                   | Terminal for Test. (Usually conect to GND via resistance.)                                                                |

|                                | 29     | VM                                                      | VM        | Power                  | Power                | Power Supply                                                                                                              |

|                                | 30     | CP1                                                     | VGB       | -                      | -                    | Charge pump flying capacitor for VGB (CP1)                                                                                |

|                                | 31     | CP2                                                     | VGB       | -                      | -                    | Charge pump flying capacitor for VGB (CP2)                                                                                |

|                                | 32     | VGB                                                     | VGB       | OUT                    | OUT                  | Gate drive voltage for Low-side                                                                                           |

|                                | 33     | TP2                                                     | 5V        | IN                     | IN                   | Terminal for Test. (Usually conect to GND)                                                                                |

|                                | 34     | CP3                                                     | VM        | -                      | -                    | Charge pump flying capacitor for VGT (CP3)                                                                                |

|                                | 35     | CP4                                                     | VGT       | -                      | -                    | Charge pump flying capacitor for VGT (CP4)                                                                                |

|                                | 36     | VGT                                                     | VGT       | OUT                    | OUT                  | Gate drive voltage for High-side                                                                                          |

|                                | 37     | DrvGND1                                                 | GND       | GND                    | GND                  | Ground potential for driving circuits of Pre-Driver.                                                                      |

|                                | 38     | WLOUT                                                   | VGB       | OUT                    | OUT                  | Output of Pre-driver for W phase Low-side (Nch MOSFET).                                                                   |

|                                | 39     | w                                                       | VM        | IN                     | IN                   | W phase voltage.                                                                                                          |

| Pre-Driver                     | 40     | WHOUT                                                   | VGT       | OUT                    | OUT                  | Output of Pre-driver for W phase High-side (Nch MOSFET).                                                                  |

|                                | 41     | VLOUT                                                   | VGB       | OUT                    | OUT                  | Output of Pre-driver for V phase Low-side (Nch MOSFET).                                                                   |

|                                | 42     | V                                                       | VM        | IN                     | IN                   | V phase voltage.                                                                                                          |

|                                | 43     | VHOUT                                                   | VGT       | OUT                    | OUT                  | Output of Pre-driver for V phase High-side (Nch MOSFET).                                                                  |

|                                | 44     | ULOUT                                                   | VGB       | OUT                    | OUT                  | Output of Pre-driver for U phase Low-side (Nch MOSFET).                                                                   |

|                                | 45     | U                                                       | VM        | IN                     | IN                   | U phase voltage.                                                                                                          |

|                                | 46     | UHOUT                                                   | VGT       | OUT                    | OUT                  | Output of Pre-driver for U phase High-side (Nch MOSFET).                                                                  |

|                                | 47     | DrvGND2                                                 | GND       | GND                    | GND                  | Ground potential for driving circuits of Pre-Driver.                                                                      |

|                                | 48     | AGND2                                                   | GND       | GND                    | GND                  | Ground potential for analog and logic circuits of Pre-Driver.                                                             |

|                                | 49     | COMMON                                                  | VM        | IN                     | IN                   | Input for Common signal of Motor.                                                                                         |

|                                | 50     | ISENN                                                   | 5V        | IN                     | IN                   | Connect Negative side of Shunt resistor.                                                                                  |

|                                | 51     | ISENP                                                   | 5V        | IN                     | IN                   | Connect Positive side of Shunt resistor.                                                                                  |

|                                | 52     | WH                                                      | 5V        | IN                     | IN                   | RAJ306001:Input of Hall IC signal for W phase                                                                             |

|                                | 02     |                                                         |           | IN/OUT                 | IN                   | RAJ306010:Input of Hall IC signal for W phase.<br>Output of BEFM amplifier signal.                                        |

|                                | 53     | VH                                                      | 5V        | IN                     | IN                   | Input of Hall IC signal for V phase                                                                                       |

|                                | 54     | UH                                                      | 5V        | IN                     | IN                   | Input of Hall IC signal for U phase                                                                                       |

| RL78 or    | PIN    |      | I/O level | IN/OUT or    | Initial            | Terminal function                                        |

|------------|--------|------|-----------|--------------|--------------------|----------------------------------------------------------|

| Pre-Driver | Number | Name | I/O IEVEI | Power/GND    | Condition          | Terminal function                                        |

|            | 55     | P26  | VDD       | I/O          | Analog<br>function | Main Function:GPIO<br>Sub Function:ANI6                  |

|            | 56     | P25  | VDD       | I/O          | Analog<br>function | Main Function:GPIO<br>Sub Function:ANI5                  |

|            | 57     | P24  | VDD       | I/O          | Analog<br>function | Main Function:GPIO<br>Sub Function:ANI4                  |

|            | 58     | P23  | VDD       | I/O          | Analog<br>function | Main Function:GPIO<br>Sub Function:ANI3                  |

| RL78       | 59     | P22  | VDD       | VDD I/O func | Analog<br>function | Main Function:GPIO<br>Sub Function:ANI2                  |

| RL/O       | 60     | P21  | VDD       |              | Analog<br>function | Main Function:GPIO<br>Sub Function:ANI1/AVREFM           |

|            | 61     | P20  | VDD       | I/O          | Analog<br>function | Main Function:GPIO<br>Sub Function:ANI0/AVREFP/(INTP11)  |

|            | 62     | P04  | VDD       | I/O          | Input port         | Main Function:GPIO<br>Sub Function:SCK10/SCL10           |

|            | 63     | P03  | VDD       | I/O          | Analog<br>function | Main Function:GPIO<br>Sub Function:ANI16/SI10/SDA10/RxD1 |

|            | 64     | P02  | VDD       | I/O          | Analog<br>function | Main Function:GPIO<br>Sub Function:ANI17/SO10/TxD1       |

### Table 1-3 Terminal table (3/3)

### 1.3 Recommended circuit

### 1.3.1 Power supply

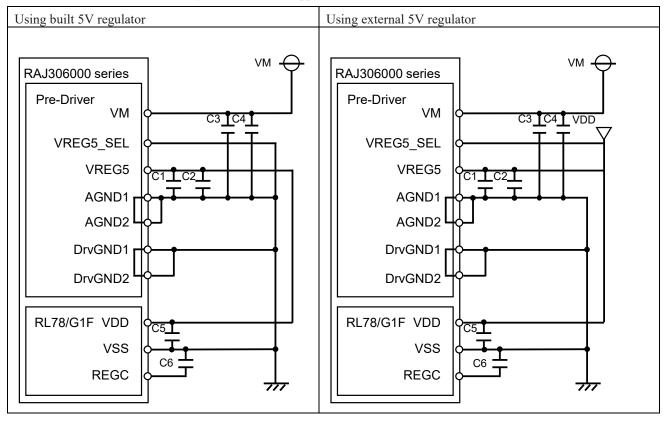

This IC has built in 5V regulator. When using built in 5V regulator, connect VREG5\_SEL Pin to GND, Then Pre-Diver regulates 5V from VM and supply to Pre-Driver and RL78/G1F. And when using external 5V regulator, connect 5V to VREG5, VREG5 SEL and VDD.

Note 1: When not using internal 5V regulator, please supply same voltage of 5V to VREG5\_SEL, VREG5 and VDD. And the sequence is as follows.

- •Start-up  $:VM \rightarrow VREG5$

- •Finish :VREG5  $\rightarrow$  VM

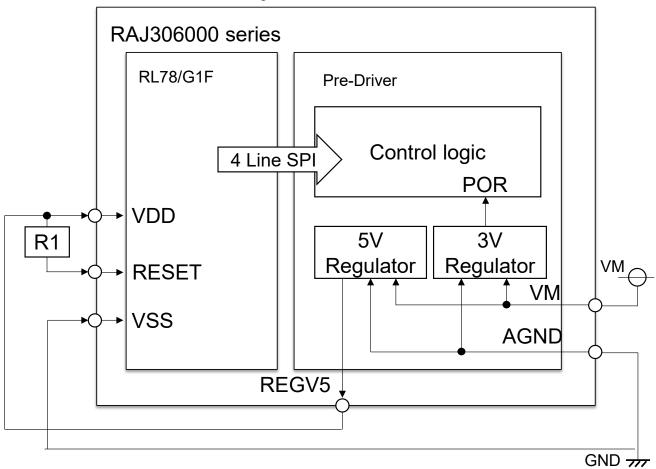

### 1.3.2 Reset function

This IC has the following two reset way.

•Power on reset by VM power supply

•Software reset by SPI communication.

RESET pin is reset for only RL78/G1F. So, when using reset pin, use with software reset.

Figure 1-3 Reset Construction.

#### RAJ306000 Series

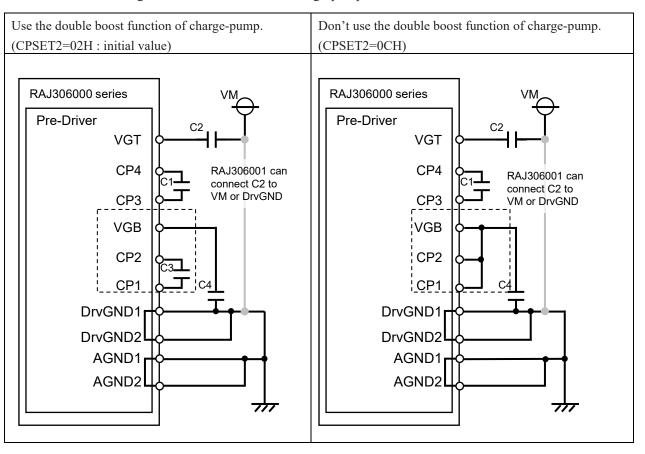

### 1.3.3 Charge-pump

The Charge-pump external circuits are shown in Figure 1-4. The recommended circuit depends on whether double boost function of charge-pump use or not. CPSE2 register initial value is 02H, this means double boost function. If you don't use double Boost, set CPSET2=0CH before you start the charge pump.

<R> In RAJ306001, connect the smoothing capacitance C2 of VGT to either VM or DrvGND. It is recommended to connect to the VM for applications where the VM voltage changes significantly.

In RAJ306010, set the connection destination of VGT smoothing capacity C2 to VM. It is prohibited to connect to DrvGND.

Figure 1-4 Boost function of charge-pump and recommended circuit.

<R>

### Table 1-4 Boost Voltage

| Setting          | VGB(V) | VGT(V) |

|------------------|--------|--------|

| Double Boost     | 13     | VM+13  |

| Not double Boost | 10     | VM+10  |

### 1.4 Recommended drive waveform

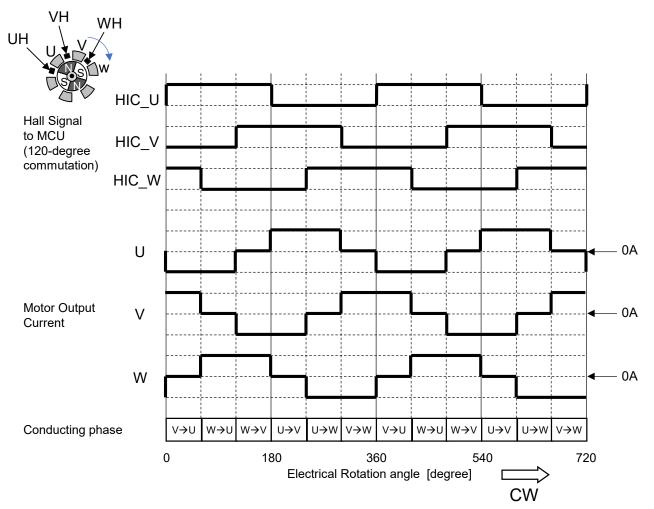

Figure 1-5 shows recommended waveform of Hall-IC signal at HIC\* and driving current when using Hall-IC.

Pre-Driver in this IC control the function of commutation drive mode.

Then using these functions, set this relationship of recommended drive waveform by using registers of SELSIG\_U, SELSIG\_V, SELSIG\_W and HALL\_SIG.

When not using the abovementioned function, there is no need to follow this recommended waveform.

### Figure 1-5 recommended drive waveform

<R>

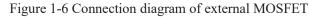

### 1.5 How to select the external MOSFET

The selection method of the external MOSFET is described.

When using the dead time adjustment function, it is necessary to use an external MOSFET that satisfies the following condition. If an external MOSFET that does not satisfy the following conditions is used, the external MOSFET may be destroyed by the through current. And when using auto deadtime adjust function, Renesas recommends not to insert the resistance on gate line of External Drive MOS. The reason is followings.

• By inserting the resistance, the signal delay is occurred on the node at before and after the resistance. By this delay, dead time auto adjust function cannot operate to External Drive MOS.

And by inserting the resistance, the impedance to fix Lo on gate node is also decreased. By decreasing impedance, "Self Turn On" phenomenon would be easily occurred and become potential high to generate through current.

Detail description of the dead time adjustment function is described in "2.5.1.1 Dead time auto adjust function".

For the external MOSFET with the condition of "Vt\_monitor> Vt\_power", fall time is calculated using the following equation and it needs the calculation result satisfies "t = <30 nsec".

When external MOSFETs satisfy the condition "Vt\_monitor =< Vt\_power", there are no restrictions.

$$t = -C \times R \times \ln\left(\frac{Vt\_power}{Vt\_monitor}\right)$$

Vt monitor :Threshold voltage of MOSFET Vgs monitor circuit

Vt\_power :External MOSFET threshold voltage

C :External MOSFET gate capacitance (Refer to the MOSFET data sheet)

R:Low side output impedance

(Refer to the gate drive output impedance in the device characteristics

reference data of the RAJ306000 series data sheet.)

Even if condition is satisfied, Renesas recommends evaluating sufficiently to select the external MOSFET, especially through current.

Showing a setting example below

Vt\_monitor :Threshold voltage of MOSFET Vgs monitor circuit = 1.0 V

Vt\_power :External MOSFET threshold voltage = 0.8 V

C:External MOSFET gate capacitance= 4000 pF

R:Low side output impedance =  $20 \Omega$

(From the device characteristic reference data of the data sheet of RAJ306000 series)

In case of calculation with the above reference value

$$t = -4000 pF \times 20 \times ln \left(\frac{0.8}{1.0}\right) = 17.85 nsec$$

This satisfies t = <30 nsec.

In the case of Vt\_power = 0.6 V,

$$t = -4000 pF \times 20 \times ln\left(\frac{0.6}{1.0}\right) = 40.87 nsec$$

This does not satisfy t = <30 nsec.

### CHAPTER 2 Pre-Driver

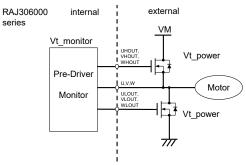

### 2.1 Terminal configuration of Pre-Driver.

### 2.1.1 The terminal connection of Pre-Driver

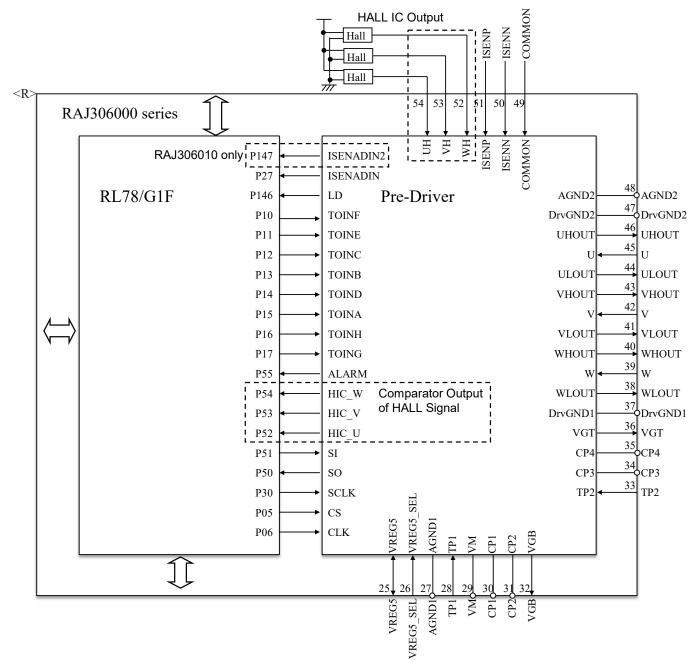

2.1.1.1 The connection when using HALL\_IC

When HALL\_IC is connected, please set to 0 (HALL\_IC control: initial value) at the HALL\_MODE\_SEL bit of the HALL\_SIG register. Signals of UH, VH, WH are outputted from HIC\_U, HIC\_V, HIC\_W via Hall IC comparator.

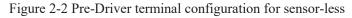

### 2.1.1.2 The connection of sensor-less mode

When controlling using the sensor-less mode, please set to1 (sensor-less control) at the HALL\_MODE\_SEL bit of the HALL\_SIG register.

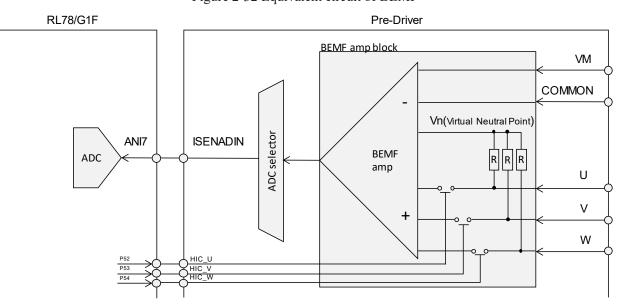

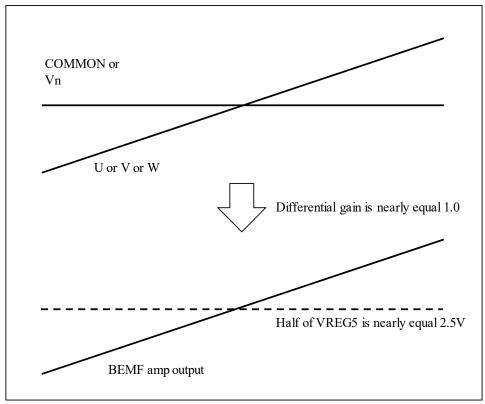

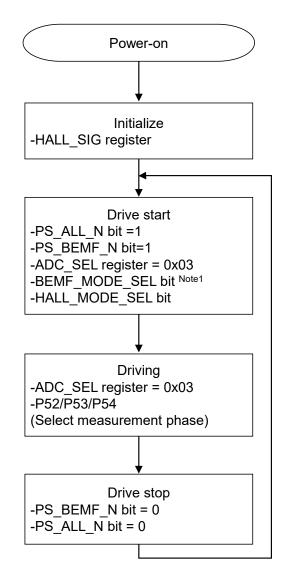

The phase that measures the back-EMF voltage can be selected by controlling P52, P53 and P54. which is the output terminal of GPIO,

When controlling in sensorless mode using RAJ306001, UH, VH, and WH terminals are pulled down by built-in resistors. If not used, open or connect to GND.

When controlling in sensorless mode using RAJ306010, there is a function to output BEMF amplifier output from WH terminal. When using this function, do not connect WH pin to GND.

### 2.1.2 Pre-Driver terminal table

Table 2-1 shows the Pre-Driver external pins.

Table 2-2 shows the internal pins of the pre-driver internally connected to the RL78/G1F.

| Number<br>25<br>26 | Name<br>VREG5 | I/O level | IN/OUT or<br>Power/GND | Initial   | Function                                                                                                                |

|--------------------|---------------|-----------|------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------|

|                    | VREG5         |           |                        | Condition |                                                                                                                         |

| 26                 |               | 5V        | IN/OUT                 | IN/OUT    | Function of VREG5 pin is depends on VREG5_SEL pin level<br>VREG5_SEL=GND:Built-in 5V regulator is selected. (Output 5V) |

|                    | VREG5_SEL     | VDD       | IN                     | IN        | VRE65_SEL=6ND.bulletin 3V regulator is selected. (Output 3V)                                                            |

| 27                 | AGND1         | GND       | GND                    | GND       | Ground potential for analog and logic circuits of Pre-Driver.                                                           |

| 28                 | TP1           | VDD       | IN                     | IN        | Terminal for Test. (Usually conect to GND via resistance.)                                                              |

| 29                 | VM            | VM        | Power                  | Power     | Power Supply                                                                                                            |

| 30                 | CP1           | VGB       | -                      | -         | Charge pump flying capacitor for VGB (CP1)                                                                              |

| 31                 | CP2           | VGB       | -                      | -         | Charge pump flying capacitor for VGB (CP2)                                                                              |

| 32                 | VGB           | VGB       | OUT                    | OUT       | Gate drive voltage for Low-side                                                                                         |

| 33                 | TP2           | 5V        | IN                     | IN        | Terminal for Test. (Usually conect to GND)                                                                              |

| 34                 | CP3           | VM        | -                      | -         | Charge pump flying capacitor for VGT (CP3)                                                                              |

| 35                 | CP4           | VGT       | -                      | -         | Charge pump flying capacitor for VGT (CP4)                                                                              |

| 36                 | VGT           | VGT       | OUT                    | OUT       | Gate drive voltage for High-side                                                                                        |

| 37                 | DrvGND1       | GND       | GND                    | GND       | Ground potential for driving circuits of Pre-Driver.                                                                    |

| 38                 | WLOUT         | VGB       | OUT                    | OUT       | Output of Pre-driver for W phase Low-side (Nch MOSFET).                                                                 |

| 39                 | W             | VM        | IN                     | IN        | W phase voltage.                                                                                                        |

| 40                 | WHOUT         | VGT       | OUT                    | OUT       | Output of Pre-driver for W phase High-side (Nch MOSFET).                                                                |

| 41                 | VLOUT         | VGB       | OUT                    | OUT       | Output of Pre-driver for V phase Low-side (Nch MOSFET).                                                                 |

| 42                 | V             | VM        | IN                     | IN        | V phase voltage.                                                                                                        |

| 43                 | VHOUT         | VGT       | OUT                    | OUT       | Output of Pre-driver for V phase High-side (Nch MOSFET).                                                                |

| 44                 | ULOUT         | VGB       | OUT                    | OUT       | Output of Pre-driver for U phase Low-side (Nch MOSFET).                                                                 |

| 45                 | U             | VM        | IN                     | IN        | U phase voltage.                                                                                                        |

| 46                 | UHOUT         | VGT       | OUT                    | OUT       | Output of Pre-driver for U phase High-side (Nch MOSFET).                                                                |

| 47                 | DrvGND2       | GND       | GND                    | GND       | Ground potential for driving circuits of Pre-Driver.                                                                    |

| 48                 | AGND2         | GND       | GND                    | GND       | Ground potential for analog and logic circuits of Pre-Driver.                                                           |

| 49                 | COMMON        | VM        | IN                     | IN        | Input for Common signal of Motor.                                                                                       |

| 50                 | ISENN         | 5V        | IN                     | IN        | Connect Negative side of Shunt resistor.                                                                                |

| 51                 | ISENP         | 5V        | IN                     | IN        | Connect Positive side of Shunt resistor.                                                                                |

| FD                 |               | EV        | IN                     | IN        | RAJ306001:Input of Hall IC signal for W phase                                                                           |

| 52                 | VVH           | WH 5V -   | IN/OUT                 | IN        | RAJ306010:Input of Hall IC signal for W phase.<br>Output of BEFM amplifier signal.                                      |

| 53                 | VH            | 5V        | IN                     | IN        | Input of Hall IC signal for V phase                                                                                     |

| 54                 | UH            | 5V        | IN                     | IN        | Input of Hall IC signal for U phase                                                                                     |

Table 2-1 Pre-Driver external pins.

|             |           |                        | Table 2-2 Pre-Driver internal pins.                                                                                                                                                               |

|-------------|-----------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN<br>Name | I/O level | IN/OUT or<br>Power/GND | Function                                                                                                                                                                                          |

| ISENADIN2   | Analog    | OUT                    | RAJ306010 only:Output analog signal of current sense amplifier(P147).                                                                                                                             |

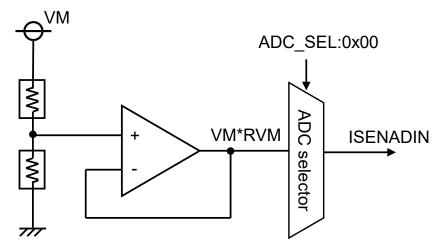

| ISENADIN    | Analog    | OUT                    | Output analog signal of selected by ADC_SEL register to ANI17(P27).                                                                                                                               |

| LD          | Digital   | OUT                    | Output moter lock status to P147 pin.                                                                                                                                                             |

| TOINF       | Digital   | IN                     | Input of PWM pulse from TRDIOD1(P10) pin.                                                                                                                                                         |

| TOINE       | Digital   | IN                     | Input of PWM pulse from TRDIOC1(P11) pin.                                                                                                                                                         |

| TOINC       | Digital   | IN                     | Input of PWM pulse from TRDIOB1(P12) pin.                                                                                                                                                         |

| TOINB       | Digital   | IN                     | Input of PWM pulse from TRDIOA1(P13) pin.                                                                                                                                                         |

| TOIND       | Digital   | IN                     | Input of PWM pulse from TRDIOD0(P14) pin.                                                                                                                                                         |

| TOINA       | Digital   | IN                     | Input of PWM pulse from TRDIOB0(P15) pin.                                                                                                                                                         |

| TOINH       | Digital   | IN                     | Input of PWM pulse from TRDIOC0(P16) pin.                                                                                                                                                         |

| TOING       | Digital   | IN                     | Input of PWM pulse from TRDIOA0(P17) pin.                                                                                                                                                         |

| ALARM       | Digital   | OUT                    | Output ALARM pulse to INTP4(P55) pin.                                                                                                                                                             |

| HIC_W       | Digital   | IN/OUT                 | Function of HIC_W depends on HALL_MODE_SEL bit.<br>0:Select hall-comparator W phase output tp INTP3(P54).<br>1:Select W phase BEMF measurement instruction signal input for sensor-less from P54. |

| HIC_V       | Digital   | IN/OUT                 | Function of HIC_V depends on HALL_MODE_SEL bit.<br>0:Select hall-comparator V phase output tp INTP2(P53).<br>1:Select V phase BEMF measurement instruction signal input for sensor-less from P53  |

| HIC_U       | Digital   | IN/OUT                 | Function of HIC_U depends on HALL_MODE_SEL bit.<br>0:Select hall-comparator V phase output tp INTP1(P52).<br>1:Select V phase BEMF measurement instruction signal input for sensor-less from P52  |

| SI          | Digital   | IN                     | 4Line-SPI:Input data from SO00(P51) pin as CSI00.                                                                                                                                                 |

| SO          | Digital   | OUT                    | 4Line-SPI:Output data to SI00(P50) pin as CSI00.<br>Set on-chip pull-up enable in RL78/G1F.                                                                                                       |

| SCLK        | Digital   | IN                     | 4Line-SPI::Output communication clk[1MHz] to SCK00(P30) pin as CSI00.                                                                                                                             |

| CS          | Digital   | IN                     | 4Line-SPI:Input chip select signal from P05 pin.H;Not selected,L:Selected.                                                                                                                        |

| CLK         | Digital   | IN                     | Input system clock[4MHz] from TRJIO0(P06).                                                                                                                                                        |

### 2.2 System clock of Pre-Driver

In order to use the Pre-Driver of this IC, it is necessary to supply the system clock by using the pulse output function of the I/O setting and timer RJ of RL78/G1F.

- I/O setting Peripheral I/O redirection register 1 (PIOR1): Set to 0BH [PIOR13,12,11,10]= [1, 0, 1, 1] Target pin: RL78/G1F P06 is selected as TRJIO0 P06 is internally connected to the CLK pin of the pre-driver.

- 2. Timer RJ

<R>

Operation mode: Pulse output mode.

Cycle setting: Set the timer RJ counter register 0 (TRJ0) to 125ns. The output is inverted every 125ns. As a result, a signal with a cycle of 250 ns (4 MHz) is output to the Pre-Driver as a clock.

The Pre-Driver has a clock stop detection function and switches to the power save mode when it is determined that the clock has not been input.

The internal interface terminals are changed as shown in Table 2-3 shows the Pre-Driver pin states and recommended settings for the MCU pins when the clock is stopped. When stopping the Pre-Driver to save power, change the MCU pin processing while the clock is stopped.

Also, if the following register settings of the pre-driver are set to 1 at the start of clock re-supply, a charge pump related status error may be detected. Set these bits to 0 before stopping the clock.

- 1. MOT\_EN bit of motor drive control setting register,

- 2. PS\_CPREG\_N, PS\_CP\_N bits in the power save control setting register for each function

Table 2-3 Internal terminal state when clock supply is stopped

| PreD                | river     | RL78/G1F   |                                                                                               |  |  |

|---------------------|-----------|------------|-----------------------------------------------------------------------------------------------|--|--|

| PIN                 | Level     | PIN        | Recommended pin processing                                                                    |  |  |

| ISENADIN            | Hi-Z      | P27/ANI7   | Set output pin and output low level.                                                          |  |  |

| ISENADIN2<br>Note 1 | Hi-Z      | P147/ANI18 | Please select either setting<br>●Set Output low level<br>●Set input pin and internal pull-up. |  |  |

| LD                  | Pull-down | P146       | Set input pin.                                                                                |  |  |

| TOINF               | Pull-down | P10        |                                                                                               |  |  |

| TOINE               | Pull-down | P11        |                                                                                               |  |  |

| TOINC               | Pull-down | P12        |                                                                                               |  |  |

| TOINB               | Pull-down | P13        | Set output pin and output low level.                                                          |  |  |

| TOIND               | Pull-down | P14        |                                                                                               |  |  |

| TOINA               | Pull-down | P15        |                                                                                               |  |  |

| TOINH               | Pull-down | P16        |                                                                                               |  |  |

| TOING               | Pull-down | P17        |                                                                                               |  |  |

| ALARM               | Pull-down | P55        | Set input pin.                                                                                |  |  |

| HIC_W               | Pull-down | P54        |                                                                                               |  |  |

| HIC_V               | Pull-down | P53        |                                                                                               |  |  |

| HIC_U               | Pull-down | P52        |                                                                                               |  |  |

| SI                  | Pull-down | P51        | Set output pin and output low level.                                                          |  |  |

| SO                  | Hi-Z      | P50        |                                                                                               |  |  |

| SCLK                | Pull-down | P30        |                                                                                               |  |  |

| CS                  | Pull-down | P05        |                                                                                               |  |  |

| CLK                 | Pull-down | P06        |                                                                                               |  |  |

Note 1 ISENADIN2 is RAJ306010 only. In case of RAJ306001, regardless of the power save status, please process the terminals when stopped.

\*Perform port switching processing while the clock is stopped.

### 2.3 Communication format

When setting Pre-Driver register, use 1MHz 4-Line SPI communication by using CSI00 (SCK00, SO00, SI00) and P05 (CS) pin. Output the CS signal is by using GPIO of P05.

Figure 2-3 Shows Communication format. SPI communication is denied when not satisfy the format.

|                                  | r igule 2 9 Communication format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| -Write<br>CS(P05)<br>SCLK(SCK00) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| MOSI(SO00)                       | R/W(L)         Add[6]         Add[3]         Add[2]         Add[1]         Add[0]         WData[7]         WData[6]         WData[4]         WData[2]         WData[1]         WData[1 |      |

| MISO(SI00)                       | Hiz "L" kvel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Hi-z |

| -Read<br>CS(P05)                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| SCLK(SCK00)                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| MOSI(SO00)                       | R/W(H)         Add[6]         Add[5]         Add[4]         Add[3]         Add[2]         Add[1]         Add[0]         Don't Care                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| MISO(SI00)                       | Hi-z "L" kvel RData[7] RData[6] RData[6] RData[6] RData[4] RData[2] RData[1] RData[0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Hi-z |

### Figure 2-3 Communication format

### RAJ306000 Series

<R>

### 2.4 Pre-Driver register

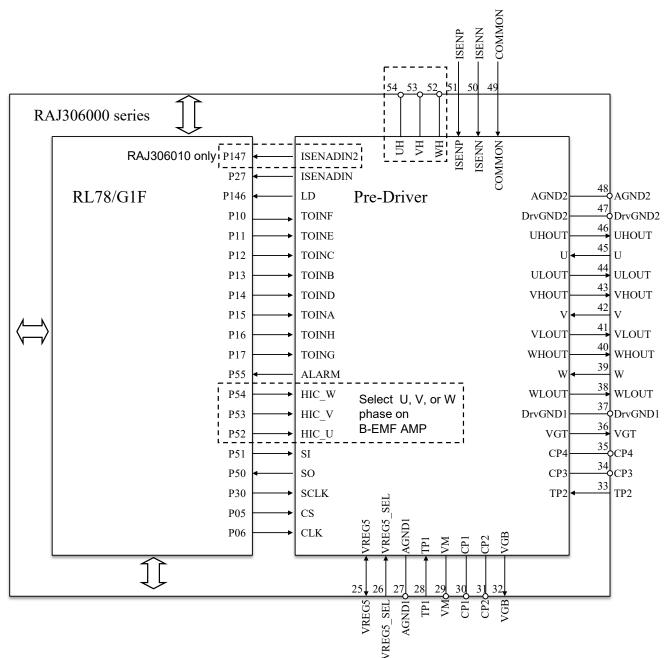

The register map is shown in Table 2-4.

• The column "b14-8" means the address of each registers. Set value to 14-8 bit in SPI communication.

• "0" and "1" mean initial value for each bit after reset. For these registers, Set to these values at writing.

|                                             |            |             |          |             |                     | register           | шар                |                    |                   |                         |                 |                 |

|---------------------------------------------|------------|-------------|----------|-------------|---------------------|--------------------|--------------------|--------------------|-------------------|-------------------------|-----------------|-----------------|

| Register Name                               | Symbol     | After Reset | R/W      | b14-8       | [7]                 | [6]                | [5]                | [4]                | [3]               | [2]                     | [1]             | [0]             |

| -                                           | -          | -           | -        | 00h         | 0                   | 0                  | 0                  | 0                  | 0                 | 0                       | 0               | 0               |

| Power Save Control                          | PS_ALL     | 00h         | R/W      | 02h         | 0                   | 0                  | 0                  | 0                  | 0                 | 0                       | 0               | PS_ALL_N        |

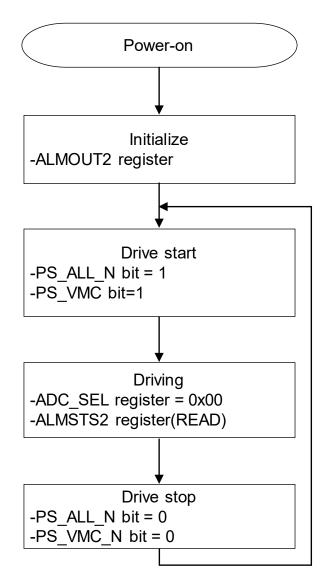

| By Function Power Control Setting           | PS         | 00h         | R/W      | 04h         | PS_PRE_N            | 0                  | PS_BEMF_N          | PS_CSAMP_N         | PS_VMC_N          | PS_HALL_N               | PS_CPREG_N      | PS_CP_N         |

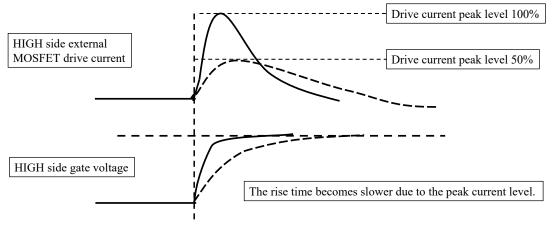

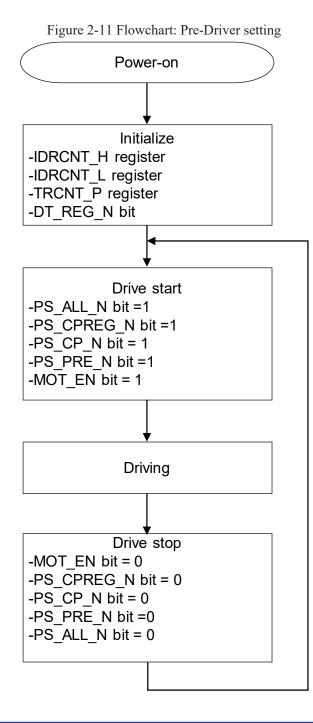

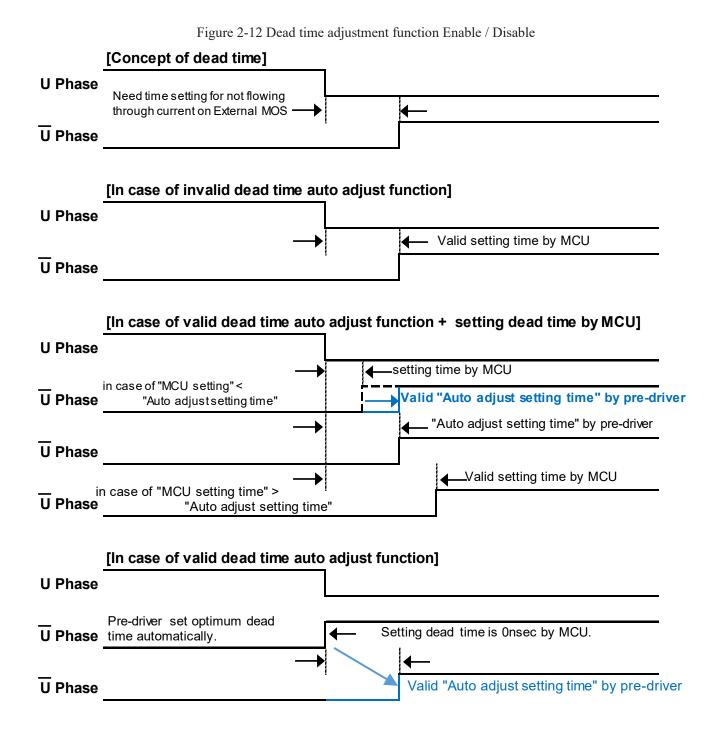

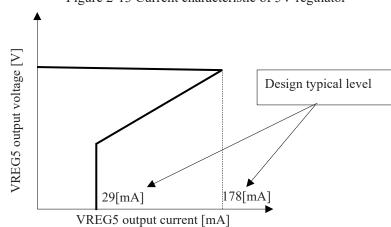

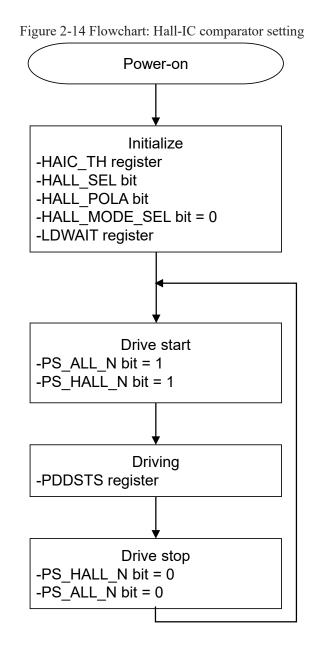

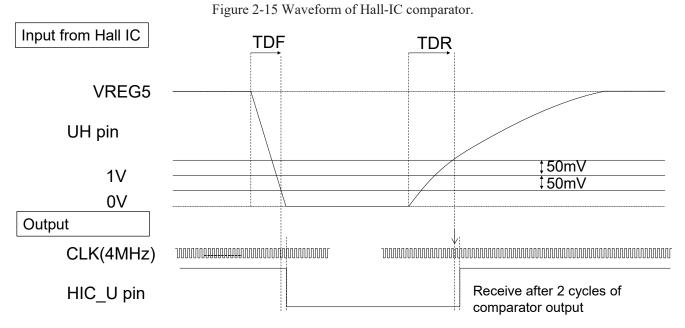

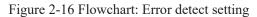

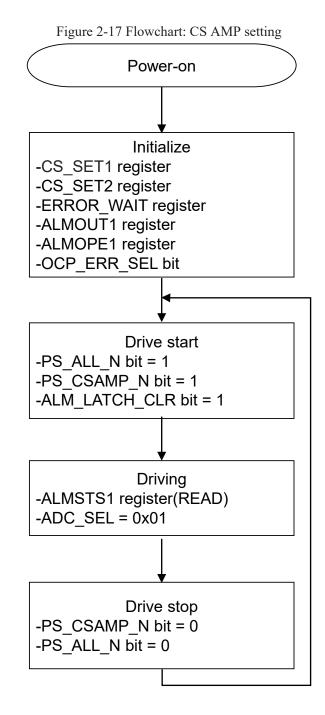

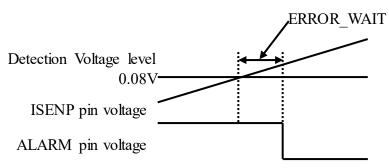

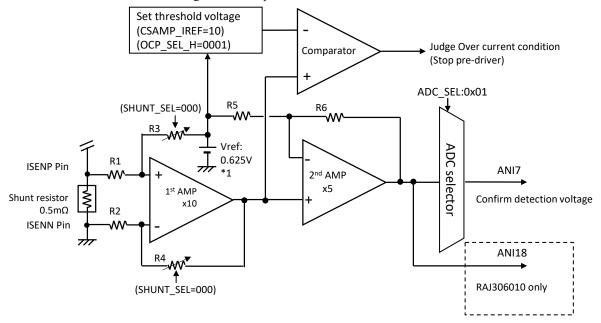

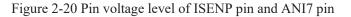

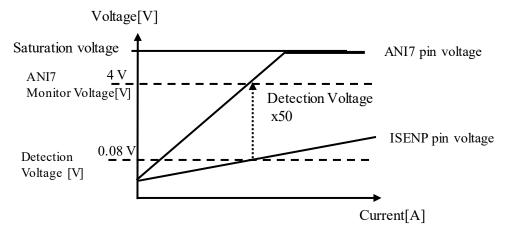

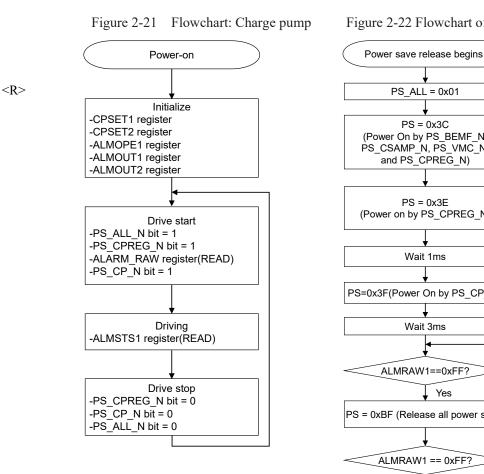

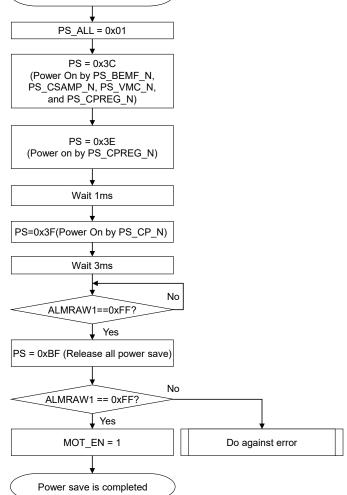

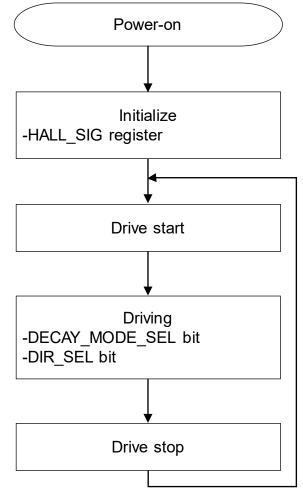

| Software Reset                              | SW_RESET   | 00h         | R/W      | 06h         | 0                   | 0                  | 0                  | 0                  | 0                 | 0                       | 0               | SW_RESET        |