#### RENESAS

# ne GreenPAK<sup>TM</sup> ookbook

# 2. Sequential Logic

Basic Blocks

Functions

3. Signal Conditioning

4. Safety Features

. Communication Protocols

#### Introduction to GreenPAK

Renesas Electronics GreenPAK ICs are a family of Programmable Mixed-signal ICs that provide a small, cost-effective, and personalized solution to common problems that system-level circuit designers face. GreenPAK provides a means of considerably reducing PCB size, BOM cost, and design time.

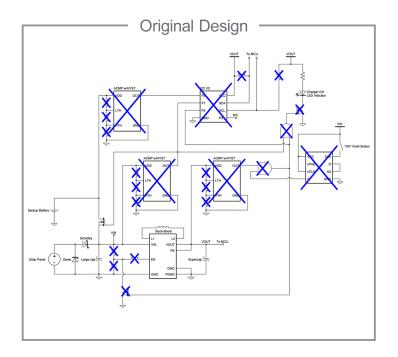

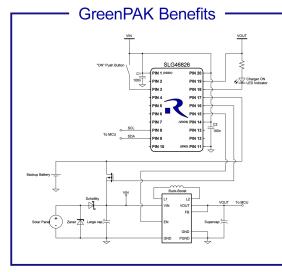

#### Design reduced by

- 5 IC

- 2 NMOS transistors

- 14 passive components

#### Example of Size Reduction w/ GreenPAK

Due to the features and configurability of GreenPAK, narrowing the scope of possible applications can be difficult.

With the right motivation a designer can use GreenPAK in almost any application within most industries. This document is createdd to bolster this motivation and know-how. We provide a the Cookbook to designers to highlight where GreenPAK can be used within their projects. The Cookbook outlines different techniques and provides completed applications to help designers use GreenPAK on their own.

#### The Cookbook Structure

The majority of subsections within this document are organized into two categories: Technique and Application. Techniques focus on a task accomplished using only one or a few macrocells. Application sections describe how techniques can be used or mixed together to create real, valuable applications. Generally, the easiest techniques and applications will be at the beginning of a chapter.

Each application has an associated the GreenPAK Designer file that can be viewed and modified.

# 2. Sequential Logic

Basic Blocks

Functions

3. Signal Conditioning

4. Safety Features

**Protocols**

6. Pulse-based Control

#### Making Your Own Design With the Cookbook

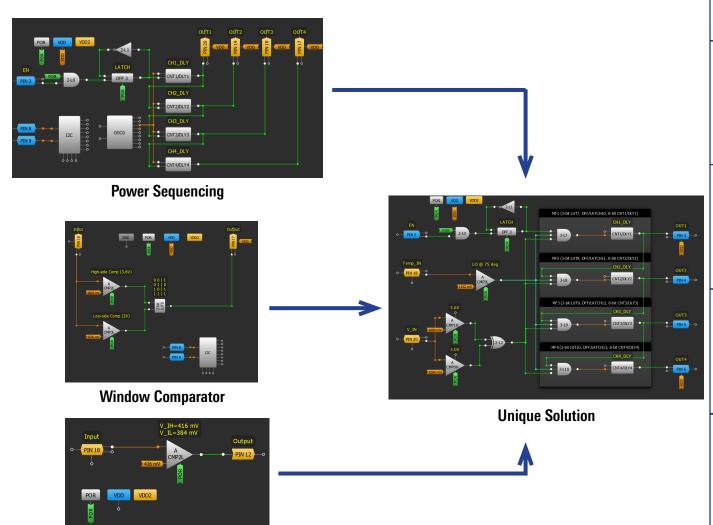

The applications outlined in the Cookbook are simple realization of real-world applications. However, GreenPAK ICs have the macrocells and functionality to add far more value than the designs in this Cookbook. Renesas Electronics helped designers create thousands of unique designs, where simple applications, both similar and different to the Cookbook applications, were expanded, combined, and personalized.

For example, the <u>Application: Basic Sequencer</u> can be combined with many of the applications within <u>Chapter 4: Safety Features</u> to create a self-regulating, customized sequencing application.

**Overtemperature Detection**

The resulting integrated solution is more complex yet still does not incorporate all available macrocells. With the entire GreenPAK ICs family at your disposal, the number of permutations and modifications available for the designs in this Cookbook are endless. Feel free to completely reuse a design shown in this Cookbook or incorporate some of the techniques in this paper into your own design. After all, it is your recipe.

#### The GreenPAK Cookbook

1.Basic Blocks & Functions

2. Sequential

3. Signal Conditioning

4. Safety Features

5. Communication Protocols

6. Pulse-based Control

7. Power Management

#### **Contents**

| Introduction to GreenPAK                                        | 2         |

|-----------------------------------------------------------------|-----------|

| The Cookbook Structure                                          | 2         |

| Making Your Own Design With the Cookbook                        | 3         |

| Chapter 1 Basic Blocks & Functions                              | 8         |

| Technique: Learning More About a Macrocell                      | 9         |

| Overview: Digital Macrocells                                    | 9         |

| Technique: Configuring Standard Logic with LUT Macrocells       | 10        |

| Overview: Oscillators                                           | 10        |

| Overview: Analog Comparators                                    | 10        |

| Overview: I/Os                                                  | 11        |

| Overview: Interconnections                                      | 11        |

| Technique: Simulation and Emulation Using the GreenPAK Designer | 12        |

| Technique: GreenPAK Programming                                 | 13        |

| Technique: OE Pin                                               | 14        |

| Application: Parity Bit Generator                               | 15        |

| Application: 8-bit Multiplexer                                  | 16        |

| Application: Demultiplexer                                      | 17        |

| Technique: Changing I2C Address                                 | 18        |

| Chapter 2 Sequential Logic                                      | 19        |

| Technique: Optimizing CNT/DLY Accuracy                          | 20        |

| Technique: Sequencing CNT/DLY Blocks                            | 21        |

| Application: System Reset                                       | 22        |

| Application: Several Button Reset                               | 23        |

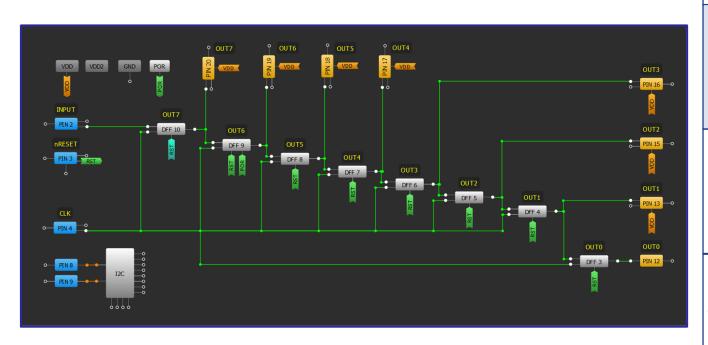

| Application: Basic Sequencer                                    | 24        |

| Application: Cascaded Sequencer                                 | 25        |

| Application: Voltage Monitoring Power Sequencer                 | 26        |

| Application: Ship Mode Controller                               | 27        |

| Technique: Creating a Synchronous State Machine from an ASM     | 28        |

| Application: N-Length Bitstream                                 | 29        |

| Technique: Multiplexing a Bitstream                             | 30        |

| Application: 10 Year Counter                                    | 31        |

| Application: Square Wave Generator                              | 32        |

| Application: Two Event Button Press                             | 33        |

| Application: Advanced Voltage Monitoring Power Sequencer        | 34        |

| Chapter 3 Signal Conditioning                                   | <b>35</b> |

| Technique: Using a CNT/DLY Block as a Deglitch Filter           | 36        |

| Technique: Edge Detector                                        | 37        |

| Application: Interrupt Controller                               | 38        |

| Technique: Creating a Bi-directional Counter                    | 39        |

| Application: Encoder                                            | 40        |

| Application: Distance Sense                                     | 41        |

| Application: Frequency Range Detector                           | 42        |

| Application: Frequency Divider                                  | 43        |

| Technique: Zero-Voltage Cross Detection                         | 44        |

4

9. Advanced Analog Features

2. Sequential

3. Signal Conditioning

4. Safety Features

5. Communication Protocols

6. Pulse-based Control

7. Power Management

| Application: Analog Storage Element                                     | 45 |

|-------------------------------------------------------------------------|----|

| Chapter 4 Safety Features                                               | 46 |

| echnique: Reducing ACMP Power Consumption                               | 47 |

| echnique: Wake-Sleep Controller                                         | 48 |

| Application: Window Comparator                                          | 49 |

| Application: Over Temperature Protection                                | 50 |

| Application: Battery Charge Indicator                                   | 51 |

| Application: Low Voltage Indicator for Infotainment                     | 52 |

| Application: Watchdog Timer                                             | 53 |

| Application: Voltage Level Detection                                    | 54 |

| Application: Power Backup Management                                    | 55 |

| Application: N-pulse Presence Watchdog                                  | 56 |

| echnique: Using the Temperature Sensor Block                            | 57 |

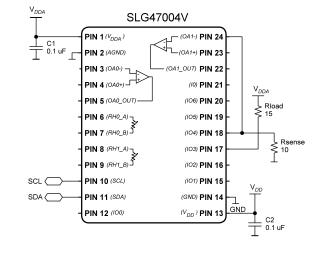

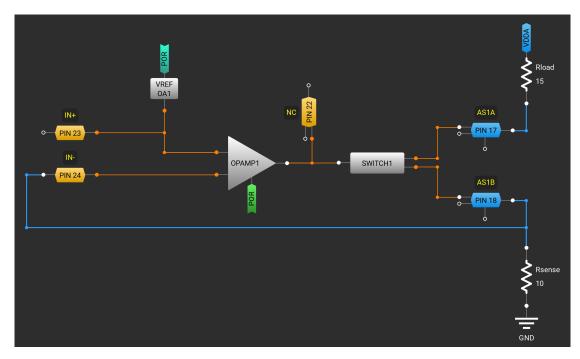

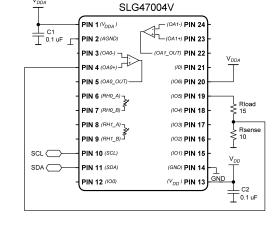

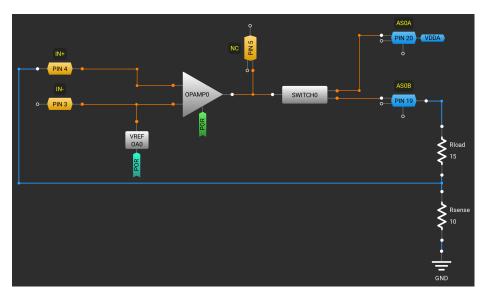

| Application: Current Detection Through External Sense Resistor          | 58 |

| Application: Monitor Four Levels for One Analog Signal With One MS ACMP | 59 |

| Application: Monitor Four Separate Analog Signals With One MS ACMP      | 60 |

| Chapter 5 Communication Protocols                                       | 61 |

| echnique: Changing Your Design with I2C                                 | 62 |

| echnique: Creating an I2C command                                       | 63 |

| echnique: Using the Serial to Parallel Interface (SPI) Block            | 64 |

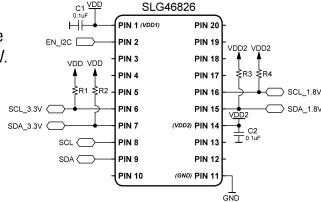

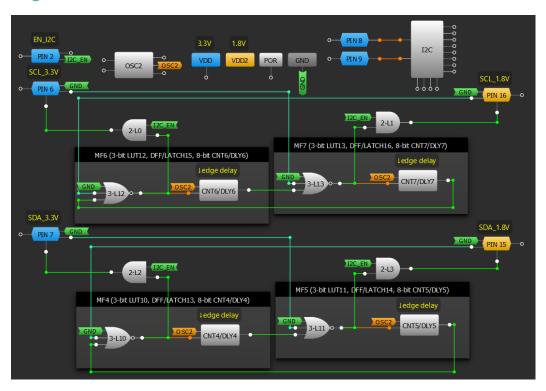

| echnique: Level Shifting                                                | 65 |

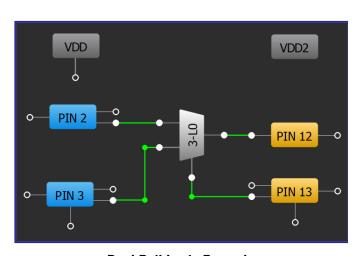

| echnique: Sending a Preset Number of Pulses                             | 66 |

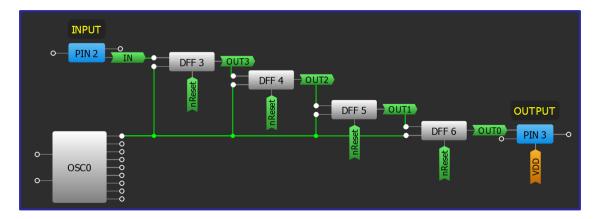

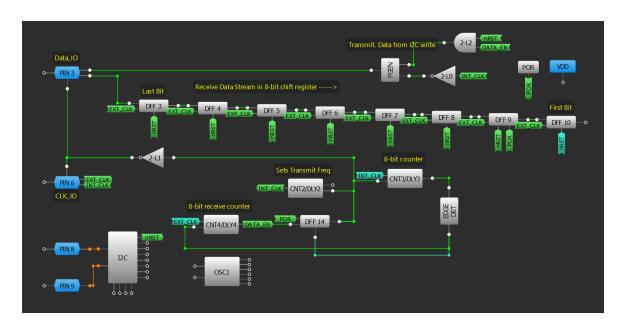

| echnique: Building a Shift Register                                     | 67 |

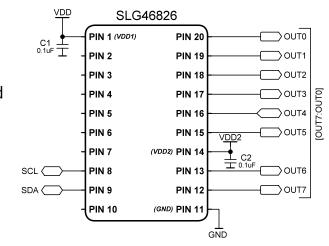

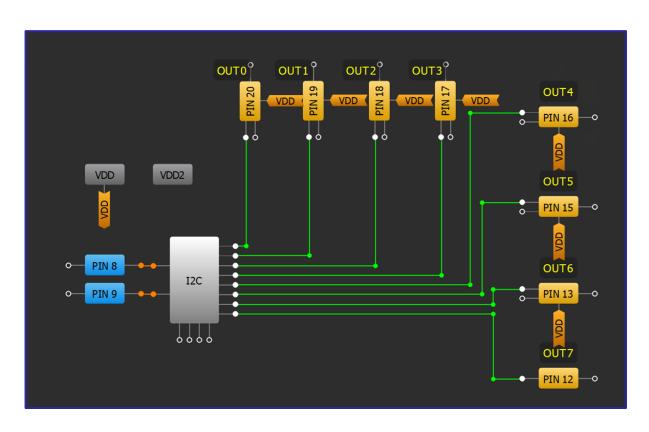

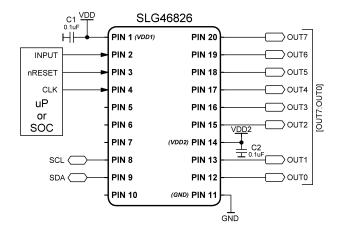

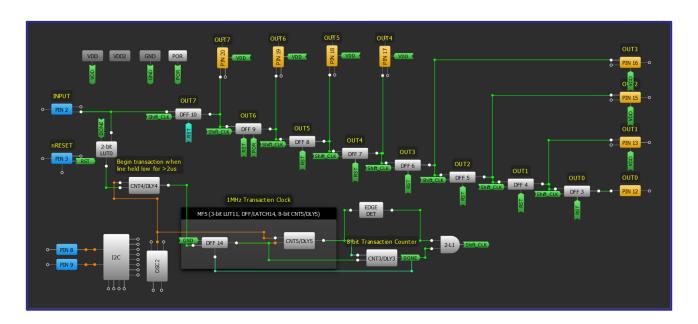

| Application: I2C GPIO Expansion                                         | 68 |

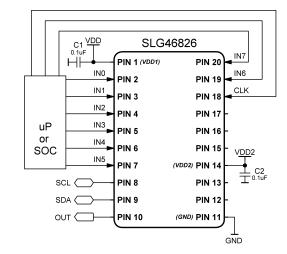

| Application: Serial to Parallel (External Clock)                        | 69 |

| Application: Serial to Parallel (Internal Clock)                        | 70 |

| Application: Parallel to Serial                                         | 71 |

| Application: Bi-Directional Communication (Transmit First)              | 72 |

| Application: Bi-Directional Communication (Receive First)               | 73 |

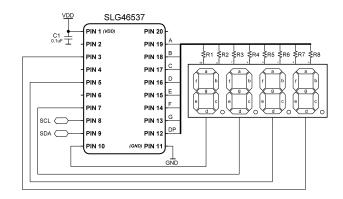

| Application: 7-Segment Display Using ASM and I2C                        | 74 |

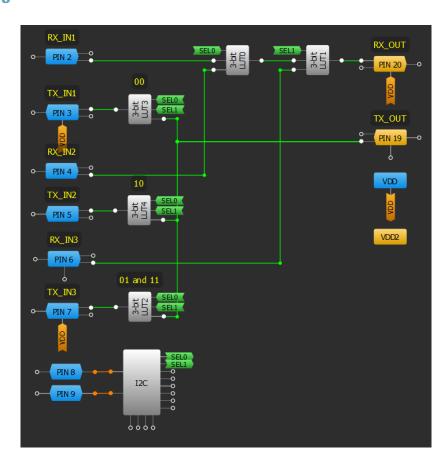

| Application: Communication MUX Using I2C                                | 75 |

| Application: I2C Level Shifter                                          | 76 |

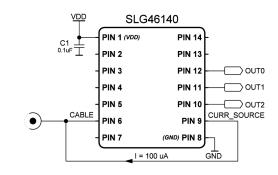

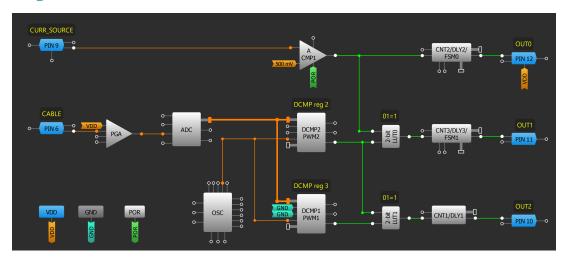

| Application: Connection Detect                                          | 77 |

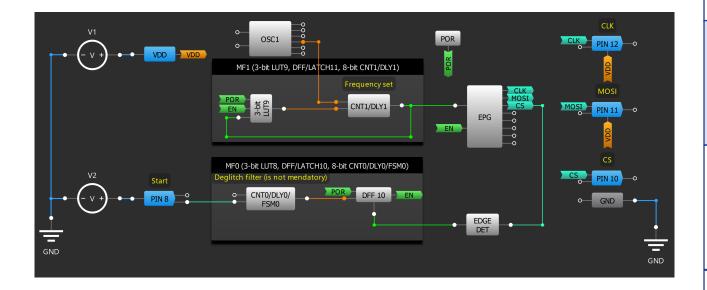

| Application: Custom Pattern Generator                                   | 78 |

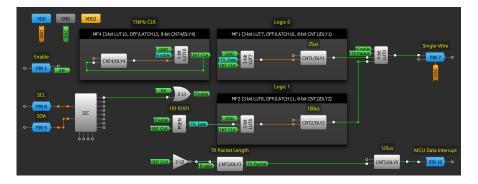

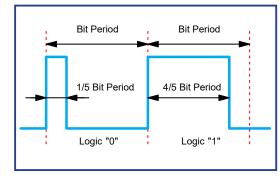

| echnique: Sending Serial Protocols Using Duty Cycle Detection           | 79 |

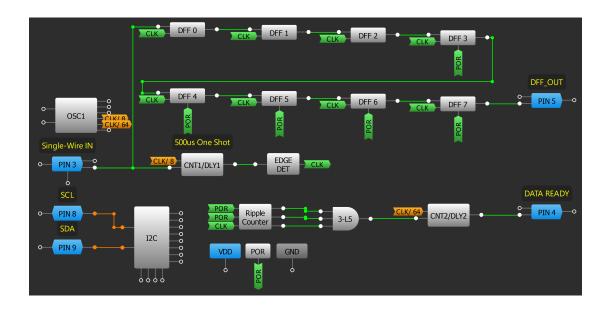

| echnique: Reading Serial Protocols with a Shift Register                | 80 |

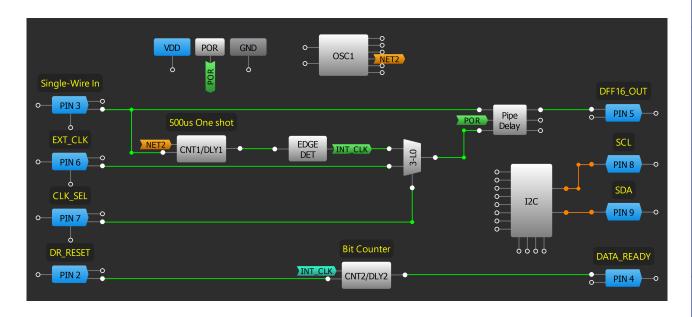

| echnique: Reading Serial Protocols with a Pipe Delay                    | 81 |

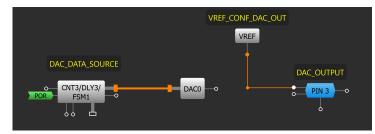

| echnique: Using the Digital-to-Analog Converter (DAC)                   | 82 |

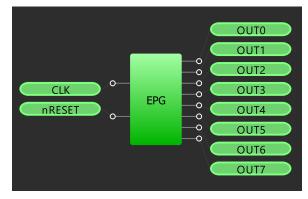

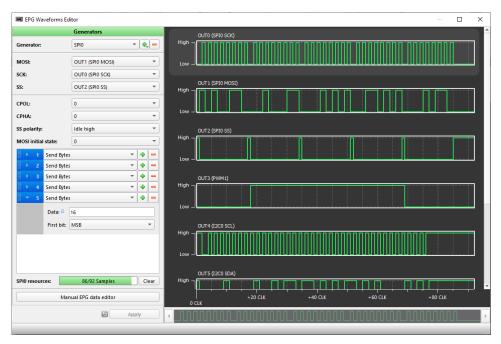

| echnique: EPG                                                           | 83 |

| Application: I2C Master Read Command with ACK Check and Data Comparison | 84 |

| Application: I2C Master Write Command with ACK Check                    | 85 |

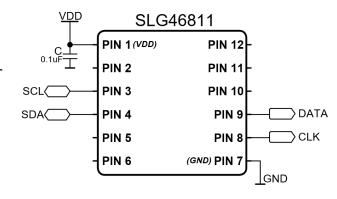

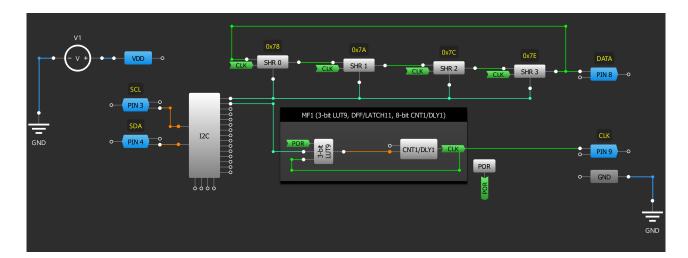

| Application: I2C Programable Pattern Generator Using Shift Registers    | 86 |

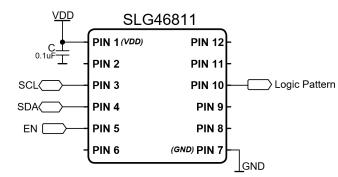

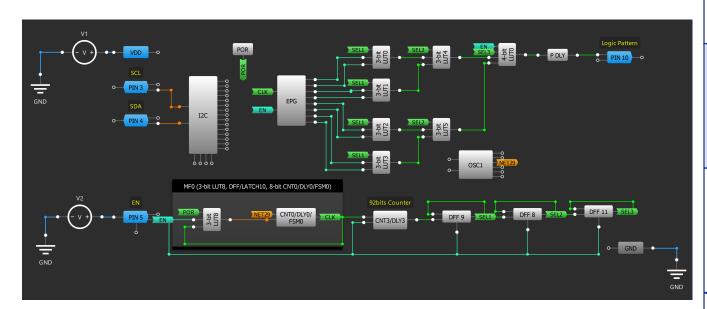

| Application: Long Length Pattern Using EPG                              | 87 |

| Application: Basic SPI Master                                           | 88 |

| Chapter 6 Pulse-based Control                                           | 89 |

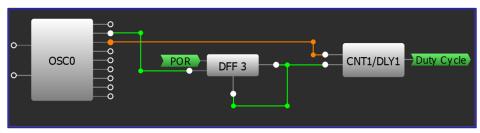

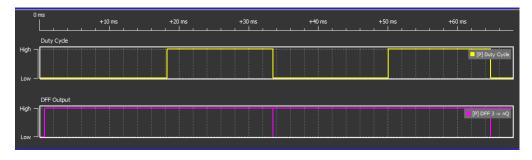

| echnique: Setting a Constant Duty Cycle                                 | 90 |

|                                                                         | 50 |

5

9. Advanced

RENESAS

#### The GreenPAK Cookbook

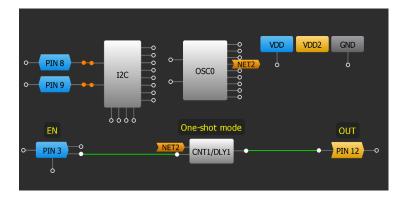

| Technique: One Shot Implementation                                                   | 91  |

|--------------------------------------------------------------------------------------|-----|

| Application: Constant Current LED Driver                                             | 92  |

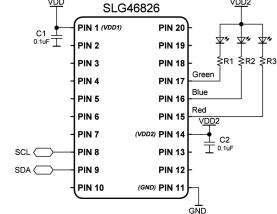

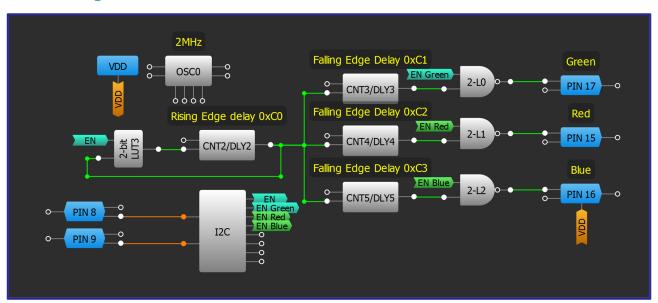

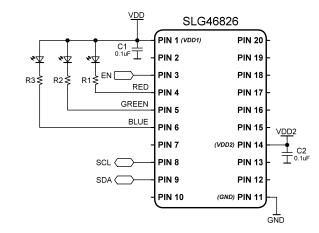

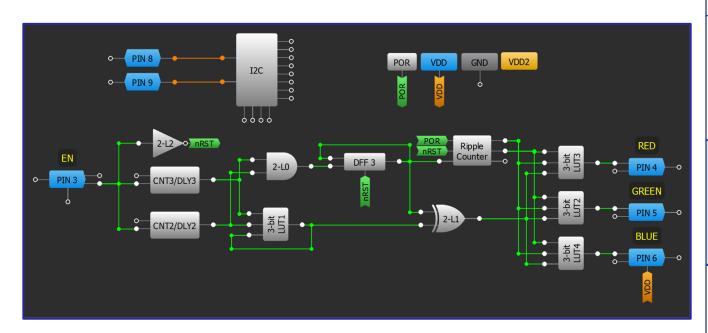

| Application: RGB LED Control via I2C                                                 | 93  |

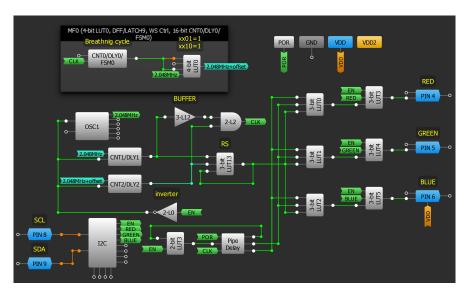

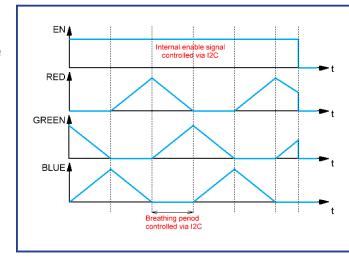

| Technique: Creating a Breathing LED Pattern                                          | 94  |

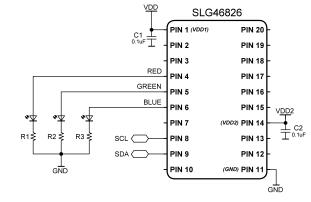

| Application: Breathing RGB LED                                                       | 95  |

| Application: Breathing RGB LED Control with I2C                                      | 96  |

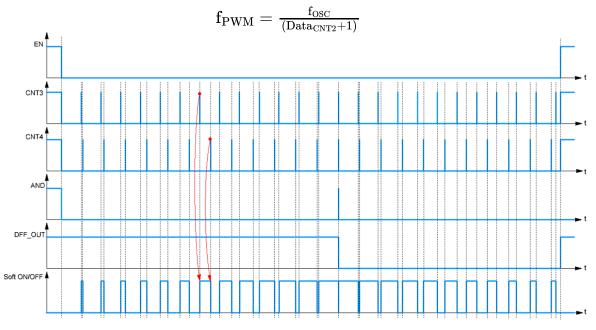

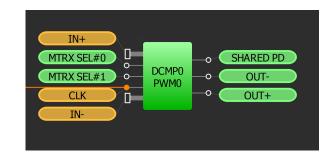

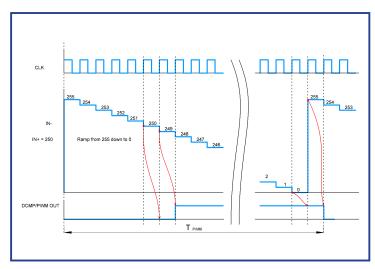

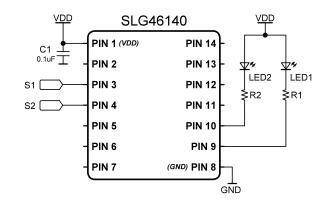

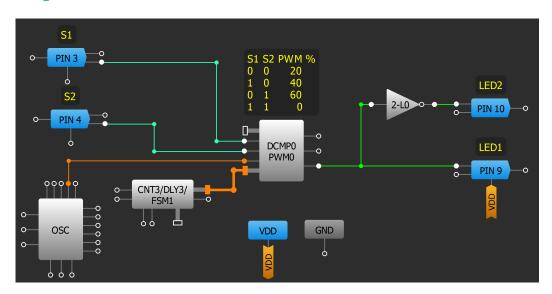

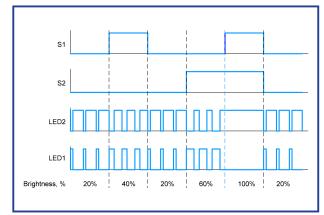

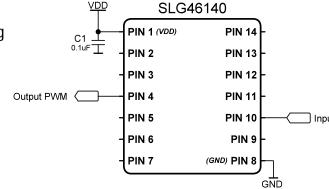

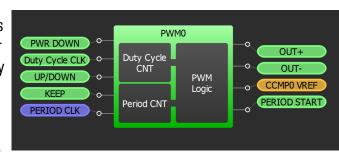

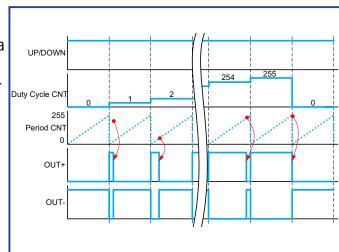

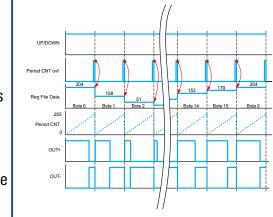

| Technique: Using DCMP/PWM Macrocell in PWM Mode                                      | 97  |

| Application: PWM Selection                                                           | 98  |

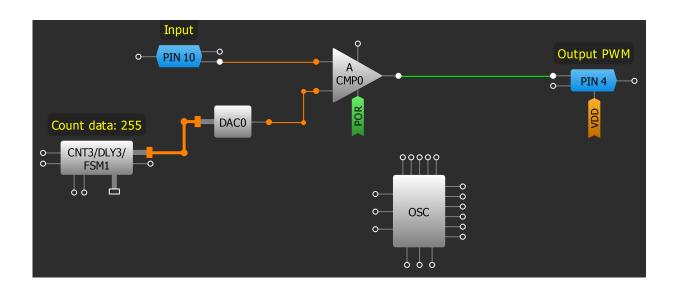

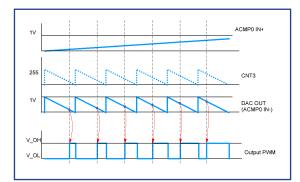

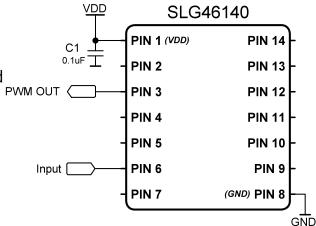

| Application: PWM Generator Using ACMP and DAC                                        | 99  |

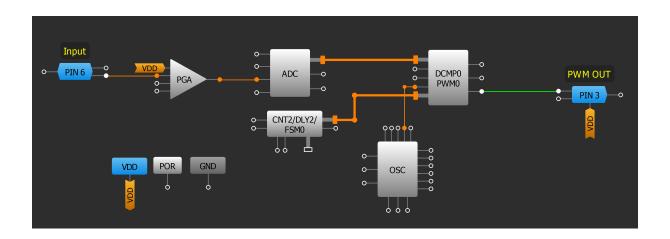

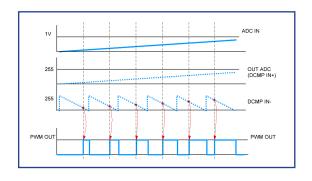

| Application: PWM Generator Using ADC                                                 | 100 |

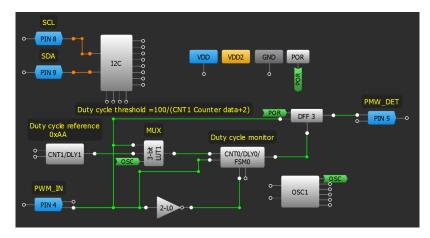

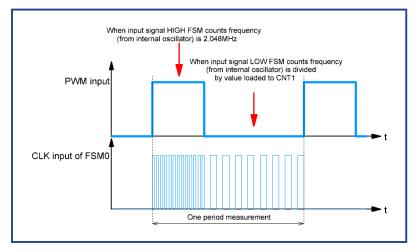

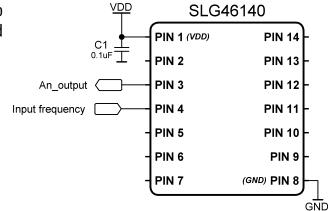

| Technique: Duty Cycle Detection                                                      | 101 |

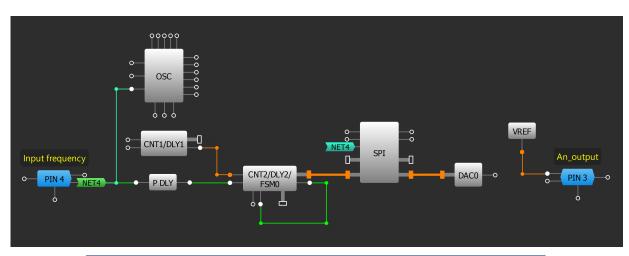

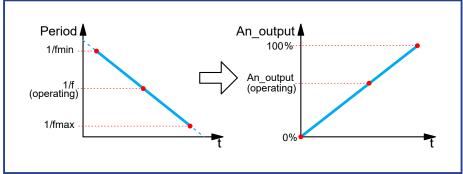

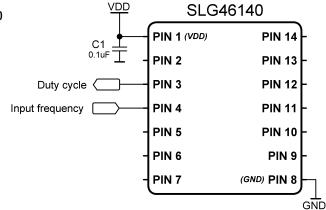

| Application: Frequency to Analog Voltage Converter                                   | 102 |

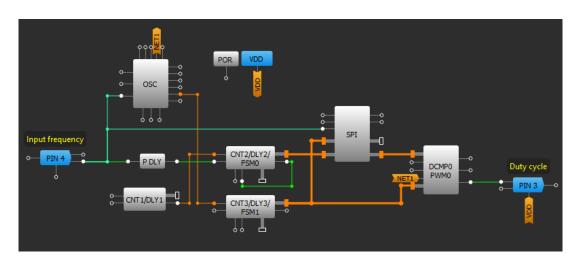

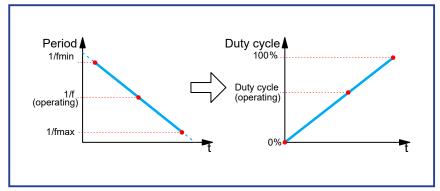

| Application: Frequency to Duty Cycle Converter                                       | 103 |

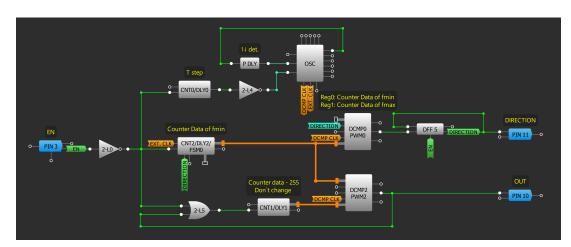

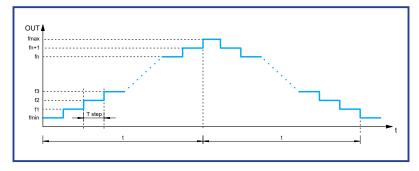

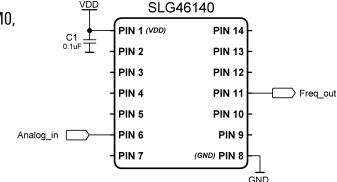

| Application: Linear Frequency Modulation                                             | 104 |

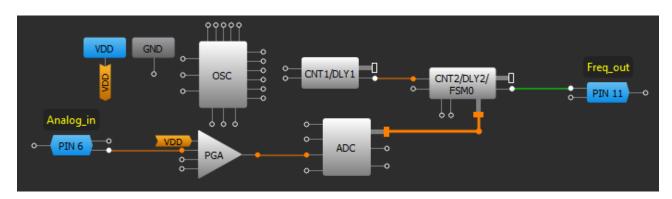

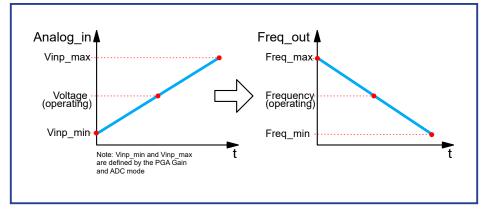

| Application: Voltage-Controlled Oscillator                                           | 105 |

| Chapter 7 Power Management                                                           | 106 |

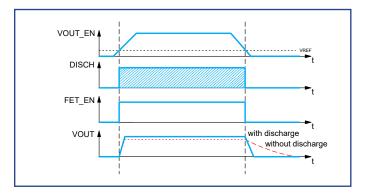

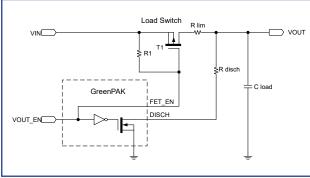

| Technique: Output Discharge                                                          | 107 |

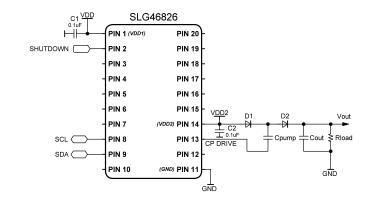

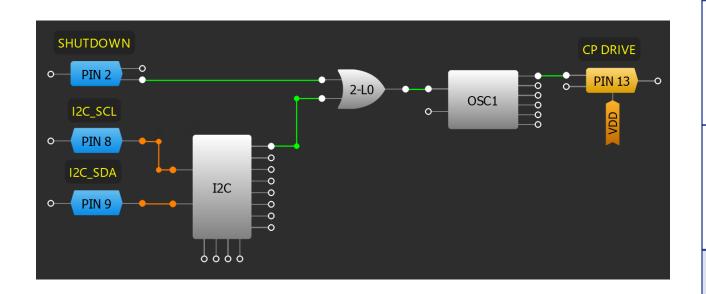

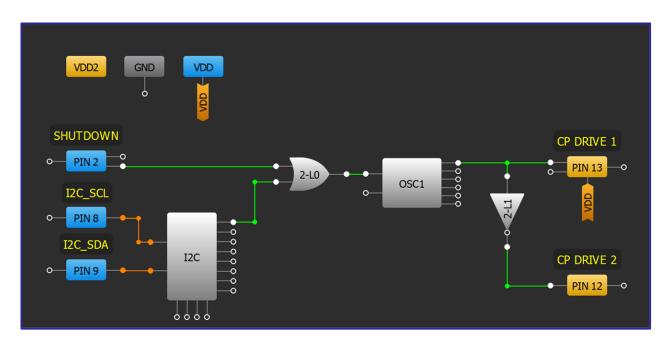

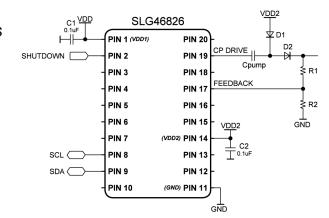

| Application: Charge Pump                                                             | 108 |

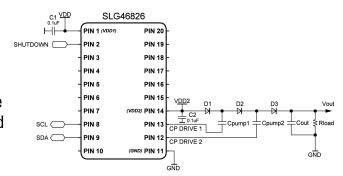

| Application: Two-Stage Charge Pump                                                   | 109 |

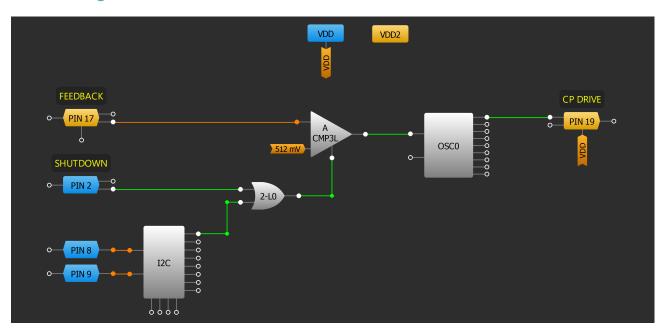

| Application: Charge Pump with Output Regulation                                      | 110 |

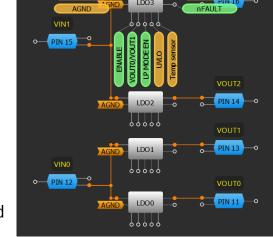

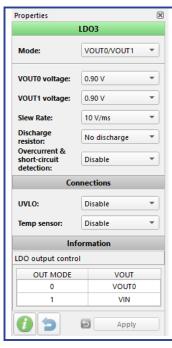

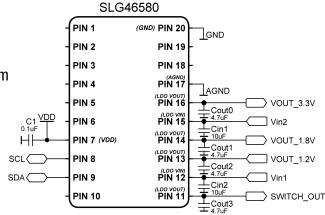

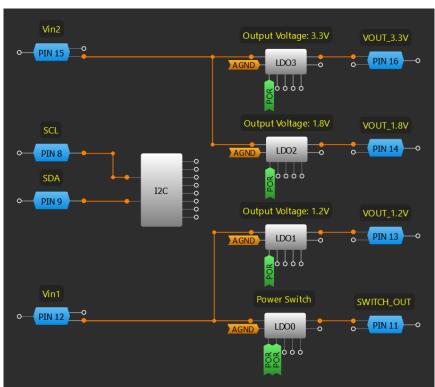

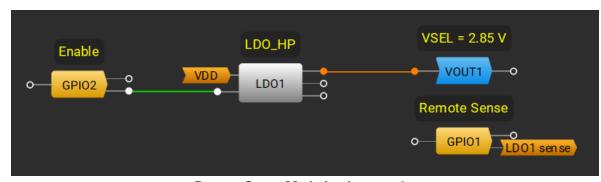

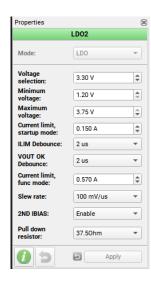

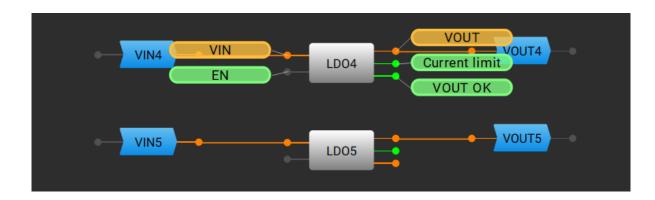

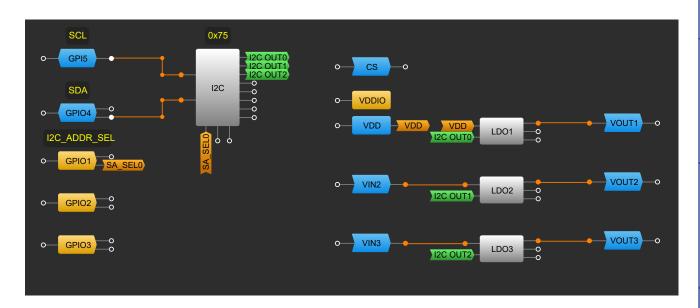

| Technique: Using the LDO Regulators                                                  | 111 |

| Application: Flexible Power Island                                                   | 112 |

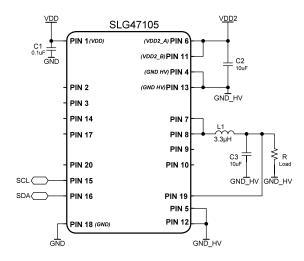

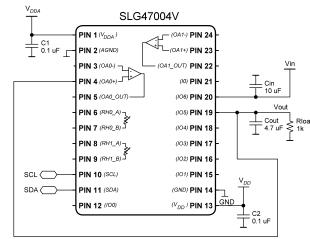

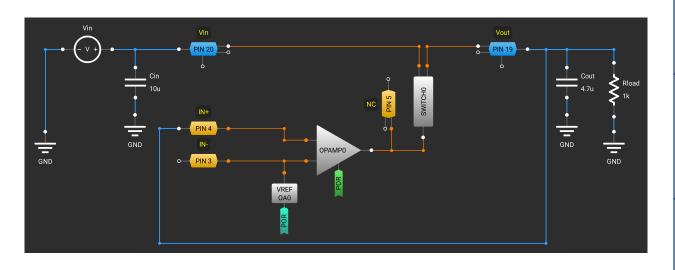

| Application: Boost (Step-up) Converter                                               | 113 |

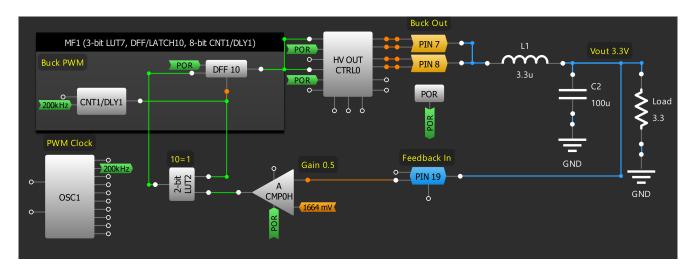

| Application: Buck (Step-down) Converter                                              | 114 |

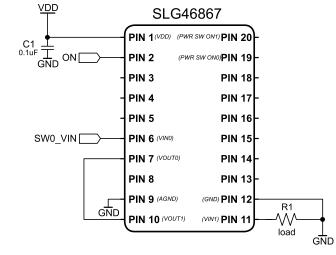

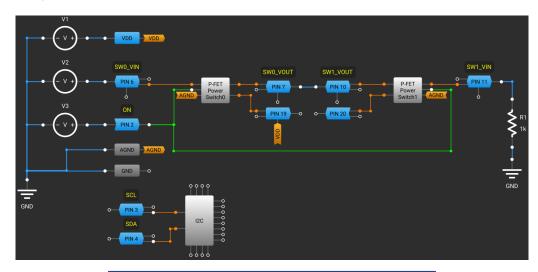

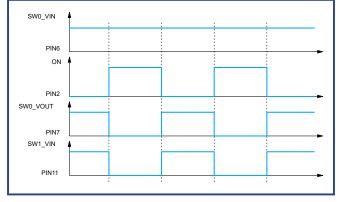

| Application: Back-to-Back Reverse Current Blocking                                   | 115 |

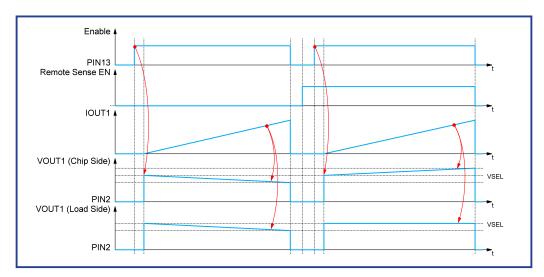

| Technique: Remote Sense Functionality                                                | 116 |

| Technique: LDO Explained                                                             | 117 |

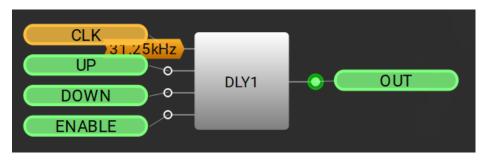

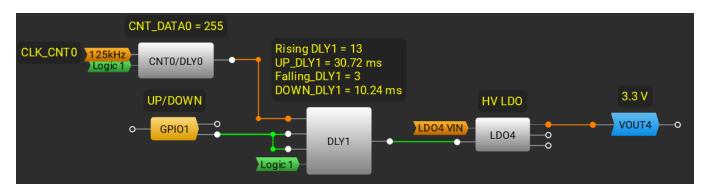

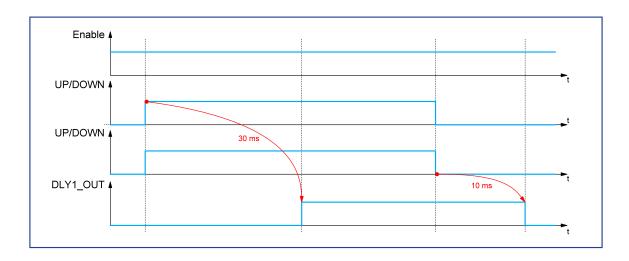

| Technique: Delay Macrocells                                                          | 118 |

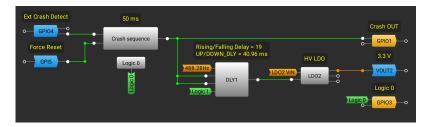

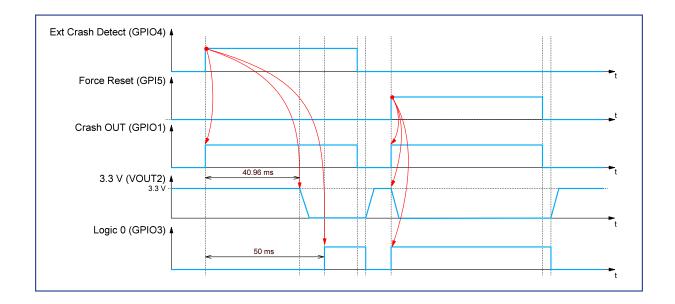

| Technique: Crash Sequence Block                                                      | 119 |

| Technique: GPIOs Features                                                            | 120 |

| Technique: Protection Features                                                       | 121 |

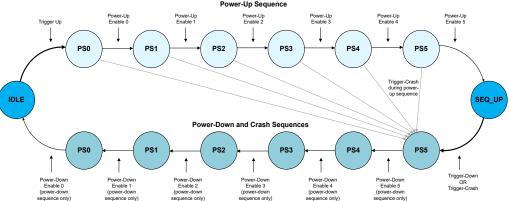

| Technique: Power Sequencer Explained                                                 | 122 |

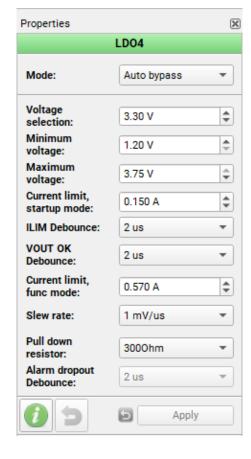

| Technique: SLG51002 HC LDOs Auto Bypass Mode Explained                               | 123 |

| Technique: SLG51002, SLG51003 I2C Control Code Selection                             | 124 |

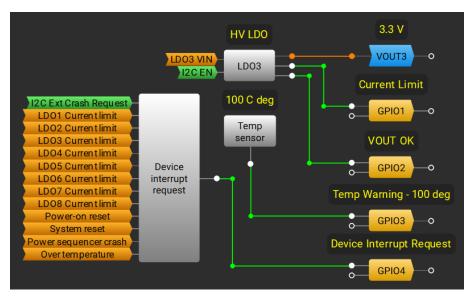

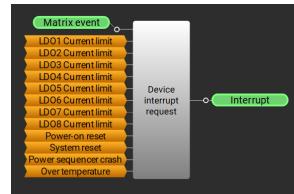

| Technique: SLG5100x Device Interrupt Request Block                                   | 125 |

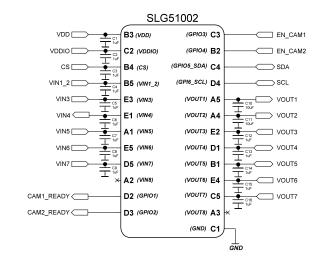

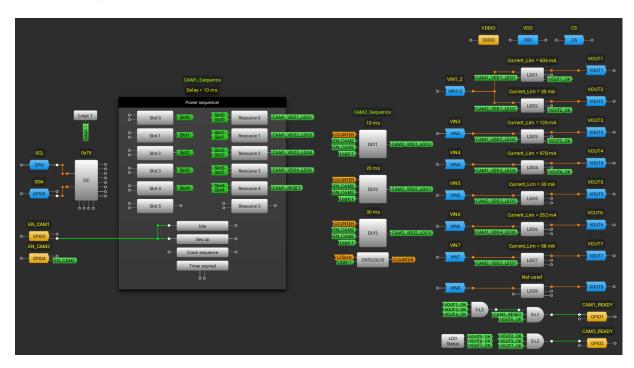

| Application: Scenario of Two Independent Sequences Using the SLG51002                | 126 |

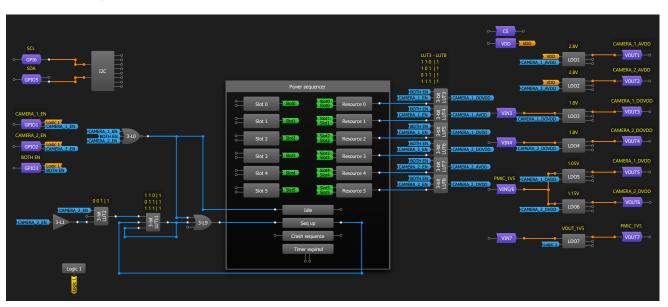

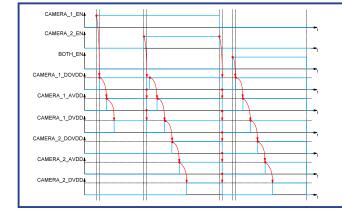

| Application: Powering Two Cameras with Sequencer and Two Scenarios for the SLG51000C | 127 |

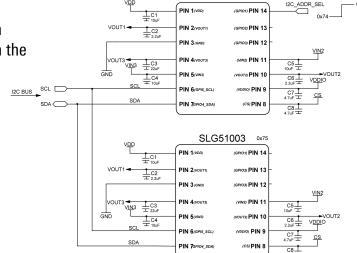

| Application: SLG51002/3 I2C Address Configuration without                            | 128 |

| Reprogramming                                                                        | 128 |

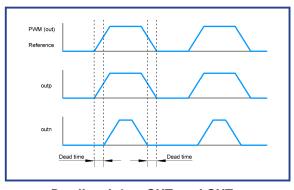

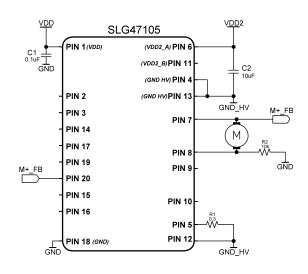

| Chapter 8 Motor Control                                                              | 129 |

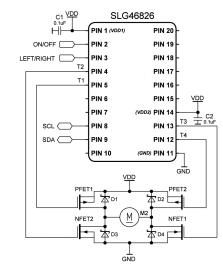

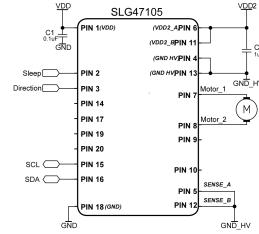

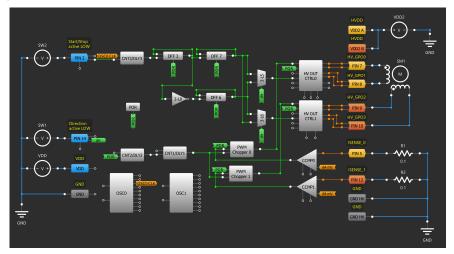

| Application: H-Bridge Control                                                        | 130 |

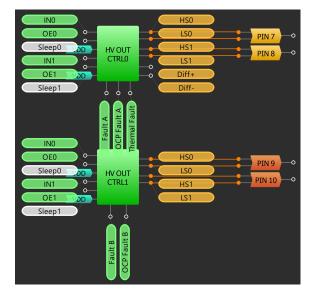

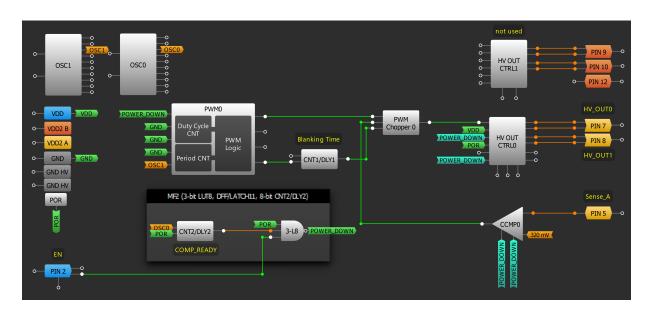

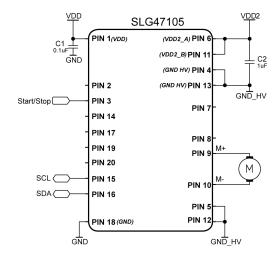

| Technique: Using the HV OUT CTRL Blocks                                              | 131 |

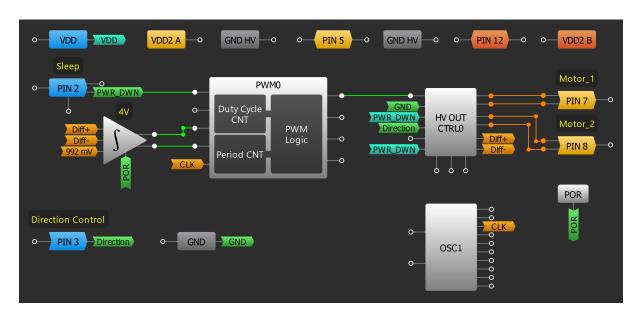

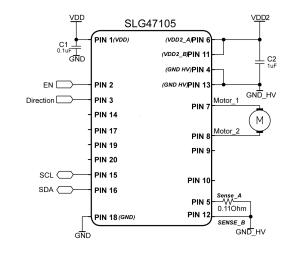

| Technique: Using the SLG47105 PWM Blocks in Regular Mode                             | 132 |

| Technique: Using the SLG47105 PWM Blocks in Preset Registers Mode                    | 133 |

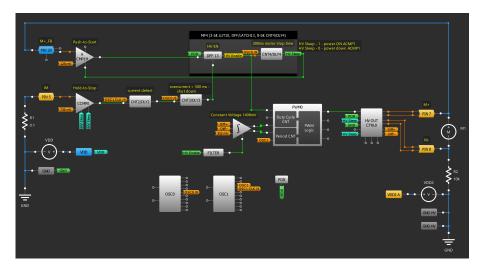

| Application: Constant Voltage Brushed DC Motor Driver                                | 134 |

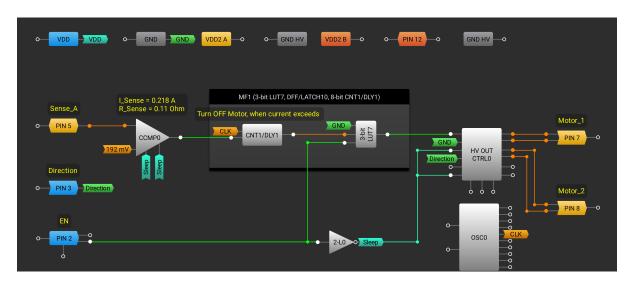

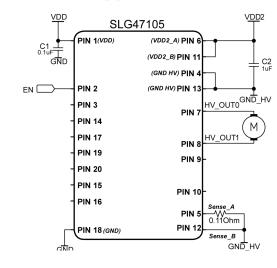

| Application: Constant Current Brushed DC Motor Driver                                | 135 |

#### The GreenPAK Cookbook

| Application: Constant Current Using the PWM Chopper           | 136 |

|---------------------------------------------------------------|-----|

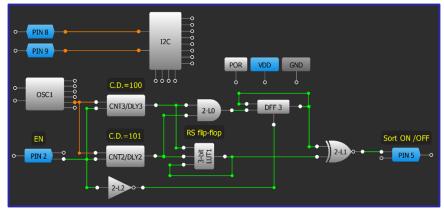

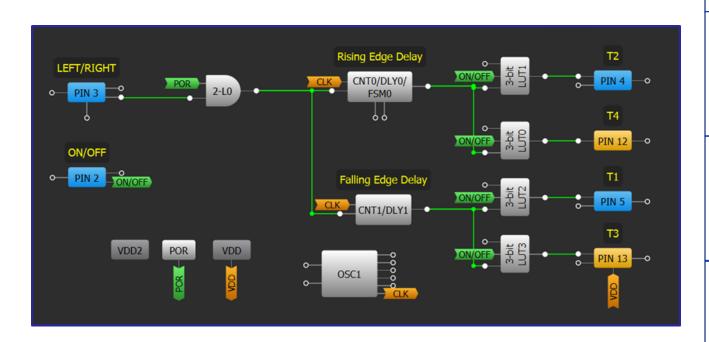

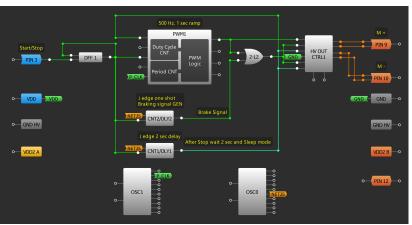

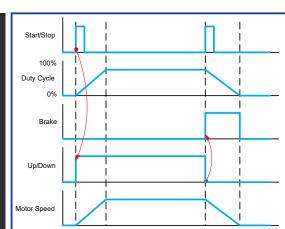

| Application: Unidirectional DC Motor Control with Soft ON/OFF | 137 |

| Application: Push-to-Start/Hold-to-Stop                       | 138 |

| Application: Bipolar Stepper Motor Driver                     | 139 |

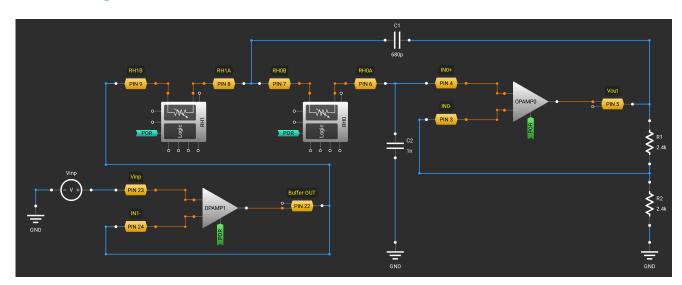

| Chapter 9 Advanced Analog Features                            | 140 |

| Application: Adjustable Active Filter Using OpAmp             | 141 |

| Application: Adjustable Inverting OpAmp                       | 142 |

| Application: Adjustable Non-Inverting Op Amp                  | 143 |

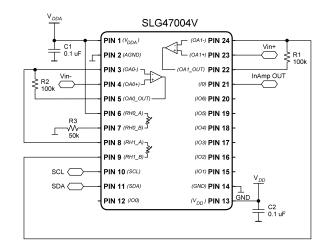

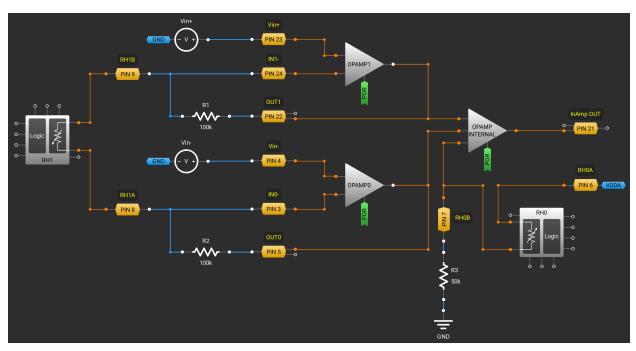

| Application: Instrumentation Amplifier                        | 144 |

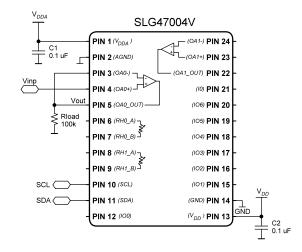

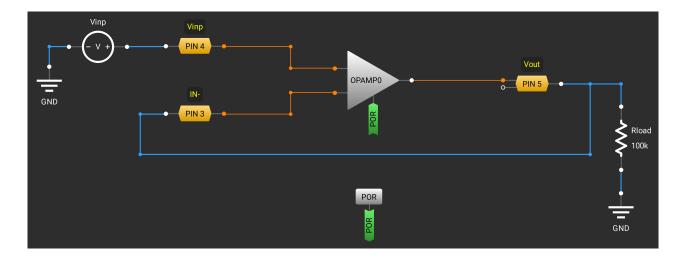

| Application: Voltage Follower Using OpAmp                     | 145 |

| Application: Current Sink Using OpAmp and N-channel FET       | 146 |

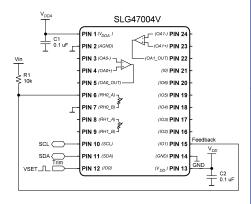

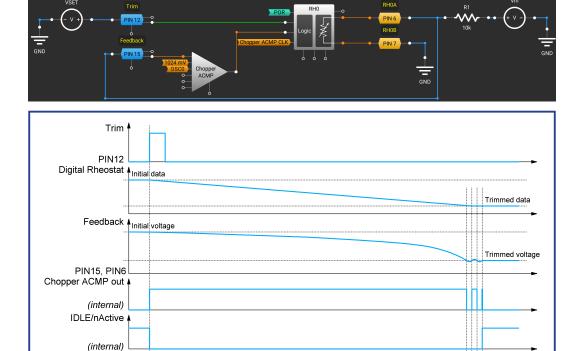

| Application: Auto-Trim                                        | 147 |

| Application: Current Source Using OpAmp and P-channel FET     | 148 |

| Application: Voltage Regulator Using OpAmp                    | 149 |

| Technique: Using Chopper ACMP with Digital Rheostats          | 150 |

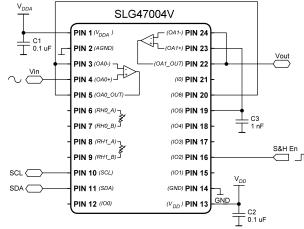

| Application: Sample and Hold Circuit                          | 151 |

| Application: Finding Maximum Point of Input Voltage           | 152 |

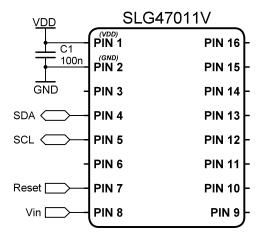

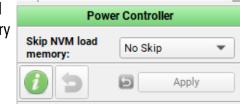

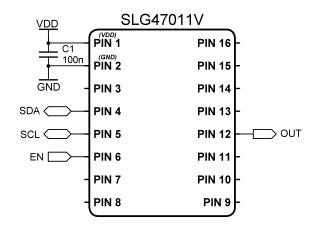

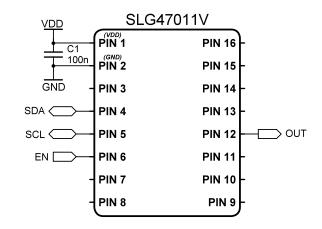

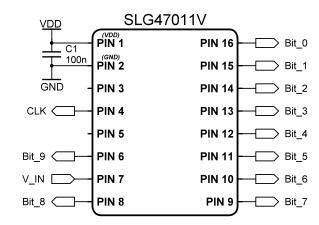

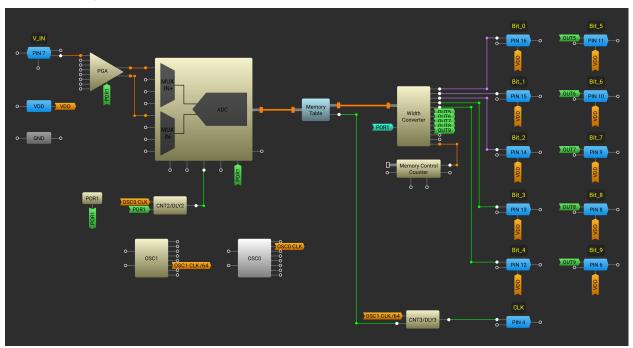

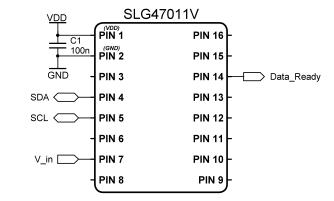

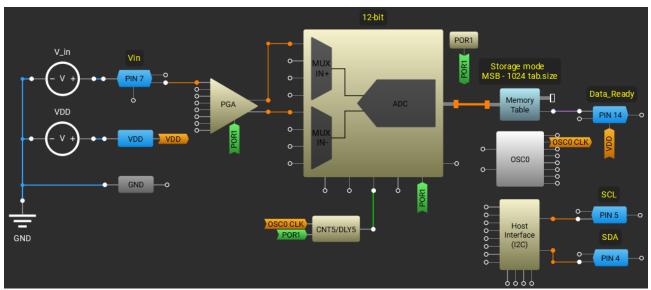

| Technique: Using Power Controller in the SLG47011             | 153 |

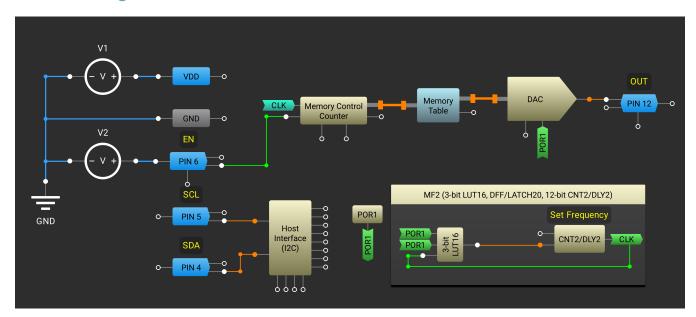

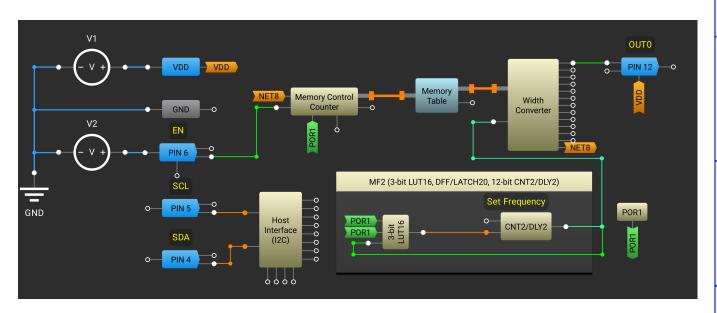

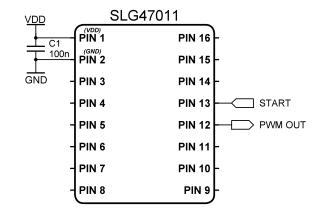

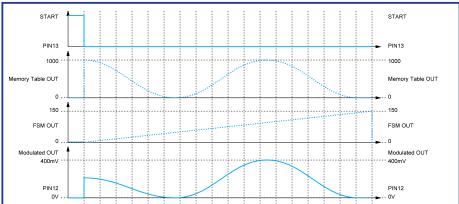

| Application: Waveform Generator Using Memory Table            | 154 |

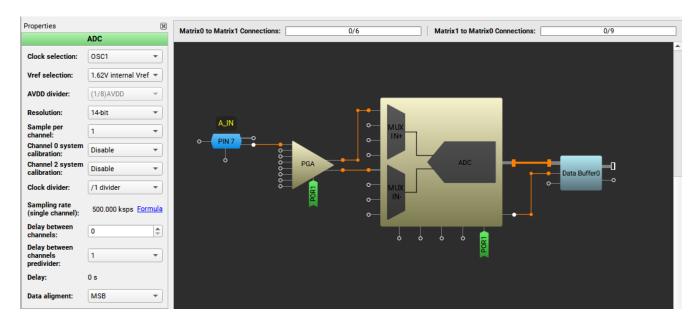

| Technique: ADC Calibration Procedure                          | 155 |

| Application: Signal Generator Using Memory Table              | 156 |

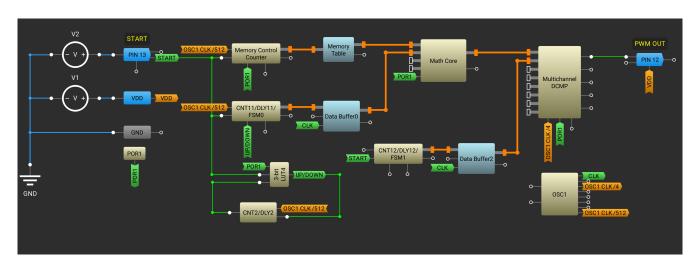

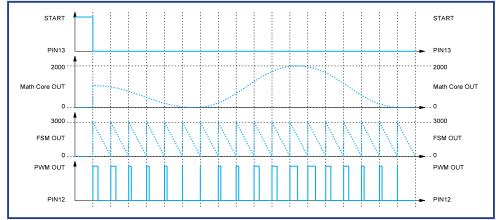

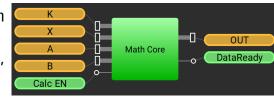

| Application: Signal Modulation Using MathCore (PWM)           | 157 |

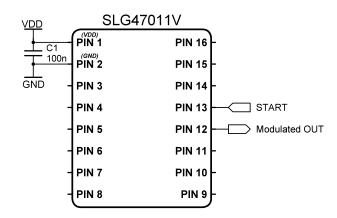

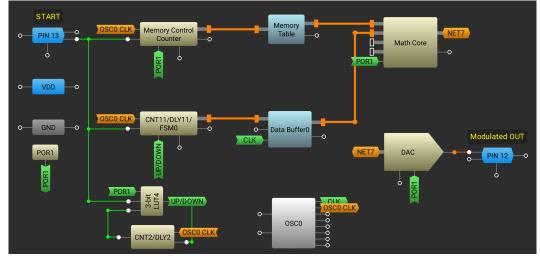

| Application: Signal Modulation Using MathCore                 | 158 |

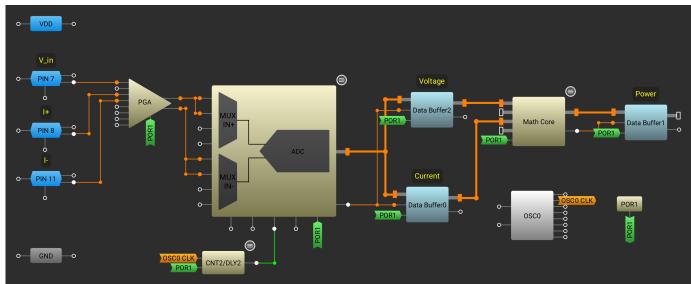

| Application: DC Power Measurement                             | 159 |

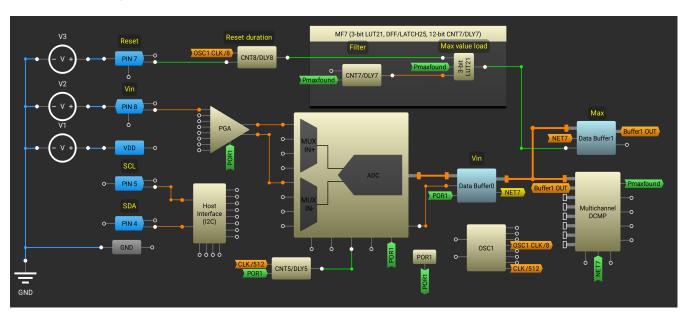

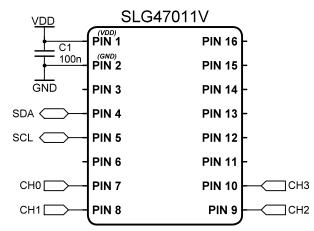

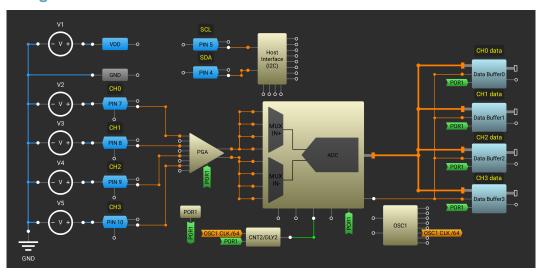

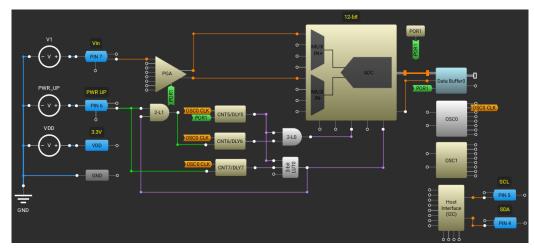

| Application: 4 Channel ADC Measurement with Data Buffer Table | 160 |

| Application: Analog to Parallel Converter                     | 161 |

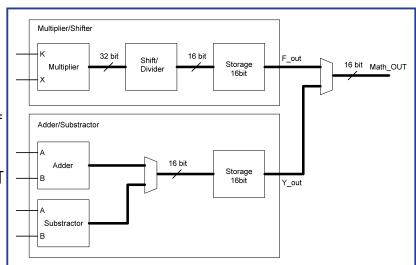

| Technique: MathCore Usage                                     | 162 |

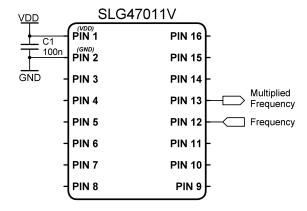

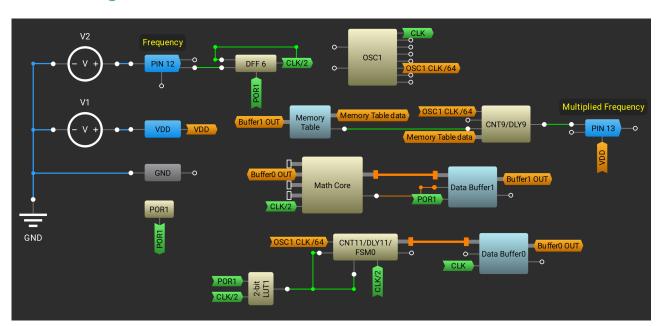

| Application: Frequency Multiplier                             | 163 |

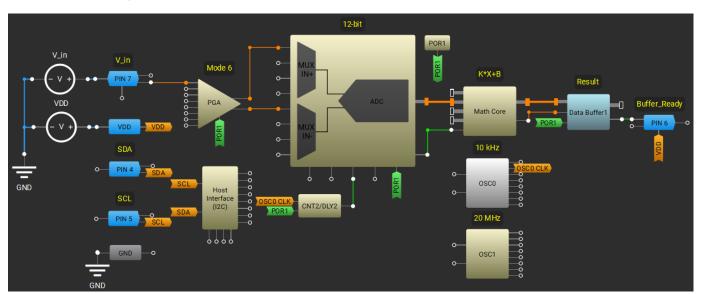

| Application: Arithmetic Operation f(x)=kx+b                   | 164 |

| Application: ADC with Memory Table in Storage Mode            | 165 |

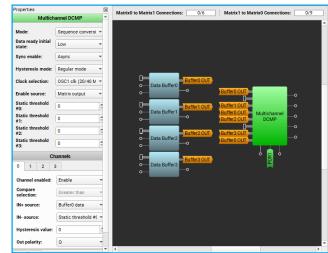

| Technique: Multichannel DCMP                                  | 166 |

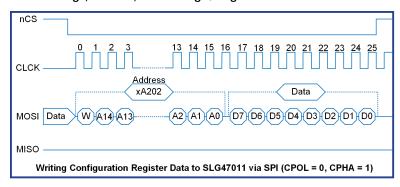

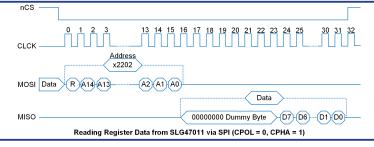

| Technique: Reading/Writing Data via SPI                       | 167 |

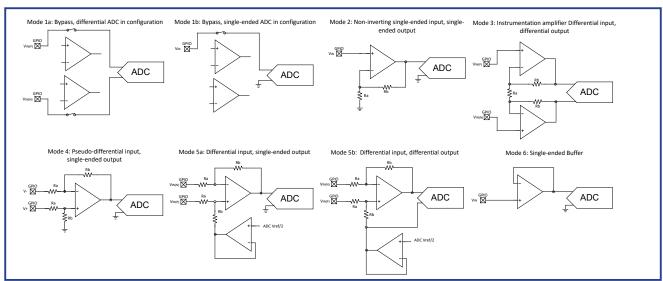

| Technique: Different Modes in PGA                             | 168 |

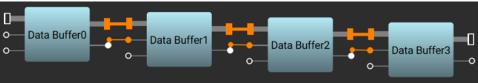

| Technique: Using Data Buffer                                  | 169 |

| Application: ADC ON/OFF Function                              | 170 |

| Technique: ADC Delay Between Channels                         | 171 |

| Revision History                                              | 172 |

| ·                                                             |     |

1.Basic Blocks & Functions

2. Sequential Logic

3. Signal Conditioning

4. Safety Features

5. Communication Protocols

6. Pulse-based Control

7. Power Management

8. Motor Control

9. Advanced Analog Features

# **Chapter 1 Basic Blocks and Functions**

This chapter introduces many of the basic building blocks found in the GreenPAK that will be used throughout the Cookbook. It will also present a few simple combinational logic designs that utilize look-up tables (LUTs).

### 2. Sequential Logic

1.Basic Blocks Functions

3. Signal Conditioning

4. Safety Features

Communication Protocols

9. Advanced Analog Features

#### **Technique: Learning More About a Macrocell**

This technique works with any version of the GreenPAK Designer.

While using the GreenPAK Designer, you may wish to learn more about a specific macrocell. To do so:

Info Button

- 1. Select the macrocell in the GreenPAK Designer.

- 2. Click Properties.

- 3. In the Properties window, in the bottom-left, click Info Button.

#### **Overview: Digital Macrocells**

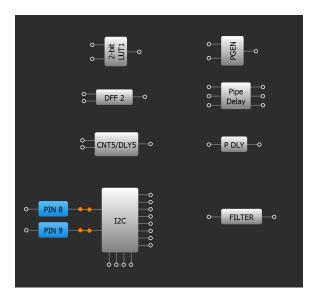

Digital macrocells are the basic functional components of any GreenPAK. They include:

Common Digital Macrocells:

- Look-Up Table (LUT)

- D Flip-Flop (DFF)/Latch

- Counter/Delay (CNT/DLY)

#### Communication:

- I2C (many devices)

- SPI (select devices)

#### Less Common:

- Pattern Generator (PGEN)

- Pipe Delay

- Programmable delay (PDLY)

- Filter/Edge Detector

**Digital Macrocells**

Many components in the GreenPAK Designer can be configured to be one of multiple types of macrocells. This is indicated in the name of the digital macrocell. For example, 2-bit LUTO/DFF/LATCH0 can be, as the name implies, a LUT, DFF, or LATCH. The selection of macrocell type is configured using the Type option in the Properties window.

# 2. Sequential Logic

Basic Blocks & Functions

3. Signal Conditioning

4. Safety Features

Communication Protocols

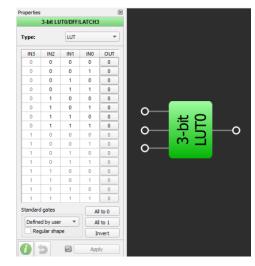

#### **Technique: Configuring Standard Logic with LUT Macrocells**

This technique works with any GreenPAK.

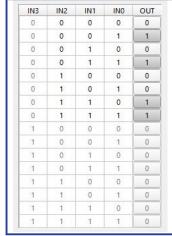

Look-up tables are used in the GreenPAK Designer to configure any digital logic for a two, three, or four input, single output logic macrocell. The logic configuration is edited in the Properties window.

Most of the logic implemented in GreenPAK designs is standardized logic, such as MUX, AND, OR, and others. To expedite these common configurations, the Properties window has a Standard gates option that automatically convert the logic table into a standard gate configuration. If the Regular shape option is left unchecked, the LUT shape will change to the standardized gate symbol.

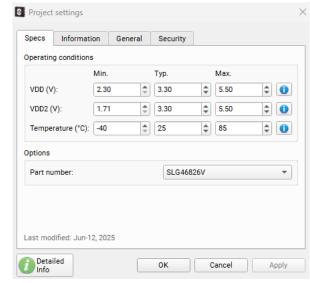

Config for 3-bit LUTO

#### **Overview: Oscillators**

GreenPAK ICs contain at least two oscillators. Many GreenPAKs, such as the SLG46826, have three oscillators. The most common, non-divided frequencies of the oscillators within GreenPAK are:

- 2 KHz low speed, low power oscillator

- 2 MHz medium speed

- 2 5MHz high speed

Each oscillator has several outputs, each with several pre-dividers to allow flexibility in clocking. To save power, Auto power-on allows you to turn off the oscillator when the clock is not needed.

More information about oscillators can be found by using the Information button when the component is selected.

**Oscillators**

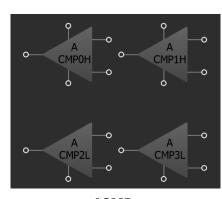

#### **Overview: Analog Comparators**

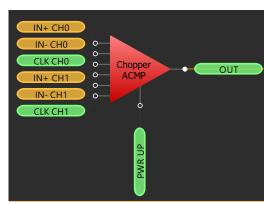

Almost every GreenPAK is equipped with two or more analog comparators [ACMPs], each with two input sources: IN+ and IN-. The input source of each ACMP is configured in the Properties window.

More information about analog comparators can be found by using the Information button when the component is selected.

**ACMPs**

10

#### Overview: I/Os

I/Os within GreenPAK are very flexible. The I/O capabilities vary from pin to pin and part to part, so a design should be mapped to the necessary pin configuration before choosing a specific GreenPAK.

Outputs can be configured to be a push-pull or an open-drain in either a NMOS or PMOS configuration. A scaling factor, such as 2x, indicates that the output strength is doubled.

Additionally, pull-up and pull-down resistor options of 10 k $\Omega$ , 100 k $\Omega$ , and 1 M $\Omega$  are available on output pins.

Multiple input options are available as well, such as Digital-In, Digital-In with Schmitt trigger, Low Voltage Digital-In and Analog-In. Analog-in is used as an input to an ACMP.

# Push-pull (1x) Open drain (1x) Push-pull (2x) Open drain (2x) Open drain (2x) Open drain (2x) Open drain (2x)

Typical I/O Structure

#### **Overview: Interconnections**

The GreenPAK Designer makes it easy to create interconnections. The system will guide you which connections you can make. When you click on any connection point, the system:

- Highlights all available connections in green

- Gives you a "rubber band" connection that you can stretch to any of these green connection

- This results in a green wire to show you interconnections you made.

Interconnections

#### Technique: Simulation and Emulation Using the GreenPAK Designer

Emulation is available for all GreenPAK parts and simulation is available for many GreenPAK ICs.

Toolbar

When developing a design, it is important to be able to quickly test the functionality. The GreenPAK Designer makes debugging effective and easy.

There are two ways to quickly check your design:

- 1. Simulation

- 2. Emulation.

Simulation simulates the operation of the circuit in conditions depictive of reality without the need of a physical IC. It should be kept in mind that simulation cannot provide all the nuances of a real-world system.

Emulation allows, with the presence of a demo board and the GreenPAK chip, to check the operation of your design directly in the hardware without permanently programming a part. Follow these steps to quickly make changes to the project and use your emulation to check your guesswork:

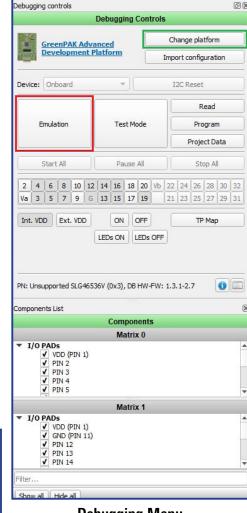

- 1. If the design is ready for debug, select the Debug button (boxed in red in the figure "Debugging Menu") to go to the emulation/simulation selection menu.

- 2. Next, select the platform with the help of which you want to check your design.

- 3. After selecting a platform, go to the debug menu, where further actions will be suggested depending upon the platform you choose.

- 4. If you need to change the platform, you can do this at any time by selecting Change platform.

**Debugging Menu**

I.Basic Blocks Functions

#### **Technique: GreenPAK Programming**

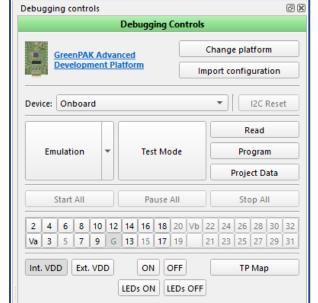

Debugging control is available for all GreenPAKs.

#### Toolbar in the GreenPAK Designer

When developing a design, it is important to be able to quickly test the functionality. The GreenPAK Designer makes debugging effective and easy:

#### **Change platform**

Select the type of hardware platform with the supported features.

#### **Import configuration**

Import user configuration of test points from other platforms.

#### **Device**

Allows the user to work with an external chip on a specified device address.

#### **I2C Reset**

Suppose I2C serial communication is established with the device. In that case, it is possible to reset the device to initial power-up conditions, including the configuration of all macrocells and all connections provided by the Connection Matrix. This is implemented by setting the register I2C reset bit to '1', which causes the device to re-enable the Power-On Reset (POR) sequence, including the reload of all register data from NVM.

#### **Emulation**

- Emulation of the current project will be loaded to the chip (but not programmed) and will be ready for a test on the hardware board.

- Emulation (sync). In addition to emulation, each change made in the project will be immediately loaded onto the chip.

#### **Test mode**

Test mode is used for connecting or disconnecting the chip's I/O pads to TP controls configured by the user. Also, the user can check a programmed chip using the test mode without emulation. To do this: turn on the test mode and internal VDD button. The test mode can work without power on the chip. The user will control the power manually.

#### Read

Read chip data using the hardware board.

#### **Program**

Program chip with the current project. For some chip models, a user can configure the programming process by using the following options:

- Program NVM (program the chip's NVM)

- Program EEPROM (program the chip's EEPROM)

#### **Project Data**

The table of NVM and EEPROM (available for specific chip revisions) bits.

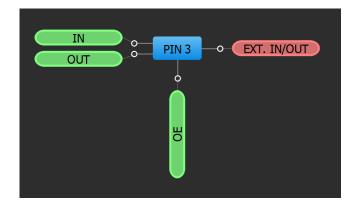

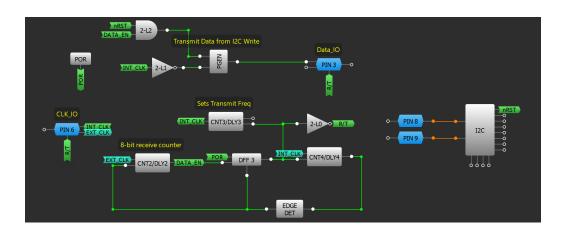

#### **Technique: OE Pin**

This technique can be used within any GreenPAK with OE pins.

Typically, GreenPAK IO is configured as an input or output. However, in most GreenPAKs, there are some pins with Output Enable (OE) selection allowing to dynamically change between a digital input and digital output. When the OE GPIO is set as a permanent input, the OE pin is set to ground, and if the GPIO is set as a permanent output, the OE pin is set to VDD. Setting the GPIO as a Digital input/output allows for this selection to be made in the matrix.

Setting the GPIO as a digital input/output allows for two-way communication. It also allows for the GPIO to be set to Hi-Z in addition to a logical HIGH and LOW.

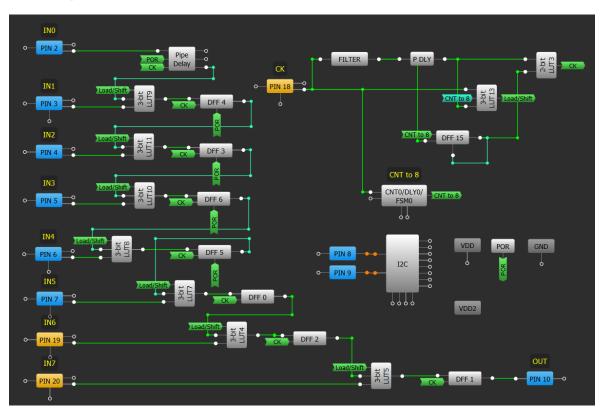

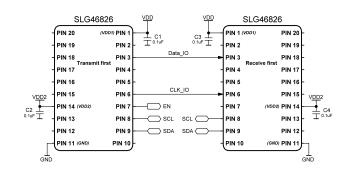

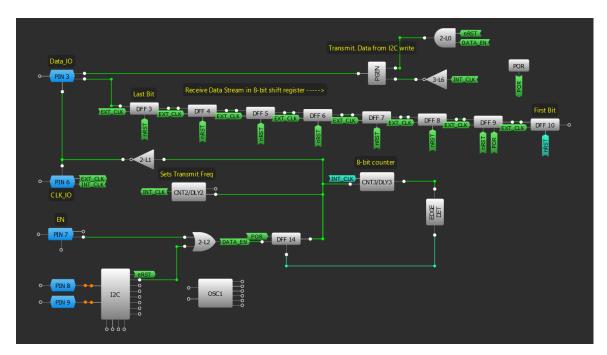

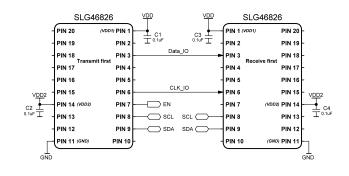

If the GPIO is used for two-way communication, it is important to implement a timing circuit for OE selection. In the example circuit below the OE pins of CLK\_IO and Data\_IO are switched from LOW to HIGH after CNT2 sees 8 clocks, consequently setting the OE pins as outputs to transmit the internal signals. After another 8 clocks the OE pins are reset low, setting them as inputs again to receive an external signal.

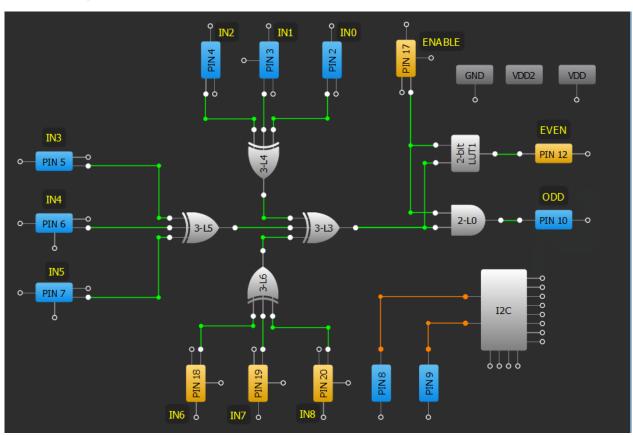

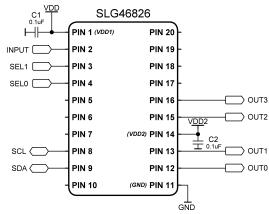

#### **Application: Parity Bit Generator**

Parity Bit Generators are used to check the integrity of a signal. It is the simplest implementation of a Cyclic Redundancy Check (CRC). Parity Bits are used prior to committing data to an MCU or other control unit to ensure the incoming data is not corrupted.

#### **Ingredients**

- Any GreenPAK

- No other components are needed

#### SLG46826 PIN 1 (VDD1) PIN 20 PIN 2 **PIN 19** INO [ PIN 3 IN1 ( **PIN 18** PIN 4 **PIN 17** □ ENABLE IN2 PIN 5 **PIN 16** IN3 PIN 6 **PIN 15** (VDD2) PIN 14 PIN 7 IN5 [ PIN 8 PIN 13 PIN 9 **PIN 10** (GND) PIN 11 ODD ( GND

#### **GreenPAK Diagram**

- Connect input pins using XOR gates using <u>Technique</u>: <u>Configuring Standard Logic w/ LUT Macrocells</u>. XOR gates are used to calculate the running sum of 1's.

- 2. Add logic for the ENABLE signal.

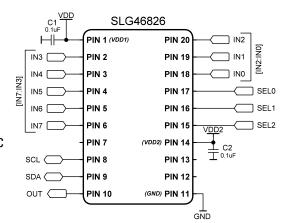

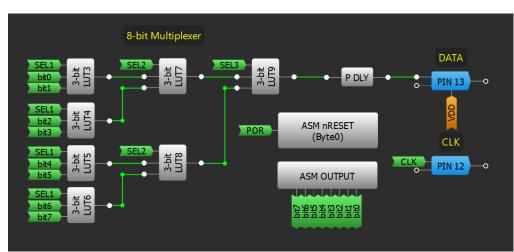

#### **Application: 8-bit Multiplexer**

A Multiplexer, or MUX, is used to select an output from multiple input signals. It is used in applications where several communication lines need to be sent across a single line. By using the GreenPAK as the MUX, the latency time in transmission can be in nanoseconds, compared to discrete logic IC's.

#### **Ingredients**

- Any GreenPAK

- No other components are needed

#### **GreenPAK Diagram**

- 1. Connect input pins to four LUTs configured as multiplexers using <u>Technique</u>: <u>Configuring Standard Logic w/ LUT Macrocells</u>. INx should connect to A or B, SELO should connect to S on all four MUXs.

- 2. Add second and third stage cascading multiplexer blocks to create the more significant SEL bits.

- 3. Add an output pin connected to the last-stage multiplexer.

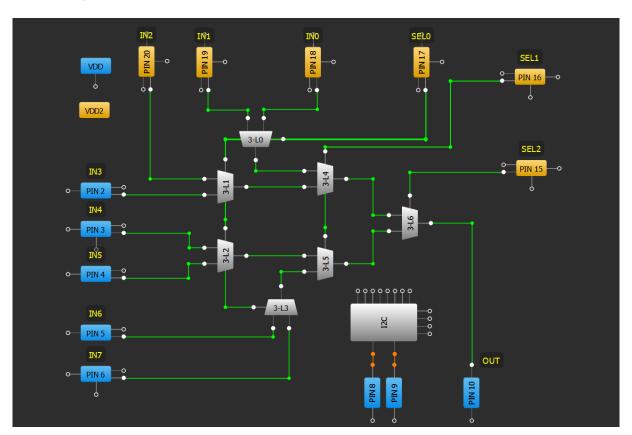

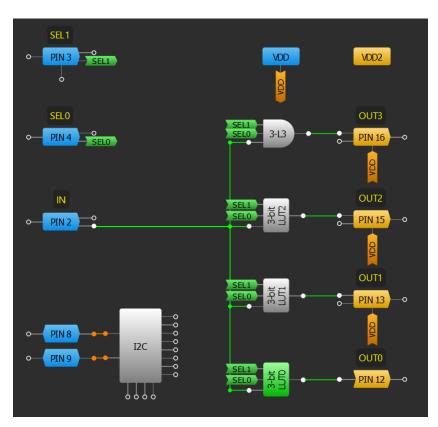

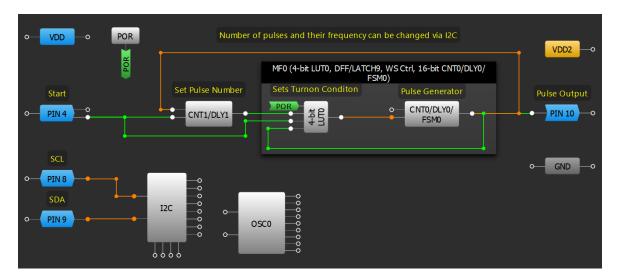

#### **Application: Demultiplexer**

A demultiplexer is used in applications where it is needed to send several different types of data across one line and is commonly found in communication systems.

#### **Ingredients**

- Any GreenPAK

- No other components are needed

#### **GreenPAK Diagram**

- 1. Configure input pins for a signal input (IN), two select lines (SELx), and four output pins (OUTx).

- 2. Configure the LUTs so each pass the signal from IN upon a specific logic input on the select lines. For example, 3-L3 will be HIGH when SELO, SEL1, and IN are HIGH.

#### 2. Sequential Logic

Basic Blocks

Functions

3. Signal Conditioning

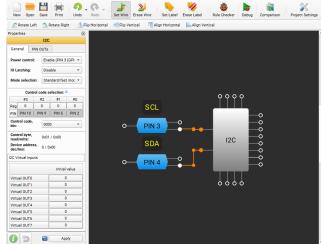

#### **Technique: Changing I2C Address**

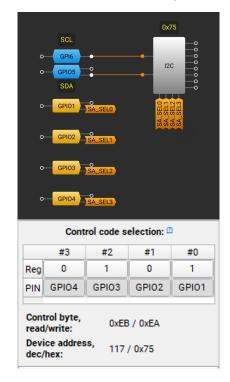

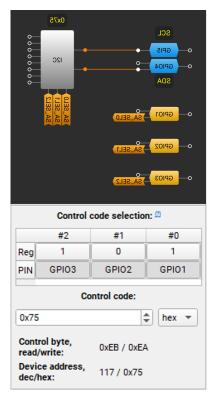

This technique describes the I2C address selection options for the SLG46855 device. The I2C Serial Communication Macrocell allows flexible configuration of its slave address (Control Code), providing two distinct methods for address selection:

#### 1. Register-Based Address Selection (Default)

By default, the 4-bit I2C Control Code is sourced directly from an internal configuration register. This method is typically used when the I2C slave device operates with a fixed, predefined address set during programming.

#### Advantages:

- Fixed and predictable address.

- Suitable for systems with a single I2C slave or where address conflicts are unlikely.

- Simpler hardware setup no additional pins required for address selection.

#### 2. External Pin-Based Address Selection

Alternatively, each bit of the I2C Control Code can be sourced from external GPIO pins (PIN 2, PIN 5, PIN 9, and PIN 10). When external addressing is enabled, the binary value of the address is determined by the voltage levels on these pins at runtime:

- PIN 2 Least Significant Bit (LSB)

- PIN 10 Most Significant Bit (MSB)

#### Advantages:

- 2.1. Provides flexibility to change the I2C address without reprogramming the device.

- 2.2. Enables easy integration of multiple identical devices on the same I2C bus by assigning unique

addresses via hardware configuration (for example, pull-up/pull-down resistors).

2.3. Useful in modular or configurable systems where address conflicts might occur.

**Note**: This feature is specific to the SLG46855. Not all Renesas GreenPAK or AnalogPAK devices support external I2C address configuration. Always consult the product datasheet to verify whether this feature is available for the specific chip you are using.

# **Chapter 2 Sequential Logic**

This chapter presents applications that involve sequential logic. Some sequential logic applications are counters, system reset circuits, power sequencers, and state machines

3. Signal Conditioning

1.Basic Blocks & Functions

2. Sequential

4. Safety Features

s y

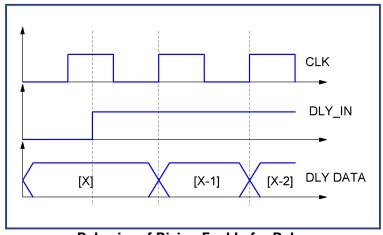

#### **Technique: Optimizing CNT/DLY Accuracy**

This technique works with any GreenPAK. The accuracy of the oscillator and CNT/DLY blocks vary from part-to-part.

GreenPAK ICs, like all chips with internal oscillators, have inherent variation in timing. This is attributed to factors like manufacturing, temperature and, in the case of GreenPAK, user design practices. By using simple design principles the accuracy of counters and delays within a GreenPAK design can be improved.

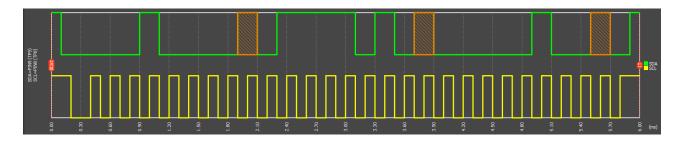

The relationship between the oscillators and CNT/DLY blocks should be considered. The oscillators are global oscillators; they are used for any number of CNT/DLY blocks and aren't initially synchronized to the start/stop of a delay or counter. Consequently, when a counter or delay is enabled it will only begin to increment on the next clock edge. This is depicted in figure below, where an enable signal for a delay is activated mid-clock-cycle and doesn't begin to decrement until the next rising edge.

**Behavior of Rising Enable for Delay**

This is factored into the typical delay time calculation for the CNT/DLY blocks:

where t is between 0 and 1

Thus, as the value of "Counter\_Data" increases, the influence of "t" on the delay time will be proportionately less. Additionally, the absolute value of the delay time is kept the same, despite using a larger "Counter\_Data" value, if a faster "clock" value is used. In the Properties window of the selected CNT/DLY block both the Counter Data value and the Clock Source can be modified.

Additionally, the timing characteristics within the datasheet of the respective GreenPAK should be referenced to ensure factors such as Power-ON time, frequency settling time and percent deviation across temperature are considered.

# 2. Sequential Logic

Basic Blocks & Functions

3. Signal Conditioning

4. Safety Features

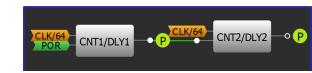

#### **Technique: Sequencing CNT/DLY Blocks**

This technique will work with any GreenPAK.

Delay blocks can be chained together to sequence signals. By chaining the output of one delay block to the input of another a sequential set of delays is made.

**Sequential Rising Edge Delays**

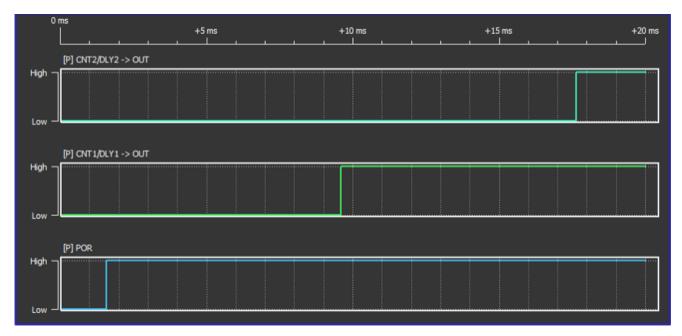

The CNT/DLY blocks in the sequential set should be set to "Delay" in the Mode setting within the Properties window. Typically, the Edge select setting should be the same for all sequenced components. The figure below shows the effect of the two sequential CNT/DLY blocks set to rising edge, 8 ms delays of the Power-On-Reset (POR) signal.

**Sequential Delay Simulation**

One can also chain together CNT blocks for a longer counted time. When Chaining CNT blocks together, the CLK of the CNT should be driven by the output of the previous counter. This is done in the properties by selecting a CNT block and in the Properties window, choosing the Clock connection to be sourced from the previous CNTx/DLYx.

**Sequential Counters**

PIN 20

PIN 1

PIN 18

PIN 17

PIN 16

PIN 15

**PIN 13**

PIN 1

SLG46826

PIN 1 (VDD1)

PIN 2

PIN 3

PIN 4

nWD [

Basic Blocks & Functions

SOC

nRESET

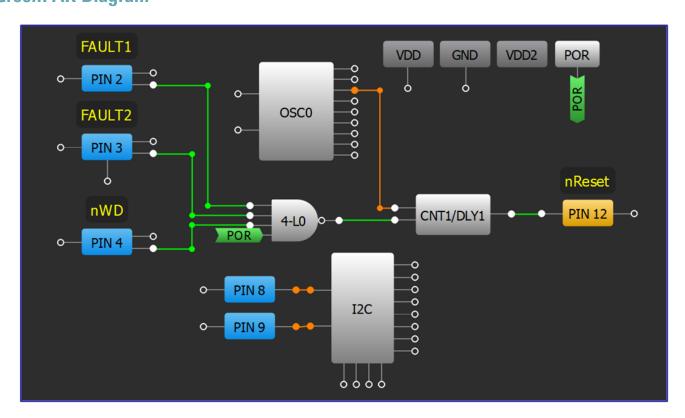

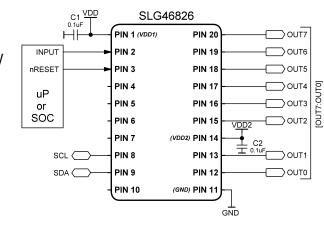

#### **Application: System Reset**

No other components are needed

System Reset ICs are used to provide a reset to a microprocessor during faults, manual resets, brown-outs and more.

# Ingredients PIN 5 PIN 6 PIN 7 PIN 8 PIN 8 PIN 9

#### GreenPAK Diagram

Any GreenPAK

- 1. Configure an I/O as an input for each input signal.

- 2. Add LUT logic to create a HIGH signal when any of the lines are active. The logic is dependent on whether each signal is active-high or active-low.

- 3. Configure a CNT/DLY block to "One shot" mode, with Edge select configured to "Rising." Set the Counter data to create the desired length of pulse. For an active-low pulse change the Output polarity to "Inverted (nOUT)."

- 4. Connect the CNT/DLY block's output to an output pin.

I.Basic Blocks Functions

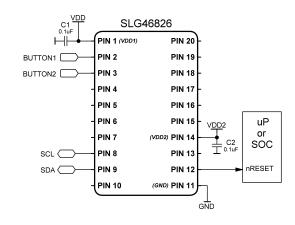

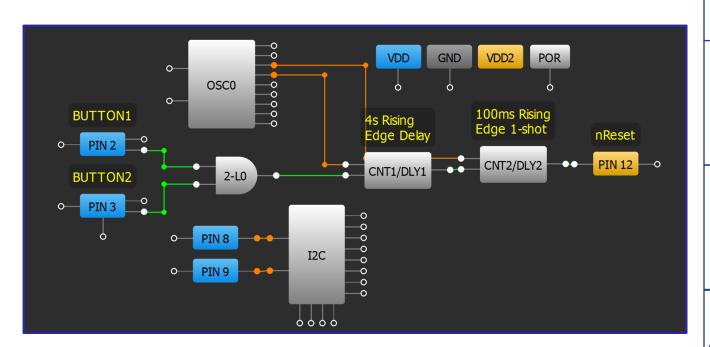

#### **Application: Several Button Reset**

Pressing and holding several buttons to initiate a hard reset is a common interface in many devices. Implementing this application in a separate IC ensures the reset will be acknowledged and acted upon, even if the rest of the system is experiencing one or more software, firmware, or hardware issues.

#### **Ingredients**

- Any GreenPAK

- No other components are needed

#### **GreenPAK Diagram**

- 1. Configure an I/O as an input for each button.

- 2. Add LUT logic to create a HIGH signal when both buttons are active. The logic is dependent on whether each signal is active-high or active-low.

- 3. Configure a CNT/DLY block to "Delay" mode, with Edge select configured to "Rising". Set the Counter data to create the desired length of button hold time. For an active-low pulse change the Output polarity to "Non-inverted (OUT)."

- 4. Configure a second CNT/DLY block to "One shot" mode, with Edge select configured to "Rising." Set the Counter data to create the desired length of pulse. For an active-low pulse change the Output polarity to "Inverted (nOUT)."

- 5. Connect the CNT/DLY block's output to an output pin

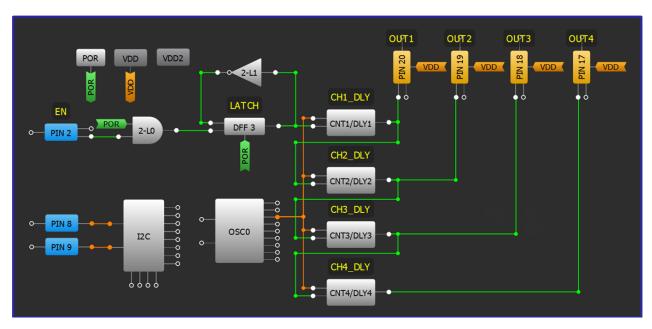

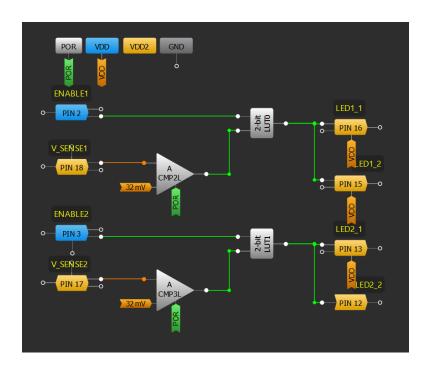

#### **Application: Basic Sequencer**

Sequencers are used when a designer needs to sequentially activate different portions of a system. This is critical for applications that require several power rails.

#### **Ingredients**

- Any GreenPAK

- No other components are needed

#### **GreenPAK Diagram**

- 1. Use LUTs to configure the desired start-up condition.

- 2. Use a latch or DFF to maintain the start-up signal so it can be read by DLY blocks.

- 3. Chain the Delays using Technique: Sequencing CNT/DLY Blocks.

- 4. Connect each delay channel to the desired output pins.

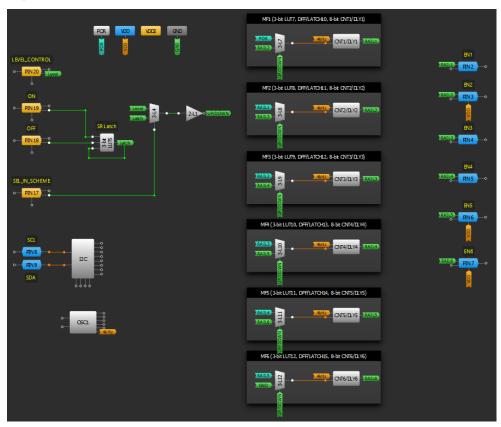

#### **Application: Cascaded Sequencer**

Sequencers are used when a designer needs to sequentially activate different portions of a system. It is typical to have a cascaded sequence, such that a rail does not turn off until all the rails below it have turned off.

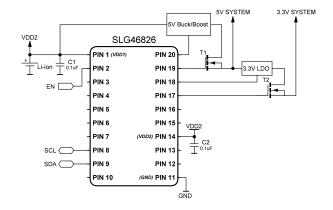

#### SLG46826 PIN 1 (VDD1) **PIN 20** ] LEVEL\_CONTROL PIN 2 **PIN 19** ПО Г **PIN 18** PIN 3 OFF PIN 4 **PIN 17** SEL\_IN\_SCHEME PIN 5 **PIN 16** PIN 6 **PIN 15** PIN 7 (VDD2) PIN 14 PIN 8 **PIN 13** PIN 9 **PIN 12 PIN 10** (GND) PIN 11

#### **Ingredients**

- Any GreenPAK

- No other components are needed

#### **GreenPAK Diagram**

- 1. Configure input structure. Here you can select between level and latching control with PIN17.

- 2. Multiplex inputs to DLYs within a Multi-function block to achieve a cascaded effect.

- 3. Connect the DLY outputs to push pull output pins.

I.Basic Blocks Functions

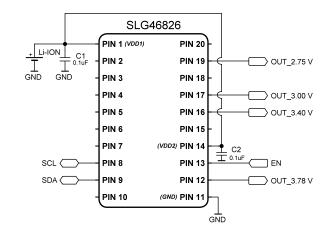

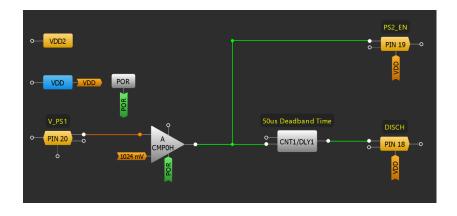

#### **Application: Voltage Monitoring Power Sequencer**

Sequencers are used when a designer needs to sequentially activate different portions of a system. It is typical to have a cascaded sequence, such that a rail does not turn off until all the rails below it have turned off.

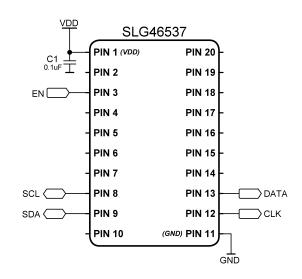

SLG46537

#### **Ingredients**

- Any GreenPAK with 3 ACMPs

- Six resistors

#### **GreenPAK Diagram**

- 1. Configure input pins for the EN and voltage monitoring.

- 2. Configure output pins to sequence system.

- 3. Power on ACMPs, connecting POR to PWR UP and configure the IN- source of each with the desired voltage threshold levels.

- 4. Configure DLYs with the desired delay times.

- 5. Configure LUTs with the proper logic functions.

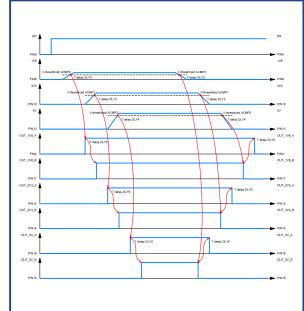

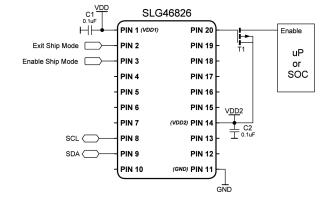

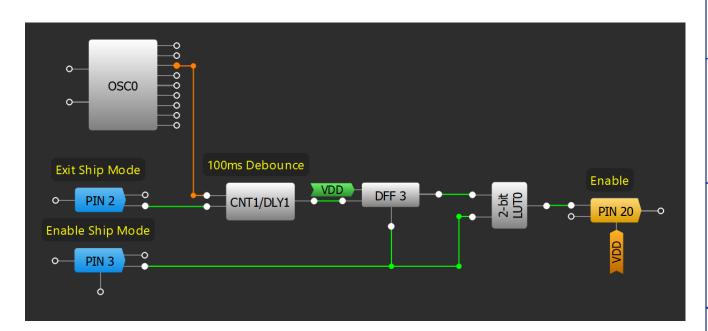

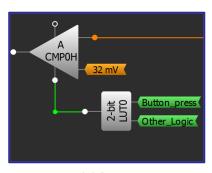

#### **Application: Ship Mode Controller**

An ultra-low power button monitor can save battery life while a product is not yet with the end user. This enables a better first experience by the user.

#### **Ingredients**

- Any GreenPAK

- External PMOS load switch

#### **GreenPAK Diagram**

- 1. Configure PIN2 as an input with 1 M $\Omega$  pullup.

- 2. Set desired Button delay time in CNT1/DLY1.

- 3. Modify LUT contents for correct polarity in and out of ship mode.

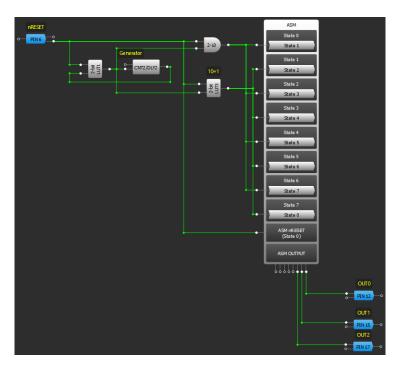

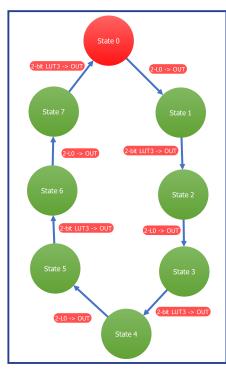

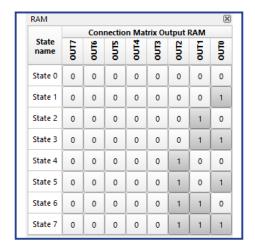

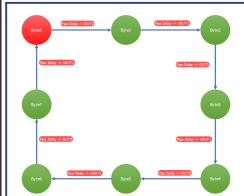

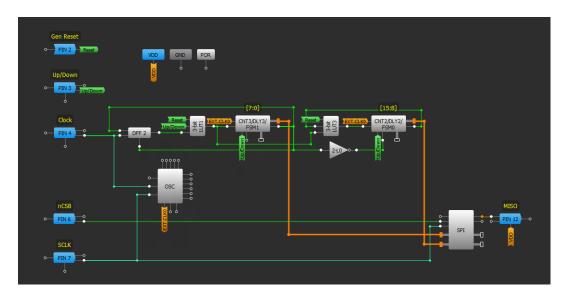

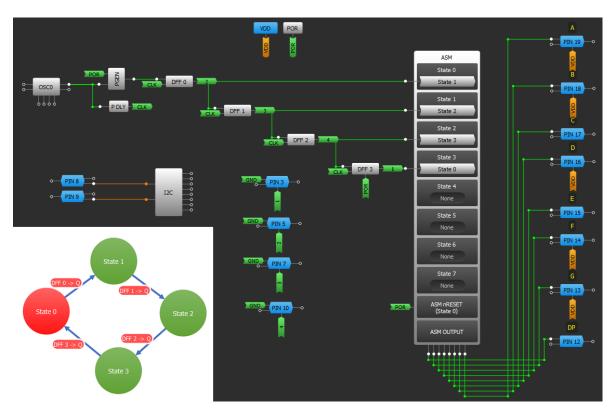

#### Technique: Creating a Synchronous State Machine from an ASM

Synchronous state machines (SSM) transitios on the edge of an incoming clock if the transition condition is met. The generic approach to convert a GreenPAK Asynchronous State Machine (ASM) macrocell into a SSM uses a clock signal with a pulse width greater than the ASM transition time.

Consider the SSM in the 3-bit counter example above. CNT2 and 2-bit LUT1 are used to generate the clock. The ASM uses 8 states connected in series. 2-bit LUT0 and 2-bit LUT3 are used to prevent a logic high signal on two near state transitions. The value of the ASM output for every state is shown below.

The ASM changes from the reset state (State 0) to the next state (State 1) when PIN6 goes high. The following transitions through the states occur as CNT2 toggles first high, then low, and so on.

For more a detailed information about the process of creating an SSM with the ASM see <u>AN-1126 ASM to Synchronous Conversion</u>.

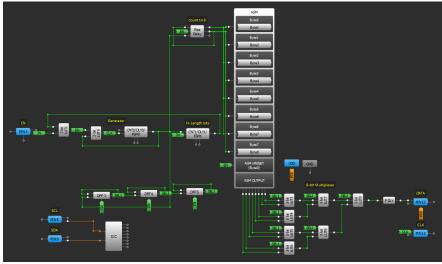

#### **Application: N-Length Bitstream**

A bitstream is a sequence of bits transmitted continuously over a communications path. The GreenPAK can create a repeating string of up to 64 bits.

#### **Ingredients**

Any GreenPAK with an ASM

#### **GreenPAK Diagram**

- 1. Configure a generator and 8-bit Multiplexer using Application: 8-bit Multiplexer.

- 2. Configure CNT1 to determine the length of the bitstream.

- 3. Configure the ASM using Technique: Creating a Synchronous State Machine from an ASM.

- 4. Connect the outputs of the 8-bit multiplexer and generator to the desired output PINs.

- 5. The length of the bitstream (counter data of CNT1) can be changed using I2C.

- 6. The DATA stored in the ASM output RAM can be changed using I2C.

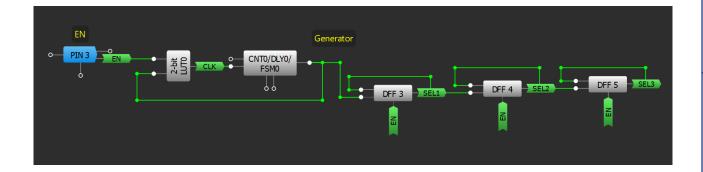

#### Technique: Multiplexing a Bitstream

This technique can be used in any GreenPAK.

GreenPAKs are often used to transfer a data pattern. If the data is transferred from the GreenPAK or the data is transmitted along several lines from the SoC, they must be amalgamated for transmission on one line. Below is an example of the GreenPAK multiplexing a bitstream originating from the ASM output RAM.

The generator circuit is shown above. The generator implements the operation of the CLK line for the synchronous data transmission, enabled by the EN signal. The generator also implements the multiplexer operation algorithm for the correct combination of the transmitted data on one line.

The 8-bit multiplexer circuit is shown above. All LUTs are configured collectively as an 8-bit multiplexer (see AN-1003) the MUX truth table is also shown above. The multiplexer outputs the combination of bits from the ASM block outputs according to the algorithm of the generator and the data is transmitted on one line to DATA. The DATA output will always be the same as the MSB of the ASM output RAM. when EN is LOW. The ASM output RAM can be changed via I2C. logic can also be implemented to change the state of the ASM in order to change the data bits. If the ASM isn't available, the inputs can be pulled high or low for the data values.

**PIN 20**

**PIN 19**

GND

Lifetime Indiactor

SLG46826

PIN 1 (VDD1)

PIN 2

1.Basic Blocks & **Functions**

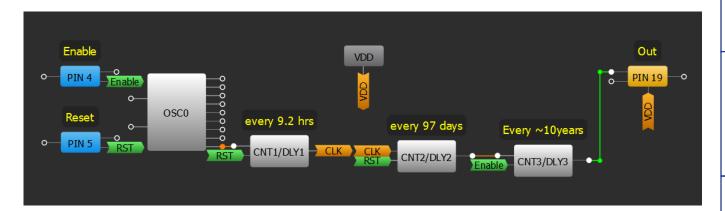

#### **Application: 10 Year Counter**

No other components are needed

Ultra-long counters can be used to determine the lifetime of a product without requiring a large tax on the power budget.

#### or **\***LED1 soc PIN 3 **PIN 18** \$R1 Enable PIN 4 **PIN 17 PIN 16** GND PIN 6 **PIN 15** V<u>DD</u>2 **Ingredients** (VDD2) PIN 14 PIN 7 PIN 8 **PIN 13 PIN 12** Any GreenPAK **PIN 10** (GND) PIN 11

<u>VDD</u>

uР

#### **GreenPAK Diagram**

- 1. Chain the Counters using Technique: Sequencing CNT/DLY Blocks.

- Connect input pins and output pin.

- Set timing in CNT properties.

Basic Blocks &

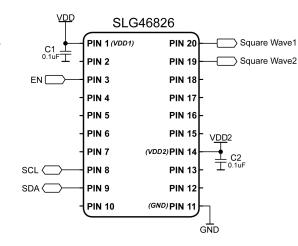

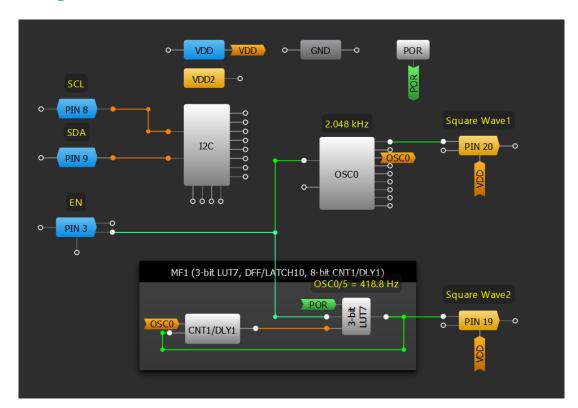

#### **Application: Square Wave Generator**

Square waves are essential for clocking digital systems. They can easily be implemented in GreenPAK with the oscillator blocks or a delayed logic for a customized frequency.

#### **Ingredients**

- Any GreenPAK

- No other components needed

#### **GreenPAK Diagram**

#### **Design Steps**

- 1. Configure the EN input and the square wave outputs.

- 2. Use an internal oscillator to generate a square wave on PIN20. The 'CLK' predivider and 'OUT0' second divider can be altered to customize the frequency.

- 3. Use a both edge delay and a LUT to generate a square wave on PIN19. This configuration allows the user to divide down the frequency of the square wave by a finer adjustment.

Division Coefficient = Counter Data + 2

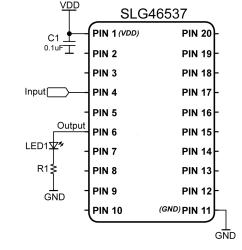

#### **Application: Two Event Button Press**

Using a single button to generate several events is a common solution to save on external control components. Using one button and predetermined time intervals you can organize control of an LED flashlight.

#### **Ingredients**

- Any GreenPAK

- One LED

- One resistor

#### **GreenPAK Diagram**

- 1. Configure GPIO pins as an input for button and an output for LED control.

- 2. Add CNTO/DLYO, CNT1/DLY1, and a DFF to remember the last state.

- 3. Configure the CNT/DLY blocks to "Delay" mode, with Edge select configured to "Rising."

- 4. Configure the CNTO/DLYO output as "nOUT."

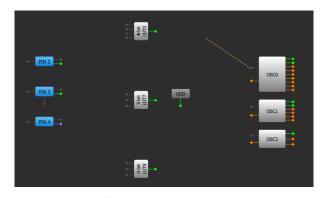

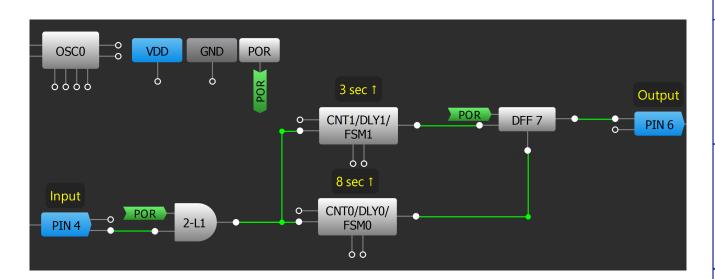

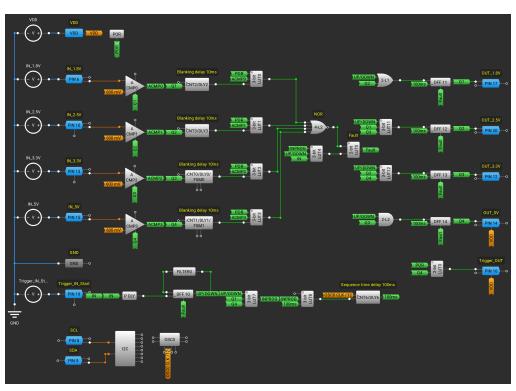

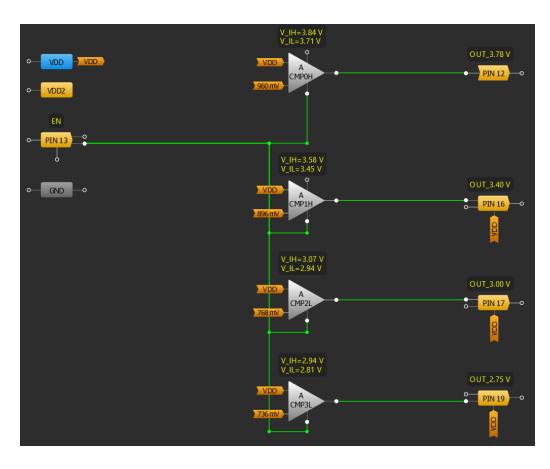

#### Application: Advanced Voltage Monitoring Power Sequencer

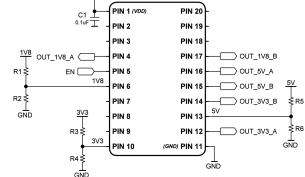

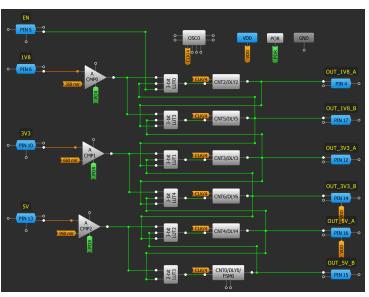

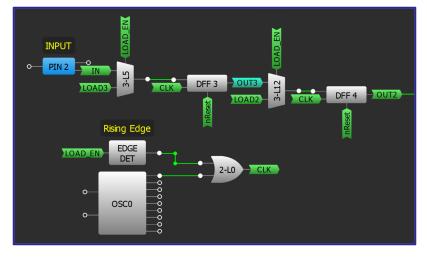

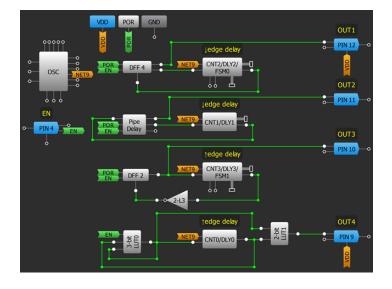

Sequencers are used when a designer needs to monitor several supply rails and activate them in a predefined order. In this design the system enables four voltage rails only after each monitored input reaches its valid threshold. A rail will not turn on until the previous rail has stabilized, ensuring a controlled and safe power-up sequence.

#### **Ingredients**

Any GreenPAK device with 4 ACMPs

#### **GreenPAK Diagram**

#### **Design Steps**

- 1. Configure input pins for the four monitored voltage rails (1.8 V, 2.5 V, 3.3 V, 5 V) and the Trigger\_IN\_Start control pin.

- 2. Set up output pins that will represent the sequenced enable lines for each rail.

- 3. Power on ACMPs, connecting Q1, Q2, Q3 and Q4 (out's of DFF) to PWR UP and configure the IN- source of each with the desired voltage threshold levels.

- 4. Implement sequencing logic: each validated rail output triggers the delay stage of the next rail, forming a cascaded activation chain.

- 5. Configure Fault logic using LUTs to disable the sequence if any monitored voltage falls below its threshold.

- 6. Generate final Trigger\_OUT to signal sequence completion after all rails have been enabled.

Basic Blocks

Functions

### Chapter 3 **Signal Conditioning**

This chapter presents applications that interpret an external signal and condition it to be useful for an operation within a system. Some applications that involve this are frequency division/multiplication, filters, and sensor controllers.

.Basic Blocks & **Functions**

2. Sequential

5. Communication

6. Pulse-based

Management

**Analog Features**

# 2. Sequential Logic

Basic Blocks & Functions

3. Signal Conditioning

4. Safety Features

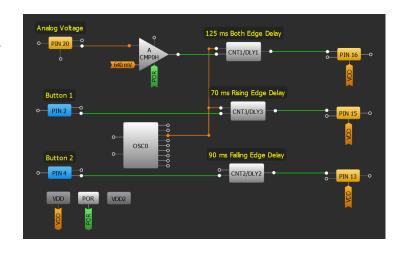

#### Technique: Using a CNT/DLY Block as a Deglitch Filter

This technique can be used in any GreenPAK

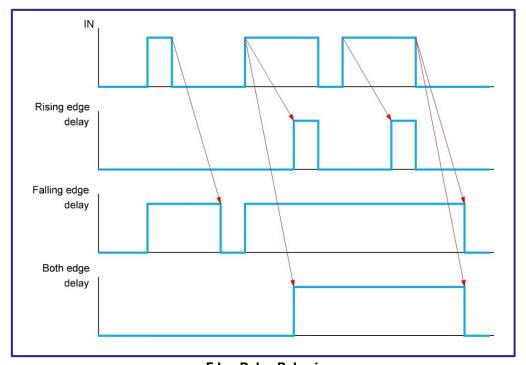

Deglitch / debounce filters are used to eliminate glitches - spurious signal transitions. Glitches occur in situations like a button being pressed/released or when a voltage is very close to a threshold of a hysteresis-less PIN.

There are 3 possible edge-triggered options to configure a deglitch delay: rising, falling or both. In this case delay block will filter pulses shorter then delay value with corresponding polarity: active high for rising edge, active low for falling edge, both High and Low for both edge delay.

**Example Deglitch Delay Options**

See diagram below:

**Edge Delay Behavior**

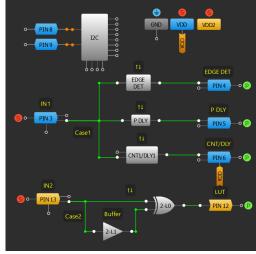

#### **Technique: Edge Detector**

This technique can be used in any GreenPAK.

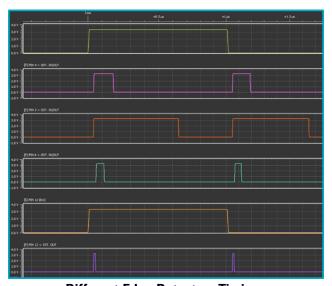

Edge detectors are important components in digital electronics. It is a simple circuit with one input and one output. Edge detectors create a short pulse when a defined edge (rising, falling, or both) is detected. It's useful for implementing a reset function, watchdog timer, or other edge-dependent applications. There are several ways to implement an edge detector (see figure below). To read a detailed description on how to build edge detectors and see more examples see <a href="AN-1046 Various Edge Detector Circuits">AN-1046 Various Edge Detector Circuits</a>.

**Edge Detector Implementation**

Option 1 uses the built-in edge detector feature in EDGE DET, P DLY, and CNT/DLY blocks. These blocks have the benefit of producing a longer duration pulse compared to Option 2 (figure below).

**Different Edge Detectors Timings**

Option 2 uses the small delay caused by signal propagation through a buffer. This delayed signal is compared by a 2-bit XOR to the original input, whose propagation time is exceptionally small. The short delay through the buffer causes a difference between the XOR's inputs, which generates a short pulse on its output. Because of the internal structure of the LUTs their inputs have different propagation delay time.

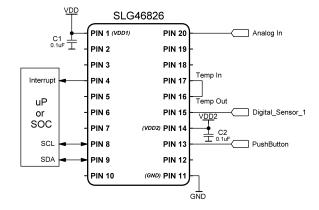

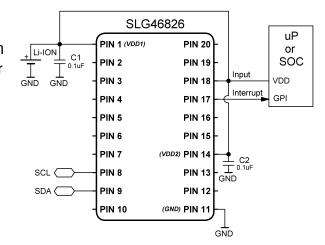

#### **Application: Interrupt Controller**

The GreenPAK can be configured to monitor multiple different interruptible signals and aggregate that information for the host processor to act on. The microprocessor or SOC can read the output of each DFF via I2C to determine the source of the fault.

#### **Ingredients**

- Any GreenPAK

- No other components are needed

#### **GreenPAK Diagram**

- 1. Configure PINs 16, 17, and 18 as "Analog Input/Output."

- 2. Configure levels of ACMPs to proper threshold.

- 3. Wire DFFs to OR gate and set PIN4 as output.

- 4. Configure DLY1 to desired debounce time.

### 2. Sequential Logic

1.Basic Blocks Functions

3. Signal Conditioning

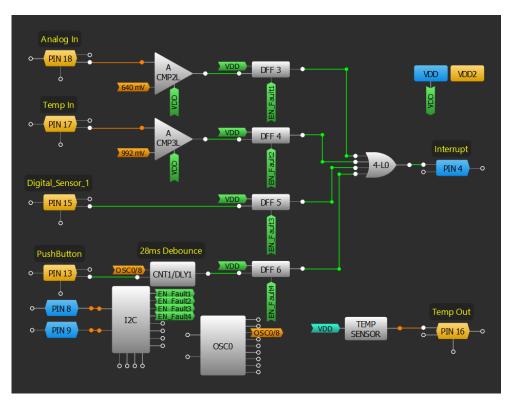

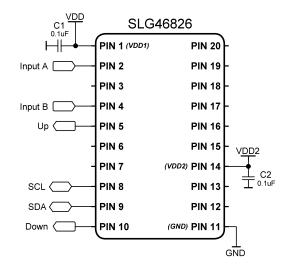

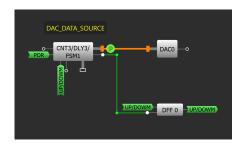

#### **Technique: Creating a Bi-directional Counter**

This technique can be used within any GreenPAK that includes an SPI interface. Alternatives to this technique can be accomplished using other GreenPAKs with an FSM block and storing the counter information using an I2C read command, parallel output, or other method.

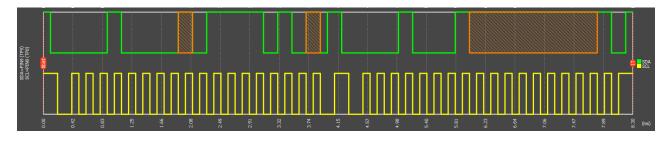

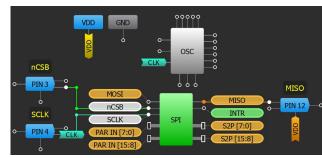

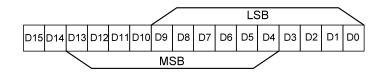

A Counter is a basic digital circuit used for counting input events (pulses, edges), often constructed using a cascade of digital flip-flops. In GreenPAK some CNT/DLY blocks are more robust, and can be used as a finite state machine (FSM) that is not only capable of incrementing but can decrement or hold the current value, dictated by interconnects in the GreenPAK matrix. This technique exemplifies this behaviour by using two FSM blocks in GreenPAK to monitor a pulse input (Clock) and output the corresponding 16-bit sequence via the SPI macrocell.

16-bit FSM with SPI Output

The 16-bit FSM with an output to the SPI block counts input clock pulses in a constructed 16-bit register (FSM0, FSM1). At any time a user can read the value via SPI, reset the 16-bit register, or change the count direction.

The 16-bit counter is implemented using two counters (FSM0 and FSM1 blocks) with additional logic. Bits [15:8] are stored in FSM0, [7:0] in FSM1. Both FSMs are connected to the SPI block, which can output serial data via SPI. The count direction is controlled by an Up/Down pin, directly connected to the FSM blocks' UP matrix output. If this pin is HIGH, the system counts UP, if this pin is LOW, the system counts DOWN. Gen Reset pin is used to reset both counter values (active HIGH).

The Clock input pin is applied simultaneously at the CLK input of FSM1 and FSM0. FSM1 counts each clock, whereas FSM0 counts only when FSM1 counter value is 255 and Up/Down signal is HIGH or when FSM1 counter value is 0 and Up/Down signal is LOW. This functionality is achieved using the KEEP input of the FSM0. When this signal is HIGH the counter value of the FSM0 is not changing despite the clock signal. KEEP is connected to FSM1 output through an inverter. In turn, FSM1's output is only HIGH when counter value is 0 and Up/Down signal is LOW, or when counter value is 255 and Up/Down signal is HIGH.

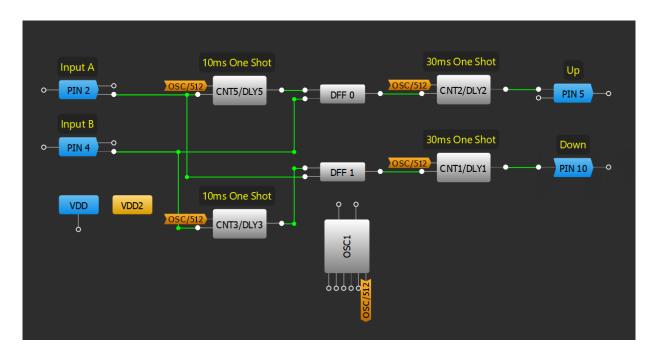

#### **Application: Encoder**

Encoders are used to convert rotary or linear motion to a digital signal. This design is optimized for mouse wheels and volume control in headsets.

#### **Ingredients**

- Any GreenPAK

- No other components are needed

#### **GreenPAK Diagram**

- 1. Configure pins as digital inputs.

- 2. Configure two pins as output to designate direction of encoder.

- 3. Set CNT3/DLY3 and CNT5/DLY5 to the "One shot" mode with the desired filter time.

- 4. Configure DFFs to detect direction (Up or Down).

- 5. Set CNT1/DLY1 and CNT2/DLY2 to the "One shot" mode with the desired output pulse width.

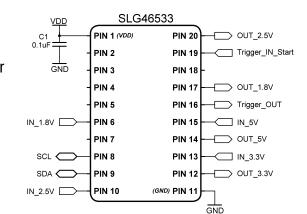

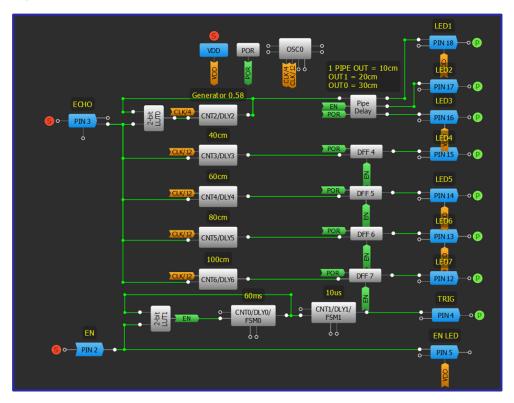

#### **Application: Distance Sense**

Ultrasonic ranging modules provide a non-contact measurement function. This design is a controller for an ultrasonic rangefinder based on the HC-SR04.

#### **Ingredients**

- Any GreenPAK

- LED for each distance measurement

- Resistor for each distance measurement

#### SLG46537 PIN 1 (VDD) PIN 20 EN [ PIN 2 **PIN 19** PIN 3 **PIN 18** ЕСНО [ PIN 4 **PIN 17** TRIG ( PIN 5 PIN 7 PIN 8 PIN 9 PIN 10 (GND) PIN 11 GND

#### **GreenPAK Diagram**

- 1. Configure GPIO input for Echo and output for Trig.

- 2. Add LUT logic and CNT/DLY0 to create a generator with ENABLE signal.

- 3. Add Pipe Delay and CNT/DLY2 to create a generator for detect distance.

- 4. Configure CNT/DLY blocks as a rising edge delay to measure varied distances.

- 5. Add and configure DFFs to latch distance data.

- 6. Connect each DFF output to the desired output pins and configure as open drain.

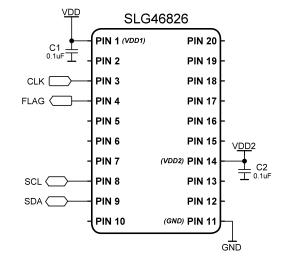

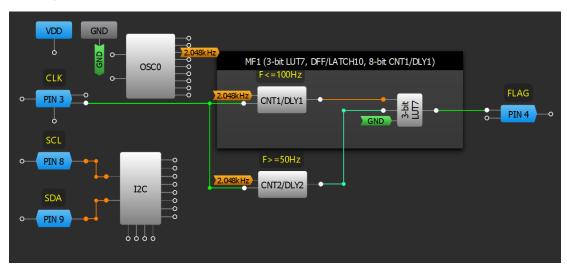

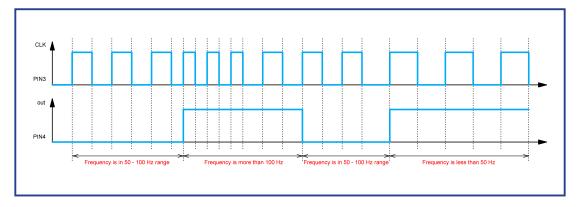

#### **Application: Frequency Range Detector**

Many devices have a specific frequency range in which they operate and require the input clock to stay within this range. This application is used to detect if the input clock frequency is within the desired range.

#### **Ingredients**

Any GreenPAK

#### **GreenPAK Diagram**

- 1. Configure GPIO pins as an input for the clock and output for the flag.

- 2. Configure CNT/DLY blocks to the "Frequency detect" mode with a rising edge detect.

- 3. Set each CNT/DLY block respectively to the minimum and maximum frequency values.

- 4. Configure a LUT to go high when the frequency is outside the desired frequency range.

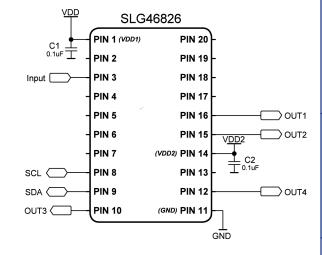

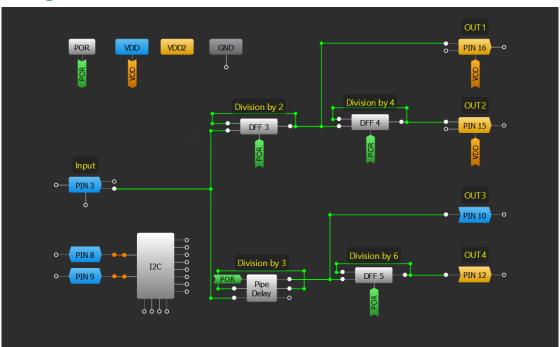

#### **Application: Frequency Divider**

Frequency dividers are used to divide the input frequency into different coefficients. It can used for improving the performance of electronic countermeasure equipment, communication systems and laboratory instruments.

#### **Ingredients**

- Any GreenPAK

- No other components are needed

#### **GreenPAK Diagram**

- 1. Configure inputs for each inputs signal (Input frequency, coefficient).

- 2. Use DFF and Pipe Delay to divide the frequency for the first stage.

- 3. Use another DFF to divide the signal by a factor for the second stage.

- 4. Configure LUT logic to decide outputs into specified coefficient.

# 2. Sequential Logic

I.Basic Blocks Functions

3. Signal Conditioning

4. Safety Features

**Communication Protocols**

6. Pulse-based Control

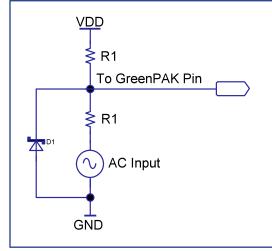

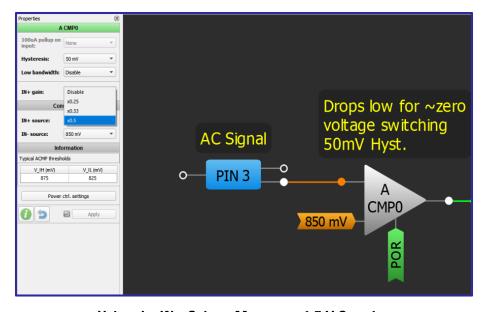

#### **Technique: Zero-Voltage Cross Detection**

This technique can be used in GreenPAKs that include ACMP's.

Zero-voltage cross detection is commonly used as an accurate method of detecting AC characteristics, such as frequency and phase.

GreenPAKs have a pin voltage range of 0 V to a VDD value of 5.5 V. To interpret an AC signal that crosses at the 0 V point using the GreenPAK a DC offset shift should be implemented between the AC signal and the GreenPAK pin. This can be accomplished by a 1:1 resistor divider between VDD of the GreenPAK and the AC signal, shown in the Basic DC Offset figure.

Zero-voltage cross detection requires, at minimum, one or two comparators and a counter. The comparators check the incoming AC signal against a reference voltage, which can either come from the GreenPAK's available reference voltages or an external reference point. If a desired ZVCD voltage is greater than the available GreenPAK reference voltages the AC signal may instead be reduced by using the IN+ gain option within the comparator's property settings and comparing the reduced AC value to a similarly scaled scaled reference.

**Basic DC Offset**

Using the IN+ Gain to Measure a 1.7 V Crossing

2. Sequential

Conditioning

4. Safety

Communication

6. Pulse-based Control

7. Power Management

**Protocols**

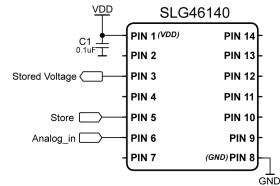

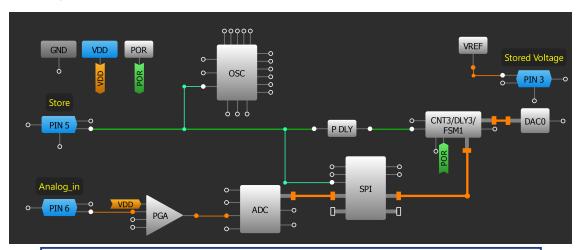

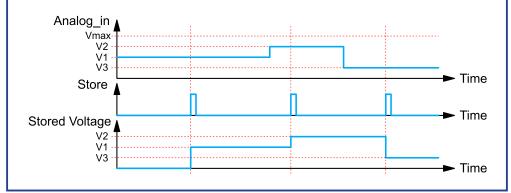

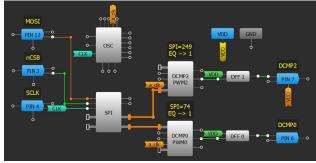

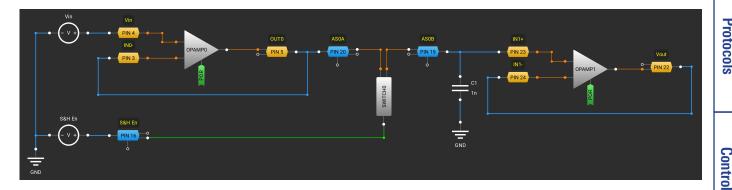

#### **Application: Analog Storage Element**

This application can be used to store the analog voltage on an output until the rising edge is applied to the Store input. The input and output analog voltages lie within the range of 0-1 V.

#### **Ingredients**

Any GreenPAK with an ADC, SPI, and DAC

#### **GreenPAK Diagram**

#### **Design Steps**

- Configure SPI to "ADC/FSM buffer" mode, change the PAR input data source to "ADC".

- 2. Configure FSM0 to "Set (counter value = FSM data)" and change the FSM data source to "SPI [7:0]."

- 3. Configure DAC Input selection to "From DCMP1's input" and VREF Source selector to "DACO out".

- 4. Connect Store input directly to SPI SCLK and FSM1 SET IN through P DLY set as a both edge delay.

9. Advanced Analog Features

### Cor

Basic Blocks & Functions

2. Sequential

3. Signal

Conditioning

-eatures

Protocols

6. Pulse-based Control

# **Chapter 4 Safety Features**

This chapter presents applications that are intended to respond to fault conditions in a system and protect it from damage. Some applications that provide safety to electronic systems are battery indicators, watchdog timers, and temperature sensors.

RENESAS

#### **Technique: Reducing ACMP Power Consumption**

This technique can be used in GreenPAKs that include ACMP's. The reduction in power consumption will vary.

GreenPAKs are often used in projects to reduce the system's current consumption. However, several components within GreenPAKs, when active, can cause a noticeable change in current consumption. Amongst the most consumptive macrocells are the analog comparators. Table 1 is taken from the SLG46826 datasheet to highlight the ACMP's consumption.

Luckily, ACMPs can be shut down when not in use. This is done in two ways:

- 1. Through the PWR UP input of the ACMP.

- 2. Enabling a wake-sleep controller (WS Ctrl) for the ACMP.

| Note                                                                                                      | V <sub>DD</sub> = 2.5 V | V <sub>DD</sub> = 3.3 V | V <sub>DD</sub> = 5.0 V | Unit |

|-----------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|-------------------------|------|

| Chip Quiescent                                                                                            | 0.39                    | 0.43                    | 0.53                    | μΑ   |

| Vref OUT0 (Source none, Source Temp<br>Sensor, Buffer On)                                                 | 12.79                   | 12.95                   | 13.57                   | μА   |

| Vref OUT0 (Source none, Source Temp<br>Sensor, Buffer Off)                                                | 7.62                    | 7.67                    | 7.87                    | μА   |

| Vref OUT1 (Source none, Buffer On)                                                                        | 6.53                    | 6.61                    | 7.02                    | μΑ   |

| Vref OUT1 (Source none, Buffer Off)                                                                       | 1.40                    | 1.44                    | 1.54                    | μΑ   |

| Vref (ACMPxH, 0.32 mV, Buffer On)                                                                         | 12.24                   | 12.59                   | 12.21                   | μΑ   |

| Vref (ACMPxL, 0.32 mV, Buffer On)                                                                         | 6.93                    | 7.01                    | 7.43                    | μΑ   |

| ACMP0H, 1H, 2L, 3L,hysteresis<br>disabled, gain = 1, +IN - IO11, 12, 13, 14<br>Pull Up 1M, Vref = 32 mV   | 65.86                   | 67.12                   | 70.77                   | μА   |

| ACMP0H, 1H, 2L, 3L,hysteresis<br>disabled, gain = 1, +IN - IO11, 12, 13, 14<br>Pull Down 1M, Vref = 32 mV | 37.34                   | 38.05                   | 40.29                   | μА   |

| ACMP0H, 1H, 100 μA disabled,<br>hysteresis disabled, gain = 1, +IN - IO13,<br>14 Pull Up 1M               | 63.85                   | 65.11                   | 68.71                   | μА   |

| ACMP0H, 1H, 100 μA disabled,<br>hysteresis disabled, gain = 1, +IN - IO13,<br>14 Pull Down 1M             | 35.97                   | 36.68                   | 38.87                   | μА   |

| ACMP0H, 100 μA disabled,<br>hysteresis disabled, gain = 1, +IN - VDD,<br>Vref = 32 mV                     | 36.30                   | 36.96                   | 38.85                   | μА   |

| ACMP0H, 100 μA enabled, hysteresis<br>disabled, gain = 1, +IN - IO14 Pull Up 1M,<br>Vref = 32 mV          | 46.77                   | 47.31                   | 49.23                   | μА   |

| ACMP0H, 100 μA enabled, hysteresis<br>disabled, gain = 1, +IN - IO14<br>Pull Down 1M, Vref = 32 mV        | 49.02                   | 50.29                   | 53.75                   | μА   |

**Table 1 SLG46826 Current Consumption**

Wake-sleep control requires a dedicated counter configured to "Wake sleep controller" mode. This is available in many (but not all) GreenPAKs. PWR UP control can be used in any GreenPAK with ACMPs. When the signal is HIGH the ACMP is on; using logic, counters or other macrocells to turn off the ACMP can drastically reduce power consumption. For example, if two different voltage thresholds are needed the higher-threshold ACMP can be kept inactive until the lower threshold is met.

(a) Logic

(b) Duty Cycle

Common PWR UP Configurations

(c) Cascaded

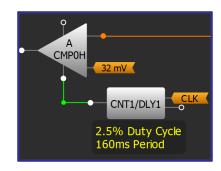

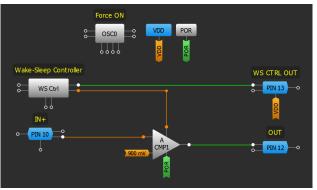

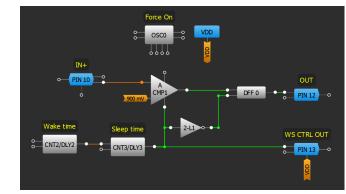

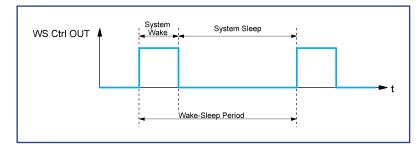

#### **Technique: Wake-Sleep Controller**

Waking and sleeping analog macrocells is useful for reducing power consumption. It is possible to accomplish this with the wake-sleep controller for analog macrocells like ACMPs and ADCs.

Wake-sleep involves switching analog macrocells on and off periodically. For some GreenPAKs this function can be implemented using the WS Ctrl block. For those that don't have this block, it can be implemented using two counters (one counter if there is no need to change the wake time), a D flip-flop, and an inverter. The figures below display examples using these respective methods.

Two Counter Method

Without wake -sleep implemented, the total current consumption consists of:

- Quiescent current

- ACMP current

**Behavior of Wake-Sleep**

With wake-sleep implemented, the quiescent current is approximated as follows:

$$I_{WS} = \frac{System~Wake}{System~Wake+System~Sleep} \cdot I_{without~WS} = \frac{System~Wake}{WS~Period} \cdot I_{without~WS}$$

The total current with wake-sleep implemented is:

$$Total\ Current = I_{Quiescent} + I_{OSC} + I_{Wake\ Sleep}$$

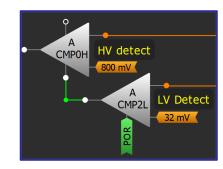

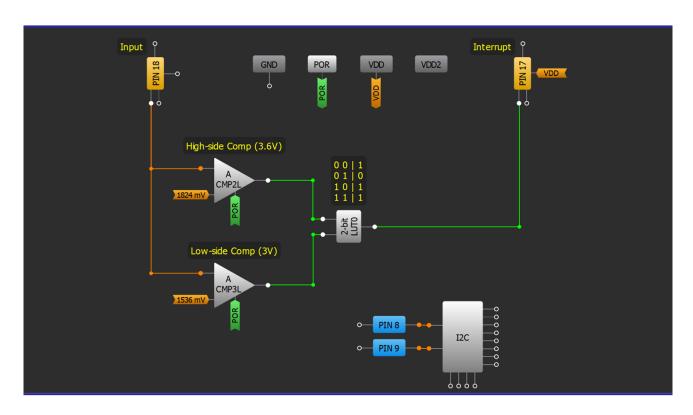

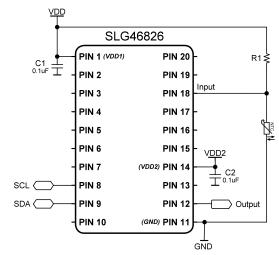

#### **Application: Window Comparator**

Window comparators are an essential part of any design that runs off a depletable power source, like a battery or supercapacitor. By monitoring battery voltage, a device can opt to stop using nonessential resources at low battery levels. This can prevent permanent damage to the device.

#### **Ingredients**

- Any GreenPAK w/ ACMP's

- No other components are needed

#### **GreenPAK Diagram**

- 1. Configure the High-side ACMP2L by using the IN- source and IN+ gain options to set the desired high-side threshold.

- 2. Repeat step 1 for the low side ACMP with the low-side threshold.

- 3. Change the IN+ source for the second comparator to ACMP2L IN+ source.

- 4. Add the LUT logic to trigger an interrupt when the LOW-side comp is low or high-side is high.

#### **Application: Over Temperature Protection**

An over temperature protection circuit is widely used to alert a system of high temperatures. This circuit protects the system from overheating when the internal temperature exceeds a safe threshold.

#### **Ingredients**

- Any GreenPAK w/ ACMP's

- One resistor

- One NTC thermistor

#### **GreenPAK Diagram**

- 1. Set the IN+ source of ACMP2L to PIN18 and IN- source to the desired threshold.

- 2. Connect one node of the resistor to VDD and the second node to PIN18.

- 3. Connect one node of the NTC thermistor to PIN18 and the second node to GND.

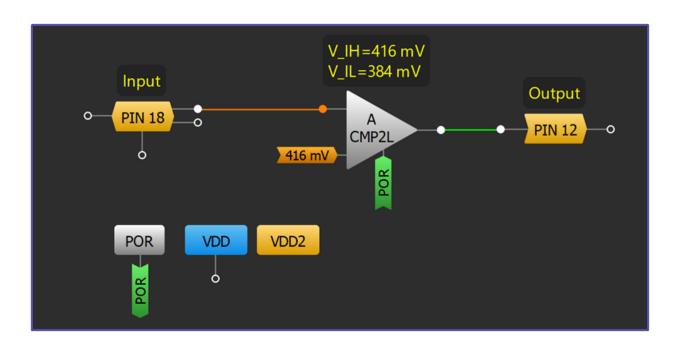

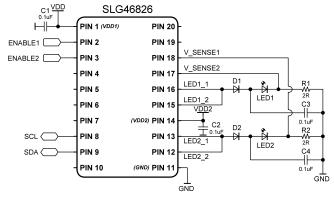

#### **Application: Battery Charge Indicator**

Battery charge indicators are used in battery-powered devices to indicate the state of charge. This design is optimized for a lithium-ion battery.

#### **Ingredients**

- Any GreenPAK w/ ACMP's

- No other components are needed

#### **GreenPAK Diagram**

- 1. Connect pin to PWR UP pin of ACMP0H, ACMP1H, ACMP2L, and ACMP3L.

- 2. Set IN+ source of all the ACMPs to "VDD/PIN20" and each IN- source to the desired threshold level.

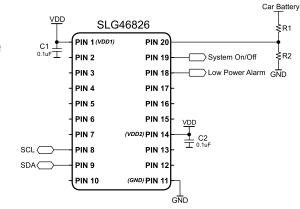

#### **Application: Low Voltage Indicator for Infotainment**

Voltage indicators are used in battery-powered devices to indicate the state of charge. This device monitors the voltage levels of a car battery and adjusts infotainment activities as needed to conserve power.

#### **Ingredients**

- Any GreenPAK

- Two resistors for voltage divider

#### **GreenPAK Diagram**

- Configure the ACMPOH IN+ source as "PIN 20" and the other ACMPs as "ACMPOH IN+ source".

- 2. Add a voltage divider on PIN 20 to handle high voltage from the car battery.

- 3. Configure the IN- source to the desired voltage threshold values.

- 4. Configure logic to determine the voltage level windows for the outputs.

- 5. Add a debounce delay in between ACMP2L and 3-bit LUTO.

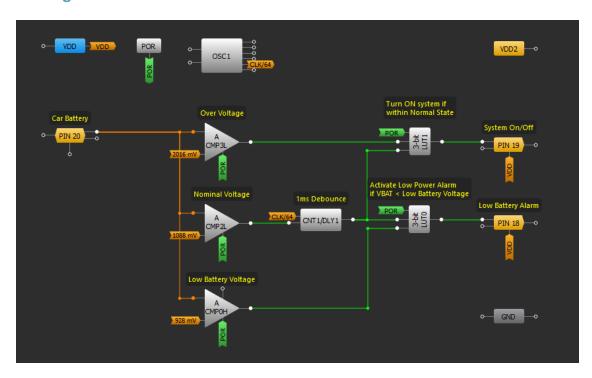

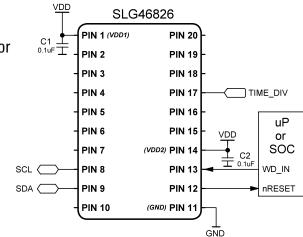

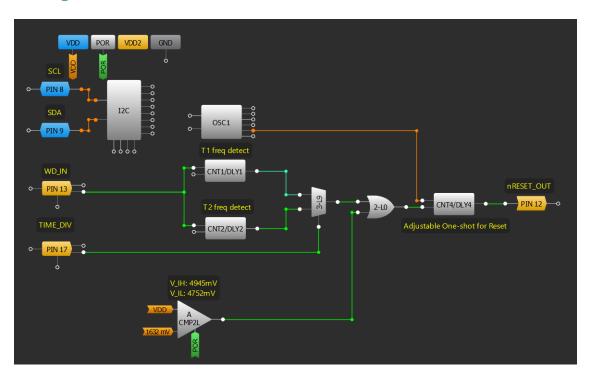

#### **Application: Watchdog Timer**

Watchdog timers are used for automatically generating a system reset signal if the microcontroller or microprocessor neglects to periodically send a pulse. Monitoring for low supply voltage is an additional, common feature of watchdog ICs.

#### **Ingredients**

- Any GreenPAK w/ ACMP's

- No other components are needed

#### **GreenPAK Diagram**

- 1. Set undervoltage threshold with an ACMP.

- 2. Configure two CNT/DLY blocks to the "Frequency detect" mode.

- 3. Design the digital logic to combine active signals from undervoltage and watchdog timeout.

- 4. Add a one shot block to trigger the reset pulse. It can be inverted to be active low.

54

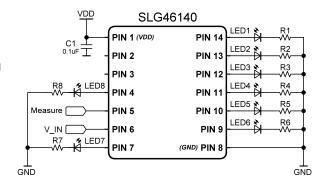

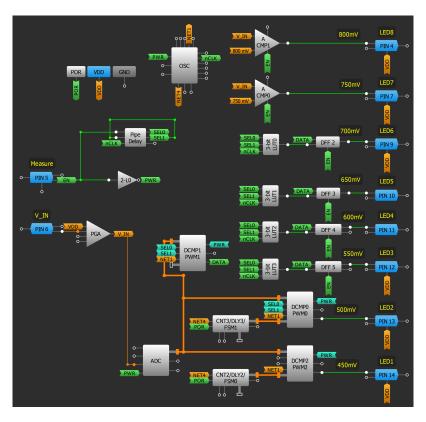

#### **Application: Voltage Level Detection**

Some applications require multiple voltage levels to be evaluated, rather than a few distinct levels. This application shows how to use of ACMPs, DCMPs, and an ADC to monitor the voltage amplitude.

#### **Ingredients**

- Any GreenPAK with ACMPs, DCMPs, and an ADC

- Up to eight LEDs and resistors

#### **GreenPAK Diagram**

- 1. Power on the ADC, DCMPs, and ACMPs.

- 2. Configure the DCMPs using Technique: Using DCMP/PWM Macrocell in PWM Mode.

- 3. Set the IN- of each ACMP and DCMP with the desired voltage threshold levels.

- 4. Add LUT and DFF logic to select and write data of the amplitude of the analog voltage from DCMP1.

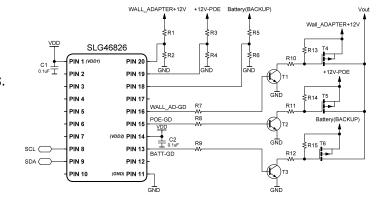

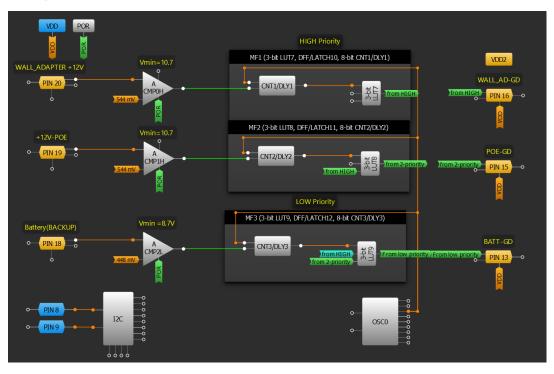

**Application: Power Backup Management**

Power Backup management is used when a designer must guarantee the non-interrupted power supply of a system from different sources.

RENESAS

#### **Ingredients**

- Any GreenPAK with three ACMPs.

- External resistor dividers to attenuate input signal to the operating value range of ACMPs.

#### **GreenPAK Diagram**

- 1. Use three ACMPs to detect power input signals.

- 2. Use CNT/DLY blocks configured as a delay to implement a debounce filter.

- 3. Add logic cells to create switching priority between input sources.

I.Basic Blocks Functions

2. Sequential

Conditioning

4. Safety

Communication

6. Pulse-based

Control

7. Power Management

**Protocols**

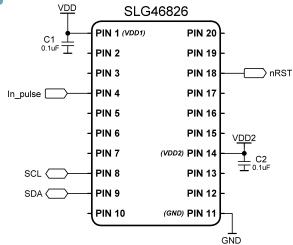

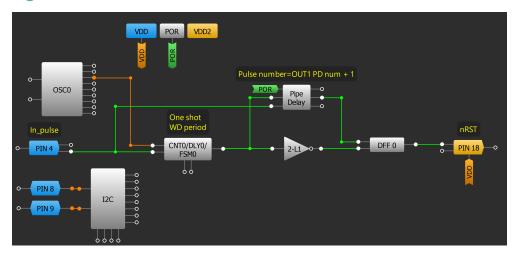

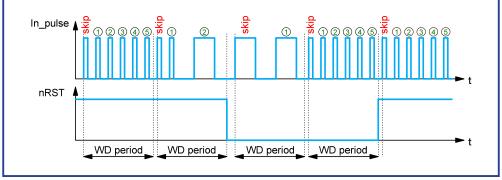

#### **Application: N-pulse Presence Watchdog**

Watchdog timers are used for automatically generating a system reset signal if the microcontroller or microprocessor neglects to periodically send a pulse. This application monitors the number of pulses that go to the GreenPAK during a watchdog period. If the number is less than the predefined pulse number, a system reset will be triggered.

#### **Ingredients**

Any GreenPAK

#### **GreenPAK Diagram**

- 1. Configure CNTO/DLYO/FSMO as a one shot with the desired watchdog period.

- 2. Define the pulse number in the Pipe Delay (Note: Pulse number = 0UT1 PD num + 1).

- 3. Invert the output of the one shot and connect it to the CLK input of DFFO.

- 4. Connect nOUT1 of the Pipe Delay to the D input of DFF0.

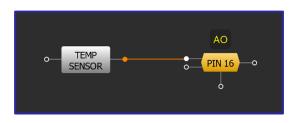

#### **Technique: Using the Temperature Sensor Block**

This technique can be used with any GreenPAK that has a Temperature Sensor macrocell inside.

Some ICs have an analog Temperature Sensor (TS) with an output voltage linearly proportional to the Centigrade temperature. The TS is rated to operate in a temperature range of -40°C to 85°C. The error in the whole temperature range does not exceed  $\pm 0.85\%$ . The TS output can be connected directly to the Analog Output or to the ACMP positive input. The TS may have two output voltage ranges and a Power Up input. The Power Up optionally can be activated using the matrix input or from the register. The TS can also be activated and the range can be changed via I2C. The TS output voltage at a constant temperature has very low variations over VDD changes (for example, in the SLG46826, the output voltage error is less than  $\pm 0.08\%$  at all temperatures).

**Temperature Sensor Macrocell**

The TS output voltage can be calculated using the following formula:

$Vts = K \times T + V0$

Where:

Vts - TS Output Voltage;

K - Coefficient;

T - Temperature in °C;

V0 - Output Voltage at 0 °C.

**Temperature Sensor Connected to Analog**

The temperature proportional voltage signal can be applied to the Analog Output (PIN16). The Power down source configuration should be set to "From register".

Temperature Sensor output signal can be compared to the reference voltage in the ACMP block (See the figure below), which generates a twostate signal at the discrete output. In order to decrease the power consumption TS\_EN is used. TS\_EN enables the Temperature Sensor and switches the ACMP3L on. Power down source should be set to "From matrix."

**Temperature Comparator**

GreenPAK with TS can:

- measure PCB components temperature

- measure FET or BJT case temperature

- create an alarm signal for SoC or in closed-loop applications

- minimize errors for ADCs, DACs, OpAmps and other temperature dependent schematics

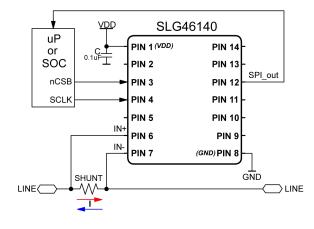

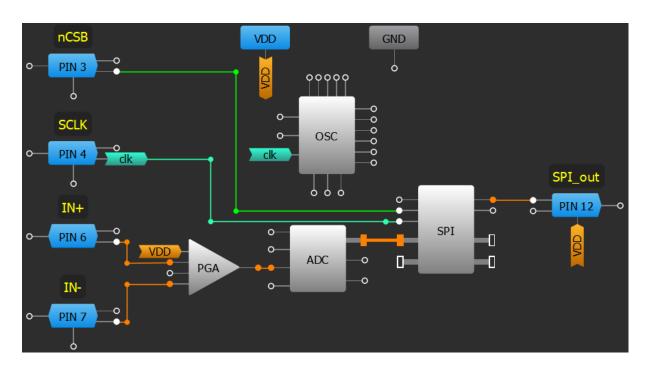

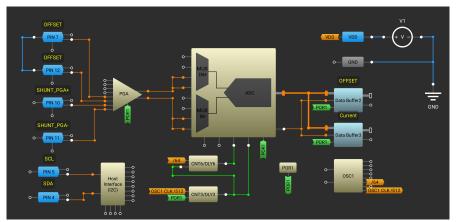

#### **Application: Current Detection Through External Sense Resistor**

The GreenPAK can be used to sense the current going through a device by sensing the voltage across a sense resistor. This application outputs a serial code to represent the value it has sensed.

RENESAS

#### **Ingredients**

- Any GreenPAK with a PGA, ADC, and SPI

- One resistor

#### **GreenPAK Diagram**

- 1. Power up the ADC by removing VDD from the PWR DOWN input.

- 2. Configure the PGA to "Differential" mode. It will automatically connect to the ADC, PIN6, and PIN7.

- 3. Configure SPI to the "P2S" mode and change the PAR input data source to "ADC."

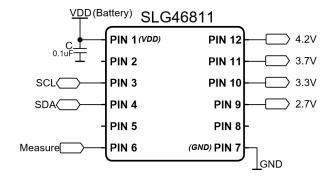

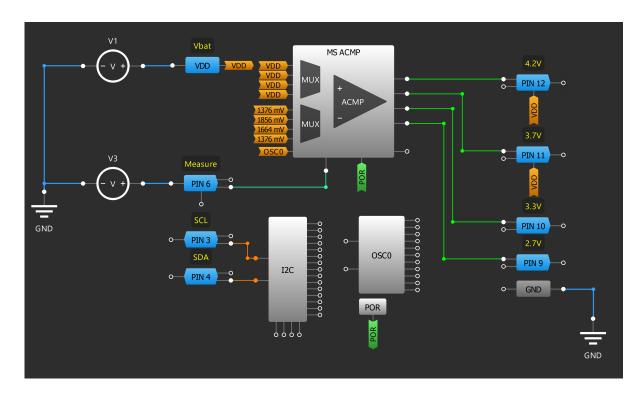

### **Application: Monitor Four Levels for One Analog Signal With One MS ACMP**

Monitoring four levels for one analog signal with a GreenPAK can be useful in a variety of applications. For instance, it can be used for battery management, fluid level control, temperature, light, proximity, pressure, humidity sensing, etc

RENESAS

#### **Ingredients**

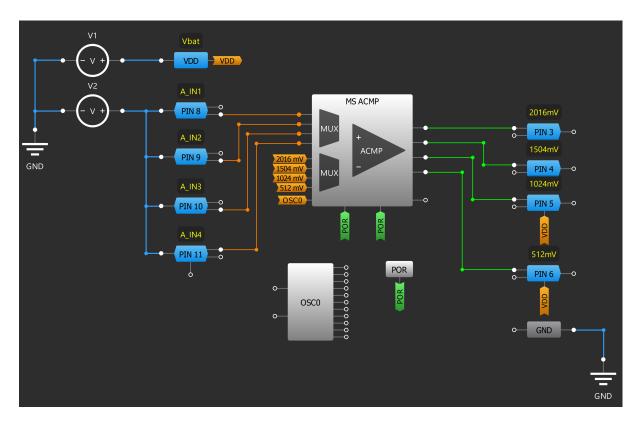

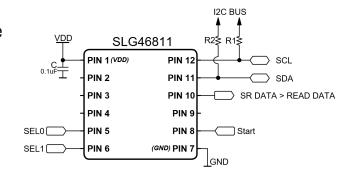

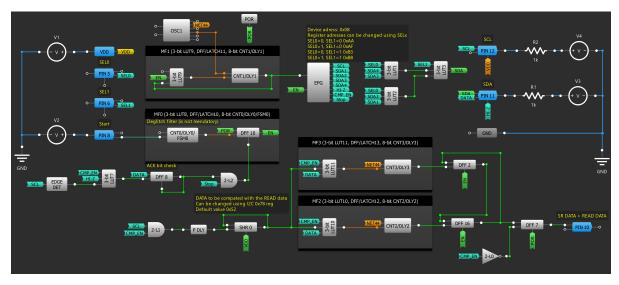

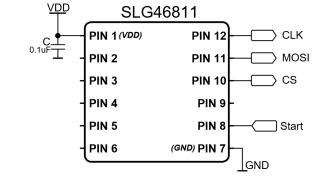

SLG46811V or any GPAK with appropriate number of ACMPs

#### **GreenPAK Diagram**

- 1. Configure MS ACMP to Multi-channel mode and choose 4-channels.

- 2. Choose Rising Edge Activation to Enable MS ACMP.

- 3. Adjust the IN- source for Channel 0 Channel 3.

- 4. Configure PIN6 as digital input and connect it to Enable input of MS ACMP. By every rising edge applied to PIN6 MS ACMP will measure the VDD voltage output the result to PIN9-PIN12.

- 5. I2C can rewrite the ACMPs' threshold values.

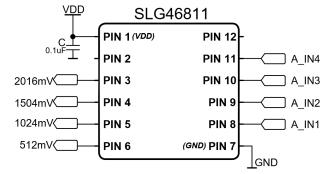

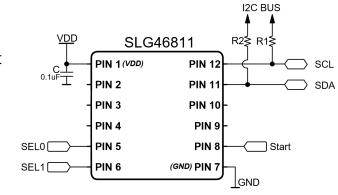

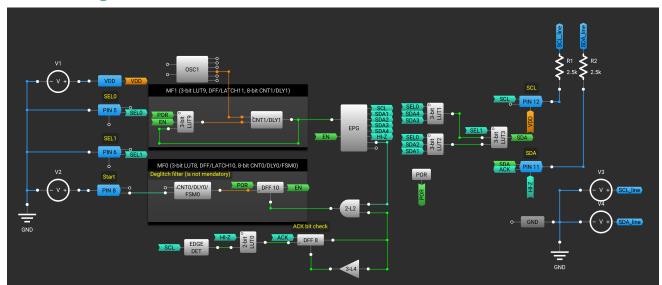

### **Application: Monitor Four Separate Analog Signals With One MS ACMP**

Monitoring four separate analog signals with a GreenPAK can be useful in a number applications, where four independent voltage signals change slowly.

#### **Ingredients**

SLG46811V or any GPAK with appropriate number of ACMPs

#### **GreenPAK Diagram**

- 1. Configure MS ACMP to Multi-channel mode and choose 4 channels.

- 2. Choose High-Level Activation and connect POR (MS ACMP will be continuously sampling) to ENABLE input of MS ACMP.

- 3. Adjust the IN-source for Channel 0 Channel 3. The voltage at PIN8 PIN11 is compared to the reference, and the output to PIN3-PIN6 accordingly.

- 4. I2C can rewrite the ACMPs' threshold values.

# **Chapter 5 Communication Protocols**

This chapter presents applications that involve communication between devices. The following applications and techniques involve I2C, serial, parallel communication protocols.

Many of the techniques and applications available in this section rely upon a GreenPAK's I2C capability. To learn about I2C within a GreenPAK please consult the chip's Datasheet.

RENESAS

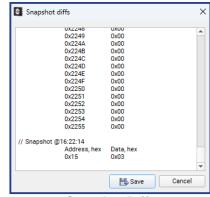

#### **Technique: Changing Your Design with I2C**

This technique can be used in any I2C compatible device.

If a GreenPAK device is I2C compatible its behavior can be edited even after it has been programmed. However, a device must be MTP-compatible and undergo In-System Programming [ISP] to retain design changes after it has lost power. This technique outlines a fast way to determine which I2C commands need to be performed to change a design.

- 1. Complete your initial design. This is the design the IC will use whenever it's booted up.

- 2. In the GreenPAK Designer, select the I2C Reconfigurator.

**I2C Tools Button**

- 3. In the I2C Reconfigurator select the snapshot button (boxed in red), or press SHIFT+A. This will take an I2C commandlist "snapshot" of your current design.

- 4. Change your design to the next configuration.

- 5. Take a snapshot using the method in step 3 to create the second snapshot.

- Click the Snapshot diffs button (boxed in green). This will show the I2C commands necessary to create this design. It is not necessary to program these, since they are instantiated on the boot-up of the GreenPAK.

- 7. Scroll down the Snapshot diffs list, where you will find the second snapshot. This will show only the values that have changed between the first and second snapshot.

- 8. These values, shown in the red box on the right, correlate to the hexadecimal address and data value that need to be sent in I2C to change the threshold value of the ACMP (or any other change that may occur).

**I2C Reconfigurator**

**Snapshot Diffs**

# 2. Sequential Logic

Basic Blocks

Functions

3. Signal Conditioning

4. Safety Features

#### **Technique: Creating an I2C command**

This technique can be used in any GreenPAK with an I2C macrocell With the I2C generator a user can create an I2C signal based on logic generators. It consists of two logic generators acting as SDA and SCL lines. The user can combine predefined I2C primitives to generate the needed waveform and choose an SCL frequency: 1 k, 2.5 k, and 5 kHz for the GreenPAK Advanced Development Platform and 1 k, 2.5 k, 5 k, 10 k, 20 k, 50 k, 100 k, 200 k, 400 k, 1000 kHz for the GreenPAK Pro Development Platform.

To create an I2C signal using the I2C Generator:

- 1. Select the Debug button.

- 2. Select "I2C generator" on the SDA input external connector setting of the I2C block.

- 3. Go to Signal Wizard by clicking EDIT.