# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

### Notice

- All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics atta abooks, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU ROHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

The revision list can be viewed directly by clicking the title page.

The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# 32

# SH-3/SH-3E/SH3-DSP

Software Manual

Renesas 32-Bit RISC Microcomputer SuperH<sup>™</sup> RISC engine Family

Rev.4.00 2006.05

Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any thirdparty's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or resurrent control to the ownert control laws and regulations of lapan and/or the

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

# Introduction

The SH-3/SH-3E/SH3-DSP is a new generation of RISC microcomputers that integrate a RISCtype CPU and the peripheral functions required for system configuration onto a single chip to achieve high-performance operation. It can operate in a power-down state, which is an essential feature for portable equipment.

These CPUs have a RISC-type instruction set. Basic instructions can be executed in one clock cycle, improving instruction execution speed. In addition, the CPU has a 32-bit internal architecture for enhanced data-processing ability.

In addition, the SH-3E supports single-precision floating point calculations as well as entirely PCAPI compatible emulation of double-precision floating point calculations. The SH-3E instructions are a subset of the floating point calculations conforming to the IEEE754 standard.

This programming manual describes in detail the instructions for the SH-3/SH-3E/SH3-DSP and is intended as a reference on instruction operation and architecture. It also covers the pipeline operation, which is a feature of the SH-3/SH-3E/SH3-DSP. For information on the hardware, please refer to the hardware manual for the product in question.

Please contact a Renesas sales office for information on development environment systems.

Rev. 4.00 May 15, 2006 page iii of xviii

# Renesas

# **Organization of This Manual**

Table 1 describes how this manual is organized. Table 2 show the relationships between the items listed and lists the sections within this manual that cover those items.

| Category                             | Section Title                          | Contents                                                                                                                                                                          |

|--------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introduction                         | 1. Features                            | CPU features                                                                                                                                                                      |

| Architecture (1)                     | 2. Programming model                   | Types and structure of general registers, control registers and system registers                                                                                                  |

|                                      | 3. Data Formats                        | Data formats for registers and memory                                                                                                                                             |

|                                      | 4. Floating Point<br>Processor Unit    | FPU register configuration, FPU exceptions                                                                                                                                        |

|                                      | 5. DSP Operations<br>and Data Transfer | Fixed-point operations, integer operations, logic<br>operations, multiplication, shift operations,<br>overview of DSP operations such as saturation<br>operations, repeat control |

| Introduction to<br>instructions      | 6. Instruction<br>Features             | Instruction features, addressing modes, and instruction formats                                                                                                                   |

|                                      | 7. Instruction Set                     | Summary of instructions by category and list in alphabetic order                                                                                                                  |

| Detailed information on instructions | 8. Instruction<br>Descriptions         | Operation of each instruction in alphabetical order                                                                                                                               |

| Architecture (2)                     | 9. Processing States                   | Power-down and other processing states                                                                                                                                            |

|                                      | 10. Pipeline Operation                 | Pipeline operation                                                                                                                                                                |

# Table 1Manual Organization

| Category                       | Торіс                                                                                                                                                          | Sec  | tion Title                                |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------|

| Introduction and               | CPU features                                                                                                                                                   | 1.   | Features                                  |

| features                       | Instruction features                                                                                                                                           | 6.1  | RISC-Type Instruction Set                 |

|                                | Pipelines                                                                                                                                                      | 10.1 | Basic Configuration of<br>Pipelines       |

|                                |                                                                                                                                                                | 10.2 | Slot and Pipeline Flow                    |

| Architecture                   | Organization of registers                                                                                                                                      | 2.   | Programming model                         |

|                                | Data formats                                                                                                                                                   | 3.   | Data Formats                              |

|                                | Floating point processor unit                                                                                                                                  | 4.   | Floating Point Processor Unit             |

|                                | DSP                                                                                                                                                            | 5.   | DSP Operations and Data<br>Transfer       |

|                                | Processing states, reset state, exception<br>processing state, bus release state,<br>program execution state, power-down<br>state, sleep mode and standby mode | 9.   | Processing States                         |

|                                | Pipeline operation                                                                                                                                             | 10.  | Pipeline Operation                        |

| Introduction to                | Instruction features                                                                                                                                           | 6.   | Instruction Features                      |

| instructions                   | Addressing modes                                                                                                                                               | 6.2  | Addressing Modes                          |

|                                | Instruction formats                                                                                                                                            | 6.3  | Instruction Formats                       |

| List of<br>instructions        | Instruction sets                                                                                                                                               | 7.1  | Instruction Set by<br>Classification      |

|                                |                                                                                                                                                                | 7.2  | Instruction Set in Alphabetical Order     |

| Detailed                       | Detailed information of instruction                                                                                                                            | 8.   | Instruction Description                   |

| information on<br>instructions | operation                                                                                                                                                      | 10.7 | Instruction Pipelines                     |

| IIISUUCUOIIS                   | Number of instruction execution states                                                                                                                         | 10.3 | Number of Instruction<br>Execution Cycles |

# Table 2Subjects and Corresponding Sections

# Main Revisions for This Edition

| Item | Page | Revision (See Manual for Details)                                     |

|------|------|-----------------------------------------------------------------------|

| All  | _    | <ul> <li>Notification of change in company name amended</li> </ul>    |

|      |      | (Before) Hitachi, Ltd. $\rightarrow$ (After) Renesas Technology Corp. |

Rev. 4.00 May 15, 2006 page vii of xviii

Rev. 4.00 May 15, 2006 page viii of xviii

# Contents

| Secti | on 1    | Features                                       | 1  |

|-------|---------|------------------------------------------------|----|

| 1.1   | SH-3 (  | CPU Features                                   | 1  |

| 1.2   | SH3-D   | SP Features                                    | 2  |

| Secti | on 2    | Programming Model                              | 5  |

| 2.1   |         | zation of Registers                            | 5  |

|       | 2.1.1   | Privileged Mode and Banks                      | 5  |

| 2.2   | Genera  | I-Purpose Registers                            | 11 |

| 2.3   |         | l Registers                                    | 13 |

| 2.4   |         | n Registers                                    | 15 |

| 2.5   |         | Register Value                                 | 16 |

| Secti | on 3    | Data Formats                                   | 17 |

| 3.1   | Data F  | ormat in Registers                             | 17 |

| 3.2   | Data F  | ormat in Memory                                | 17 |

| 3.3   | Data F  | ormat for Immediate Data                       | 18 |

| 3.4   | DSP T   | ype Data Formats (SH3-DSP Only)                | 18 |

| Secti | on 4    | Floating Point Unit (SH-3E Only)               | 21 |

| 4.1   | Introdu | iction                                         | 21 |

| 4.2   | Floatin | g Point Registers and System Registers for FPU | 22 |

|       | 4.2.1   | Floating Point Register File                   | 22 |

|       | 4.2.2   | Floating Point Communication Register (FPUL)   | 22 |

|       | 4.2.3   | Floating Point Status/Control Register (FPSCR) | 22 |

| 4.3   | Floatin | g Point Format                                 | 24 |

|       | 4.3.1   | Floating Point Format                          | 24 |

|       | 4.3.2   | Not a Number (NaN)                             | 25 |

|       | 4.3.3   | Denormalized Values                            | 25 |

|       | 4.3.4   | Other Special Values                           | 25 |

| 4.4   | Floatin | g Point Exception Model                        | 26 |

|       | 4.4.1   | Enabled Exception                              | 26 |

|       | 4.4.2   | Disabled Exception                             | 26 |

|       | 4.4.3   | Exception Event and Code for FPU               | 27 |

|       | 4.4.4   | Alignment of Floating Point Data in Memory     | 27 |

|       | 4.4.5   | Arithmetic with Special Operands               | 27 |

| 4.5   | Synchr  | onization Issues                               | 27 |

| Secti | on 5    | DSP Operation Functions and Data Transfers (SH3-DSP Only) | 29 |

|-------|---------|-----------------------------------------------------------|----|

| 5.1   | ALU F   | ixed Decimal Point Operations                             | 30 |

|       | 5.1.1   | Function                                                  | 30 |

|       | 5.1.2   | Instructions and Operands                                 | 32 |

|       | 5.1.3   | DC Bit                                                    | 32 |

|       | 5.1.4   | Condition Bits                                            | 35 |

|       | 5.1.5   | Overflow Prevention Function (Saturation Operation)       | 35 |

| 5.2   | ALU I   | nteger Operations                                         | 35 |

| 5.3   | ALU I   | ogical Operations                                         | 37 |

|       | 5.3.1   | Function                                                  | 37 |

|       | 5.3.2   | Instructions and Operands                                 | 38 |

|       | 5.3.3   | DC Bit                                                    | 39 |

|       | 5.3.4   | Condition Bits                                            | 39 |

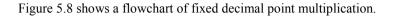

| 5.4   | Fixed I | Decimal Point Multiplication                              | 39 |

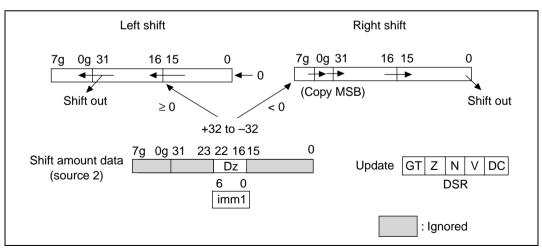

| 5.5   | Shift C | perations                                                 | 41 |

|       | 5.5.1   | Arithmetic Shift Operations                               | 42 |

|       | 5.5.2   | Logical Shift Operations                                  | 44 |

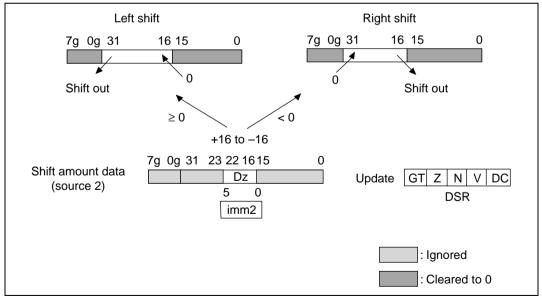

| 5.6   | The M   | SB Detection Instruction                                  | 45 |

|       | 5.6.1   | Function                                                  | 45 |

|       | 5.6.2   | Instructions and Operands                                 | 49 |

|       | 5.6.3   | DC Bit                                                    | 49 |

|       | 5.6.4   | Condition Bits                                            | 50 |

| 5.7   | Round   | ing                                                       | 50 |

|       | 5.7.1   | Operation Function                                        | 50 |

|       | 5.7.2   | Instructions and Operands                                 | 52 |

|       | 5.7.3   | DC Bit                                                    | 52 |

|       | 5.7.4   | Condition Bits                                            | 53 |

|       | 5.7.5   | Overflow Prevention Function (Saturation Operation)       | 53 |

| 5.8   | Condit  | ion Select Bits (CS) and the DSP Condition Bit (DC)       | 53 |

| 5.9   | Overfl  | ow Prevention Function (Saturation Operation)             | 55 |

| 5.10  | Data T  | ransfers                                                  | 56 |

|       | 5.10.1  | X and Y Memory Data Transfer                              | 56 |

|       | 5.10.2  | Single Data Transfers                                     | 57 |

| 5.11  |         | nd Contention                                             | 60 |

| 5.12  | DSP R   | epeat (Loop) Control                                      | 61 |

|       |         | Usage Notes                                               | 65 |

| 5.13  | Condit  | ional Instructions and Data Transfers                     | 69 |

| Secti | on f    | Instruction Fostures                                      | 71 |

| Secti |         | Instruction Features                                      | 71 |

| 6.1   |         | Γype Instruction Set                                      | 71 |

|       | 6.1.1   | 16-Bit Fixed Length                                       | 71 |

|      | 6.1.2   | One Instruction/Cycle                                      | . 71 |

|------|---------|------------------------------------------------------------|------|

|      | 6.1.3   | Data Length                                                | . 71 |

|      | 6.1.4   | Load-Store Architecture                                    | . 72 |

|      | 6.1.5   | Delayed Branch Instructions                                | . 72 |

|      | 6.1.6   | Multiplication/Accumulation Operation                      | . 72 |

|      | 6.1.7   | T Bit                                                      | . 72 |

|      | 6.1.8   | Immediate Data                                             | . 73 |

|      | 6.1.9   | Absolute Address                                           | . 73 |

|      | 6.1.10  | 16-Bit/32-Bit Displacement                                 | . 74 |

|      | 6.1.11  | Privileged Instructions                                    | . 74 |

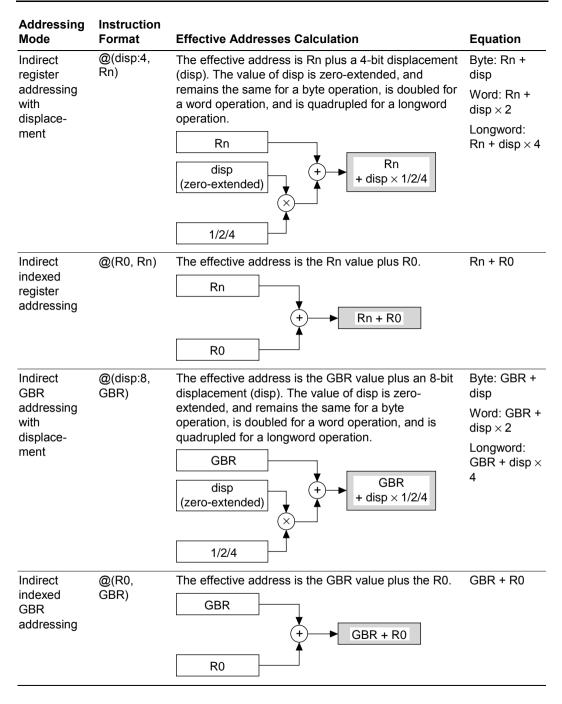

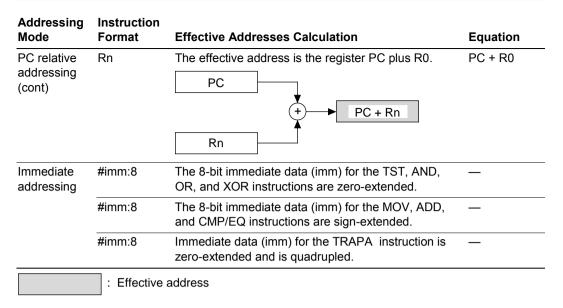

| 6.2  | CPU Ir  | struction Addressing Modes                                 | . 75 |

| 6.3  | DSP D   | ata Addressing (SH3-DSP Only)                              | . 78 |

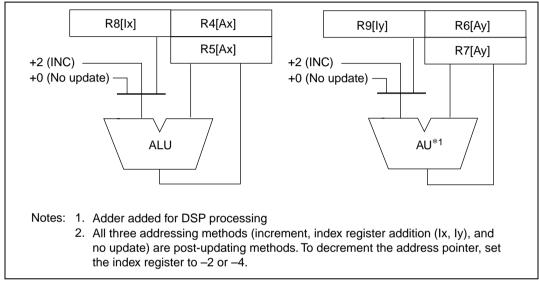

|      | 6.3.1   | X and Y Data Addressing                                    | . 79 |

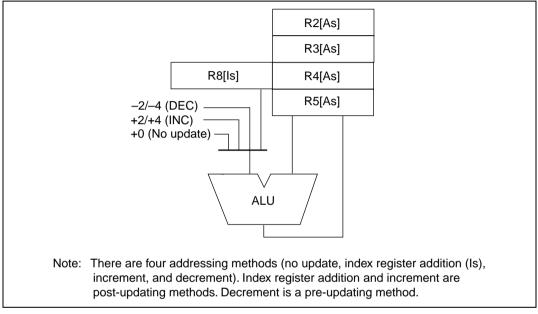

|      | 6.3.2   | Single Data Addressing                                     | . 80 |

|      | 6.3.3   | Modulo Addressing                                          | . 81 |

|      | 6.3.4   | DSP Addressing Operation                                   | . 83 |

| 6.4  | Instruc | tion Format of CPU Instructions                            |      |

| 6.5  |         | tion Formats for DSP Instructions (SH3-DSP Only)           |      |

|      | 6.5.1   | Double and Single Data Transfer Instructions               |      |

|      | 6.5.2   | Parallel Processing Instructions                           | . 91 |

| Sect | ion 7   | Instruction Set                                            | . 95 |

| 7.1  |         | tion Set by Classification                                 |      |

| /    | 7.1.1   | Data Transfer Instructions                                 |      |

|      | 7.1.2   | Arithmetic Instructions                                    |      |

|      | 7.1.3   | Logic Operation Instructions                               |      |

|      | 7.1.4   | Shift Instructions                                         |      |

|      | 7.1.5   | Branch Instructions                                        |      |

|      | 7.1.6   | System Control Instructions                                |      |

|      | 7.1.7   | Floating Point Instructions (SH-3E Only)                   |      |

|      | 7.1.8   | FPU System Register Related CPU Instructions (SH-3E Only)  |      |

|      | 7.1.9   | CPU Instructions That Support DSP Functions (SH3-DSP Only) |      |

| 7.2  |         | tion Set in Alphabetical Order                             |      |

| 7.3  |         | ata Transfer Instruction Set (SH3-DSP Only)                |      |

|      |         | Double Data Transfer Instructions (X Memory Data)          |      |

|      | 7.3.2   | Double Data Transfer Instructions (Y Memory Data)          |      |

|      | 7.3.3   | Single Data Transfer Instructions.                         |      |

| 7.4  |         | peration Instruction Set (SH3-DSP Only)                    |      |

|      | 7.4.1   | ALU Arithmetic Operation Instructions                      |      |

|      | 7.4.2   | ALU Logical Operation Instructions                         |      |

|      | 7.4.3   | Fixed Decimal Point Multiplication Instructions            |      |

|      |         | 1                                                          |      |

Rev. 4.00 May 15, 2006 page xi of xviii

|      | 7.4.4    | Shift Operation Instructions                                             | 137 |

|------|----------|--------------------------------------------------------------------------|-----|

|      | 7.4.5    | System Control Instructions                                              | 139 |

|      | 7.4.6    | NOPX and NOPY Instruction Code                                           | 140 |

| Sect | ion 8    | Instruction Descriptions                                                 | 141 |

| 8.1  | Sample   | e Description (Name): Classification                                     | 141 |

| 8.2  | Instruc  | tion Description (Listing and Description of Instructions Common         |     |

|      | to the S | SH-3, SH-3E and SH3-DSP)                                                 | 145 |

|      | 8.2.1    | ADD (Add Binary): Arithmetic Instruction                                 | 145 |

|      | 8.2.2    | ADDC (Add with Carry): Arithmetic Instruction                            | 146 |

|      | 8.2.3    | ADDV (Add with V Flag Overflow Check): Arithmetic Instruction            | 147 |

|      | 8.2.4    | AND (AND Logical): Logic Operation Instruction                           | 148 |

|      | 8.2.5    | BF (Branch if False): Branch Instruction                                 | 150 |

|      | 8.2.6    | BF/S (Branch if False with Delay Slot): Branch Instruction               | 151 |

|      | 8.2.7    | BRA (Branch): Branch Instruction                                         | 153 |

|      | 8.2.8    | BRAF (Branch Far): Branch Instruction                                    | 155 |

|      | 8.2.9    | BSR (Branch to Subroutine): Branch Instruction                           | 157 |

|      | 8.2.10   | BSRF (Branch to Subroutine Far): Branch Instruction                      |     |

|      | 8.2.11   | BT (Branch if True): Branch Instruction                                  | 161 |

|      | 8.2.12   | BT/S (Branch if True with Delay Slot): Branch Instruction                | 162 |

|      | 8.2.13   | CLRMAC (Clear MAC Register): System Control Instruction                  | 164 |

|      | 8.2.14   | CLRS (Clear S Bit): System Control Instruction                           | 165 |

|      | 8.2.15   | CLRT (Clear T Bit): System Control Instruction                           | 166 |

|      | 8.2.16   | CMP/cond (Compare Conditionally): Arithmetic Instruction                 | 167 |

|      | 8.2.17   | DIV0S (Divide Step 0 as Signed): Arithmetic Instruction                  | 171 |

|      | 8.2.18   | DIV0U (Divide Step 0 as Unsigned): Arithmetic Instruction                | 172 |

|      | 8.2.19   | DIV1 (Divide Step 1): Arithmetic Instruction                             | 173 |

|      | 8.2.20   | DMULS.L (Double-Length Multiply as Signed): Arithmetic Instruction       | 178 |

|      | 8.2.21   | DMULU.L (Double-Length Multiply as Unsigned): Arithmetic Instruction     | 180 |

|      | 8.2.22   | DT (Decrement and Test): Arithmetic Instruction                          | 182 |

|      | 8.2.23   | EXTS (Extend as Signed): Arithmetic Instruction                          | 183 |

|      | 8.2.24   | EXTU (Extend as Unsigned): Arithmetic Instruction                        | 184 |

|      | 8.2.25   | JMP (Jump): Branch Instruction                                           | 185 |

|      | 8.2.26   | JSR (Jump to Subroutine): Branch Instruction                             | 187 |

|      | 8.2.27   | LDC (Load to Control Register): System Control Instruction               |     |

|      |          | (Privileged Only)                                                        | 189 |

|      | 8.2.28   | LDRE (Load Effective Address to RE Register): System Control Instruction |     |

|      |          | (SH3-DSP Only)                                                           | 195 |

|      | 8.2.29   | LDRS (Load Effective Address to RS Register): System Control Instruction |     |

|      |          | (SH3-DSP Only)                                                           | 197 |

|      | 8.2.30   | LDS (Load to System Register): System Control Instruction                |     |

| 8.2.31 | LDTLB (Load PTEH/PTEL to TLB): System Control Instruction                  |     |

|--------|----------------------------------------------------------------------------|-----|

|        | (Privileged Only)                                                          | 204 |

| 8.2.32 | MAC.L (Multiply and Accumulate Long): Arithmetic Instruction               | 205 |

| 8.2.33 | MAC (Multiply and Accumulate): Arithmetic Instruction                      | 208 |

| 8.2.34 | MOV (Move Data): Data Transfer Instruction                                 | 211 |

| 8.2.35 | MOV (Move Immediate Data): Data Transfer Instruction                       | 216 |

| 8.2.36 | MOV (Move Peripheral Data): Data Transfer Instruction                      | 219 |

| 8.2.37 | MOV (Move Structure Data): Data Transfer Instruction                       | 222 |

| 8.2.38 | MOVA (Move Effective Address): Data Transfer Instruction                   | 225 |

| 8.2.39 | MOVT (Move T Bit): Data Transfer Instruction                               | 226 |

| 8.2.40 | MUL.L (Multiply Long): Arithmetic Instruction                              | 227 |

| 8.2.41 | MULS.W (Multiply as Signed Word): Arithmetic Instruction                   | 228 |

| 8.2.42 | MULU.W (Multiply as Unsigned Word): Arithmetic Instruction                 | 229 |

| 8.2.43 | NEG (Negate): Arithmetic Instruction                                       | 230 |

| 8.2.44 | NEGC (Negate with Carry): Arithmetic Instruction                           | 231 |

| 8.2.45 | NOP (No Operation): System Control Instruction                             | 232 |

| 8.2.46 | NOT (NOT-Logical Complement): Logic Operation Instruction                  | 233 |

| 8.2.47 | OR (OR Logical) Logic Operation Instruction                                | 234 |

| 8.2.48 | PREF (Prefetch Data to the Cache)                                          | 236 |

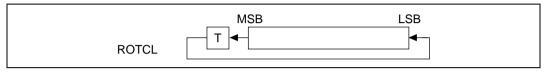

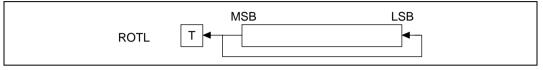

| 8.2.49 | ROTCL (Rotate with Carry Left): Shift Instruction                          | 237 |

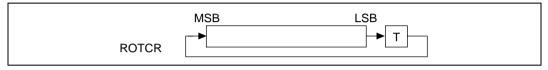

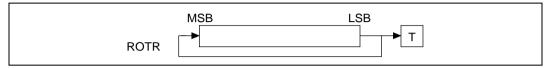

| 8.2.50 | ROTCR (Rotate with Carry Right): Shift Instruction                         | 238 |

| 8.2.51 | ROTL (Rotate Left): Shift Instruction                                      | 239 |

| 8.2.52 | ROTR (Rotate Right): Shift Instruction                                     | 240 |

| 8.2.53 | RTE (Return from Exception): System Control Instruction (Privileged Only)  | 241 |

| 8.2.54 | RTS (Return from Subroutine): Branch Instruction                           | 243 |

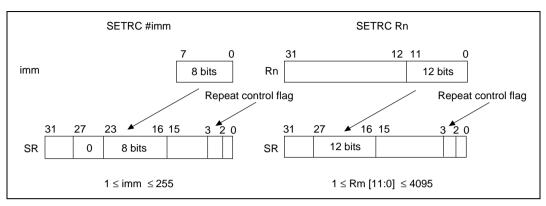

| 8.2.55 | SETRC (Set Repeat Count to RC): System Control Instruction                 |     |

|        | (SH3-DSP Only)                                                             | 245 |

| 8.2.56 | SETS (Set S Bit): System Control Instruction                               | 247 |

| 8.2.57 | SETT (Set T Bit): System Control Instruction                               | 248 |

| 8.2.58 | SHAD (Shift Arithmetic Dynamically): Shift Instruction                     | 249 |

| 8.2.59 | SHAL (Shift Arithmetic Left): Shift Instruction                            | 251 |

| 8.2.60 | SHAR (Shift Arithmetic Right): Shift Instruction                           | 252 |

| 8.2.61 | SHLD (Shift Logical Dynamically): Shift Instruction                        | 253 |

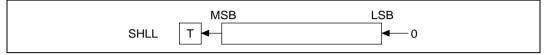

| 8.2.62 | SHLL (Shift Logical Left): Shift Instruction                               | 255 |

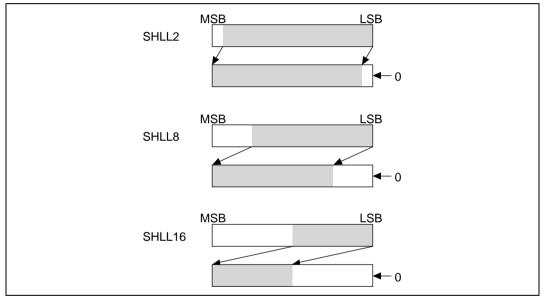

| 8.2.63 | SHLLn (Shift Logical Left n Bits): Shift Instruction                       | 256 |

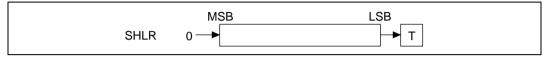

| 8.2.64 | SHLR (Shift Logical Right): Shift Instruction                              | 258 |

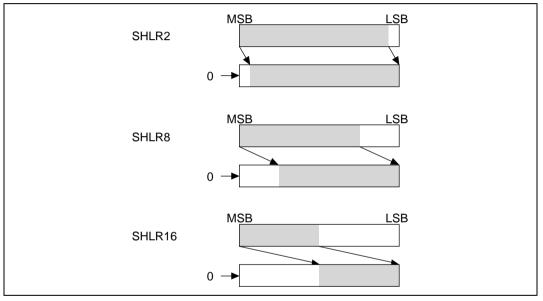

| 8.2.65 | SHLRn (Shift Logical Right n Bits): Shift Instruction                      |     |

| 8.2.66 | SLEEP (Sleep): System Control Instruction (Privileged Only)                |     |

| 8.2.67 | STC (Store Control Register): System Control Instruction (Privileged Only) | 262 |

| 8.2.68 | STS (Store System Register): System Control Instruction                    | 267 |

| 8.2.69 | SUB (Subtract Binary): Arithmetic Instruction                              |     |

Rev. 4.00 May 15, 2006 page xiii of xviii

|     | 8.2.70   | SUBC (Subtract with Carry): Arithmetic Instruction                        | 273 |

|-----|----------|---------------------------------------------------------------------------|-----|

|     | 8.2.71   | SUBV (Subtract with V Flag Underflow Check): Arithmetic Instruction       | 274 |

|     | 8.2.72   | SWAP (Swap Register Halves): Data Transfer Instruction                    | 276 |

|     | 8.2.73   | TAS (Test and Set): Logic Operation Instruction                           |     |

|     | 8.2.74   | TRAPA (Trap Always): System Control Instruction                           | 279 |

|     | 8.2.75   | TST (Test Logical): Logic Operation Instruction                           | 280 |

|     | 8.2.76   | XOR (Exclusive OR Logical): Logic Operation Instruction                   | 282 |

|     | 8.2.77   | XTRCT (Extract): Data Transfer Instruction                                | 284 |

| 8.3 | Floating | g Point Instructions and FPU Related CPU Instructions (SH-3E Only)        | 285 |

|     | 8.3.1    | FABS (Floating Point Absolute Value): Floating Point Instruction          | 287 |

|     | 8.3.2    | FADD (Floating Point Add): Floating Point Instruction                     | 289 |

|     | 8.3.3    | FCMP (Floating Point Compare): Floating Point Instruction                 | 292 |

|     | 8.3.4    | FDIV (Floating Point Divide): Floating Point Instruction                  | 296 |

|     | 8.3.5    | FLDI0 (Floating Point Load Immediate 0): Floating Point Instruction       | 298 |

|     | 8.3.6    | FLDI1 (Floating Point Load Immediate 1): Floating Point Instruction       | 299 |

|     | 8.3.7    | FLDS (Floating Point Load to System Register): Floating Point Instruction | 300 |

|     | 8.3.8    | FLOAT (Floating Point Convert from Integer): Floating Point Instruction   | 301 |

|     | 8.3.9    | FMAC (Floating Point Multiply Accumulate): Floating Point Instruction     | 302 |

|     | 8.3.10   | FMOV (Floating Point Move): Floating Point Instruction                    | 305 |

|     | 8.3.11   | FMUL (Floating Point Multiply): Floating Point Instruction                | 309 |

|     | 8.3.12   | FNEG (Floating Point Negate): Floating Point Instruction                  | 311 |

|     | 8.3.13   | FSQRT (Floating Point Square Root): Floating Point Instruction            | 312 |

|     | 8.3.14   | FSTS (Floating Point Store From System Register): Floating Point          |     |

|     |          | Instruction                                                               | 314 |

|     | 8.3.15   | FSUB (Floating Point Subtract): Floating Point Instruction                | 315 |

|     | 8.3.16   | FTRC (Floating Point Truncate And Convert To Integer):                    |     |

|     |          | Floating Point Instruction                                                | 318 |

|     | 8.3.17   | LDS (Load to System Register): FPU Related CPU Instruction                | 320 |

|     | 8.3.18   | STS (Store from FPU System Register): FPU Related CPU Instruction         | 323 |

| 8.4 | DSP Da   | ata Transfer Instructions (SH3-DSP Only)                                  | 326 |

|     | 8.4.1    | MOVS (Move Single Data between Memory and DSP Register):                  |     |

|     |          | DSP Data Transfer Instruction                                             | 333 |

|     | 8.4.2    | MOVX (Move between X Memory and DSP Register):                            |     |

|     |          | DSP Data Transfer Instruction                                             | 335 |

|     | 8.4.3    | MOVY (Move between Y Memory and DSP Register):                            |     |

|     |          | DSP Data Transfer Instruction                                             | 336 |

|     | 8.4.4    | NOPX (No Access Operation for X Memory): DSP Data Transfer Instruction    |     |

|     | 8.4.5    | NOPY (No Access Operation for Y Memory): DSP Data Transfer Instruction    |     |

| 8.5 | -        | peration Instructions                                                     |     |

|     | 8.5.1    | PABS (Absolute): DSP Arithmetic Operation Instruction                     | 351 |

|     | 8.5.2  | [if cc]PADD (Addition with Condition): DSP Arithmetic Operation              |     |

|-----|--------|------------------------------------------------------------------------------|-----|

|     |        | Instruction                                                                  | 354 |

|     | 8.5.3  | PADD PMULS (Addition & Multiply Signed by Signed): DSP Arithmetic            |     |

|     |        | Operation Instruction                                                        | 357 |

|     | 8.5.4  | PADDC (Addition with Carry): DSP Arithmetic Operation Instruction            | 359 |

|     | 8.5.5  | [if cc] PAND (Logical AND): DSP Logical Operation Instruction                | 362 |

|     | 8.5.6  | [if cc] PCLR (Clear): DSP Arithmetic Operation Instruction                   | 365 |

|     | 8.5.7  | PCMP (Compare Two Data): DSP Arithmetic Operation Instruction                | 367 |

|     | 8.5.8  | [if cc] PCOPY (Copy with Condition): DSP Arithmetic Operation Instruction    | 369 |

|     | 8.5.9  | [if cc] PDEC (Decrement by 1): DSP Arithmetic Operation Instruction          | 372 |

|     | 8.5.10 | [if cc] PDMSB (Detect MSB with Condition): DSP Arithmetic Operation          |     |

|     |        | Instruction                                                                  | 375 |

|     | 8.5.11 | [if cc] PINC (Increment by 1 with Condition): DSP Arithmetic Operation       |     |

|     |        | Instruction                                                                  | 379 |

|     | 8.5.12 | [if cc] PLDS (Load System Register): DSP System Control Instruction          | 382 |

|     | 8.5.13 | PMULS (Multiply Signed by Signed): DSP Arithmetic Operation Instruction      | 384 |

|     | 8.5.14 | [if cc] PNEG (Negate): DSP Arithmetic Operation Instruction                  | 385 |

|     | 8.5.15 | [if cc] POR (Logical OR): DSP Logical Operation Instruction                  | 388 |

|     | 8.5.16 | PRND (Rounding): DSP Arithmetic Operation Instruction                        | 391 |

|     | 8.5.17 | [if cc] PSHA (Shift Arithmetically with Condition): DSP Arithmetic Shift     |     |

|     |        | Instruction                                                                  | 394 |

|     | 8.5.18 | [if cc] PSHL (Shift Logically with Condition): DSP Logical Shift Instruction | 400 |

|     | 8.5.19 | [if cc] PSTS (Store System Register): DSP System Control Instruction         | 405 |

|     | 8.5.20 | [if cc]PSUB (Subtract with Condition): DSP Arithmetic Operation              |     |

|     |        | Instruction                                                                  | 408 |

|     | 8.5.21 | PSUB PMULS (Subtraction & Multiply Signed by Signed): DSP Arithmetic         |     |

|     |        | Operation Instruction                                                        | 411 |

|     | 8.5.22 | PSUBC (Subtraction with Carry): DSP Arithmetic Operation Instruction         | 413 |

|     | 8.5.23 | [if cc] PXOR (Logical Exclusive OR): DSP Logical Operation Instruction       | 415 |

| G4  | 0 1    | Drease in a States                                                           | 410 |

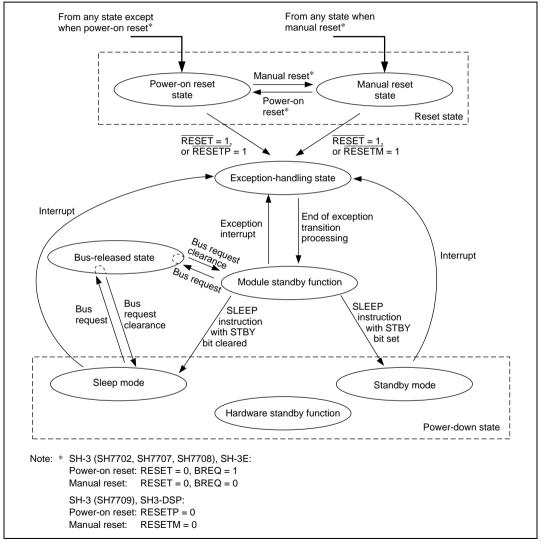

|     |        | Processing States                                                            |     |

| 9.1 |        | ransitions                                                                   |     |

|     | 9.1.1  | Reset State                                                                  |     |

|     | 9.1.2  | Exception Processing State                                                   |     |

|     | 9.1.3  | Program Execution State                                                      |     |

|     | 9.1.4  | Power-Down State                                                             |     |

|     | 9.1.5  | Bus Release State                                                            |     |

| 9.2 |        |                                                                              |     |

|     | 9.2.1  | Sleep Mode                                                                   |     |

|     | 9.2.2  | Standby Mode                                                                 |     |

|     | 9.2.3  | Hardware Standby Mode                                                        | 421 |

Rev. 4.00 May 15, 2006 page xv of xviii

|       | 9.2.4   | Module Standby Function                                                   | 422 |

|-------|---------|---------------------------------------------------------------------------|-----|

| Secti | on 10   | Pipeline Operation                                                        | 423 |

| 10.1  |         | Configuration of Pipelines                                                |     |

|       |         | Five-Stage Pipeline                                                       |     |

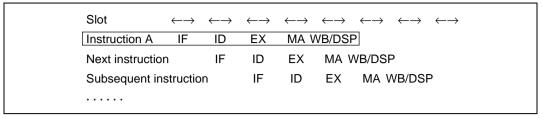

|       | 10.1.2  | Slot and Pipeline Flow                                                    | 424 |

|       |         | Number of Cycles Required for Execution of One Slot                       |     |

|       |         | Number of Instruction Execution Cycles                                    |     |

| 10.2  |         | tion                                                                      |     |

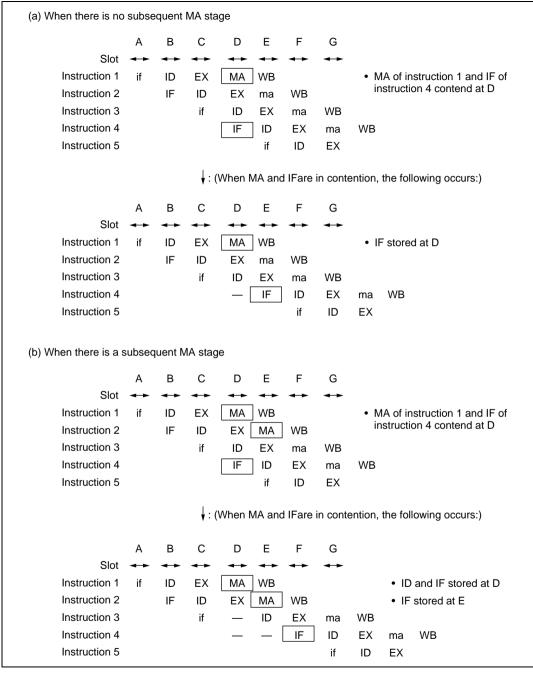

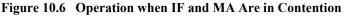

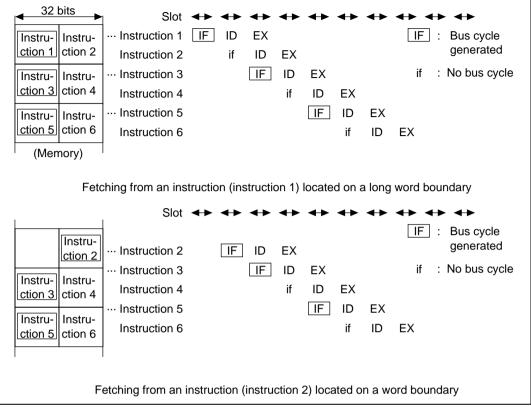

|       | 10.2.1  | Contention between Instruction Fetch (IF) and Memory Access (MA)          | 427 |

|       | 10.2.2  | Effects of Memory Load Instructions on Pipelines                          | 431 |

|       |         | Contention due to SR Update Instructions                                  |     |

|       | 10.2.4  | Multiplier Access Contention                                              | 432 |

|       | 10.2.5  | FPU Contention (SH-3E Only)                                               | 433 |

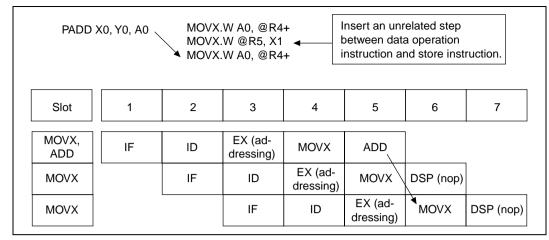

|       | 10.2.6  | Contention between DSP Data Operation Instructions and Store Instructions |     |

|       |         | (SH3-DSP Only)                                                            | 435 |

|       | 10.2.7  | Relationship between Load and Store Instructions (SH3-DSP Only)           | 436 |

| 10.3  | Program | nming Guidelines                                                          | 437 |

|       | 10.3.1  | Correspondence between Contention and Instructions                        | 437 |

|       | 10.3.2  | Increasing Instruction Execution Speed                                    | 440 |

|       | 10.3.3  | Number of Cycles                                                          | 440 |

| 10.4  | Operati | on of Instruction Pipelines                                               | 441 |

|       | 10.4.1  | Data Transfer Instructions                                                | 458 |

|       | 10.4.2  | Arithmetic Instructions                                                   | 463 |

|       | 10.4.3  | Logic Operation Instructions                                              | 469 |

|       | 10.4.4  | Shift Instructions                                                        | 474 |

|       | 10.4.5  | Branch Instructions                                                       | 476 |

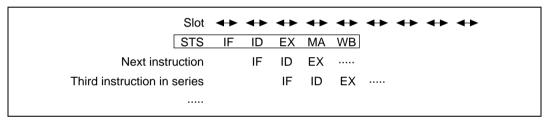

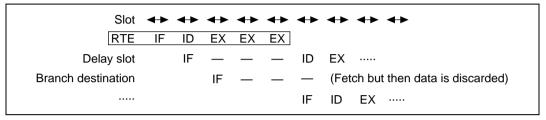

|       | 10.4.6  | System Control Instructions                                               | 481 |

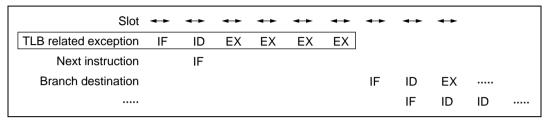

|       | 10.4.7  | Exception Processing                                                      | 496 |

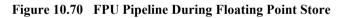

|       | 10.4.8  | Pipeline for FPU Instructions (SH-3E Only)                                | 500 |

|       | 10.4.9  | DSP Data Transfer Instructions (SH3-DSP Only)                             | 502 |

|       | 10.4.10 | DSP Operation Instructions (SH3-DSP Only)                                 | 508 |

| Appe  | endix A | Instruction Code                                                          | 515 |

|       |         | tion Set by Addressing Mode                                               | 515 |

|       | A.1.1   | No Operand                                                                |     |

|       | A.1.2   | Direct Register Addressing                                                |     |

|       | A.1.3   | Indirect Register Addressing                                              |     |

|       | A.1.4   | Post-Increment Indirect Register Addressing                               |     |

|       | A.1.5   | Pre-Decrement Indirect Register Addressing                                |     |

|       | A.1.6   | Indirect Register Addressing with Displacement                            |     |

|       |         |                                                                           |     |

Rev. 4.00 May 15, 2006 page xvi of xviii

|     | A.1.7    | Indirect Indexed Register Addressing      | 528 |

|-----|----------|-------------------------------------------|-----|

|     | A.1.8    | Indirect GBR Addressing with Displacement | 528 |

|     | A.1.9    | Indirect Indexed GBR Addressing           | 529 |

|     | A.1.10   | PC Relative Addressing with Displacement  | 529 |

|     | A.1.11   | PC Relative Addressing                    | 529 |

|     | A.1.12   | Immediate                                 | 530 |

| A.2 | Instruct | tion Sets by Instruction Format           | 532 |

|     | A.2.1    | 0 Format                                  | 533 |

|     | A.2.2    | n Format                                  | 534 |

|     | A.2.3    | m Format                                  | 538 |

|     | A.2.4    | nm Format                                 | 541 |

|     | A.2.5    | md Format                                 | 545 |

|     | A.2.6    | nd4 Format                                | 545 |

|     | A.2.7    | nmd Format                                | 545 |

|     | A.2.8    | d Format                                  | 546 |

|     | A.2.9    | d12 Format                                | 547 |

|     | A.2.10   | nd8 Format                                | 547 |

|     | A.2.11   | i Format                                  | 547 |

|     | A.2.12   | ni Format                                 | 548 |

| A.3 | Operati  | ion Code Map                              | 549 |

| App | endix E  | B Pipeline Operation and Contention       | 555 |

# Section 1 Features

# 1.1 SH-3 CPU Features

The SH-3/SH-3E/SH3-DSP has RISC-type instruction sets. Basic instructions are executed in one clock cycle, which dramatically improves instruction execution speed. The CPU also has an internal 32-bit architecture for enhanced data processing ability. Table 1.1 lists the SH-3/SH-3E/SH3-DSP CPU features.

| Feature                    | Description                                                                                                                                                                                                         |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Architecture               | Renesas Technology original architecture                                                                                                                                                                            |

|                            | • 32-bit internal data bus                                                                                                                                                                                          |

| General-register machine   | Sixteen 32-bit general registers (eight banked registers)                                                                                                                                                           |

|                            | Five 32-bit control registers                                                                                                                                                                                       |

|                            | Four 32-bit system registers (SH-3)                                                                                                                                                                                 |

|                            | Six 32-bit system registers (SH-3E)                                                                                                                                                                                 |

| Instruction set            | Instruction length: 16-bit fixed length for improved code efficiency                                                                                                                                                |

|                            | • Load-store architecture (basic arithmetic and logic operations are executed between registers)                                                                                                                    |

|                            | Delayed branch system used for reduced pipeline disruption                                                                                                                                                          |

|                            | Instruction set optimized for C language                                                                                                                                                                            |

| Instruction execution time | One instruction/cycle for basic instructions                                                                                                                                                                        |

| Address space              | Architecture makes 4 Gbytes available                                                                                                                                                                               |

| On-chip multiplier         | <ul> <li>Multiplication operations (32 bits × 32 bits → 64 bits) executed in 2 to 5 cycles, and multiplication/accumulation operations (32 bits × 32 bits + 64 bits → 64 bits) executed in 2 to 5 cycles</li> </ul> |

| Pipeline                   | Five-stage pipeline                                                                                                                                                                                                 |

| Processing states          | Reset state                                                                                                                                                                                                         |

|                            | Exception processing state                                                                                                                                                                                          |

|                            | Program execution state                                                                                                                                                                                             |

|                            | Power-down state                                                                                                                                                                                                    |

|                            | Bus release state                                                                                                                                                                                                   |

# Table 1.1 SH-3/SH-3E/SH3-DSP CPU Features

| Feature           | Description                                                                                                          |

|-------------------|----------------------------------------------------------------------------------------------------------------------|

| Power-down states | Sleep mode                                                                                                           |

|                   | Standby mode                                                                                                         |

|                   | Hardware standby mode                                                                                                |

| FPU (SH-3E only)  | Single-precision floating point format                                                                               |

|                   | Subset of IEEE754 standard data types                                                                                |

|                   | <ul> <li>Invalid calculation exception and divide-by-zero exception (in compliance with IEEE754 standard)</li> </ul> |

|                   | Rounding to zero (in compliance with IEEE754 standard)                                                               |

|                   | General purpose register file, 16 32-bit floating point registers                                                    |

|                   | <ul> <li>Execution pitch for basic instructions: 1 cycle/latency or 2 cycles<br/>(FADD, FSUB, FMUL)</li> </ul>       |

|                   | FMAC (floating point multiply accumulate)                                                                            |

|                   | Execution pitch: 1 cycle/latency or 2 cycles                                                                         |

|                   | Support for FDIV and FSQRT                                                                                           |

|                   | <ul> <li>Support for FLDI0 and FLDI1 (load constant 0/1)</li> </ul>                                                  |

# **1.2 SH3-DSP Features**

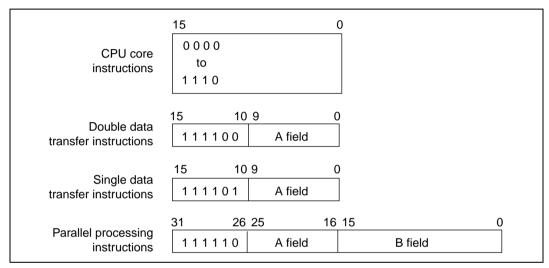

The SH3 CPU only has 16-bit instructions. The SH3-DSP basically has the same 16-bit instructions, but it also has additional 32-bit DSP instructions that it uses for parallel processing of DSP type instructions. The SH3 CPU use a standard Neumann architecture, but the SH3-DSP has the DSP data paths of the expanded Harvard architecture. Table 1.2 lists the added features of SH3-DSP.

| Feature             | Description                                                                                                                 |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------|

| DSP unit            | Multiplier                                                                                                                  |

|                     | Arithmetic logic unit (ALU)                                                                                                 |

|                     | Barrel shifter                                                                                                              |

|                     | DSP registers                                                                                                               |

|                     | MSB detection                                                                                                               |

| Multiplier          | • 16 bits $\times$ 16 bits $\rightarrow$ 32 bits (fixed decimal point)                                                      |

|                     | 1 cycle multiplier                                                                                                          |

| DSP registers       | Two 40-bit data registers                                                                                                   |

|                     | Six 32-bit data registers                                                                                                   |

|                     | <ul> <li>Modulo register (MOD, 32 bits) added to control registers</li> </ul>                                               |

|                     | <ul> <li>Repeat counter (RC) added to status registers (SR)</li> </ul>                                                      |

|                     | <ul> <li>Repeat start register (RS, 32-bit) and repeat end register (RE, 32-<br/>bit) added to control registers</li> </ul> |

| DSP data bus        | Expanded Harvard architecture                                                                                               |

|                     | Simultaneous access of two data bus and one instruction bus                                                                 |

| On-chip memory      | 16-kbyte RAM                                                                                                                |

| Parallel processing | <ul> <li>Maximum of four parallel processes (ALU operation, multiplication,<br/>and two loads or stores)</li> </ul>         |

| Address operator    | Two address operators                                                                                                       |

|                     | Address operations for accessing two memories                                                                               |

| DSP data addressing | Increment decrement and index                                                                                               |

| modes               | <ul> <li>Increment decrement and index can have modulo addressing or<br/>not</li> </ul>                                     |

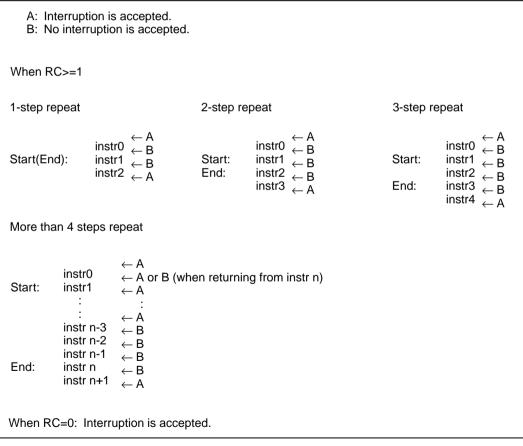

| Repeat control      | Zero-overhead repeat control (loop)                                                                                         |

| Instruction set     | • 16 or 32 bits                                                                                                             |

|                     | <ul> <li>— 16 bits (for load or store only)</li> </ul>                                                                      |

|                     | <ul> <li>— 32 bits (including for ALU operations and multiplication)</li> </ul>                                             |

|                     | <ul> <li>SuperH microprocessor instructions added for accessing DSP registers.</li> </ul>                                   |

| Pipeline            | Five-stage pipeline                                                                                                         |

|                     | Fifth stage is the DSP stage                                                                                                |

|                     |                                                                                                                             |

# Table 1.2 Features of SH3-DSP Series Microprocessor CPUs

# Section 2 Programming Model

# 2.1 Organization of Registers

# 2.1.1 Privileged Mode and Banks

**Processing Modes**: The SH-3/SH-3E/SH3-DSP has two operating modes: user mode and privileged mode. The SH-3/SH-3E/SH3-DSP operates in user mode under normal conditions and enters privileged mode in response to an exception or interrupt. There are three types of registers: general, system, and control. All of these registers are 32 bits. Which registers can be accessed through software depends on the processing mode.

**General-Purpose Registers**: There are 16 general-purpose registers, numbered R0 through R15. General-purpose registers R0 to R7 are banked registers that are switched by the processor mode.

In privileged mode, the register bank (RB) bit in the status register (SR) defines which banked registers can be accessed as general-purpose registers and which cannot. Inaccessible registers can be accessed through the load control register (LDC) and store control register (STC) instructions.

When the RB bit is one (BANK1 is selected), BANK1 general-purpose registers R0\_BANK1 through R7\_BANK1 and non-banked general-purpose registers R8 through R15 (a total of 16 registers) can be accessed as general-purpose registers R0 through R15 and BANK0 general-purpose registers R0\_BANK0 through R7\_BANK0 (eight registers) are accessed by the LDC and STC instructions. When the RB bit is a zero (BANK0 is selected), BANK0 general-purpose registers R0\_BANK0 through R7\_BANK0 and nonbanked general-purpose registers R8 through R15 (16 registers) can be accessed as general-purpose registers R0 through R15 and BANK1 general-purpose registers R0\_BANK0 through R7\_BANK0 and nonbanked general-purpose registers R8 through R15 (16 registers) can be accessed as general-purpose registers R0 through R15 and BANK1 general-purpose registers R0\_BANK1 through R7\_BANK1 (eight registers) are accessed by the LDC and STC instructions.

In user mode, BANK0 general-purpose registers R0\_BANK0 through R7\_BANK0 and nonbanked general-purpose registers R8 through R15 can be accessed as general-purpose registers R0 through R15 (a total of 16 registers) and BANK1 general-purpose registers R0\_BANK1 through R7\_BANK1 (eight registers) cannot be accessed.

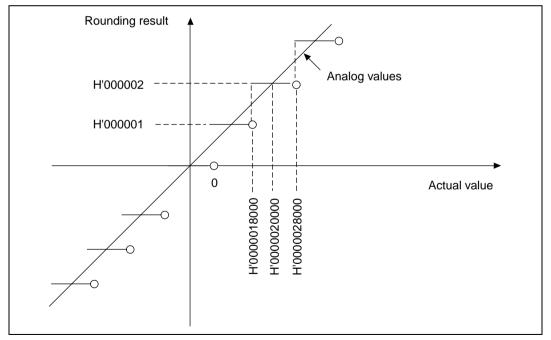

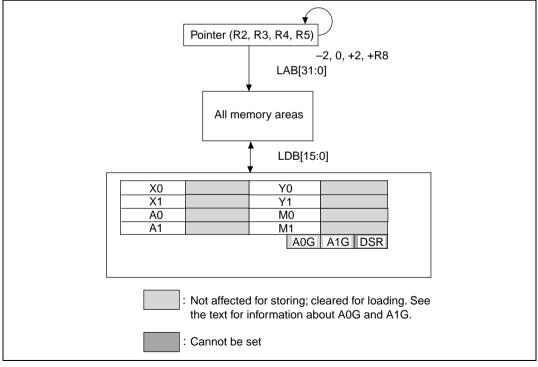

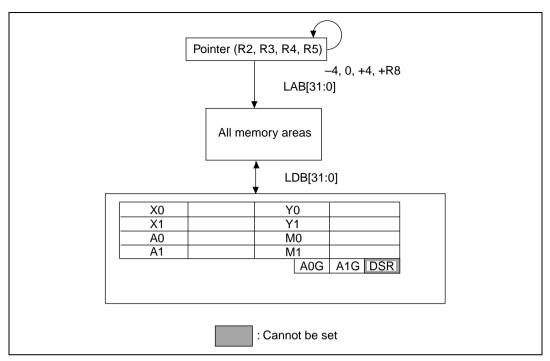

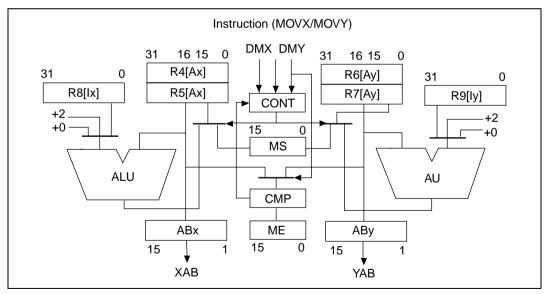

When the DSP extended features of the SH3-DSP are enabled, DSP instructions use X and Y data memory and L bus data memory (single data) addressing for eight of the 16 general-purpose registers.

To access X memory, R4 and R5 are used as the X address register [Ax] and R8 is used as the X index register [Ix]. To access the Y memory, R6 and R7 are used as the Y address register [Ay]

# Renesas

### Section 2 Programming Model

and R9 is used as the Y index register [Iy]. To access single data using the L bus, R2, R3, R4, and R5 are used as the single data address register and R8 as the single data index register [Is].

DSP type instructions can simultaneously access X and Y memory. There are two groups of address pointers for specifying the X and Y data memory addresses.

**Control Registers**: The control registers include registers that can be accessed in either mode (the global base register (GBR) and status register (SR)) and registers that can only be accessed in privileged mode (the saved status register (SSR), saved program counter (SPC), and vector base register (VBR)). Some bits in the status register (for example, the RB bit) can only be accessed in privileged mode.

System Registers: There are four system registers that can be accessed in either processing mode:

- Multiply and accumulate registers

- Multiply and accumulate high (MACH)

- Multiply and accumulate low (MACL)

- Procedure register (PR)

- Program counter (PC)

The register configurations are shown in figure 2.1 by processing mode. Switch between user and privileged modes using the processing operation mode bit in the status register.

**Floating Point Registers and System Registers Used by the FPU (SH-3E Only):** There are 16 floating point registers: FR0 to FR15. These are used as source and destination registers for single-precision floating point operations.

The system registers used by the FPU are the floating point communication register (FPUL) and the floating point status/control register (FPSCR). These are used for communication between the FPU and CPU as well as exception handling settings.

The register configurations for the different processing modes are illustrated in Figure 2.1 and Figure 2.2. Refer to 4. Floating Point Unit.

| 31                 | 0 |

|--------------------|---|

| R0_BANK0*1 *2      |   |

| R1_BANK0*2         |   |

| R2_BANK0*2         |   |

| R3_BANK0*2         |   |

| R4_BANK0*2         |   |

| R5_BANK0*2         |   |

| R6–BANK0*2         |   |

| R7_BANK0*2         |   |

| R8                 |   |

| R9                 |   |

| R10                |   |

| R11                |   |

| R12                |   |

| R13                |   |

| R14                |   |

| R15                |   |

| 31                 | 0 |

| FR0*3              |   |

| FR1*3              |   |

| FR2*3              |   |

|                    |   |

|                    |   |

| •                  |   |

| FR15 <sup>*3</sup> |   |

|                    |   |

|   | 00      |

|---|---------|

|   | 5K      |

| - |         |

|   | FPSCR*3 |

|   | 11001   |

| GBR                |

|--------------------|

| MACH               |

| MACL               |

| FPUL <sup>*3</sup> |

| PR                 |

| PC   |  |

|------|--|

| <br> |  |

- Notes: 1. Register R0 is used as an index register in the indexed register-indirect addressing mode and indexed GBR-indirect addressing mode. There are some instructions for which only R0 can be used as the source or destination register.

- 2. R0 to R7 are banked registers, and BANK0 is used in the user mode.

- 3. These registers only exist on the SH-3E. They are used for floating point operations. Refer to 4. Floating Point Unit for details on FR0 to FR15, FPSCR, and FPUL.

# Figure 2.1 User Mode Programming Model

# Renesas

| 31 0                                                       | 31 0                                                    |

|------------------------------------------------------------|---------------------------------------------------------|

| R0_BANK1*1*2                                               | R0_BANK0*1 *2                                           |

| R1_BANK1*2                                                 | R1_BANK0*2                                              |

| R2_BANK1*2                                                 | R2–BANK0 <sup>*2</sup>                                  |

| R3_BANK1*2                                                 | R3_BANK0*2                                              |

| R4_BANK1*2                                                 | R4_BANK0*2                                              |

| R5_BANK1*2                                                 | R5_BANK0 <sup>*2</sup>                                  |

| R6_BANK1*2                                                 | R6–BANK0 <sup>*2</sup>                                  |

| R7_BANK1*2                                                 | R7_BANK0*2                                              |

| R8                                                         | R8                                                      |

| R9                                                         | R9                                                      |

| R10                                                        | R10                                                     |

| R11                                                        | R11                                                     |

| R12                                                        | R12                                                     |

| R13                                                        | R13                                                     |

| R14                                                        | R14                                                     |

| R15                                                        | R15                                                     |

|                                                            |                                                         |

| FR0*4                                                      | FR0*4                                                   |

| FR1*4                                                      | FR1*4                                                   |

| FR2*4                                                      | FR2*4                                                   |

|                                                            |                                                         |

| :                                                          | :                                                       |

|                                                            | :                                                       |

| FR15 <sup>*4</sup>                                         | FR15                                                    |

|                                                            |                                                         |

| 31 0                                                       | 31 0                                                    |

| SR                                                         | SR                                                      |

| SSR<br>FROOR#4                                             | SSR<br>FROOD#4                                          |

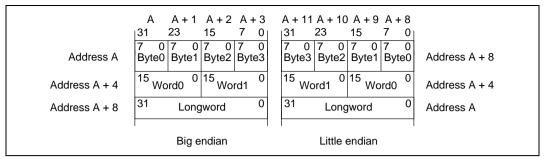

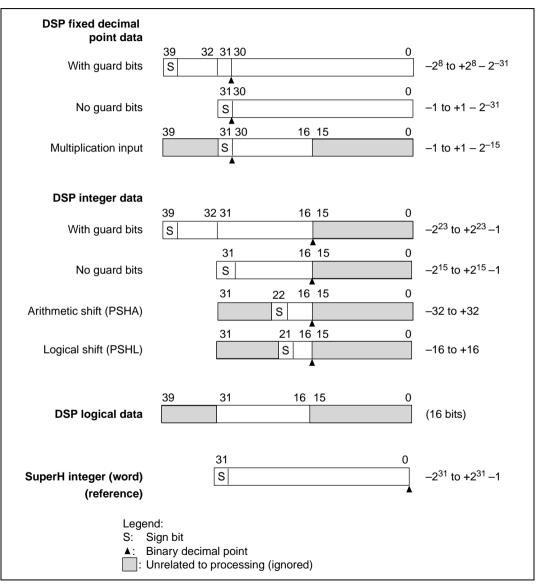

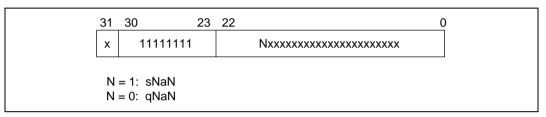

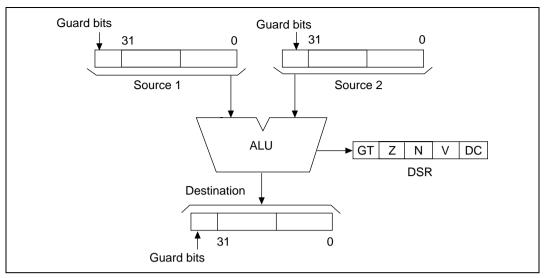

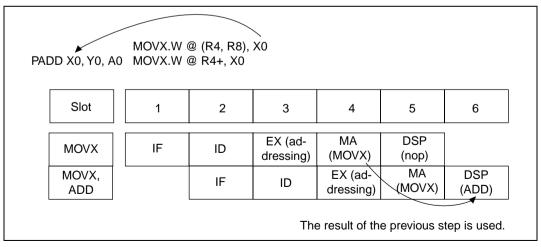

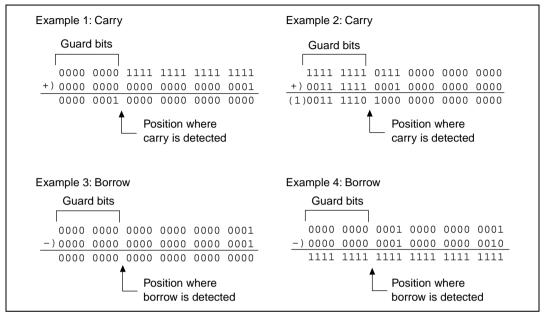

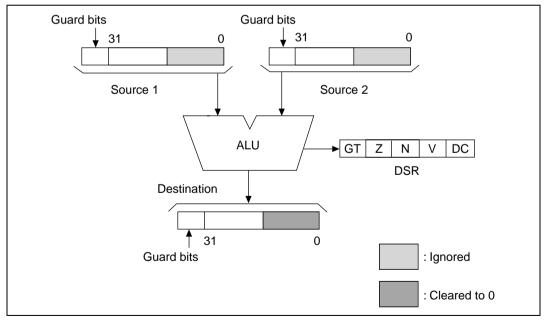

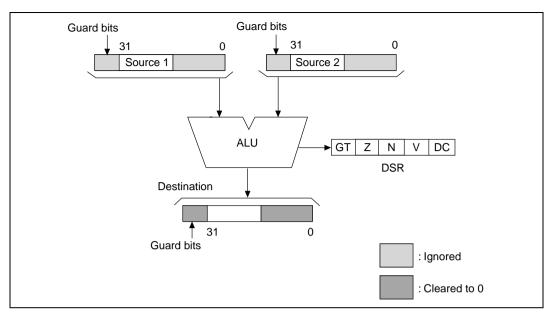

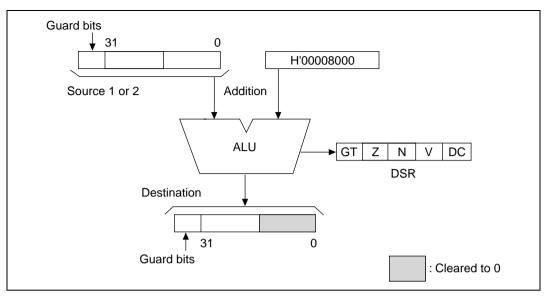

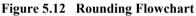

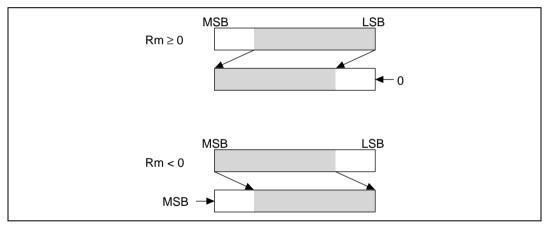

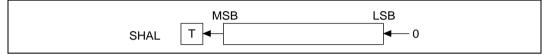

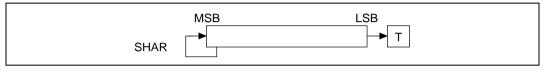

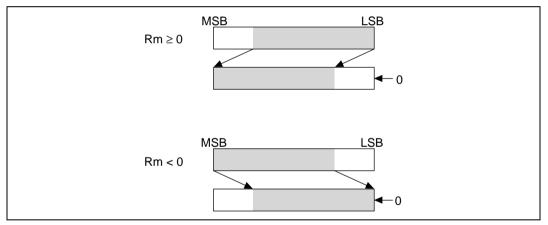

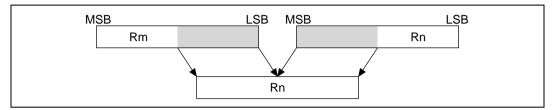

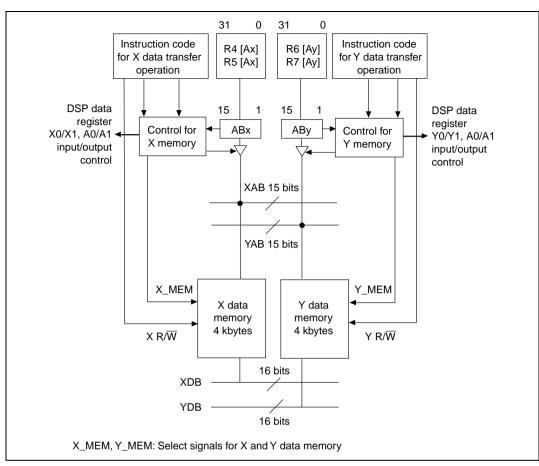

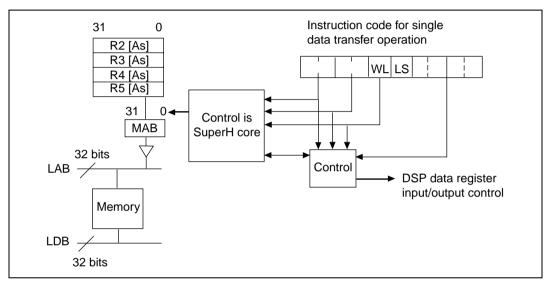

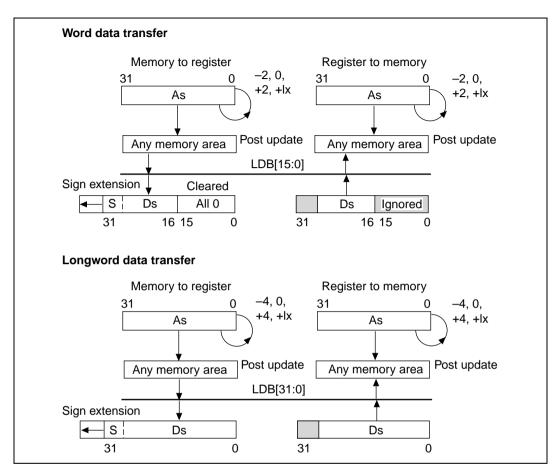

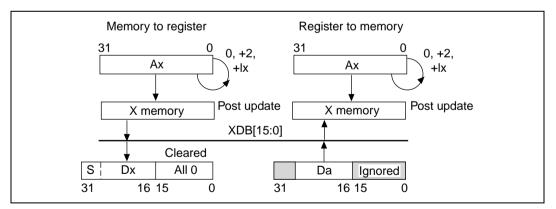

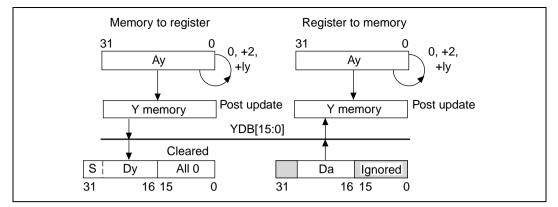

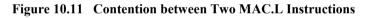

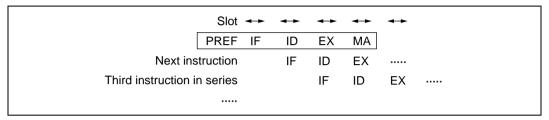

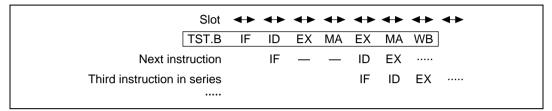

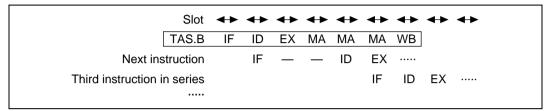

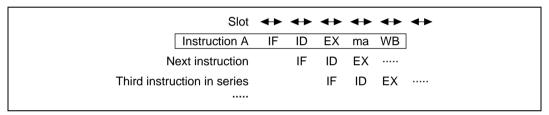

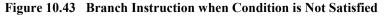

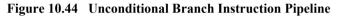

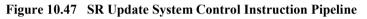

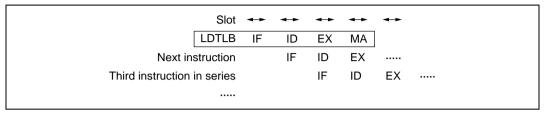

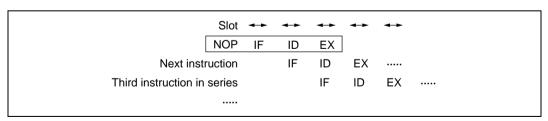

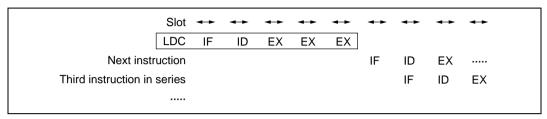

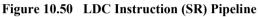

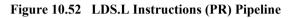

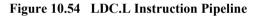

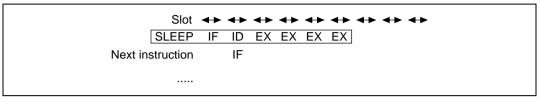

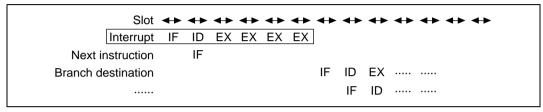

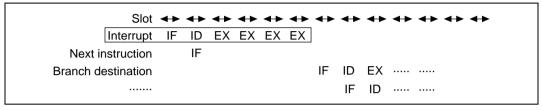

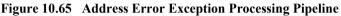

| FPSCR <sup>*4</sup>                                        | FPSCR <sup>*4</sup>                                     |