# RXファミリ

ユーザーズマニュアル ソフトウェア編

ルネサス32ビットマイクロコンピュータ RXファミリ

本資料に記載の全ての情報は本資料発行時点のものであり、ルネサス エレクトロニクスは、 予告なしに、本資料に記載した製品または仕様を変更することがあります。 ルネサス エレクトロニクスのホームページなどにより公開される最新情報をご確認ください。

### 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意 事項については、本文を参照してください。なお、本マニュアルの本文と異なる記載がある場合は、本文の 記載が優先するものとします。

### 1. 未使用端子の処理

【注意】未使用端子は、本文の「未使用端子の処理」に従って処理してください。

CMOS 製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI 周辺のノイズが印加され、LSI 内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。未使用端子は、本文「未使用端子の処理」で説明する指示に従い処理してください。

### 2. 電源投入時の処置

【注意】電源投入時は、製品の状態は不定です。

電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。

外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の状態は保証できません。

同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットの かかる一定電圧に達するまでの期間、端子の状態は保証できません。

3. リザーブアドレス (予約領域) のアクセス禁止

【注意】リザーブアドレス(予約領域)のアクセスを禁止します。

アドレス領域には、将来の機能拡張用に割り付けられているリザーブアドレス(予約領域)があります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

4. クロックについて

【注意】リセット時は、クロックが安定した後、リセットを解除してください。

プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。

リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、 クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子 (または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定し てから切り替えてください。

5. 製品間の相違について

【注意】型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。

同じグループのマイコンでも型名が違うと、内部 ROM、レイアウトパターンの相違などにより、電気的特性の範囲で、特性値、動作マージン、ノイズ耐量、ノイズ輻射量などが異なる場合があります。型名が違う製品に変更する場合は、個々の製品ごとにシステム評価試験を実施してください。

# 略号について

本マニュアルで使用する略号について、以下に説明します。

| 分類    | 略号                | 意味                                                                                                                                         |

|-------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 記号    | IMM               | 即値(Immediate)を表します。                                                                                                                        |

|       | SIMM              | 処理サイズに合わせて、符号拡張される即値(Signed)を表します。                                                                                                         |

|       | UIMM              | 処理サイズに合わせて、ゼロ拡張される即値 (Unsigned)を表します。                                                                                                      |

|       | src               | 命令オペランドのソース(Source)を表します。                                                                                                                  |

|       | dest              | 命令オペランドのデスティネーション(Destination)を表します。                                                                                                       |

|       | dsp               | 相対アドレッシングの変位(Displacement)を表します。                                                                                                           |

|       | pcdsp             | プログラムカウンタ相対アドレッシングの変位(Displacement)を表します。                                                                                                  |

|       | [ ]               | 間接アドレッシングを表します。                                                                                                                            |

|       | Rn                | 汎用レジスタを表します。特に断りがない場合は、R0~R15が指定できます。                                                                                                      |

|       | Rs                | 汎用レジスタ(Source)を表します。特に断りがない場合は、R0~R15が指定できます。                                                                                              |

|       | Rs2               | 主にADD、AND、CMP、MUL、OR、PUSHM、SUB、TST命令の説明に使用されます。これらの命令では、オペランドに2つの汎用レジスタ (Source)が指定可能なため、第1汎用レジスタ (Source)をRs、第2汎用レジスタ (Source)をRs2と表記します。 |

|       | Rd                | 汎用レジスタ ( Destination ) を表します。特に断りがない場合は、R0 ~ R15 が指定できます。                                                                                  |

|       | Rd2               | 主にPOPM、RTSD命令の説明に使用されます。これらの命令では、オペランドに2つの汎用レジスタ(Destination)が指定可能なため、第1汎用レジスタ(Destination)をRd、第2汎用レジスタ(Destination)をRd2と表記します。            |

|       | Rb                | 汎用レジスタ (Base ) を表します。特に断りがない場合は、R0 ~ R15 が<br>指定できます。                                                                                      |

|       | Ri                | 汎用レジスタ (Index ) を表します。特に断りがない場合は、R0 ~ R15<br>が指定できます。                                                                                      |

|       | Rx                | 制御レジスタを表します。PC、ISP、USP、INTB、PSW、BPC、BPSW、FINTV、FPSWが指定できます。PCはMVFC、PUSHC命令のsrcにのみ指定できます。                                                   |

|       | flag              | PSWのビット(U、I)、フラグ(O、S、Z、C)を表します。                                                                                                            |

| 数值    | 000 <u>b</u>      | 2進数を表します。                                                                                                                                  |

|       | 0000 <u>h</u>     | 16進数を表します。                                                                                                                                 |

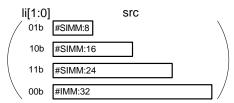

| ビット長  | #IMM <u>:8</u> など | オペランド記号の有効ビット長を表します。                                                                                                                       |

|       | :1                | 有効ビット長が1ビットであることを表します。                                                                                                                     |

|       | :2                | 有効ビット長が2ビットであることを表します。                                                                                                                     |

|       | :3                | 有効ビット長が3ビットであることを表します。                                                                                                                     |

|       | <u>:4</u>         | 有効ビット長が4ビットであることを表します。                                                                                                                     |

|       | <u>:5</u>         | 有効ビット長が5ビットであることを表します。                                                                                                                     |

|       | <u>:8</u>         | 有効ビット長が8ビットであることを表します。                                                                                                                     |

|       | :16               | 有効ビット長が16ビットであることを表します。                                                                                                                    |

|       | :24               | 有効ビット長が24ビットであることを表します。                                                                                                                    |

|       | :32               | 有効ビット長が32ビットであることを表します。                                                                                                                    |

| サイズ指定 | MOV <u>.W</u> など  | 命令の取り扱うサイズを指定する記号です。                                                                                                                       |

|       | <u>.B</u>         | バイト (8ビット) を指定します。                                                                                                                         |

|       | .W                | ワード(16ビット)を指定します。                                                                                                                          |

|       | <u>.</u>          | ロングワード (32ビット)を指定します。                                                                                                                      |

| 分類                        | 略号                          | 意味                                                                |

|---------------------------|-----------------------------|-------------------------------------------------------------------|

| 分岐距離指定                    | BRA <u>.A</u> など            | 分岐の相対距離の有効ビット長を指定する記号です。                                          |

|                           | <u>.S</u>                   | 3ビットのPC前方相対を表します。有効値は、3~10 です。                                    |

|                           | <u>.B</u>                   | 8ビットのPC相対を表します。有効値は、-128~127 です。                                  |

|                           | <u>.W</u>                   | 16 ビットのPC 相対を表します。有効値は、-32768 ~ 32767 です。                         |

|                           | A                           | 24 ビットのPC 相対を表します。<br>有効値は、-8388608 ~ 8388607 です。                 |

|                           | <u>.</u>                    | 32 ビットのPC相対を表します。<br>有効値は、-2147483648~2147483647です。               |

| メモリオペランドに付加さ<br>れるサイズ拡張指定 | dsp:16[Rs] <u>.UB</u> など    | メモリオペランドのサイズと拡張方法を指定する記号です。省略した場合、ロングワードとして扱います。                  |

|                           | <u>.B</u>                   | バイト(8ビット)を指定します。拡張方法は符号拡張です。                                      |

|                           | <u>.UB</u>                  | バイト(8ビット)を指定します。拡張方法はゼロ拡張です。                                      |

|                           | .W                          | ワード(16ビット)を指定します。拡張方法は符号拡張です。                                     |

|                           | .UW                         | ワード(16ビット)を指定します。拡張方法はゼロ拡張です。                                     |

|                           | Ţ                           | ロングワード (32ビット)を指定します。                                             |

| オペレーション                   | (原則としてC言語の文<br>て説明します。)     | -<br>法規則に則っています。以下に、本マニュアルで使用している表記につい                            |

|                           | =                           | 代入演算子です。右辺の値を左辺に代入します。                                            |

|                           | -                           | 単項演算子の負号、または二項演算子の「差」を表します。                                       |

|                           | +                           | 二項演算子の「和」を表します。                                                   |

|                           | *                           | ポインタ演算子、または二項演算子の「積」を表します。                                        |

|                           | /                           | 二項演算子の「商」を表します。                                                   |

|                           | %                           | 二項演算子の「剰余」を表します。                                                  |

|                           | ~                           | 単項ビット演算子の「NOT」を表します。                                              |

|                           | &                           | 二項ビット演算子の「AND」を表します。                                              |

|                           |                             | 二項ビット演算子の「OR」を表します。                                               |

|                           | ٨                           | 二項ビット演算子の「Exclusive OR」を表します。                                     |

|                           | ,                           | 文の終了を表します。                                                        |

|                           | { }                         | 複文の開始と終了を表します。{ }内には複数の文が記述できます。                                  |

|                           | if(式)文1 else 文2             | if文を表します。式を評価して、真であれば文1を、偽であれば文2を実<br>行します。                       |

|                           | for(文1;式;文2)文3              | for文を表します。文1を実行した後、式を評価して、真であれば文3を実行します。文3の実行後は、文2を実行した後、式を評価します。 |

|                           | do 文 while(式);              | do文を表します。式が真の間、文を実行します。式の真偽にかかわらず、<br>文は最低1回実行されます。               |

|                           | while(式)文                   | while文を表します。式が真の間、文を実行します。                                        |

|                           | ==、!=                       | 比較演算子です。順に「等しい」「等しくない」を表します。                                      |

|                           | >, <                        | 比較演算子です。順に「大なり」「小なり」を表します。                                        |

|                           | >=、<=                       | 比較演算子です。'>'、'<' に '=='の条件が加わります。                                  |

|                           | &&                          | 論理演算子です。左側の条件と、右側の条件の「AND」を表します。                                  |

|                           | II                          | 論理演算子です。左側の条件と、右側の条件の「OR」を表します。                                   |

|                           | <<、>>                       | シフト演算子です。「左にシフト」「右にシフト」を表します。                                     |

|                           | tmp、tmp0、tmp1、<br>tmp2、tmp3 | 一時レジスタを表します。                                                      |

|                           | !                           | logical NOT。変数や式のブール値を反転します。                                      |

| 浮動小数点数                    | NaN                         | 非数 (Not a Number )                                                |

| 浮動小数点形式                   | SNaN                        | Signaling NaN                                                     |

|                           | QNaN                        | Quiet NaN                                                         |

|                           | QNaN                        | Quiet NaN                                                         |

# 目次

| Rλ | (ファミリ命令        | 一覧                                    | 7  |

|----|----------------|---------------------------------------|----|

|    | アルファベッ         | ト順ページ早見表                              | 7  |

|    | 機能別ページ         | 早見表                                   | 11 |

| 1. | CPU 機能 .       |                                       | 16 |

|    |                |                                       |    |

|    | 1.2 CPU        | レジスタセット                               | 17 |

|    | 1.2.1          | 汎用レジスタ (R0 ~ R15)                     | 18 |

|    | 1.2.2          | 制御レジスタ                                | 18 |

|    | 1.2.2.1        | 割り込みスタックポインタ (ISP) /ユーザスタックポインタ (USP) | 19 |

|    | 1.2.2.2        | 割り込みテーブルレジスタ(INTB)                    | 19 |

|    | 1.2.2.3        | プログラムカウンタ (PC)                        | 19 |

|    | 1.2.2.4        | プロセッサステータスワード (PSW)                   | 20 |

|    | 1.2.2.5        | バックアップ PC(BPC)                        | 22 |

|    | 1.2.2.6        | バックアップ PSW(BPSW)                      | 22 |

|    | 1.2.2.7        | 高速割り込みベクタレジスタ(FINTV)                  | 22 |

|    | 1.2.2.8        | 浮動小数点ステータスワード(FPSW)                   | 23 |

|    | 1.2.3          | アキュムレータ (ACC)                         | 25 |

|    | 1.3 浮動         | 小数点例外                                 | 26 |

|    | 1.3.1          | オーバフロー                                | 26 |

|    | 1.3.2          | アンダフロー                                | 26 |

|    | 1.3.3          | 精度異常                                  | 27 |

|    | 1.3.4          | ゼロ除算                                  | 27 |

|    | 1.3.5          | 無効演算                                  |    |

|    | 1.3.6          | 非実装処理                                 | 28 |

|    | 1.4 プロ         | セッサモード                                |    |

|    | 1.4.1          | スーパバイザモード                             |    |

|    |                | ユーザモード                                |    |

|    |                | 特権命令                                  |    |

|    |                | プロセッサモード間の移行                          |    |

|    |                | タタイプ                                  |    |

|    |                | 整数                                    |    |

|    |                | 浮動小数点数                                |    |

|    |                | ビット                                   |    |

|    |                | ストリング                                 |    |

|    |                | タ配置                                   |    |

|    | 1.6.1<br>1.6.2 | レジスタのデータ配置メモリ上のデータ配置                  |    |

|    |                | タテーブル                                 |    |

|    |                | タテーフル<br>固定ベクタテーブル                    |    |

|    |                | 可変ベクタテーブル                             |    |

|    |                | リタペクタ / 一 / / /                       |    |

|    | 1.0 / l'       | * < * -1-1H4                          |    |

| 2. | アドレ   | ノッシングモード             | 36  |

|----|-------|----------------------|-----|

|    | 2.1   | 本章の見方                | 37  |

|    | 2.2   | アドレッシングモード           | 38  |

|    | 2.2.1 | IMM の範囲              | 41  |

| 3. | 命令.   |                      | 42  |

|    | 3.1   | 本章の見方                | 42  |

|    | 3.2   | 命令詳細説明               | 48  |

| 4. | 命令日   | コード                  | 163 |

|    | 4.1   | -<br>本章の見方           |     |

|    | 4.2   | 命令コード詳細説明            |     |

| 5. | 何しかしな | 几理                   | 237 |

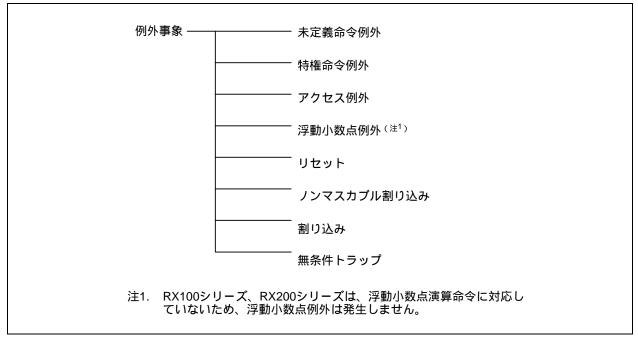

| Ο. | 5.1   | 例外事象                 |     |

|    | 5.1.1 | 未定義命令例外              |     |

|    | 5.1.2 | 特権命令例外               |     |

|    | 5.1.3 | アクセス例外               | 238 |

|    | 5.1.4 | 浮動小数点例外              | 238 |

|    | 5.1.5 | リセット                 | 238 |

|    | 5.1.6 | ノンマスカブル割り込み          | 238 |

|    | 5.1.7 | 割り込み                 | 238 |

|    | 5.1.8 | 無条件トラップ              | 238 |

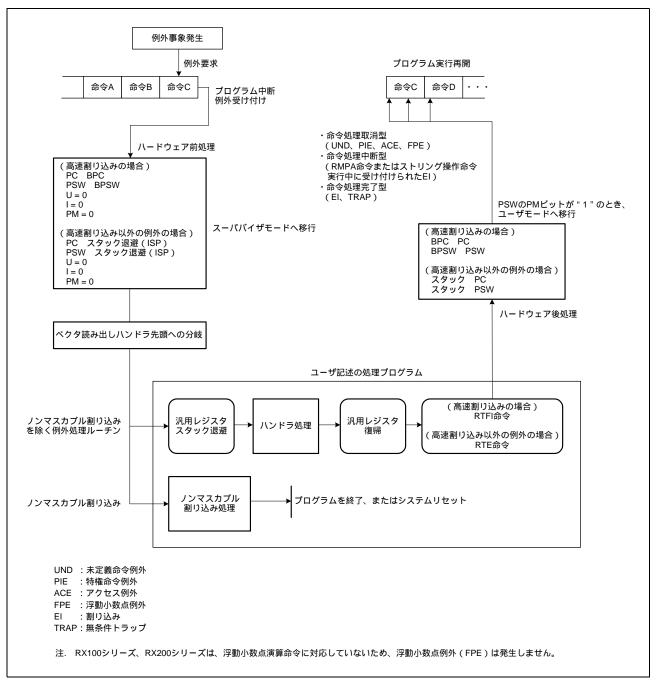

|    | 5.2   | 例外の処理手順              | 239 |

|    | 5.3   | 例外事象の受け付け            | 241 |

|    | 5.3.1 | 受け付けタイミングと保存される PC 値 | 241 |

|    | 5.3.2 | ベクタと PC、PSW の退避場所    | 241 |

|    | 5.4   | 例外の受け付け/復帰時のハードウェア処理 | 242 |

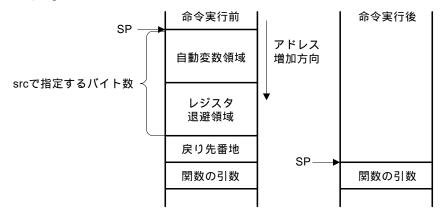

|    | 5.5   | ハードウェア前処理            | 243 |

|    | 5.5.1 | 未定義命令例外              | 243 |

|    | 5.5.2 | 特権命令例外               | 243 |

|    | 5.5.3 | アクセス例外               | 243 |

|    | 5.5.4 | 浮動小数点例外              | 243 |

|    | 5.5.5 | リセット                 | 244 |

|    | 5.5.6 | ノンマスカブル割り込み          | 244 |

|    | 5.5.7 | 割り込み                 | 244 |

|    | 5.5.8 | 無条件トラップ              | 244 |

|    | 5.6   | 例外処理ルーチンからの復帰        | 245 |

|    | 5.7   | 例外事象の優先順位            | 245 |

| 索  | 引     |                      | 246 |

| 改  | 訂記録   |                      | 249 |

RXファミリ RXファミリ命令一覧

# RX ファミリ命令一覧

RX ファミリは、90 種類の命令を持っています。

RX600 シリーズは、全命令に対応します。

RX100 シリーズ、RX200 シリーズは、8 種類の浮動小数点演算命令(FADD、FCMP、FDIV、FMUL、FSUB、FTOI、ITOF、ROUND)を除く、82 命令に対応します。

# アルファベット順ページ早見表 (1/4)

| =-                | ーモニック | 機能      | 命令詳細<br>記載ページ | 命令コード詳細<br>記載ページ |

|-------------------|-------|---------|---------------|------------------|

| ABS               |       | 絶対値     | 49            | 167              |

| ADC               |       | キャリ付き加算 | 50            | 168              |

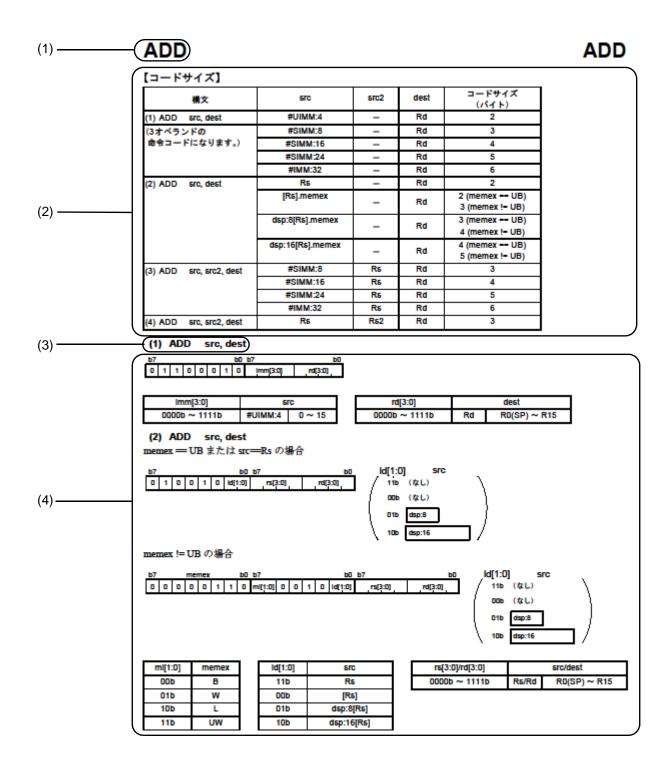

| ADD               |       | キャリなし加算 | 51            | 169              |

| AND               |       | 論理積     | 53            | 171              |

| BCLR BCnd BGEU BC |       | ビットクリア  | 55            | 173              |

| BCnd              | BGEU  | 相対条件分岐  | 56            | 175              |

|                   | ВС    |         | 56            | 175              |

|                   | BEQ   |         | 56            | 175              |

|                   | BZ    |         | 56            | 175              |

|                   | BGTU  |         | 56            | 175              |

|                   | BPZ   |         | 56            | 175              |

|                   | BGE   |         | 56            | 175              |

|                   | BGT   |         | 56            | 175              |

|                   | ВО    |         | 56            | 175              |

|                   | BLTU  |         | 56            | 175              |

|                   | BNC   |         | 56            | 175              |

|                   | BNE   |         | 56            | 175              |

|                   | BNZ   |         | 56            | 175              |

|                   | BLEU  |         | 56            | 175              |

|                   | BN    |         | 56            | 175              |

|                   | BLE   |         | 56            | 175              |

|                   | BLT   |         | 56            | 175              |

|                   | BNO   |         | 56            | 175              |

# アルファベット順ページ早見表 (2/4)

| ニーモニック    |       | 機能              | 命令詳細<br>記載ページ | 命令コード詳細記載ページ |

|-----------|-------|-----------------|---------------|--------------|

| BMCnd     | BMGEU | 条件ビット転送         | 57            | 176          |

|           | ВМС   |                 | 57            | 176          |

|           | BMEQ  |                 | 57            | 176          |

|           | BMZ   |                 | 57            | 176          |

|           | BMGTU |                 | 57            | 176          |

|           | BMPZ  |                 | 57            | 176          |

|           | BMGE  |                 | 57            | 176          |

|           | BMGT  |                 | 57            | 176          |

|           | ВМО   |                 | 57            | 176          |

|           | BMLTU |                 | 57            | 176          |

|           | BMNC  |                 | 57            | 176          |

|           | BMNE  |                 | 57            | 176          |

|           | BMNZ  |                 | 57            | 176          |

|           | BMLEU |                 | 57            | 176          |

|           | BMN   |                 | 57            | 176          |

|           | BMLE  |                 | 57            | 176          |

|           | BMLT  |                 | 57            | 176          |

|           | BMNO  |                 | 57            | 176          |

| BNOT      |       | ビット反転           | 59            | 177          |

| BRA       |       | 相対無条件分岐         | 60            | 178          |

| BRK       |       | 無条件トラップ         | 61            | 179          |

| BSET      |       | ビットセット          |               | 179          |

| BSR       |       | 相対サブルーチン分岐      | 63            | 181          |

| BTST      |       | ビットテスト          | 64            | 182          |

| CLRPSW    |       | PSWのフラグ、ビットのクリア | 65            | 183          |

| CMP       |       | 比較              | 66            | 184          |

| DIV       |       | 符号付き除算          | 67            | 185          |

| DIVU      |       | 符号なし除算          | 68            | 187          |

| EMUL      |       | 符号付き乗算          | 69            | 188          |

| EMULU     |       | 符号なし乗算          | 71            | 189          |

| FADD (注1) | )     | 浮動小数点加算         | 73            | 190          |

| FCMP(注1)  | )     | 浮動小数点比較         | 75            | 191          |

| FDIV (注1) |       | 浮動小数点除算         | 77            | 192          |

| FMUL(注1)  | )     | 浮動小数点乗算         | 79            | 192          |

| FSUB (注1) | )     | 浮動小数点減算         | 81            | 193          |

| FTOI (注1) |       | 浮動小数点数 整数变換     | 83            | 194          |

| INT       |       | ソフトウェア割り込み      | 85            | 195          |

| ITOF (注1) |       | 整数 浮動小数点数变换     | 86            | 195          |

| JMP       |       | 無条件分岐           | 88            | 196          |

| JSR       |       | サブルーチン分岐        | 89            | 196          |

| MACHI     |       | 上位16ビット積和演算     | 90            | 196          |

| MACLO     |       | 下位16ビット積和演算     | 91            | 197          |

# アルファベット順ページ早見表 (3/4)

| ニーモニック                         | 機能                      | 命令詳細<br>記載ページ | 命令コード詳細 記載ページ |

|--------------------------------|-------------------------|---------------|---------------|

| MAX                            | 最大值選択                   | 92            | 198           |

| MIN                            | 最小值選択                   | 93            | 199           |

| MOV                            | 転送                      | 94            | 200           |

| MOVU                           | 符号なしデータ転送               | 98            | 205           |

| MUL                            | 乗算                      | 99            | 206           |

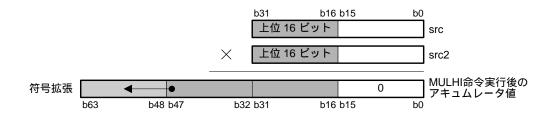

| MULHI                          | 上位16ビット乗算               | 101           | 207           |

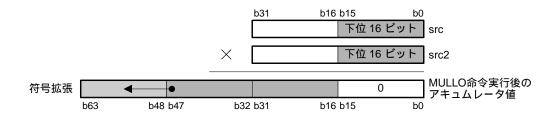

| MULLO                          | 下位16ビット乗算               | 102           | 208           |

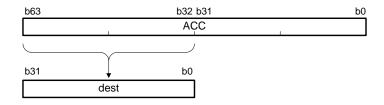

| MVFACHI                        | アキュムレータ上位32ビットからの転送     | 103           | 208           |

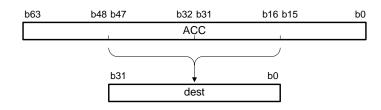

| MVFACMI                        | アキュムレータ中央32 ビットからの転送    | 104           | 208           |

| MVFC                           | 制御レジスタからの転送             | 105           | 209           |

| MVTACHI                        | アキュムレータ上位32ビットへの転送      | 106           | 209           |

| MVTACLO                        | アキュムレータ下位32ビットへの転送      | 107           | 210           |

| MVTC                           | 制御レジスタへの転送              | 108           | 210           |

| MVTIPL (特権命令 ) <sup>(注2)</sup> | 割り込み優先レベル設定             | 109           | 211           |

| NEG                            | 符号反転                    | 110           | 212           |

| NOP                            | ノーオペレーション               | 111           | 212           |

| NOT                            | 論理反転                    | 112           | 213           |

| OR                             | 論理和                     | 113           | 214           |

| POP                            | スタックからレジスタへのデータ復帰       | 115           | 215           |

| POPC                           | 制御レジスタの復帰               | 116           | 216           |

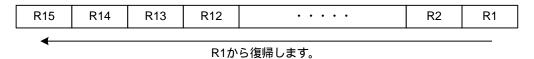

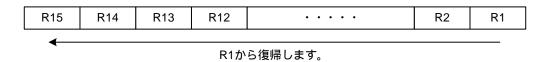

| POPM                           | 複数レジスタの復帰               | 117           | 216           |

| PUSH                           | スタックヘデータ退避              | 118           | 217           |

| PUSHC                          | 制御レジスタの退避               | 119           | 218           |

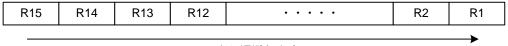

| PUSHM                          | 複数レジスタの退避               | 120           | 218           |

| RACW                           | 16ビット符号付きアキュムレータ丸め処理    | 121           | 219           |

| REVL                           | エンディアン変換                | 123           | 219           |

| REVW                           | エンディアン変換                | 124           | 219           |

| RMPA                           | 積和演算                    | 125           | 220           |

| ROLC                           | キャリ付き左回転                | 127           | 220           |

| RORC                           | キャリ付き右回転                | 128           | 220           |

| ROTL                           | 左回転                     | 129           | 221           |

| ROTR                           | 右回転                     | 130           | 221           |

| ROUND (注1)                     | 浮動小数点数 整数变换             | 131           | 222           |

| RTE (特権命令)                     | 例外からの復帰                 | 134           | 222           |

| RTFI(特権命令)                     | 高速割り込みからの復帰             | 135           | 222           |

| RTS                            | サブルーチンからの復帰             | 136           | 223           |

| RTSD                           | スタックフレームの解放とサブルーチンからの復帰 | 137           | 223           |

| SAT                            | 32ビット符号付き飽和処理           | 139           | 223           |

| SATR                           | RMPA 命令用64 ビット符号付き飽和処理  | 140           | 224           |

| SBB                            | ボロー付き減算                 | 141           | 224           |

# アルファベット順ページ早見表 (4/4)

| ニーモニック   |       | 機能              | 命令詳細<br>記載ページ | 命令コード詳細<br>記載ページ |

|----------|-------|-----------------|---------------|------------------|

| SCCnd    | SCGEU | 条件設定            | 142           | 225              |

|          | SCC   |                 | 142           | 225              |

|          | SCEQ  |                 | 142           | 225              |

|          | SCZ   |                 | 142           | 225              |

|          | SCGTU |                 | 142           | 225              |

|          | SCPZ  |                 | 142           | 225              |

|          | SCGE  |                 | 142           | 225              |

|          | SCGT  |                 | 142           | 225              |

|          | SCO   |                 | 142           | 225              |

|          | SCLTU |                 | 142           | 225              |

|          | SCNC  |                 | 142           | 225              |

|          | SCNE  |                 | 142           | 225              |

|          | SCNZ  |                 | 142           | 225              |

|          | SCLEU |                 | 142           | 225              |

|          | SCN   |                 | 142           | 225              |

|          | SCLE  |                 | 142           | 225              |

|          | SCLT  |                 | 142           | 225              |

|          | SCNO  |                 | 142           | 225              |

| SCMPU    |       | ストリング比較         | 143           | 225              |

| SETPSW   |       | PSWのフラグ、ビットのセット | 144           | 226              |

| SHAR     |       | 算術右シフト          | 145           | 226              |

| SHLL     |       | 論理/算術左シフト       | 146           | 227              |

| SHLR     |       | 論理右シフト          | 147           | 228              |

| SMOVB    |       | 逆方向ストリング転送      | 148           | 228              |

| SMOVF    |       | 順方向ストリング転送      | 149           | 229              |

| SMOVU    |       | ストリング転送         | 150           | 229              |

| SSTR     |       | ストリングストア        | 151           | 229              |

| STNZ     |       | 条件付き転送          | 152           | 230              |

| STZ      |       | 条件付き転送          | 153           | 230              |

| SUB      |       | ボローなし減算         | 154           | 231              |

| SUNTIL   |       | ストリングサーチ        | 155           | 232              |

| SWHILE   |       | ストリングサーチ        | 157           | 232              |

| TST      |       | テスト             | 159           | 233              |

| WAIT(特権部 | 令)    | ウェイト            | 160           | 234              |

| XCHG     |       | 交換              | 161           | 235              |

| XOR      |       | 排他的論理和          | 162           | 236              |

注 1. RX100 シリーズ、RX200 シリーズは、浮動小数点演算命令に対応していません。

注 2. RX610 グループは、MVTIPL 命令に対応していません。

# 機能別ページ早見表 (1/5)

| 命令の種類    | ニーモニック | 機能                   | 命令詳細<br>記載ページ | 命令コード詳細 記載ページ |

|----------|--------|----------------------|---------------|---------------|

| 算術 / 論理  | ABS    | 絶対値                  | 49            | 167           |

| 演算命令     | ADC    | キャリ付き加算              | 50            | 168           |

|          | ADD    | キャリなし加算              | 51            | 169           |

|          | AND    | 論理積                  | 53            | 171           |

|          | CMP    | 比較                   | 66            | 184           |

|          | DIV    | 符号付き除算               | 67            | 185           |

|          | DIVU   | 符号なし除算               | 68            | 187           |

|          | EMUL   | 符号付き乗算               | 69            | 188           |

|          | EMULU  | 符号なし乗算               | 71            | 189           |

|          | MAX    | 最大值選択                | 92            | 198           |

|          | MIN    | 最小值選択                | 93            | 199           |

|          | MUL    | 乗算                   | 99            | 206           |

|          | NEG    | 符号反転                 | 110           | 212           |

|          | NOP    | ノーオペレーション            | 111           | 212           |

|          | NOT    | 論理反転                 | 112           | 213           |

|          | OR     | 論理和                  | 113           | 214           |

|          | RMPA   | 積和演算                 | 125           | 220           |

|          | ROLC   | キャリ付き左回転             | 127           | 220           |

|          | RORC   | キャリ付き右回転             | 128           | 220           |

|          | ROTL   | 左回転                  | 129           | 221           |

|          | ROTR   | 右回転                  | 130           | 221           |

|          | SAT    | 32ビット符号付き飽和処理        | 139           | 223           |

|          | SATR   | RMPA命令用64ビット符号付き飽和処理 | 140           | 224           |

|          | SBB    | ボロー付き減算              | 141           | 224           |

|          | SHAR   | 算術右シフト               | 145           | 226           |

|          | SHLL   | 論理/算術左シフト            | 146           | 227           |

|          | SHLR   | 論理右シフト               | 147           | 228           |

|          | SUB    | ボローなし減算              | 154           | 231           |

|          | TST    | テスト                  | 159           | 233           |

|          | XOR    | 排他的論理和               | 162           | 236           |

|          | FADD   | 浮動小数点加算              | 73            | 190           |

| 演算命令(注1) | FCMP   | 浮動小数点比較              | 75            | 191           |

|          | FDIV   | 浮動小数点除算              | 77            | 192           |

|          | FMUL   | 浮動小数点乗算              | 79            | 192           |

|          | FSUB   | 浮動小数点減算              | 81            | 193           |

|          | FTOI   | 浮動小数点数 整数变換          | 83            | 194           |

|          | ITOF   | 整数 浮動小数点数变換          | 86            | 195           |

|          | ROUND  | 浮動小数点数 整数变換          | 131           | 222           |

RXファミリ命令一覧

# 機能別ページ早見表 (2/5)

| 命令の種類 | =     | ーモニック | 機能                | 命令詳細<br>記載ページ | 命令コード詳細<br>記載ページ |

|-------|-------|-------|-------------------|---------------|------------------|

| 転送命令  | MOV   |       | 転送                | 94            | 200              |

|       | MOVU  |       | 符号なしデータ転送         | 98            | 205              |

|       | POP   |       | スタックからレジスタへのデータ復帰 | 115           | 215              |

|       | POPC  |       | 制御レジスタの復帰         | 116           | 216              |

|       | POPM  |       | 複数レジスタの復帰         | 117           | 216              |

|       | PUSH  |       | スタックヘデータ退避        | 118           | 217              |

|       | PUSHC |       | 制御レジスタの退避         | 119           | 218              |

|       | PUSHM |       | 複数レジスタの退避         | 120           | 218              |

|       | REVL  |       | エンディアン変換          | 123           | 219              |

|       | REVW  |       | エンディアン変換          | 124           | 219              |

|       | SCCnd | SCGEU | 条件設定              | 142           | 225              |

|       |       | SCC   |                   | 142           | 225              |

|       |       | SCEQ  |                   | 142           | 225              |

|       |       | SCZ   |                   | 142           | 225              |

|       |       | SCGTU |                   | 142           | 225              |

|       |       | SCPZ  |                   | 142           | 225              |

|       |       | SCGE  |                   | 142           | 225              |

|       |       | SCGT  |                   | 142           | 225              |

|       |       | SCO   |                   | 142           | 225              |

|       |       | SCLTU |                   | 142           | 225              |

|       |       | SCNC  |                   | 142           | 225              |

|       |       | SCNE  |                   | 142           | 225              |

|       |       | SCNZ  |                   | 142           | 225              |

|       |       | SCLEU |                   | 142           | 225              |

|       |       | SCN   |                   | 142           | 225              |

|       |       | SCLE  |                   | 142           | 225              |

|       |       | SCLT  |                   | 142           | 225              |

|       |       | SCNO  |                   | 142           | 225              |

|       | STNZ  | •     | 条件付き転送            | 152           | 230              |

|       | STZ   |       | 条件付き転送            | 153           | 230              |

|       | XCHG  |       | 交換                | 161           | 235              |

# 機能別ページ早見表 (3/5)

| 命令の種類 | =-   | モニック | 機能                          | 命令詳細<br>記載ページ | 命令コード詳細<br>記載ページ |

|-------|------|------|-----------------------------|---------------|------------------|

| 分岐命令  | BCnd | BGEU | 相対条件分岐                      | 56            | 175              |

|       |      | BC   |                             | 56            | 175              |

|       |      | BEQ  |                             | 56            | 175              |

|       |      | BZ   |                             | 56            | 175              |

|       |      | BGTU |                             | 56            | 175              |

|       |      | BPZ  |                             | 56            | 175              |

|       |      | BGE  |                             | 56            | 175              |

|       |      | BGT  |                             | 56            | 175              |

|       |      | ВО   |                             | 56            | 175              |

|       |      | BLTU |                             | 56            | 175              |

|       |      | BNC  |                             | 56            | 175              |

|       |      | BNE  |                             | 56            | 175              |

|       |      | BNZ  |                             | 56            | 175              |

|       |      | BLEU |                             | 56            | 175              |

|       |      | BN   |                             | 56            | 175              |

|       |      | BLE  |                             | 56            | 175              |

|       |      | BLT  |                             | 56            | 175              |

|       |      | BNO  |                             | 56            | 175              |

|       | BRA  |      | 相対無条件分岐                     | 60            | 178              |

|       | BSR  |      | 相対サブルーチン分岐                  | 63            | 181              |

|       | JMP  |      | 無条件分岐                       | 88            | 196              |

|       | JSR  |      | サブルーチン分岐                    | 89            | 196              |

|       | RTS  |      | サブルーチンからの復帰                 | 136           | 223              |

|       | RTSD |      | スタックフレームの解放とサブルーチンか<br>らの復帰 | 137           | 223              |

# 機能別ページ早見表 (4/5)

| 命令の種類 | =        | ーモニック                  | 機能              | 命令詳細<br>記載ページ | 命令コード詳細<br>記載ページ |

|-------|----------|------------------------|-----------------|---------------|------------------|

| ビット操作 | BCLR     |                        | ビットクリア          | 55            | 173              |

| 命令    | BMCnd    | BMGEU                  | 条件ビット転送         | 57            | 176              |

|       |          | ВМС                    | 7               | 57            | 176              |

|       |          | BMEQ                   | 7               | 57            | 176              |

|       |          | BMZ                    | 7               | 57            | 176              |

|       |          | BMGTU                  | 7               | 57            | 176              |

|       |          | BMPZ                   | 7               | 57            | 176              |

|       |          | BMGE                   | 7               | 57            | 176              |

|       |          | BMGT                   |                 | 57            | 176              |

|       |          | ВМО                    |                 | 57            | 176              |

|       |          | BMLTU                  |                 | 57            | 176              |

|       |          | BMNC                   |                 | 57            | 176              |

|       |          | BMNE                   |                 | 57            | 176              |

|       |          | BMNZ                   | 7               | 57            | 176              |

|       |          | BMLEU                  |                 | 57            | 176              |

|       |          | BMN                    | 7               | 57            | 176              |

|       |          | BMLE                   |                 | 57            | 176              |

|       |          | BMLT                   |                 | 57            | 176              |

|       |          | BMNO                   |                 | 57            | 176              |

|       | BNOT     |                        | ビット反転           | 59            | 177              |

|       | BSET     |                        | ビットセット          | 62            | 179              |

|       | BTST     |                        | ビットテスト          | 64            | 182              |

| ストリング | SCMPU    |                        | ストリング比較         | 143           | 225              |

| 操作命令  | SMOVB    |                        | 逆方向ストリング転送      | 148           | 228              |

|       | SMOVF    |                        | 順方向ストリング転送      | 149           | 229              |

|       | SMOVU    |                        | ストリング転送         | 150           | 229              |

|       | SSTR     |                        | ストリングストア        | 151           | 229              |

|       | SUNTIL   |                        | ストリングサーチ        | 155           | 232              |

|       | SWHILE   |                        | ストリングサーチ        | 157           | 232              |

| システム  | BRK      |                        | 無条件トラップ         | 61            | 179              |

| 操作命令  | CLRPSW   |                        | PSWのフラグ、ビットのクリア | 65            | 183              |

|       | INT      |                        | ソフトウェア割り込み      | 85            | 195              |

|       | MVFC     |                        | 制御レジスタからの転送     | 105           | 209              |

|       | MVTC     |                        | 制御レジスタへの転送      | 108           | 210              |

|       | MVTIPL ( | 持権命令 ) <sup>(注2)</sup> | 割り込み優先レベル設定     | 109           | 211              |

|       | RTE(特権   |                        | 例外からの復帰         | 134           | 222              |

|       | RTFI(特格  |                        | 高速割り込みからの復帰     | 135           | 222              |

|       | SETPSW   |                        | PSWのフラグ、ビットのセット | 144           | 226              |

|       | WAIT(特   |                        | ウェイト            | 160           | 234              |

RXファミリ命令一覧

# 機能別ページ早見表 (5/5)

| 命令の種類   | ニーモニック  | 機能                   | 命令詳細<br>記載ページ | 命令コード詳細 記載ページ |

|---------|---------|----------------------|---------------|---------------|

| DSP機能命令 | MACHI   | 上位16ビット積和演算          | 90            | 196           |

|         | MACLO   | 下位16ビット積和演算          | 91            | 197           |

|         | MULHI   | 上位16ビット乗算            | 101           | 207           |

|         | MULLO   | 下位16ビット乗算            | 102           | 208           |

|         | MVFACHI | アキュムレータ上位32ビットからの転送  | 103           | 208           |

|         | MVFACMI | アキュムレータ中央32ビットからの転送  | 104           | 208           |

|         | MVTACHI | アキュムレータ上位32ビットへの転送   | 106           | 209           |

|         | MVTACLO | アキュムレータ下位32ビットへの転送   | 107           | 210           |

|         | RACW    | 16ビット符号付きアキュムレータ丸め処理 | 121           | 219           |

注 1. RX100 シリーズ、RX200 シリーズは、浮動小数点演算命令に対応していません。

注 2. RX610 グループは、MVTIPL 命令に対応していません。

# 1. CPU 機能

RX CPU は、使用頻度の高い命令に短縮フォーマットを用意していますので、少ないメモリ容量で効率の良いプログラムを開発できます。また、1 クロックで実行する命令を持ち、高速な演算処理を実現しました。

RX CPU は、90 種類の命令 (73 種類の基本命令、8 種類の浮動小数点演算命令、9 種類の DSP 機能命令) を持っています。

RX600 シリーズは、全命令に対応します。

RX100 シリーズ、RX200 シリーズは、8 種類の浮動小数点演算命令を除く、82 命令に対応します。

RX CPU は、10 種類のアドレッシングモードを持ち、レジスターレジスタ間、レジスターメモリ間の演算や、ビットを対象とする演算ができます。また、メモリーメモリ間の転送ができます。乗算器を内蔵していますので、高速な乗算ができます。

### 1.1 特長

- 最小命令実行時間:1命令1クロックで実行

- アドレス空間:4Gバイト・リニアアドレス

- CPU レジスタセット

汎用レジスタ:32 ビット×16本

制御レジスタ:32 ビット×9 本 アキュムレータ:64 ビット×1 本

• 基本命令: 73 種類

分岐距離に応じた相対分岐命令 可変長命令形式(1バイト長~8バイト長) 頻出命令に短縮フォーマットを用意

- 浮動小数点演算命令:8種類(注1)

- DSP 機能命令: 9 種類

16 ビット×16 ビットの乗算、積和演算に対応 アキュムレータの丸め命令に対応

- アドレッシングモード:10種類

- プロセッサモードスーパバイザモード、ユーザモード

- 浮動小数点演算ユニット(注1)

単精度浮動小数点数(32 ビット)に対応

IEEE754 に準拠したデータタイプ、および例外に対応

- メモリプロテクションユニット (オプション機能)

- データ配置 リトルエンディアン/ビッグエンディアン選択可能

注 1. RX100 シリーズ、RX200 シリーズは、対応していません。

# 1.2 CPU レジスタセット

RX CPU のレジスタには、汎用レジスタ(16 本)と、制御レジスタ(9 本)、および DSP 機能命令で使用するアキュムレータ(1 本)があります。

|                      | ACC (アキュムレータ)                        |

|----------------------|--------------------------------------|

| DSP機能命令関連レジスタ<br>b63 | b                                    |

|                      | FPSW (浮動小数点ステータスワード) <sup>(注2)</sup> |

|                      | FINTV (高速割り込みベクタレジスタ)                |

|                      |                                      |

|                      | BPSW (バックアップPSW)                     |

|                      | BPC (バックアップPC)                       |

|                      | PSW (プロセッサステータスワード)                  |

|                      | PC (プログラムカウンタ)                       |

|                      | INTB (割り込みテーブルレジスタ)                  |

|                      | USP (ユーザスタックポインタ)                    |

|                      | ISP (割り込みスタックポインタ)                   |

|                      | 制御レジスタ<br>b31 b                      |

|                      |                                      |

|                      | R14<br>R15                           |

|                      | R13                                  |

|                      | R12                                  |

|                      | R11                                  |

|                      | R9<br>R10                            |

|                      | R8                                   |

|                      | R7                                   |

|                      | R6                                   |

|                      | R5                                   |

|                      | R3<br>R4                             |

|                      | R2                                   |

|                      | R1                                   |

|                      | R0 (SP) <sup>(注1)</sup>              |

|                      | 汎用レジスタ<br>b31 b                      |

図 1.1 CPU レジスタセット

ユーザスタックポインタ (USP) に切り替わります。

注2. RX100シリーズ、RX200シリーズは、FPSWを命令のオペランドとして指定することはできません。

# 1.2.1 汎用レジスタ(R0~R15)

汎用レジスタは、16本( $R0 \sim R15$ )あります。汎用レジスタ  $R0 \sim R15$  は、データレジスタやアドレスレジスタとして使用します。

汎用レジスタ R0 には、汎用レジスタとしての機能に加えて、スタックポインタ (SP) としての機能が割り当てられています。SP は、プロセッサステータスワード (PSW) のスタックポインタ指定ビット (U) によって、割り込みスタックポインタ (ISP)、またはユーザスタックポインタ (USP) に切り替わります。

### 1.2.2 制御レジスタ

制御レジスタには、以下の9本のレジスタがあります。

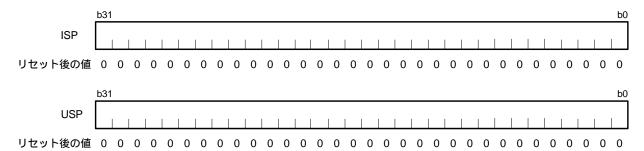

- 割り込みスタックポインタ (ISP)

- ユーザスタックポインタ (USP)

- 割り込みテーブルレジスタ (INTB)

- プログラムカウンタ (PC)

- プロセッサステータスワード (PSW)

- バックアップ PC (BPC)

- バックアップ PSW (BPSW)

- 高速割り込みベクタレジスタ (FINTV)

- 浮動小数点ステータスワード (FPSW) (注1)

注 1. RX100 シリーズ、RX200 シリーズは、FPSW を命令のオペランドとして指定することはできません。

スタックポインタ (SP) には、割り込みスタックポインタ (ISP) と、ユーザスタックポインタ (USP) の2種類があります。使用するスタックポインタ (ISP/USP) は、プロセッサステータスワード (PSW) のスタックポインタ指定ビット (U) によって切り替えられます。

ISP、USPに4の倍数を設定すると、スタック操作を伴う命令や、割り込みシーケンスのサイクル数が短くなります。

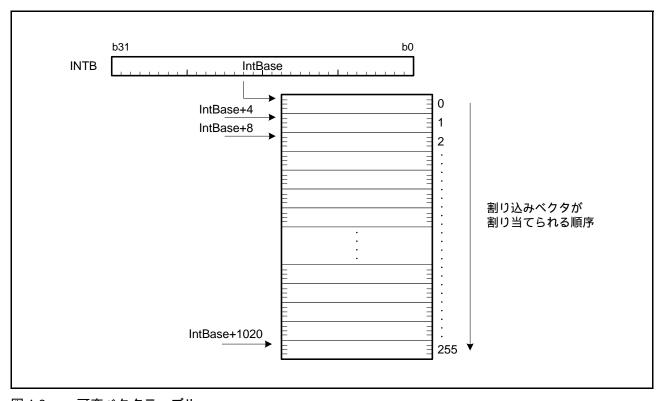

# 1.2.2.2 割り込みテーブルレジスタ (INTB)

リセット後の値 不定

割り込みテーブルレジスタ(INTB)には、可変ベクタテーブルの先頭番地を設定してください。

# 1.2.2.3 プログラムカウンタ(PC)

リセット後の値 リセットベクタ (FFFFFFCh~FFFFFFh番地に書かれた値)

プログラムカウンタ (PC) は、実行中の命令の番地を示します。

# 1.2.2.4 プロセッサステータスワード (PSW)

| _       | b31 | b30 | b29 | b28 | b27<br>(注) | b26  | b25   | b24 | b23 | b22 | b21 | b20 | b19 | b18 | b17 | b16 |

|---------|-----|-----|-----|-----|------------|------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|         | -   | -   | -   | -   |            | IPL[ | [3:0] |     | -   | -   |     | PM  | -   | -   | U   | 1   |

| リセット後の値 | 0   | 0   | 0   | 0   | 0          | 0    | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| _       | b15 | b14 | b13 | b12 | b11        | b10  | b9    | b8  | b7  | b6  | b5  | b4  | b3  | b2  | b1  | b0  |

|         | -   | -   | -   | -   | -          | -    | -     | -   | -   | -   | 1   | -   | 0   | S   | Z   | С   |

| リセット後の値 | 0   | 0   | 0   | 0   | 0          | 0    | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

注. RX610グループでは割り込み優先レベルが0~7のため、b27は予約ビットです。b27への書き込みは無効になります。

| ビット     | シンボル            | ビット名           | 機能                                                                                                                                                                                                                                                                                                                                  | R/W |

|---------|-----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0      | С               | キャリフラグ         | 0:キャリの発生なし<br>1:キャリの発生あり                                                                                                                                                                                                                                                                                                            | R/W |

| b1      | Z               | ゼロフラグ          | 0:演算結果は0でなかった<br>1:演算結果は0であった                                                                                                                                                                                                                                                                                                       | R/W |

| b2      | S               | サインフラグ         | 0:演算結果は正または0であった<br>1:演算結果は負であった                                                                                                                                                                                                                                                                                                    | R/W |

| b3      | 0               | オーバフローフラグ      | 0:オーバフローの発生なし<br>1:オーバフローの発生あり                                                                                                                                                                                                                                                                                                      | R/W |

| b15-b4  | -               | 予約ビット          | 書く場合、"0"としてください。<br>読むと"0"が読めます。                                                                                                                                                                                                                                                                                                    | R/W |

| b16     | (注1)            | 割り込み許可ビット      | 0:割り込み禁止<br>1:割り込み許可                                                                                                                                                                                                                                                                                                                | R/W |

| b17     | U(注1)           | スタックポインタ指定ビット  | 0:割り込みスタックポインタ(ISP)を指定<br>1:ユーザスタックポインタ(USP)を指定                                                                                                                                                                                                                                                                                     | R/W |

| b19-b18 | -               | 予約ビット          | 書く場合、"0"としてください。<br>読むと"0"が読めます。                                                                                                                                                                                                                                                                                                    | R/W |

| b20     | PM (注1、2、3)     | プロセッサモード設定ビット  | 0:スーパバイザモードに設定<br>1:ユーザモードに設定                                                                                                                                                                                                                                                                                                       | R/W |

| b23-b21 | -               | 予約ビット          | 書く場合、"0"としてください。<br>読むと"0"が読めます。                                                                                                                                                                                                                                                                                                    | R/W |

| b27-b24 | IPL[3:0] (注1、4) | プロセッサ割り込み優先レベル | b27 b24<br>0 0 0 0: 優先レベル0(最低)<br>0 0 1: 優先レベル1<br>0 0 1 0: 優先レベル2<br>0 0 1 1: 優先レベル3<br>0 1 0 0: 優先レベル4<br>0 1 0 1: 優先レベル5<br>0 1 1 0: 優先レベル6<br>0 1 1 1: 優先レベル7<br>1 0 0 0: 優先レベル8<br>1 0 0 1: 優先レベル9<br>1 0 1 0: 優先レベル10<br>1 0 1 1: 優先レベル11<br>1 1 0 0: 優先レベル12<br>1 1 0 1: 優先レベル13<br>1 1 1 0: 優先レベル14<br>1 1 1 1: 優先レベル15(最高) | R/W |

| b31-b28 | -               | 予約ビット          | 書く場合、"0"としてください。<br>読むと"0"が読めます。                                                                                                                                                                                                                                                                                                    | R/W |

- 注1. ユーザモードのときは、MVTC、POPC 命令による IPL[3:0]、PM、U、I ビットへの書き込みは無視されます。また、MVTIPL命令でIPL[3:0] ビットへの書き込みを行おうとした場合は、特権命令例外が発生します。

- 注2. スーパバイザモードのときは、MVTC、POPC命令によるPMビットへの書き込みは無視されます。それ以外のビットへの書き込みはできます。

- 注3. スーパバイザモードからユーザモードに切り替える場合は、スタックに退避されたPSWのPMビットを"1"にした後、RTE命令を実行するか、バックアップPSW(BPSW)のPMビットを"1"にした後、RTFI命令を実行してください。

- 注4. RX610グループでは割り込み優先レベルが0~7のため、b27は予約ビットです。b27への書き込みは無効になります。

プロセッサステータスワード (PSW) は、命令実行の結果や、CPU の状態を示します。

### C フラグ (キャリフラグ)

演算結果にキャリ、ボロー、シフトアウトが発生したことを示します。

### Z フラグ (ゼロフラグ)

演算結果が0であったことを示します。

### Sフラグ(サインフラグ)

演算結果が負であったことを示します。

# O フラグ (オーバフローフラグ)

演算中にオーバフローしたことを示します。

### Iビット(割り込み許可ビット)

割り込み要求の受け付けを許可するビットです。例外を受け付けると、このビットは"0"になります。

### U ビット(スタックポインタ指定ビット)

使用するスタックポインタ (ISP/USP) を指定するビットです。例外を受け付けると、このビットは"0" になります。スーパバイザモードからユーザモードに移行すると、このビットは"1"になります。

### PM ビット(プロセッサモード設定ビット)

プロセッサの動作モードを設定するビットです。例外を受け付けると、このビットは"0"になります。

### IPL[3:0] ビット(プロセッサ割り込み優先レベル)

IPL[3:0] ビットは、優先レベル 0 (最低) ~ 優先レベル 15 (最高) までの 16 段階のプロセッサ割り込み 優先レベルを指定します。要求があった割り込みの優先レベルが、プロセッサ割り込み優先レベルより高い場合、その割り込みが許可されます。IPL[3:0] ビットをレベル 15 (Fh) に設定したとき、すべての割り込みが禁止されます。IPL[3:0] ビットは、ノンマスカブル割り込みが発生したとき、レベル 15 (Fh) になります。割り込みが発生したとき、受け付けた割り込みの優先レベルになります。

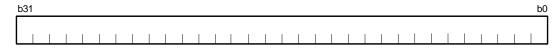

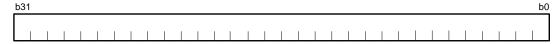

リセット後の値 不定

バックアップ PC (BPC) は、割り込み応答を高速化するために設けられたレジスタです。高速割り込みが発生すると、プログラムカウンタ (PC) の内容が BPC に退避されます。

# 1.2.2.6 バックアップ PSW (BPSW)

リセット後の値 不定

バックアップ PSW (BPSW) は、割り込み応答を高速化するために設けられたレジスタです。高速割り込みが発生すると、プロセッサステータスワード (PSW) の内容が BPSW に退避されます。BPSW のビットの割り当ては、PSW に対応しています。

## 1.2.2.7 高速割り込みベクタレジスタ (FINTV)

リセット後の値 不定

高速割り込みベクタレジスタ(FINTV)は、割り込み応答を高速化するために設けられたレジスタです。 高速割り込み発生時の分岐先番地を設定してください。

# 1.2.2.8 浮動小数点ステータスワード (FPSW)

| _       | b31 | b30 | b29 | b28 | b27 | b26 | b25 | b24 | b23 | b22 | b21 | b20 | b19 | b18 | b17 | b16  |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|

|         | FS  | FX  | FU  | FZ  | FO  | FV  | -   | -   | -   | -   | 1   | -   | -   | -   | -   | -    |

| リセット後の値 | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    |

| _       | b15 | b14 | b13 | b12 | b11 | b10 | b9  | b8  | b7  | b6  | b5  | b4  | b3  | b2  | b1  | b0   |

|         | -   | EX  | EU  | EZ  | EO  | EV  | -   | DN  | CE  | СХ  | CU  | CZ  | со  | CV  | RM[ | 1:0] |

| リセット後の値 | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    |

| ビット     | シンボル               | ビット名            | 機能                                                                  | R/W           |

|---------|--------------------|-----------------|---------------------------------------------------------------------|---------------|

| b1-b0   | RM[1:0]            | 浮動小数点丸めモード設定ビット | b1 b0<br>0 0:最近値への丸め<br>0 1:0方向への丸め<br>1 0:+ 方向への丸め<br>1 1:- 方向への丸め | R/W           |

| b2      | CV                 | 無効演算要因フラグ       | 0:無効演算の発生なし<br>1:無効演算の発生あり                                          | R/(W)<br>(注1) |

| b3      | СО                 | オーバフロー要因フラグ     | 0:オーバフローの発生なし<br>1:オーバフローの発生あり                                      | R/(W)<br>(注1) |

| b4      | CZ                 | ゼロ除算要因フラグ       | 0:ゼロ除算の発生なし<br>1:ゼロ除算の発生あり                                          | R/(W)<br>(注1) |

| b5      | CU                 | アンダフロー要因フラグ     | 0:アンダフローの発生なし<br>1:アンダフローの発生あり                                      | R/(W)<br>(注1) |

| b6      | CX                 | 精度異常要因フラグ       | 0:精度異常の発生なし<br>1:精度異常の発生あり                                          | R/(W)<br>(注1) |

| b7      | CE                 | 非実装処理要因フラグ      | 0:非実装処理の発生なし<br>1:非実装処理の発生あり                                        | R/(W)<br>(注1) |

| b8      | DN                 | 非正規化数の0フラッシュビット | 0:非正規化数を非正規化数として扱う<br>1:非正規化数を0として扱う <sup>(注2)</sup>                | R/W           |

| b9      | -                  | 予約ビット           | 書く場合、"0"としてください。<br>読むと"0"が読めます。                                    | R/W           |

| b10     | EV                 | 無効演算例外処理許可ビット   | 0:無効演算発生による例外処理を禁止<br>1:無効演算発生による例外処理を許可                            | R/W           |

| b11     | EO                 | オーバフロー例外処理許可ビット | 0:オーバフロー発生による例外処理を禁止<br>1:オーバフロー発生による例外処理を許可                        | R/W           |

| b12     | EZ                 | ゼロ除算例外処理許可ビット   | 0:ゼロ除算発生による例外処理を禁止<br>1:ゼロ除算発生による例外処理を許可                            | R/W           |

| b13     | EU                 | アンダフロー例外処理許可ビット | 0:アンダフロー発生による例外処理を禁止<br>1:アンダフロー発生による例外処理を許可                        | R/W           |

| b14     | EX                 | 精度異常例外処理許可ビット   | 0:精度異常発生による例外処理を禁止<br>1:精度異常発生による例外処理を許可                            | R/W           |

| b25-b15 | -                  | 予約ビット           | 書く場合、"0"としてください。<br>読むと"0"が読めます。                                    | R/W           |

| b26     | FV(注3)             | 無効演算フラグ         | 0:無効演算の発生なし<br>1:無効演算の発生あり <sup>(注8)</sup>                          | R/W           |

| b27     | FO <sup>(注4)</sup> | オーバフローフラグ       | 0:オーバフローの発生なし<br>1:オーバフローの発生あり <sup>(注8)</sup>                      | R/W           |

| b28     | FZ <sup>(注5)</sup> | ゼロ除算フラグ         | 0:ゼロ除算の発生なし<br>1:ゼロ除算の発生あり <sup>(注8)</sup>                          | R/W           |

| b29     | FU <sup>(注6)</sup> | アンダフローフラグ       | 0:アンダフローの発生なし<br>1:アンダフローの発生あり <sup>(注8)</sup>                      | R/W           |

| ビット | シンボル               | ビット名           | 機能                                         | R/W |

|-----|--------------------|----------------|--------------------------------------------|-----|

| b30 | FX <sup>(注7)</sup> | 精度異常フラグ        | 0:精度異常の発生なし<br>1:精度異常の発生あり <sup>(注8)</sup> | R/W |

| b31 | FS                 | 浮動小数点エラーサマリフラグ | FU、FZ、FO、FVフラグの論理和を反映                      | R   |

- 注1. "0"を書いた場合、"0"になります。"1"を書いた場合、前の値を保持します。

- 注2. 正の非正規化数は+0、負の非正規化数は-0として扱います。

- 注3. EVビットが"0"のときに、FVフラグは有効となります。

- 注4. EOビットが"0"のときに、FOフラグは有効となります。

- 注5. EZビットが"0"のときに、FZフラグは有効となります。

- 注6. EUビットが"0"のときに、FUフラグは有効となります。

- 注7. EXビットが"0"のときに、FXフラグは有効となります。

- 注8. 当該ビットが一度"1"になると、ソフトウェアで"0"にするまで"1"を保持します。

浮動小数点ステータスワード (FPSW) は、浮動小数点演算結果を示します。浮動小数点命令に対応していない製品では、常に "00000000h" が読め、書き込みは無視されます。

例外処理許可ビット(Ej)で例外処理を許可(Ej="1")した場合は、例外処理ルーチンで該当する Cj フラグをチェックし、例外発生の要因を判断することができます。例外処理を禁止(Ej="0")した場合は、一連の処理の最後に Fj フラグをチェックし、例外発生の有無を確認することができます。 Fj フラグは蓄積フラグです。(j=X、U、Z、O、V)

注. RX100 シリーズ、RX200 シリーズは、命令のオペランドとして FPSW を指定することはできません。

### RM[1:0] ビット (浮動小数点丸めモード設定ビット)

浮動小数点丸めモードを設定します。

## 【浮動小数点丸めモードの説明】

• 最近値への丸め(デフォルト): 無限の有効桁を持つとして計算した場合の結果と近い方の値へ丸める。

中間時は結果が偶数になる方向へ丸める

• 0 方向への丸め : 結果の絶対値が小さくなる方向へ丸める(単純な切り捨て)

+∞方向への丸め : 結果の値が大きくなる方向へ丸める-∞方向への丸め : 結果の値が小さくなる方向へ丸める

- (1)「最近値への丸め」はデフォルトのモードであり、最も正確な値を返します。

- (2) 「0 方向への丸め」、「 $+\infty$ 方向への丸め」、「 $-\infty$ 方向への丸め」は、区間演算(Interval arithmetic)を使用した精度保証を行うときに使用します。

### CV フラグ(無効演算要因フラグ) CO フラグ(オーバフロー要因フラグ)

CZ フラグ(ゼロ除算要因フラグ) CU フラグ(アンダフロー要因フラグ)

### CX フラグ(精度異常要因フラグ) CE フラグ(非実装処理要因フラグ)

IEEE754 規格で規定された5つの例外(オーバフロー、アンダフロー、精度異常、ゼロ除算、無効演算)の他に、非実装処理が発生した場合に該当するフラグが"1"になります。

- "1" の場合、浮動小数点演算命令実行時に"0"になります。

- MVTC、POPC 命令で "0" を書いた場合、"0" になります。"1" を書いた場合、前の値を保持します。

### DN ビット(非正規化数の 0 フラッシュビット)

"0"のとき非正規化数を非正規化数として扱います。

"1"のとき非正規化数を0として扱います。

EV ビット(無効演算例外処理許可ビット) EO ビット(オーバフロー例外処理許可ビット)

EZ ビット(ゼロ除算例外処理許可ビット) EU ビット(アンダフロー例外処理許可ビット)

### EX ビット(精度異常例外処理許可ビット)

浮動小数点演算命令実行により、IEEE754 規格で規定された 5 つの例外が発生したときに、CPU が例外 処理に移行するかどうかを制御します。"0" の場合、例外処理は禁止されます。"1" の場合、例外処理が許可されます。

# FV フラグ(無効演算フラグ ) FO フラグ (オーバフローフラグ ) FZ フラグ (ゼロ除算フラグ ) FU フラグ (アンダフローフラグ ) FX フラグ (精度異常フラグ )

例外処理許可ビット  $E_j$  が "0"(例外処理を禁止)の場合、IEEE754 規格で規定された 5 つの例外が発生すると、該当するフラグが "1" になります。

- Ej="1"(例外処理を許可)のときは、このフラグは動きません。

- 当該フラグが"1"になると、ソフトウェアで"0"にするまで"1"を保持します。(蓄積フラグ)

### FS フラグ(浮動小数点エラーサマリフラグ)

FU、FZ、FO、FV フラグの論理和を反映します。

# 1.2.3 アキュムレータ(ACC)

リセット後の値 不定

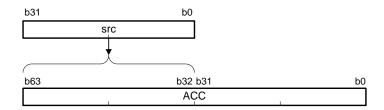

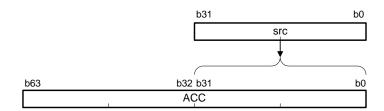

アキュムレータ(ACC)は、64 ビットのレジスタです。DSP機能命令で使用されます。また、ACC は乗算命令(EMUL、EMULU、FMUL、MUL)、積和演算命令(RMPA)でも使用され、これらの命令実行の際は ACC の値が変更されます。

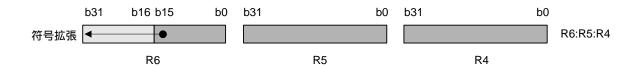

ACC への書き込みには、MVTACHI 命令と MVTACLO 命令を使用します。MVTACHI 命令は上位側 32 ビット(b63  $\sim$  b32)に、MVTACLO 命令は下位側 32 ビット(b31  $\sim$  b0)にデータを書きます。

読み出しには、MVFACHI 命令と MVFACMI 命令を使用します。MVFACHI 命令で上位側 32 ビット(b63  $\sim$  b32)、MVFACMI 命令で中央の 32 ビット(b47  $\sim$  b16)のデータをそれぞれ読みます。

# 1.3 浮動小数点例外

浮動小数点例外は、IEEE754 規格で規定された 5 つの例外(オーバフロー、アンダフロー、精度異常、ゼロ除算、無効演算)の他に、非実装処理を検出した場合に発生します。以下に、浮動小数点例外を発生させる事象の概要を示します。

注. RX100 シリーズ、RX200 シリーズは、浮動小数点演算命令に対応していないため、浮動小数点例外は発生しません。

### 1.3.1 オーバフロー

オーバフローは、演算結果の絶対値が浮動小数点フォーマットで表現可能な値よりも大きくなった場合に 発生します。表 1.1 にオーバフロー発生時の演算結果を示します。

表1.1 オーバフロー発生時の演算結果

| 浮動小数点丸めモード | 結果の符号 | 演算結果(デスティネーションレジスタの値) |         |  |  |  |

|------------|-------|-----------------------|---------|--|--|--|

| 浮動小数点丸のモート | 編表の行号 | EO ="0"               | EO ="1" |  |  |  |

| - 方向への丸め   | +     | +MAX                  | 変化なし    |  |  |  |

|            | -     | -                     |         |  |  |  |

| + 方向への丸め   | +     | +                     |         |  |  |  |

|            | -     | -MAX                  |         |  |  |  |

| 0方向への丸め    | +     | +MAX                  |         |  |  |  |

|            | -     | -MAX                  |         |  |  |  |

| 最近値への丸め    | +     | +                     |         |  |  |  |

|            | -     | -                     |         |  |  |  |

注. EO ="0"のとき、オーバフローが発生すると精度異常が発生します。

# 1.3.2 アンダフロー

アンダフローは、演算結果の絶対値が浮動小数点フォーマットの正規化数で表現可能な値よりも小さくなった場合(ただし、0を除く)に発生します。表 1.2 にアンダフロー発生時の演算結果を示します。

### 表1.2 アンダフロー発生時の演算結果

| 演算結果(デスティネーションレジスタの内容)     |         |

|----------------------------|---------|

| EU ="0"                    | EU ="1" |

| DN ="0"のとき、変化しない(非実装処理が発生) | 変化なし    |

| DN ="1"のとき、"0"を返す          |         |

# 1.3.3 精度異常

精度異常は、無限の有効桁を持つと仮定して計算した結果と、演算結果が異なっていた場合に発生します。表 1.3 に精度異常発生条件と演算結果を示します。

### 表1.3 精度異常発生条件と演算結果

| 発生条件                   | 演算結果(デスティネーションレジスタの内容)      |         |  |  |  |

|------------------------|-----------------------------|---------|--|--|--|

| 光土赤什                   | EX ="0"                     | EX ="1" |  |  |  |

| オーバフロー例外禁止状態でのオーバフロー発生 | 「表1.1 オーバフロー発生時<br>の演算結果」参照 | 変化なし    |  |  |  |

| 丸めの発生                  | 丸め後の値                       |         |  |  |  |

- 注1. アンダフロー発生時、精度異常は発生しません。

- 注2. オーバフロー例外許可状態でのオーバフロー発生時、丸めの発生にかかわらず、精度異常は発生しません。

# 1.3.4 ゼロ除算

ゼロ除算は、0 でない有限数を0 で割った場合に発生します。**表 1.4** にゼロ除算発生時の演算結果を示します。

#### 表1.4 ゼロ除算発生時の演算結果

| カロマム 米石 | 演算結果(デスティネーションレジスタの内容)     |         |  |  |  |  |  |

|---------|----------------------------|---------|--|--|--|--|--|

| 被除数     | EZ ="0"                    | EZ ="1" |  |  |  |  |  |

| 0でない有限数 | ± (符号は除数、被除数の符号の排他的論理和となる) | 変化なし    |  |  |  |  |  |

### 注. 以下のときは、ゼロ除算は発生しません。

| 被除数           | 動作               |

|---------------|------------------|

| 0             | 無効演算発生           |

|               | 例外は発生しない。結果は     |

| 非正規化数(DN="0") | 非実装処理発生          |

| QNaN          | 例外は発生しない。結果はQNaN |

| SNaN          | 無効演算発生           |

# 1.3.5 無効演算

無効演算は、無効な演算が実行された場合に発生します。表 1.5 に無効演算発生条件と演算結果を示します。

表1.5 無効演算発生条件と演算結果

| 発生条件                                            | 演算結果 (デスティネーションレジスタの内容)                            |         |  |  |  |  |  |

|-------------------------------------------------|----------------------------------------------------|---------|--|--|--|--|--|

| 光王宗什                                            | EV ="0"                                            | EV ="1" |  |  |  |  |  |

| SNaNオペランドに対する演算                                 | QNaN                                               | 変化なし    |  |  |  |  |  |

| + +(- ) 、+ -(+ ) 、(- )                          |                                                    |         |  |  |  |  |  |

| 0×                                              |                                                    |         |  |  |  |  |  |

| 0÷0、 ÷                                          |                                                    |         |  |  |  |  |  |

| FTOI命令、ROUND命令実行時、整数変換がオーバフローするか、NaN、 を整数変換したとき | 変換前の符号ビットが、"0"のときは<br>7FFFFFFh、"1"のときは80000000hを返す |         |  |  |  |  |  |

| SNaNオペランドに対する比較                                 | デスティネーションはなし                                       |         |  |  |  |  |  |

· NaN (Not a Number) : 非数

・SNaN(Signaling NaN) : 仮数部の最上位ビットが"0"であるNaNです。SNaNを演算のソースオペランドとして使

用すると、無効演算を発生します。変数の初期値として使用することにより、プログラムのバグの発見に役立ちます。なお、SNaNはハードウェアで生成することはありません。 仮数部の最上位ビットが"1"であるNaNです。QNaNを演算のソースオペランドとして使

・QNaN(Quiet NaN) 用しても、無効演算は発生しません(比較、フォーマット変換を除く)。演算によって伝

播するため、例外処理を実行せずに結果だけを見てデバッグを行うことができます。な

お、QNaNは演算によりハードウェアが生成します。

表 1.6 に演算結果が QNaN となる場合の生成規則を示します。

表1.6 QNaN生成規則

| ソースオペランド              | 演算結果(デスティネーションレジスタの内容) |  |  |  |  |  |

|-----------------------|------------------------|--|--|--|--|--|

| SNaN Ł QNaN           | QNaN化されたSNaNソースオペランド   |  |  |  |  |  |

| ともにSNaN               | QNaN化されたdest           |  |  |  |  |  |

| ともにQNaN               | dest                   |  |  |  |  |  |

| SNaNと実数               | QNaN化されたSNaNソースオペランド   |  |  |  |  |  |

| QNaNと実数               | QNaNソースオペランド           |  |  |  |  |  |

| どちらもNaNでないケースで無効演算発生時 | 7FFFFFFh               |  |  |  |  |  |

注. SNaNのQNaN化は、仮数部の最上位ビットを"1"にして行います。

### 1.3.6 非実装処理

非実装処理は、DN="0"で非正規化数が演算オペランドとして与えられるか、DN="0"で演算の結果、アンダフローが発生した場合に発生します。DN="1"では非実装処理は発生しません。

非実装処理発生による例外処理を禁止することはできません(非実装処理発生による例外処理を禁止する 例外処理許可ビットはありません)。デスティネーションレジスタは変化しません。

## 1.4 プロセッサモード

RX CPU には、スーパバイザモード、およびユーザモードの2つのプロセッサモードがあります。これらのプロセッサモードとメモリプロテクション機能を使用して、CPU リソースやメモリに対する階層的な保護機構を実現することができます。各プロセッサモードには、メモリアクセスや実行可能な命令に対する権限を規定しており、スーパバイザモードはユーザモードより高い権限を持っています。リセット後は、スーパバイザモードで動作します。

## 1.4.1 スーパバイザモード

スーパバイザモードでは、すべての CPU リソースにアクセスすることができ、また、すべての命令を実行することができます。ただし、MVTC、POPC 命令によるプロセッサステータスワード (PSW) のプロセッサモード設定ビット (PM) への書き込みは無視されます。PM ビットへの書き込み方法については、「1.2.2.4 プロセッサステータスワード (PSW)」を参照してください。

### 1.4.2 ユーザモード

ユーザモードでは、一部の CPU リソースへのライトアクセスが制限されます。ライトアクセスが制限される CPU リソースは以下のとおりです。この制限はすべての命令からのアクセスが対象になります。

- プロセッサステータスワード (PSW) の一部のビット (IPL[3:0]、PM、U、I)

- 割り込みスタックポインタ (ISP)

- 割り込みテーブルレジスタ (INTB)

- バックアップ PSW (BPSW)

- バックアップ PC (BPC)

- 高速割り込みベクタレジスタ (FINTV)

### 1.4.3 特権命令

特権命令は、スーパバイザモードでのみ実行可能な命令です。ユーザモードで特権命令を実行すると、特権命令例外が発生します。特権命令には、RTFI、MVTIPL、RTE、WAIT 命令があります。

### 1.4.4 プロセッサモード間の移行

プロセッサモードは、プロセッサステータスワード (PSW) のプロセッサモード設定ビット (PM) によって切り替えられます。ただし、MVTC、POPC 命令による PM ビットの書き換えは無効です。以下に示す方法で切り替えてください。

(1) ユーザモードからスーパバイザモードへの移行

例外が発生すると PSW の PM ビットが "0" になり、CPU はスーパバイザモードへ移行します。ハードウェア前処理は、スーパバイザモードで実行されます。例外が発生する直前のプロセッサモードは、退避された PSW の PM ビットに保持されます。

(2) スーパバイザモードからユーザモードへの移行

スタック上に退避されている PSW の PM ビットを "1" にした後 RTE 命令を実行する、あるいはバック アップ PSW (BPSW) に退避されている PSW の PM ビットを "1" にした後 RTFI 命令を実行することにより、ユーザモードへ移行します。ユーザモードへ移行すると、PSW のスタックポインタ指定ビット(U)が "1" になります。

## 1.5 データタイプ

RX CPU は、整数、浮動小数点数、ビット、ストリングの4種類のデータを扱うことができます。

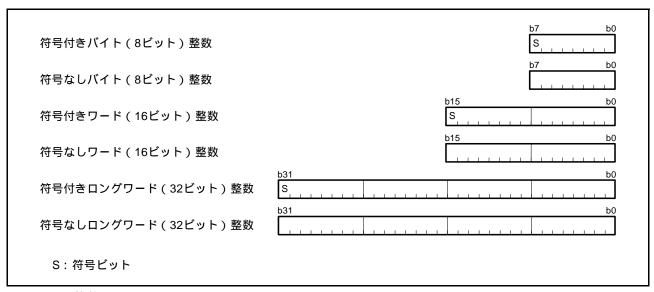

### 1.5.1 整数

整数には、符号付きと、符号なしがあります。符号付き整数の負の値は、2の補数で表現します。

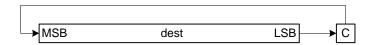

#### 図 1.2 整数

### 1.5.2 浮動小数点数

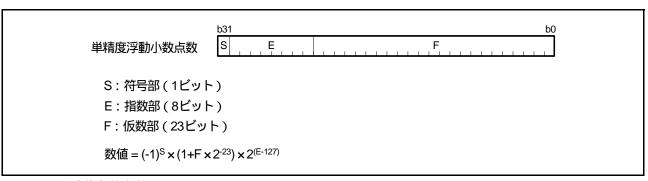

浮動小数点数は、IEEE754で規定されている単精度浮動小数点数に対応しています。浮動小数点数は、浮動小数点演算命令 FADD、FCMP、FDIV、FMUL、FSUB、FTOI、ITOF、ROUND の 8 種類の命令で使用できます。

注. RX100シリーズ、RX200シリーズは、浮動小数点演算命令に対応していないため、浮動小数点数は使用しません。

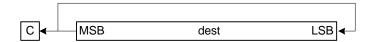

### 図 1.3 浮動小数点数

浮動小数点数は、以下の数値に対応しています。

- 0 < E < 255 (正規化数 Normal Numbers)

- E=0かつF=0 (ゼロ Signed Zero)

- E=0かつF>0 (非正規化数 Subnormal Numbers) (注)

- E = 255 かつ F = 0 (無限大 Infinity)

- E = 255 かつ F > 0 (非数 NaN : Not a Number)

- 注. FPSW の DN ビットが "1" のときは、0 として扱います。DN ビットが "0" のときは、非実装処理が発生します。

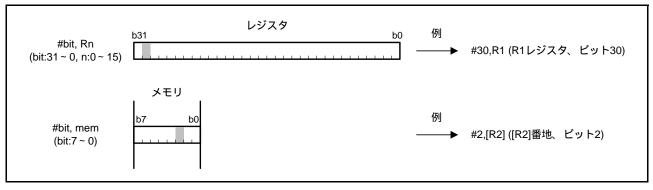

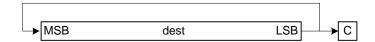

## 1.5.3 ビット

ビットは、ビット操作命令 BCLR、BMCnd、BNOT、BSET、BTST の 5 種類の命令で使用できます。 レジスタのビットは、対象とするレジスタと、31  $\sim$  0 のビット番号で指定します。

メモリのビットは、対象とするアドレスと、 $7 \sim 0$ のビット番号で指定します。アドレス指定に使用できるアドレッシングモードは、レジスタ間接、レジスタ相対の2種類です。

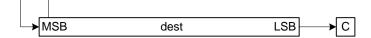

図 1.4 ビット

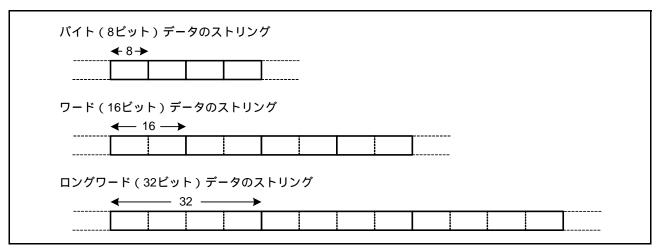

### 1.5.4 ストリング

ストリングとは、バイト (8 ビット)、ワード (16 ビット)、またはロングワード (32 ビット) のデータ を任意の数だけ連続して並べたデータタイプです。ストリングは、ストリング操作命令 SCMPU、SMOVB、SMOVF、SMOVU、SSTR、SUNTIL、SWHILE の7種類の命令で使用できます。

図 1.5 ストリング

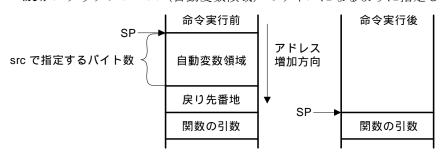

# 1.6 データ配置

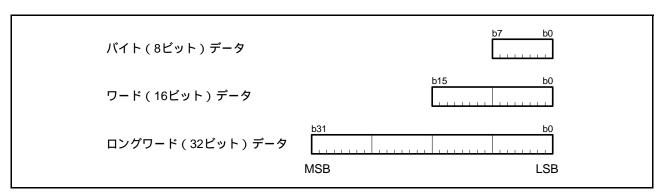

## 1.6.1 レジスタのデータ配置

レジスタのデータサイズと、ビット番号の関係を図1.6に示します。

図 1.6 レジスタのデータ配置

# 1.6.2 メモリ上のデータ配置

メモリ上のデータサイズは、バイト (8 ビット)、ワード (16 ビット)、ロングワード (32 ビット) の 3 種類です。データ配置は、リトルエンディアンか、ビッグエンディアンかを選択することができます。メモリ上のデータ配置を図 1.7 に示します。

| データタイプ    | アドレス                           | データイメージ<br>( リトルエンディアン ) |   |   | ı |   |   |     | ・タイメージ<br>グエンディアン)<br> |   |   |   |   |   |   |     |

|-----------|--------------------------------|--------------------------|---|---|---|---|---|-----|------------------------|---|---|---|---|---|---|-----|

| 1ビットデータ   | L番地                            | b7 7 6                   | 5 | 4 | 3 | 2 | 1 | b0  | b7                     | 6 | 5 | 4 | 3 | 2 | 1 | b0  |

| バイトデータ    | L番地                            | MSB                      |   |   |   |   |   | LSB | MSB                    |   |   |   |   |   |   | LSB |

| ワードデータ    | M番地<br>M+1番地                   | MSB                      |   |   |   |   |   | LSB | MSB                    |   |   |   |   |   |   | LSB |

| ロングワードデータ | N番地<br>N+1番地<br>N+2番地<br>N+3番地 | MSB                      |   |   |   |   |   | LSB | MSB                    |   |   |   |   |   |   | LSB |

図 1.7 メモリ上のデータ配置

### 1.7 ベクタテーブル

ベクタテーブルには、固定ベクタテーブルと可変ベクタテーブルがあります。ベクタテーブルは、1 ベクタあたり 4 バイトで構成されており、各ベクタには対応する例外処理ルーチンの先頭アドレスを設定します。

## 1.7.1 固定ベクタテーブル

注 1. RX100 シリーズ、RX200 シリーズは、浮動小数点演算命令に対応していないため、浮動小数点例外は発生しません。

|          | MSB <sub>I</sub> | I I      | LSB |  |  |  |  |

|----------|------------------|----------|-----|--|--|--|--|

| FFFFF80h | (予約領域)           |          |     |  |  |  |  |

| :        |                  |          |     |  |  |  |  |

| FFFFFCCh | (予約              | <br> 領域) |     |  |  |  |  |

| FFFFFD0h | 特権命令例外           |          |     |  |  |  |  |

| FFFFFD4h | アクセ              | ス例外      |     |  |  |  |  |

| FFFFFD8h | (予約              | 領域)      |     |  |  |  |  |

| FFFFFDCh | 未定義命令例外          |          |     |  |  |  |  |

| FFFFFE0h | (予約領域)           |          |     |  |  |  |  |

| FFFFFE4h | 浮動小数点例外 (注1)     |          |     |  |  |  |  |

| FFFFFE8h | (予約領域)           |          |     |  |  |  |  |

| FFFFFECh | (予約領域)           |          |     |  |  |  |  |

| FFFFFF0h | (予約領域)           |          |     |  |  |  |  |

| FFFFFF4h | (予約領域)           |          |     |  |  |  |  |

| FFFFFF8h | ノンマスカブル割り込み      |          |     |  |  |  |  |

| FFFFFFCh | リセット             |          |     |  |  |  |  |

注1. RX100シリーズ、RX200シリーズは、浮動小数点演算命令に対応していないため、浮動小数点例外は発生しません。

図 1.8 固定ベクタテーブル

# 1.7.2 可変ベクタテーブル

可変ベクタテーブルは、テーブルの配置アドレスを変えることができるベクタテーブルです。割り込みテーブルレジスタ (INTB) の内容で示された値を先頭アドレス (IntBase) とする 1,024 バイトの領域に、無条件トラップ、割り込みの各ベクタを配置しています。図 1.9 に可変ベクタテーブルを示します。

可変ベクタテーブルには、ベクタごとに番号  $(0\sim255)$  が付けられています。無条件トラップ発生要因の INT 命令では INT 命令番号  $(0\sim255)$  に対応したベクタが、BRK 命令では番号 0 のベクタが割り当てられています。また、割り込み要因では、製品ごとに決められた番号  $(0\sim255)$  が割り当てられています。

図 1.9 可変ベクタテーブル

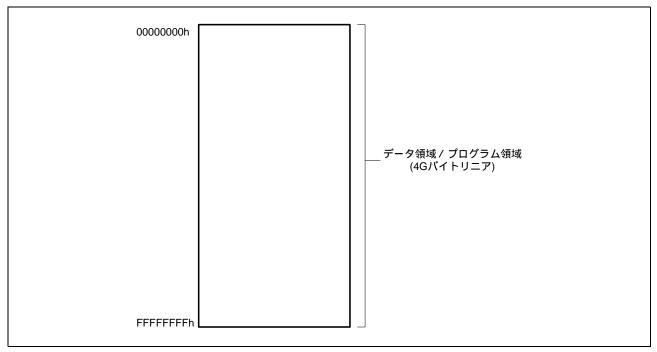

# 1.8 アドレス空間

RX CPU のアドレス空間は、00000000h 番地から FFFFFFF 番地までの 4G バイトあります。プログラム 領域およびデータ領域合計最大 4G バイトをリニアにアクセス可能です。RX CPU のアドレス空間を図 1.10 に示します。各領域は、各製品、動作モードによって異なります。詳細は、各製品のハードウェアマニュアルを参照してください。

図 1.10 アドレス空間

RXファミリ 2. アドレッシングモード

# 2. アドレッシングモード

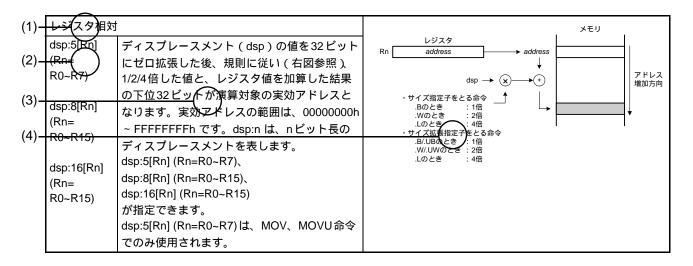

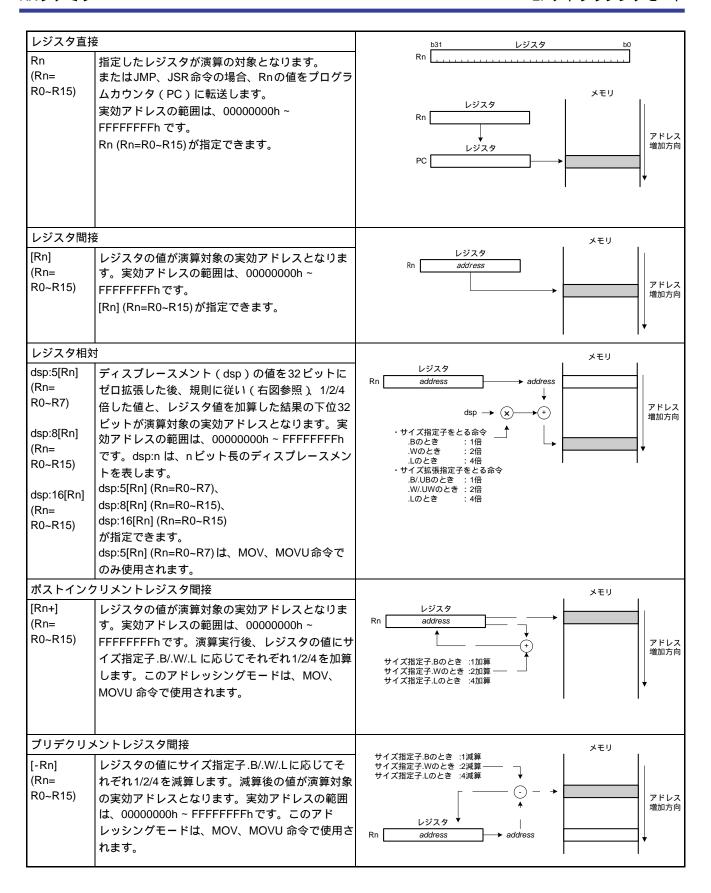

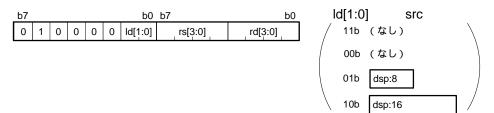

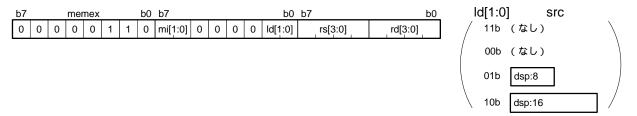

アドレッシングモードごとに、アドレッシングモードを示す記号、動作について説明します。 アドレッシングモードは、以下に示す 10 種類があります。

- 即値

- レジスタ直接

- レジスタ間接

- レジスタ相対

- ポストインクリメントレジスタ間接

- プリデクリメントレジスタ間接

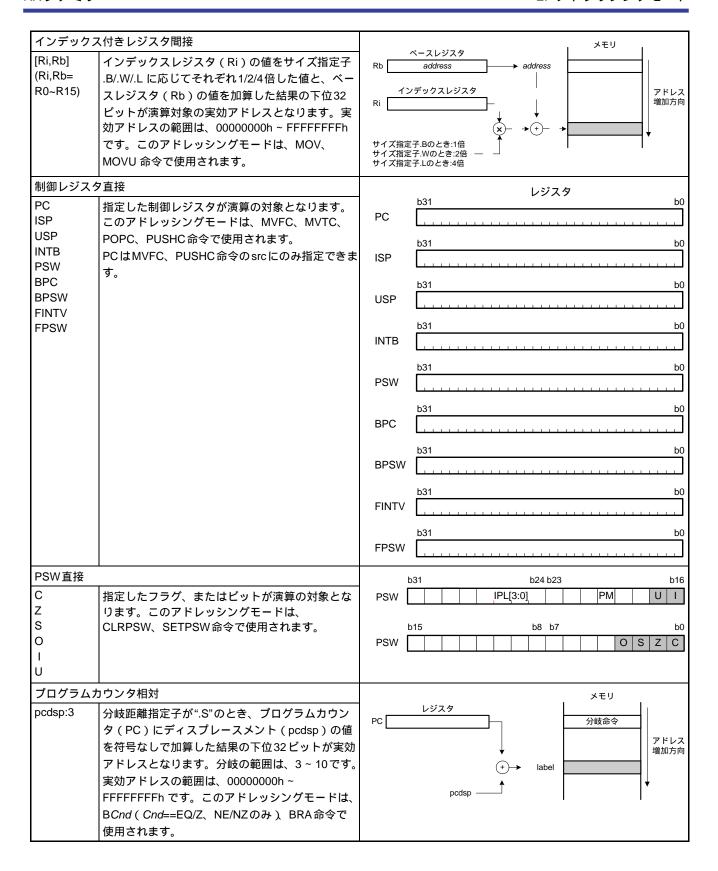

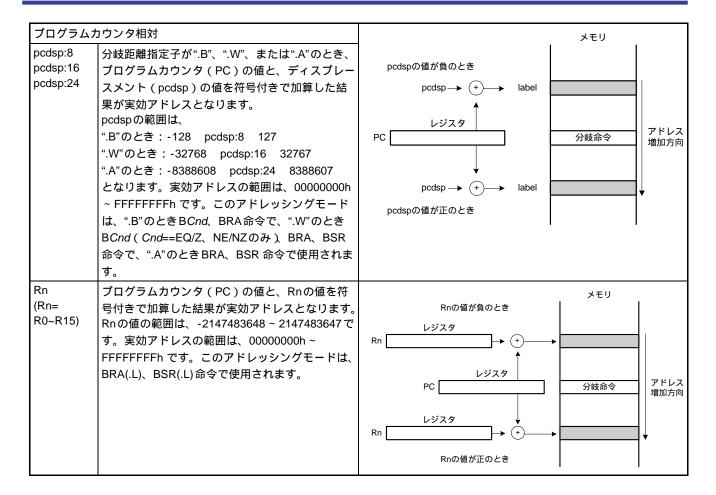

- インデックス付きレジスタ間接

- 制御レジスタ直接

- PSW 直接

- プログラムカウンタ相対

RXファミリ 2. アドレッシングモード

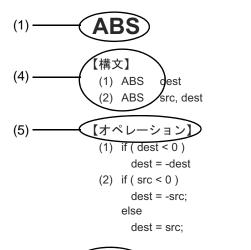

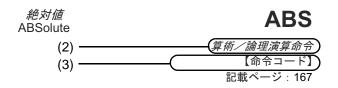

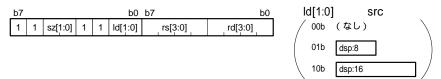

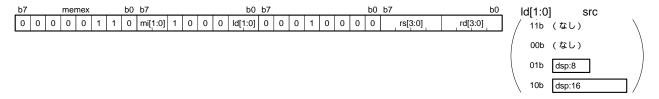

#### 2.1 本章の見方

本章の見方を以下に実例をあげて示します。

#### (1) 名称

アドレッシングモードの名称です。

#### (2) 記号

アドレッシングモードを示す記号です。

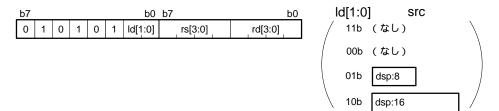

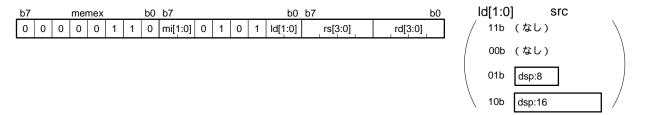

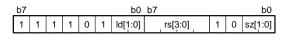

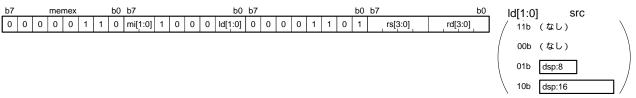

":8"、":16"は、直前の値の有効ビット数を示します。マニュアルの記載上、有効ビット数を明記する必要があるために付加していますが、プログラムを記述するときは、付加する必要はありません。

#### (3) 解説

動作、実効アドレスの範囲を説明します。

#### (4) 動作図

動作を図で説明します。

# 2.2 アドレッシングモード

| 即値                           |                                                                                                                                                                               |                         |                          | b0              |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------|-----------------|

| #IMM:1<br>#IMM:3<br>#IMM:4   | ・#IMM:1<br>#IMMで示した1ビット即値が演算の対象となりま                                                                                                                                           | #IMM:1                  |                          | b2 b0           |

| #UIMM:4<br>#IMM:5            | す。このアドレッシングモードは、RACW命令の<br>ソースで使用されます。                                                                                                                                        | #IMM:3                  |                          |                 |

|                              | ・#IMM:3<br>#IMMで示した3ビット即値が演算の対象となりま                                                                                                                                           | #IMM:4                  |                          | b3 b0           |

|                              | す。このアドレッシングモードは、ビット操作命令(BCLR、BM <i>Cnd</i> 、BNOT、BSET、BTST)のビット番号指定で使用されます。                                                                                                   | #UIMM:4 b31             | ゼロ拡張                     | b4 b3 b0        |

|                              | ・#IMM:4<br>#IMMで示した4ビット即値が演算の対象となりま<br>す。このアドレッシングモードは、MVTIPL命令<br>の割り込み優先レベル指定で使用されます。                                                                                       | #IMM:5                  |                          | b4 b0           |

|                              | ・#UIMM:4<br>#UIMMで示した4ビット即値を32 ビットにゼロ拡張した結果が演算の対象となります。このアドレッシングモードは、ADD、AND、CMP、MOV、MUL、OR、SUB命令のソースで使用されます。                                                                 |                         |                          |                 |

|                              | ・#IMM:5 #IMMで示した5ビット即値が演算の対象となります。このアドレッシングモードは、ビット操作命令(BCLR、BM <i>Cnd</i> 、BNOT、BSET、BTST)のビット番号指定、算術/論理演算命令(SHAR、SHLL、SHLR)のシフト幅指定、および算術/論理演算命令(ROTL、ROTR)のローテート幅指定で使用されます。 |                         |                          |                 |

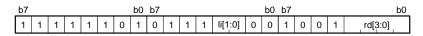

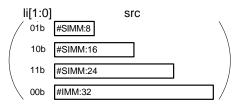

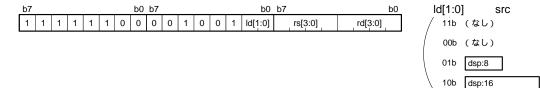

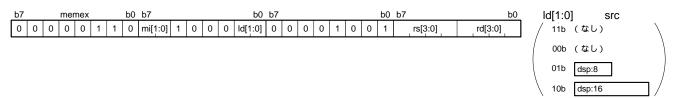

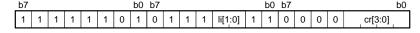

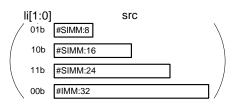

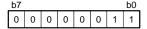

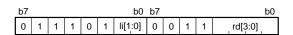

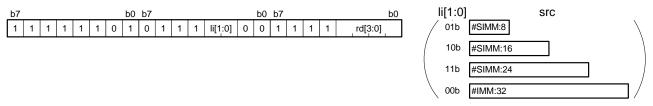

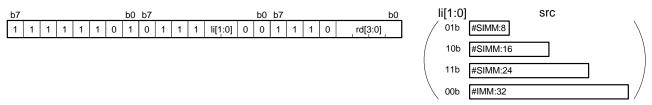

| #IMM:8<br>#SIMM:8<br>#UIMM:8 | 即値で指定した値が演算の対象となります。ただし、#UIMMで指定した即値は処理サイズにゼロ拡張した結果が、#SIMMで指定した即値は処理サイ                                                                                                        | <u>処理サイズが</u><br>#IMM:8 | Bのとき                     | b7 b0           |