## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<a href="http://www.renesas.com">http://www.renesas.com</a>)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

16

# CPUBD-2268F

H8S Super Low Power CPU Board

Microcomputer Development Environment System

# CPUBD-2268F – CPU Board for H8S/2200 Super Low Power Series Microcomputer User's Manual

Published by : Renesas System Solutions Asia Pte. Ltd.

Date : January 7th, 2004, version 1.0

Copyright(C) Renesas System Solutions Asia Pte. Ltd. All rights reserved.

### **Trademarks**

a) General

All brand or product names used in this manual are trademarks or registered trademarks of their respective companies or organizations.

b) Specific

Microsoft, MS and MS-DOS is registered trademark.

Windows and Windows NT are trademarks of Microsoft Corporation.

Pentium is a registered trademark of Intel.

Renesas System Solutions Asia Pte. Ltd.

### IMPORTANT INFORMATION

- READ this user's manual before using this emulator product.

- KEEP the user's manual handy for future reference.

Do not attempt to use the product until you fully understand its mechanism.

#### **CPUBD:**

Throughout this document, the term "CPUBD" shall be defined as the H8S Super Low Power Series Low-cost CPU Board, CPUBD-2268F produced only by Renesas System Solutions Asia Pte. Ltd. excludes all subsidiary products. The user system or a host computer is not included in this definition.

### **Purpose of the Product:**

This product is a development-supporting unit for use as training and evaluation tool. The product must only be used for the above purpose.

#### **Improvement Policy:**

Renesas System Solutions Asia Pte. Ltd. (hereafter collectively referred to as Renesas) pursues a policy of continuing improvement in design, performance, and safety of the emulator product. Renesas reserves the right to change, wholly or partially, the specifications, design, user's manual, and other documentation at any time without notice.

### **Target User of the Product:**

This product should only be used by those who have carefully read and thoroughly understood the information as well as restrictions contained in the user's manual. Do not attempt to use the product until you fully understand its mechanism.

It is highly recommended that first-time user be instructed by users that are well versed in the operation of emulator product.

### LIMITED WARRANTY

Renesas warrants its products to be manufactured in accordance with published specifications and free from defects in material and/or workmanship. The foregoing warranty does not cover damage caused by fair wear and tear, abnormal store condition, incorrect use, accidental misuse, abuse, neglect, corruption, misapplication, addition or modification or by the use with other hardware or software, as the case may be, with which the product is incompatible. No warranty of fitness for a particular purpose is offered. The user assumes the entire risk of using the product. Any liability of Renesas is limited exclusively to the replacement of defective materials or workmanship.

### **DISCLAIMER**

RENESAS MAKES NO WARRANTIES, EITHER EXPRESS OR IMPLED, ORAL OR WRITTEN, EXCEPT AS PROVIDED HEREIN, INCLUDING WITHOUT LIMITATION THEREOF, WARRANTIES AS TO MARKETABILITY, MECRCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE OR USE, OR AGAINST INFRINGEMENT OF ANY PATENT. IN NO EVENT SHALL RENESAS BE LIABLE FOR ANY DIRECT, INCIDENTAL OR CONSEQUENTIAL DAMAGES OF ANY NATURE, OR LOSSES OR EXPENSES RESULTING FROM ANY DEFECTIVE EMULATOR PRODUCT, THE USE OF ANY EMULATOR PRODUCT OR ITS DOCUMENTATION, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. EXCEPT AS EXPRESSLY STATED OTHERWISE IN THIS WARRANTY, THIS EMULATOR PRODUCT IS SOLD "AS IS". AND YOU MUST ASSUME ALL RISK FOR THE USE AND RESULTS OBTAINED FROM THE EMULATOR PRODUCT.

#### **State Law:**

Some states do not allow the exclusion or limitation of implied warranty or liability for incidental or consequential damages, so the above limitation or exclusion may not apply to you. This warranty gives you specific legal rights, and you may have other rights which may varies from state to state.

### The Warranty is Void in the Following Cases:

Renesas shall have no liability or legal responsibility for any problems caused by misuse, abuse, misapplication, neglect, improper handling, installation, repair or modifications of the emulator product without Renesas's prior written consent or any problems caused by the user system.

#### **Restrictions:**

- 1. Earthing (applies only to manual for Renesas hardware products)

- This hardware is designed for use with equipment that is fully earthed.

- Ensure that all equipments used are appropriately earthed.

- Failure to do so could lead to danger for the operator or damaged to equipments.

- 2. Electrostatic Discharge Precautions (applies only to manuals for Renesas hardware products)

- This hardware contains devices that are sensitive to electrostatic discharge.

- Ensure appropriate precautions are observed during handling and accessing connections.

- Failure to do so could result in damage to the equipment.

### All Right Reserved:

This user's manual and emulator product are copyrighted and all rights are reserved by Renesas. No part of this user's manual, all or part, any be reproduced or duplicated in any form, in hardcopy or machine-readable form, by any means available without Renesas's prior written consent.

### Other Important Things to Keep in Mind:

- Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Renesas Technology's semiconductor products. Renesas assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 2. No license is granted by implication or otherwise under any patents or other rights of any third party or Renesas.

- 3. MEDICAL APPLICATIONS: Renesas Technology's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Renesas Technology (Asia Sales company). Such use includes, but is not limited to, use in life support systems. Buyers of Renesas Technology's products are requested to notify the relevant Renesas Technology (Asia Sales offices) when planning to use the products in MEDICAL APPLICATIONS.

### Figures:

Some figures in this user's manual may show items different from your actual system.

### **Limited Anticipation of Danger:**

Renesas cannot anticipate every possible circumstance that might involve a potential hazard. The warnings in this user's manual and on the emulator product are therefore not all inclusive. Therefore, you must use the emulator product safely at your own risk.

### **PREFACE**

#### About this manual

This manual explains how to install and setup the H8S/2268F CPU board for evaluating the performance of the H8S/2268F microcomputer. Hereafter, the H8S/2268F CPU board shall term as 'CPUBD'.

Operation using the HEW pure debugger software is also detailed in the manual.

#### 1. Introduction

Gives an introduction about the CPU board, package, specification and functions.

### 2. Installation

Explains how to install the hardware and accompanied software to a host computer.

### 3. Setup of HEW (Pure Debugger) for CPU Board

Describes the setup steps before embarking on a new project development.

### 4. Performing Emulation

Describes the various functions available in HEW

### 5. Usage Constraints

Highlights the various constraints that may encounter by user when operating the CPU board.

#### 6. Hardware

Explains the various hardware blocks in the CPU board.

### 7. Monitor software

Explains the purpose of the monitor software, the implementation requirements and how to use the monitor software.

### 8. Flash Programming

Explains the difference between two programming modes and how CPU board operates in these modes.

#### 9. Tutorial

Provides a step-by-step guide in using the CPU board to perform debugging.

### 10. Demonstration Program

Provides two demonstration programs for user to have hands-on experience with the CPU board.

### **11.** Trouble-Shooting

Advises on some basic fault finding methods and commonly make mistakes.

Appendix A - CPUBD-2268F Board Layout

Appendix B – H8S/2268F Memory Map

Appendix C – Pin Assignment for JP1 ~ JP4

Appendix D - Pin assignment for CON1 & CON2

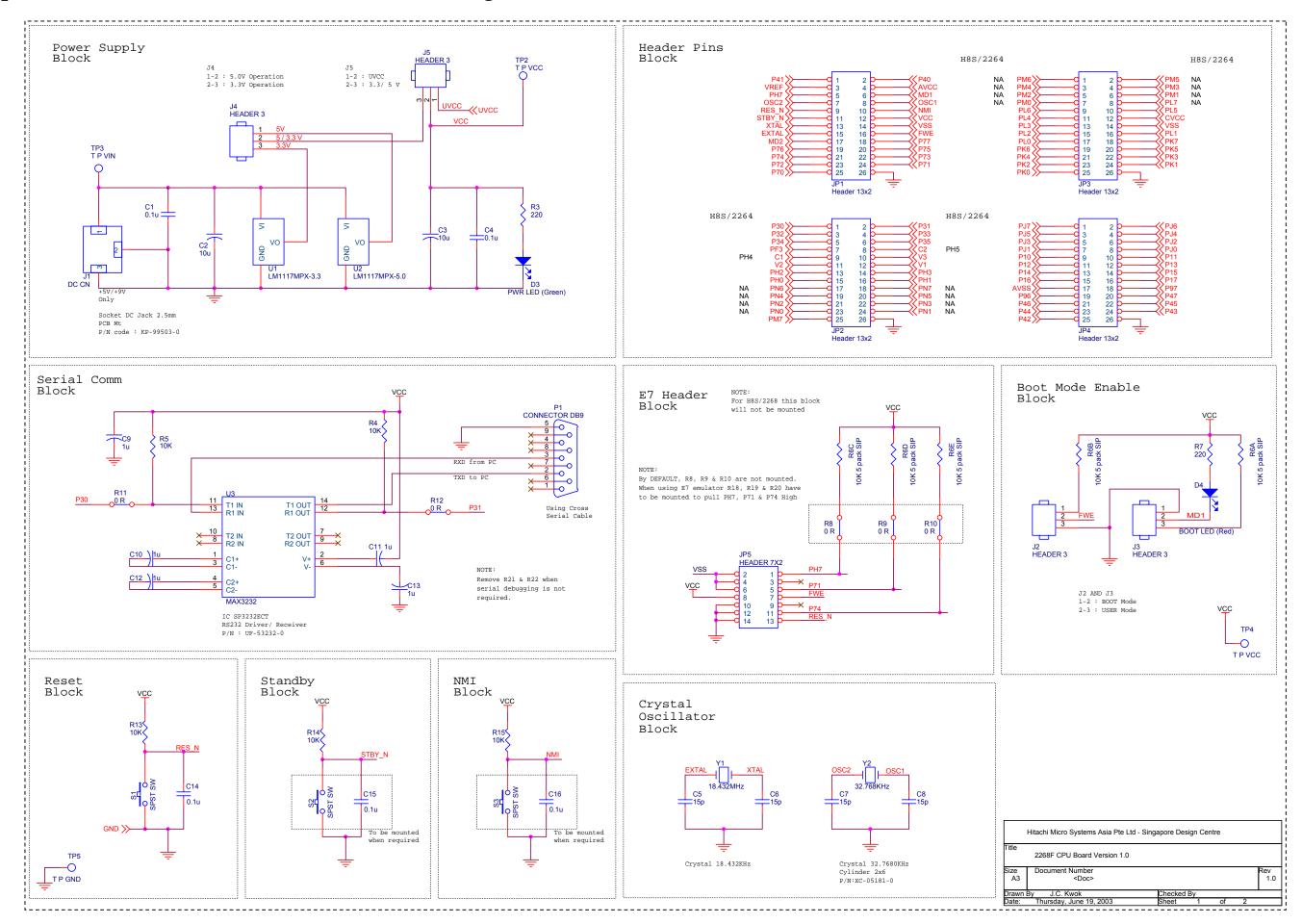

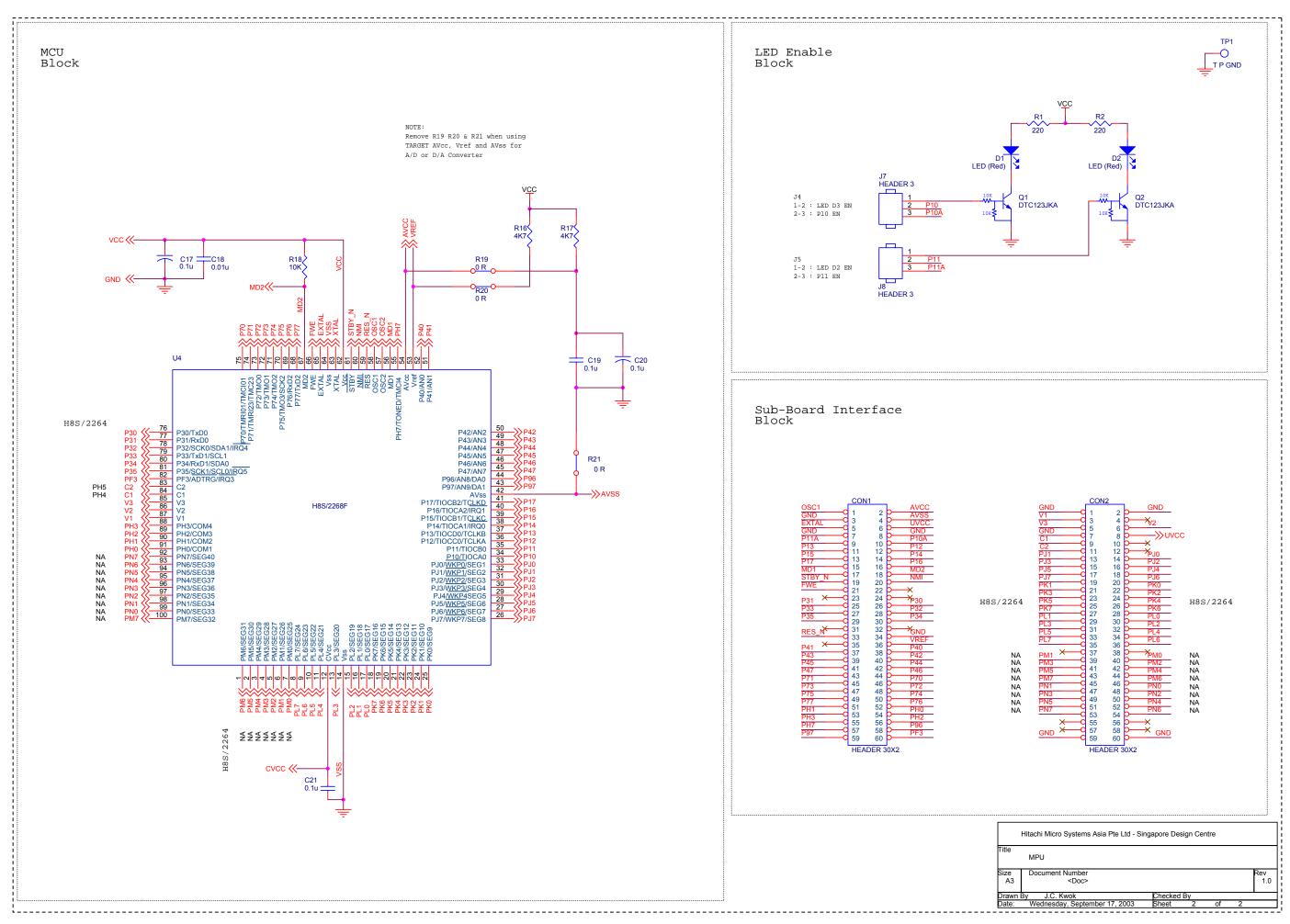

Appendix E – Schematic drawings

Appendix F – Bill of Materials

### **Technical Support**

The CPUBD is a product for evaluation purposes only. We do NOT supply the same level of support as for the full functioned development tools, however, you may contact the sales offices for downloads and documents.

### **Related Manuals:**

H8S, H8/300 series C/C++ Compiler, Assembler, Optimizing Linkage Editor User's Manual H8S/2268 Series, H8S/2264 Series Hardware Manual

# **Table of Contents**

| SECTION 1. | INTRODUCTION                                               | 1  |

|------------|------------------------------------------------------------|----|

| 1.1. SPEC  | IFICATION                                                  | 2  |

|            | General                                                    |    |

|            | Serial Communication                                       |    |

|            | Power Input                                                |    |

|            | Memory Map                                                 |    |

|            | Interface with Application Board                           |    |

|            | Interface with E7 emulator                                 |    |

|            | Monitor software                                           |    |

|            | BD Functional Blocks                                       |    |

|            | AGE                                                        |    |

|            | Hardware Components                                        |    |

|            | Software Components                                        |    |

|            | MARY OF CPUBD-2268F FUNCTIONS.                             |    |

| SECTION 2. |                                                            |    |

|            |                                                            |    |

|            | EL OF PARTS ON CPU BOARD                                   |    |

|            | ALLING THE CPU BOARD                                       |    |

|            | MUNICATION PORT BAUD RATE                                  |    |

|            | ER SUPPLY FOR CPU BOARD                                    |    |

|            | PERS OPTIONS                                               |    |

|            | Voltage Regulator Selection                                |    |

|            | Power Supply Selection Jumpers for MCU                     |    |

|            | User Program Mode [Standalone] Selection Jumpers [Default] |    |

|            | Boot Mode Selection Jumpers                                |    |

|            | Flash Write Enable                                         |    |

|            | User LED Selection                                         |    |

| 2.6. INST. | ALLATION OF HEW (PURE DEBUGGER) FOR CPU BOARD              | 13 |

| 2.7. Regi  | STERING TOOLCHAINS                                         | 18 |

| SECTION 3. | SETUP OF HEW (PURE DEBUGGER) FOR CPU BOARD                 | 20 |

| 3.1. Runi  | NING HEW (PURE DEBUGGER) FOR CPU BOARD                     | 20 |

|            | ATING A NEW WORKSPACE                                      |    |

|            | Without Toolchain                                          |    |

|            | With Toolchain                                             |    |

|            | CTING THE TARGET (DEBUG SETTINGS)                          |    |

| SECTION 4. | PERFORMING EMULATION                                       |    |

|            |                                                            |    |

|            | I-PERFORMANCE EMBEDDED WORKSHOP                            |    |

|            | PILER CONFIGURATION & DEBUGGER SESSION                     |    |

|            | Session Without Toolchain                                  |    |

|            | Session With Toolchain                                     |    |

|            | JG SETTINGS                                                |    |

|            | NECTING & DISCONNECTING WITH THE EMULATOR                  |    |

|            | LATOR SETTING                                              |    |

|            | Configure Platform                                         |    |

| 4.5.1.1.   |                                                            |    |

| 4.5.2.     | Memory Mapping                                             | 36 |

|            |                                                            |    |

| 4.6.    | VIEWING OF PROGRAM                                    | 38 |

|---------|-------------------------------------------------------|----|

| 4.6     | 5.1. Source Code level                                |    |

| 4.6     | 5.2. Disassembly level                                | 39 |

| 4.7.    | MCU RELATED INFORMATION                               | 40 |

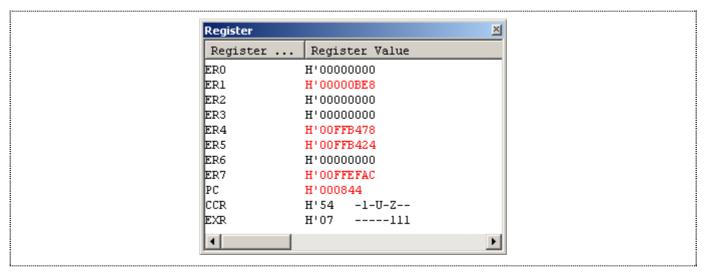

| 4.7     | 7.1. Registers                                        | 40 |

| 4.7     | 7.2. Memory                                           | 41 |

| 4.7     | 7.3. I/O                                              | 41 |

| 4.7     | 7.4. Status                                           | 42 |

| 4       | 4.7.4.1. Status - Memory                              | 42 |

| 4       | 4.7.4.2. Status - Platform                            | 43 |

| 4       | 4.7.4.3. Status - Events                              | 43 |

| 4.7     | 7.5. Symbol                                           | 44 |

| 4       | 4.7.5.1. Label                                        | 44 |

| 4       | 4.7.5.2. Watch                                        | 45 |

| 4       | 4.7.5.3. Local                                        | 46 |

| 4.7     | 7.6. Break Functions                                  | 47 |

| 4.7     | 7.7. Stack Trace                                      |    |

| 4.8.    | MCU MEMORY MANIPULATION                               | 49 |

| 4.9.    | EXECUTION OF MCU CODE                                 | 50 |

| 4.9     | 9.1. Reset CPU                                        | 50 |

| 4.9     | 9.2. Go, Reset Go, Goto Cursor, Set PC to Cursor, Run | 51 |

| 4.9     | 9.3. Step Functions                                   | 52 |

| 4.10.   | C-SOURCE LEVEL DEBUGGING                              | 54 |

| SECTION | ON 5. USAGE PRECAUTIONS                               | 55 |

|         |                                                       |    |

| 5.1.    | CORRUPTION OF MONITOR SOFTWARE                        |    |

| 5.2.    | Interrupt                                             |    |

| 5.3.    | TIMING ISSUES                                         |    |

| 5.4.    | WATCHDOG TIMER                                        |    |

| 5.5.    | SCIO, PC Break* and TRAP1                             |    |

| 5.6.    | SOFTWARE BREAKPOINT                                   |    |

| 5.7.    | STEP                                                  |    |

| 5.8.    | POWER-DOWN MODES                                      | 57 |

| 5.9.    | E7 INTERFACE [APPLICABLE WITH H8S/2264F MCU ONLY]     |    |

| 5.10.   | OTHER CONSTRAINTS                                     | 58 |

| SECTION | ON 6. HARDWARE                                        | 59 |

| 6.1.    | Microcomputer                                         | 59 |

| 6.2.    | POWER SUPPLY CIRCUITRY                                |    |

| 6.3.    | Reset Circuitry                                       |    |

| 6.4.    | CLOCK CIRCUITRY                                       | 60 |

| 6.5.    | SERIAL COMMUNICATION BLOCK [VIA SCI0]                 | 60 |

| 6.6.    | FLASH ROM & RAM                                       |    |

| 6.7.    | LEDs                                                  |    |

| 6.8.    | BOOT MODE ENABLE                                      |    |

| 6.9.    | E7 INTERFACE [APPLICABLE WITH H8S/2264F MCU ONLY]     |    |

| 6.10.   |                                                       |    |

| 6.11.   |                                                       |    |

| SECTI   |                                                       |    |

|         |                                                       |    |

| 7.1.    | INTRODUCTION TO MONITOR SOFTWARE                      |    |

| 7.2.    | PROGRAM DEVELOPMENT                                   | 62 |

| 7.3. Moni   | ITOR SOFTWARE REQUIREMENTS                           | 62  |

|-------------|------------------------------------------------------|-----|

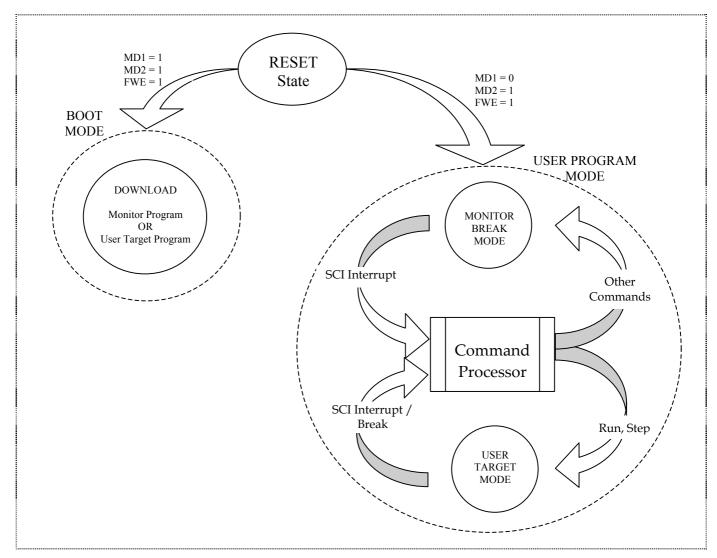

| 7.4. Modi   | E TRANSITION                                         | 63  |

| 7.5. Using  | G MONITOR SOFTWARE                                   | 64  |

| 7.6. Inter  | RRUPTS USED BY THE MONITOR                           | 64  |

| 7.7. Brea   | KPOINTS                                              | 65  |

| SECTION 8.  | FLASH PROGRAMMING                                    | 66  |

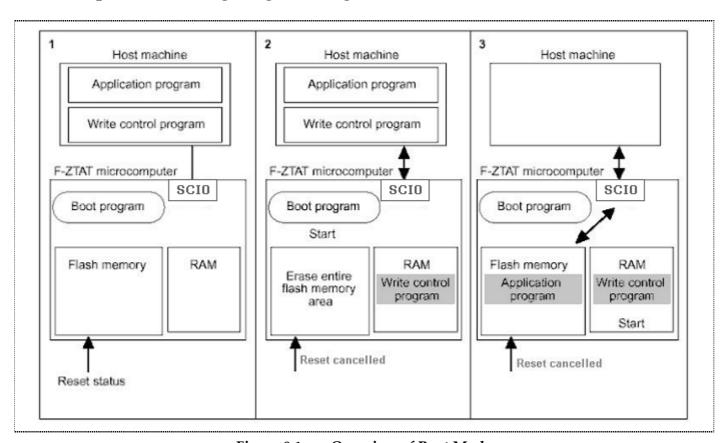

| 8.1. FLAS   | SH Programming the CPUBD                             | 66  |

| 8.1.1. I    | Boot Mode:                                           | 66  |

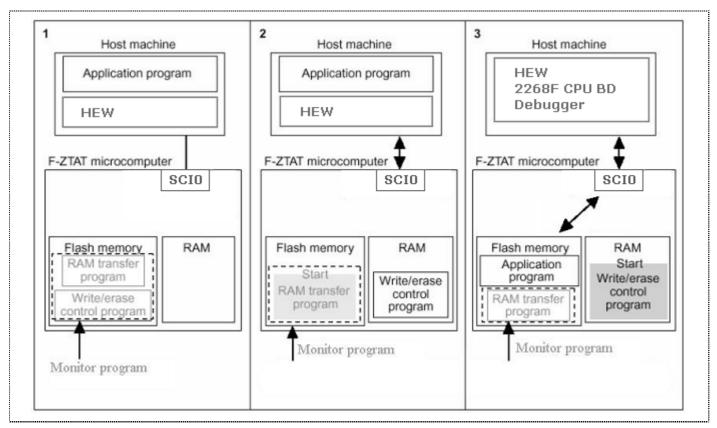

|             | User Program Mode:                                   |     |

| 8.2. Oper   | ATION DURING PROGRAMMING KERNEL EXECUTION            | 67  |

| SECTION 9.  | TUTORIAL                                             | 69  |

| 9.1. INTRO  | ODUCTION                                             | 69  |

|             | RVIEW                                                |     |

|             | ORIAL SETUP                                          |     |

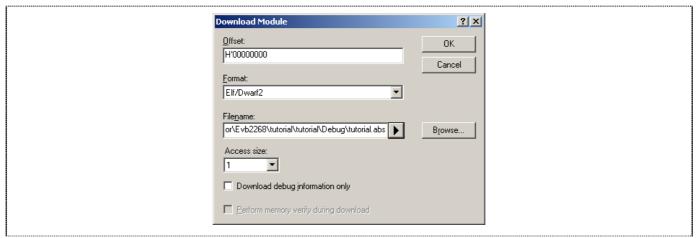

|             | Downloading the tutorial Program                     |     |

|             | Displaying the Program Listing                       |     |

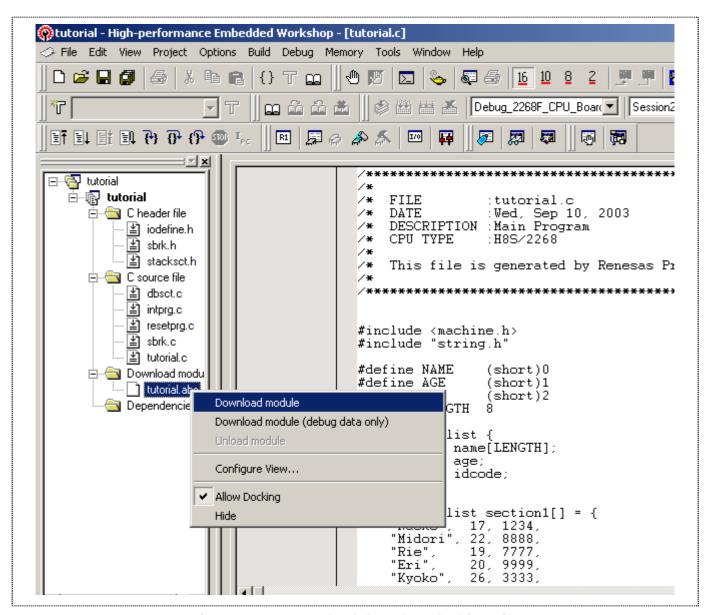

|             | G BREAKPOINTS                                        |     |

|             | Setting a Program Count (PC) Breakpoint              |     |

|             | Executing the Program                                |     |

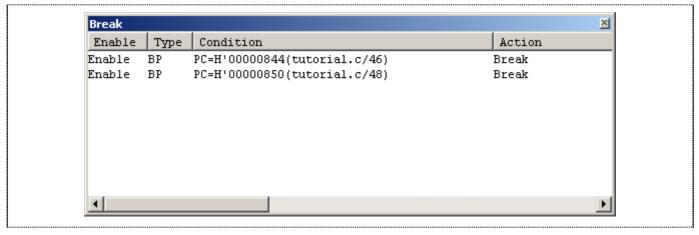

|             | Reviewing the Breakpoints<br>Examining MCU Registers |     |

|             | MINING MEMORY AND VARIABLES                          |     |

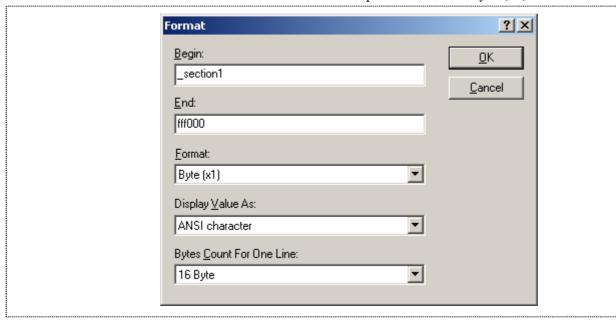

|             | Viewing Memory                                       |     |

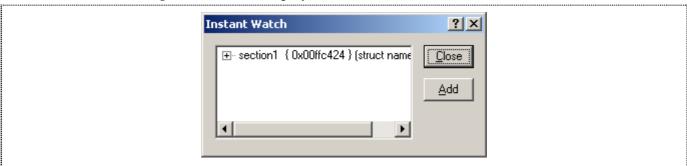

|             | Watching Variables                                   |     |

|             | PING THROUGH A PROGRAM                               |     |

| 9.7. WATO   | CHING LOCAL VARIABLES                                | 87  |

| 9.8. SAVE   | S THE SESSION                                        | 88  |

| 9.9. What   | T NEXT?                                              | 88  |

| SECTION 10. | DEMONSTRATION PROGRAM                                | 89  |

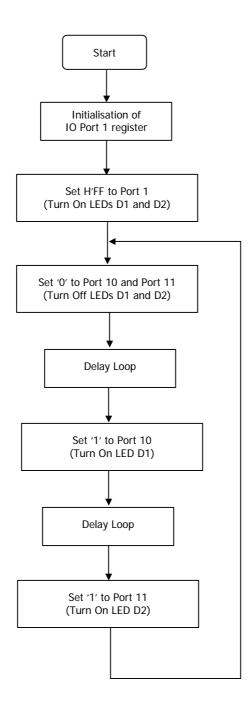

| 10.1. BL    | INKING LEDs                                          | 89  |

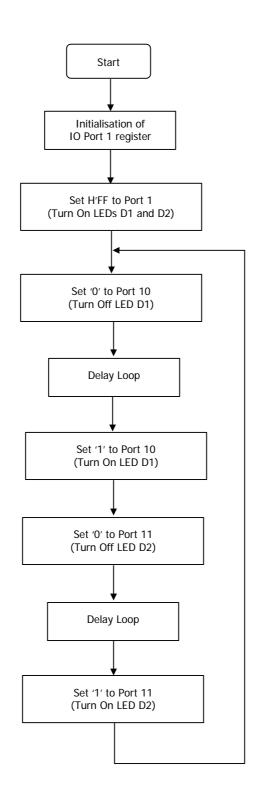

| 10.2. Ru    | INNING LEDs                                          | 90  |

| SECTION 11. | TROUBLE-SHOOTING                                     | 91  |

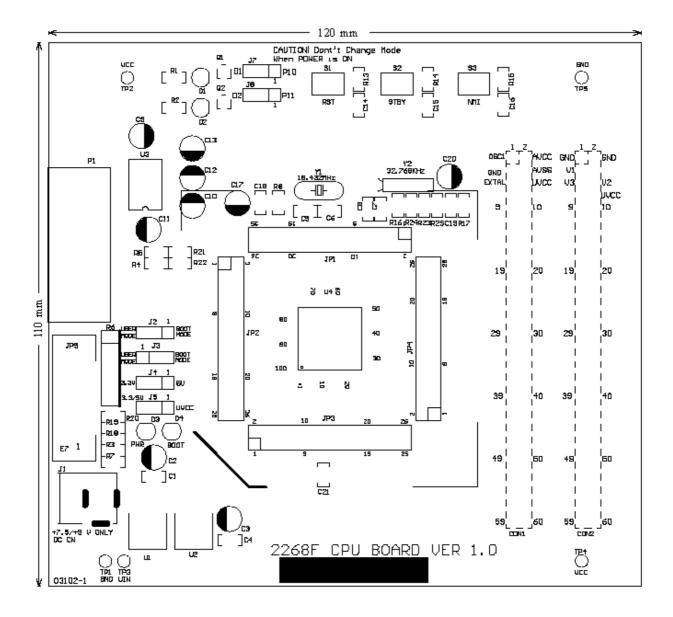

| APPENDIX A  | CPUBD-2268F BOARD LAYOUT                             | 93  |

| APPENDIX B  | H8S/2268F MEMORY MAP                                 | 95  |

| APPENDIX C  | PIN ASSIGNMENT FOR JP1~JP4                           | 96  |

| APPENDIX D  | PIN ASSIGNMENT FOR CON1 & CON2                       | 98  |

| APPENDIX E  | CPUBD-2268F SCHEMATIC DRAWINGS                       | 100 |

| APPENDIX F  | BILL OF MATERIALS                                    | 103 |

| RENESAS TE  | CHNOLOGY (ASIA SALES OFFICES)                        | 104 |

# Figures & Tables

| 4            |

|--------------|

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

| 16           |

| 16           |

|              |

|              |

|              |

|              |

| 20           |

| 21           |

| 21           |

| 22           |

| 22           |

|              |

| 24           |

| 24           |

|              |

| 26           |

| 27           |

| ΓOOLCHAIN29  |

| TOOLCHAIN 29 |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

| 39           |

| 40           |

| 40           |

| 41           |

| 41           |

| 42           |

| 43           |

| 43           |

| 44           |

| 44           |

|              |

| FIGURE 4.22 | Watch                                                      | 45 |

|-------------|------------------------------------------------------------|----|

| FIGURE 4.23 | Locals                                                     | 46 |

| FIGURE 4.24 | Tooltip                                                    | 46 |

| FIGURE 4.25 | VIEW CODE                                                  | 47 |

| FIGURE 4.26 | STACK TRACE                                                | 48 |

| FIGURE 4.27 | MEMORY FUNCTIONS                                           | 49 |

| FIGURE 4.28 | DEBUG FUNCTIONS                                            |    |

| FIGURE 4.29 | STEP PROGRAM                                               |    |

| FIGURE 4.30 | STEP MODE                                                  |    |

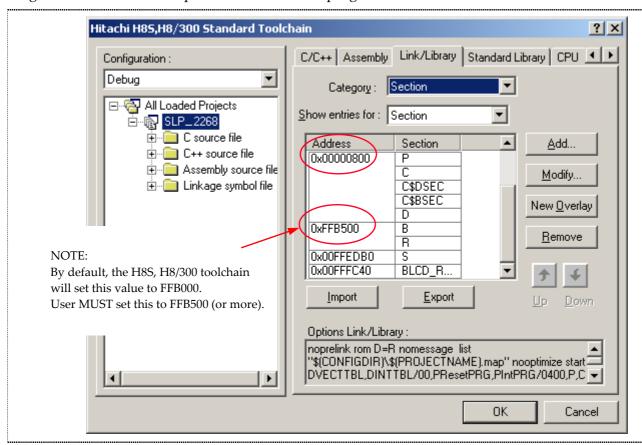

| FIGURE 5.1  | PROGRAM SECTION                                            |    |

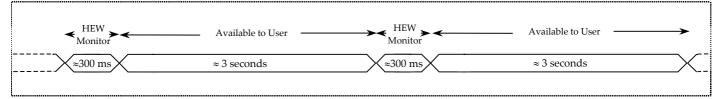

| FIGURE 5.2  | TIMING DIAGRAM OF HEW                                      |    |

| Figure 7.1  | MODE TRANSITION DIAGRAM                                    |    |

| Figure 8.1  | OVERVIEW OF BOOT MODE                                      |    |

| Figure 8.2  | OVERVIEW OF USER PROGRAM MODE                              |    |

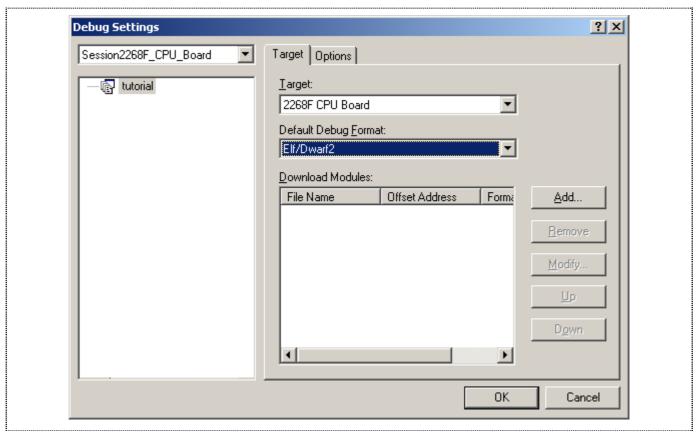

| Figure 9.1  | DEBUG SETTINGS WITH LOAD OBJECT FILE DIALOGUE              |    |

| Figure 9.2  | CONFIGURE LOAD OBJECT FILE DIALOGUE                        |    |

| Figure 9.3  | DOWNLOAD THE SELECTED OBJECT FILE                          |    |

| Figure 9.4  | SOURCE-WINDOW "RESETPRG.C"                                 |    |

| Figure 9.5  | SOURCE-WINDOW "TUTORIAL.C"                                 |    |

| Figure 9.6  | SETTING A BREAKPOINT                                       |    |

| Figure 9.7  | PROGRAM BREAK                                              |    |

| Figure 9.8  | SYSTEM STATUS WINDOW                                       |    |

| Figure 9.9  | Breakpoints Window                                         |    |

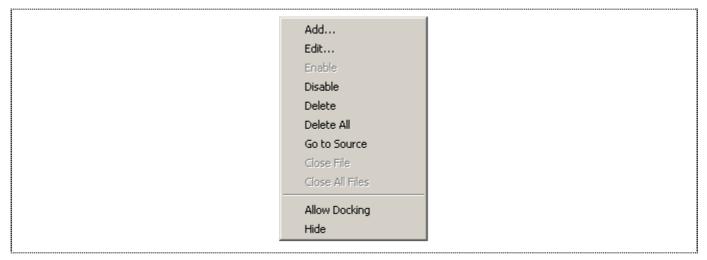

| FIGURE 9.10 | POPUP IN BREAKPOINTS WINDOW.                               |    |

| FIGURE 9.11 | CPU REGISTERS WINDOW                                       |    |

| FIGURE 9.12 | CHANGING REGISTER VALUE.                                   |    |

| FIGURE 9.13 | OPEN MEMORY WINDOW                                         |    |

| FIGURE 9.14 | MEMORY WINDOW                                              |    |

| FIGURE 9.15 | INSTANT WATCH DIALOGUE BOX                                 |    |

| FIGURE 9.16 | WATCH WINDOW                                               |    |

| FIGURE 9.17 | ADD WATCH DIALOGUE BOX                                     |    |

| FIGURE 9.18 | WATCH WINDOW                                               |    |

| FIGURE 9.19 | DISPLAYING INDIVIDUAL ELEMENTS IN AN ARRAY                 |    |

| FIGURE 9.20 | EXECUTING UP TO A FUNCTION CALL                            |    |

| FIGURE 9.21 | Locals Window                                              |    |

| FIGURE 9.22 | DISPLAYING INDIVIDUAL ELEMENTS IN AN ARRAY                 | δδ |

| Table 2.1   | LIST OF JUMPERS.                                           |    |

| TABLE 2.2   | OPERATING VOLTAGE SELECTION JUMPERS FOR MCU                |    |

| TABLE 2.3   | POWER SUPPLY SELECTION JUMPERS FOR MCU.                    |    |

| TABLE 2.4   | USER PROGRAM MODE [STANDALONE] SELECTION JUMPERS [DEFAULT] |    |

| TABLE 2.5   | BOOT MODE SELECTION JUMPERS                                |    |

| TABLE 2.6   | FLASH WRITE ENABLE JUMPERS                                 |    |

| TABLE 2.7   | LED SELECTION JUMPERS                                      |    |

| TABLE 4.1   | Types of Breaks Encountered During Emulation               |    |

| TABLE 6.1   | COMPONENTS FOR E7 EMULATOR                                 |    |

| Table 7.1   | INTERRUPTS USED BY MONITOR PROGRAM                         | 64 |

### **Section 1. Introduction**

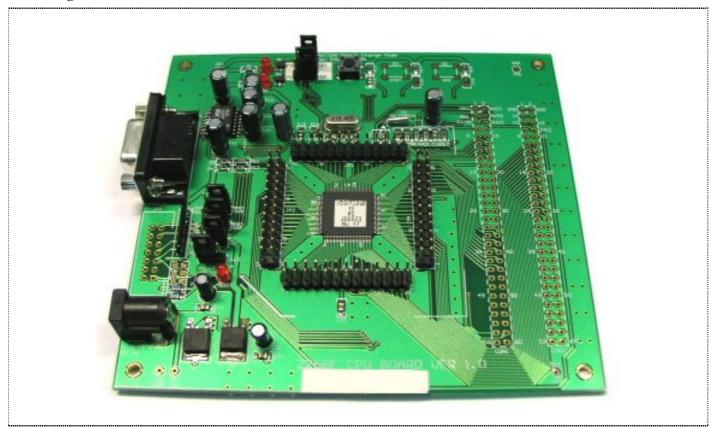

H8S/2268F CPU board (CPUBD-2268F) is a low cost training and MCU performance evaluation tool for the H8S Super Low Power family series of microcomputers.

It is also implemented with flash programming feature for the H8S/2268 F-ZTAT microcomputer. It contains a FP-100B package H8S/2268F microcomputer on the board. This CPUBD is also able to support the H8S/2264 F-ZTAT microcomputer.

The H8S/2268F CPU board adopts the standard Renesas High-performance Embedded Workshop (HEW). HEW is a Window-based integrated development platform. In this package, a pure debugger is included in the HEW component.

The diagram below shows the H8S/2268F CPU Board:

Figure 1.1 H8S/2268F CPU Board [CPUBD-2268F]

### 1.1. Specification

#### 1.1.1. General

- H8S/2268F microcomputer (using HD64F2268FA20 FP-100B device)

- 256Kbytes of FLASH memory (Monitor software uses approx. 7Kbytes)

- 16Kbytes of on-chip RAM (Monitor software work area uses 4Kbytes)

- Two user LED indicators

- One push button for reset control

- One boot mode LED indicator

- One Power LED indicator

- All Input/Output signals are being pulled out for user connection via CON1 & CON2

### 1.1.2. Serial Communication

- Utilizes Serial Communication Interface 0 via RS-232 DB-9F socket and RS-232 transceiver chip.

- Supports communication at a baud rate of 115,200bps [non-configurable during debugging].

### 1.1.3. Power Input

Accept dual DC power supply at +7.5 volt. ~ +9.0 volt only. [Ripple Rejection ratio more then 60dbm]

### 1.1.4. Memory Map

• If the CPUBD is to be used with debugger, a section in the memory area is reserved for monitor software. See Appendix *B* for memory map diagrams.

### 1.1.5. Interface with Application Board

It is designed to interface with any application board via two 30x2pin connector sockets.

### 1.1.6. Interface with E7 emulator

• For debugging with E7 emulator, it is only supported with H8S/2264F microcomputer.

#### 1.1.7. Monitor software

A FLASH-resident debugging monitor software hosted on the CPUBD for performing debugging operations.

### 1.2. CPUBD Functional Blocks

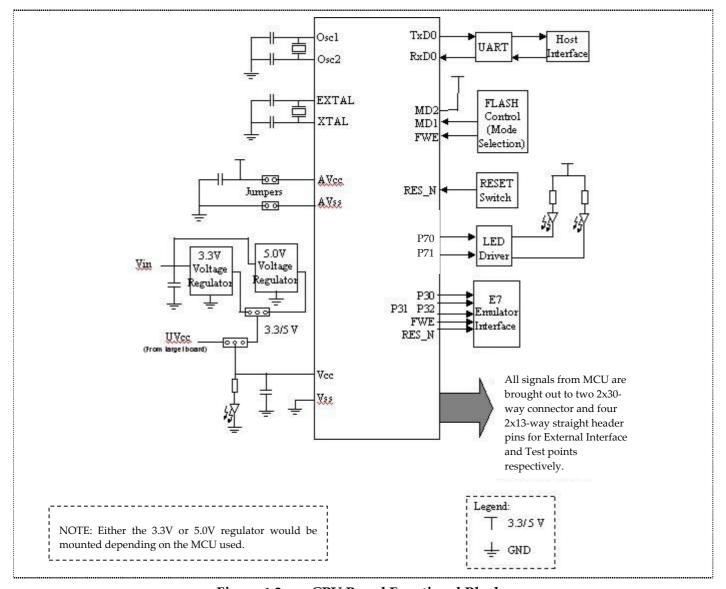

The CPUBD comprises of a H8S/2268F or H8S/2264F microcomputer, serial port, and boot mode control and user interface.

Figure 1.2 CPU Board Functional Blocks

The boot mode circuitry is necessary to place the CPUBD into Boot mode for programming the FLASH. To enter into Boot mode, respective jumper headers on the CPUBD must be shorted.

SCI0 is used to program the board's on-chip flash memory, using the flash programming software built-into the HEW with pure debugger. If the user is not using the serial port for flash programming the CPUBD or debugging, this serial port is available to user.

The HEW with pure debugger software combined with the monitor software programmed into the device provides high level debugging via SCI0.

When connecting external analogue signals, it is important that CPUBD is configured properly with respect to analogue voltage supply and reference. There are two user LEDs on board that can be used by user for their evaluation and are driven directly by the MCU.

All the I/O signals are being tracked out to four 2x13-way straight header connectors for user access as well as to two 2x30-way sockets to allow connection to a target board. These I/O signals are available to user if either flash programming or debugging is not used.

### 1.3. Package

The CPUBD is supplied in a package containing the following components:

Figure 1.3 CPUBD-2268F Package

### 1.3.1. Hardware Components

The hardware components included in the package are listed below.

- 1 x H8S/2268F CPU Board

- 1 x RS-232 Serial cable

- 1 x DC Power Input Jack free-end cable

- 2 x 30x2pin connectors [not assembled]

- 1 x 7x2pin connector [not assembled]

### 1.3.2. Software Components

The package includes a CD ROM containing:

- HEW installer

- User's Manual

- Tutorial program Source code

- Schematic drawings.

Before proceeding, user has to check that all the items listed in the packing list. Please contact the relevant Renesas Technology sales office in Asia if any item is missing.

## 1.4. Summary of CPUBD-2268F functions

| Items                        | Specifications                                                                                                                                                                                                                                                |  |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Supported Microcomputers     | ■ H8S/2268F and H8S/2264F                                                                                                                                                                                                                                     |  |

| Operating Frequency          | ■ 18.432MHz (System clock)                                                                                                                                                                                                                                    |  |

|                              | ■ 32.768KHz (Sub clock)                                                                                                                                                                                                                                       |  |

| Supported Operating Voltage  | ■ 3.3 and 5.0 Volts.*1                                                                                                                                                                                                                                        |  |

| Host Machine                 | <ul> <li>Recommended Pentium<sup>TM</sup> III or equivalent processor PC</li> <li>Recommended 128Mbytes RAM and 100Mbytes hard dispace</li> <li>Microsoft Windows 98, Windows Me, Windows NT 4 Windows 2000 or Windows XP</li> <li>One Serial port</li> </ul> |  |

| Host Interface               | <ul><li>RS-232 Serial Interface</li><li>Baud rate @ 115,200 bps</li></ul>                                                                                                                                                                                     |  |

| Supported File Format        | <ul><li>Motorola S-type</li><li>ELF/Dwarf2</li></ul>                                                                                                                                                                                                          |  |

| Interface Software           | HEW with pure debugger                                                                                                                                                                                                                                        |  |

| Emulation Functions          | <ul> <li>C – source level debugging (e.g. instant watch)</li> <li>Modify and display MCU registers</li> <li>Perform real-time emulation of a target program</li> </ul>                                                                                        |  |

| Memory Functions             | <ul><li>Copy, Search, Fill, Load and Save memory functions</li><li>Modifies and displays memory content</li></ul>                                                                                                                                             |  |

| Breakpoint                   | PC breakpoint (max. 256)                                                                                                                                                                                                                                      |  |

| Step Functions               | Step In/ Step Out/ Step Over                                                                                                                                                                                                                                  |  |

| On-board Programming         | <ul> <li>Support on-board programming - Boot mode and User program mode</li> </ul>                                                                                                                                                                            |  |

| Flash Protection             | Flash program/ erase protection by hardware                                                                                                                                                                                                                   |  |

| User LEDs                    | Supports two user's LEDs                                                                                                                                                                                                                                      |  |

| Interface with E7 Emulator   | ■ Supports E7 emulator* <sup>2</sup>                                                                                                                                                                                                                          |  |

| Interface with Target system | Supports emulation on a target system                                                                                                                                                                                                                         |  |

| Power Supply for CPU board   | DC +7.5 Volt. to +9.0 Volt. supplied from external input                                                                                                                                                                                                      |  |

| Environmental                | <ul> <li>Operating Temperature: 10 °C to 35 °C</li> <li>Humidity: 30% to 85% RH</li> <li>No condensation and corrosive gas</li> </ul>                                                                                                                         |  |

NOTE: \*1 Current microcomputer mounted operates at 5.0 Volts only.

\*2 For H8S/2264F microcomputer only

### Section 2. Installation

### 2.1. Label of Parts on CPU Board

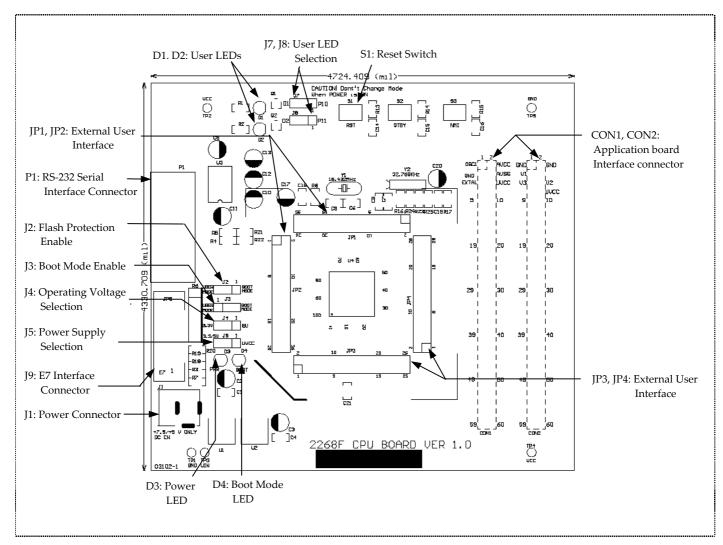

Figure 2.1 shows the name of each part of the CPUBD.

Figure 2.1 Names of Parts on CPU Board

### 2.2. Installing the CPU Board

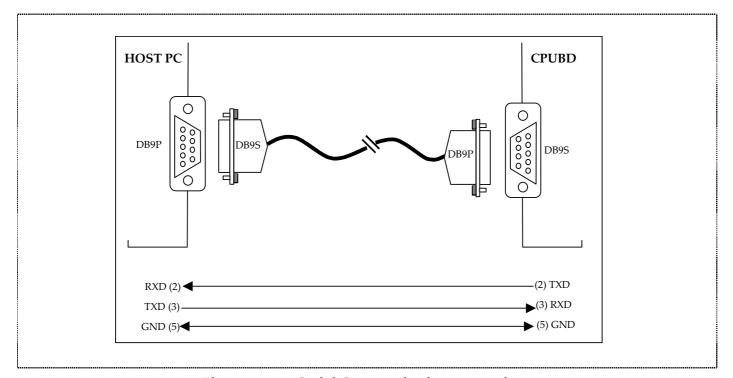

Installing the CPUBD requires power and serial connection to a host computer. The serial communication cable for connecting the CPUBD to a host computer is supplied. The serial connection cable uses a 1:1 connectivity.

The diagram below shows how to connect the CPUBD to a host machine or notebook computer equipped with a DB-9P connector.

Figure 2.2 Serial Communication connections

### 2.3. Communication Port Baud Rate

The baud rate utilized by the CPUBD is FIXED at 115,200bps.

### 2.4. Power Supply for CPU Board

The CPUBD requires a D.C. power supply from +7.5 VDC  $\sim$  +9 VDC at approximately 100mA supplied to the J1 connector. Prepare the D.C. power supply separately. The power cable is included with this product. Since total power consumption can vary widely due to external connections, use a power supply capable of providing at least 250mA at +7.5 VDC  $\pm$  5%.

Two regulators, 3.3 and 5.0 Volts, are used to step down the input voltage. This is to cater for 2 different operating voltages (3.3V and 5.0 V) of the microcomputer. The current CPU board uses the 5.0V MCU.

When power is supplied to the CPUBD, a PWR LED, D3 is lit; otherwise, check the power connection for polarity reversal.

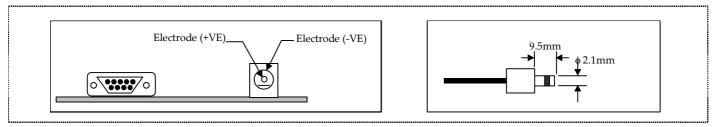

Figure 2.3 shows the specification of the power connector and the DC plug respectively.

Figure 2.3 Power Connector & DC Plug

### 2.5. Jumpers Options

The CPUBD has several jumpers to allow various settings for the user:

| Jumper Designator | Jumper Name   | Jumper Descriptions                                                |  |

|-------------------|---------------|--------------------------------------------------------------------|--|

| J2                | FWE SEL       | Select either to enable or disable FWE                             |  |

| Ј3                | BOOT MODE SEL | Select either BOOT or USER mode                                    |  |

| J4                | 3.3 / 5V SEL  | Select either +3.3V or +5.0V depending on operating voltage of MCU |  |

| J5                | VCC SEL       | Select source of power supply                                      |  |

| J7                | LED SEL       | Select either to use D1 or P10                                     |  |

| Ј8                |               | Select either to use D2 or P11                                     |  |

Table 2.1 List of Jumpers

Please refer to Figure 2.1 for the locations of the jumpers.

### 2.5.1. Voltage Regulator Selection

The CPUBD caters for operation of either 3.3V or 5.0V. The table below shows how to select the required operating voltage.

| CPUBD<br>Operating<br>Voltage | Jumper<br>Name | Jumper<br>Designator | Jumper Selection                  | Descriptions                                 |

|-------------------------------|----------------|----------------------|-----------------------------------|----------------------------------------------|

| 3.3 Volts.                    | 3.3V           | J4                   | Short Pin 2 to Pin 3              | Power from output of 3.3 V voltage regulator |

| 5.0 Volts.                    | 5V             |                      | Short Pin 1 to Pin 2<br>[Default] | Power from output of 5.0 V voltage regulator |

Table 2.2 Operating Voltage Selection Jumpers for MCU

### 2.5.2. Power Supply Selection Jumpers for MCU

This is the jumper switch to select the source of power supply to the MCU. As shown in Table 2.1 below, any setting not listed in Table 2.2 is not allowed.

| Connect to<br>Application<br>Board | Jumper<br>Name | Jumper<br>Designator | Jumper Selection                                             | Descriptions                                                                                 |

|------------------------------------|----------------|----------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Not<br>Connected                   | 3.3V/5V        | J5                   | Short Pin 2 to Pin 3 [Default] [Do not short Pin 1 to Pin 2] | Power of MCU is supplied from the CPUBD.  Verify the operating voltage selected in Table 2.1 |

| Connected                          | UVCC           |                      | Short Pin 1 to Pin 2 [Do not short Pin 2 to Pin 3]           | Power of MCU is supplied from application board                                              |

Table 2.3 Power Supply Selection Jumpers for MCU

### 2.5.3. User Program Mode [Standalone] Selection Jumpers [Default]

This is the jumper switch to place the CPUBD into the user program mode for standalone operation. This is necessary for flashing of the user software into the FLASH ROM of the MCU.

| Jumper Designator | Jumper Selection     | Descriptions                                           |

|-------------------|----------------------|--------------------------------------------------------|

| J2                | Short Pin 1 to Pin 2 | Enable FWE                                             |

| Ј3                | Short Pin 2 to Pin 3 | To place CPUBD into User Program mode<br>[Normal mode] |

| J5                | Short Pin 2 to Pin 3 | Power of MCU is supplied from the CPUBD                |

| J7                | Short Pin 1 to Pin 2 | User LEDs D1 and D2 are used                           |

| J8                | Short Pin 1 to Pin 2 |                                                        |

Table 2.4 User Program Mode [Standalone] Selection Jumpers [Default]

### 2.5.4. Boot Mode Selection Jumpers

This is the jumper switch to place the CPUBD into the boot mode. This is necessary for flashing the kernel software and monitor software into the FLASH ROM of the MCU.

| Jumper Designator | Connection | Jumper Selection               | Descriptions                  |

|-------------------|------------|--------------------------------|-------------------------------|

| J2                | FWE        | Short Pin 1 to Pin 2 [Default] | Enable FWE                    |

| J3                | MD1        | Short Pin 1 to Pin 2           | To place CPUBD into Boot mode |

Table 2.5 Boot Mode Selection Jumpers

### 2.5.5. Flash Write Enable

FWE (Flash Write Enable) provides hardware protection for flash programming (writing) and erasing. When enabled (FWE pin pulled HIGH), hardware protection is disabled, enabling programming and erasing of flash memory.

When disabled (FWE pin pulled LOW), it prevents accidental flash programming and erasing, hereby protecting the user's program.

| Jumper Designator | Jumper Selection     | Descriptions                                                            |

|-------------------|----------------------|-------------------------------------------------------------------------|

| J2                | Short Pin 1 to Pin 2 | Enable FWE to allow Flash Programming & Erasing operation               |

|                   | Short Pin 2 to Pin 3 | Disable FWE to prevent accidental Flash Programming & Erasing operation |

Table 2.6 Flash Write Enable Jumpers

NOTE: FWE must always be enabled to allow Flash Programming & Erasing operation during debugging.

### 2.5.6. User LED Selection

This jumper switch enables the use of the two user LEDs, D1 and D2, connected to P10 and P11 respectively. By disabling the connection to the LEDs, the user is able to make use of these IO port pins.

| Jumper Designator | Jumper Selection     | Descriptions           |

|-------------------|----------------------|------------------------|

| J7                | Short Pin 1 to Pin 2 | Enable D1              |

|                   | Short Pin 2 to Pin 3 | Disable D1, enable P10 |

| J8                | Short Pin 1 to Pin 2 | Enable D2              |

|                   | Short Pin 2 to Pin 3 | Disable D1, enable P11 |

Table 2.7 LED Selection Jumpers

### 2.6. Installation of HEW (Pure Debugger) for CPU Board

To install the HEW (Pure Debugger) for CPUBD from the installation disk, proceed as follows:

- ☐ Insert the HEW (Pure Debugger) for CPUBD installation CD.

- ☐ Run Windows if it is not already running.

- ☐ Close all other applications that are running.

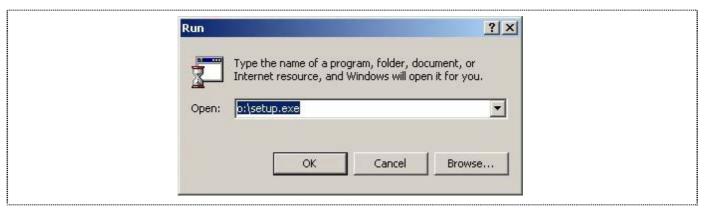

- ☐ Choose *Run* from the Program Manager File menu.

- ☐ Type *Setup* and click OK:

Figure 2.4 Run Dialogue Box

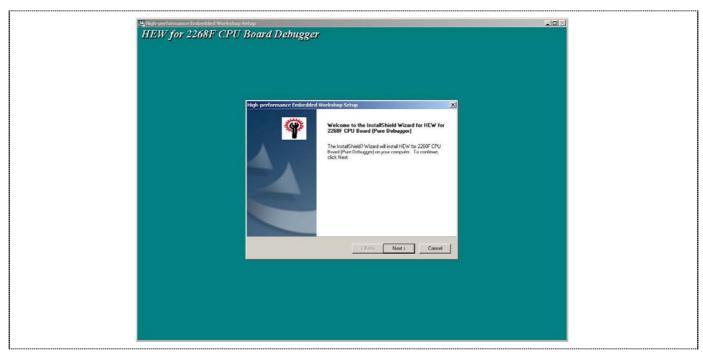

This runs the HEW (Pure Debugger) for CPUBD installer, and the following Welcome! Screen is displayed:

Figure 2.5 HEW for CPUBD Installer Welcome! Screen

☐ Click *Next* to proceed with the installation.

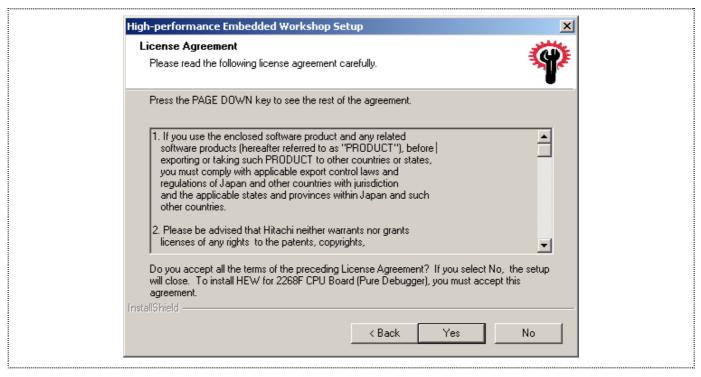

☐ Check the *License Agreement* concerning installation and then click *Yes* to proceed.

Figure 2.6 License Agreement Dialogue Box

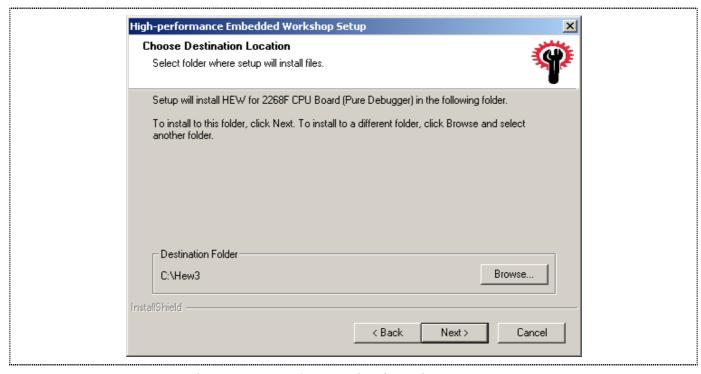

The following dialogue box enables the selection of directory in which user can install the HEW (Pure Debugger) for CPUBD.

Figure 2.7 Select Destination Directory Screen

□ Click *Next* to install into the default directory *C*:\*HEW3*, or specify an alternative directory by clicking on Browse-button.

#### NOTE:

- 1. User may install this HEW debugger in the same directory as the previously setup HEW toolchain (Make sure both are in the same version).

- 2. User may install the debugger into another directory, and register this component into the other HEW tool administration menu.

- 3. Do not install a HEW toolchain over (in the same directory) the HEW debugger

- 4. A new Toolchain can be installed if it is installed to another directory (different from the toolchain directory) and register either component to the respective HEW tool administration menu.

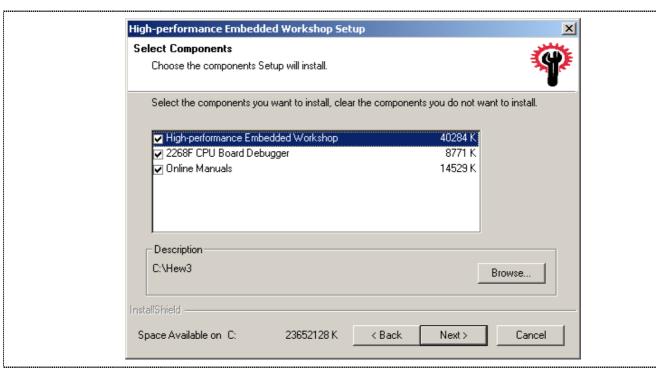

Figure 2.8 Select Components

- ☐ Select the components to be installed.

- ☐ Ensure each selection is selected in turn to confirm the correct directory it is installing into.

If user chooses *Next*, the following dialogue box will confirm each installation directory you selected. Always ensure that all components are installed in the same required directory.

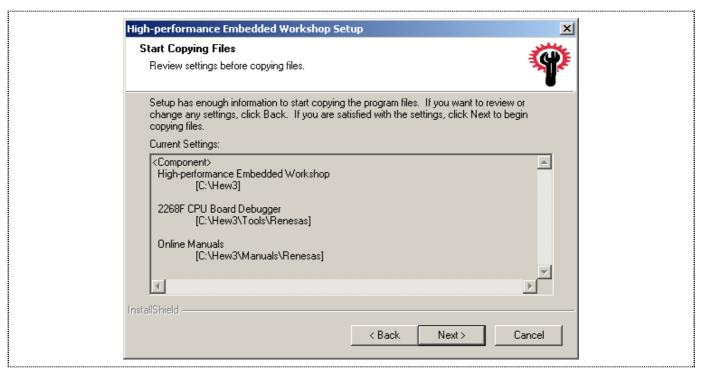

Figure 2.9 Directory Confirmation Screen

☐ Click *Next* to begin installation.

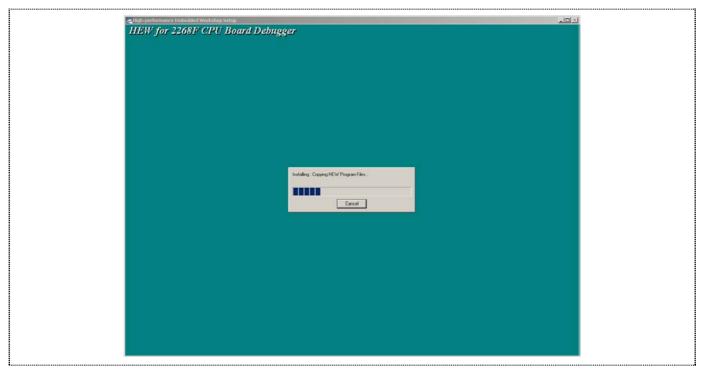

The installer then copies the HEW (Pure Debugger) for CPUBD files to the specified directory:

Figure 2.10 Installing Screen

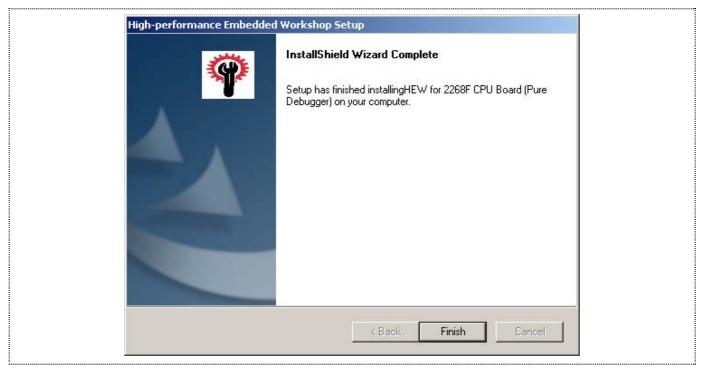

The installation will complete with the Completion screen:

Figure 2.11 Completion Screen

At the end of the installation, icons for HEW (Pure Debugger) CPUBD will be created into the *Start Menu* and ready for execution.

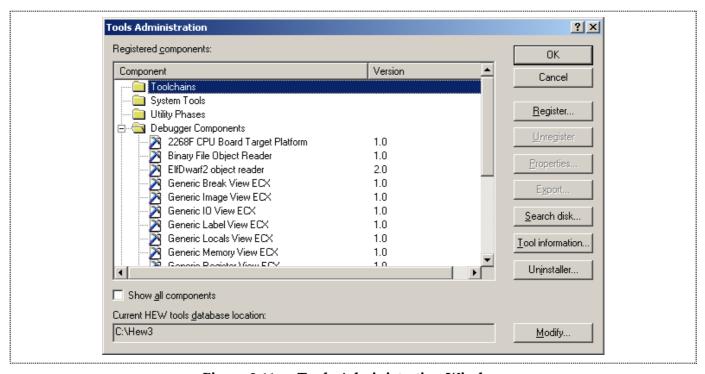

### 2.7. Registering Toolchains

The HEW (Pure Debugger) for the 2268F CPU Board does not come with any free toolchain. If the user has previously installed other versions of HEW with toolchains, these toolchains can be registered and used on the current installed version. Toolchain is a HEW component that enables the user to create, compile and like a project.

- ☐ Click on *Administration* in the *Tools* menu.

- ☐ Click on the (+) to expand the tree to view the detail components.

Figure 2.11 Tools Administration Window

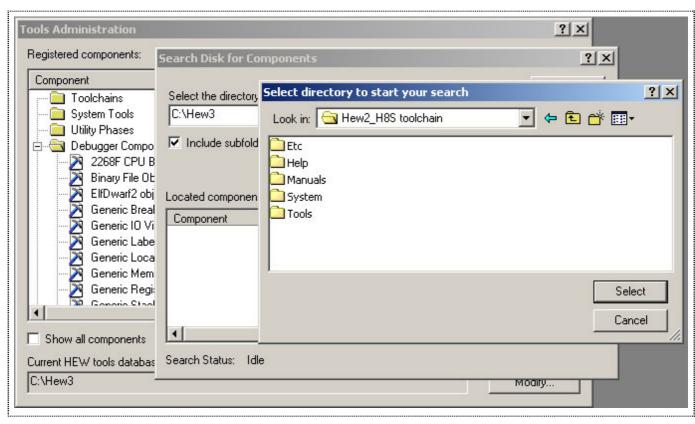

- ☐ Click on Search disk...

- ☐ Click on Browse and select the location of the previous version of HEW.

Figure 2.12 Locating Previous Versions of HEW

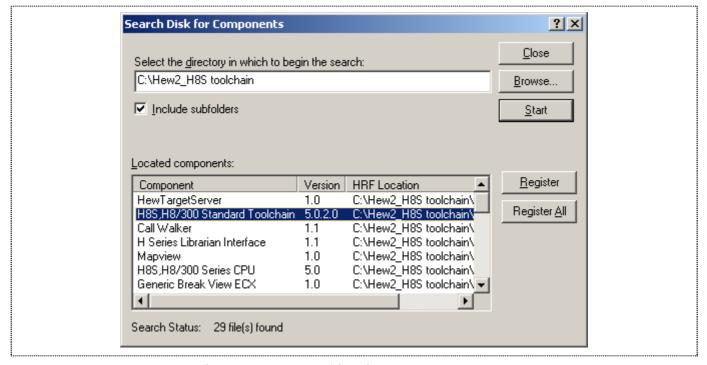

- ☐ Click on Start to start searching for components in the selected directory.

- ☐ Select the required toolchain and click Register.

Figure 2.13 Searching for HEW Components

☐ Click OK to exit the Tools Administration window. The toolchain is now installed.

## Section 3. Setup of HEW (Pure Debugger) for CPU Board

In this section, the focus is to highlight the basic steps for any initial setup for a project. On subsequent HEW activation, user will just be required to select the desired workspace/session, and the setup will be done automatically.

Ensure that the CPUBD is linked up i.e. the serial cable is linked between the CPUBD and PC, and the CPUBD is powered up.

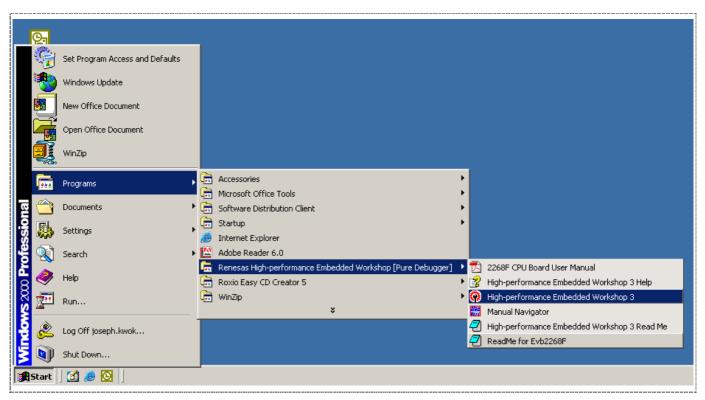

### 3.1. Running HEW (Pure Debugger) for CPU Board

☐ Execute HEW (Pure Debugger) for CPUBD by selecting HEW.

Figure 3.1 HEW (Pure Debugger) for CPUBD Icon

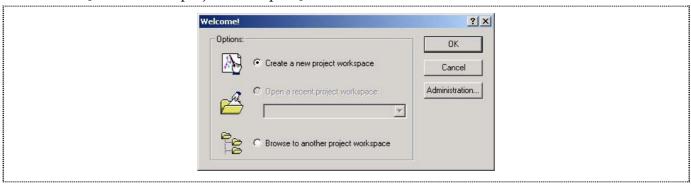

## 3.2. Creating a New Workspace

This step is to create a workspace, to inform the HEW environment, what type of tool is to be used. This will enable user to have the same setup (workspace) at the following activation of the tool.

Since it is possible that user do not have any installed toolchain, there will be two different possibilities when the workspace is being set up.

NOTE: Toolchain is a HEW component that enables the user to create, compile and link a project.

#### 3.2.1. Without Toolchain

If no toolchain is installed, the linkage between the emulator and the HEW debugger is still possible.

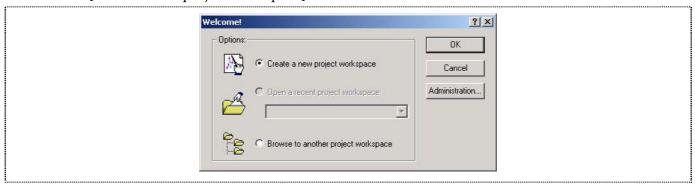

☐ Click on [Create a new project workspace]

Figure 3.2 Select Platform Dialogue Box

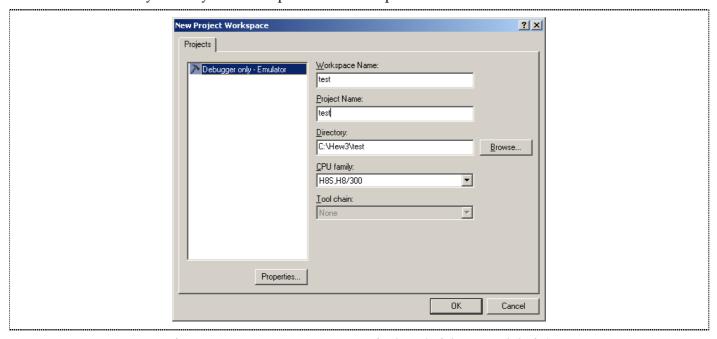

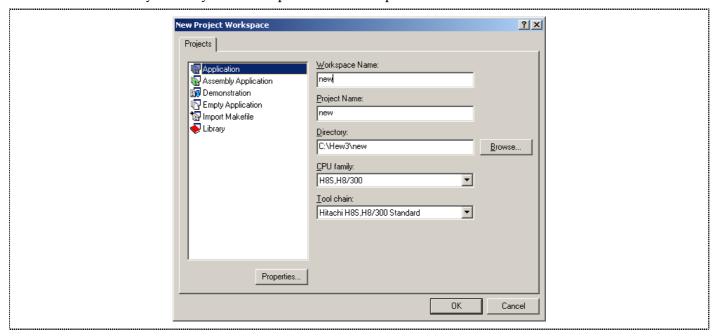

☐ Select a directory and key the workspace name as required

Figure 3.3 HEW Start-Up Window (without toolchain)

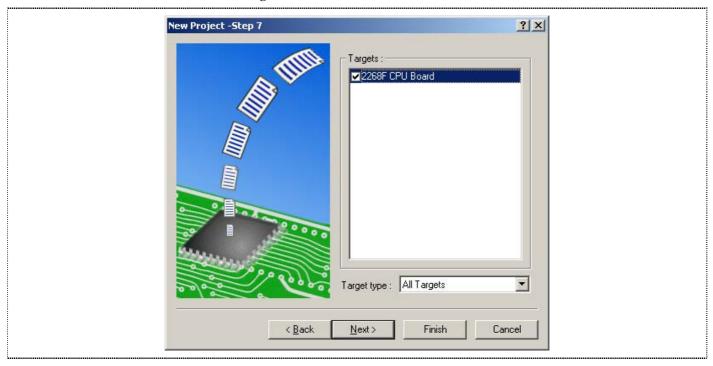

☐ Select 2268F CPU Board as the target

Figure 3.4 Select Target

### ☐ Click on [Next>] button

Figure 3.5 Debugger Configuration

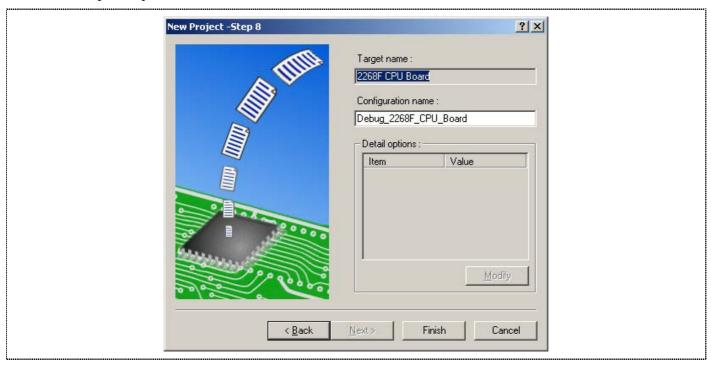

☐ Click on [Finish] button

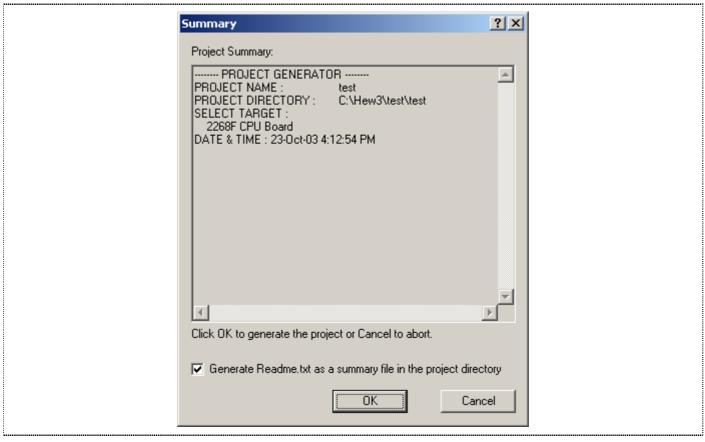

Figure 3.6 Debugger Setting Summary Window

- ☐ A summary window shows the project files that will be generated

- ☐ Click OK to proceed

Refer to Section 3.3 to proceed with the HEW setup.

#### 3.2.2. With Toolchain

When a toolchain is registered (refer to Section 2.7 for registering toolchains), user is able to create and compile codes. Creating and compiling of codes is detailed in the HEW user manual.

☐ Click on [Create a new project workspace]

Figure 3.7 Select Platform Dialogue Box

☐ Select a directory and key the workspace name as required

Figure 3.8 HEW Start-Up Window (without toolchain)

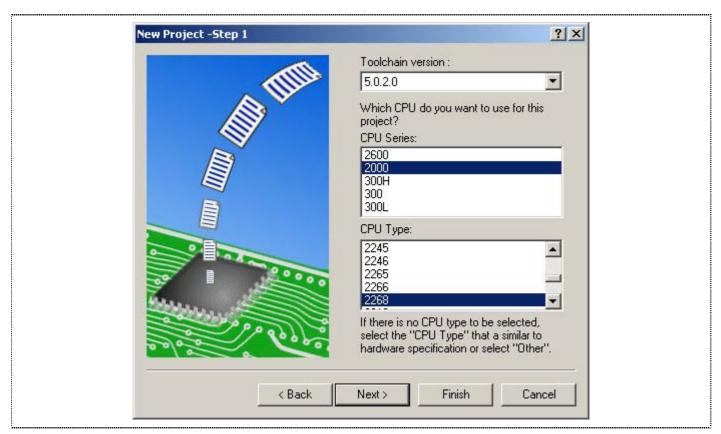

☐ Select 2268F CPU Board as the target by selecting

o CPU Series: 2000 o CPU Type: 2268

Figure 3.9 Select Target

- ☐ Complete the workspace setup by clicking on [Finish] button

- ☐ A summary window will pop up, showing the project files that will be generated

- ☐ Click OK to proceed

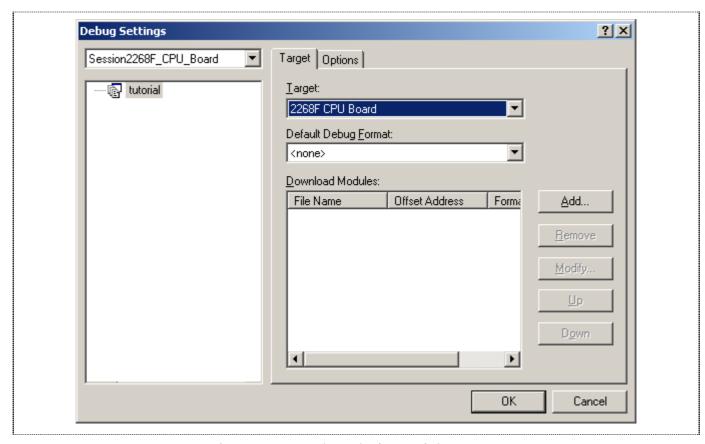

## 3.3. Selecting the Target (Debug Settings)

HEW (Pure Debugger) for CPUBD can be extended to support multiple target emulators or platforms (if the system is setup for more than one platform), user will have to choose a platform for the session from *Debug Settings...* in the *Options* menu.

Figure 3.10 Select Platform Dialogue Box

- ☐ Select '2268F CPU Board' and click OK to continue

- ☐ A warning message will pop up. Click "OK" to proceed

NOTE: User can change the target platform at any time by choosing *Debug Settings...* from the *Options* menu. Under the *Download Modules*, User can also define the Download Module/s for Debugging.

When the emulator has been successfully setup, the HEW (Pure Debugger) for CPUBD desktop window will be displayed. A message *Connected* is displayed in the Output Window.

# **Section 4. Performing Emulation**

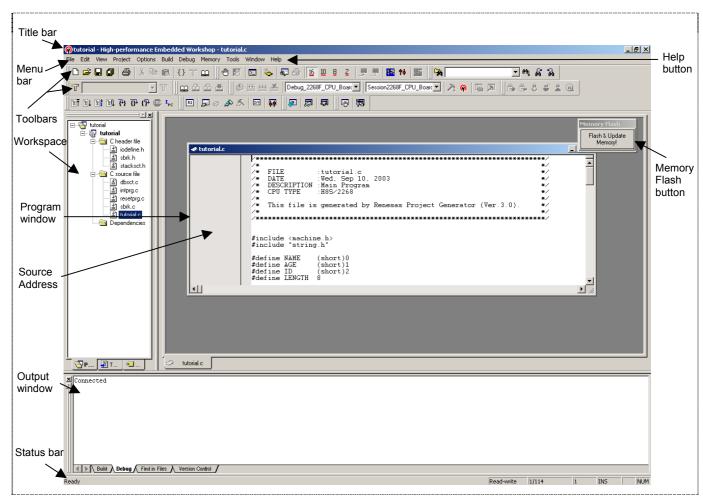

## 4.1. High-performance Embedded Workshop

The following shows a snap shot of the HEW (Pure Debugger) desktop Window:

Figure 4.1 High-Performance Embedded Workshop Window

The key features of HEW (Pure Debugger) for CPUBD are described in the following sections:

**Title Bar** : Displays the name of the currently open workspace, project and file.

Menu Bar : Give you access to the HEW (Pure Debugger) for CPUBD debugging

commands for controlling CPUBD.

**Toolbars** : Provides convenient buttons as shortcuts for the most frequently used menu

commands. The tool bar can be docked or floated. It can be created, modified and

removed.

Program Window : Displays the source code of the program being debugged as well as the

source address.

Workspace : Display the detail of current workspace, and provide a quick & easy mean of

navigation.

Output Window : Displays the various outputs from HEW. For example, build details, results

of find files.

Status Bar : Displays the status of the CPUBD. For example, progress information about

downloads.

Help Button : Activates context sensitive help about any feature of the HEW (Pure

Debugger) for CPUBD software.

**Memory Flash**

**Button**

: Flash contents of the memory window for on-chip ROM area into the MCU.

User is required to press this button when he/she manually updates the contents of the memory window for on-chip ROM\* area. This is not

required for RAM\* area.

NOTE: \* Please refer to the *Appendix B – H8/2268F Memory Map* for the on-chip ROM and RAM areas.

The major topics are highlighted as follows.

|   | Menu   | General Description | Sub Menu                 | Usage                                      |  |  |  |

|---|--------|---------------------|--------------------------|--------------------------------------------|--|--|--|

| 1 | Option | Emulation Setting   | Debug Settings           | Target Selection                           |  |  |  |

|   |        |                     | Emulator                 | View memory mapping and Configure Platform |  |  |  |

|   |        |                     |                          |                                            |  |  |  |

| 2 | View   | MCU related         | Disassembly              | View disassembly window                    |  |  |  |

|   |        | information         | CPU                      | Register, memory, Status, I/O              |  |  |  |

|   |        |                     | Symbol                   | Label                                      |  |  |  |

|   |        |                     | Code                     | Breakpoints                                |  |  |  |

|   |        |                     |                          |                                            |  |  |  |

| 3 | Memory | MCU memeory         | Fill                     |                                            |  |  |  |

|   |        | manipulation        | Refresh                  |                                            |  |  |  |

|   |        |                     |                          |                                            |  |  |  |

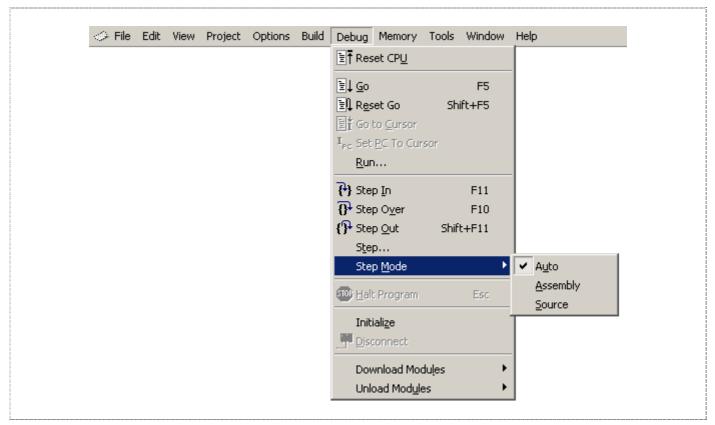

| 4 | Debug  | Execution of MCU    | Reset CPU                |                                            |  |  |  |

|   |        | Code                | Go/Reset Go /Go to       |                                            |  |  |  |

|   |        |                     | Cursor/ Set PC to Cursor |                                            |  |  |  |

|   |        |                     | /Run                     |                                            |  |  |  |

|   |        |                     | Step In/ Over/ Out/      |                                            |  |  |  |

|   |        |                     | Step mode                |                                            |  |  |  |

|   |        |                     | Initialize               |                                            |  |  |  |

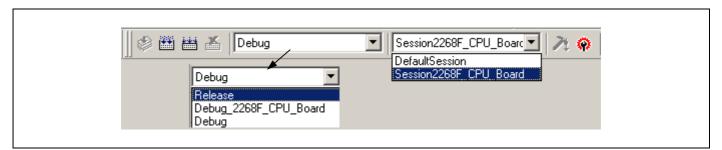

## 4.2. Compiler Configuration & Debugger Session

In HEW compiler, every setting is stored in a configuration. The configurations available when a toolchain is registered are different to that when a toolchain is not available.

Session is not directly related to a configuration. This means that multiple sessions can share the same download module and avoid unnecessary program rebuilds.

Users can create new configuration & session under the [Options\Build Configuration...] and [Options\Debug Session...] pull down menu respectively.

#### 4.2.1. Session Without Toolchain

At the HEW (Pure Debugger) environment without any toolchain, a default debugger **Session**, [Session2268F\_CPU\_Board] is created to store information of

- Target platform

- Downloadable program

- Window positioning

- Registers value settings

The default configuration created is [Debug\_2268F\_CPU\_Board].

Figure 4.2 Toolbar Showing the Session and Configuration without Toolchain

#### 4.2.2. Session With Toolchain

At the HEW (Pure Debugger) environment with a toolchain, a default debugger **Session**, [Session2268F\_CPU\_Board] is created to store information of

- Target platform

- Downloadable program

- Window positioning

- Registers value settings

Figure 4.3 Toolbar Showing the Sessions and Configurations with a Toolchain

Generally, the HEW organized the configuration & session of a workspace as follows

| Root Directory | Workspace directory Files                          | <b>Configuration directory Files</b>         |

|----------------|----------------------------------------------------|----------------------------------------------|

| (xxx.hws)      |                                                    |                                              |

| ( )            | Debug (DIR)                                        | Configuration Information & Output (abs,lst) |

|                | Release (DIR)                                      | Configuration Information & Output (abs,lst) |

|                | Debug_2268F_CPU_Board (DIR)                        | Configuration Information & Output (abs,lst) |

|                | Session2268F_CPU_Board (hsf)  DefaultSession (hsf) |                                              |

|                | C & header files                                   |                                              |

#### **Example of usage:**

User may use [Session2268F\_CPU\_Board] to link to CPUBD, & [Debug] configuration setting to debug on the project output file (xxx.abs) store in the Debug sub directory. User may switch the configuration to [Release] and debug on the new setting (e.g optimization on...).

On the other hand, user may switch the session to [DefaultSession], which may be set to link to a simulator. At this session, user may switch the configuration from [Release] to [Debug], so as to debug on the generated output (xxx.abs) in the simulator environment.

NOTE: The path name defined in the [Options\Debug Setting..] must be relative [\$(CONFIGDIR)\\$(PROJECTNAME).abs]. Otherwise, when the session is switch, the download module will not be able to switch correctly.

## 4.3. Debug Settings

The Debug Settings in [Options\Debug Settings...] is to set the environment for a session.

In HEW Pure Debugger without toolchain, users have been provided with the session

- Session2268F\_CPU\_Board

Whereas, in HEW Pure Debugger with a toolchain, users have been provided with two sessions

- Session2268F\_CPU\_Board

- DefaultSession

In each session, users are to set

- Target (2268F, Simulator...)

- Default Debug Format (Elf\Dwaf2, S-record, IntelHex...)

- Download module (\$(CONFIGDIR)\\$(PROJECTNAME).abs)

In each session, users can set a list of command chain to be executed at the [option] tab.

- At connecting the emulator

- Immediately before downloading

- Immediately after downloading

## 4.4. Connecting & Disconnecting with the Emulator

The open (activation) or close (exit) of the HEW and/or workspace will determine the emulator and HEW connectivity.

The alternative method is to use the "session" control:

In HEW (Pure Debugger) environment with a toolchain, user is provided with two sessions

- Session2268F\_CPU\_Board (linking with emulator)

- DefaultSession (no target)

Thus by switching between the sessions, the emulator can be connected & disconnected from the HEW.

## 4.5. Emulator Setting

The emulator setting, which consists of the system configuration & memory mapping, has to done before any emulation.

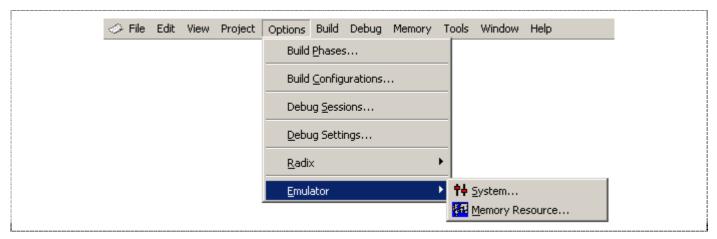

Figure 4.4 Option - Emulator

### 4.5.1. Configure Platform

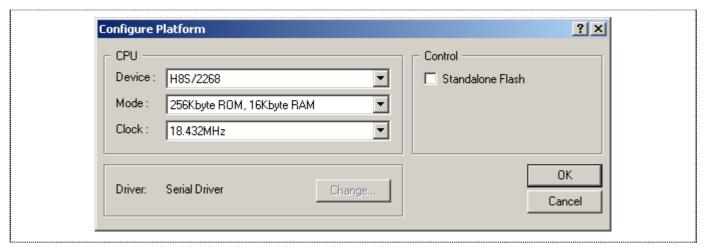

The configure platform enables the user to set their target device and mode at startup.

To setup the system configuration:

☐ From the *Options* menu, choose *Emulator*, *System*... or click on the following icon on the Toolbar:

☐ The following Configure Platform dialogue will appear:

Figure 4.5 Target Configuration Dialogue Box

The user has the option of using standalone flashing by enabling the Standalone Flash in the Control option.

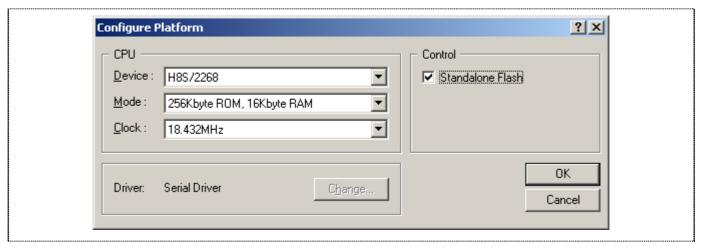

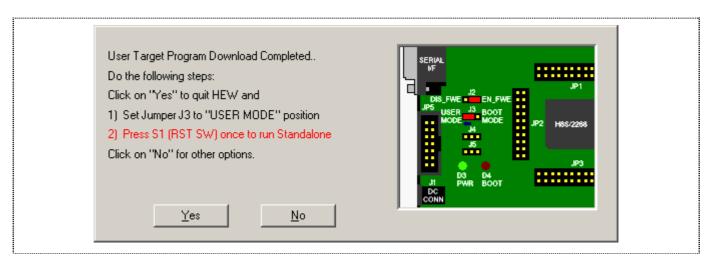

#### 4.5.1.1. Standalone Flash

Standalone Flashing downloads the user target program directly into the memory. Monitor program would not reside in the memory and hence no debugging is available if this option is used. This option should only be used when the user has finalized his/her user target program and wants to run it on the CPU Board.

Figure 4.6 Enabling Standalone Flash option

☐ Click on the check box and click OK to enable standalone flashing.

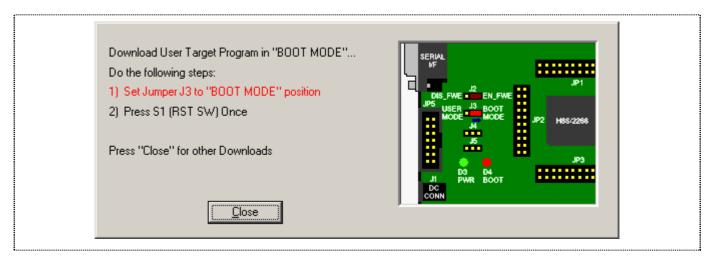

When user downloads the selected object file, the following dialogue box would appear, prompting the user to switch to Boot Mode to download the user target program.

Figure 4.7 Dialogue box for downloading user target program

After downloading the user target program, the dialogue box would prompt the user to switch to User Program Mode to run the user target program. The user can either click YES to exit HEW or click NO to re-download the user target program or Flash monitor Program.

Figure 4.8 Dialogue box for running user target program

NOTE: After pressing the reset switch when jumper J3 is in the User Mode position, the user target program will run in standalone mode, that is, no connection to HEW is required to run the user target program, no debugging is available to user.

Having successfully downloaded the user target program, user can disable FWE to enable Flash Program/ Erase Protection by switching jumper J2 to *DIS\_FWE* position, so as to prevent accidental flashing or erasing of the user target program.

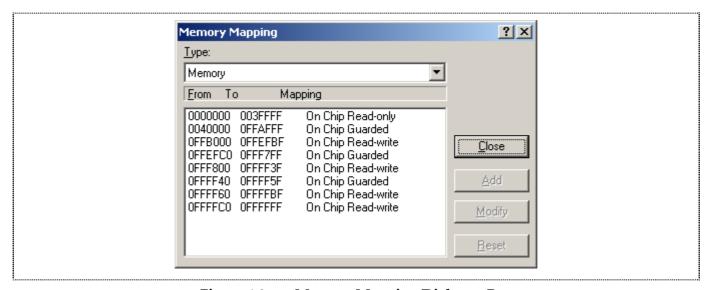

## 4.5.2. Memory Mapping

Once the device and operating mode are selected, the default memory mapping will be set. The main objective of memory mapping is to ensure that the emulator has the correct internal memory (Internal ROM, RAM, IO) access.

To display the current memory mapping:

☐ From the *Options* menu, choose *Emulator*, *Memory resource*... or click the Open memory mapping button in the toolbar:

The memory mapping is shown in the following figure:

Figure 4.9 Memory Mapping Dialogue Box

Alternatively, the CPU memory map can be viewed from the status window:

☐ From the *View* menu, choose *CPU* then *Status*, or click the View Status button in the toolbar:

☐ Select the Memory tab in Status window to show the Memory Mapping configured:

Figure 4.10 Target Memory Configuration Dialogue

NOTE: CPUBD Memory Map is for display and information purpose, user cannot configure it.

The following explains the target memory configuration dialogue:

CPU Memory Map : Display the memory configuration of the specific target

device selected.

Program Name : Display the Downloaded Module's name (User Target

Program) and the memory space that it has occupied

## 4.6. Viewing of Program

Programs can be viewed as

- Source Code level (C or assembly-language)

- Disassembly level (assembly-language)

#### 4.6.1. Source Code level

Users may double-click on the file located in the workspace window to open and view the source code. However this is merely in "editor" point of view. Users have to download the code to the emulator. Once the code is downloaded, user can observe that "address values" have appeared in the source address column of the source file.

#### NOTE:

When a break condition occurred during a running program, HEW will open up the source code or disassembly window.

- 1. If the source code information is not available, the disassembly window will be opened.

- 2. If the downloaded project is a Elf/Dwarf2-based file, and the project has been moved from its original path, the source file may not be automatically found. In this case, HEW will open a source file browser dialogue box to allow user to manually locate the file.

```

🐠 tutorial.c

_ 🗆 🗵

main()

0x00000834

count = 0;

for ( ; ; ){

0x00000840

0x0000086c

0x00000844

sort(section1, NAME);

0 \times 0 0 0 0 0 0 84 a

count++:

0 \times 000000850

sort(section1, AGE);

0x00000858

count++;

sort(section1, ID);

0x0000085e

0x00000866

count++;

void sort(list, key)

struct namelist list[];

short key;

0x0000086e

0x0000087a

short i,j,k;

```

Figure 4.11 Source Level

Information available:

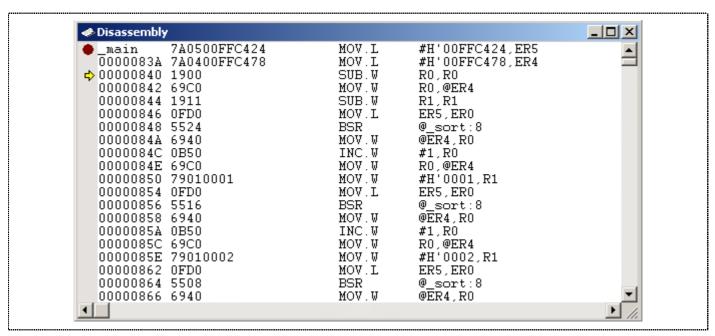

### 4.6.2. Disassembly level

User can open the disassembly window:

☐ Choose *Disassembly* from the *View* Menu, or right click on the source window, and select *Goto Disassembly*

Figure 4.12 Disassembly Window

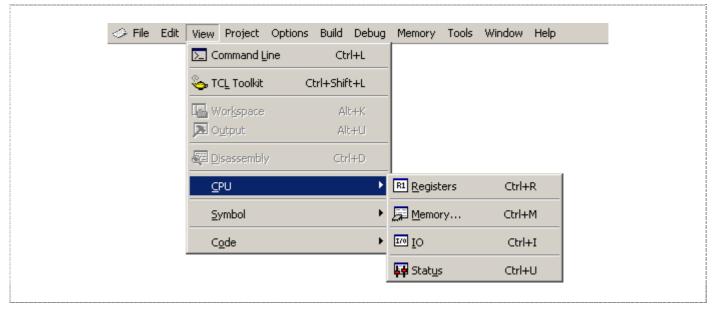

### 4.7. MCU related information

User can be monitor & control the MCU information under the view menu.

Figure 4.13 View - CPU

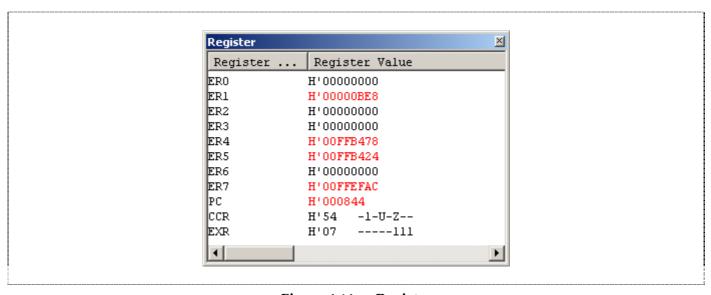

## 4.7.1. Registers

User can access these registers directly through the Register windows during break mode only.

Figure 4.14 Register

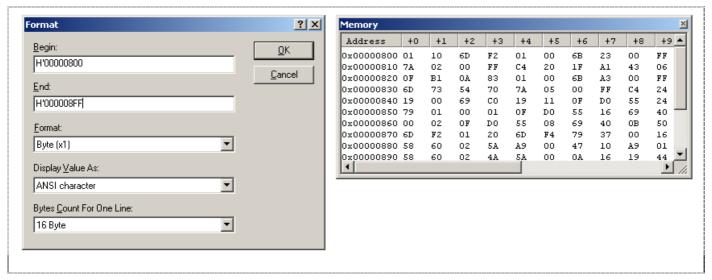

#### **4.7.2. Memory**

Users will have to set a pre-defined address range to be monitored, before user can access the memory through the memory windows. The memory window will not refresh constantly by itself. The access methodology is different when emulation is in different mode (Run or Break). More memory functions are explained in Memory manipulation.

Figure 4.15 Set Memory

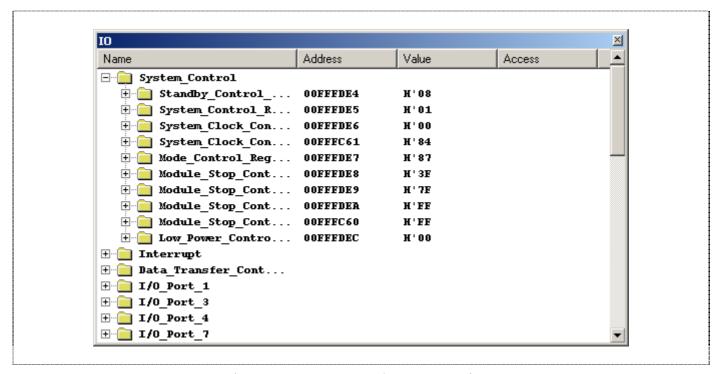

#### 4.7.3. I/O

The IO window provides an easy access to MCU IO registers. The Address & Data values of respective peripherals & MCU control registers are displayed in the IO window.

Figure 4.16 Input and Output Register

#### 4.7.4. Status

The status window uses three different tabs to monitor the emulator setting.

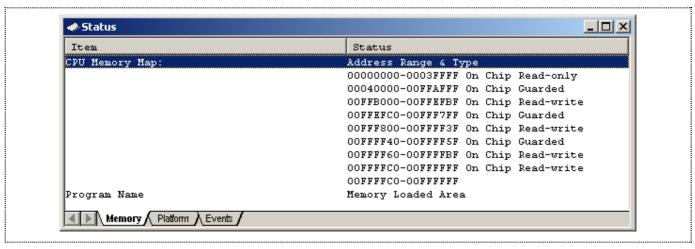

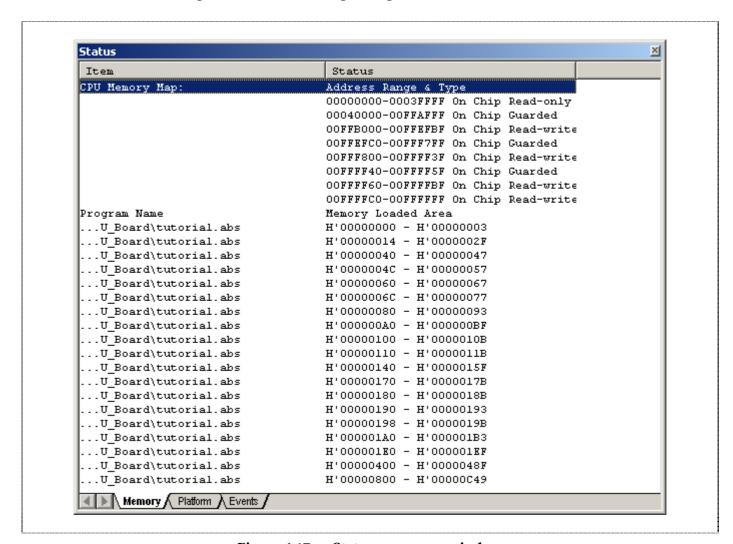

#### 4.7.4.1. Status - Memory

The memory tab display

- the available memory setting for the selected target device & mode.

- the address range where the User Target Program is loaded

Figure 4.17 Status – memory window

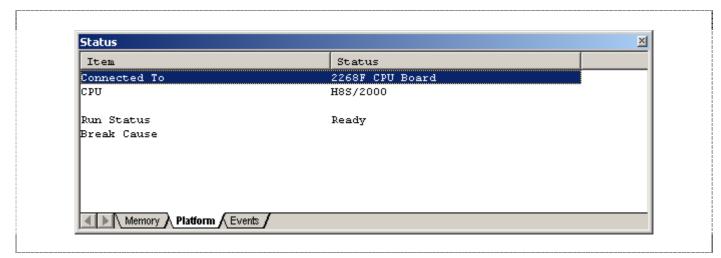

#### 4.7.4.2. Status - Platform

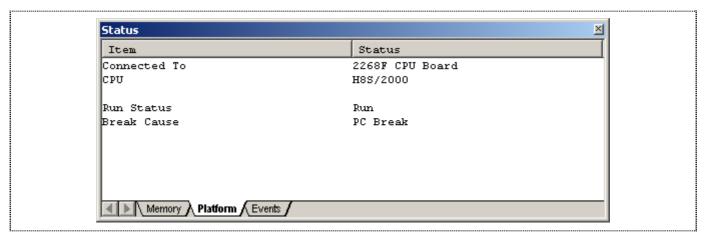

This platform tab shows the current emulation condition

- Target device

- CPU

- Run Status

- Break Cause

Figure 4.18 Status – Platform window

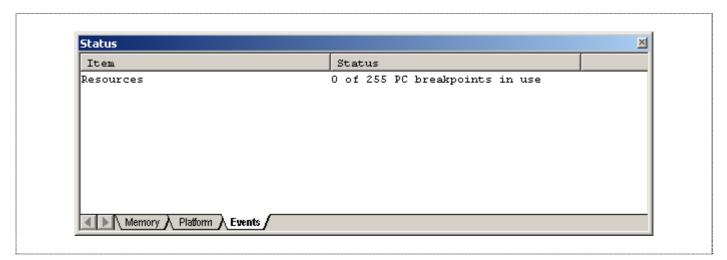

#### **4.7.4.3.** Status - Events

The events tab shows the usage of

- PC Breakpoints

Figure 4.19 Status – Events window

#### 4.7.5. Symbol

This enables easy monitoring of declared variables in the assembly or C files. If debug information is not included, the Watch and Locals sub menus will not appeared.

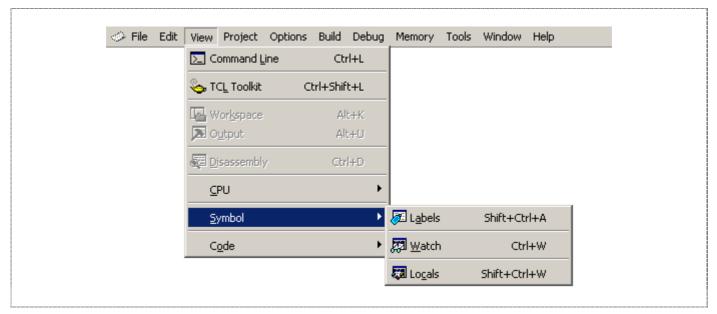

Figure 4.20 View - Symbol

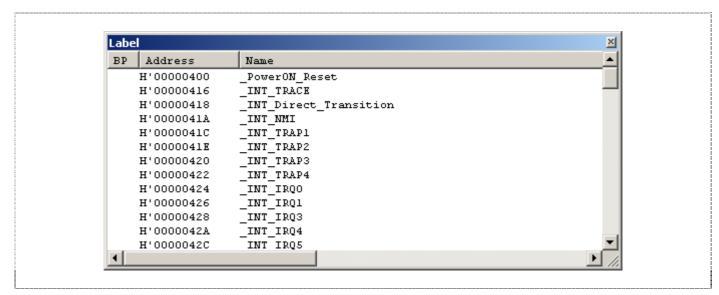

#### 4.7.5.1. Label

When debug information is included, detail of all labels will be displayed in the Label window. User can add new label into the window for simple reference too.

Figure 4.21 Label

NOTE: When a label value matches an operand, the corresponding instruction's operand is replaced by the label. If two or more labels have the same value, the earlier label (alphabetical order) will be displayed.

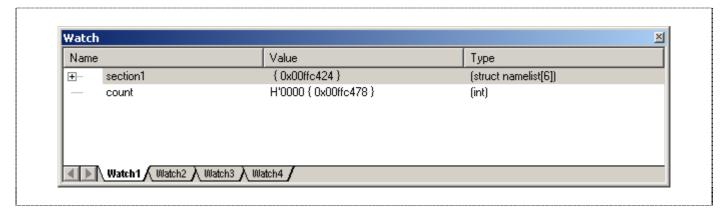

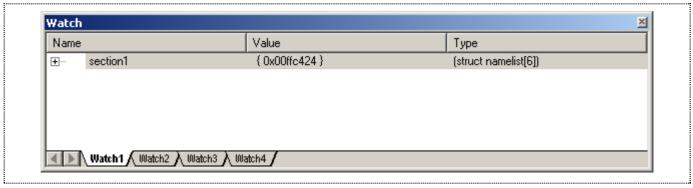

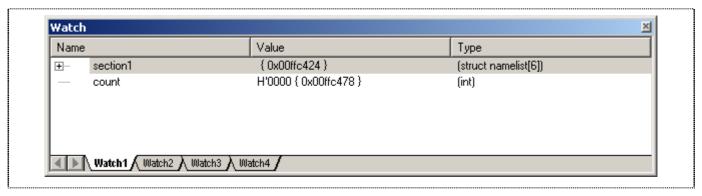

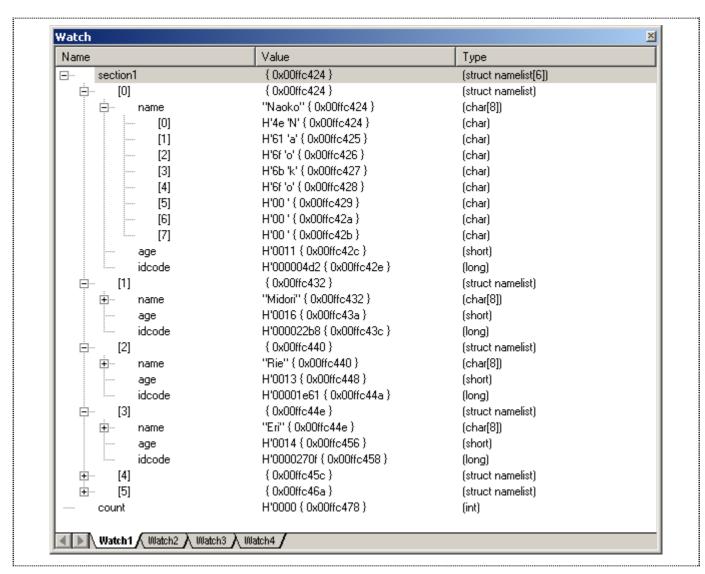

#### 4.7.5.2. Watch

User will have to add the variables into the watch window.

Figure 4.22 Watch

NOTE: The variables can be displayed only if debug information is included in the absolute file (abs)

- The variables have not been excluded after the complier optimization

- The variables are not cleared as macro.

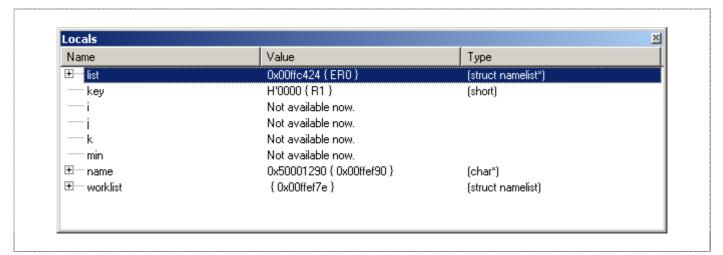

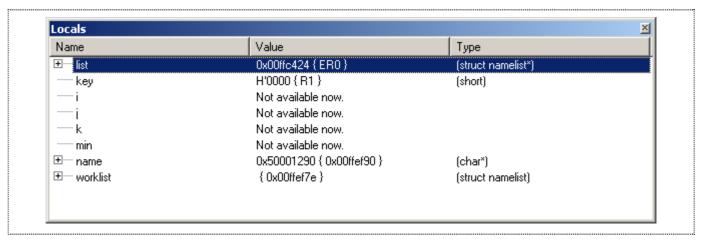

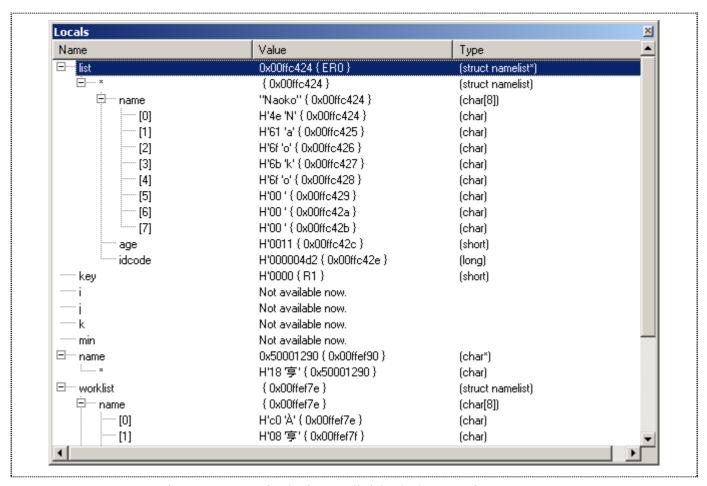

#### 4.7.5.3. Local

The Local variables will appear in the Locals window when user code has break/stop at a sub-routine.

NOTE: Local variables are temporary data stored in stack. Therefore it can only be viewed when execution stops within a routine.

Figure 4.23 Locals

Tooltip watch - place the cursor at the variable and the general information of the variable will appear.

Figure 4.24 Tooltip

#### 4.7.6. Break Functions

Various breakpoints setting are discussed as follows.

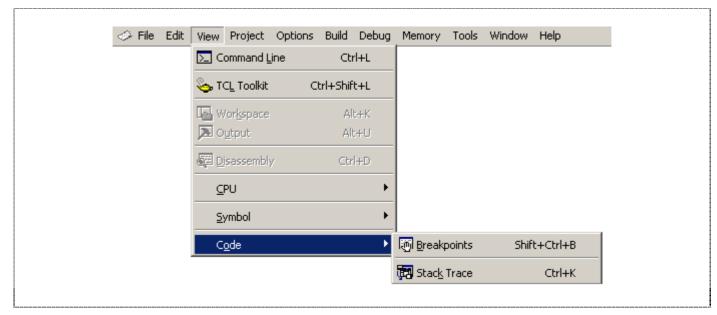

Figure 4.25 View Code

Breaks are events used to intercept the normal program execution when a specific condition is matched. There are two types of break in the 2268F CPU Board, hardware and software break.

For Hardware Event break, the preset break condition will cause the break event to occur after an instruction is executed. For Software PC break, the break condition causes the break event to occur before the break condition.

|   | Types of Break                 | Description                                                                                                                                                                                                                                                                                       |

|---|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | PC Break<br>(Software Break)   | A break occurs at the program address specified by PC Break window. The instruction at this address is replaced with a system instruction before the execution of code. If a PC breakpoint is detected, the emulation stops at the specified address before executing the subsequent instruction. |

| 2 | User Break<br>(Hardware Break) | There are 3 scenarios when a hardware break occurs:  Pressing the ESC key of the host PC  Pressing STOP button of HEW  Pressing reset switch of CPUBD                                                                                                                                             |

**Table 4.1** Types of Breaks Encountered During Emulation

#### 4.7.7. Stack Trace

The Stack Trace window can be selected if only debug information has been supplied. Stack Trace window shows the function call history.

```

◆ StackTrace

_ U X

Kind Name

Value

sort(struct namelist*,short)