## カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# ユーザーズ・マニュアル

# V850ES/KJ1+

# 32**ビ**ット・シングルチップ・マイクロコントローラ ハードウエア編

μPD70F3316 μPD70F3316Y μPD70F3318 μPD70F3318Y

資料番号 U16893JJ3V0UD00 (第3版) 発行年月 May 2006 N CP(K)

## 目次要約

| 第1章         | 概 説 20                                  |

|-------------|-----------------------------------------|

| 第2章         | <b>端子機能</b> 36                          |

| <b>第</b> 3章 | CPU <b>機能</b> 51                        |

| <b>第</b> 4章 | <b>ポート機能</b> 94                         |

| <b>第</b> 5章 | <b>バス制御機能</b> 194                       |

| 第6章         | <b>クロック発生機能</b> 221                     |

| 第7章         | 16 <b>ピット・タイマ/イベント・カウンタ</b> P (TMP) 232 |

| 第8章         | 16 <b>ピット・タイマ/イベント・カウンタ</b> 0 320       |

| 第9章         | 16 <b>ピット・タイマ/イベント・カウンタ</b> 5 399       |

| 第10章        | 8 <b>ピット・タイマ</b> H 418                  |

| 第11章        | インターパル・タイマ , 時計タイマ 441                  |

| 第12章        | ウォッチドッグ・タイマ機能 453                       |

| 第13章        | <b>リアルタイム出力機能(</b> RTO <b>)</b> 463     |

| 第14章        | A/D <b>コンパータ</b> 472                    |

| 第15章        | D/A <b>コンパータ</b> 501                    |

| 第16章        | アシンクロナス・シリアル・インタフェース (UART) 506         |

| 第17章        | クロック同期式シリアル・インタフェース0 (CSIO) 547         |

| 第18章        | 自動送受信機能付きクロック同期式シリアル・インタフェースA(CSIA)     |

|             | 574                                     |

|             | I <sup>2</sup> C <b>バス</b> 609          |

|             | DMA <b>機能(</b> DMA <b>コントローラ)</b> 686   |

|             | <b>割り込み / 例外処理機能</b> 709                |

|             | <b>キー割り込み機能</b> 751                     |

| -           | ス <b>タンバイ機能</b> 753                     |

|             | <b>リセット機能</b> 775                       |

|             | <b>クロック・モニタ</b> 790                     |

|             | <b>低電圧検出回路</b> 800                      |

|             | パワーオン・クリア回路 805                         |

|             | レギュレータ 807                              |

|             | オプション・バイト 809                           |

|             | フラッシュ・メモリ 811                           |

|             | オンチップ・ディバグ機能 835                        |

| -           | <b>電気的特性</b> 844                        |

| -           | 外形図 896                                 |

|             | <b>半田付け推奨条件</b> 897                     |

|             | 開発ツール 898                               |

|             | 命令セット一覧 909                             |

| 付録C         | <b>レジスタ索引</b> 918                       |

**付録**D 改版履歴 ... 929

#### CMOSデバイスの一般的注意事項

#### 入力端子の印加波形

#### 入力ノイズや反射波による波形歪みは誤動作の原因になりますので注意してください。

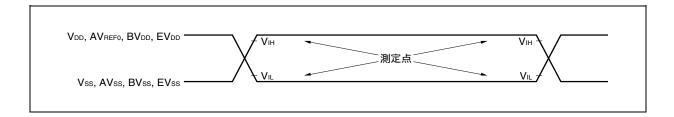

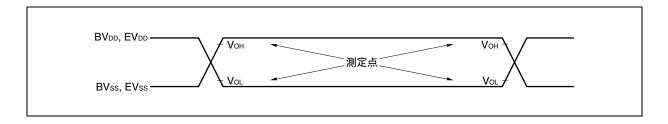

CMOSデバイスの入力がノイズなどに起因して、 $V_L$ (MAX.)から $V_H$ (MIN.)までの領域にとどまるような場合は、誤動作を引き起こす恐れがあります。入力レベルが固定な場合はもちろん、 $V_L$ (MAX.)から $V_H$ (MIN.)までの領域を通過する遷移期間中にチャタリングノイズ等が入らないようご使用ください。

#### 未使用入力の処理

#### CMOSデバイスの未使用端子の入力レベルは固定してください。

未使用端子入力については、CMOSデバイスの入力に何も接続しない状態で動作させるのではなく、プルアップかプルダウンによって入力レベルを固定してください。また、未使用の入出力端子が出力となる可能性(タイミングは規定しません)を考慮すると、個別に抵抗を介してVooまたはGNDに接続することが有効です。

資料中に「未使用端子の処理」について記載のある製品については,その内容を守ってください。

#### 静電気対策

#### MOSデバイス取り扱いの際は静電気防止を心がけてください。

MOSデバイスは強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、当社が出荷梱包に使用している導電性のトレーやマガジン・ケース、または導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。

また、MOSデバイスを実装したボードについても同様の扱いをしてください。

#### 初期化以前の状態

#### 電源投入時, MOSデバイスの初期状態は不定です。

電源投入時の端子の出力状態や入出力設定,レジスタ内容などは保証しておりません。ただし,リセット動作やモード設定で定義している項目については,これらの動作ののちに保証の対象となります。

リセット機能を持つデバイスの電源投入後は、まずリセット動作を実行してください。

#### 電源投入切断順序

内部動作および外部インタフェースで異なる電源を使用するデバイスの場合,原則として内部電源を投入した後に外部電源を投入してください。切断の際には,原則として外部電源を切断した後に内部電源を切断してください。逆の電源投入切断順により,内部素子に過電圧が印加され,誤動作を引き起こしたり,異常電流が流れ内部素子を劣化させたりする場合があります。

資料中に「電源投入切断シーケンス」についての記載のある製品については、その内容を守ってください。

#### 電源OFF時における入力信号

当該デバイスの電源がOFF状態の時に,入力信号や入出力プルアップ電源を入れないでください。 入力信号や入出力プルアップ電源からの電流注入により,誤動作を引き起こしたり,異常電流が流 れ内部素子を劣化させたりする場合があります。

資料中に「電源OFF時における入力信号」についての記載のある製品については、その内容を守ってください。

注意: µ PD70F3316, 70F3316Y, 70F3318, 70F3318Yは, Silicon Storage Technology, Inc.からライセンスを受けたSuperFlash®を使用しています。

EEPROM, IECUBE, MINICUBEは, NECエレクトロニクス株式会社の登録商標です。

Windows, Windows XPおよびWindows NTは,米国Microsoft Corporationの米国およびその他の国における登録商標または商標です。

SuperFlashは、米国Silicon Storage Technology, Inc.の米国,日本などの国における登録商標です。

PC/ATは,米国IBM社の商標です。

SPARCstationは,米国SPARC International, Inc.の商標です。

Solaris, SunOSは,米国サン・マイクロシステムズ社の商標です。

- ◆本資料に記載されている内容は2006年4月現在のもので、今後、予告なく変更することがあります。量 産設計の際には最新の個別データ・シート等をご参照ください。

- 文書による当社の事前の承諾なしに本資料の転載複製を禁じます。当社は,本資料の誤りに関し,一切その責を負いません。

- 当社は,本資料に記載された当社製品の使用に関連し発生した第三者の特許権,著作権その他の知的財産権の侵害等に関し,一切その責を負いません。当社は,本資料に基づき当社または第三者の特許権,著作権その他の知的財産権を何ら許諾するものではありません。

- 本資料に記載された回路, ソフトウエアおよびこれらに関する情報は, 半導体製品の動作例, 応用例を 説明するものです。お客様の機器の設計において, 回路, ソフトウエアおよびこれらに関する情報を使 用する場合には, お客様の責任において行ってください。これらの使用に起因しお客様または第三者に 生じた損害に関し, 当社は, 一切その責を負いません。

- 当社は,当社製品の品質,信頼性の向上に努めておりますが,当社製品の不具合が完全に発生しないことを保証するものではありません。当社製品の不具合により生じた生命,身体および財産に対する損害の危険を最小限度にするために,冗長設計,延焼対策設計,誤動作防止設計等安全設計を行ってください。

- 当社は、当社製品の品質水準を「標準水準」、「特別水準」およびお客様に品質保証プログラムを指定していただく「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。

標準水準:コンピュータ, OA機器, 通信機器, 計測機器, AV機器, 家電, 工作機械, パーソナル機器, 産業用ロボット

特別水準:輸送機器(自動車,電車,船舶等),交通用信号機器,防災・防犯装置,各種安全装置, 生命維持を目的として設計されていない医療機器

特定水準: 航空機器, 航空宇宙機器, 海底中継機器, 原子力制御システム, 生命維持のための医療機器, 生命維持のための装置またはシステム等

当社製品のデータ・シート,データ・ブック等の資料で特に品質水準の表示がない場合は,標準水準製品であることを表します。意図されていない用途で当社製品の使用をお客様が希望する場合には,事前に当社販売窓口までお問い合わせください。

(注)

- (1)本事項において使用されている「当社」とは、NECエレクトロニクス株式会社およびNECエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいう。

- (2)本事項において使用されている「当社製品」とは,(1)において定義された当社の開発,製造製品をいう。

M8E 02.11

#### はじめに

- **対象者** このマニュアルは, V850ES/KJ1+の機能を理解し, それを用いた応用システムを設計するユーザを対象とします。

- **目 的** このマニュアルは,次の構成に示すハードウエア機能をユーザに理解していただくことを目的としています。

- 構 成 V850ES/KJ1+のユーザーズ・マニュアルは,ハードウエア編(このマニュアル)と,アーキテクチャ 編(V850ES ユーザーズ・マニュアル アーキテクチャ編)の2冊に分かれています。

ハードウエア編

アーキテクチャ編

- ・端子機能

- ・CPU機能

- ・内蔵周辺機能

- ・フラッシュ・メモリ・プログラミング

・電気的特性

- ・データ・タイプ

- ・レジスタ・セット

- ・命令形式と命令セット

- ・割り込みと例外

- ・パイプラインの動作

- **読み方** このマニュアルの読者には、電気、論理回路、およびマイクロコンピュータに関する一般知識を必要とします。

レジスタ名がわかっていて、レジスタの詳細を確認するとき

付録A レジスタ索引を利用してください。

命令機能の詳細を理解しようとするとき

別冊のV850ES ユーザーズ・マニュアル アーキテクチャ編を参照してください。

レジスタ・フォーマットの見方

ビット番号を で囲んでいるものは,そのビット名称がデバイス・ファイルで予約語に定義されているものです。

一通りV850ES/KJ1+の機能を理解しようとするとき 目次に従ってお読みください。

V850ES/KJ1+の電気的特性を知りたいとき

第32章 電気的特性を参照してください。

このマニュアルでは,「xxxレジスタのyyyビット」を「xxx.yyyビット」と表記しています。ただし, プログラムにそのまま「xxx.yyy」と記述しても,コンパイラ / アセンブラでは正しく認識できません ので,注意してください。

本文欄外の 印は,本版で改訂された主な箇所を示しています。

この" "をPDF上でコピーして「検索する文字列」に指定することによって,改版箇所を容易に検索できます。

凡 例 データ表記の重み:左が上位桁,右が下位桁

アクティブ・ロウの表記: xxx(端子,信号名称に上線)

メモリ・マップのアドレス:上部-上位,下部-下位

注 :本文中に付けた注の説明

注意:気を付けて読んでいただきたい内容

備考:本文の補足説明

数の表記:2進数 ... xxxxまたはxxxxB

10進数 ... xxxx

16進数 ... xxxxH

2のべき数を示す接頭語(アドレス空間,メモリ容量):

$K( \ddagger \Box ) : 2^{10} = 1024$

M(メガ):2<sup>20</sup> = 1024<sup>2</sup>

G( ギガ $): 2^{30} = 1024^3$

# **関連資料** 関連資料は暫定版の場合がありますが,この資料では「暫定」の表示をしておりません。あらかじめ ご了承ください。

#### V850ES/KJ1+**に関する資料**

| 資料 名                            | 資料番号    |

|---------------------------------|---------|

| V850ES ユーザーズ・マニュアル アーキテクチャ編     | U15943J |

| V850ES/KJ1+ ユーザーズ・マニュアル ハードウエア編 | このマニュアル |

#### 開発ツールに関する資料(ユーザーズ・マニュアル)

| 資料 名                            | 資料番号           |         |

|---------------------------------|----------------|---------|

| QB-V850MINI(オンチップ・デバッグ・エミュレータ   | U17638J        |         |

| QB-V850ESKX1H(インサーキット・エミュレータ)   |                | U17214J |

| CA850 Ver.3.00 Cコンパイラ・パッケージ     | 操作編            | U17293J |

|                                 | C言語編           | U17291J |

|                                 | アセンブリー言語編      | U17292J |

|                                 | リンク・ディレクティブ編   | U17294J |

| PM+ Ver.6.00 プロジェクト・マネージャ       |                | U17178J |

| ID850 Ver.3.00 統合デバッガ           | 操作編            | U17358J |

| ID850QB Ver.3.10 統合デバッガ         | 操作編            | U17435J |

| SM850 Ver.2.50 システム・シミュレータ      | 操作編            | U16218J |

| SM850 Ver.2.00以上 システム・シミュレータ    | 外部部品ユーザ・オープン・イ | U14873J |

|                                 | ンタフェース仕様編      |         |

| RX850 Ver.3.20 リアルタイムOS         | 基礎編            | U13430J |

|                                 | インストレーション編     | U17419J |

|                                 | テクニカル編         | U13431J |

|                                 | タスク・デバッガ編      | U17420J |

| RX850 Pro Ver.3.20 リアルタイムOS     | 基礎編            | U13773J |

|                                 | インストレーション編     | U17421J |

|                                 | テクニカル編         | U13772J |

|                                 | タスク・デバッガ編      | U17422J |

| AZ850 Ver.3.30 システム・パフォーマンス・アナラ | U17423J        |         |

| PG-FP4 フラッシュ・メモリ・プログラマ          |                | U15260J |

# 目 次

| 第1章         | 概 説 20                                                                                              |

|-------------|-----------------------------------------------------------------------------------------------------|

|             | K <b>シリーズの製品展開</b> 20<br>1.1.1 V850ES/Kx1+, V850ES/Kx1の製品展開 20<br>1.1.2 78K0/Kx1+, 78K0/Kx1の製品展開 23 |

| 1. 3        | 特 徵 26<br>応用分野 28                                                                                   |

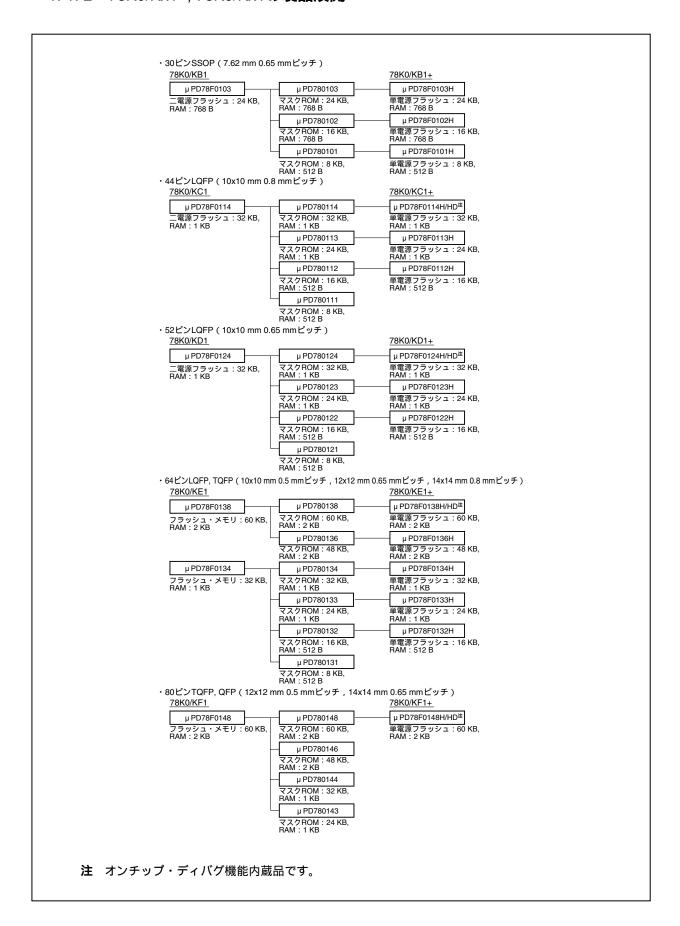

| 1. 5        | オーダ情報 28<br>端子接続図 (Top View) 29                                                                     |

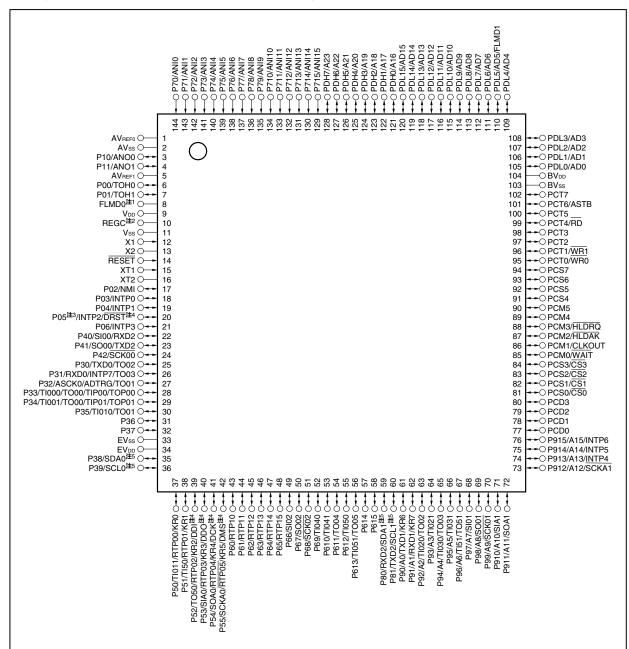

|             | 機 <b>能ブロック構成</b> 31<br>機 <b>能概要</b> 35                                                              |

| 第2章         | <b>端子機能</b> 36                                                                                      |

|             | <b>端子機能一覧</b> 36<br><b>端子状態</b> 45                                                                  |

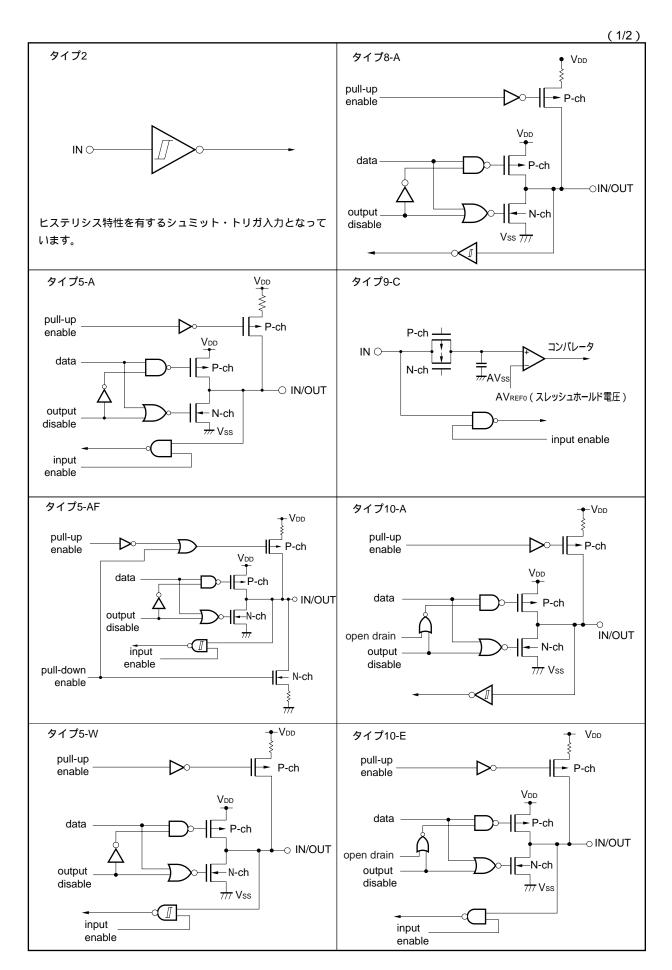

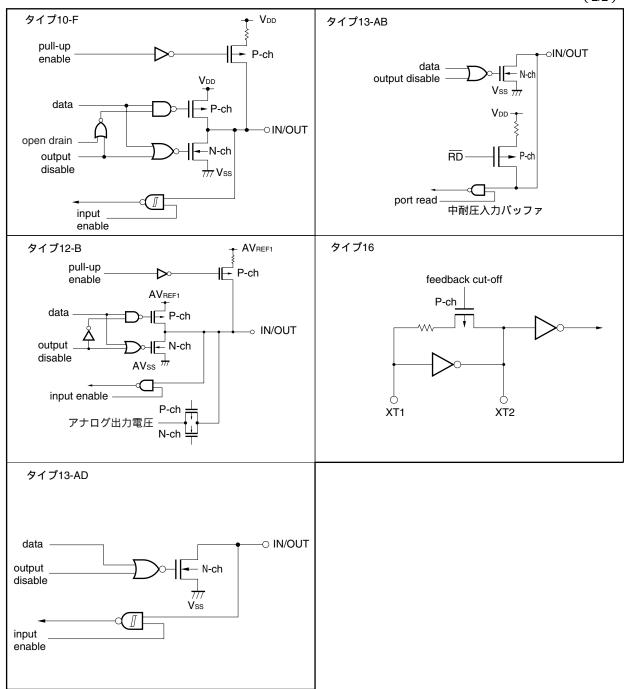

| 2. 3        | 端子の入出力回路タイプと未使用時の処理 46<br>端子の入出力回路 49                                                               |

|             | CPU機能 51                                                                                            |

|             | 特 徵 51                                                                                              |

|             | CPU <b>レジスタ・セット</b> 52<br>3. 2. 1 プログラム・レジスタ・セット 53                                                 |

| 3. 3        | 3. 2. 2 システム・レジスタ・セット 54<br><b>動作モード</b> 60                                                         |

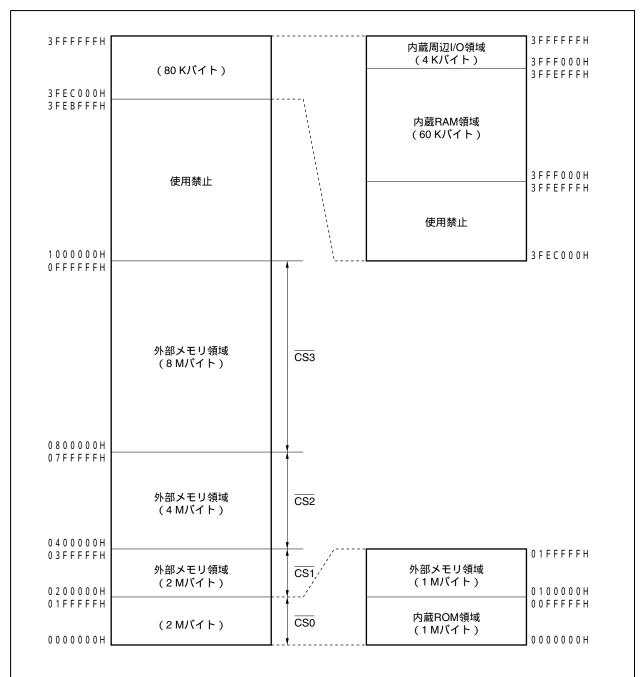

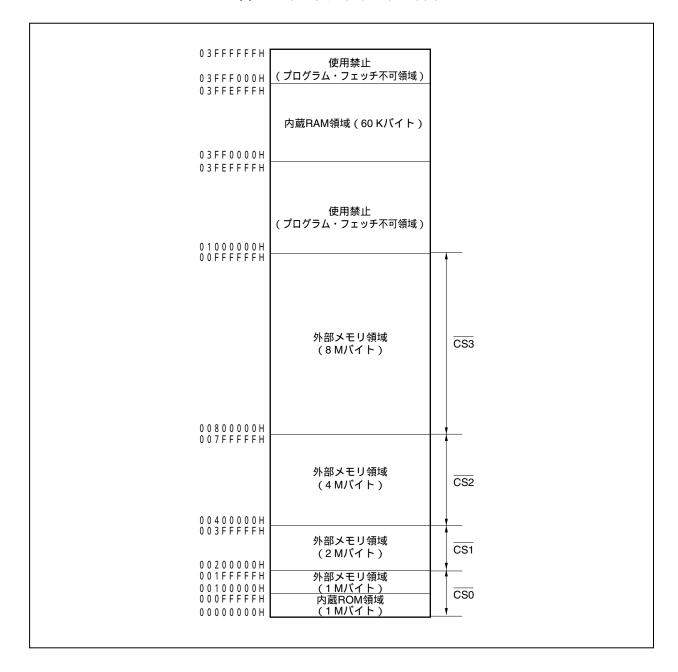

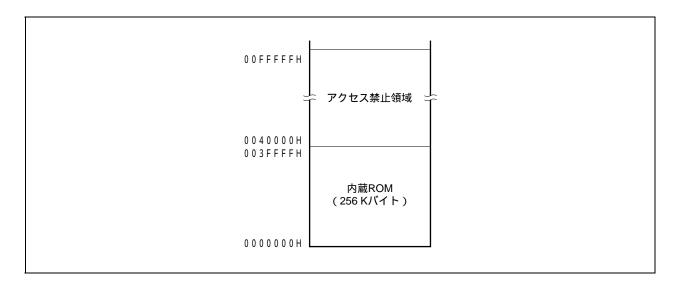

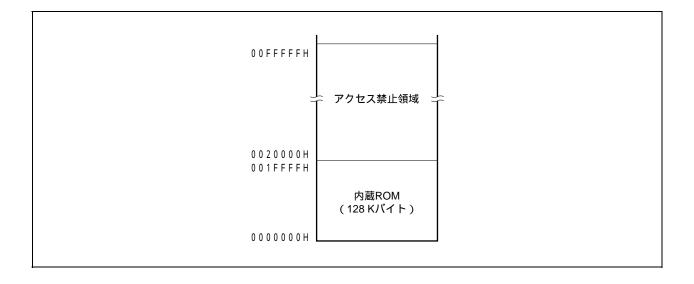

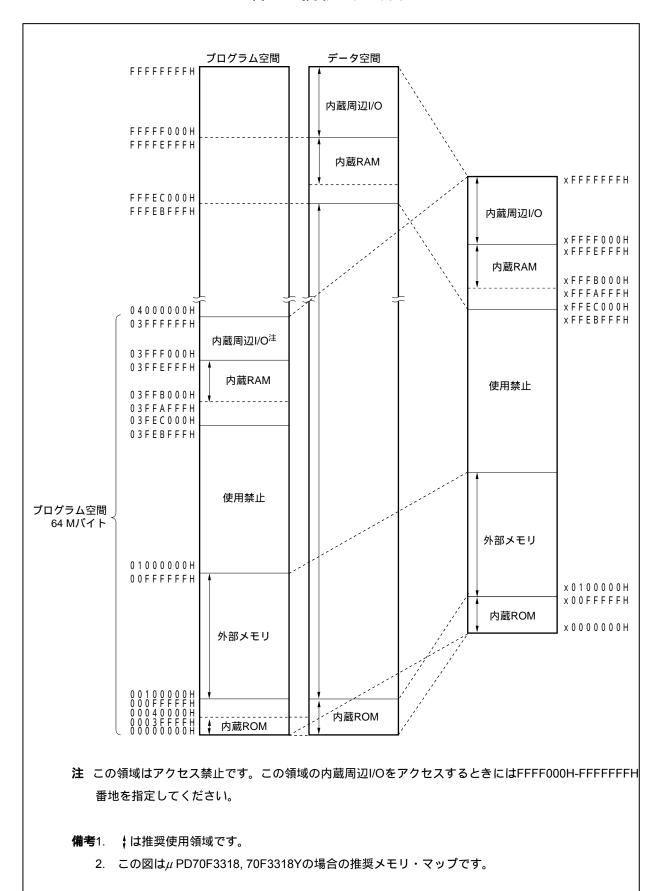

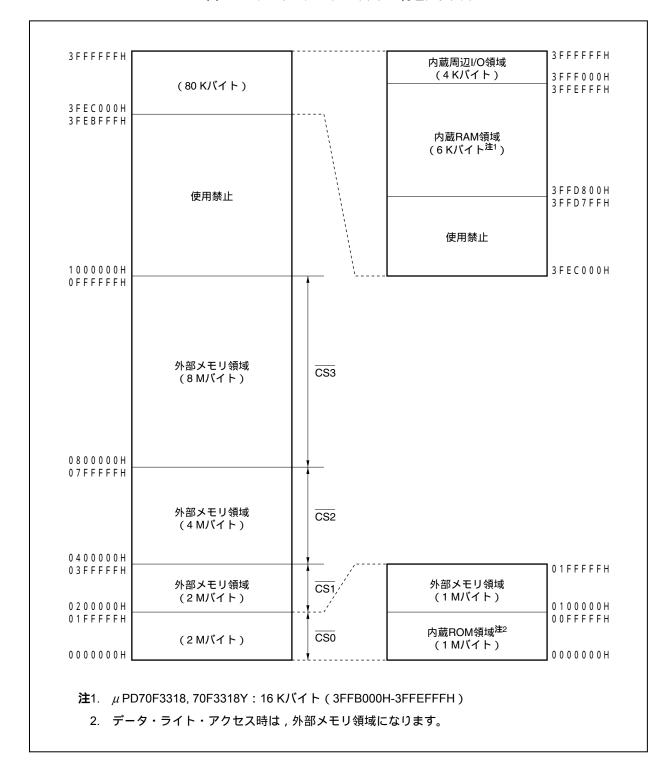

|             | <b>アドレス空間</b> 61<br>3.4.1 CPUアドレス空間 61                                                              |

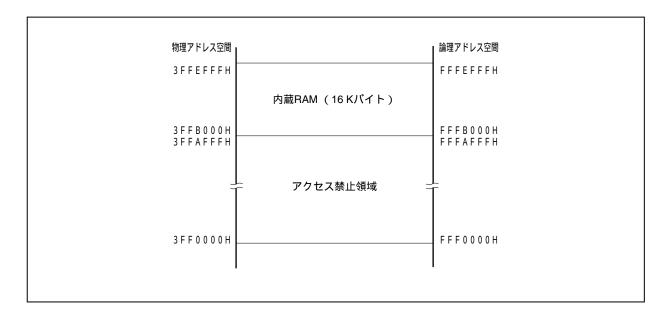

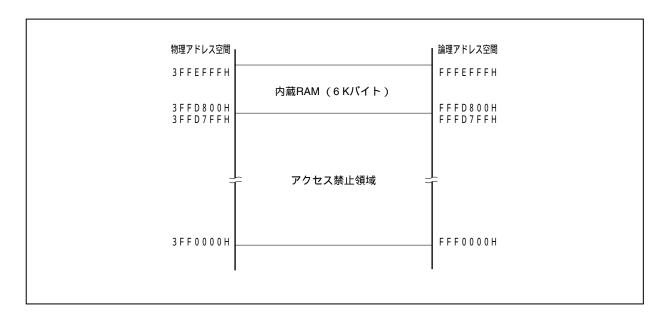

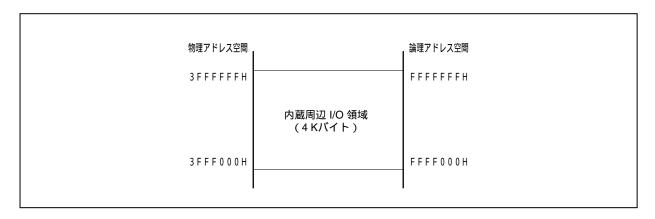

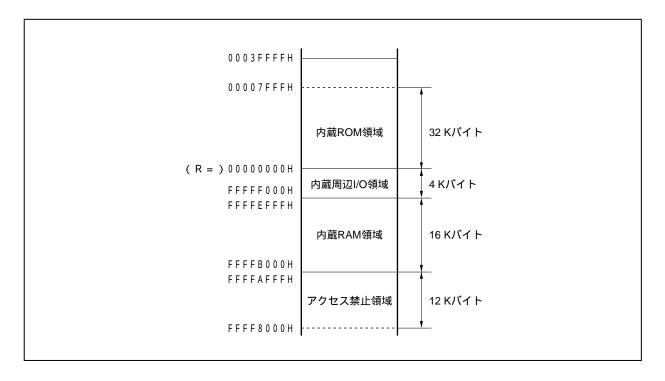

|             | 3. 4. 2 CPUアドレス空間のラップ・アラウンド 62<br>3. 4. 3 メモリ・マップ 63                                                |

|             | 3. 4. 4 領 域 … 65<br>3. 4. 5 アドレス空間の推奨使用方法 … 70                                                      |

|             | 3. 4. 6 周辺I/Oレジスタ 73                                                                                |

|             | 3. 4. 7 特定レジスタ 86<br>3. 4. 8 注意事項 90                                                                |

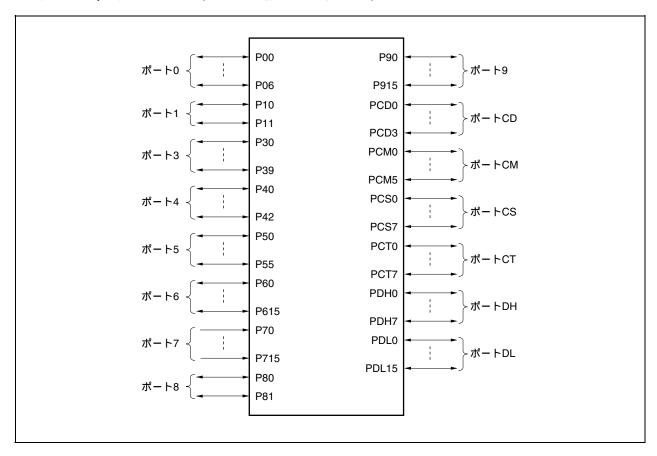

| <b>第</b> 4章 | <b>ポート機能</b> 94                                                                                     |

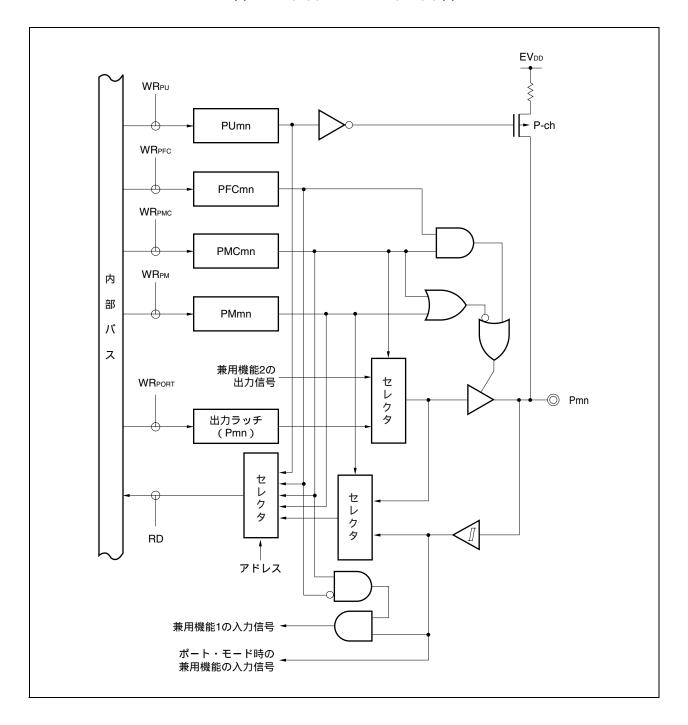

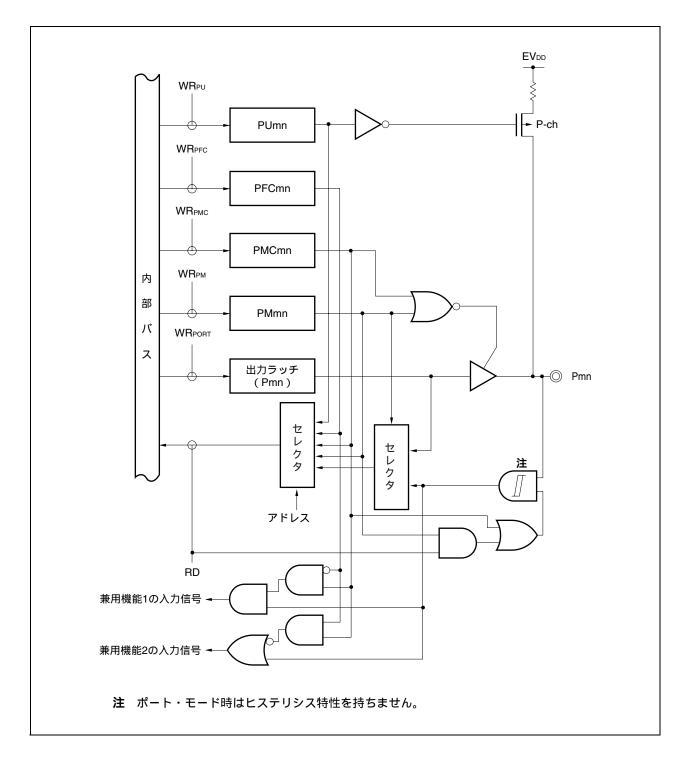

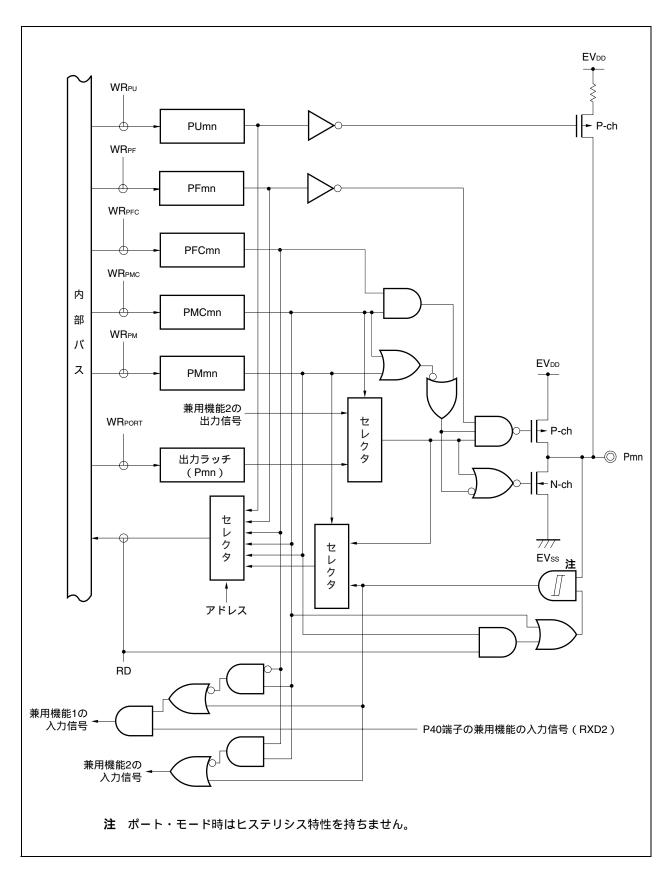

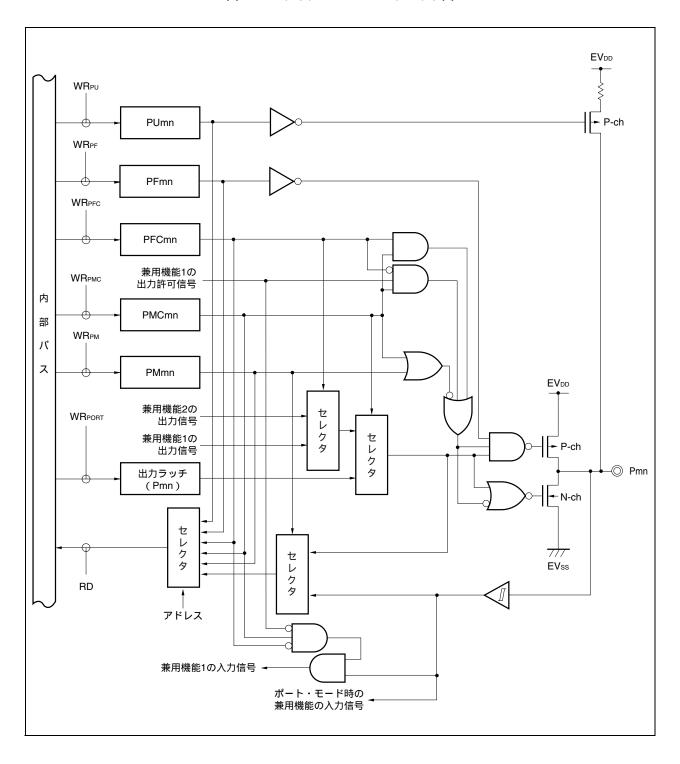

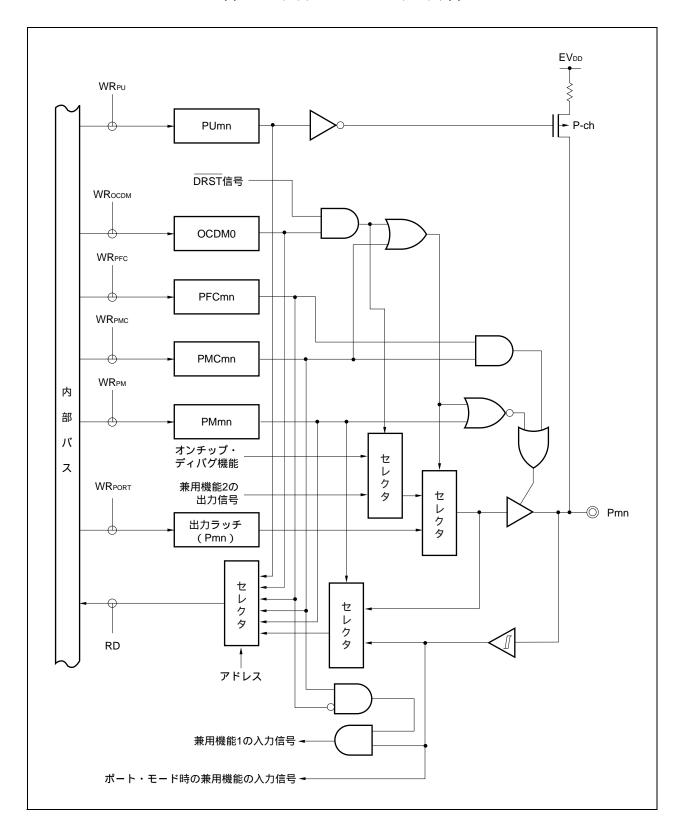

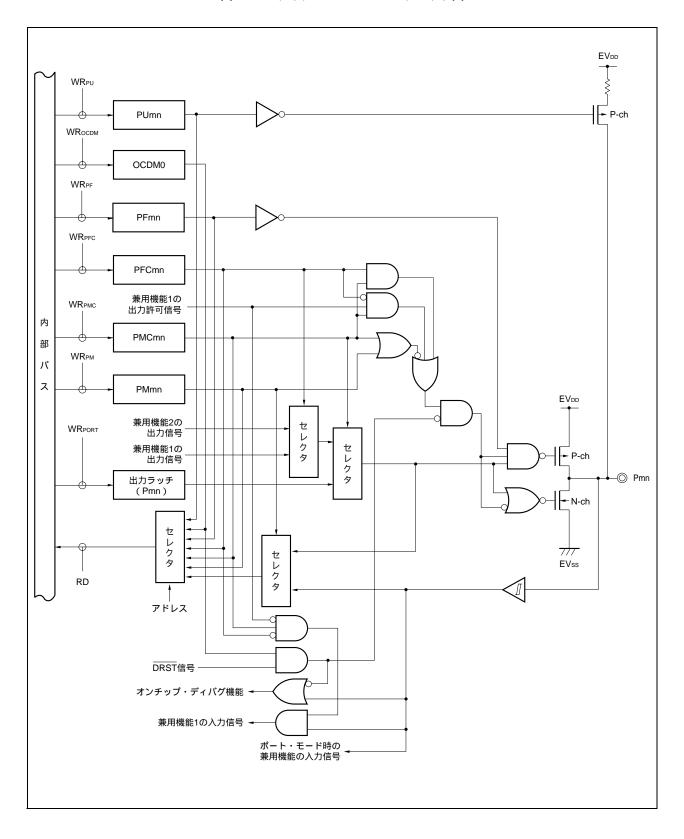

|             | 特 徴 94<br>ポートの基本構成 94                                                                               |

|             | <b>ポートの構成</b> 95                                                                                    |

|             | 4. 3. 1 ポート0 101<br>4. 3. 2 ポート1 104                                                                |

|             | 4.3.3 ポート3 106                                                                                      |

- 4.3.4 ポート4 ... 112 4.3.5 ポート5 ... 115 4.3.6 ポート6 ... 118 4. 3. 7 ポート7 ... 123 4.3.8 ポート8 ... 125 4.3.9 ポート9 ... 128 4. 3. 10 ポートCD ... 135 4.3.11 ポートCM ... 137 4. 3. 12 ポートCS ... 139 4. 3. 13 ポートCT ... 141 4.3.14 ポートDH ... 143 4. 3. 15 ポートDL ... 145

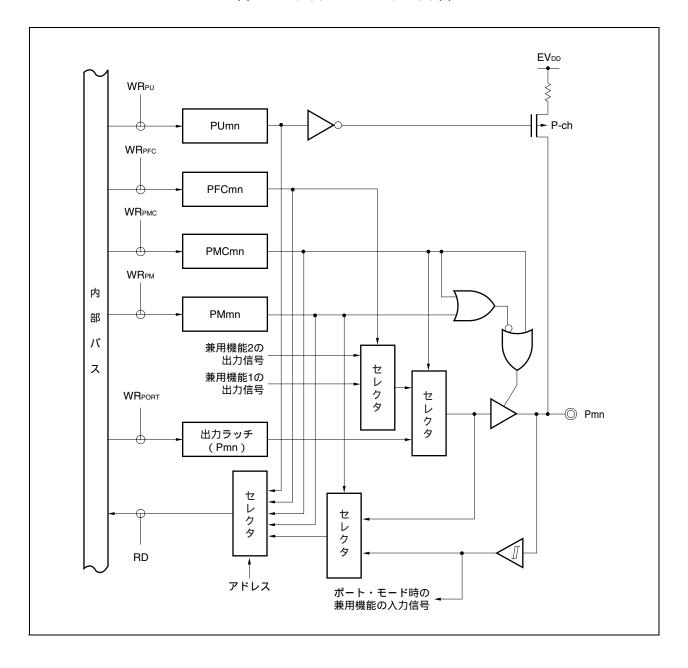

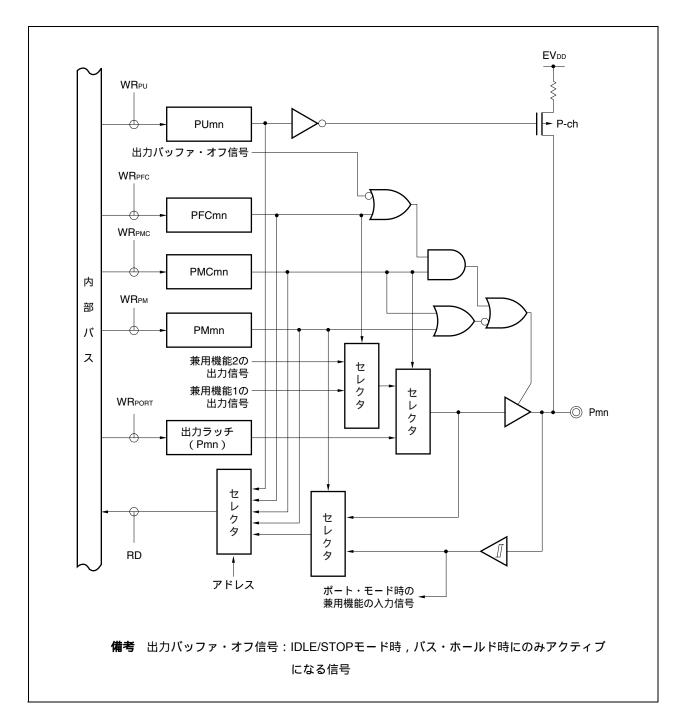

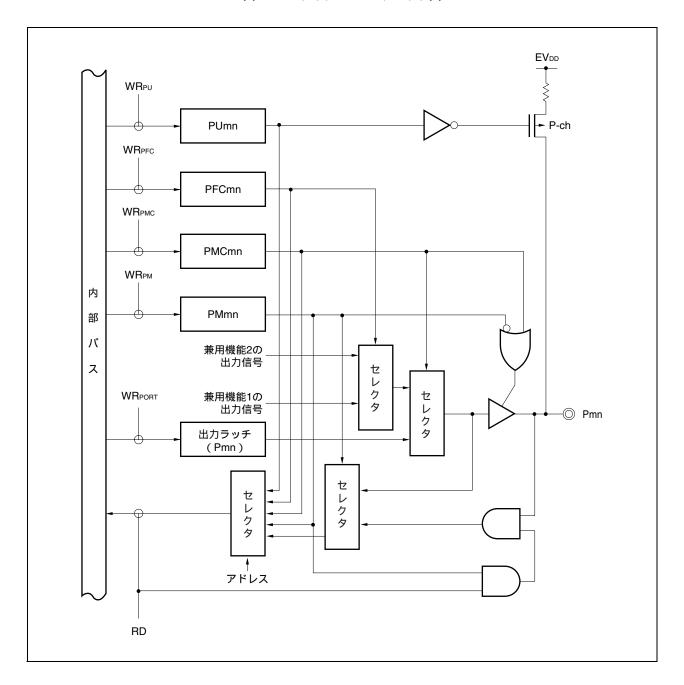

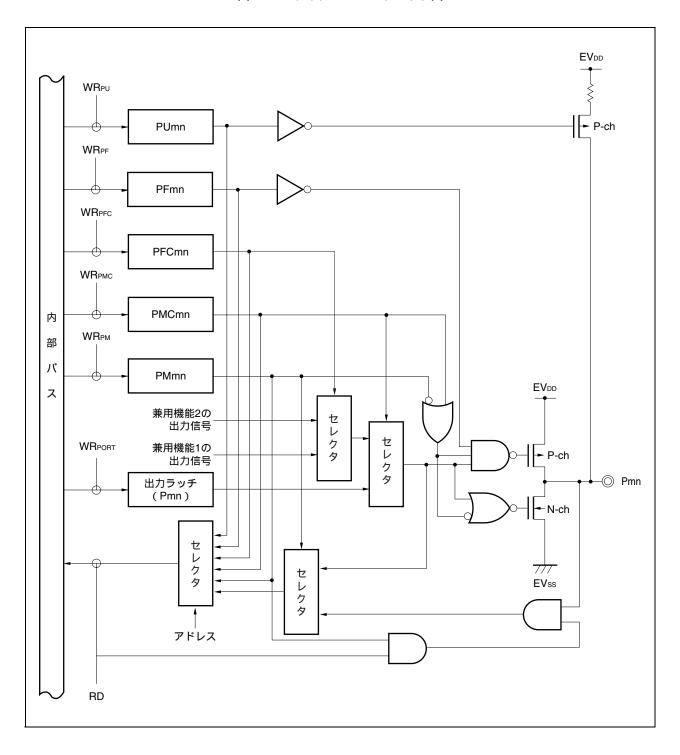

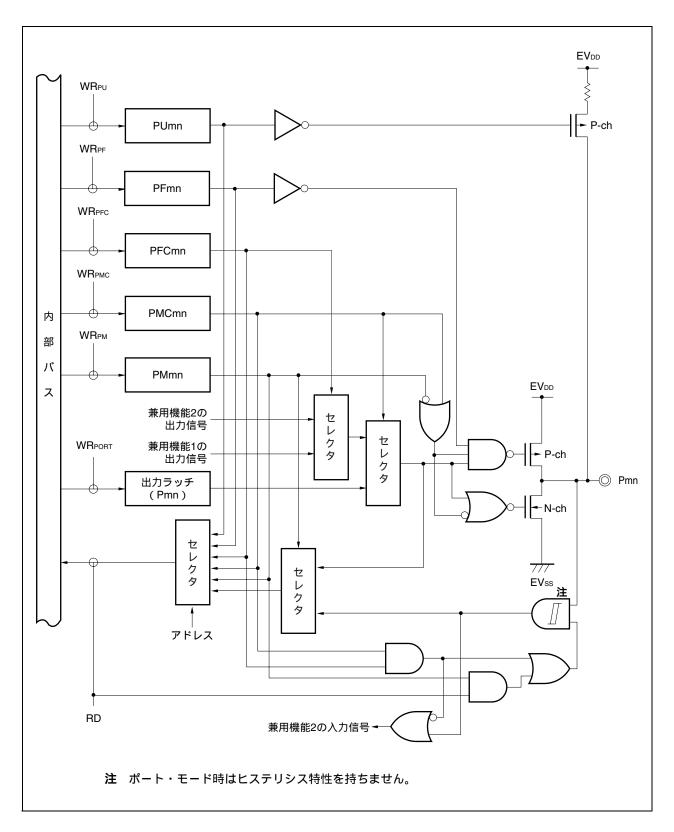

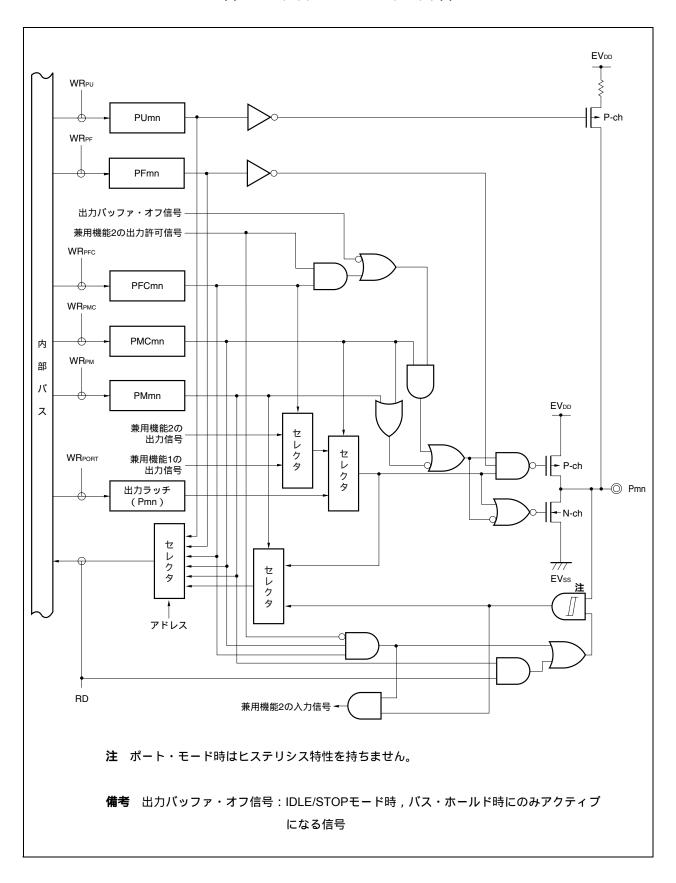

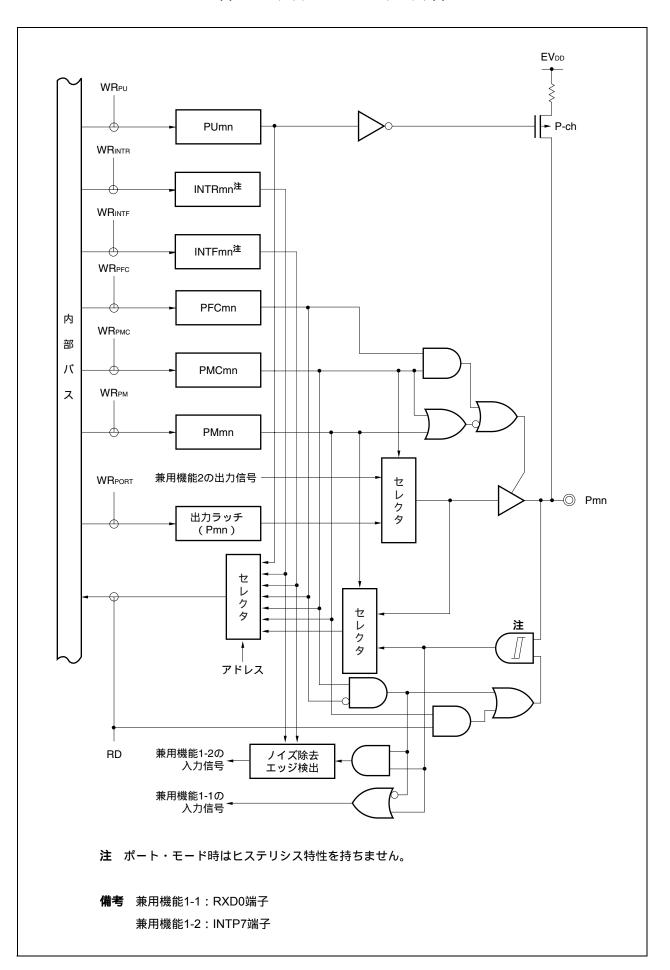

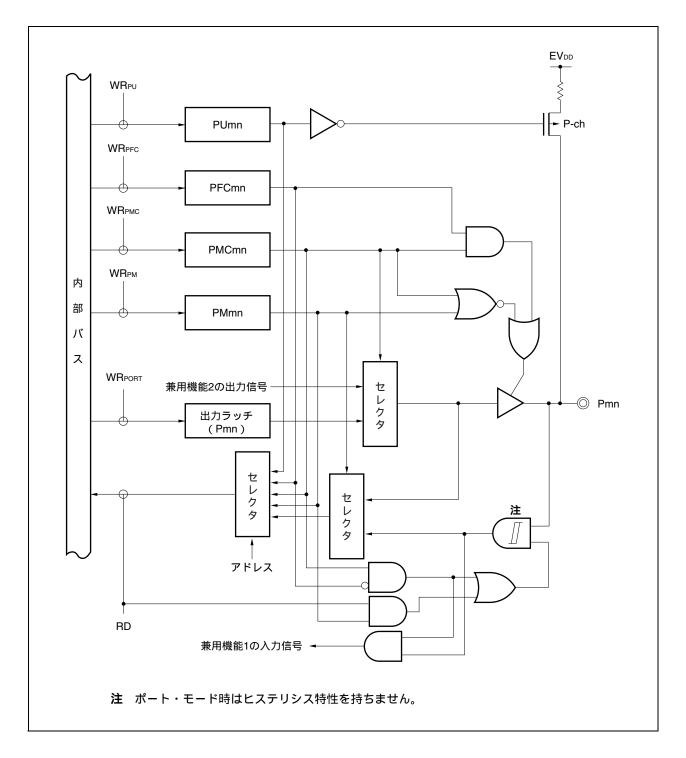

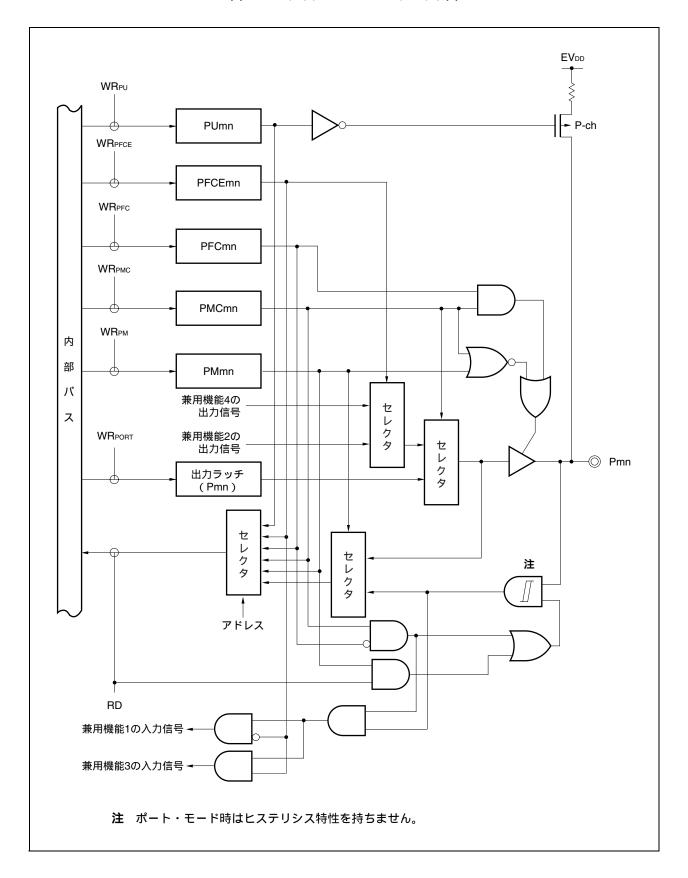

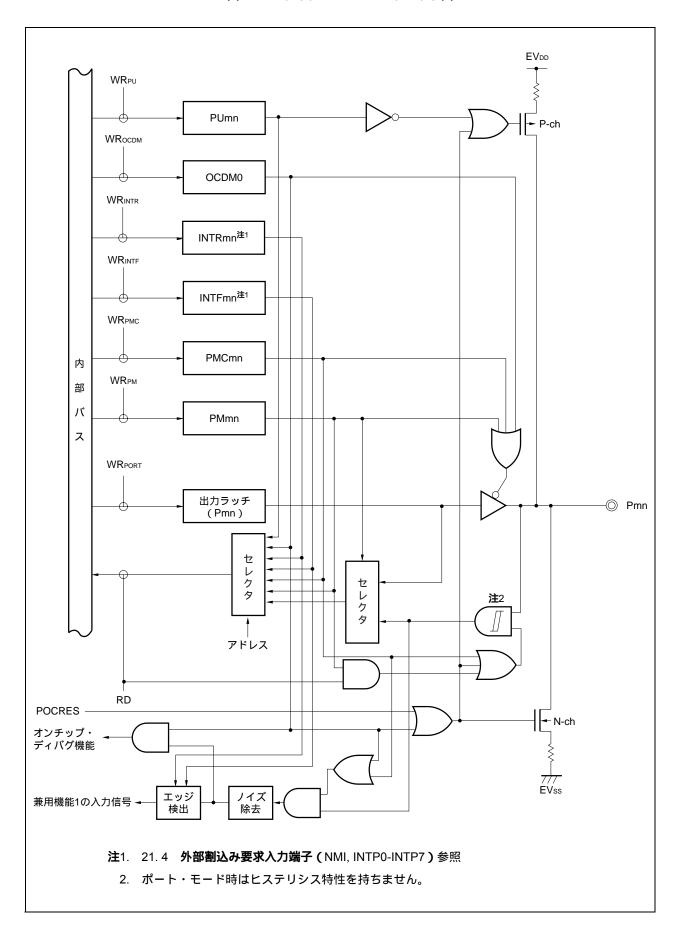

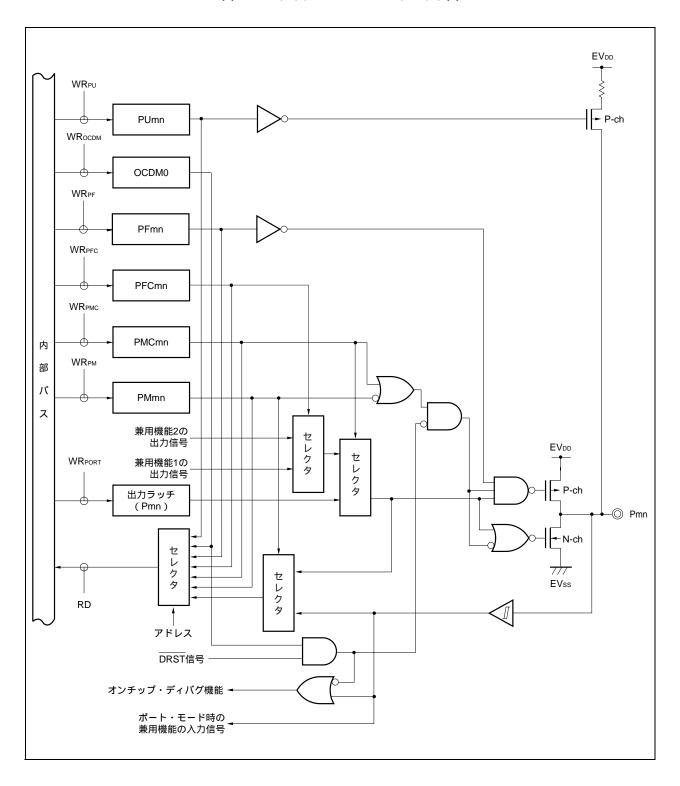

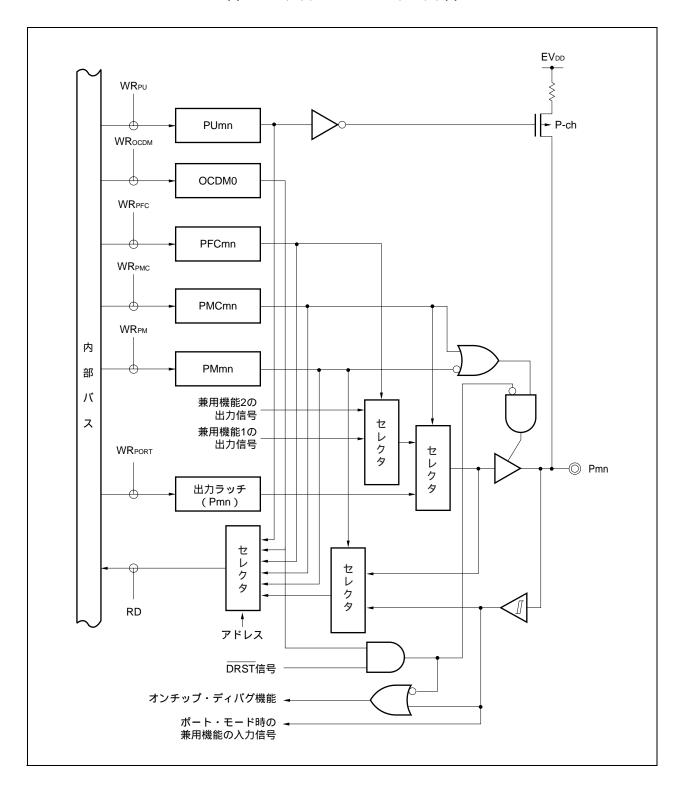

- 4.4 **ブロック図** ... 148

- 4.5 兼用機能使用時のポートのレジスタ設定 ... 183

- 4.6 注意事項 ... 192

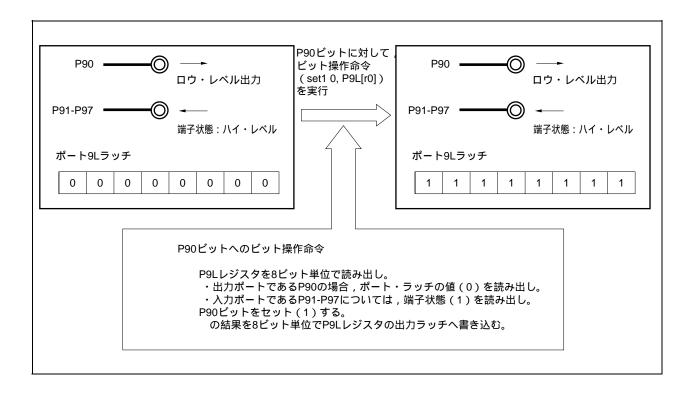

- 4.6.1 ポートnレジスタ (Pn)に対するビット操作命令に関する注意事項 ... 192

- 4.6.2 ヒステリシス特性について ... 193

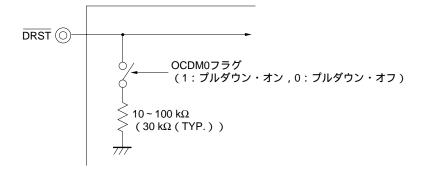

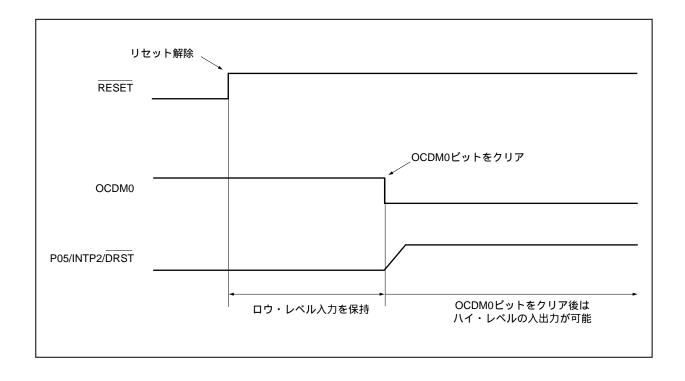

- 4.6.3 オンチップ・ディバグ用端子に関する注意事項 ... 193

- 4. 6. 4 P05/INTP2/DRST端子に関する注意事項 ... 193

#### 第5章 バス制御機能 ... 194

- 5.1 特 徵 ... 194

- 5.2 **バス制御端子** ... 195

- 5.2.1 内蔵ROM,内蔵RAM,内蔵周辺I/Oアクセス時の端子状態 ... 195

- 5.2.2 各動作モードの端子状態 ... 195

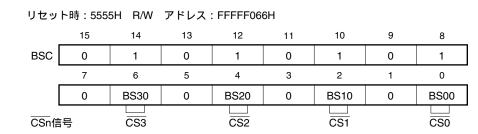

- 5.3 メモリ・ブロック機能 ... 196

- 5.3.1 チップ・セレクト制御機能 ... 197

- 5.4 外部パス・インタフェース・モード制御機能 ... 197

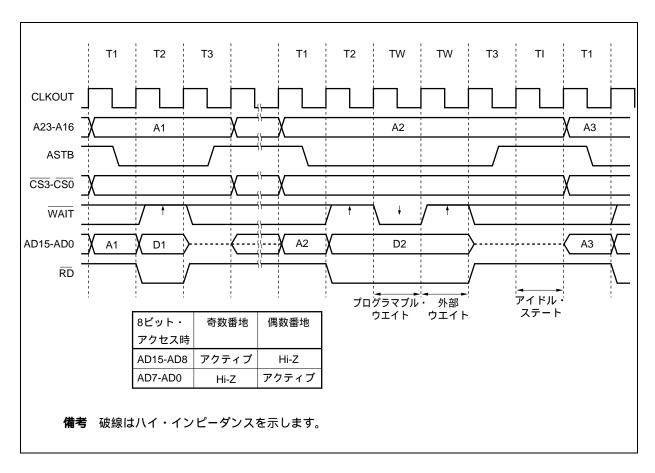

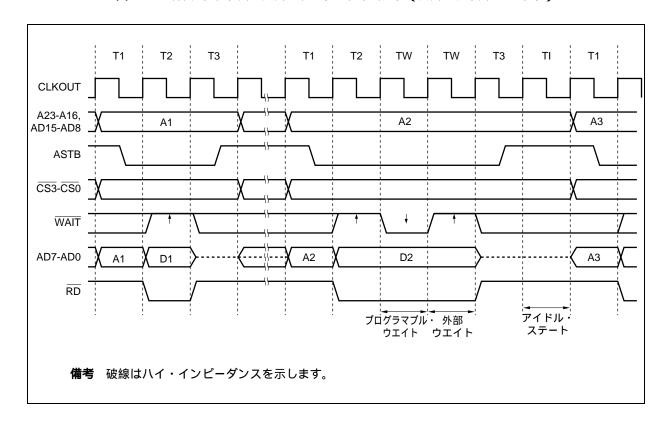

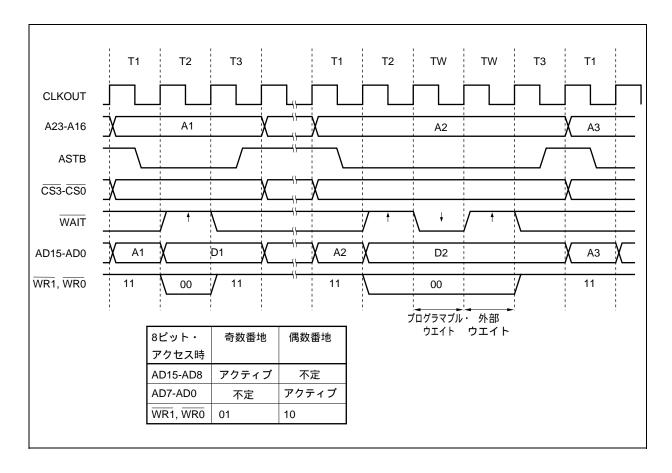

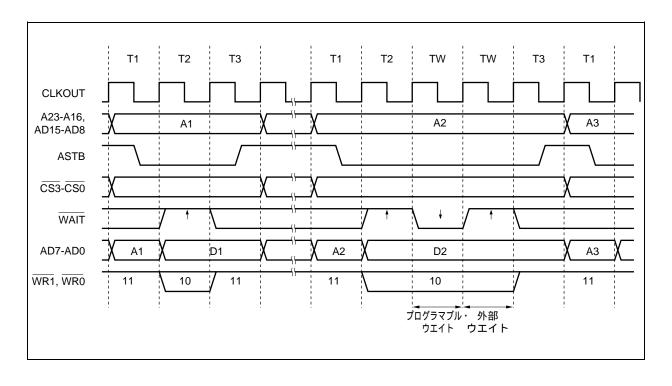

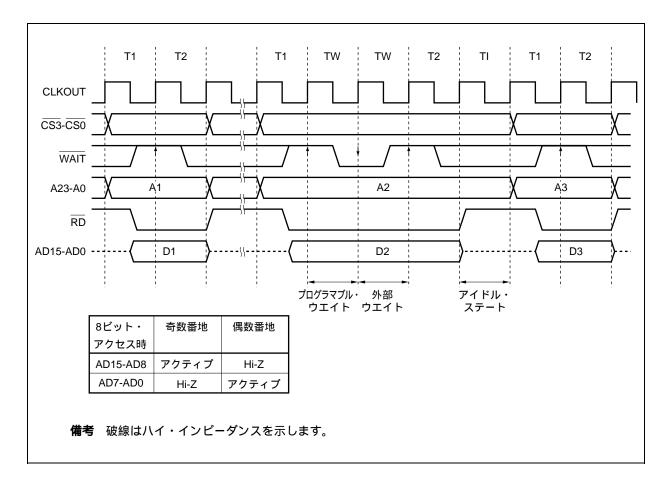

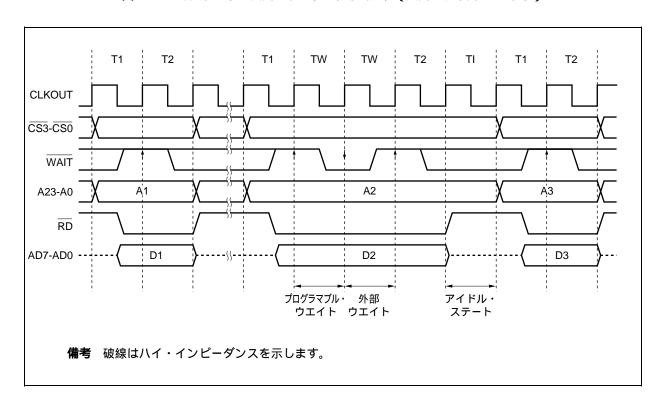

- 5.5 **バス・アクセス** ... 198

- 5.5.1 アクセス・クロック数 ... 198

- 5.5.2 バス・サイズ設定機能 ... 198

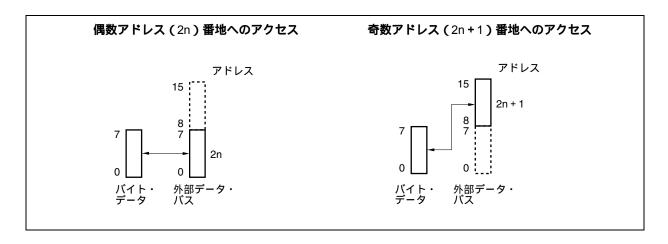

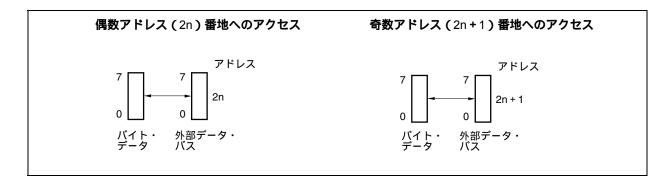

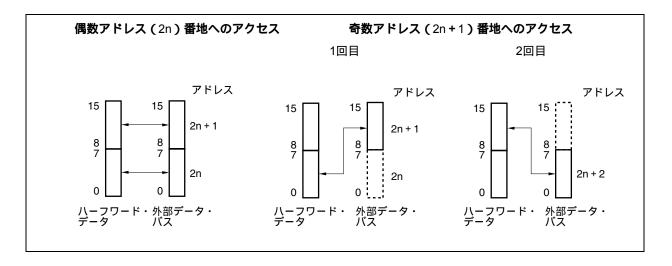

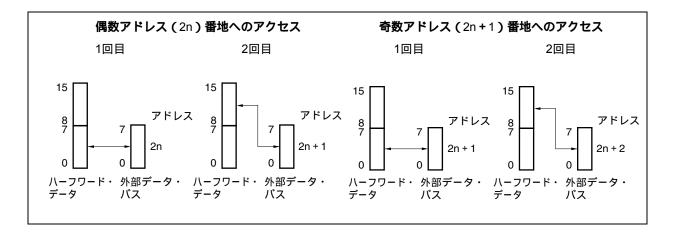

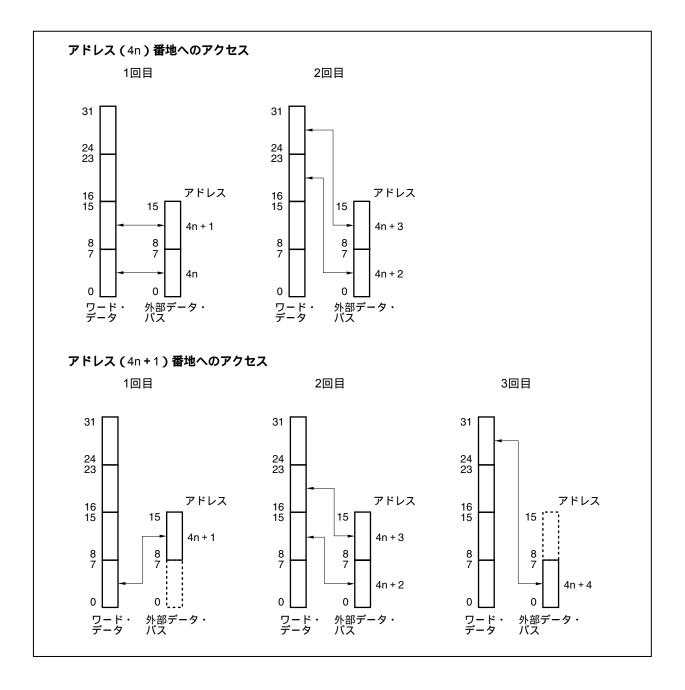

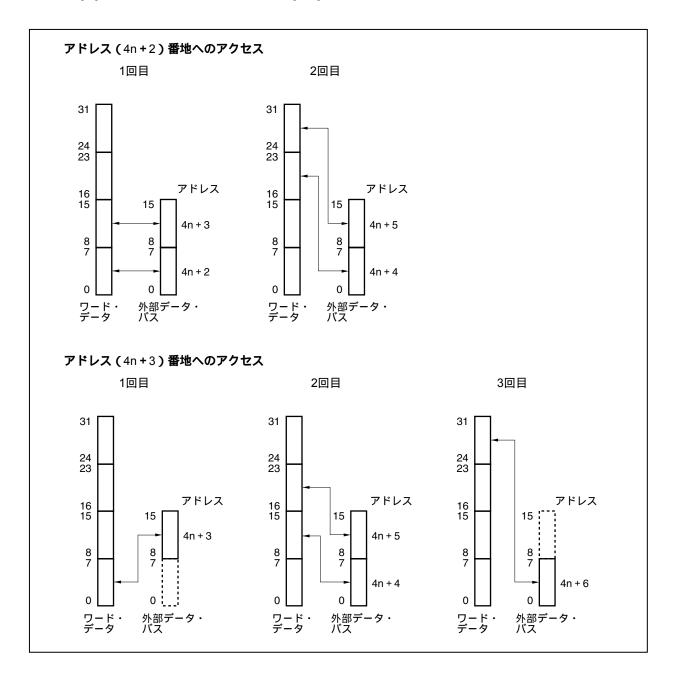

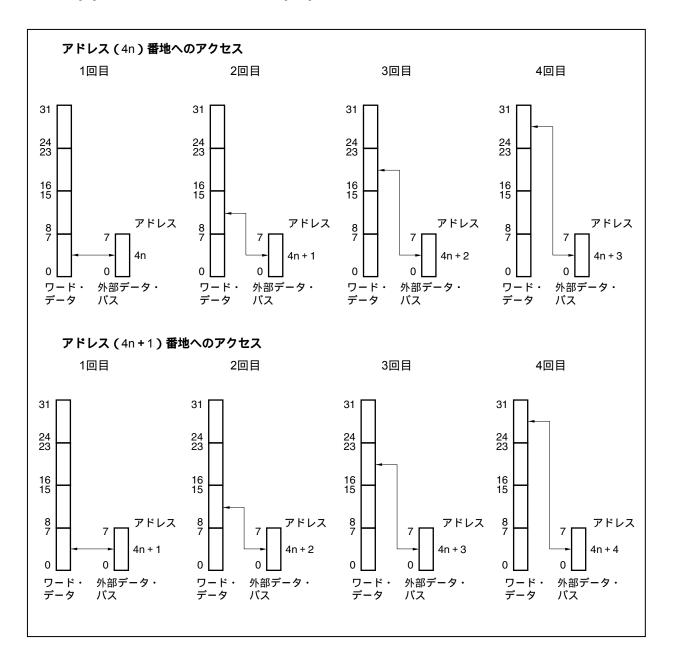

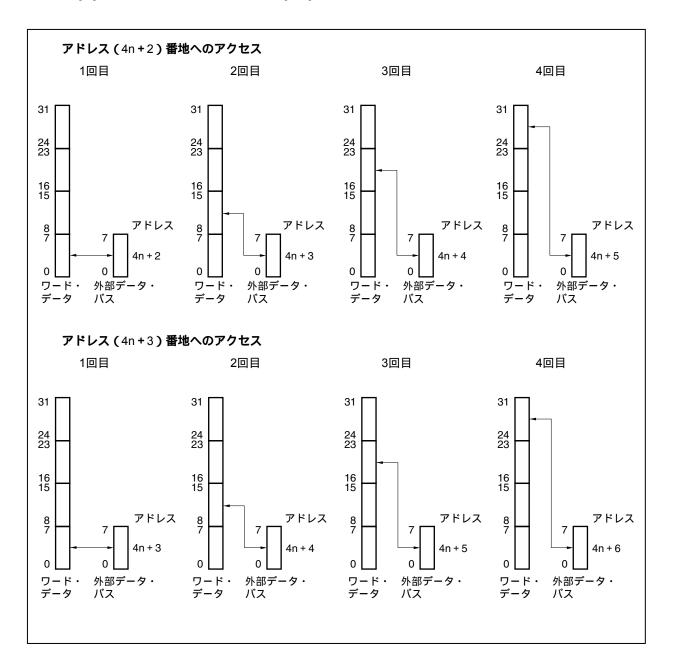

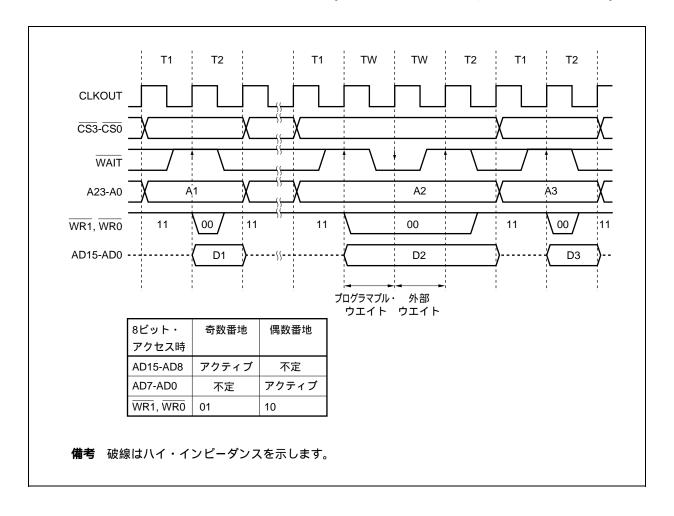

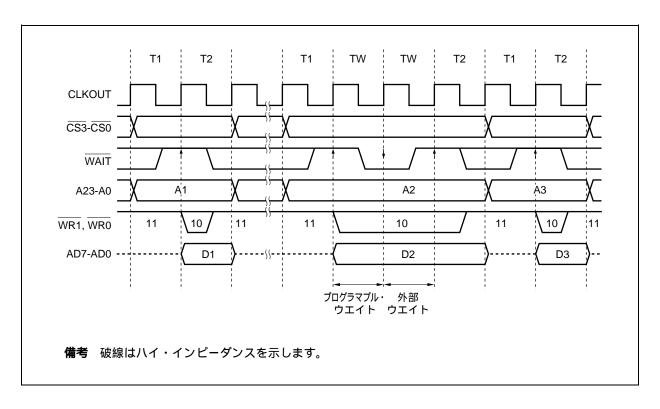

- 5.5.3 バス・サイズによるアクセス ... 199

- 5.6 ウエイト機能 ... 206

- 5.6.1 プログラマブル・ウエイト機能 ... 206

- 5.6.2 外部ウエイト機能 ... 207

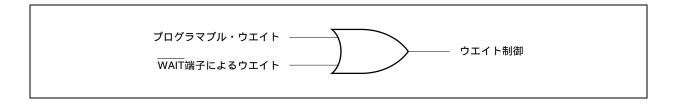

- 5.6.3 プログラマブル・ウエイトと外部ウエイトの関係 ... 208

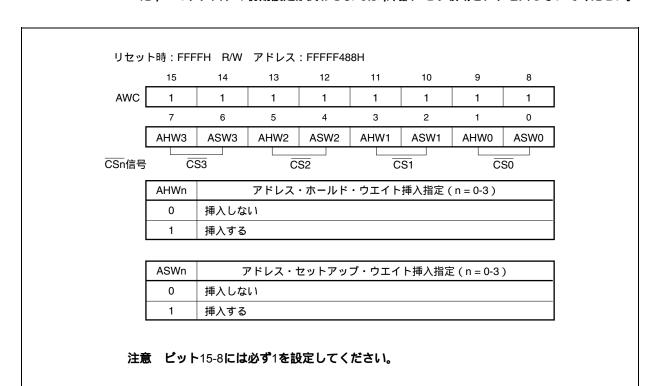

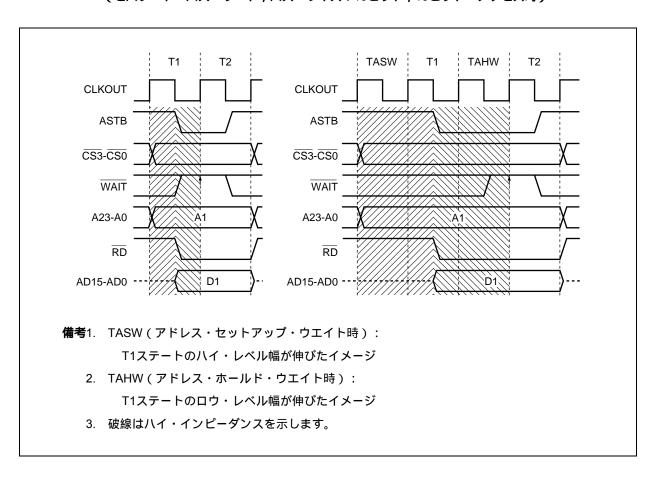

- 5. 6. 4 プログラマブル・アドレス・ウエイト機能 ... 209

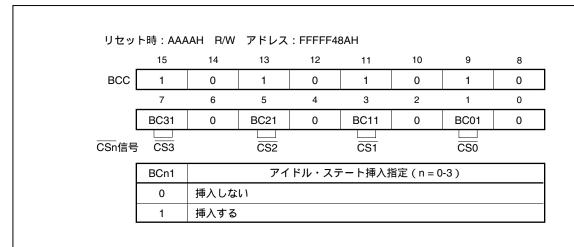

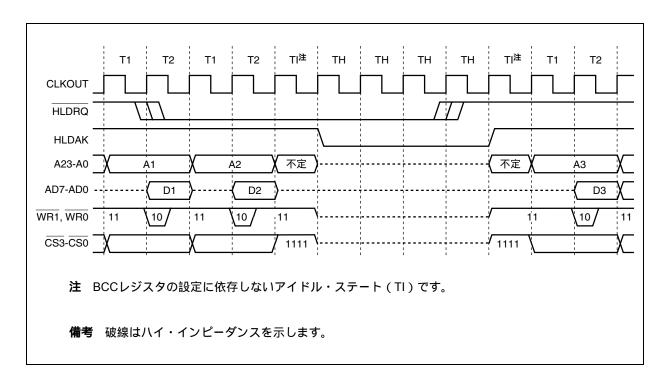

- 5.7 アイドル・ステート挿入機能 ... 210

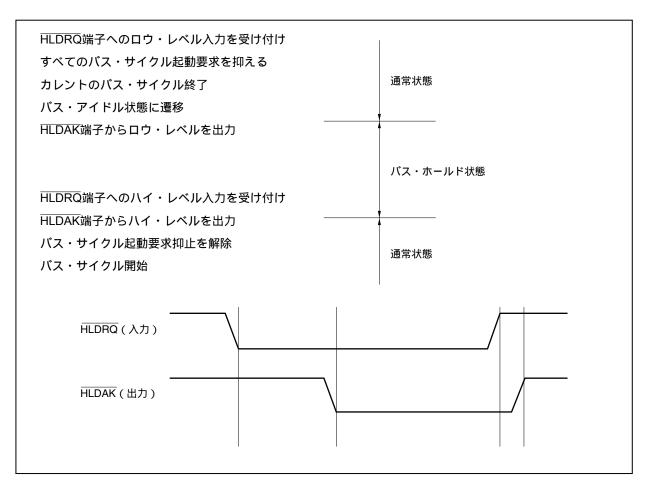

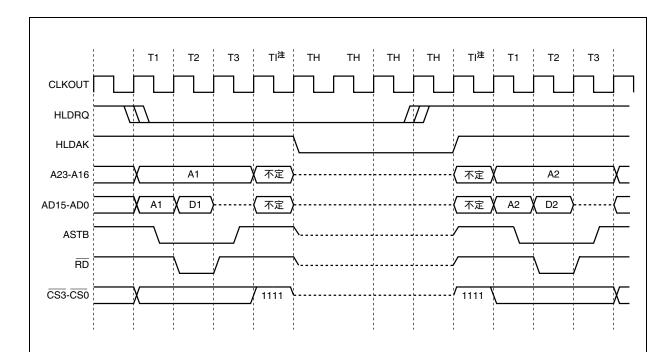

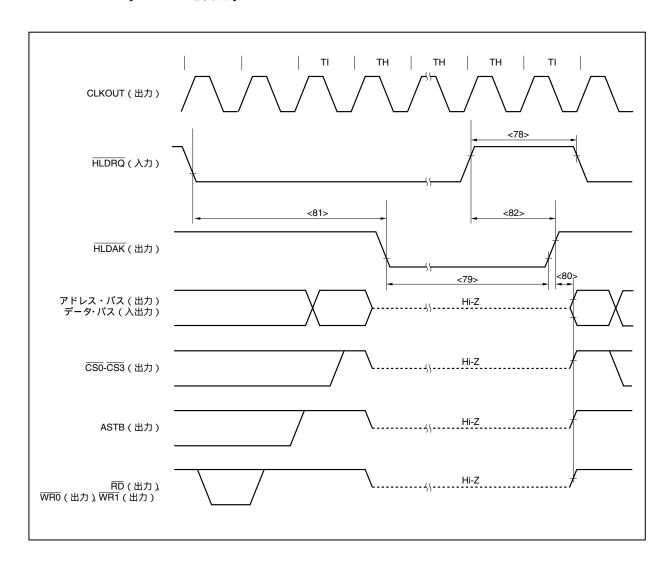

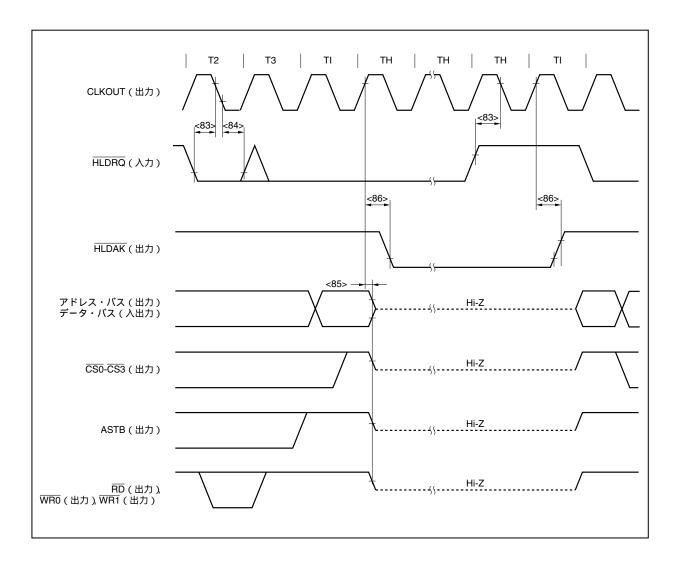

- 5.8 パス・ホールド機能 ... 211

- 5.8.1 機能概要 ... 211

- 5.8.2 バス・ホールド手順 ... 212

- 5.8.3 パワー・セーブ・モード時の動作 ... 212

- 5.9 バスの優先順位 ... 213

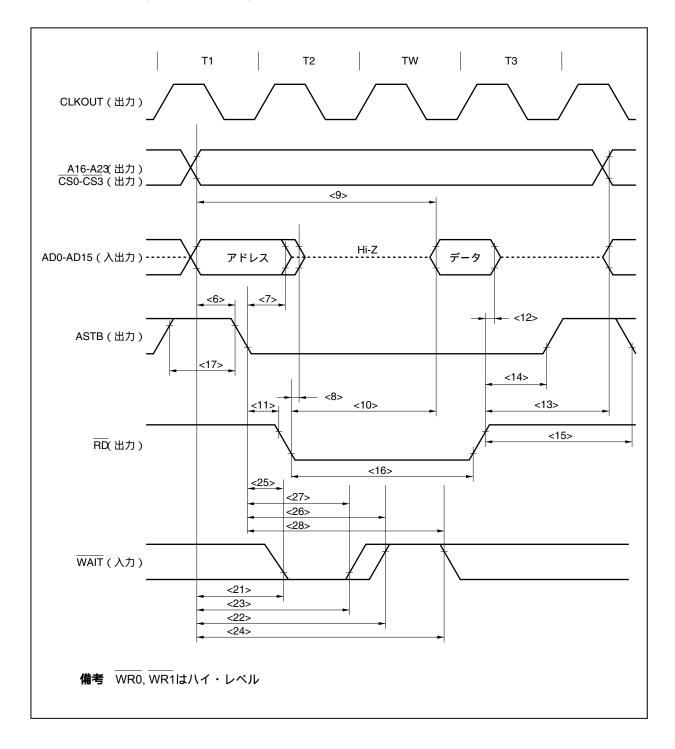

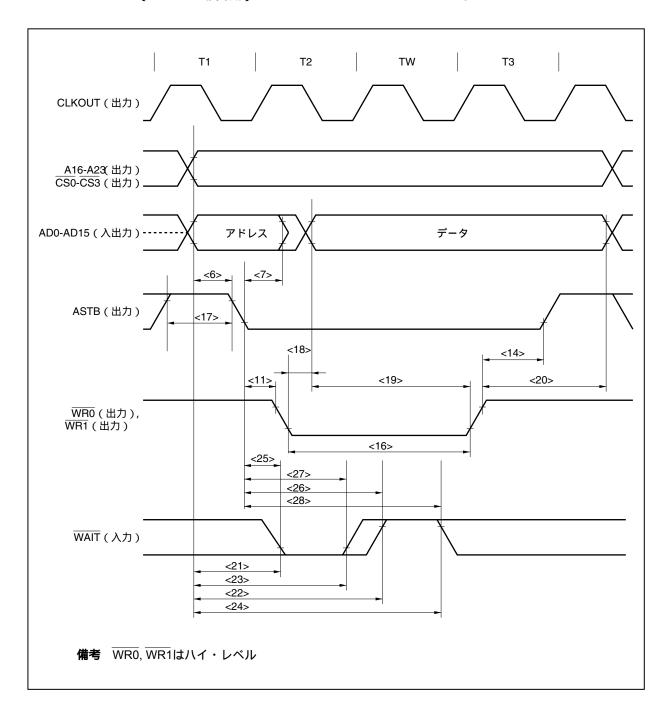

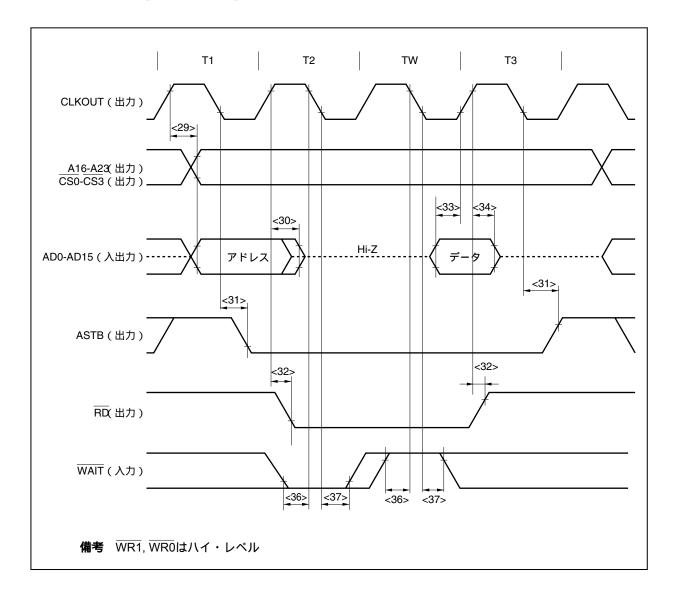

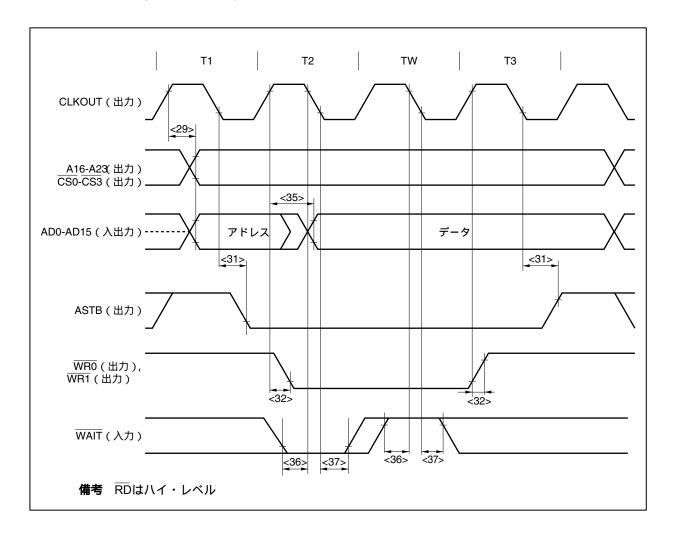

- 5. 10 **パス・タイミング** ... 214

- 5. 11 注意事項 ... 220

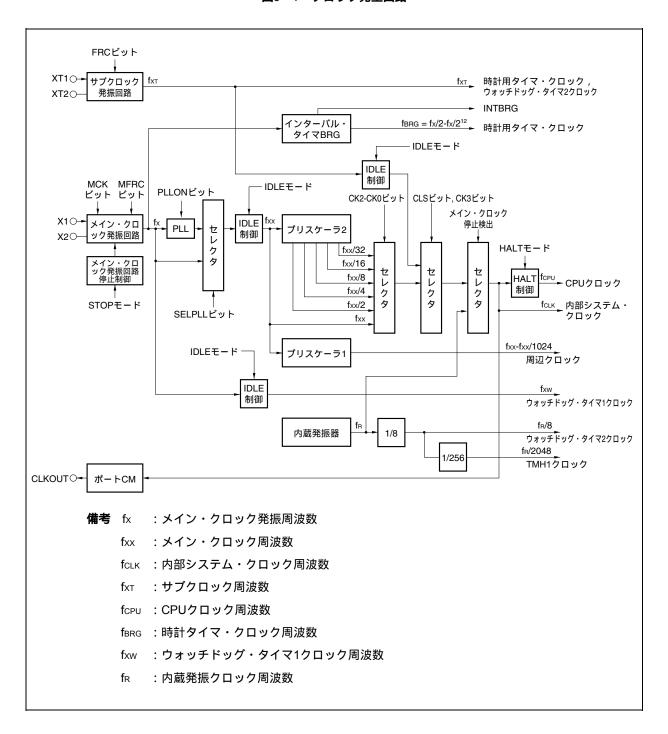

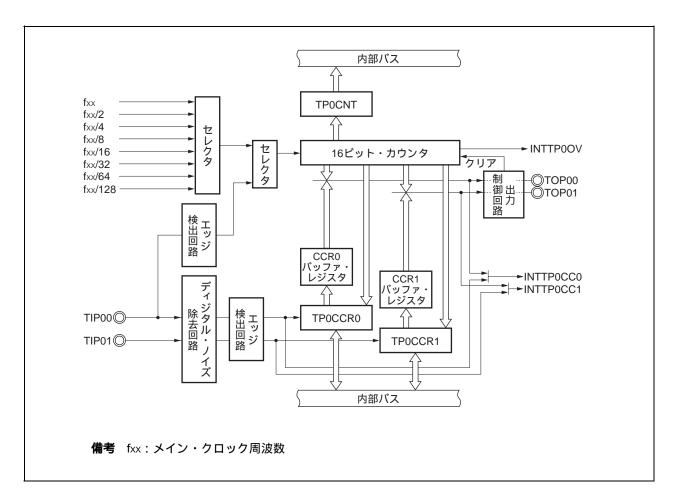

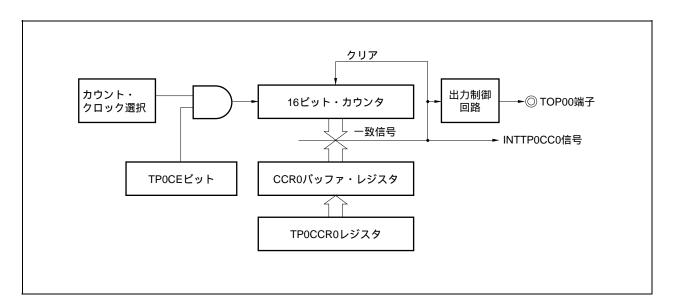

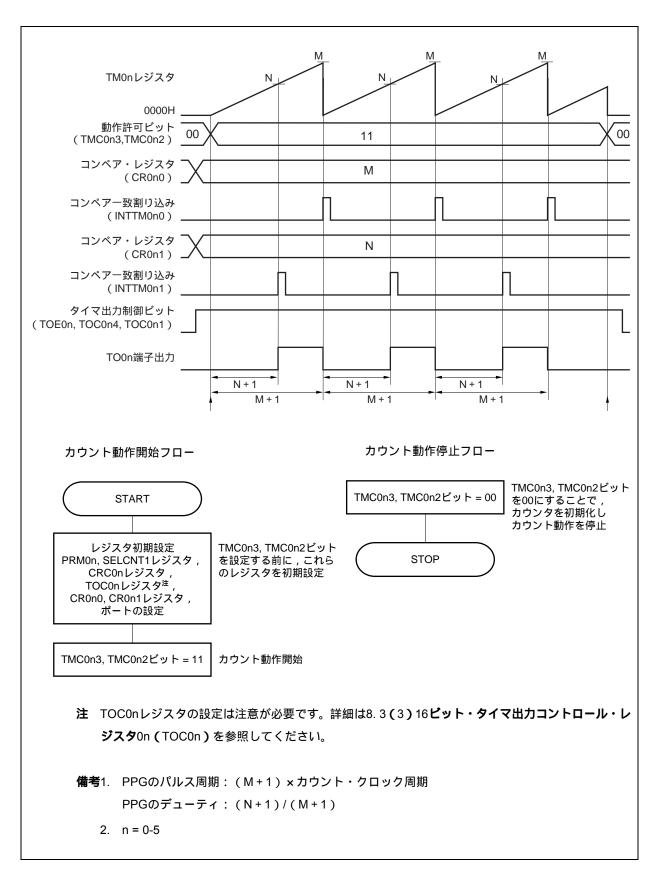

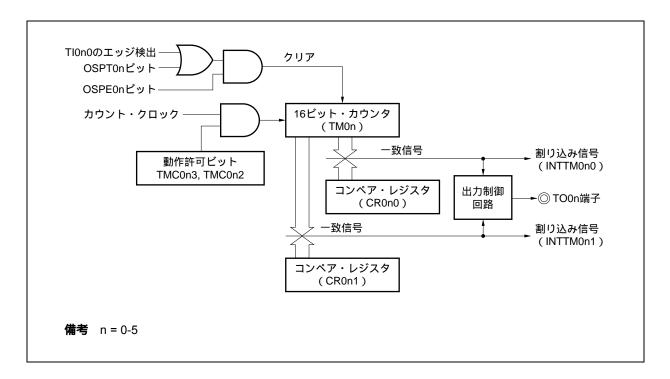

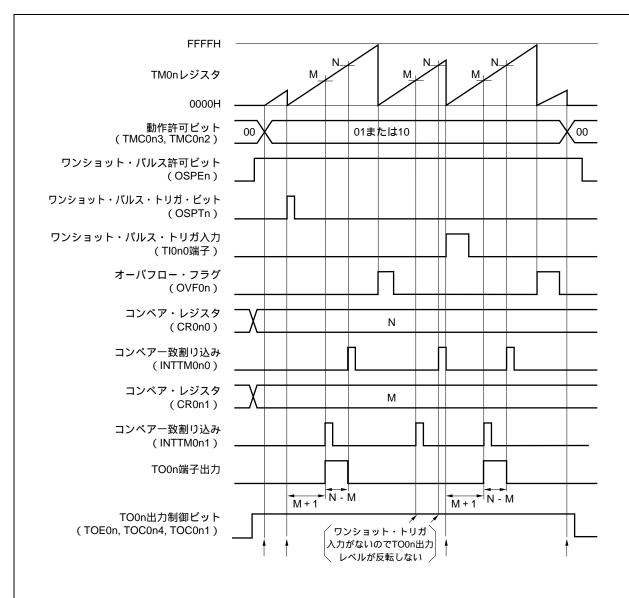

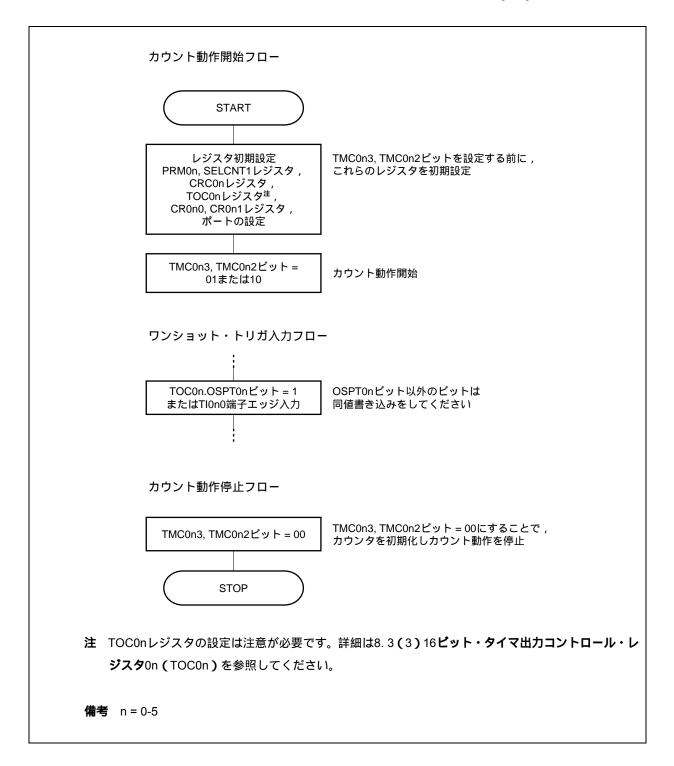

#### 第6章 クロック発生機能 ... 221 要 ... 221 6.1 概 6.2 構 成 ... 222 6.3 レジスタ ... 224 6.4 動作 ... 229 6.4.1 各クロックの動作 ... 229 6.4.2 クロック出力機能 ... 229 6.4.3 外部クロック入力機能 ... 229 6.5 PLL機能 ... 230 6.5.1 概 要 ... 230 6.5.2 レジスタ ... 230 6.5.3 使用方法 ... 231 第7章 16**ビット・タイマ / イベント・カウンタ**P (TMP) ... 232 7.1 概 要 ... 232 7.2 機 能 ... 232 7.3 構 成 ... 233 7.4 **レジスタ** ... 235 7.5 動作 ... 246 7. 5. 1 インターバル・タイマ・モード(TP0MD2-TP0MD0ビット = 000) ... 247 7.5.2 外部イベント・カウント・モード(TP0MD2-TP0MD0ビット = 001) ... 257 7.5.3 外部トリガ・パルス出力モード(TP0MD2-TP0MD0ビット = 010) ... 265 7.5.4 ワンショット・パルス出力モード(TP0MD2-TP0MD0ビット = 011) ... 277 7.5.5 PWM出力モード(TP0MD2-TP0MD0ビット = 100) ... 284 7. 5. 6 フリー・ランニング・タイマ・モード(TP0MD2-TP0MD0ビット = 101) ... 293 7.5.7 パルス幅測定モード(TP0MD2-TP0MD0ビット = 110) ... 310 7.5.8 タイマ出力動作説明 ... 316 7.6 **キャプチャ・トリガ入力端子 (TIPOa) のノイズ除去** ... 317 7.7 注意事項 ... 319 **第8章** 16**ピット・タイマ/イベント・カウンタ**0 ... 320 8.1 機 能 ... 320 成 ... 321 8.2 構 8.3 レジスタ ... 327 8.4 動作… 336 8.4.1 インターバル・タイマとしての動作 ... 336 8.4.2 方形波出力としての動作 ... 339 8.4.3 外部イベント・カウンタとしての動作 ... 343 8.4.4 TIOnO端子の有効エッジ入力によるクリア&スタート・モードとしての動作 ... 347 8.4.5 フリー・ランニング・タイマとしての動作 ... 363 8.4.6 PPG出力としての動作 ... 373 8.4.7 ワンショット・パルス出力としての動作 ... 377 8.4.8 パルス幅測定としての動作 ... 382 8.5 TM0n**の特殊な使用方法** ... 390 8.5.1 CR0n1レジスタのTM0n動作中の書き換え ... 390

| 第9章 8                | 8ピット・タイマ / イベント・カウンタ5 399                                                                                                                                                                                                                                                                                            |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9. 2<br>9. 3         | 機 能 … 399<br>構 成 … 400<br>レジスタ … 403<br>動 作 … 406<br>9.4.1 インターバル・タイマとしての動作 … 406<br>9.4.2 外部イベント・カウンタとしての動作 … 408<br>9.4.3 方形波出力としての動作 … 409<br>9.4.4 8ビットPWM出力としての動作 … 410<br>9.4.5 インターバル・タイマ(16ビット)としての動作 … 413<br>9.4.6 外部イベント・カウンタ(16ビット)としての動作 … 415<br>9.4.7 方形波出力(16ビット分解能)としての動作 … 416<br>9.4.8 注意事項 … 417 |

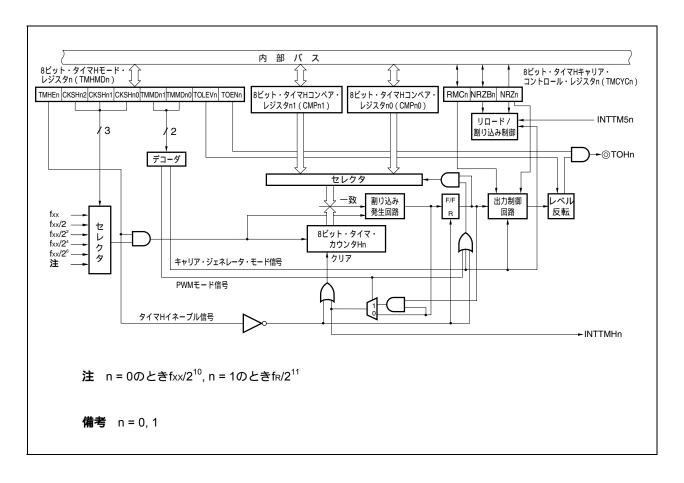

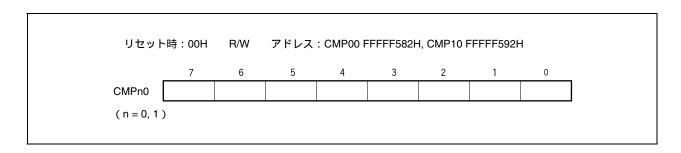

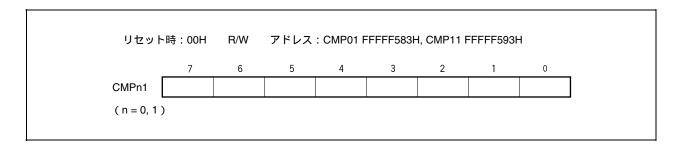

| 第10章                 | 8 <b>ビット・タイマ</b> H 418                                                                                                                                                                                                                                                                                               |

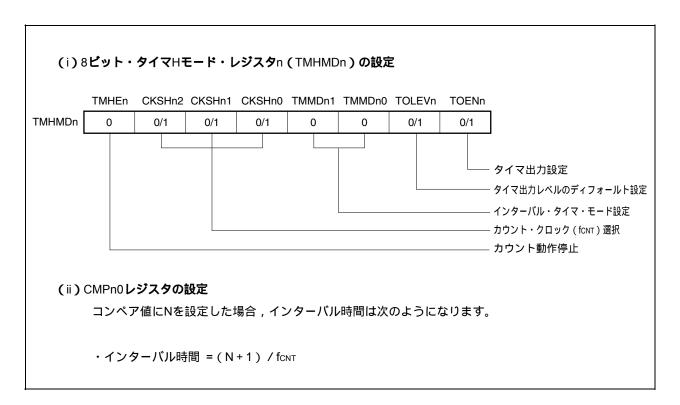

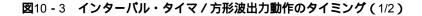

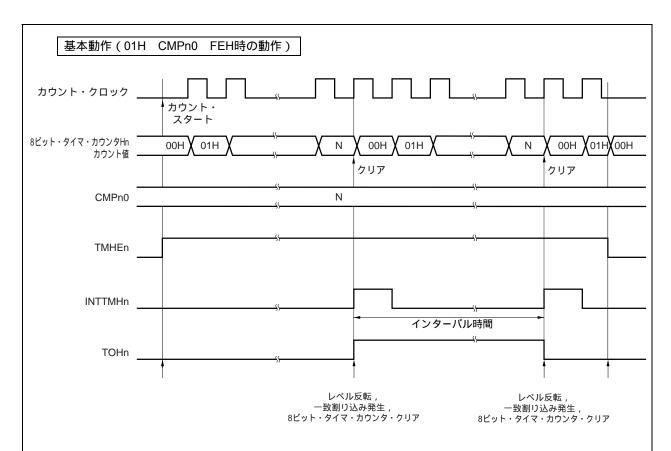

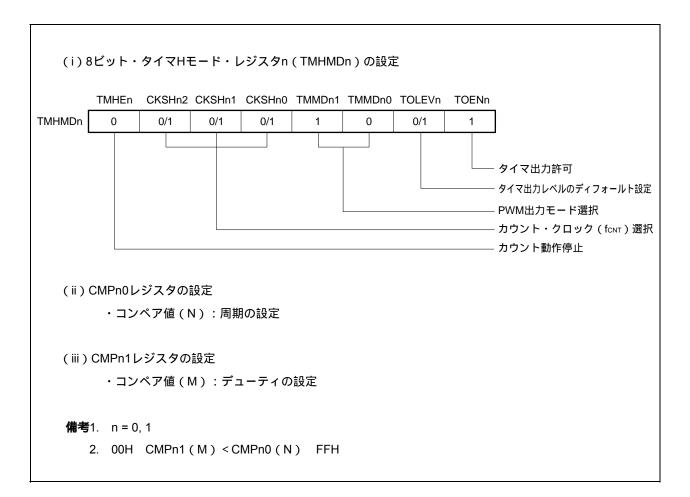

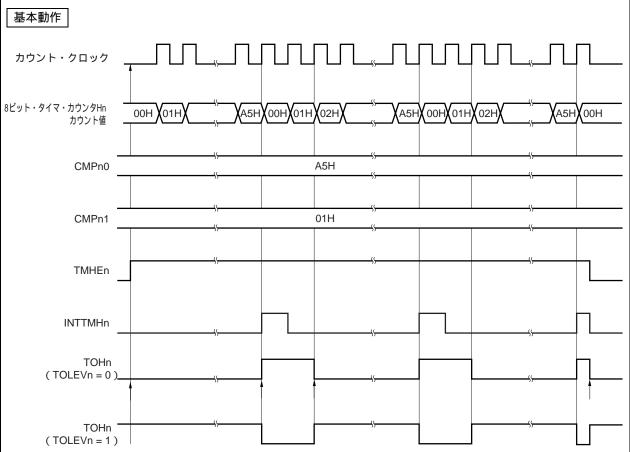

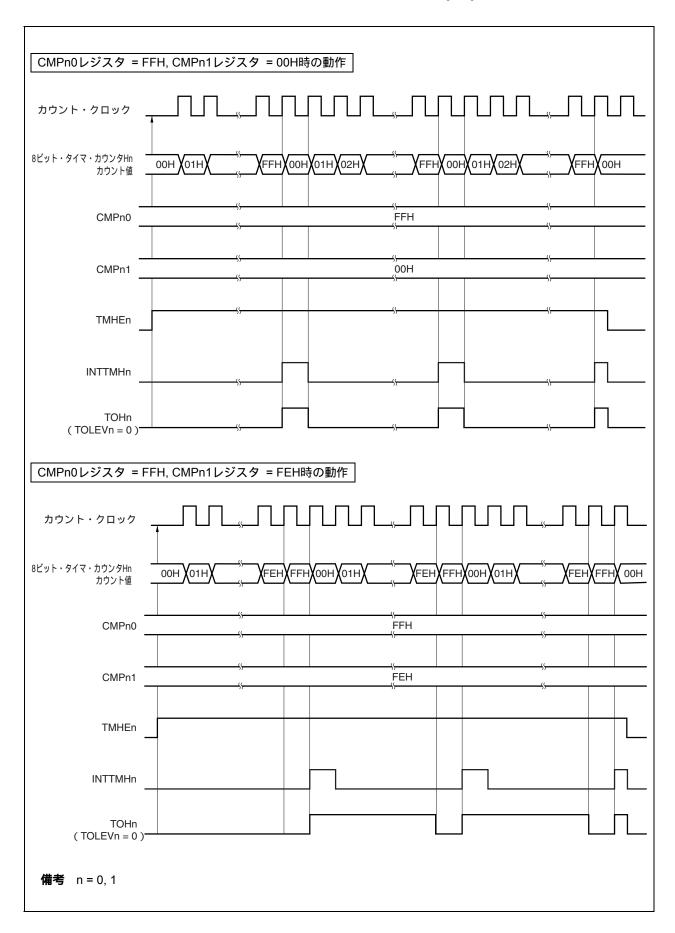

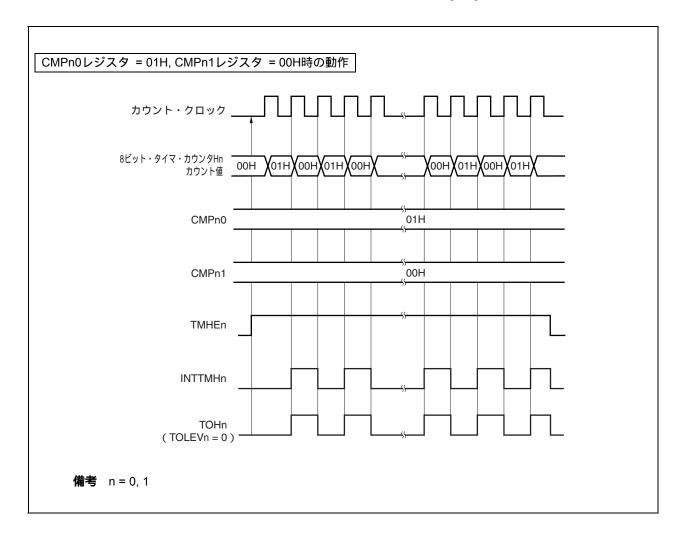

| 10. 2<br>10. 3       | 機 能 418<br>構 成 418<br>レジスタ 421<br>動 作 425<br>10.4.1 インターバル・タイマ / 方形波出力としての動作 425<br>10.4.2 PWM出力モードとしての動作 428<br>10.4.3 キャリア・ジェネレータ・モードとしての動作 434                                                                                                                                                                    |

| 第11章                 | インターパル・タイマ , 時計タイマ 441                                                                                                                                                                                                                                                                                               |

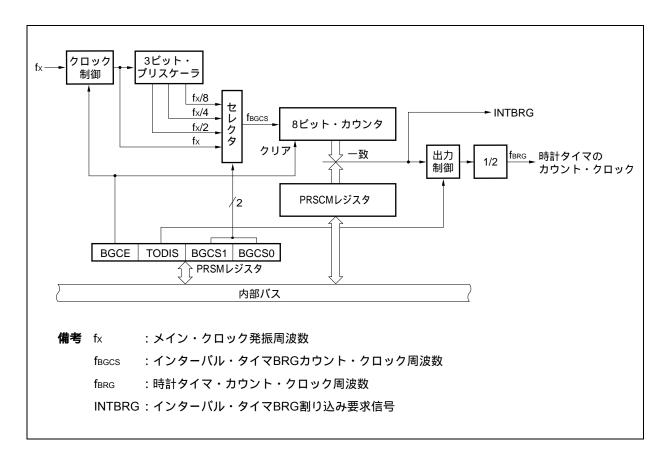

| 11. 1                | インターバル・タイマBRG 441<br>11. 1. 1 機 能 441<br>11. 1. 2 構 成 441<br>11. 1. 3 レジスタ 443<br>11. 1. 4 動 作 445                                                                                                                                                                                                                   |

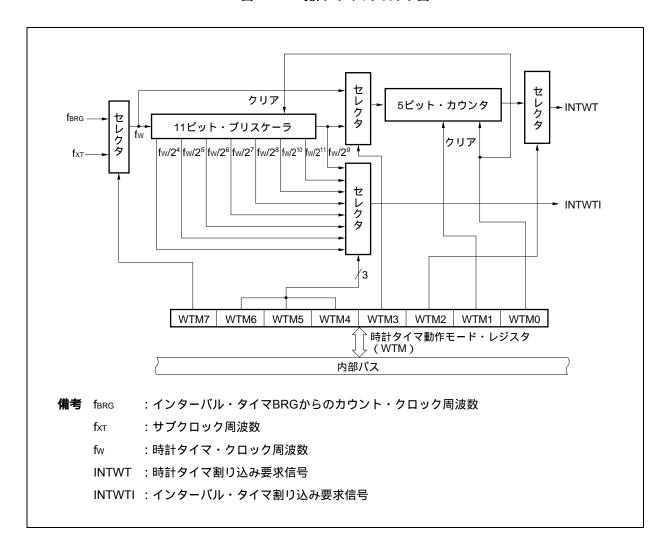

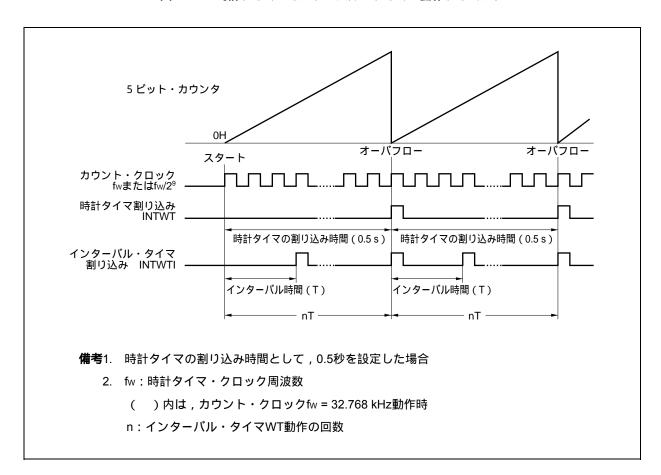

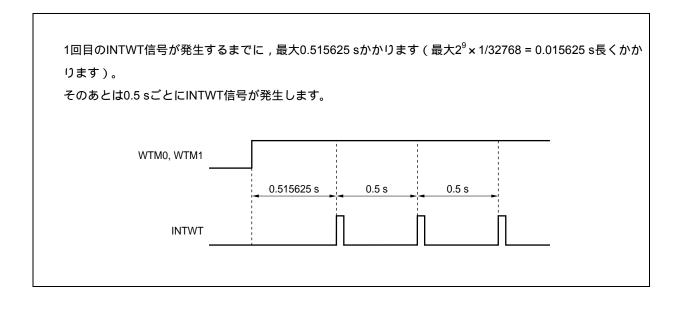

| 11. 2                | <b>時計タイマ</b> 446<br>11. 2. 1 機 能 446<br>11. 2. 2 構 成 446<br>11. 2. 3 レジスタ 448<br>11. 2. 4 動 作 450                                                                                                                                                                                                                    |

| 11. 3                | 注意事項 451                                                                                                                                                                                                                                                                                                             |

| <b>第</b> 12 <b>章</b> | ウォッチドッグ・タイマ機能 453                                                                                                                                                                                                                                                                                                    |

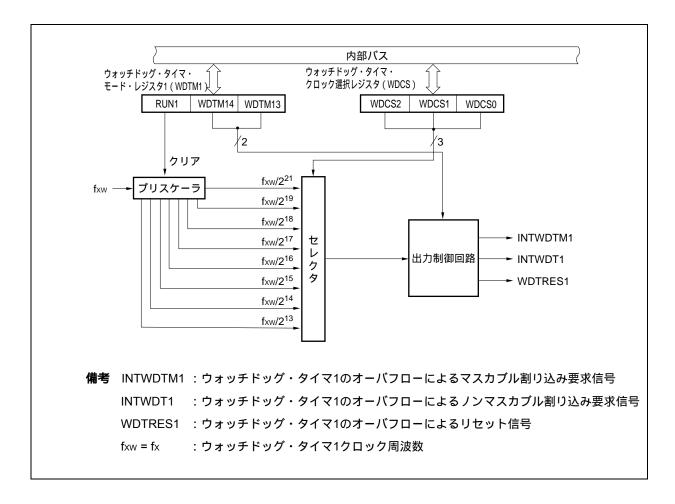

| 12. 1                | ウォッチドッグ・タイマ1       …       453         12. 1. 1       機       能       …       453         12. 1. 2       構       成       …       455         12. 1. 3       レジスタ       …       455         12. 1. 4       動       作       …       457                                                                                |

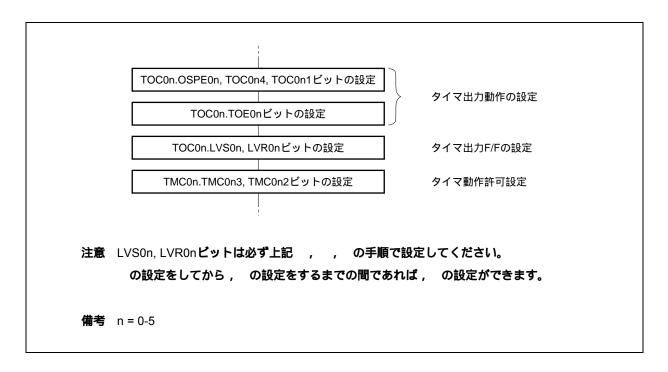

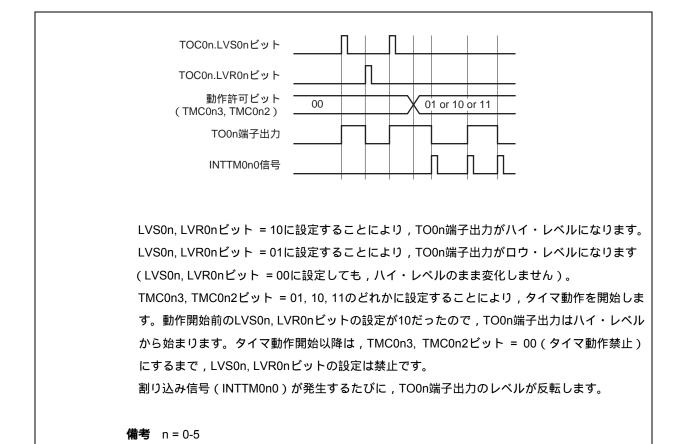

8.5.2 LVS0n, LVR0nビットの設定について ... 390

8.6 注意事項 ... 392

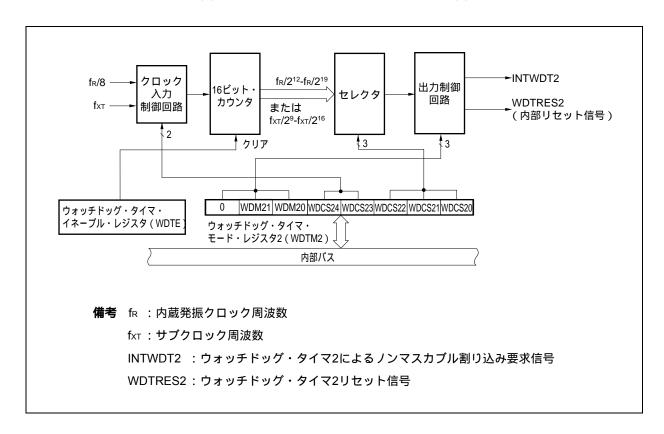

| 12. 2                | ウォッチドッグ・タイマ2 459                             |

|----------------------|----------------------------------------------|

|                      | 12. 2. 1 機 能 459                             |

|                      | 12. 2. 2 構 成 460                             |

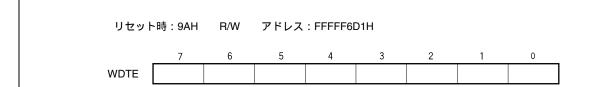

|                      | 12.2.3 レジスタ 460                              |

|                      | 12. 2. 4 動作 462                              |

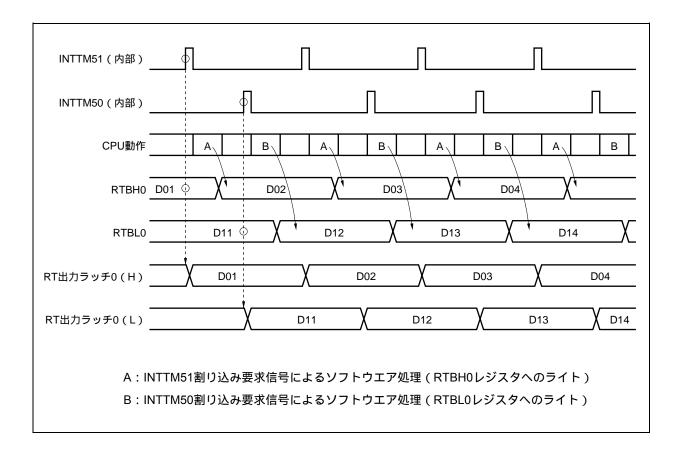

| <b>第</b> 13章         | <b>リアルタイム出力機能(</b> RTO <b>)</b> 463          |

|                      | lab. Are                                     |

|                      | 機 <b>能</b> 463                               |

|                      | <b>構 成</b> 464<br>レジスタ 466                   |

|                      | 動 作 468                                      |

|                      | 使用方法 469                                     |

| 13. 6                | <b>注意事項</b> 469                              |

| 13. 7                | セキュリティ機能 470                                 |

|                      | A/D = 3.41° A                                |

| <b>弗</b> 14 <b>草</b> | A/D <b>コンバータ</b> 472                         |

| 14. 1                | 概 要 472                                      |

| 14. 2                |                                              |

| 14. 3                | 構 成 473                                      |

| 14. 4                | レジスタ 475                                     |

| 14. 5                | 動 作 483                                      |

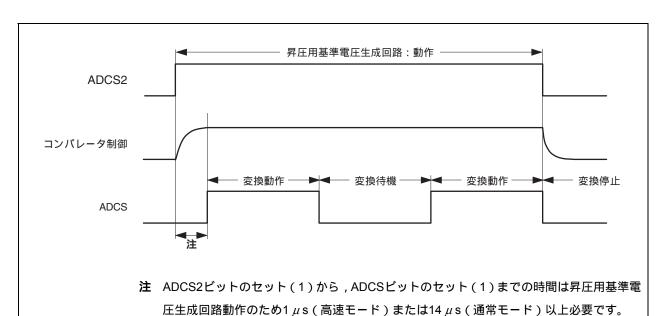

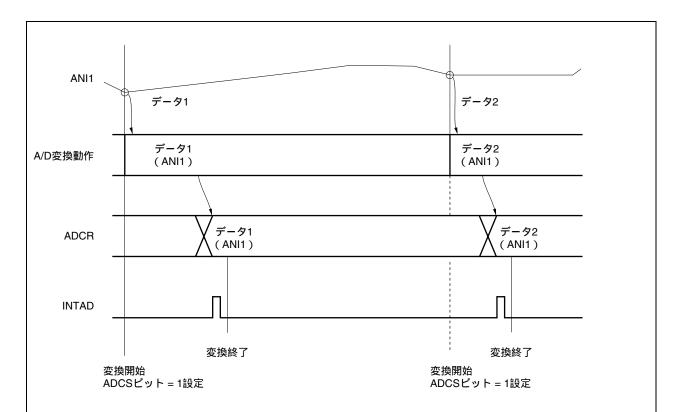

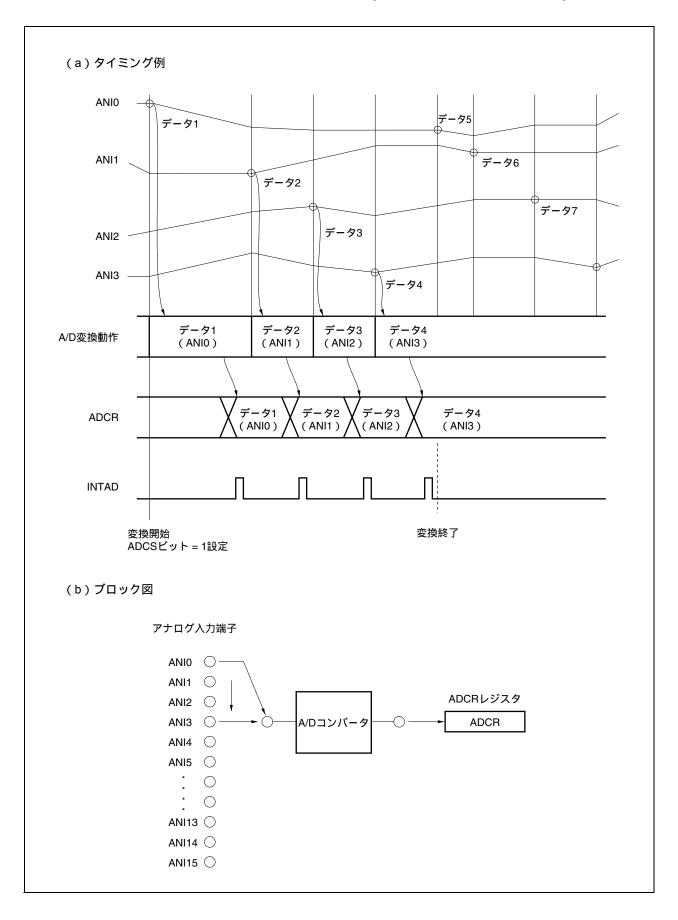

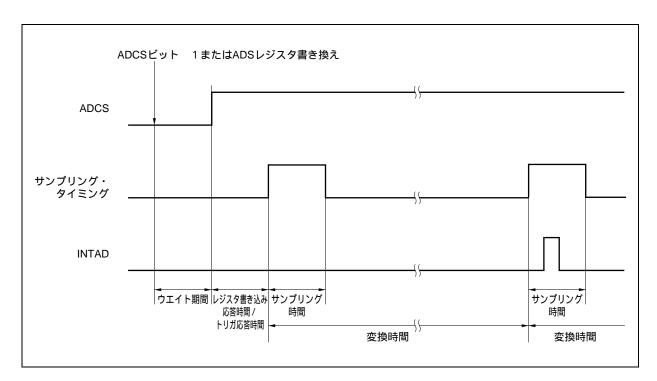

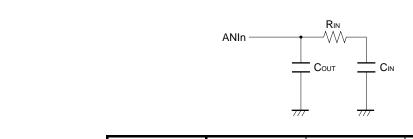

|                      | 14. 5. 1 基本動作 483                            |

|                      | 14. 5. 2 トリガ・モード 484                         |

|                      | 14.5.3 動作モード 485                             |

|                      | 14. 5. 4 パワー・フェイル検出機能 488                    |

|                      | 14. 5. 5 設定方法 489                            |

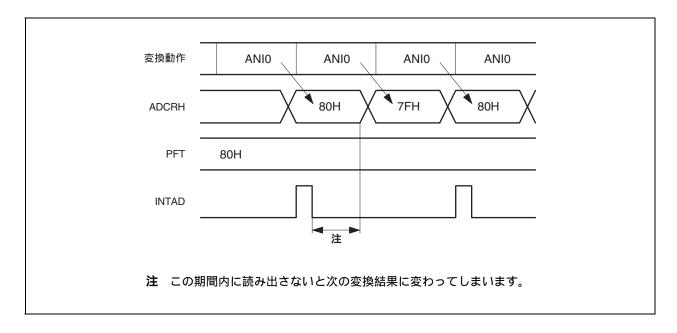

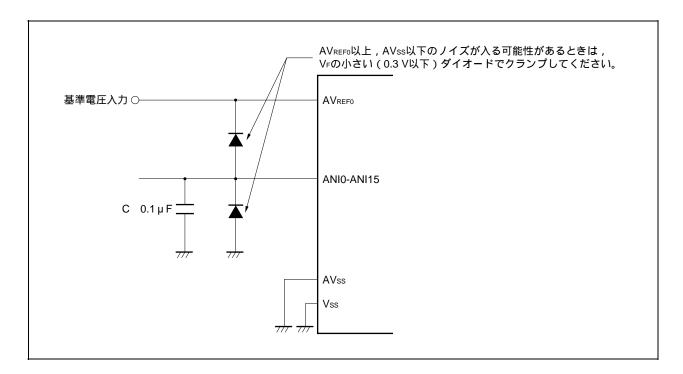

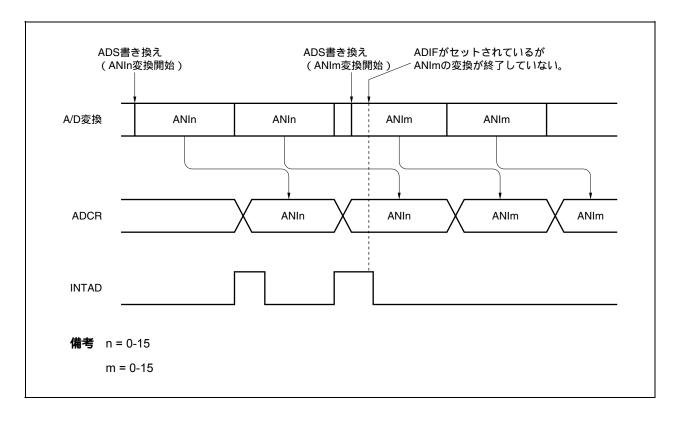

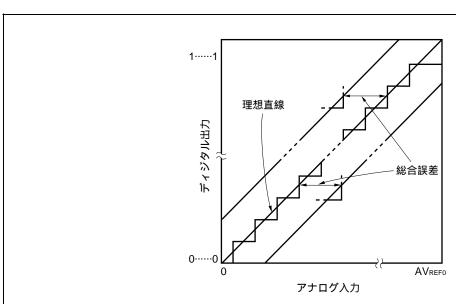

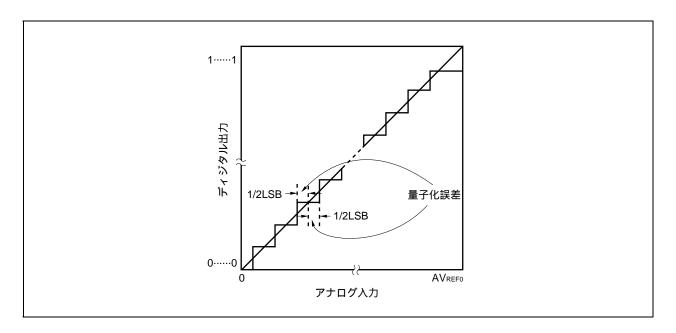

|                      | 注意事項 491<br>A/D <b>コンパータ特性表の読み方</b> 497      |

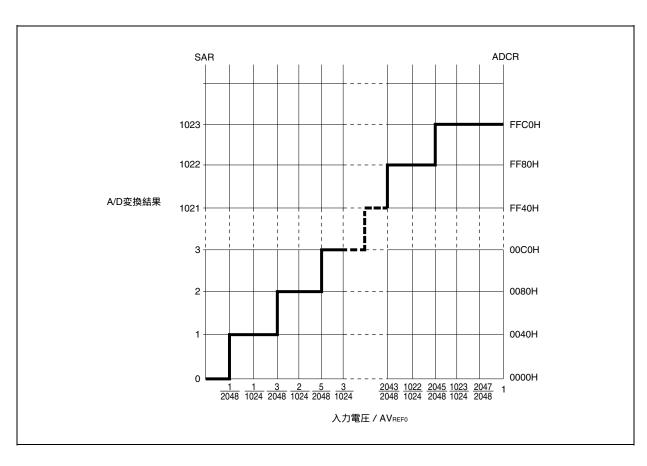

| 14. 1                | スプコンパータ特性なの数のカ」 487                          |

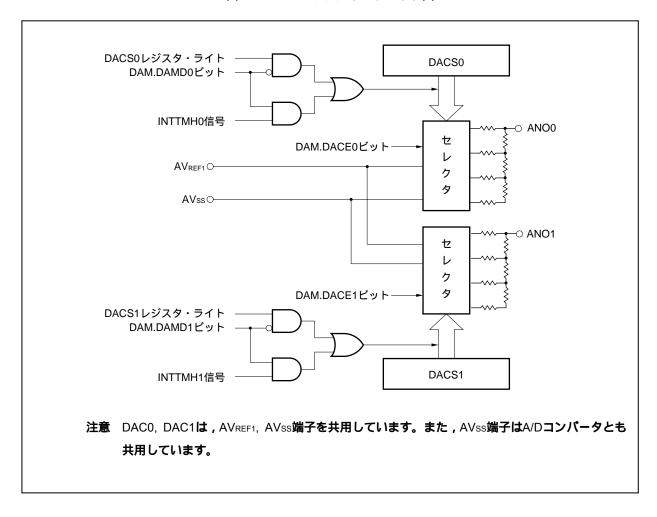

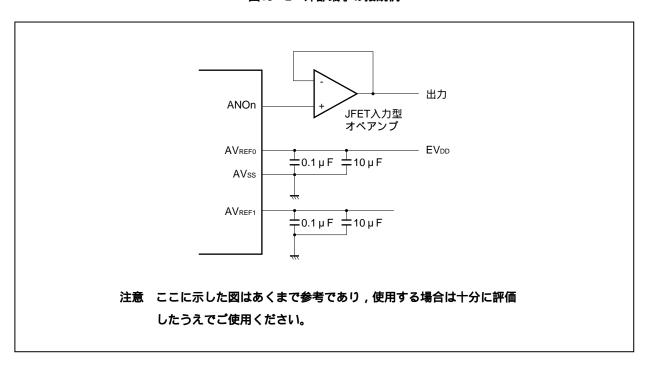

| 第15章                 | D/A <b>コンパータ</b> 501                         |

| 15 1                 | <b>機 能</b> 501                               |

|                      | 構 成 502                                      |

|                      | レジスタ 503                                     |

|                      | <b>動 作</b> 504                               |

|                      | 15. 4. 1 通常モード時の動作 504                       |

|                      | 15. 4. 2 リアルタイム出力モード時の動作 504                 |

|                      | 15. 4. 3 注意事項 505                            |

| <b>第</b> 16 <b>章</b> | アシンクロナス・シリアル・インタフェース(UART) 506               |

|                      |                                              |

| 16. 1                | UART2 <b>端子について</b> 506                      |

|                      | 16.1.1 UART2とCSI00のモード切り替え 507               |

| 40.0                 | 16. 1. 2 UART2とI <sup>2</sup> C1のモード切り替え 508 |

|                      | 特                                            |

|                      | <b>構 成</b> 510<br>レジスタ 512                   |

|                      | レンスタ 512<br>割り込み要求信号 521                     |

```

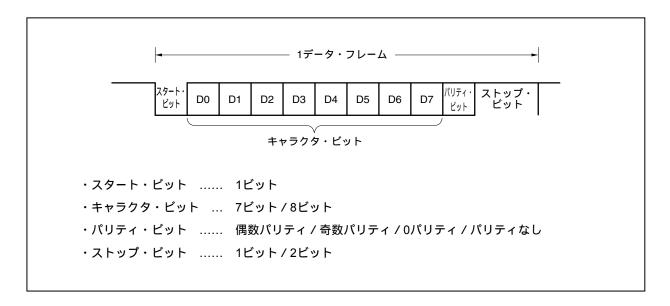

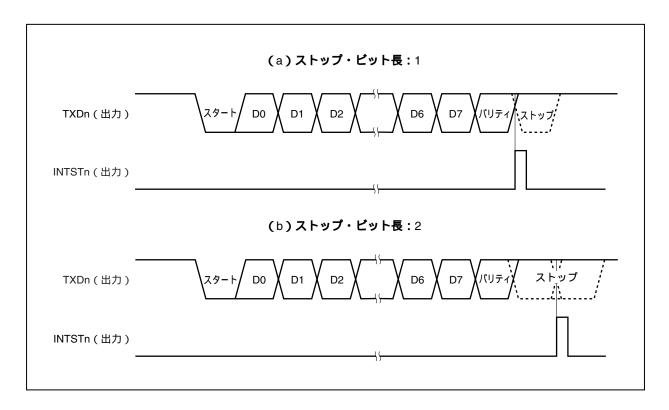

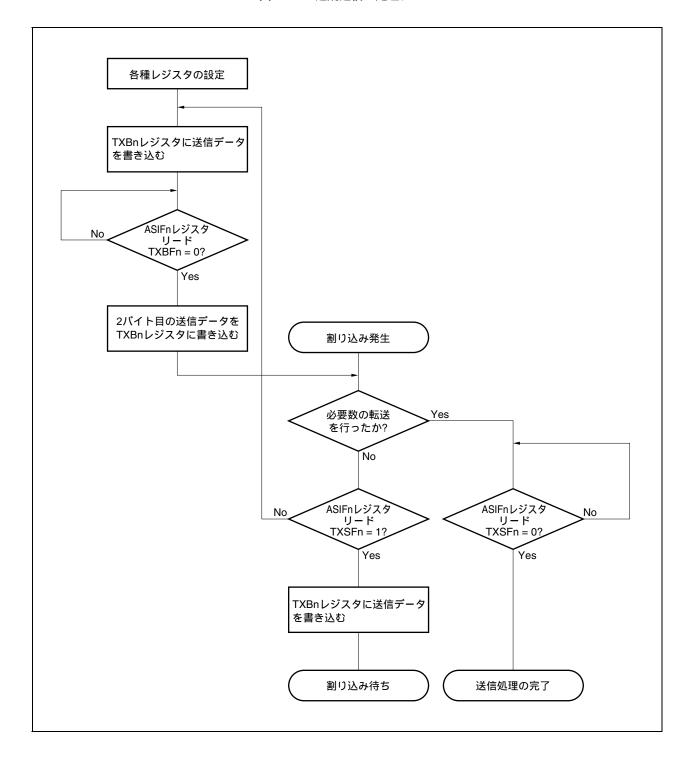

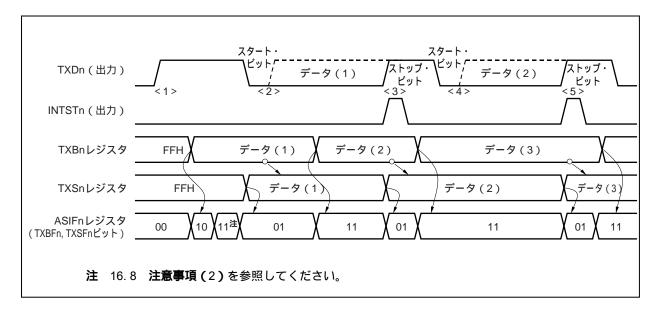

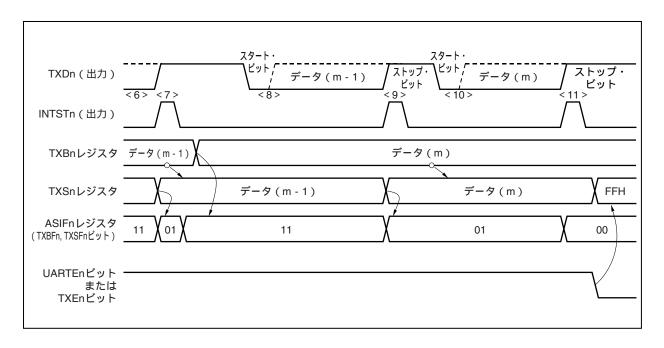

16.6 動作 ... 522

16.6.1 データ・フォーマット ... 522

16.6.2 送信動作 ... 523

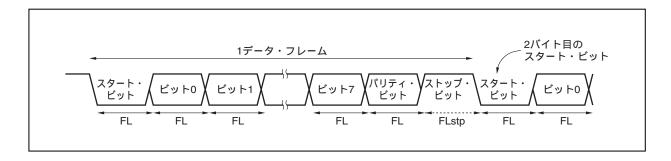

16.6.3 連続送信動作 ... 525

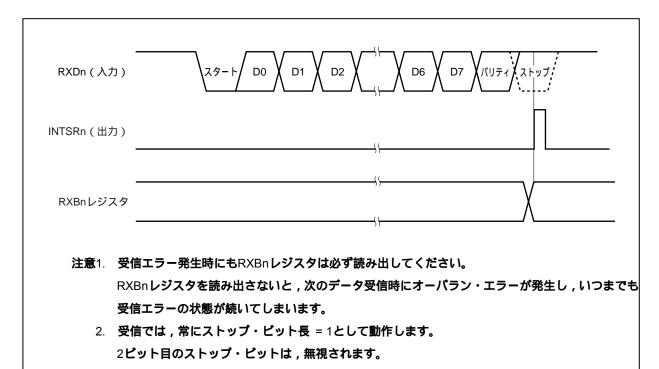

16.6.4 受信動作 ... 529

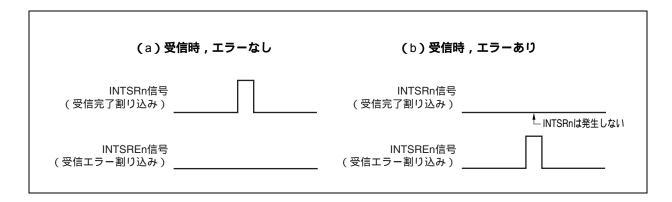

16.6.5 受信エラー ... 531

16.6.6 パリティの種類と動作 ... 532

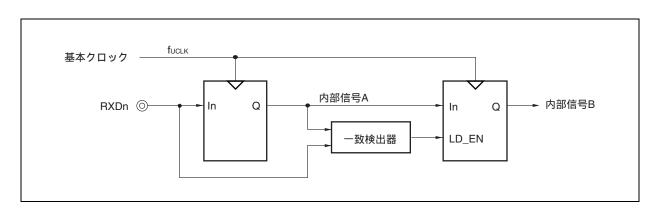

16.6.7 受信データのノイズ・フィルタ ... 533

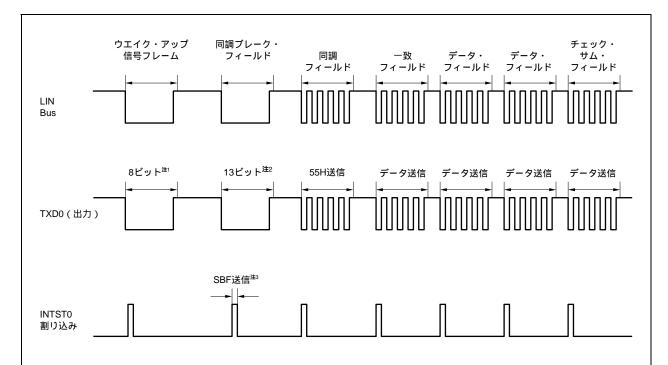

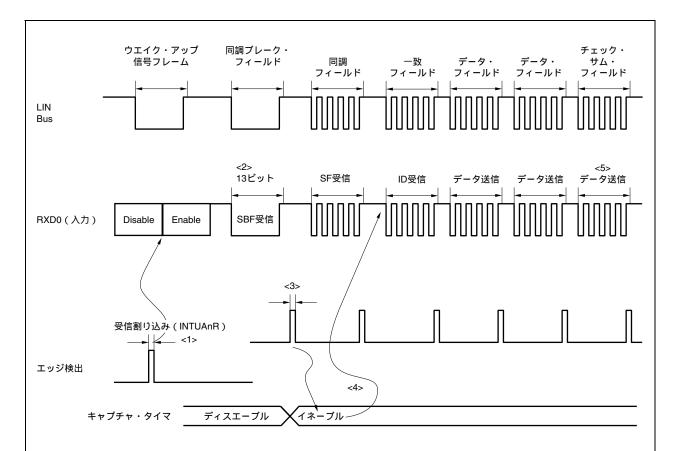

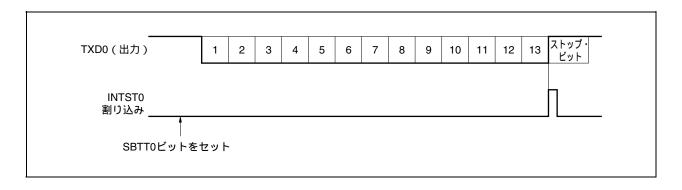

16.6.8 SBF送受信(UART0のみ) ... 534

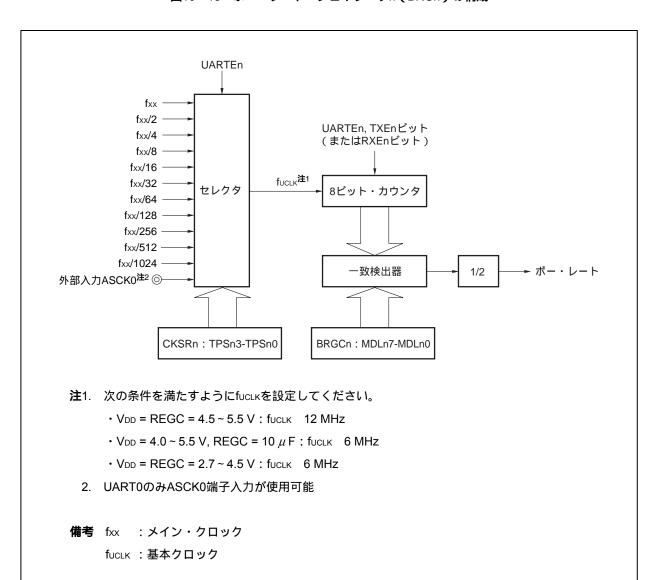

16.7 専用ボー・レート・ジェネレータn (BRGn) ... 539

16.7.1 ボー・レート・ジェネレータn (BRGn)の構成 ... 539

16.7.2 シリアル・クロックの生成 ... 540

16.7.3 ボー・レート設定例 ... 543

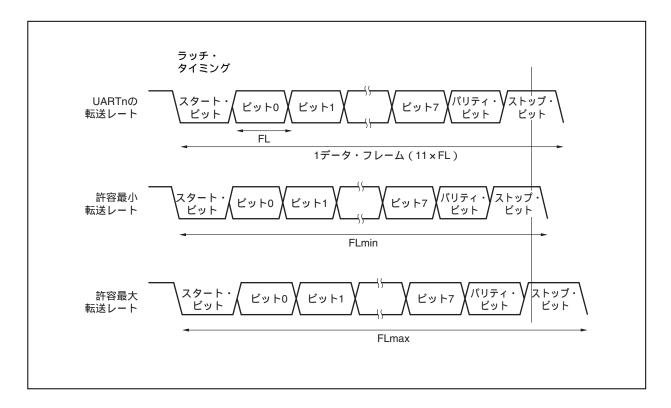

16.7.4 受信時の許容ボー・レート範囲 ... 544

16.7.5 連続送信時の転送レート ... 546

16.8 注意事項 ... 546

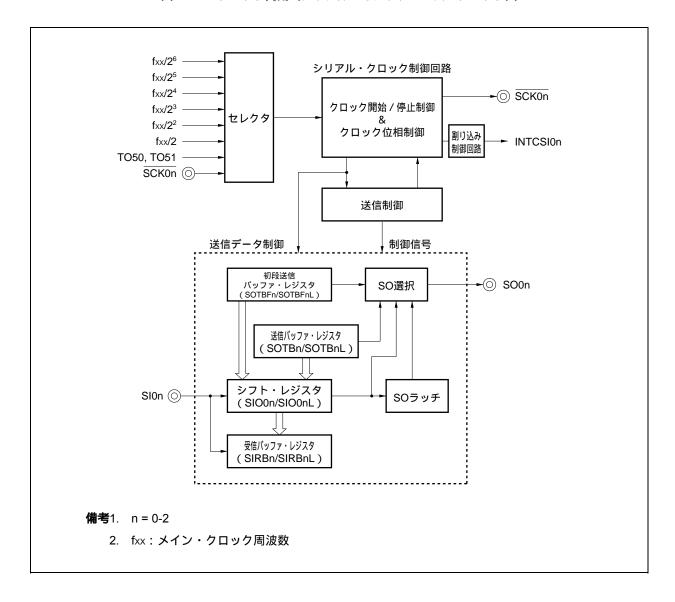

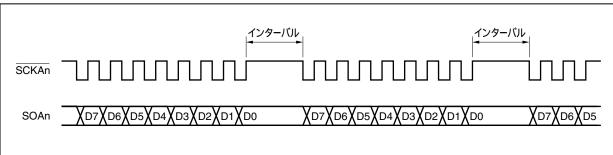

第17章 クロック同期式シリアル・インタフェース0 ( CSIO ) ... 547

17.1 特 徵 ... 547

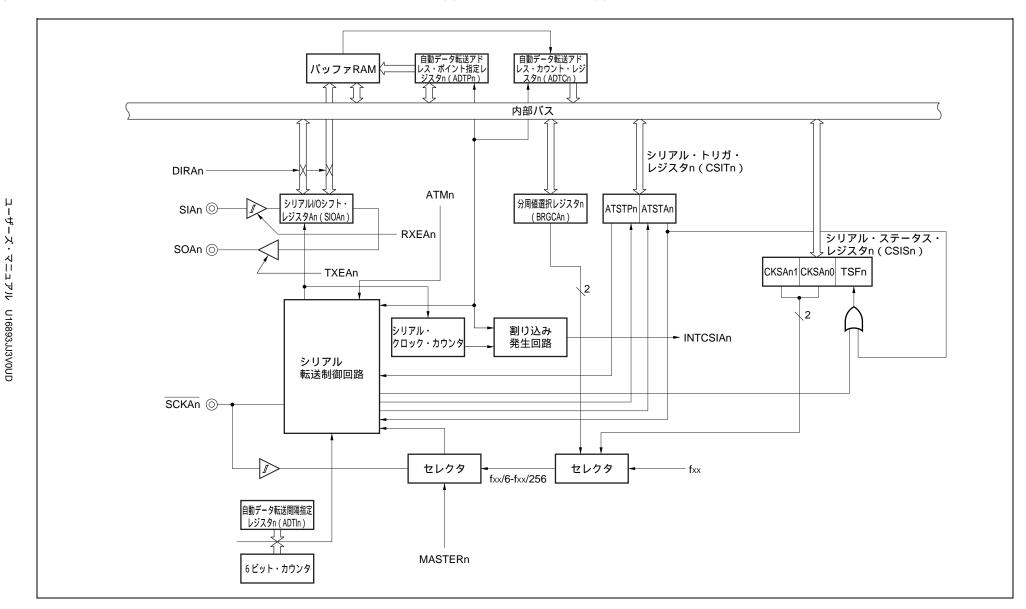

17.2 構 成 ... 548

17.3 レジスタ ... 551

17.4 動作... 560

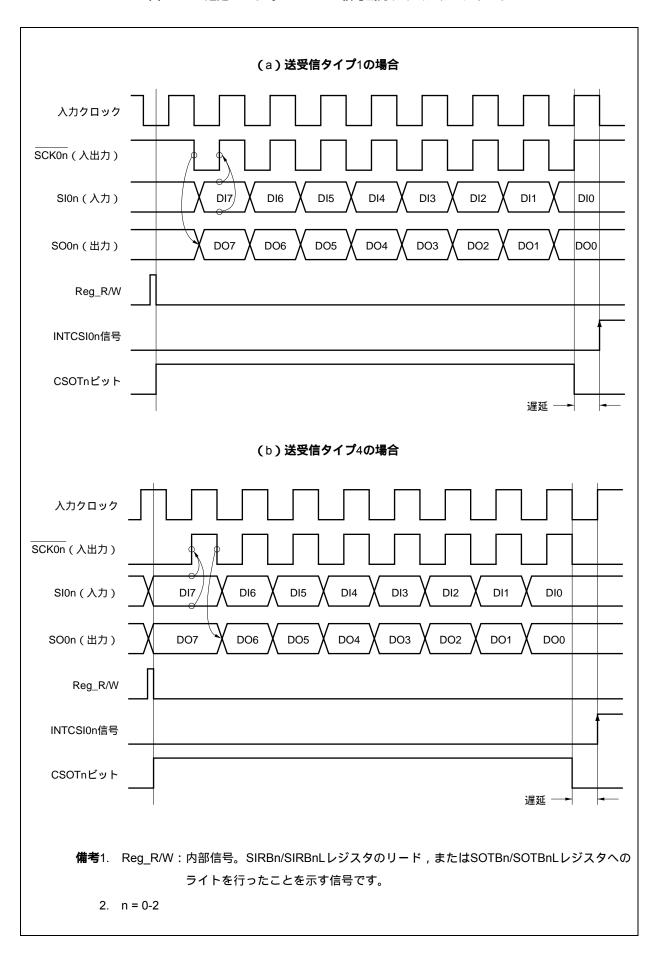

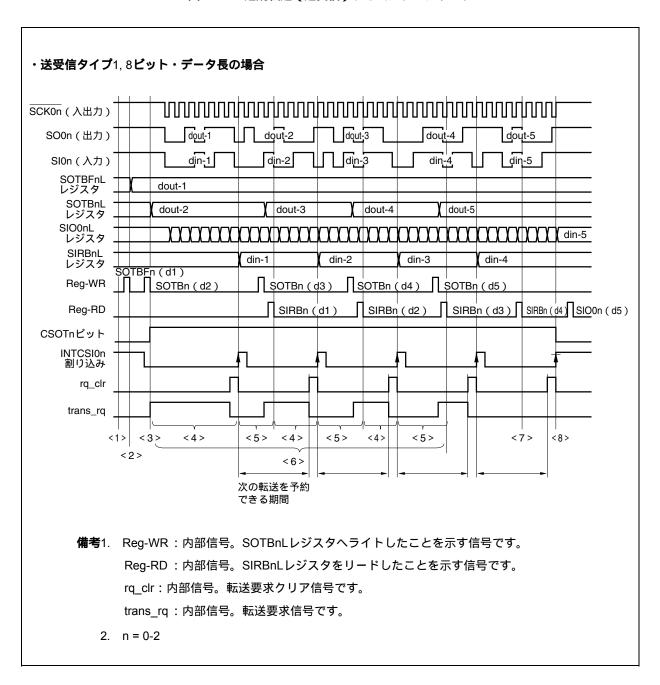

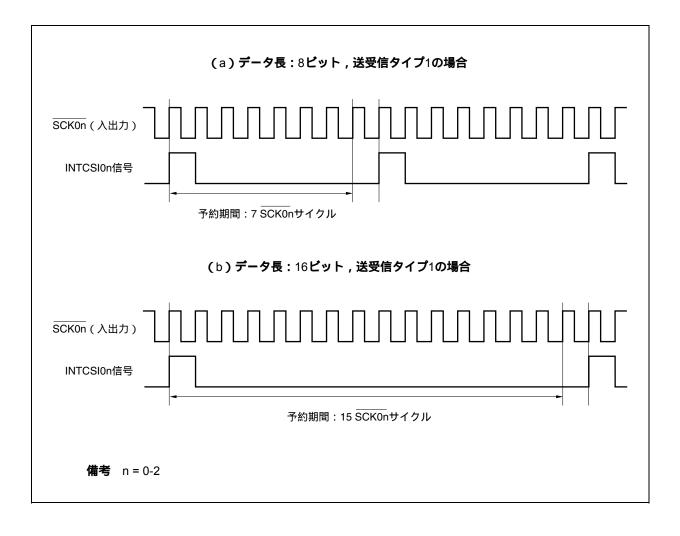

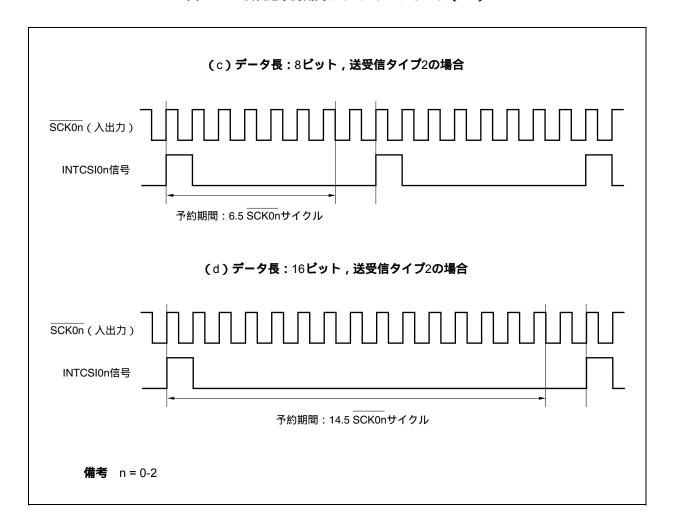

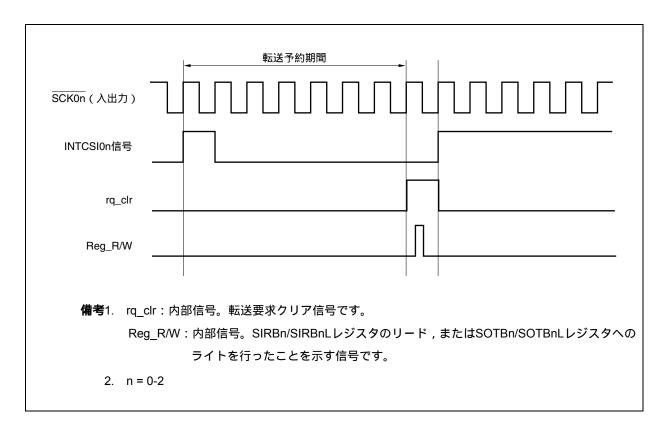

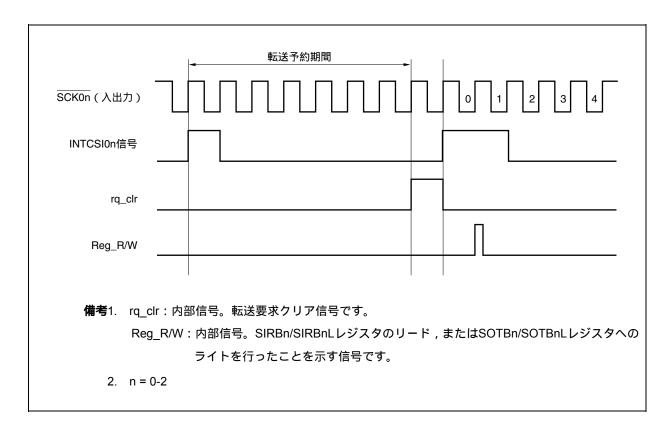

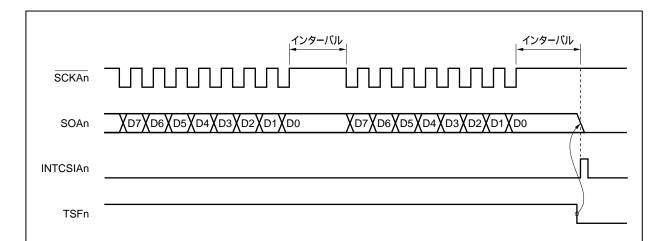

17.4.1 送受信完了割り込み要求信号(INTCSIOn) ... 560

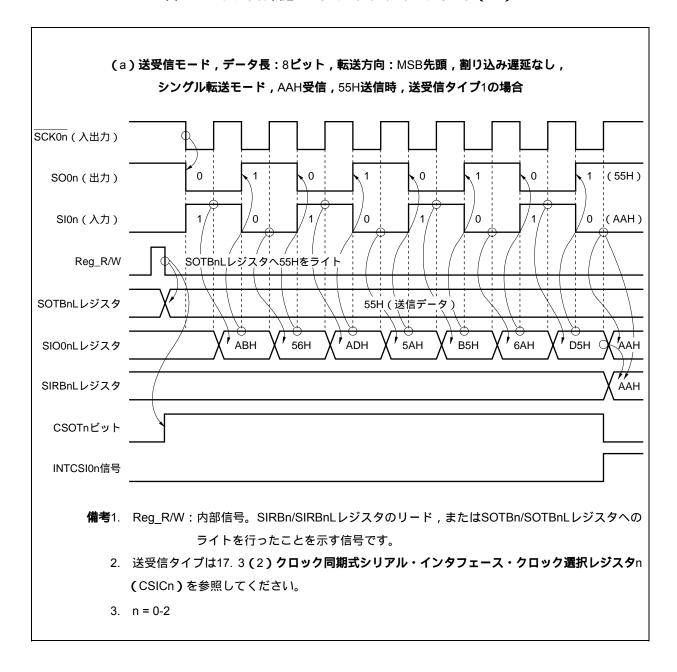

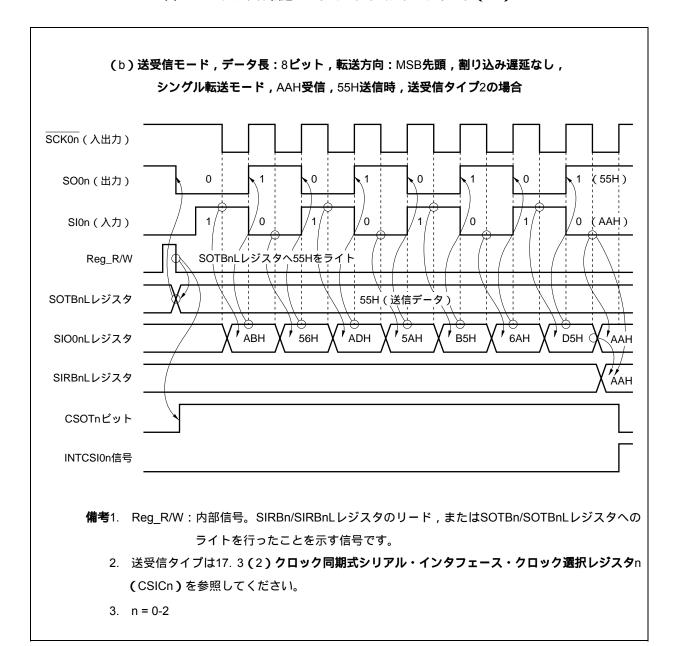

17.4.2 シングル転送モード ... 562

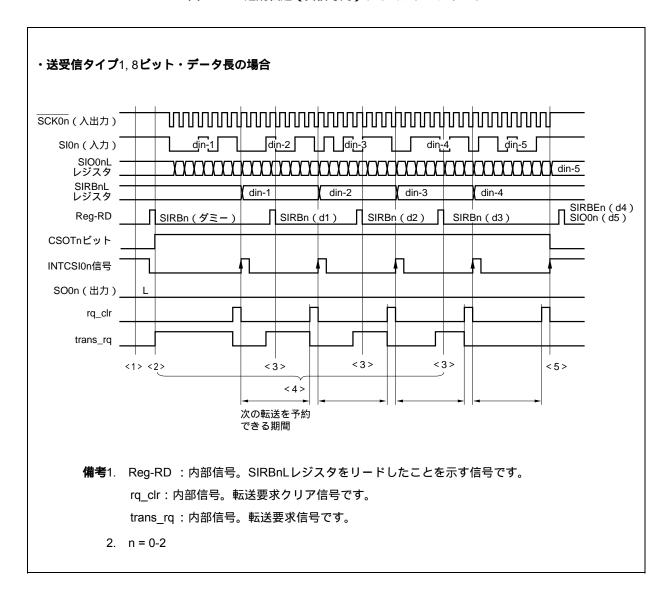

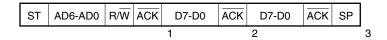

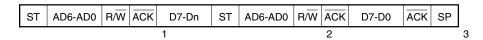

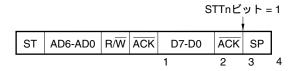

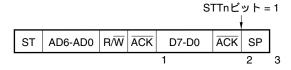

17.4.3 連続転送モード ... 565

17.5 出力端子 ... 573

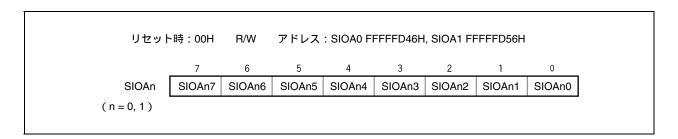

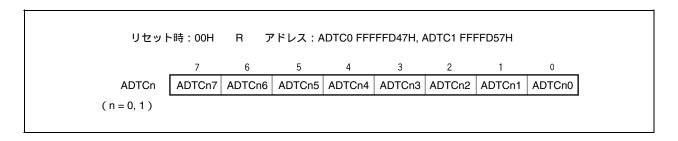

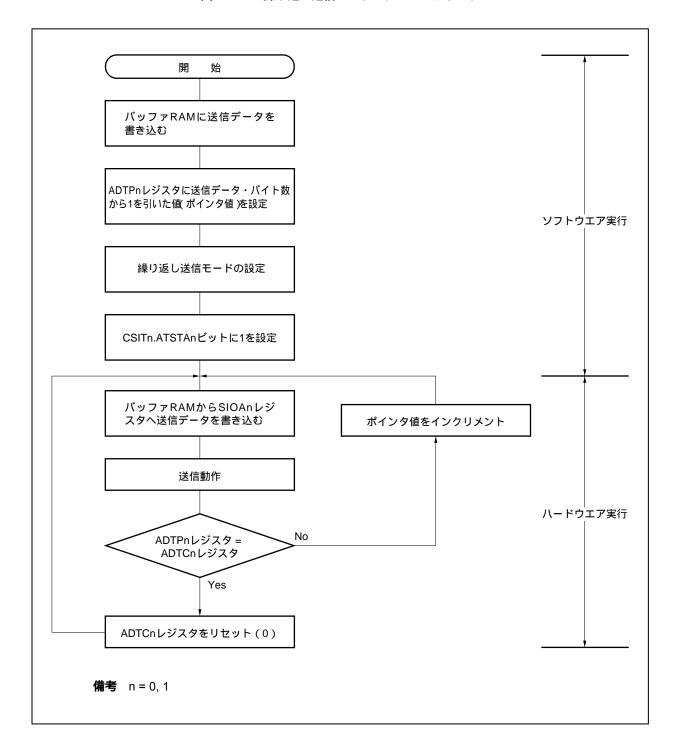

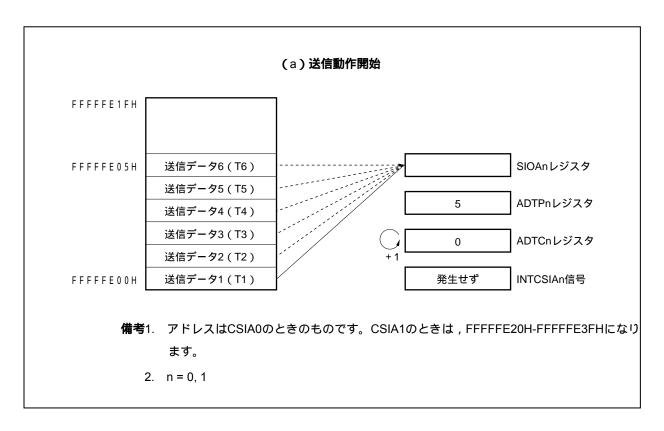

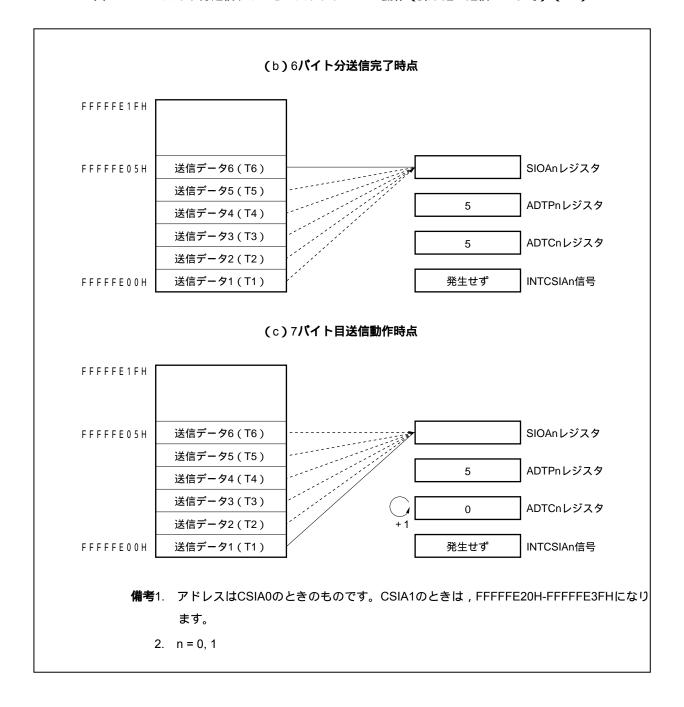

第18章 自動送受信機能付きクロック同期式シリアル・インタフェースA(CSIA) ... 574

18.1 機 能 ... 574

18.2 構

成 ... 575

18.3 レジスタ ... 578

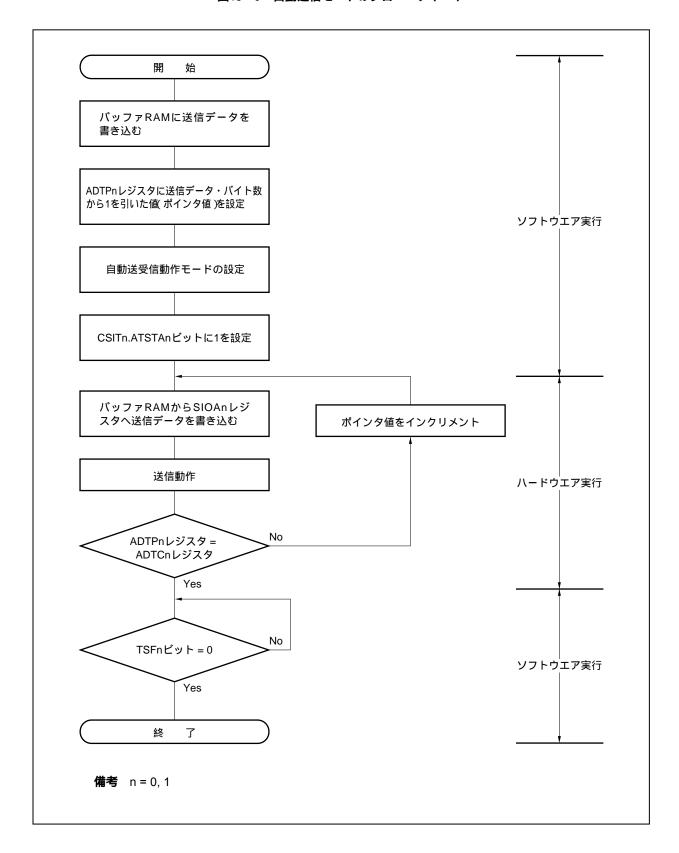

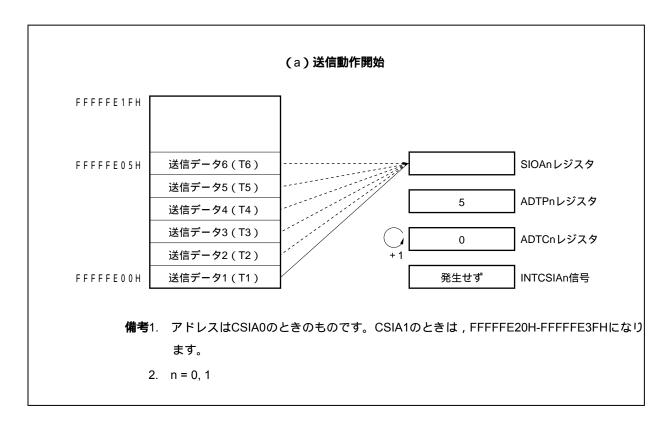

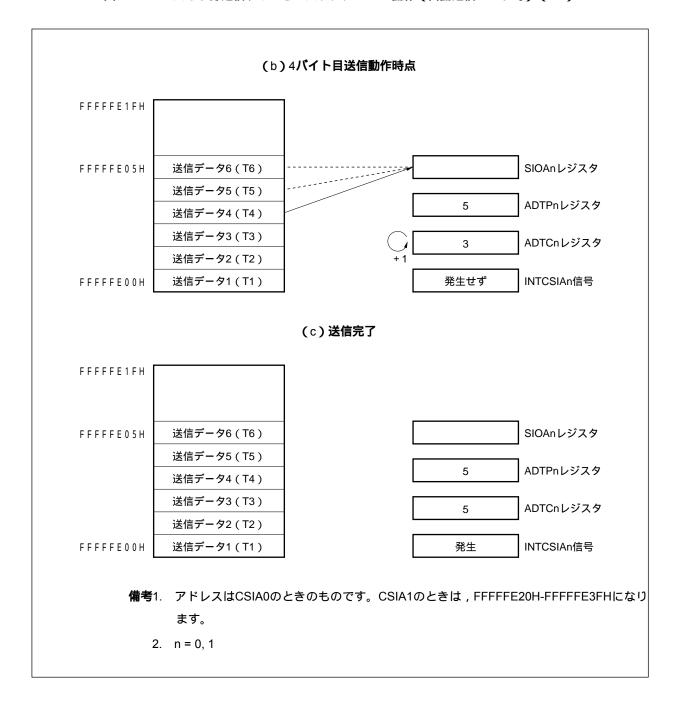

18.4 動作 ... 588

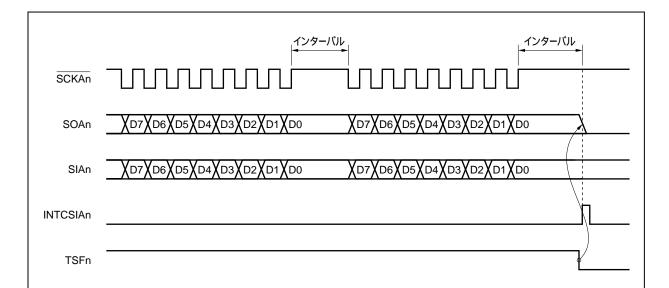

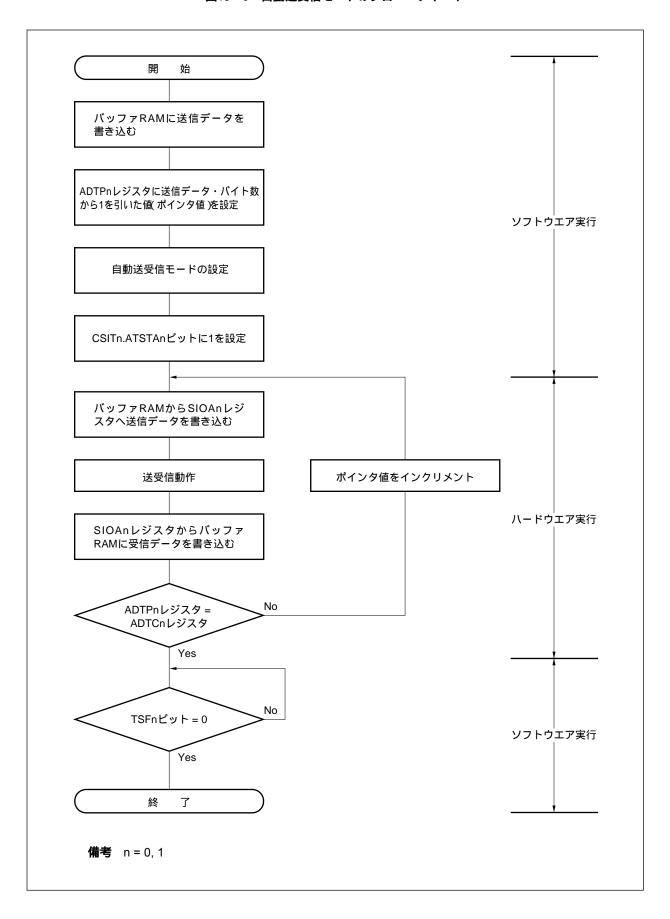

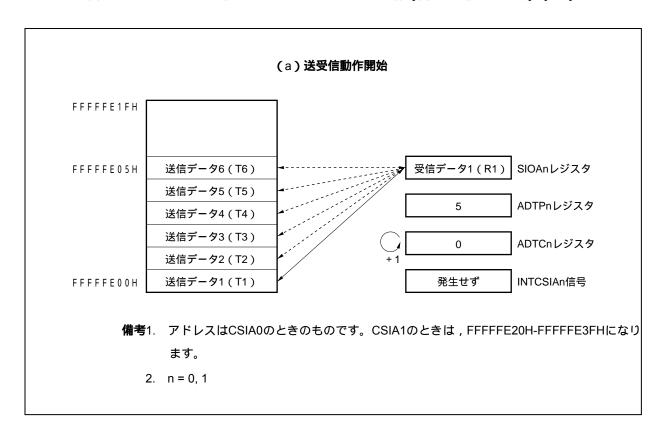

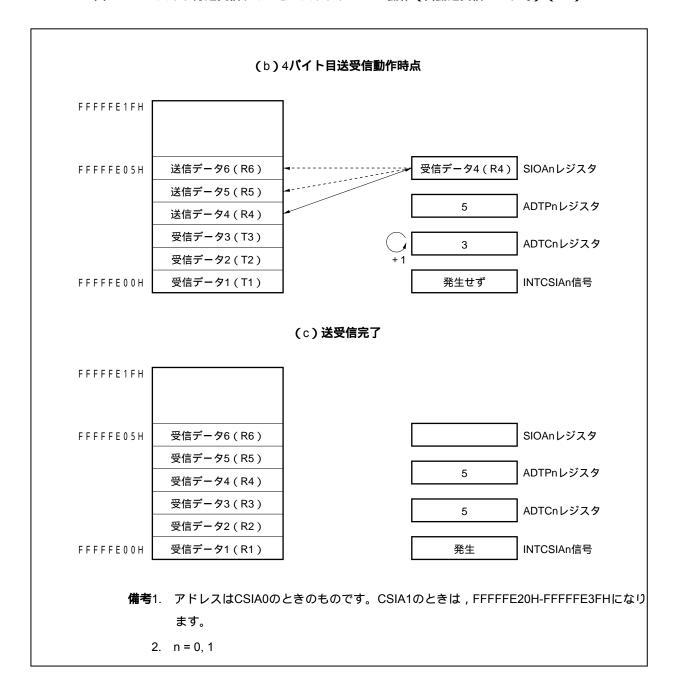

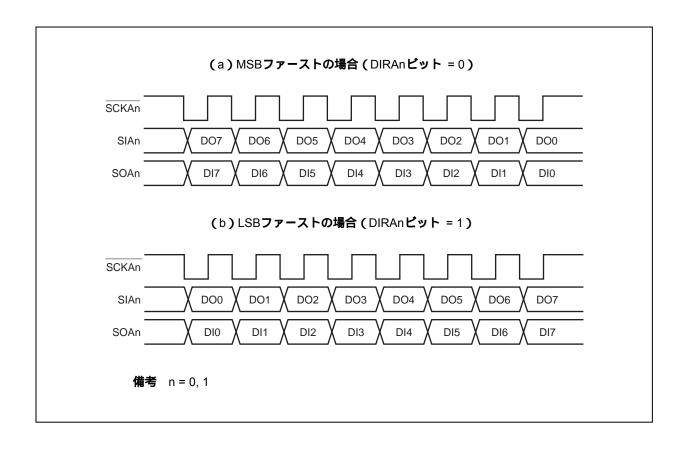

18.4.1 3線式シリアルI/Oモード ... 588

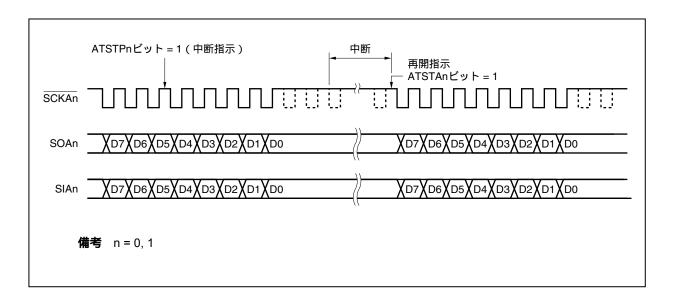

18.4.2 自動送受信機能付き3線式シリアルI/Oモード ... 592

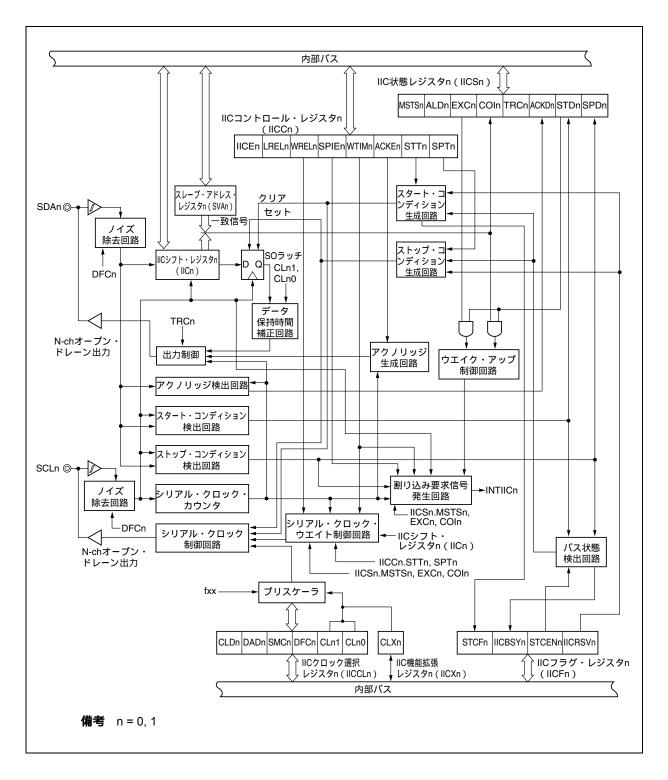

第19章 I<sup>2</sup>Cバス ... 609

19.1 UART2とI<sup>2</sup>C1のモード切り替え ... 609

19.2 特 徵 ... 610

成 ... 613

19.3 構

19.4 レジスタ ... 615

19.5 機 能 ... 629

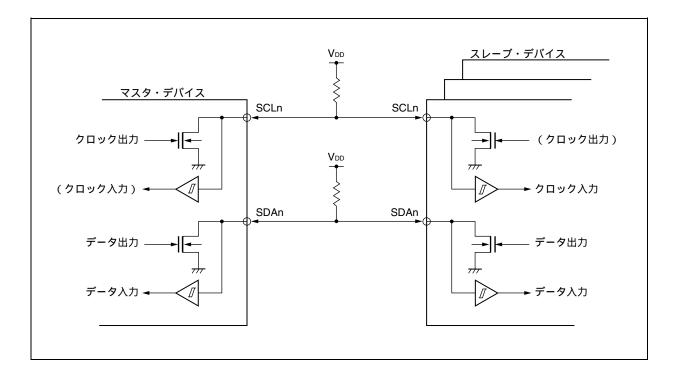

19.5.1 端子構成 ... 629

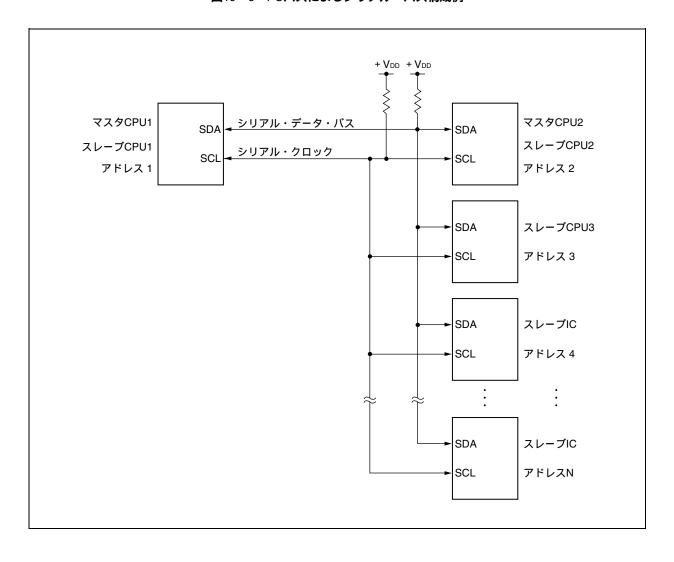

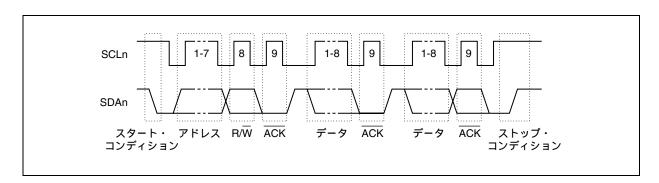

19.6 I<sup>2</sup>Cバスの定義および制御方法 ... 630

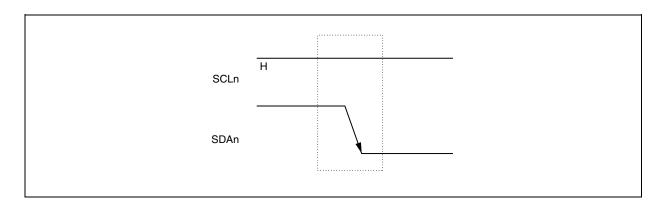

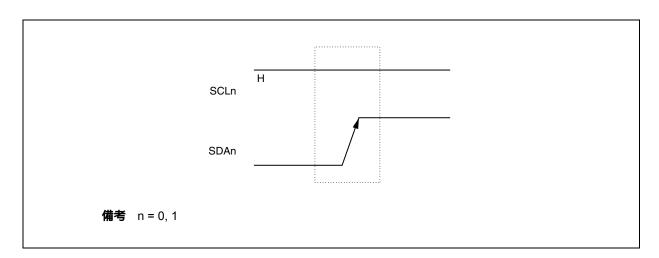

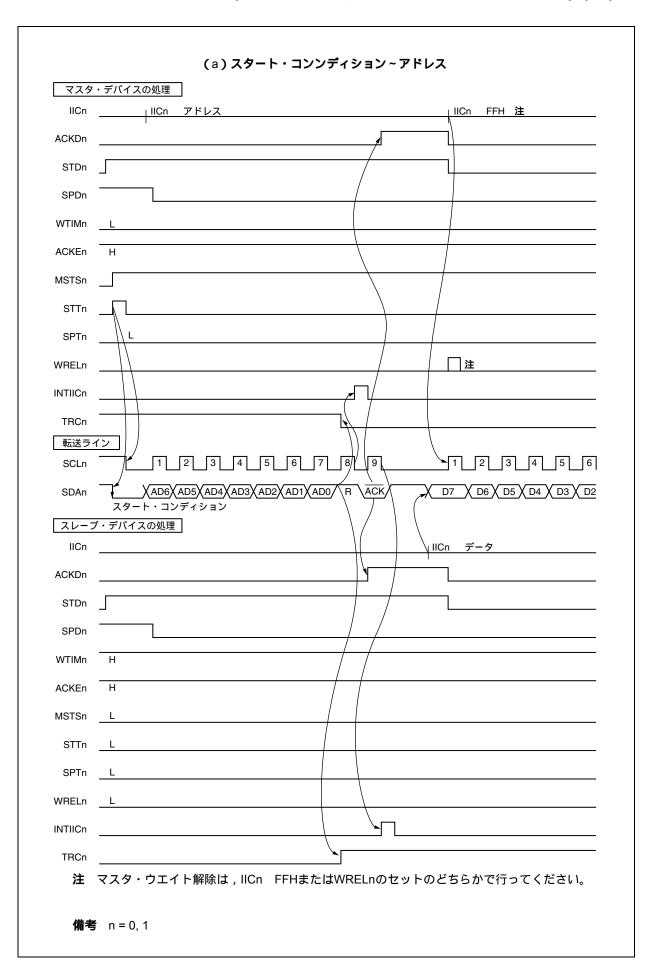

19.6.1 スタート・コンディション ... 630

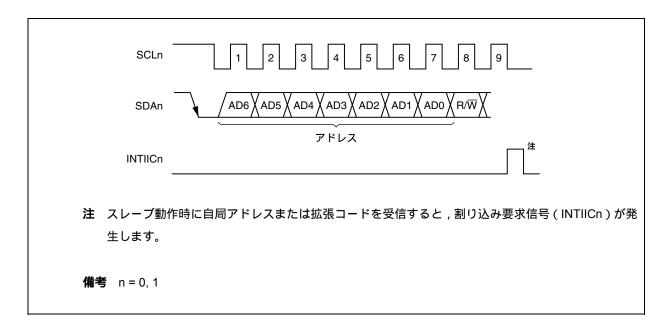

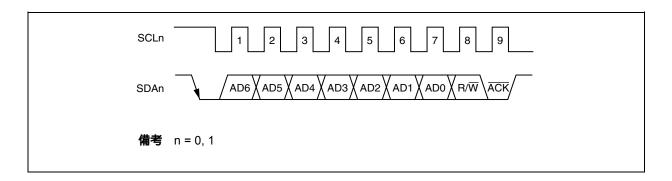

19.6.2 アドレス ... 631

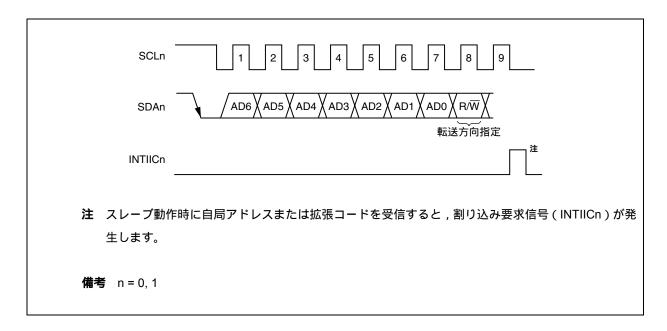

19.6.3 転送方向指定 ... 632

```

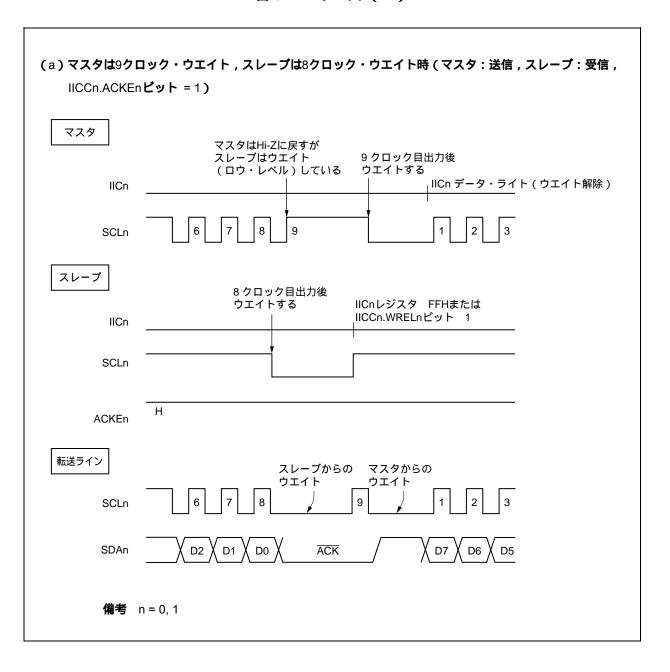

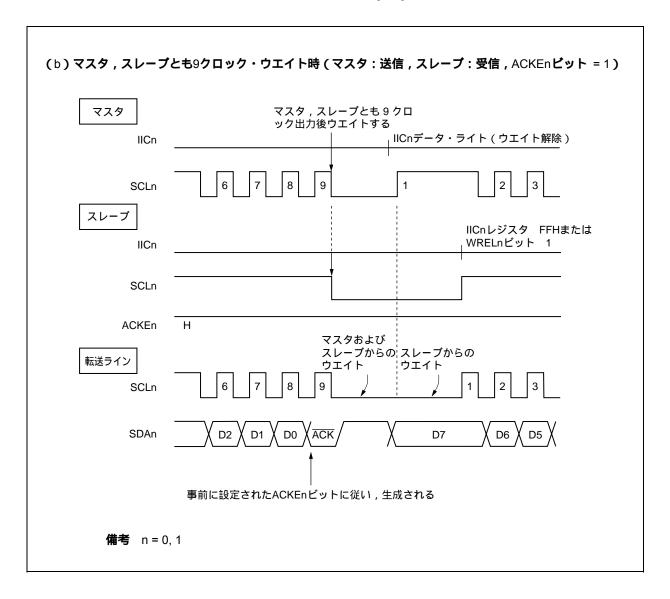

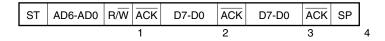

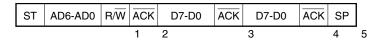

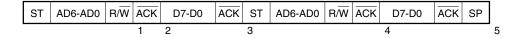

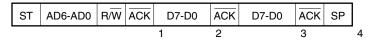

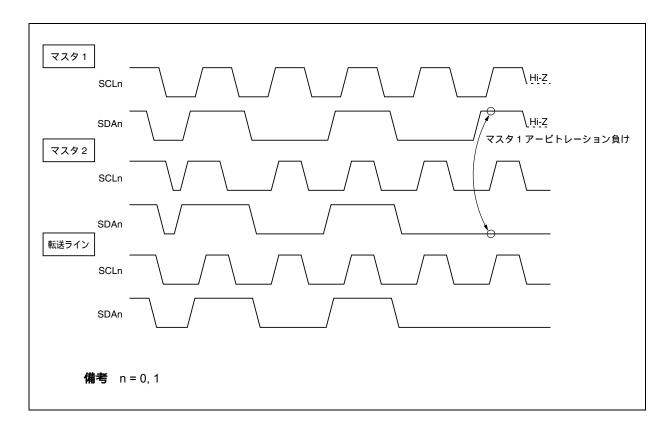

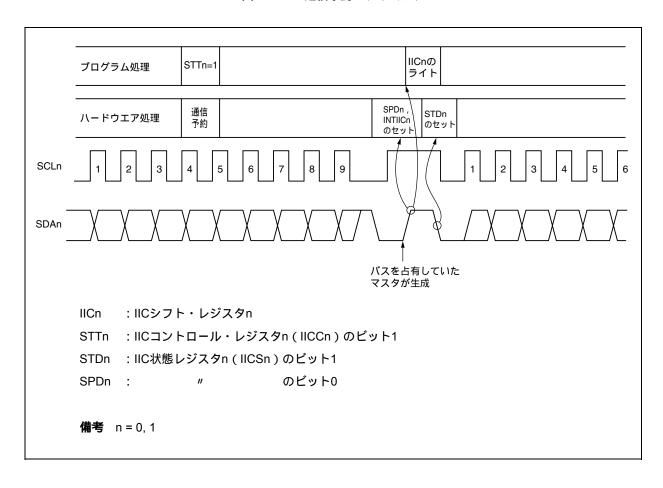

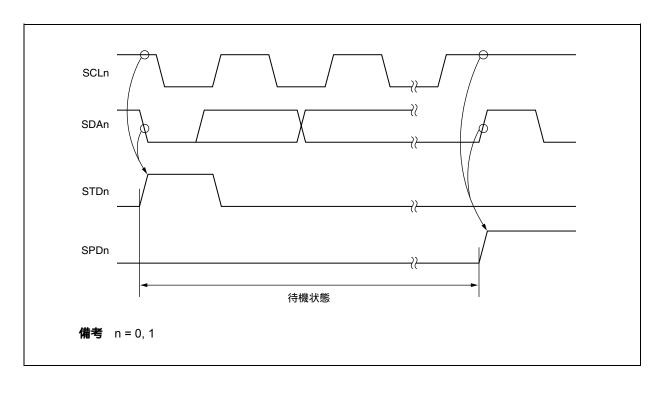

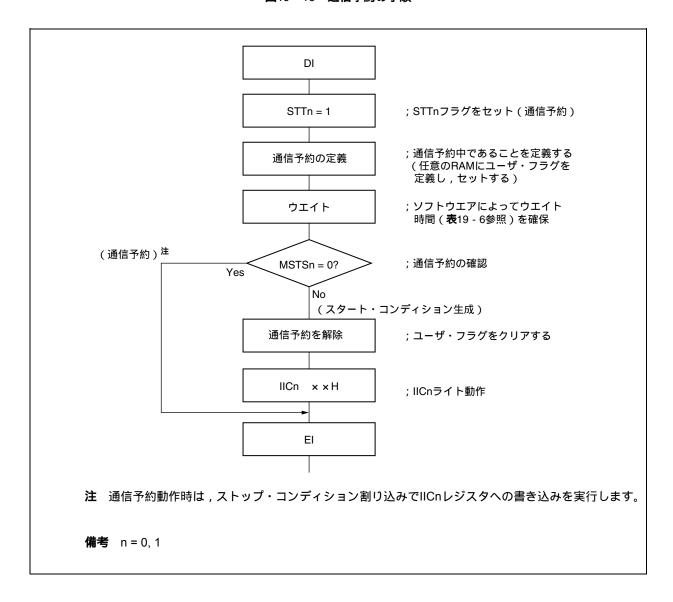

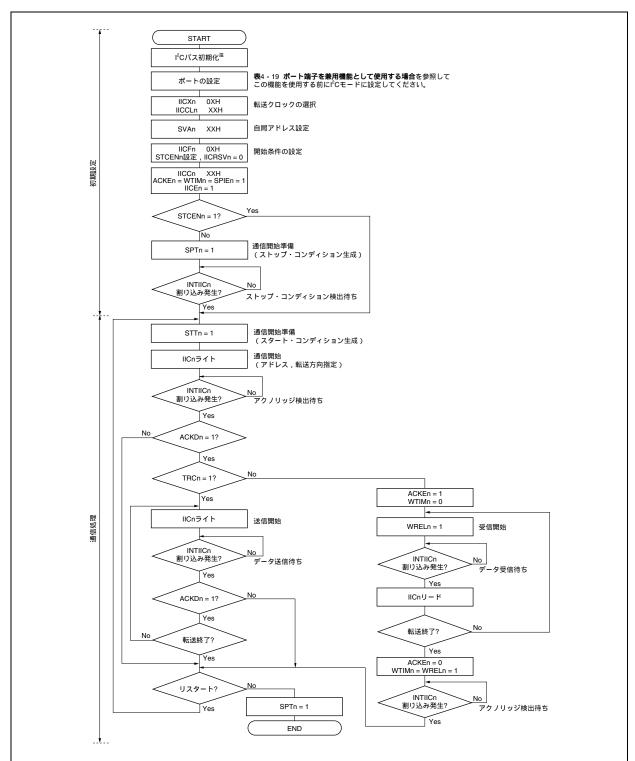

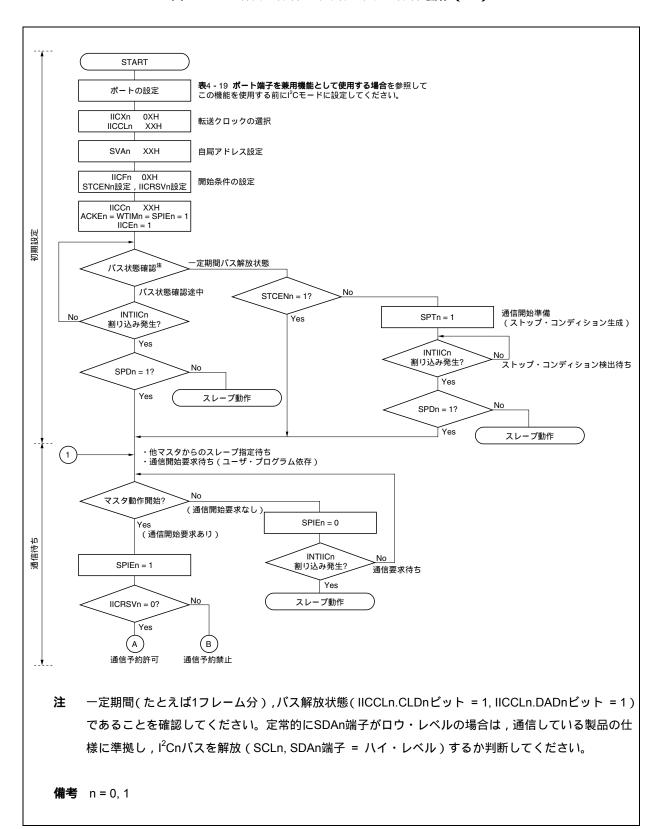

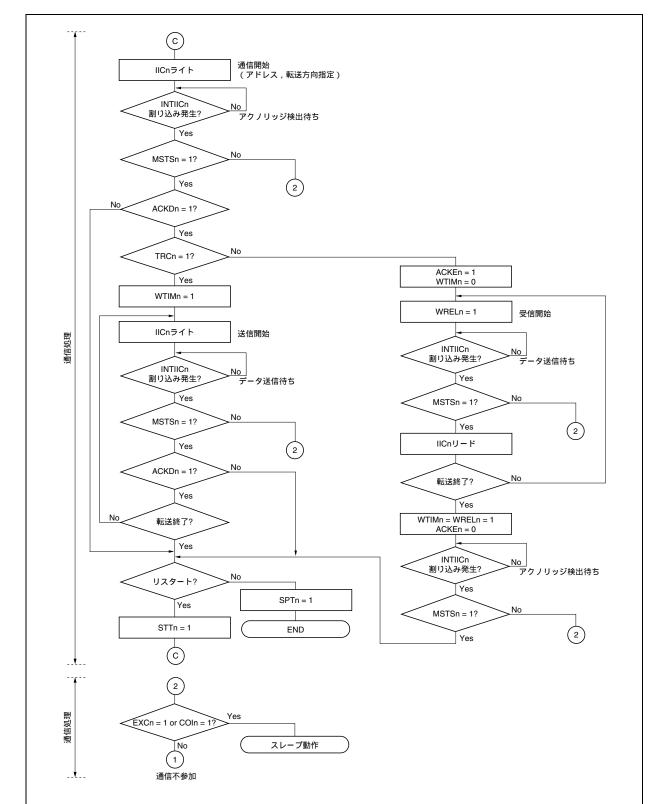

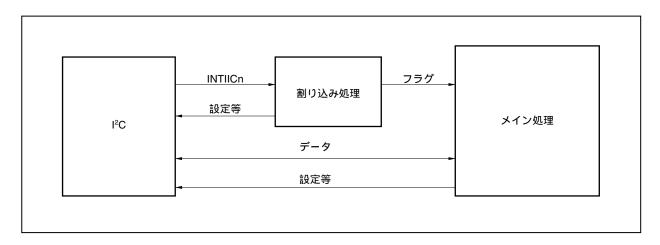

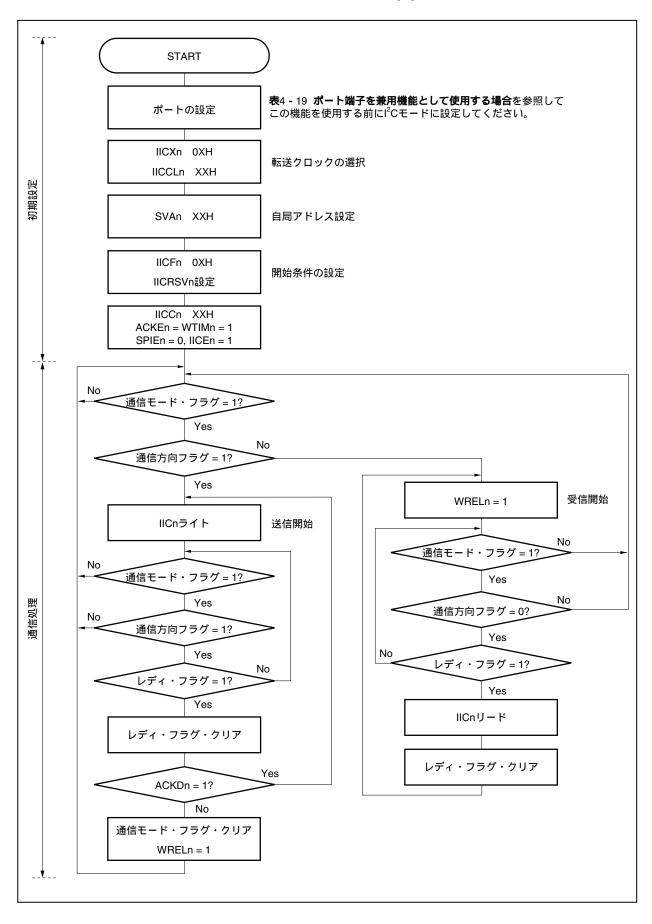

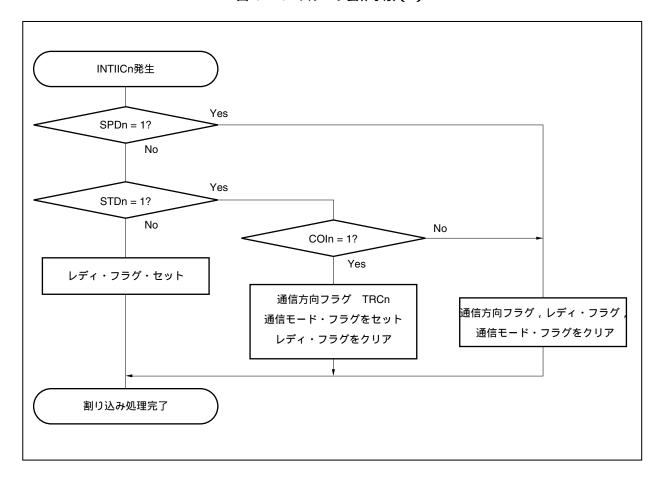

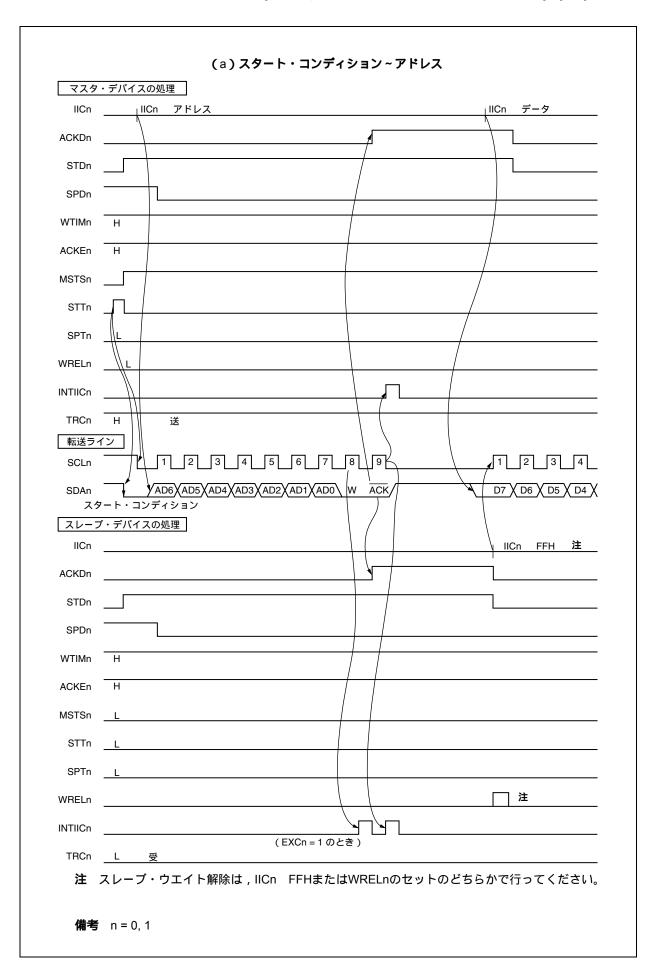

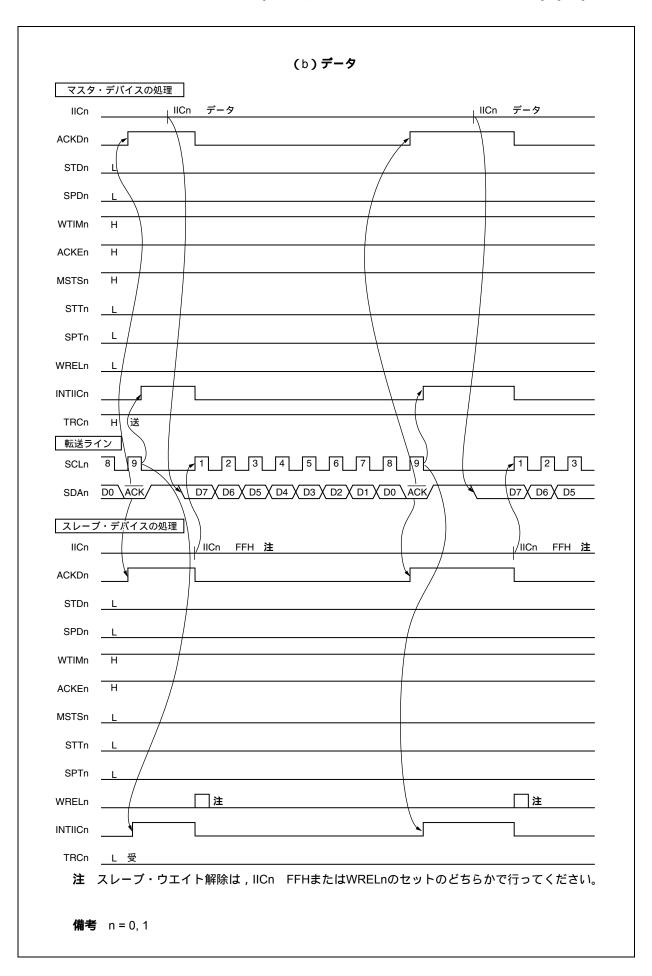

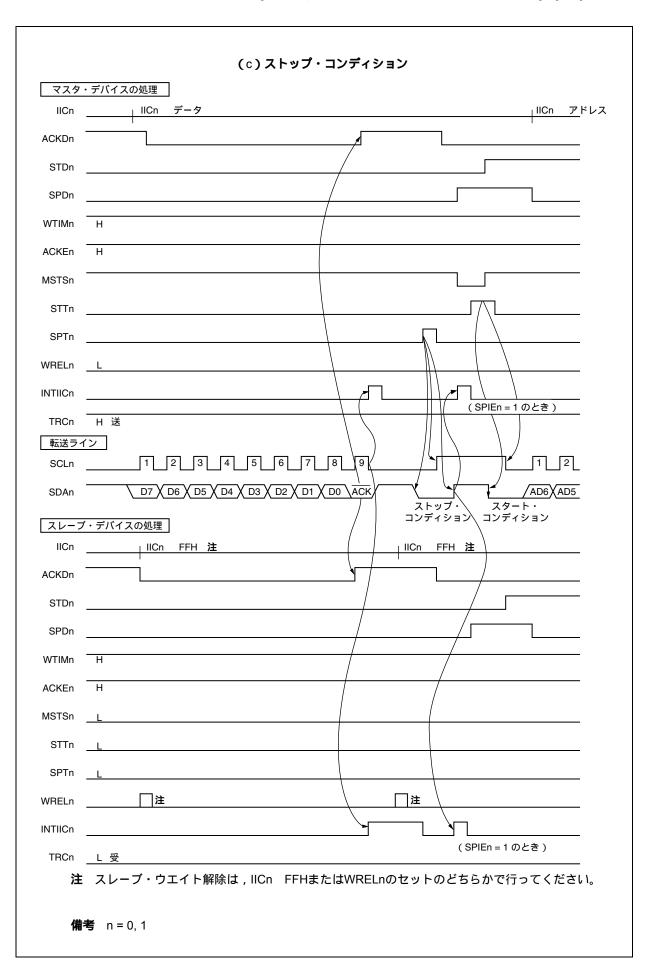

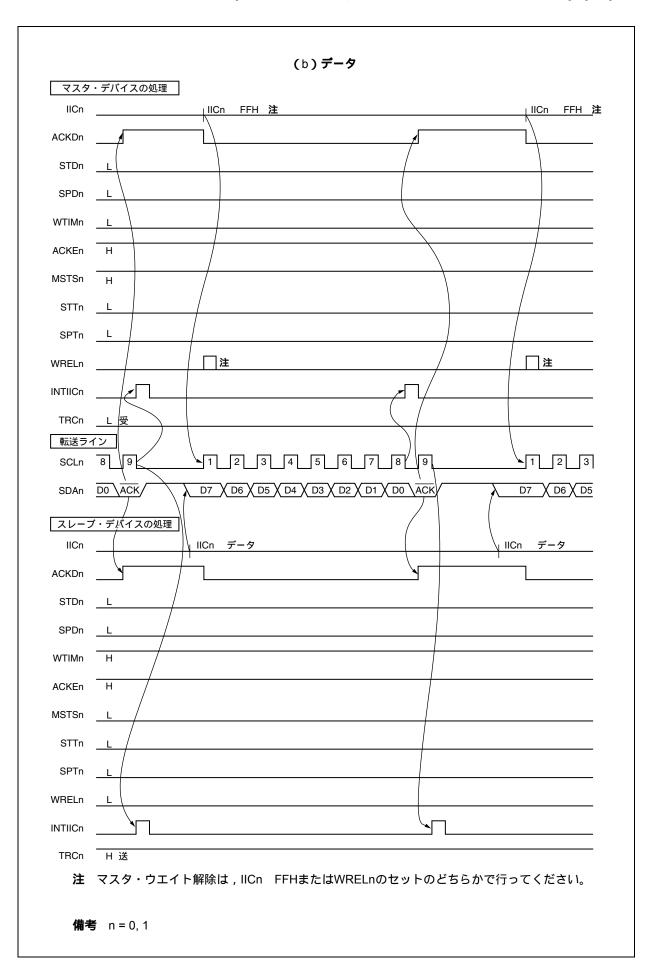

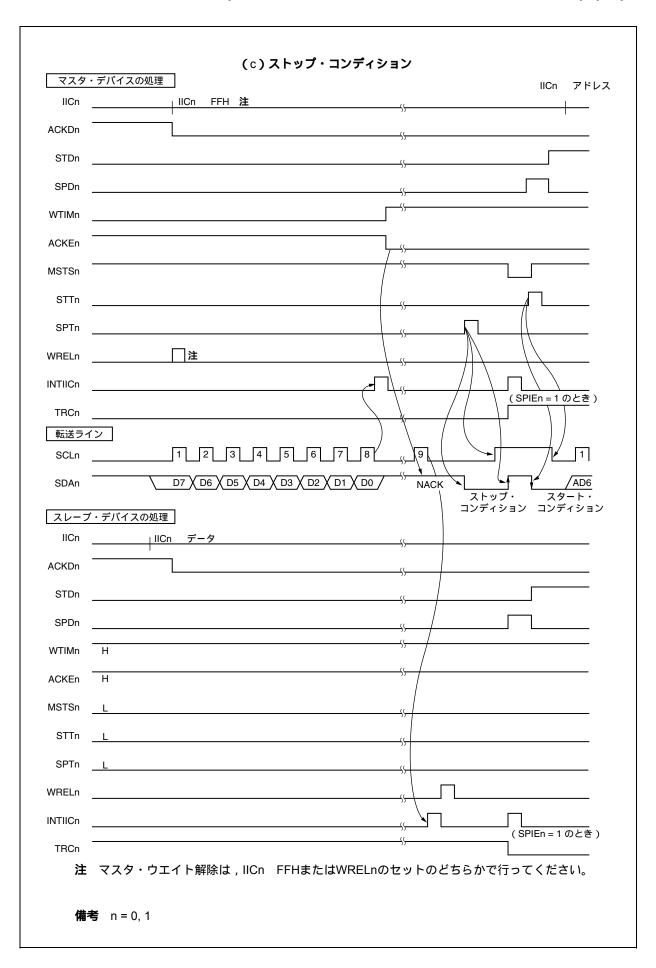

19.6.6 ウエイト ... 635 19.6.7 ウエイト解除方法 ... 637 19.7 I<sup>2</sup>C割り込み要求信号(INTIICn) ... 638 19.7.1 マスタ動作 ... 639 19.7.2 スレーブ動作(スレーブ・アドレス受信時(アドレス一致)) ... 642 19.7.3 スレーブ動作(拡張コード受信時) ... 646 19.7.4 通信不参加の動作 ... 650 19.7.5 アービトレーション負けの動作(アービトレーション負けのあと,スレーブとし て動作) ... 651 19.7.6 アービトレーション負けの動作(アービトレーション負けのあと,不参加) 19.8 **割り込み要求信号 (INTIICn) 発生タイミングおよびウエイト制御** ... 660 19.9 アドレスの一致検出方法 ... 661 19.10 エラーの検出 ... 661 19.11 拡張コード ... 662 19. 12 **アービトレーション** ... 663 19.13 ウエイク・アップ機能 ... 664 19.14 **通信予約** ... 665 19.14.1 通信予約機能許可の場合(IICFn.IICRSVnビット = 0) ... 665 19.14.2 通信予約機能禁止の場合(IICFn.IICRSVnビット = 1) ... 668 19.15 注意事項 ... 669 19.16 通信動作 ... 670 19. 16. 1 シングルマスタ・システムでのマスタ動作 ... 671

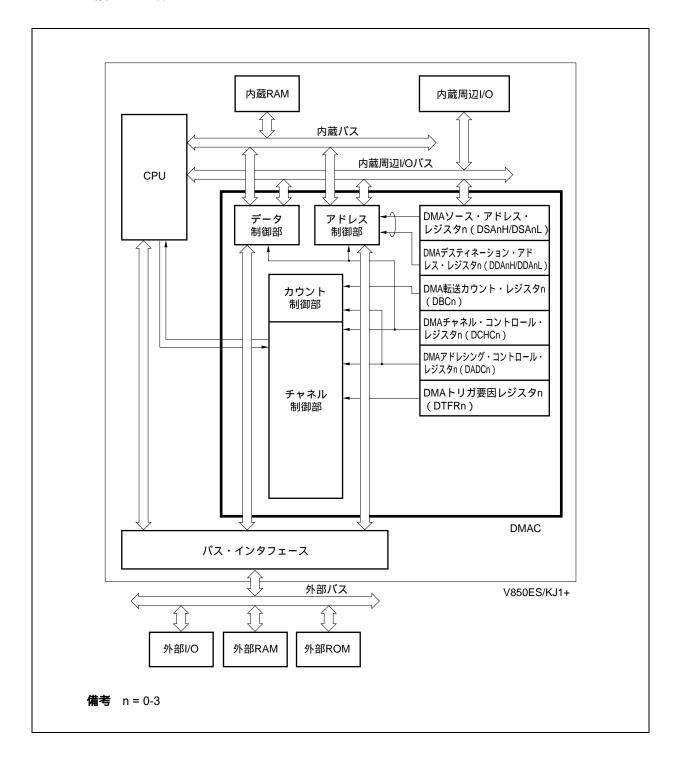

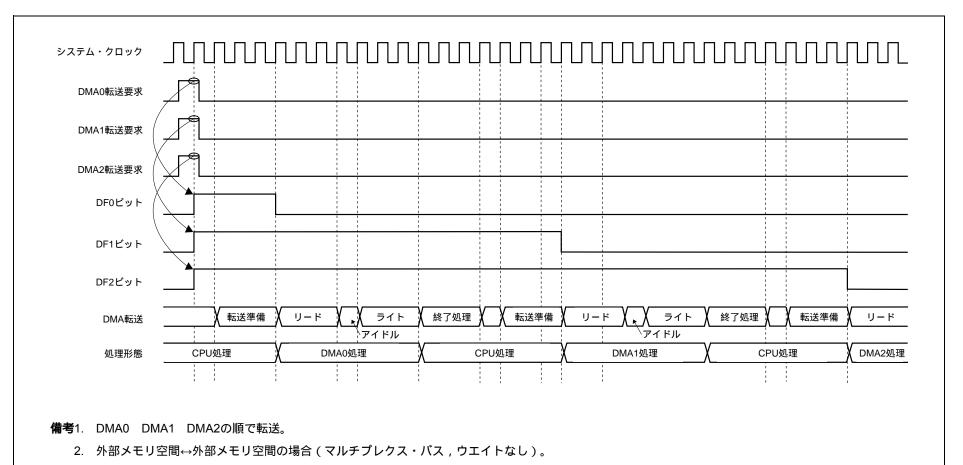

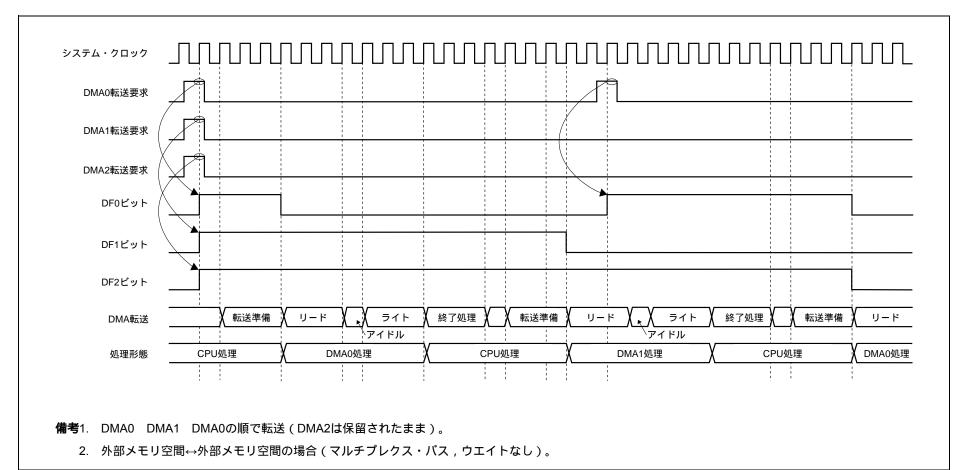

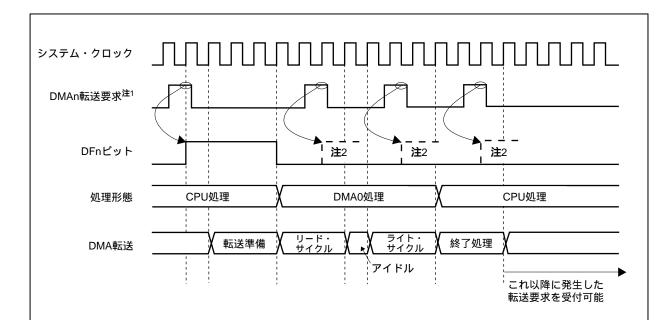

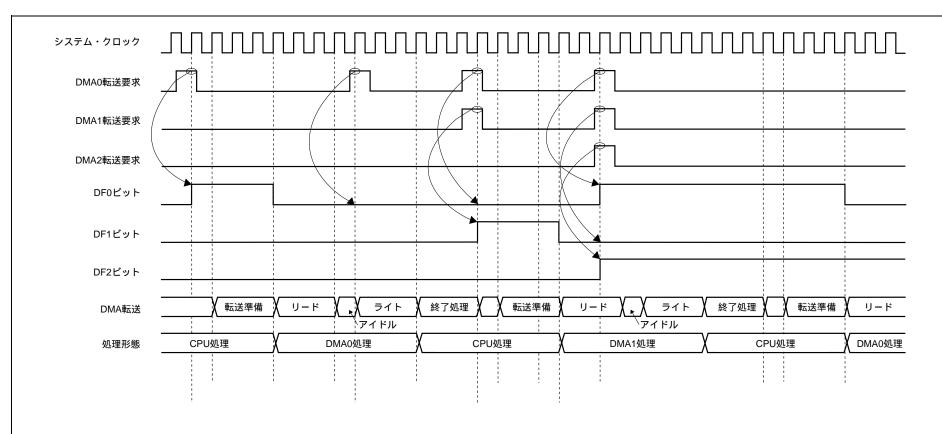

#### 第20章 DMA機能(DMAコントローラ) ... 686

19. 16. 3 スレーブ動作 ... 675 19. 17 **データ通信のタイミング** ... 679

19. 16. 2 マルチマスタ・システムでのマスタ動作 ... 672

19. 6. 4 アクノリッジ(ACK) ... 633 19. 6. 5 ストップ・コンディション ... 634

- 20.1 特 徵 ... 686

- 20.2 構 成 ... 687

- 20.3 レジスタ ... 688

- 20.4 転送対象 ... 696

- 20.5 転送モード ... 696

- 20.6 転送タイプ ... 697

- 20.7 DMA **チャネルの優先順位** ... 697

- 20.8 DMA転送に関する各種時間 ... 698

- 20.9 DMA**転送起動要因** ... 699

- 20.10 DMA**の中断要因** ... 700

- 20.11 DMA**転送の終了** ... 700

- 20.12 動作タイミング ... 700

- 20.13 注意事項 ... 705

#### 第21章 割り込み/例外処理機能 ... 709

21.1 概 要 ... 709

21.1.1 特 徴 ... 709

```

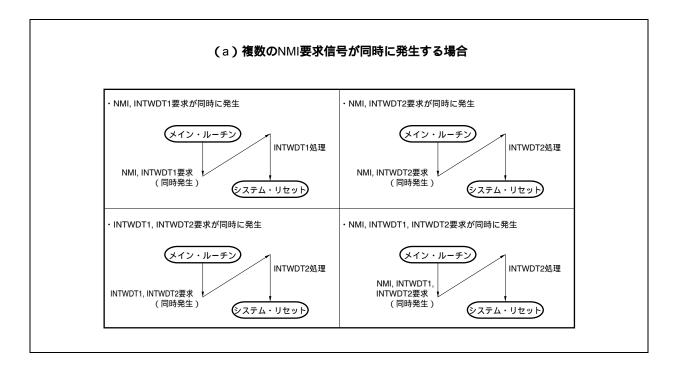

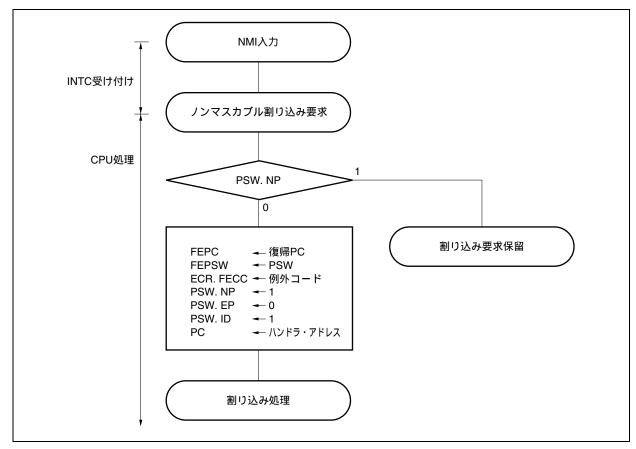

21.2 ノンマスカブル割り込み ... 713

21.2.1 動 作 ... 716

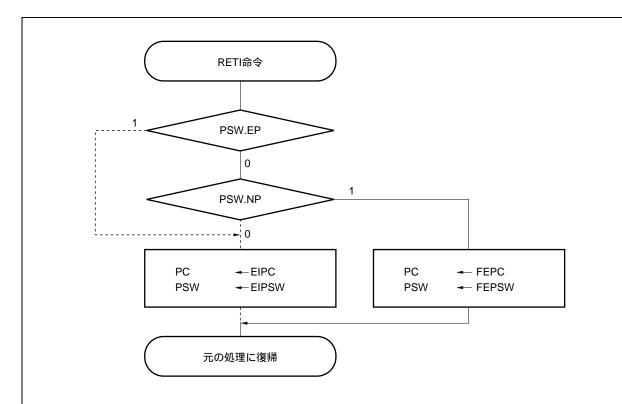

21. 2. 2 復

帰 ... 717

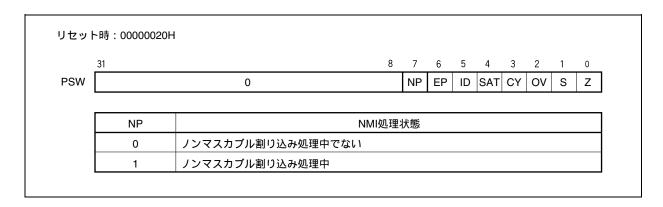

21.2.3 NPフラグ ... 718

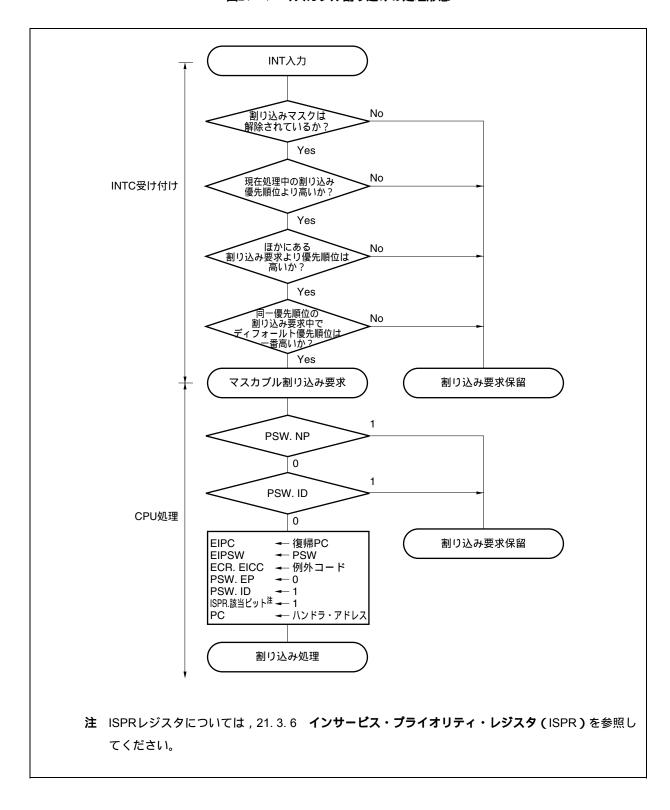

21.3 マスカブル割り込み ... 719

21.3.1 動

作 ... 719

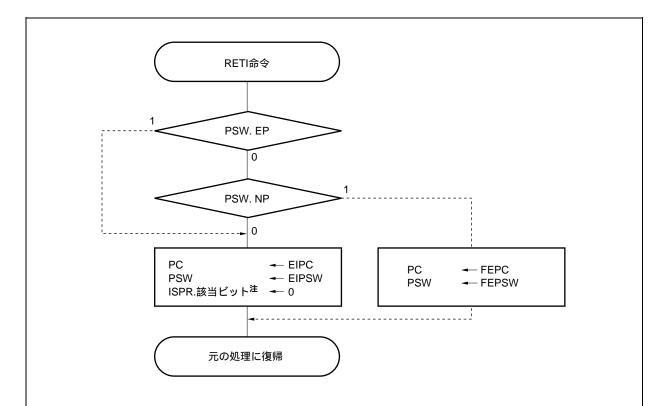

帰 ... 721

21.3.2 復

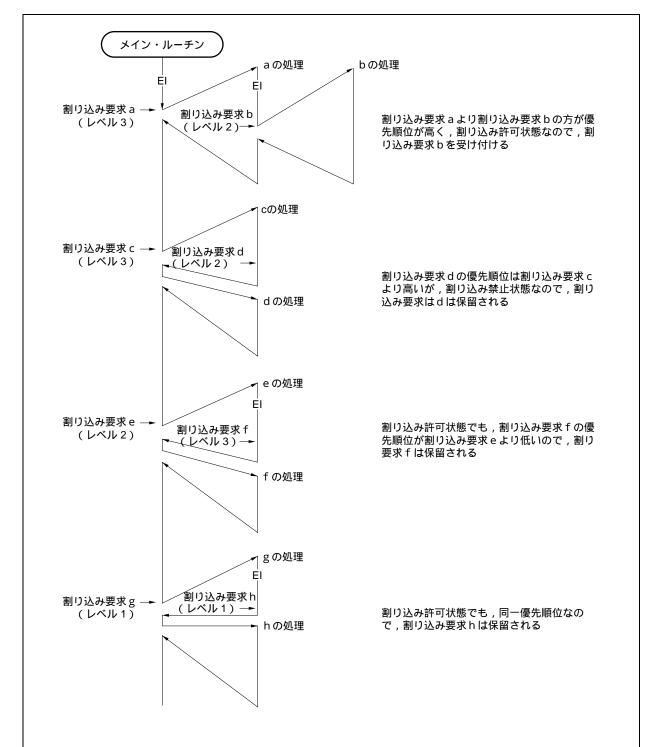

21.3.3 マスカブル割り込みの優先順位 ... 722

21.3.4 割り込み制御レジスタ(xxlCn) ... 726

21.3.5 割り込みマスク・レジスタ0-3 (IMR0-IMR3) ... 729

21.3.6 インサービス・プライオリティ・レジスタ(ISPR) ... 731

21.3.7 IDフラグ ... 732

21.3.8 ウォッチドッグ・タイマ・モード・レジスタ1(WDTM1) ... 733

21. 4 外部割り込み要求入力端子 (NMI, INTPO-INTP7) ... 734

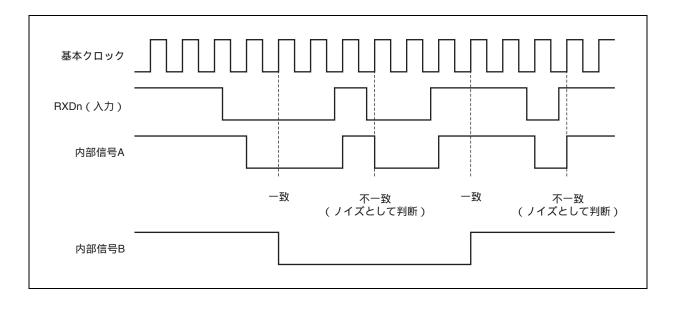

21.4.1 ノイズ除去 ... 734

21.4.2 エッジ検出 ... 736

21.5 ソフトウエア例外 ... 740

21.5.1 動 作 ... 740

21.5.2 復 帰 ... 741

21.5.3 EPフラグ ... 742

21.6 例外トラップ ... 743

21.6.1 不正命令コード ... 743

21.6.2 ディバグ・トラップ ... 745

21.7 多重割り込み処理制御 ... 747

21.8 割り込み応答時間 ... 749

21.9 CPUが割り込みを受け付けられない期間 ... 750

21.10 注意事項 ... 750

第22章 キー割り込み機能 ... 751

22.1 機 能 ... 751

22.2 レジスタ ... 752

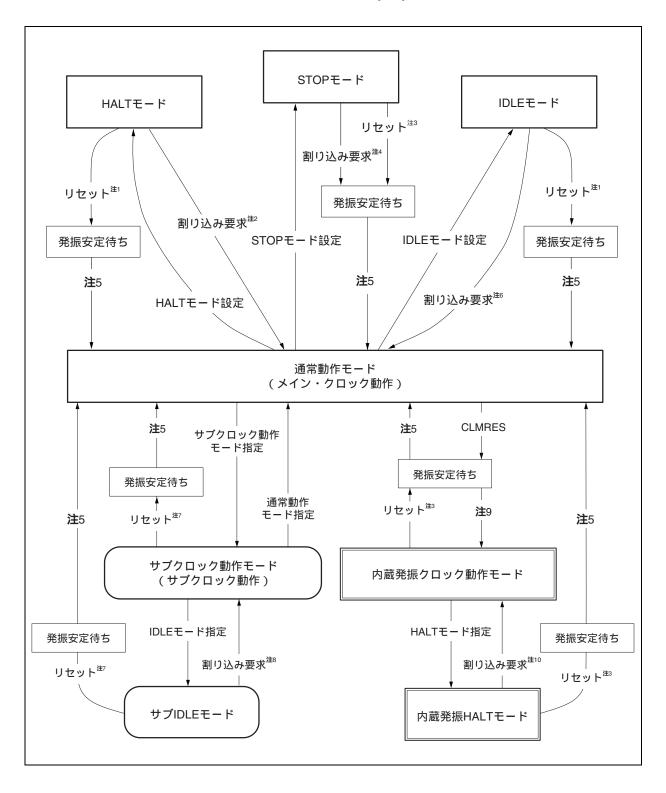

第23章 スタンバイ機能 ... 753

23.1 概 要 ... 753

23.2 レジスタ ... 756

23.3 HALTモード ... 759

23.3.1 設定および動作状態 ... 759

23.3.2 HALTモードの解除 ... 759

23.4 IDLEモード ... 761

23.4.1 設定および動作状態 ... 761

23.4.2 IDLEモードの解除 ... 762

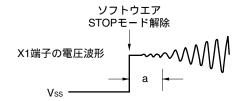

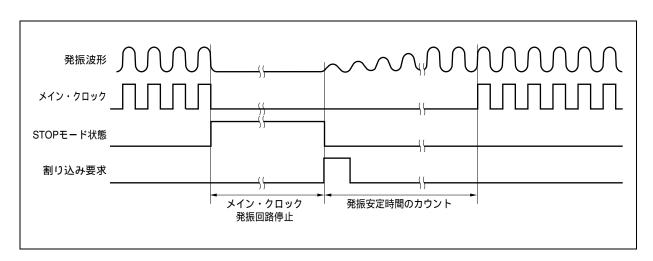

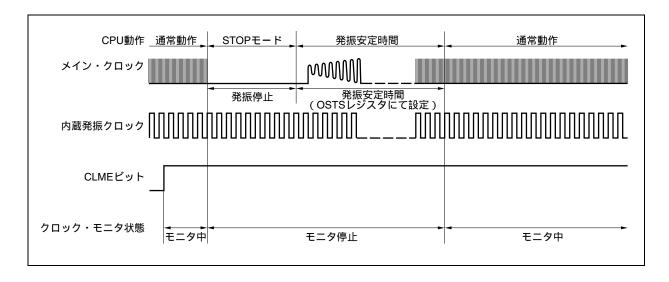

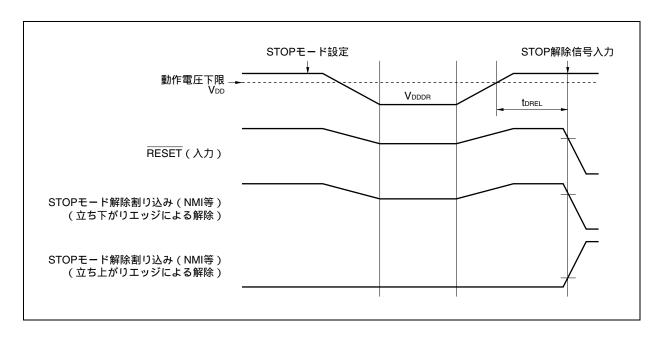

23.5 STOPモード ... 765

23.5.1 設定および動作状態 ... 765

23.5.2 STOPモードの解除 ... 765

23.5.3 STOPモード解除時の発振安定時間の確保 ... 768

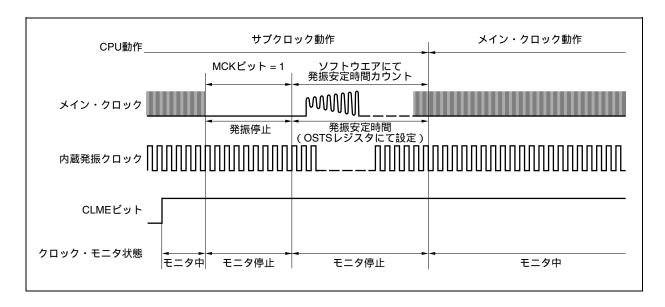

23.6 サブクロック動作モード ... 769

23.6.1 設定および動作状態 ... 769

```

| 23. 7                | 23. 6. 2 サブクロック動作モードの解除 769<br>サプIDLE <b>モード</b> 771<br>23. 7. 1 設定および動作状態 772<br>23. 7. 2 サブIDLEモードの解除 772                     |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------|

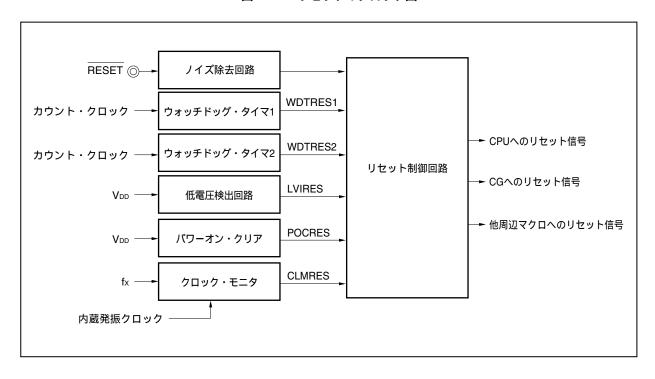

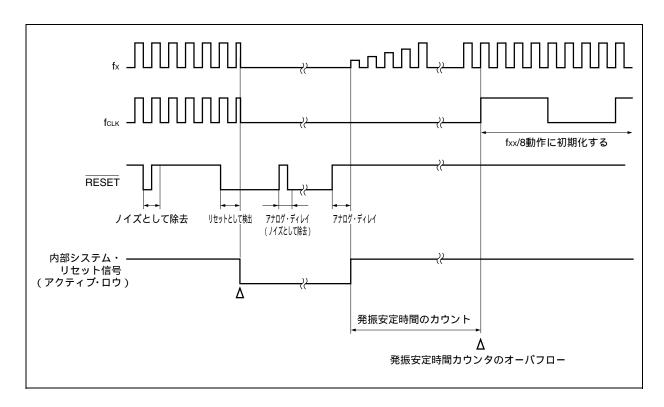

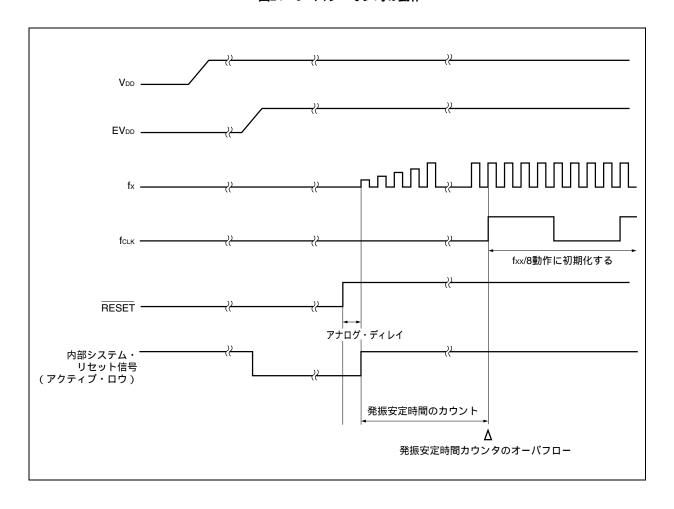

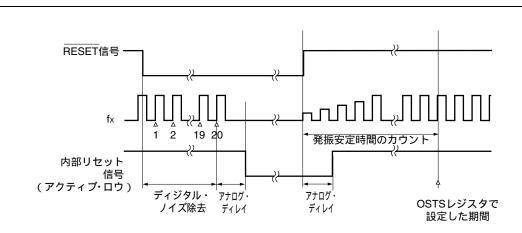

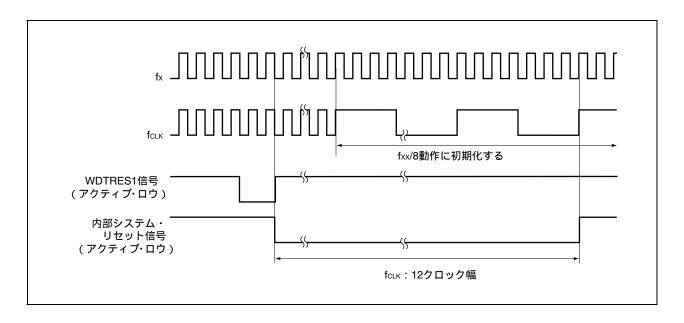

| <b>第</b> 24 <b>章</b> | <b>リセット機能</b> 775                                                                                                               |

| 24. 2                | 概 要 775<br>構 成 775<br>リセット要因を確認するレジスタ 776                                                                                       |

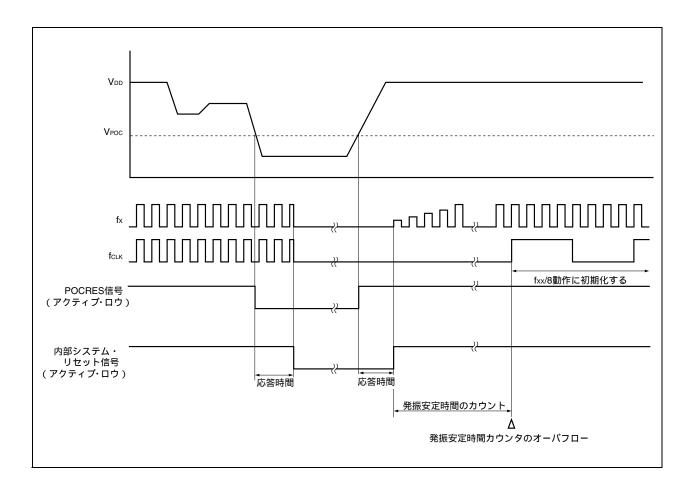

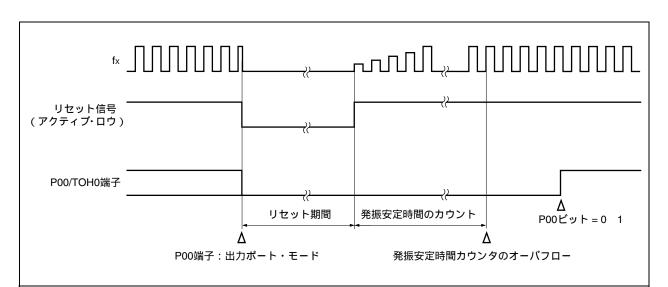

|                      | リセット要因        777         24. 4. 1       RESET端子によるリセット動作        777         24. 4. 2       WDTRES1信号によるリセット動作        782       |

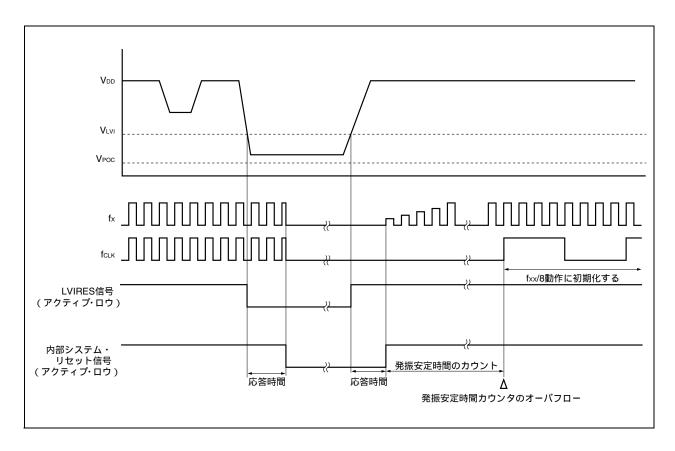

|                      | 24. 4. 3       WDTRES2信号によるリセット動作 783         24. 4. 4       パワーオン・クリアによるリセット動作 784         24. 4. 5       低電圧検出回路によるリセット動作 787 |

| 24. 5                | 24.4.6 クロック・モニタによるリセット動作 788<br><b>リセット出力機能</b> 789                                                                             |

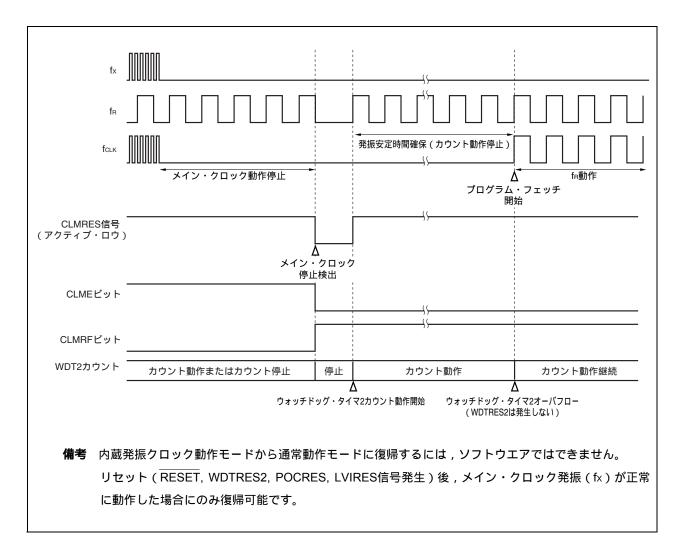

| <b>第</b> 25 <b>章</b> | <b>クロック・モニタ</b> 790                                                                                                             |

| 25. 2<br>25. 3       | 機 能 … 790<br>レジスタ … 790<br>動 作 … 792<br>内蔵発振クロック動作モード … 795<br>25.4.1 設定および動作状態 … 795                                           |

| 25. 5                | 25. 4. 2 内蔵発振クロック動作モードの解除 795内蔵発振HALTモード 79825. 5. 1 設定および動作状態 79825. 5. 2 内蔵発振HALTモードの解除 798                                   |

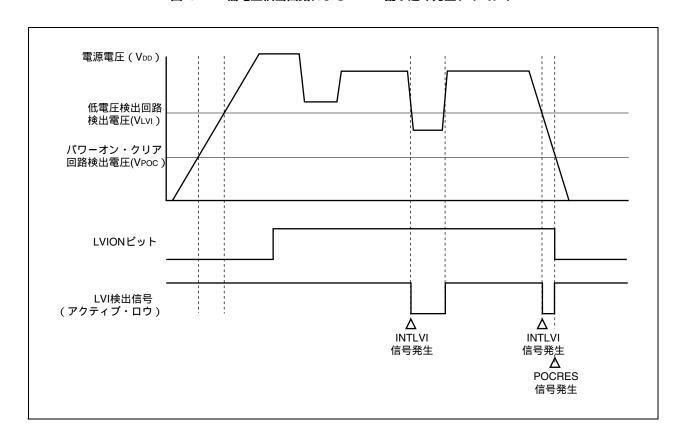

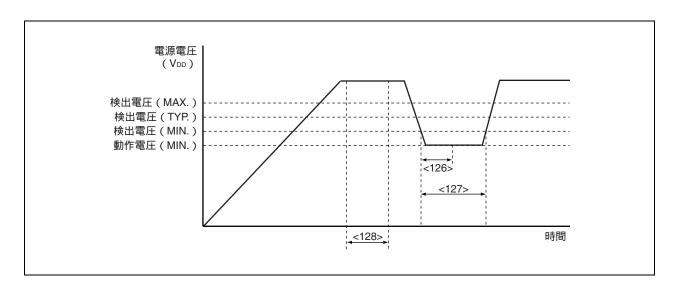

| 第26章                 | <b>低電圧検出回路</b> 800                                                                                                              |

| 26. 2<br>26. 3       | 機 能 800<br>構 成 800<br>レジスタ 801<br>動 作 803                                                                                       |

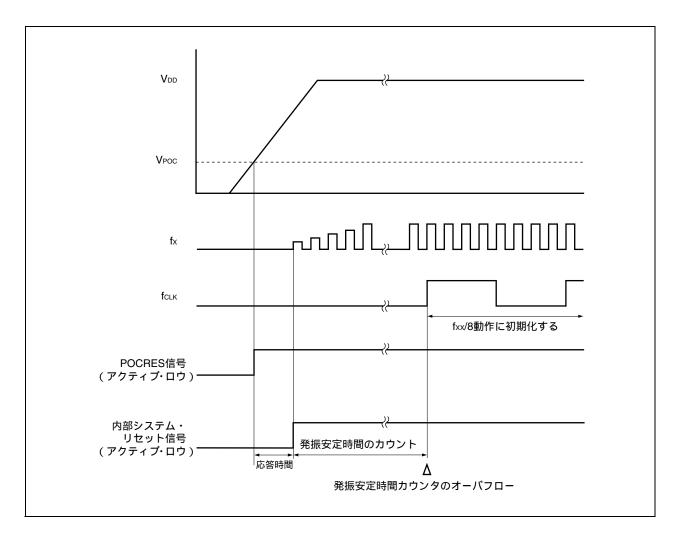

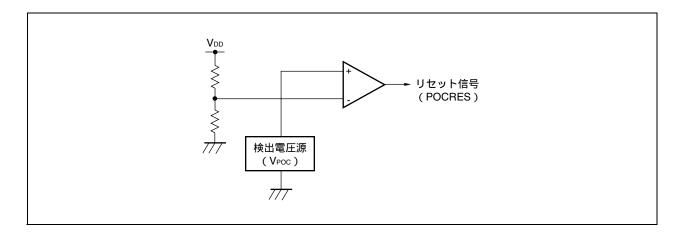

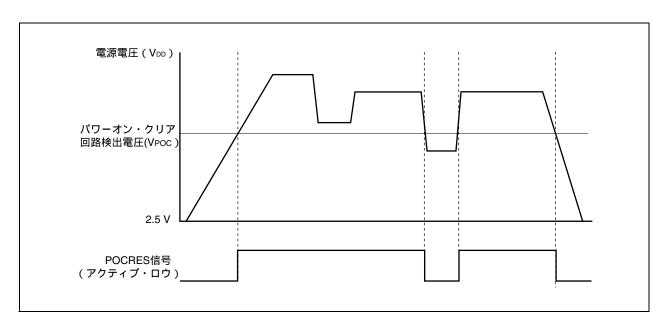

| <b>第</b> 27 <b>章</b> | パワーオン・クリア回路 805                                                                                                                 |

| 27. 2                | 機 能 805<br>構 成 805<br>動 作 806                                                                                                   |

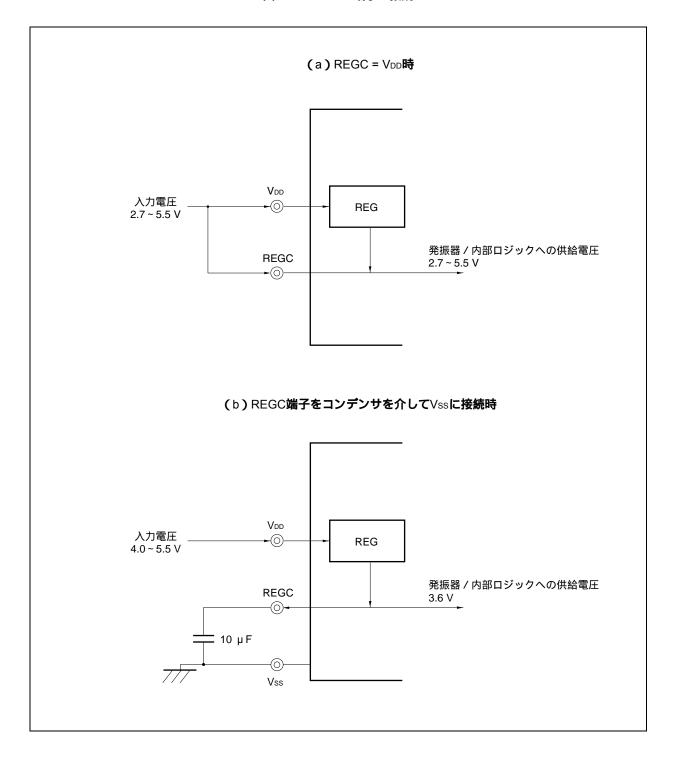

| 第28章                 | レギュレータ 807                                                                                                                      |

| 28. 1<br>28. 2       |                                                                                                                                 |

# 第29章 オプション・バイト ... 809 29.1 内蔵発振器のソフトウエアによる停止許可/禁止 ... 810

#### 第30章 フラッシュ・メモリ ... 811

- 30.1 特 徵 ... 811

- 30.2 メモリ構成 ... 812

- 30.3 機能概要 ... 813

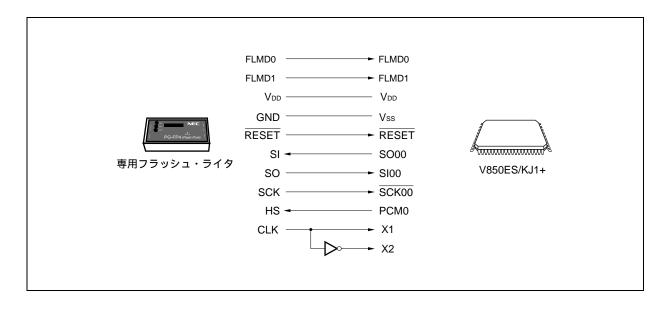

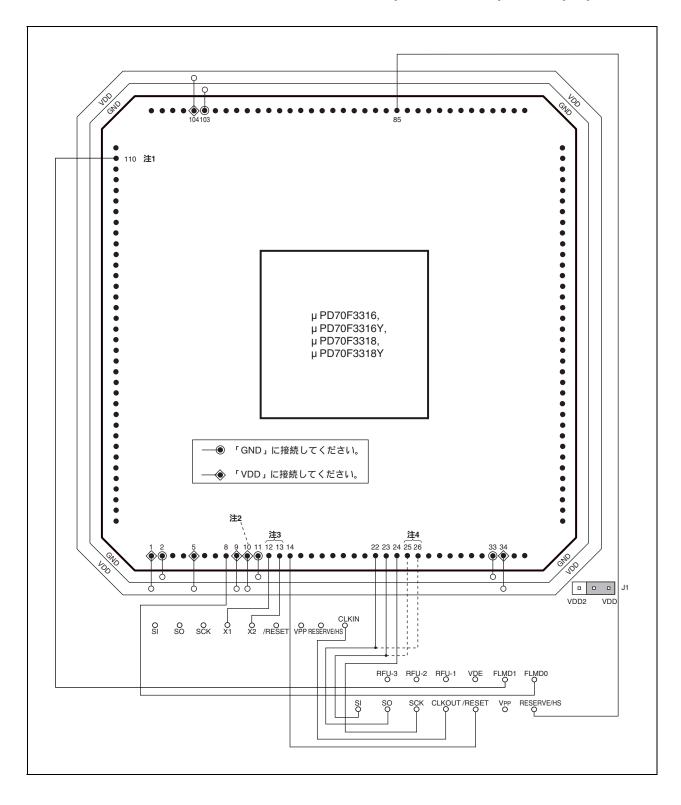

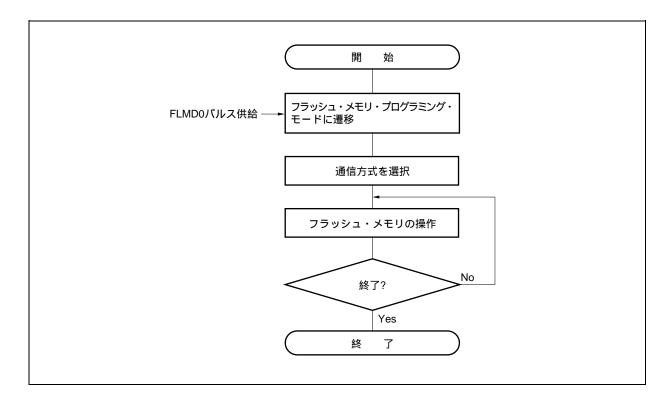

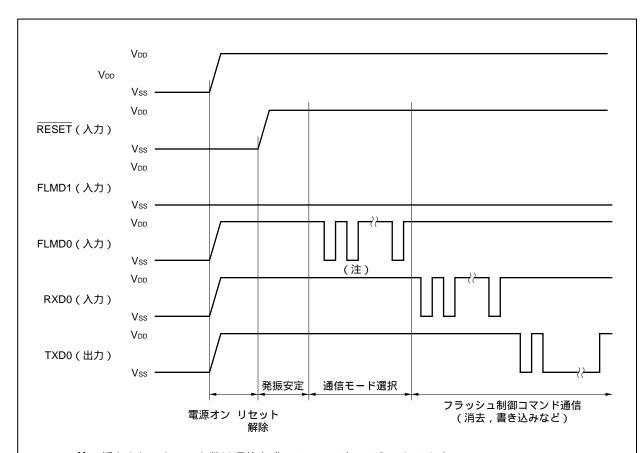

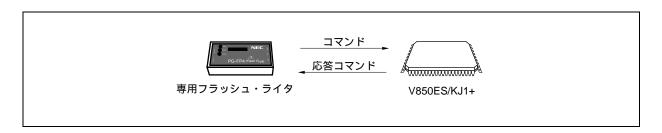

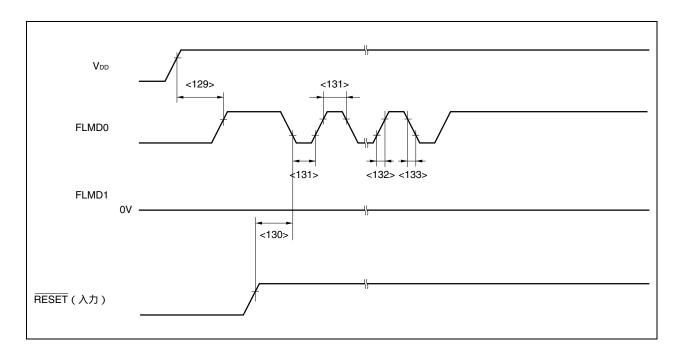

- 30.4 専用フラッシュ・ライタでの書き換え ... 817

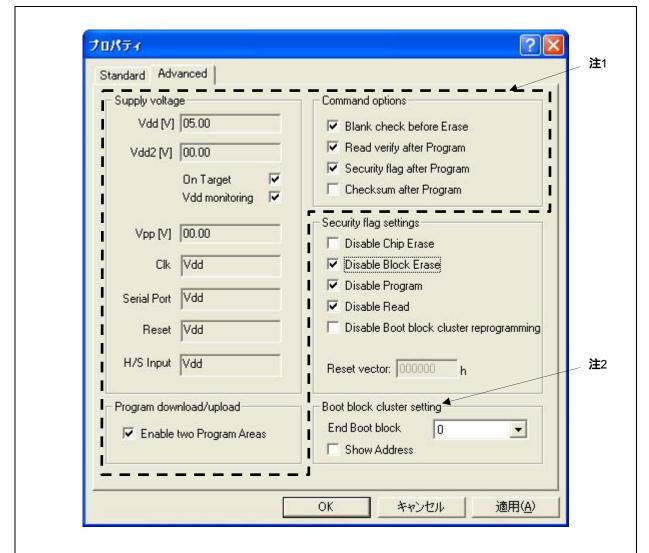

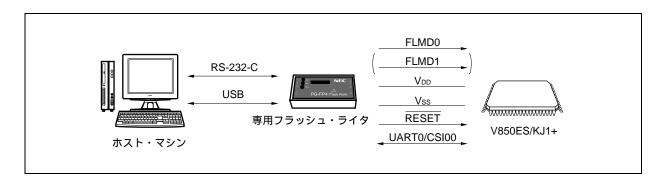

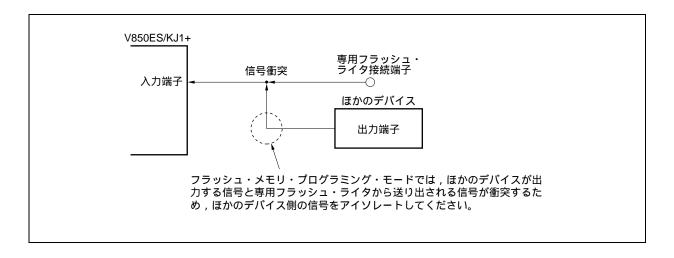

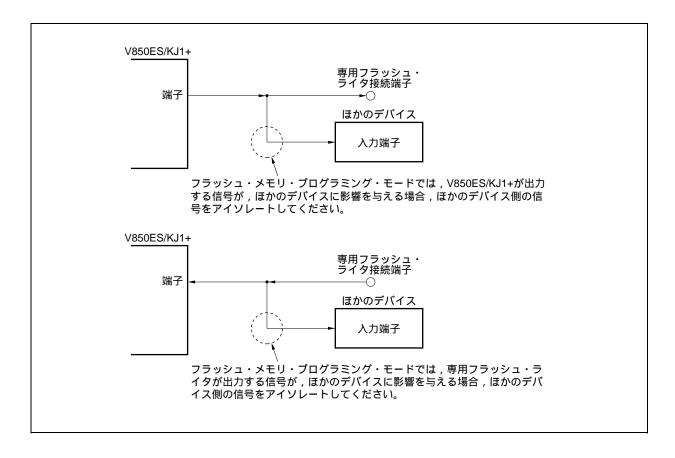

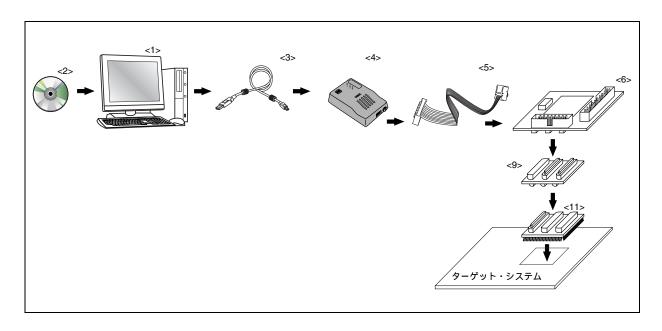

- 30.4.1 プログラミング環境 ... 817

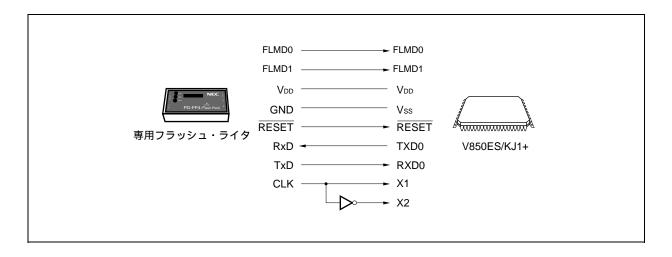

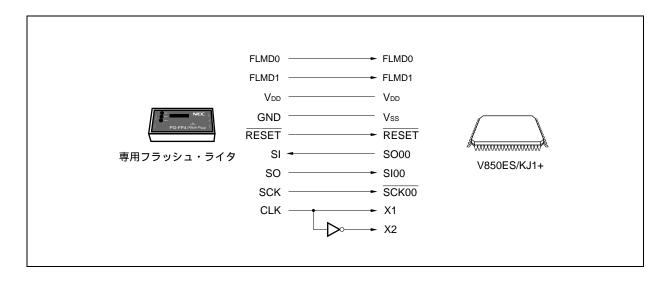

- 30.4.2 通信方式 ... 818

- 30.4.3 フラッシュ・メモリ制御 ... 823

- 30.4.4 通信方式の選択 ... 824

- 30.4.5 通信コマンド ... 825

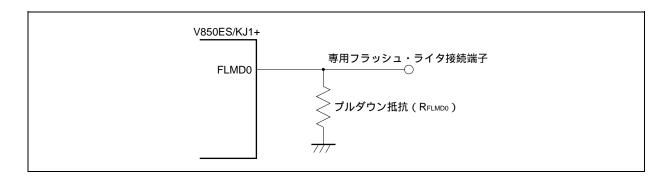

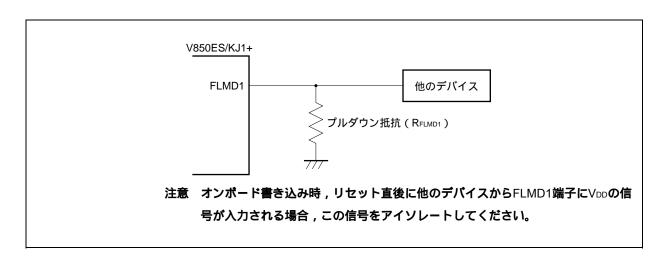

- 30.4.6 端子処理 ... 826

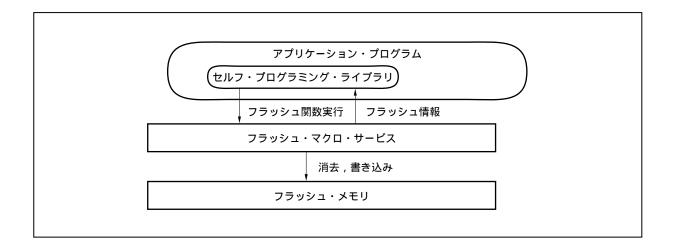

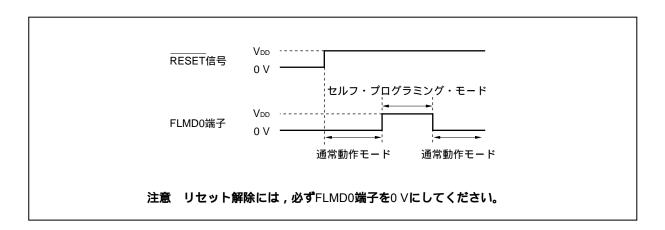

- 30.5 セルフ・プログラミングによる書き換え ... 830

- 30.5.1 概 要 ... 830

- 30.5.2 特 徵 ... 831

- 30.5.3 標準セルフ・プログラミング・フロー ... 832

29.2 リセット解除後のメイン・クロック発振の発振安定時間短縮 ... 810

- 30.5.4 フラッシュ関数一覧 ... 833

- 30.5.5 端子処理 ... 833

- 30.5.6 使用する内部資源 ... 834

#### 第31章 オンチップ・ディバグ機能 ... 835

- 31.1 特 徵 ... 835

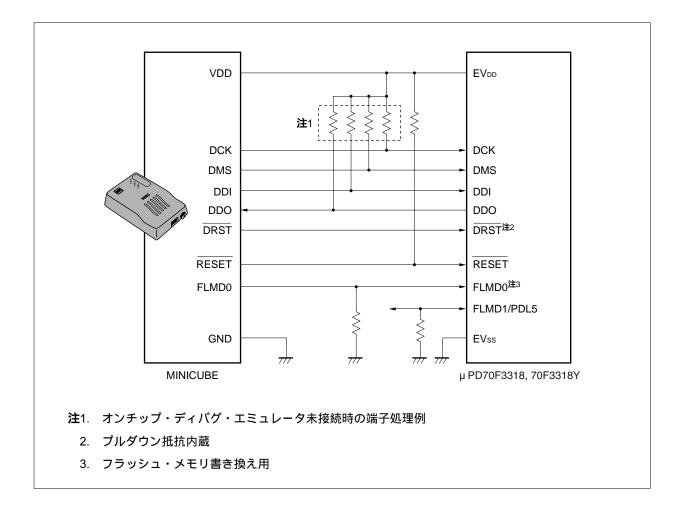

- 31.2 接続回路例 ... 836

- 31.3 インタフェース信号 ... 836

- 31.4 **レジスタ** ... 838

- 31.5 動作 ... 840

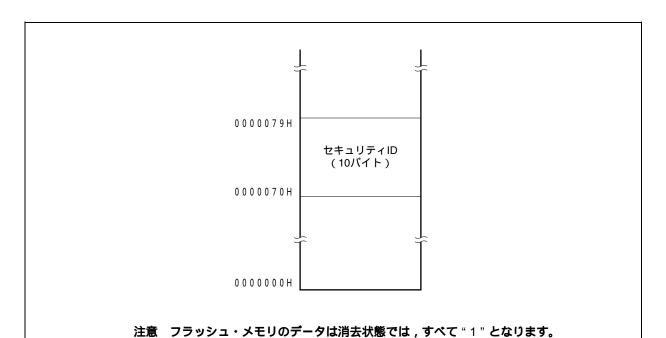

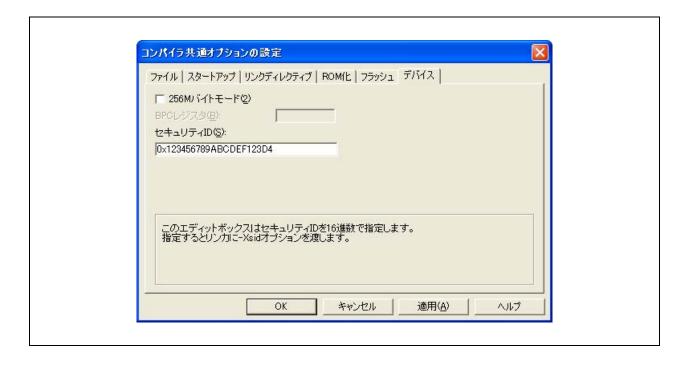

- 31.6 ROM**セキュリティ機能** ... 841 31.6.1 セキュリティID ... 841 31.6.2 設定方法 ... 842

- 31.7 注意事項 ... 843

#### 第32章 電気的特性 ... 844

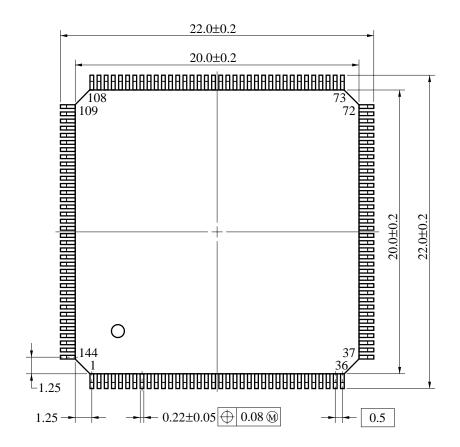

第33章 外形図 ... 896

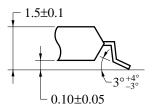

第34章 半田付け推奨条件 ... 897

#### 付録A 開発ツール ... 898

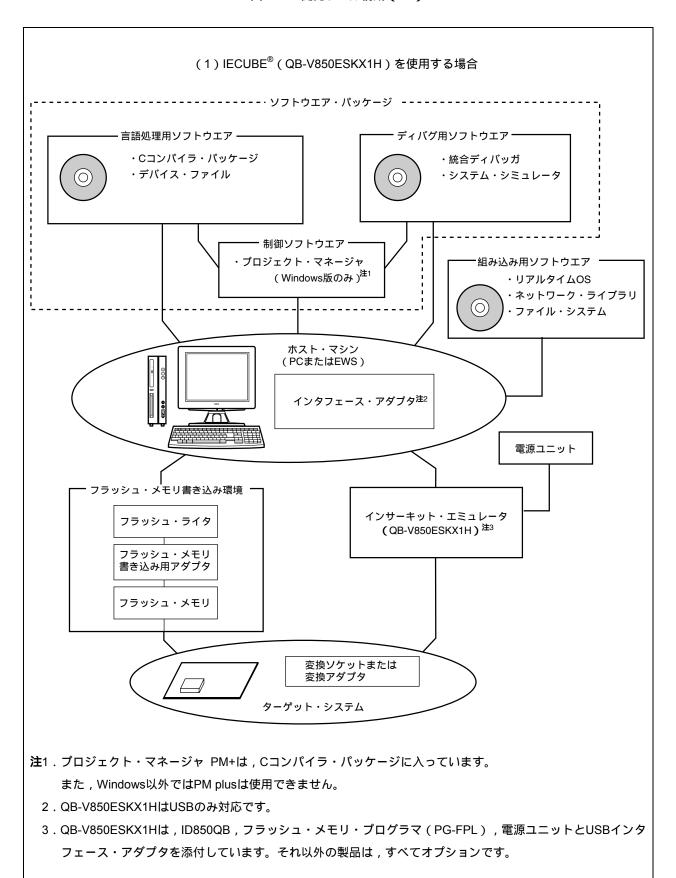

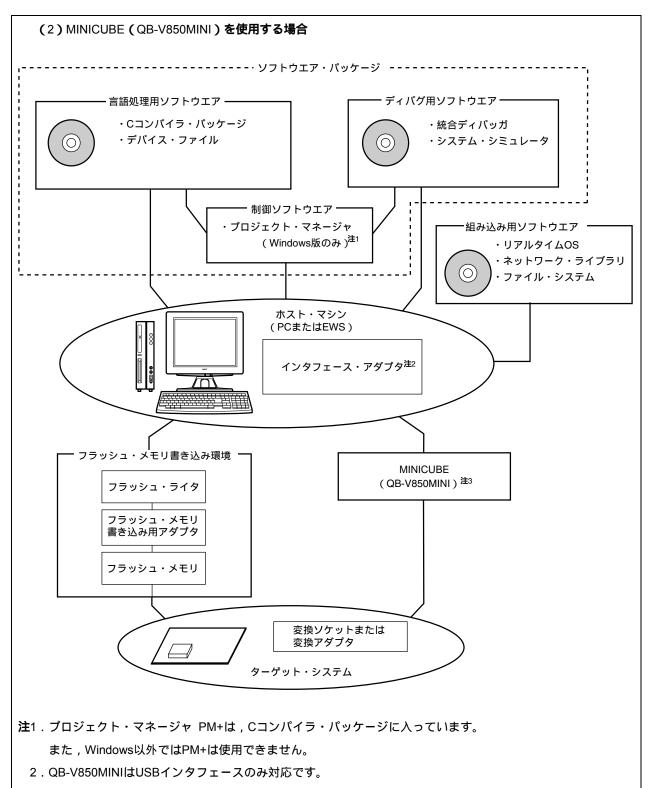

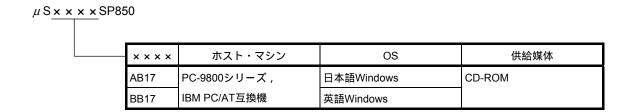

- A. 1 ソフトウエア・パッケージ ... 901

- A. 2 言語処理用ソフトウエア ... 901

- A.3 **制御ソフトウエア** ... 901

- A. 4 ディバグ用ツール (ハードウエア) ... 902

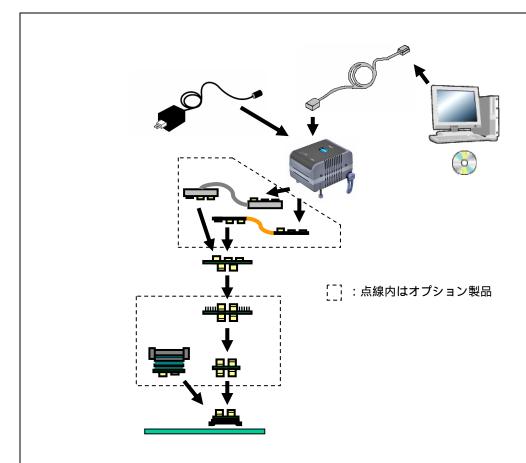

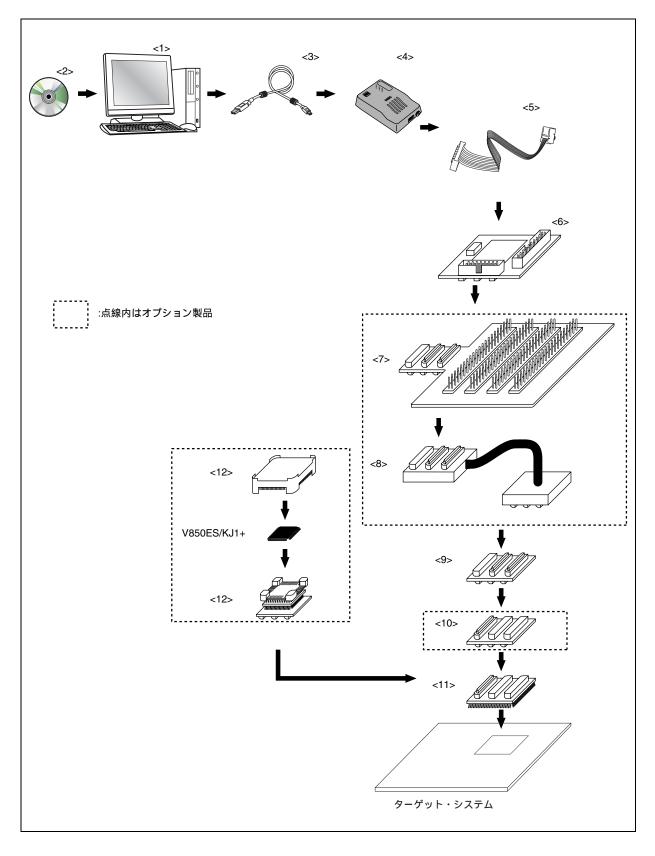

- A. 4. 1 IECUBE QB-V850ESKX1Hを使用する場合 ... 902

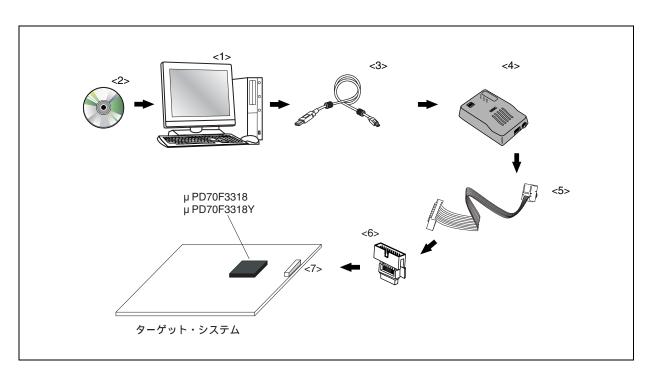

- A. 4. 2 MINICUBE QB-V850MINIを使用する場合 ... 904

- A. 5 **ディバグ用ツール (ソフトウエア)** ... 907

- A. 6 **組み込み用ソフトウエア** ... 908

- A.7 フラッシュ・メモリ書き込み用ツール ... 908

#### 付録B 命令セット一覧 ... 909

- B.1 凡 例 ... 909

- B.2 インストラクション・セット(アルファベット順) ... 912

#### **付録C レジスタ索引** ... 918

#### **付録D 改版履歴** ... 929

- D. 1 本版で改訂された主な箇所 ... 929

- D. 2 前版までの改版履歴 ... 930

#### 第1章 概 説

#### 1.1 Kシリーズの製品展開

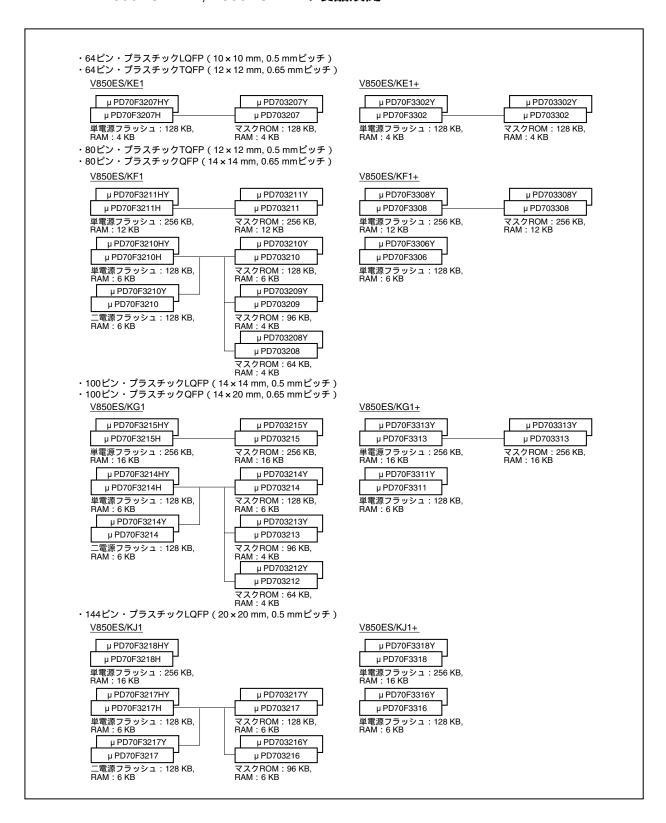

#### 1. 1. 1 V850ES/Kx1+, V850ES/Kx1**の製品展開**

#### V850ES/Kx1+の機能一覧を次に示します。

| 愛 称          |                                       | V850ES/KE1+            |           | V8                 | 50ES/KF   | -1+      | V8:                   | 50ES/KG                                      | G1+               | V850ES/KJ1+         |       |  |  |

|--------------|---------------------------------------|------------------------|-----------|--------------------|-----------|----------|-----------------------|----------------------------------------------|-------------------|---------------------|-------|--|--|

| ピン数          |                                       | 64ピン                   |           |                    | 80ピン      |          | +                     | 100ピン                                        |                   | 144ピン               |       |  |  |

| 内部           | マスクROM                                | 128                    | -         | -                  | 256       | _        | -                     | 256                                          | -                 | -                   | -     |  |  |

| メモリ          | フラッシュ・メモリ                             | -                      | 128       | 128                | -         | 256      | 128                   | -                                            | 256               | 128                 | 256   |  |  |

| (Kバイト)       |                                       |                        | <u> </u>  | 6                  | 1         | 2        | 6                     | 1                                            | 6                 | 6                   | 16    |  |  |

| 電源電圧         |                                       | 2.7 ~ 5.5 V            |           |                    |           |          |                       |                                              |                   |                     |       |  |  |

| 最小命令実行       |                                       | 50 ns@20 MHz           |           |                    |           |          |                       |                                              |                   |                     |       |  |  |

| クロック         | X1入力                                  | 2 ~ 10 MHz             |           |                    |           |          |                       |                                              |                   |                     |       |  |  |

|              | サブクロック                                | 32.768 kHz             |           |                    |           |          |                       |                                              |                   |                     |       |  |  |

|              | 内蔵発振器                                 | 240 kHz ( TYP. )       |           |                    |           |          |                       |                                              |                   |                     |       |  |  |

| ポート          | CMOS入力                                | 8                      |           | 8                  |           |          | 8                     |                                              |                   | 16                  |       |  |  |

|              | CMOS入出力                               | 41 (4) <sup>注1</sup>   |           | 57 (6)             | 注1<br>)   |          | 72 (8)                | 注1<br>)                                      |                   | 106 (12)            | 注1    |  |  |

|              | N-ch オープン・ド                           |                        |           | 2                  |           |          | 4                     |                                              |                   | 6                   |       |  |  |

|              | レーン入出力                                |                        |           |                    |           |          |                       |                                              |                   |                     |       |  |  |

| タイマ          | 16ビット(TMP)                            | 1 ch                   |           | 1 ch               |           |          | 1 ch                  |                                              |                   | 1 ch                |       |  |  |

|              | 16ビット (TM0)                           | 1 ch                   |           | 2 ch               |           |          | 4 ch                  |                                              |                   | 6 ch                |       |  |  |

|              | 8ビット (TM5)                            | 2 ch                   |           | 2 ch               |           |          | 2 ch                  |                                              |                   | 2 ch                |       |  |  |

|              | 8ビット (TMH)                            | 2 ch                   |           | 2 ch               |           |          | 2 ch                  |                                              |                   | 2 ch                |       |  |  |

|              | インターバル・タイマ                            | 1 ch                   | 1 ch      |                    |           | 1 ch     |                       |                                              | 1 ch              |                     |       |  |  |

|              | 時計                                    | 1 ch                   | 1 ch      |                    |           | 1 ch     |                       |                                              | 1 ch              |                     |       |  |  |

|              | WDT1                                  | 1 ch                   | 1 ch      |                    |           | 1 ch     |                       |                                              | 1 ch              |                     |       |  |  |

|              | WDT2                                  | 1 ch                   |           | 1 ch               |           |          | 1 ch                  |                                              |                   | 1 ch                |       |  |  |

| RTO          |                                       | 6ビット×1                 | 6ビット      | × 1 ch             |           | 6ビット     | × 1 ch                |                                              | 6ビット×2 ch         |                     |       |  |  |

| シリアル・        | CSI                                   | 2 ch                   |           | 2 ch               |           |          | 2 ch                  |                                              |                   | 3 ch                |       |  |  |

| インタフェ        | 自動送受信3線式CSI                           | -                      |           | 1 ch               |           |          | 2 ch                  |                                              |                   | 2 ch                |       |  |  |

| ース           | UART                                  | 1 ch                   |           | 1 ch               |           |          | 2 ch                  |                                              |                   | 2 ch                | 2 ch  |  |  |

|              | LIN-bus対応UART                         | 1 ch                   |           | 1 ch               | 1 ch      |          |                       | 1 ch                                         |                   |                     | 1 ch  |  |  |

|              | I <sup>2</sup> C <sup>注2</sup>        | 1 ch                   |           | 1 ch               |           |          | 1 ch                  |                                              |                   | 2 ch                |       |  |  |

| 外部バス         | アドレス空間                                | -                      |           | 128 K <i>J</i>     | バイト       |          | 3 M/\(\(\frac{1}{2}\) | <b>(                                    </b> |                   | 15 Mバイト             |       |  |  |

|              | アドレス・バス                               | 1                      |           | 16ビッ               | ۲         |          | 22ビッ                  | +                                            |                   | 24ビット               |       |  |  |

|              | モード                                   | -                      |           | マルチ                | プレクス      | このみ      | マルチ                   | プレクス                                         | / セパ              | レート                 |       |  |  |

| DMAコント       | ローラ                                   | 1                      |           | -                  |           |          | 4 ch                  |                                              |                   | 4 ch                |       |  |  |

| 10ビットA/[     | ロコンバータ                                | 8 ch                   |           | 8 ch               |           |          | 8 ch                  |                                              |                   | 16 ch               |       |  |  |

| 8ビットD/A      | コンバータ                                 | -                      |           | -                  |           |          | 2 ch                  |                                              |                   | 2 ch                |       |  |  |

| 割り込み         | 外部                                    | 9                      |           | 9                  |           |          | 9                     |                                              |                   | 9                   |       |  |  |

|              | 内部                                    | 26/27 <sup>注2</sup>    |           | 29/30 <sup>注</sup> | 2         |          | 41/42 <sup>注</sup>    | 2                                            |                   | 46/48 <sup>注2</sup> |       |  |  |

| キー・リタ-       | ーン入力                                  | 8 ch                   |           | 8 ch               |           |          | 8 ch                  |                                              |                   | 8 ch                |       |  |  |

| リセット         | RESET端子                               | あり                     |           |                    |           |          |                       |                                              |                   |                     |       |  |  |

| POC<br>LVI   |                                       | 2.7 V以下固               | 定         |                    |           |          |                       |                                              |                   |                     |       |  |  |

|              |                                       | 3.1 V/3.3 V            | ± 0.15 Vま | たは3.5 V            | //3.7 V/3 | .9 V/4.1 | V/4.3 V               | ± 0.2 V (                                    | ソフト               | ウエアによ               | り選択可能 |  |  |

|              | クロック・モニタ                              | あり(内蔵                  | 発振器によ     | るモニタ               | )         |          |                       |                                              |                   |                     |       |  |  |

| WDT1<br>WDT2 |                                       | あり                     |           |                    |           |          |                       |                                              |                   |                     |       |  |  |

|              |                                       | あり                     |           |                    |           |          |                       |                                              |                   |                     |       |  |  |

| ROMコレクション    |                                       | 4箇所 なし                 |           |                    |           |          |                       |                                              |                   |                     |       |  |  |

| レギュレーク       | タ                                     | なし                     |           | あり                 |           |          |                       |                                              |                   |                     |       |  |  |

| スタンバイ        |                                       | HALT/IDLE              | /STOP/サ   | ブIDLEモ             | ード        |          |                       |                                              |                   |                     |       |  |  |

| 動作周囲温原       | · · · · · · · · · · · · · · · · · · · | T <sub>A</sub> = -40 ~ | + 85      |                    |           |          |                       |                                              |                   |                     |       |  |  |

| <u> </u>     | のチャネル数はソ                              |                        | 1211      |                    | 25. 18    |          | THE YEAR              |                                              | <u>- ты - д ч</u> | <u> </u>            |       |  |  |

- **注**1. ( ) のチャネル数はソフトウエアによりN-chオープン・ドレーン出力選択可能な端子数です。

- 2. I<sup>2</sup>C内蔵品 (Y品)のみ。製品名については各ユーザーズ・マニュアルを参照してください。

#### V850ES/Kx1の機能一覧を次に示します。

| 愛 称          |                                | V850ES/KE1                                |             |           | V850ES/KF1       |     |      |                  |          |              | 0ES/   | KG1  | V850ES/KJ1 |                        |         |                     |  |

|--------------|--------------------------------|-------------------------------------------|-------------|-----------|------------------|-----|------|------------------|----------|--------------|--------|------|------------|------------------------|---------|---------------------|--|

| ピン数          |                                | 64ピン                                      |             |           | 80ピン             |     |      |                  |          |              | 00ピ:   |      |            | 144ピン                  |         |                     |  |

| 内部           | マスクROM                         | 128                                       | -           | 64/       | 128              | -   | 256  | _                | 64/      |              |        | 256  | -          | 96/                    | -       | _                   |  |

| メモリ          | ()()                           | 120                                       |             | 96        | 120              |     | 230  |                  | 96       | 120          |        | 230  |            | 128                    |         |                     |  |

| (Kバイト)       | フラッシュ・メモリ                      | -                                         | 128         | -         | -                | 128 | -    | 256              |          | _            | 128    | -    | 256        | -                      | 128     | 256                 |  |

|              | RAM                            |                                           |             | 4         | 6                |     |      | 2                | 4        |              | 6<br>6 |      | 6          |                        | 6       | 16                  |  |

| 電源電圧         | 10 00                          | 2.7~5.5 V                                 |             |           |                  |     |      |                  |          |              |        |      |            |                        |         |                     |  |

| 最小命令実行       | ·<br>行時間                       | 50 ns@20 MHz                              |             |           |                  |     |      |                  |          |              |        |      |            |                        |         |                     |  |

| クロック         | X1入力                           | 2 ~ 10 MHz                                |             |           |                  |     |      |                  |          |              |        |      |            |                        |         |                     |  |

|              | サブクロック                         | 32.768 kHz                                |             |           |                  |     |      |                  |          |              |        |      |            |                        |         |                     |  |

|              | 内蔵発振器                          | -                                         |             |           |                  |     |      |                  |          |              |        |      |            |                        |         |                     |  |

| ポート          | CMOS入力                         | 8                                         |             | 8         |                  |     |      |                  | 8        |              |        |      |            | 16                     |         |                     |  |

|              | CMOS入出力                        | 41 (4) <sup>注1</sup>                      |             | 57 (      | 6) <sup>2</sup>  | £1  |      |                  | 72 (     | 8)           | ±1     |      |            | 106 (12) <sup>注1</sup> |         |                     |  |

|              | N-ch オープン・ド                    |                                           |             | 2         |                  |     |      |                  | 4        |              |        |      |            | 6                      |         |                     |  |

|              | レーン入出力                         |                                           |             |           |                  |     |      |                  |          |              |        |      |            |                        |         |                     |  |

| タイマ          | 16ビット (TMP)                    | 1 ch                                      |             |           | -                |     | 1 ch | )                |          | -            |        | 1 ch | )          |                        | -       | 1 ch                |  |

|              | 16ビット(TM0)                     | 1 ch                                      |             | 2 ch      | )                |     |      |                  | 4 ch     |              |        |      |            | 6 ch                   |         |                     |  |

|              | 8ビット(TM5)                      | 2 ch                                      |             | 2 ch      | 1                |     |      |                  | 2 ch     |              |        |      |            | 2 ch                   |         |                     |  |

|              | 8ビット(TMH)                      | 2 ch                                      |             | 2 ch      | )                |     |      |                  | 2 ch     |              |        |      |            | 2 ch                   |         |                     |  |

|              | インターバル・タイマ                     | 1 ch                                      | 1 ch        | 1 ch      |                  |     |      |                  |          |              |        |      | 1 ch       |                        |         |                     |  |

|              | 時計                             | 1 ch                                      | 1 ch        | 1 ch      |                  |     |      |                  | 1 ch     |              |        |      |            | 1 ch                   |         |                     |  |

|              | WDT1                           | 1 ch                                      | 1 ch        | 1 ch      |                  |     |      |                  | 1 ch     |              |        |      |            | 1 ch                   |         |                     |  |

|              | WDT2                           | 1 ch                                      |             | 1 ch      | 1 ch             |     |      |                  |          | 1 ch         |        |      |            |                        | 1 ch    |                     |  |

| RTO          |                                | 6ビット×1                                    | ch          | 6ビット×1 ch |                  |     |      |                  | 6ビット×1ch |              |        |      |            | 6ビット×2 ch              |         |                     |  |

| シリアル・        | CSI                            | 2 ch                                      |             | 2 ch      | 2 ch             |     |      |                  |          | 2 ch         |        |      |            |                        | 3 ch    |                     |  |

| インタフェ        | 自動送受信3線式CSI                    |                                           | •           | 1 ch      |                  |     |      |                  | 2 ch     |              |        |      |            | 2 ch                   |         |                     |  |

| ース           | UART                           | 2 ch                                      |             | 2 ch      | 2 ch             |     |      |                  |          | 2 ch         |        |      |            |                        | 3 ch    |                     |  |

|              | LIN-bus対応UART                  |                                           | •           |           | -                |     |      |                  |          |              | -      |      |            | -                      |         |                     |  |

|              | I <sup>2</sup> C <sup>注2</sup> | 1 ch                                      |             | 1 ch      |                  |     |      |                  | 1 ch     |              |        |      |            | 2 ch                   |         |                     |  |

| 外部バス         | アドレス空間                         |                                           | •           |           | 128 Kバイト         |     |      |                  |          | 3 Mバイト       |        |      |            |                        | 15 Mバイト |                     |  |

|              | アドレス・バス                        |                                           | •           | -         | 16ビット            |     |      |                  |          | 22ビット        |        |      |            |                        | 24ビット   |                     |  |

|              | モード                            |                                           |             | マル        | マルチプレクスのみ        |     |      |                  |          | マルチプレクス / セパ |        |      |            |                        |         |                     |  |

| DMAコント       |                                |                                           | •           |           | -                |     |      |                  |          |              | -      |      |            |                        | -       |                     |  |

|              | コンバータ                          | 8 ch                                      |             | 8 ch      | 8 ch             |     |      |                  |          |              |        |      |            | 16 ch                  |         |                     |  |

| 8ビットD/A      |                                |                                           | •           |           |                  | -   |      |                  | 2 ch     |              |        |      |            | 2 ch                   |         |                     |  |

| 割り込み         | 外部                             | 8<br>\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |             | 8         | <b>±</b> 2       |     | ı    | <b>±</b> 2       | 8        | ±2           |        | 1    | ±2         | 8                      | £2      | :±2                 |  |

|              | 内部                             | 25/26 <sup>注2</sup>                       |             | 25/2      | 26 <sup>注2</sup> |     | 28/2 | 29 <sup>注2</sup> |          |              |        | 33/3 | 34′        | 38/40 <sup>2</sup>     | -       | 41/43 <sup>注2</sup> |  |

| キー・リタ-       | •                              | 8 ch                                      |             | 8 ch      | 1                |     |      |                  | 8 ch     |              |        |      |            | 8 ch                   |         |                     |  |

| リセット RESET端子 |                                | あり                                        |             |           |                  |     |      |                  |          |              |        |      |            |                        |         |                     |  |

|              | POC                            | なし                                        |             |           |                  |     |      |                  |          |              |        |      |            |                        |         |                     |  |

|              | LVI                            | なし                                        |             |           |                  |     |      |                  |          |              |        |      |            |                        |         |                     |  |

|              | クロック・モニタ                       | なし                                        |             |           |                  |     |      |                  |          |              |        |      |            |                        |         |                     |  |

|              | WDT1                           | あり                                        |             |           |                  |     |      |                  |          |              |        |      |            |                        |         |                     |  |

| DOM 3 L 5    | WDT2                           | あり                                        |             |           |                  |     |      |                  |          |              |        |      |            |                        |         |                     |  |

| ROMコレクション    |                                | 4箇所                                       |             | ± 12      | 1                |     |      |                  |          |              |        |      |            |                        |         |                     |  |

| レギュレーク       | 7                              | なし                                        | /CTOD/4     | あり        |                  | Ŀ   |      |                  |          |              |        |      |            |                        |         |                     |  |

| スタンバイ        | <del></del>                    | $T_A = -40 \sim$                          |             | / IULE    | τ-               | Γ   |      |                  |          |              |        |      |            |                        |         |                     |  |

| 動作周囲温原       | Z.                             | IA 40 ~                                   | <b>-</b> იე |           |                  |     |      | * 1              |          |              |        |      |            |                        |         |                     |  |

**注**1. ( )内のチャネル数はソフトウエアによりN-chオープン・ドレーン出力可能な端子数です。

2. I<sup>2</sup>C内蔵品 (Y品)のみ。製品名については各ユーザーズ・マニュアルを参照してください。

#### 1. 1. 2 78K0/Kx1+, 78K0/Kx1の製品展開

#### 78K0/Kx1の機能一覧を次に示します。

|        | は10万成化 見せか                                                                                         | (107)                                        | ٥٥                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | , , | 1   |              |       | ı        |                     |                      | 1                  |                   |            |                      |          |        |                                                                                             |    |

|--------|----------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------|-------|----------|---------------------|----------------------|--------------------|-------------------|------------|----------------------|----------|--------|---------------------------------------------------------------------------------------------|----|

|        | 愛 称                                                                                                | 78K0/KB1 78K0/KC1 78K0/KD1 78K0/KE1          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |     |              |       | 78K0/KF1 |                     |                      |                    |                   |            |                      |          |        |                                                                                             |    |

| ピン数    |                                                                                                    | ;                                            | 30ピン                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ,   |     | 44ピン         | /     |          | 52ピン                | ,                    | 64ピン               |                   |            |                      | 80ピン     |        | /                                                                                           |    |

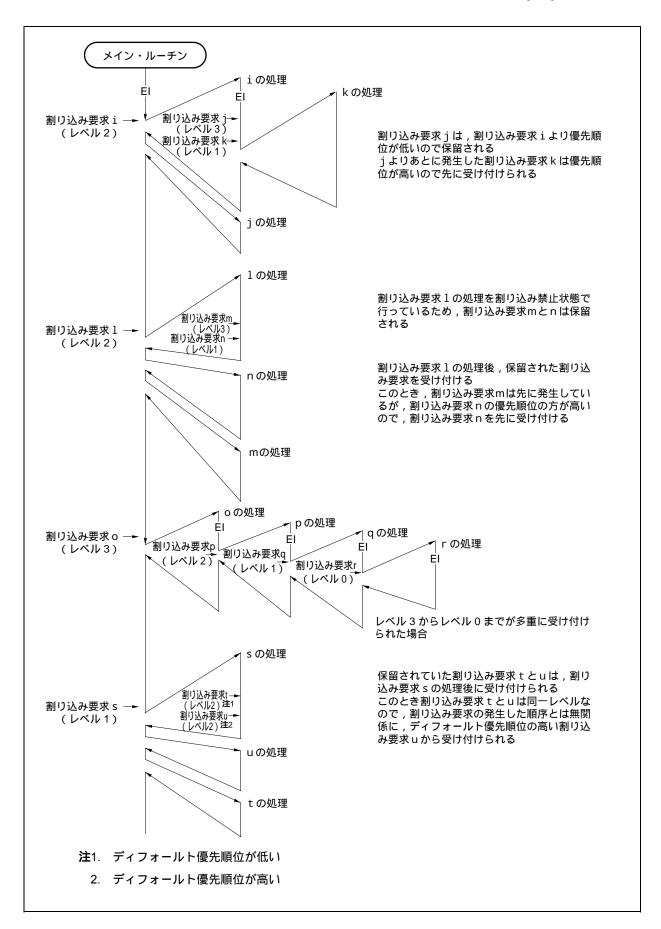

| 内部     | マスクROM                                                                                             | 8                                            | 16 /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -   | 8 / | 24/          | -     | 8 /      | 24 /                | -                    | 8 /                | 8 / 24 / - 48 / - |            |                      | 24 /     | 48 /   | -                                                                                           |    |