The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# SH7750, SH7750S, SH7750R Group

User's Manual: Hardware

Renesas 32-Bit RISC Microcomputer SuperH™ RISC engine Family / SH7750 Series

#### Notice

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(2012.4)

### **General Precautions on Handling of Product**

#### 1. Treatment of NC Pins

Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are they are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

#### 2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a pass-through current flows internally, and a malfunction may occur.

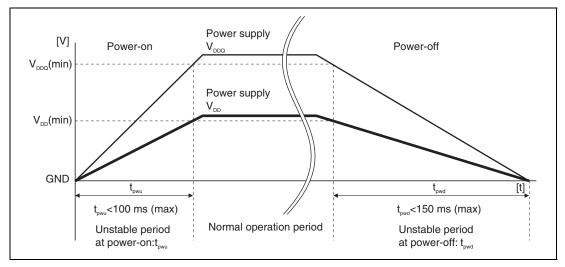

#### 3. Processing before Initialization

Page iv of lii

Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

#### 4. Prohibition of Access to Undefined or Reserved Addresses

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

### 5. Reading from/Writing to Reserved Bit of Each Register

Note: Treat the reserved bit of register used in each module as follows except in cases where the specifications for values which are read from or written to the bit are provided in the description.

The bit is always read as 0. The write value should be 0 or one, which has been read immediately before writing.

Writing the value, which has been read immediately before writing has the advantage of preventing the bit from being affected on its extended function when the function is assigned.

### **Preface**

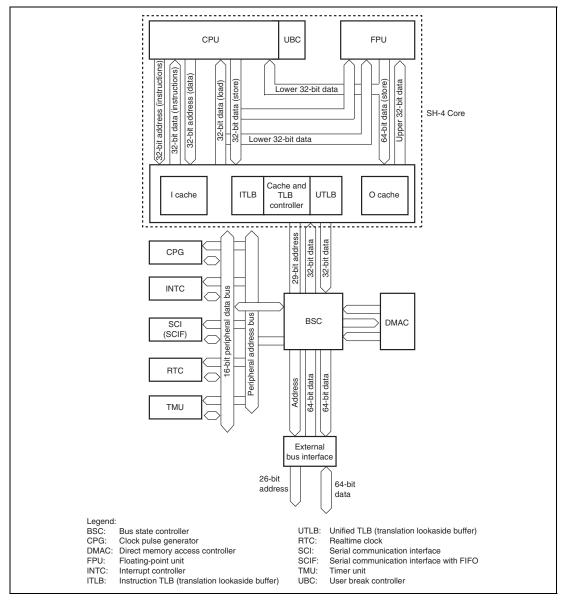

The SH-4 (SH7750 Group: SH7750, SH7750S, SH7750R) microprocessor incorporates the 32-bit SH-4 CPU and is also equipped with peripheral functions necessary for configuring a user system.

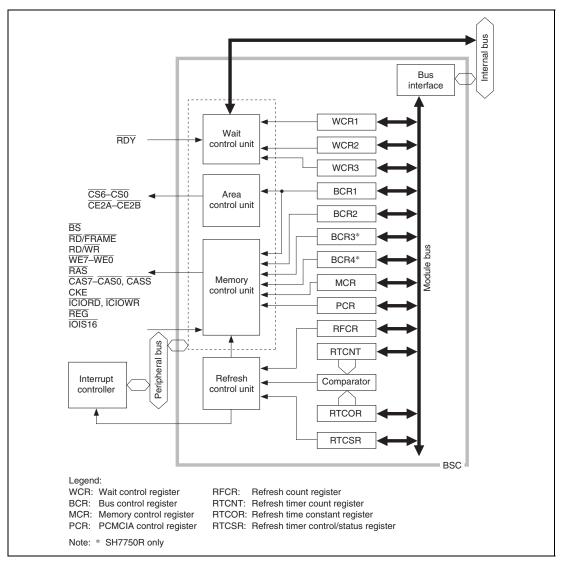

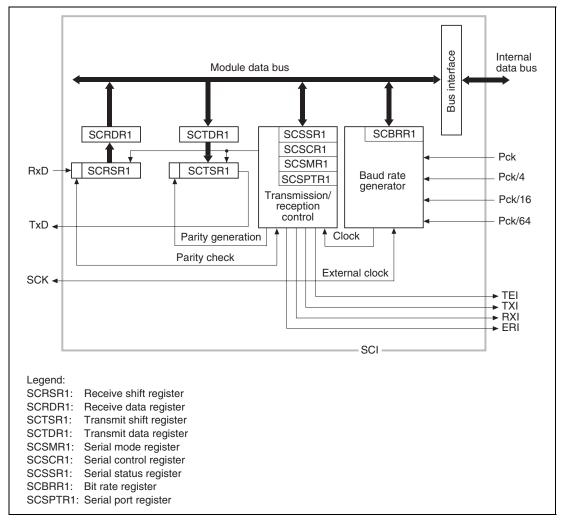

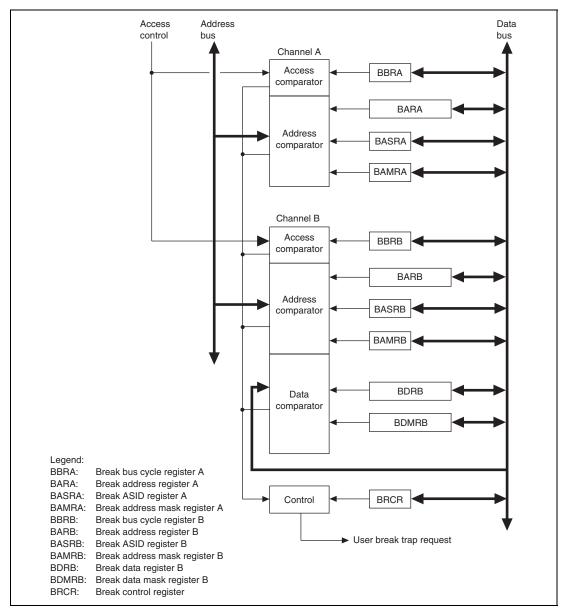

The SH7750 Group is built in with a variety of peripheral functions such as cache memory, memory management unit (MMU), interrupt controller, timers, two serial communication interfaces (SCI, SCIF), real-tim1e clock (RTC), user break controller (UBC), bus state controller (BSC) and smart card interface. This LSI can be used in a wide range of multimedia equipment. The bus controller is compatible with ROM, SRAM, DRAM, synchronous DRAM and PCMCIA, as well as 64-bit synchronous DRAM 4-bank system and 64-bit data bus.

**Target Readers:** This manual is designed for use by people who design application systems using the SH7750, SH7750S, or SH7750R.

To use this manual, basic knowledge of electric circuits, logic circuits and microcomputers is required.

**Purpose:** This manual provides the information of the hardware functions and electrical characteristics of the SH7750. SH7750S, and SH7750R.

The SH-4 Software Manual contains detailed information of executable instructions. Please read the Software Manual together with this manual.

#### How to Use the Book:

- To understand general functions

- → Read the manual from the beginning.

The manual explains the CPU, system control functions, peripheral functions and electrical characteristics in that order.

- To understanding CPU functions

- → Refer to the separate SH-4 Software Manual.

**Explanatory Note:** Bit sequence: upper bit at left, and lower bit at right

**List of Related Documents:** The latest documents are available on our Web site. Please make sure that you have the latest version.

(http://www.renesas.com/)

### • User manuals for SH7750, SH7750S, and SH7750R

| Name of Document                               | Document No.    |

|------------------------------------------------|-----------------|

| SH7750, SH7750S, SH7750R Group Hardware Manual | This manual     |

| SH-4 Software Manual                           | REJ09B0318-0600 |

### • User manuals for development tools

| Name of Document                                                                       | Document No.    |

|----------------------------------------------------------------------------------------|-----------------|

| SuperH™ RISC engine C/C++ Compiler, Assembler, Optimizing Linkage Editor User's Manual | REJ10J1571-0100 |

| SuperH™ RISC engine Simulator/Debugger User's Manual                                   | REJ10B0210-0400 |

| High-performance Embedded Workshop User's Manual                                       | REJ10J1737-0100 |

# Main Revisions for This Edition

| Item                                                                              | Page     | Revision                                                          | ı (See Man               | ual for                                              | Details)               |                          |             |

|-----------------------------------------------------------------------------------|----------|-------------------------------------------------------------------|--------------------------|------------------------------------------------------|------------------------|--------------------------|-------------|

| All                                                                               | _        | Added ONPAC-BGA products (HD6417750SBA200V and HD6417750RBA240HV) |                          |                                                      |                        |                          |             |

| 1.1 SH7750, SH7750S,                                                              | 8        | Table am                                                          | nended                   |                                                      |                        |                          |             |

| SH7750R Groups                                                                    |          | Item                                                              | Features                 |                                                      |                        |                          |             |

| Features                                                                          |          | Product lineup                                                    | Abbre-<br>viation        | Voltage<br>(Internal)                                | Operating<br>Frequency | Model No.                | Package     |

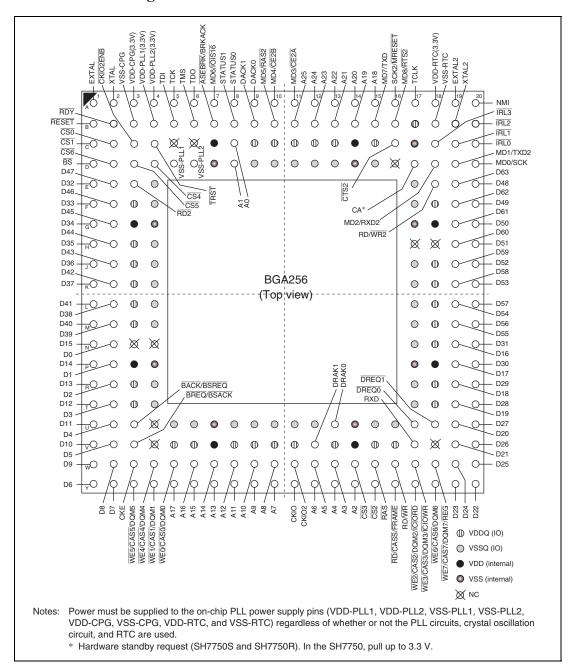

| Table 1.1 LSI Features                                                            |          |                                                                   | SH7750S                  | 1.95 V                                               | 200 MHz                | HD6417750SBP200          | 256-pin BGA |

|                                                                                   |          |                                                                   |                          |                                                      |                        | HD6417750SBA200          |             |

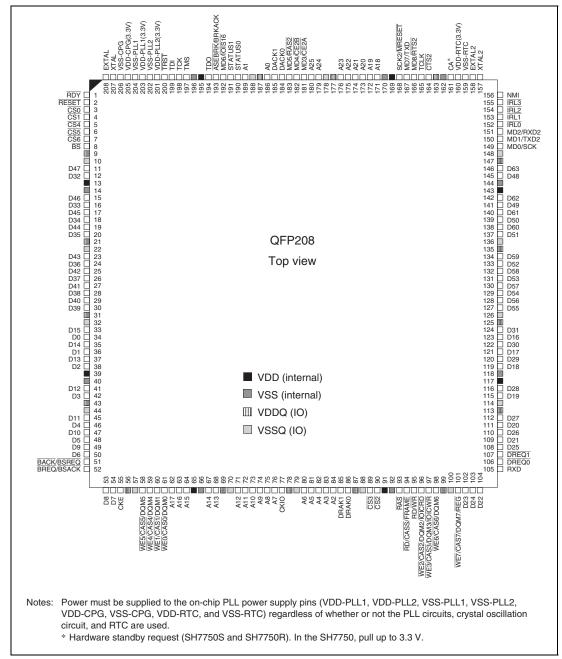

|                                                                                   |          |                                                                   |                          |                                                      |                        | HD6417750SF200           | 208-pin QFP |

|                                                                                   |          |                                                                   |                          | 1.8 V                                                | 167 MHz                | HD6417750SF167           | =           |

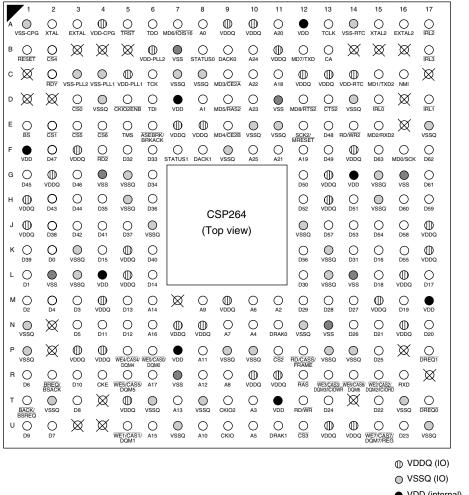

|                                                                                   |          |                                                                   |                          | 1.5 V                                                | 133 MHz                | HD6417750SVF133          |             |

|                                                                                   |          |                                                                   |                          |                                                      |                        | HD6417750SVBT133         | 264-pin CSP |

|                                                                                   |          |                                                                   | SH7750R                  | 1.5 V                                                | 240 MHz                | HD6417750RBG240          | 292-pin BGA |

|                                                                                   |          |                                                                   |                          |                                                      |                        | HD6417750RBP240          | 256-pin BGA |

|                                                                                   |          |                                                                   |                          |                                                      |                        | HD6417750RBA240H         |             |

| Section 22 Electrical<br>Characteristics                                          |          |                                                                   | escriptions<br>750SBA200 |                                                      | 11//50H                | BA240HV and              |             |

| 22.1 Absolute Maximum                                                             | 895      | Table an                                                          | d table note             | e amend                                              | ded                    |                          |             |

| Ratings                                                                           |          | Item                                                              |                          | Symb                                                 | ool Valu               | ie                       | Unit        |

| Table 22.1 Absolute Maximum Ratings                                               |          | I/O, PLL, RTC<br>voltage                                          | , CPG power supp         | bly $V_{DDQ}$ $V_{DD-PLL}$ $V_{DD-RTC}$ $V_{DD-CPC}$ | 1/2                    | to 4.2, -0.3 to 4.6*1    | V           |

|                                                                                   |          | Internal power                                                    | supply voltage           | V <sub>DD</sub>                                      |                        | to 2.5, -0.3 to 2.1*1    | V           |

|                                                                                   |          | Input voltage                                                     |                          | $V_{in}$                                             | -0.3                   | to V <sub>DDQ</sub> +0.3 | V           |

|                                                                                   |          | Operating tem                                                     | perature                 | $T_{opr}$                                            | -20                    | to 75, -40 to 85*2       | °C          |

|                                                                                   |          | Storage temper                                                    | erature                  | $T_{stg}$                                            | -55                    | to 125                   | °C          |

|                                                                                   |          | Notes: 1                                                          | . HD6417                 |                                                      | •                      | only                     |             |

| 22.2 DC Characteristics                                                           | 806 807  | Table title                                                       | e amended                | and no                                               | to addod               |                          |             |

|                                                                                   | 090, 097 |                                                                   |                          |                                                      |                        |                          |             |

| Table 22.2 DC<br>Characteristics<br>(HD6417750RBP240 (V),<br>HD6417750RBG240 (V), |          | Notes: 3                                                          | 3. T <sub>a</sub> = -40  | to 85°C                                              | of for the             | HD6417750RB              | A240HV.     |

| HD6417750RBA240HV)                                                                |          |                                                                   |                          |                                                      |                        |                          |             |

| $T_a = -20 \text{ to } +75^{\circ}\text{C}^{*3}$                                  |          |                                                                   |                          |                                                      |                        |                          |             |

| Item                                                                                                                                                                                                                                                                                         | Page     | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22.2 DC Characteristics  Table 22.4 DC  Characteristics (HD6417750RBP200 (V), HD6417750RBG200 (V), HD6417750RBA240HV* <sup>3</sup> ) $T_a = -20 \text{ to } +75^{\circ}\text{C}^{*4}$                                                                                                        | 900, 901 | Table title amended and note added  Notes: 3. This is the case when the device in use is an HD6417750RBA240HV running at 200 MHz.  4. T <sub>a</sub> = -40 to 85°C for the HD6417750RBA240HV.                                                                                                                                                                    |

| Table 22.6 DC<br>Characteristics<br>(HD6417750SBP200 (V),<br>HD6417750SBA200V)                                                                                                                                                                                                               | 904      | Table title amended                                                                                                                                                                                                                                                                                                                                              |

| 22.3 AC Characteristics Table 22.15 Clock Timing (HD6417750RBP240 (V), HD6417750RBG240 (V), HD6417750RBA240HV)  Table 22.17 Clock Timing (HD6417750BP200M (V), HD6417750SBP200 (V), HD6417750RBP200 (V), HD6417750RBP200 (V), HD6417750RBP200 (V), HD6417750RBP200 (V), HD6417750RBP200 (V), | 920      | Table title amended  Table title amended and note added  Note: * This is the case when the device in use is an HD6417750RBA240HV running at 200 MHz.                                                                                                                                                                                                             |

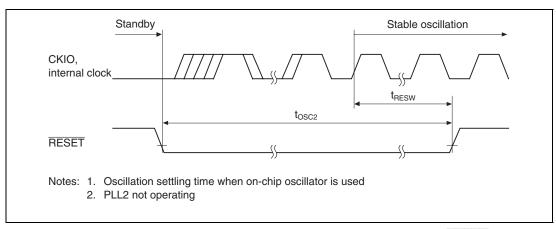

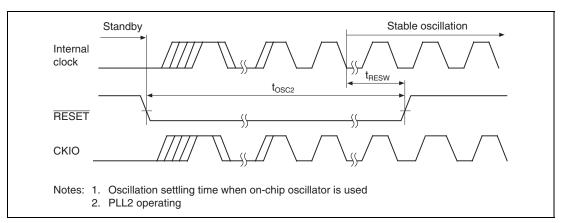

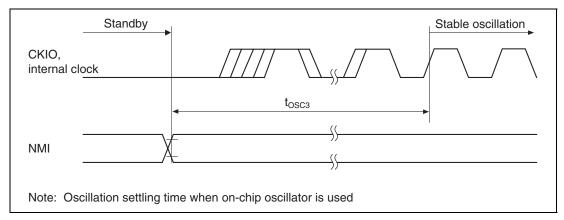

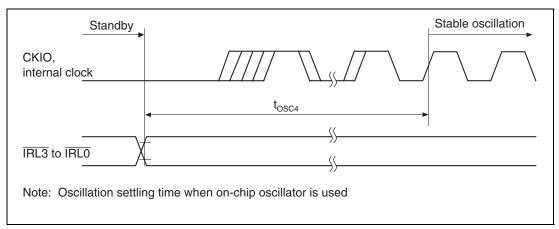

| 22.3.1 Clock and Control Signal Timing Table 22.23 Clock and Control Signal Timing (HD6417750RBP240 (V), HD6417750RBG240 (V), HD6417750RBA240HV) V <sub>DDQ</sub> = 3.0 to 3.6 V, V <sub>DD</sub> = 1.5 V, T <sub>a</sub> = -20 to +75°C* <sup>2</sup> , C <sub>L</sub> = 30 pF              | 922,923  | Table title amended and note added    tem     Standby return oscillation settling time 1*1     Standby return oscillation settling time 2*1     Standby return oscillation settling time 3*1     Notes: 1. When the oscillation settling time of a crystal resonator is lower than or equal to 1 ms.  2. T <sub>a</sub> = -40 to 85°C for the HD6417750RBA240HV. |

| iteiii                                                                                                               | raye     | nevision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22.3.1 Clock and Control<br>Signal Timing                                                                            | 926, 927 | Table title amended and note added :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Table 22.25 Clock and<br>Control Signal Timing<br>(HD6417750RBP200 (V),<br>HD6417750RBG200 (V),                      |          | Standby return oscillation settling time 1*  Standby return oscillation settling time 2*  Standby return oscillation settling time 3*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| HD6417750RBA240HV**)<br>$V_{DDQ} = 3.0 \text{ to } 3.6 \text{ V}, V_{DD} = 1.5 \text{ V}, T_a = -20 \text{ to}$      |          | Notes: 1. When the oscillation settling time of a crystal resonator is lower than or equal to 1 ms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $+75^{\circ}\text{C}^{*3}$ , $C_{L} = 30 \text{ pF}$                                                                 |          | <ol> <li>This is the case when the device in use is an HD6417750RBA240HV running at 200 MHz.</li> <li>T<sub>a</sub> = -40 to 85°C for the HD6417750RBA240HV.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Table 22.27 Clock and<br>Control Signal Timing<br>(HD6417750BP200M (V),<br>HD6417750SBP200 (V),<br>HD6417750SBA200V) | 930      | Table title amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 22.3.2 Control Signal<br>Timing<br>Table 22.32 Control<br>Signal Timing                                              | 946      | Table title and table amended    HD6417750R BP240 (V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                      |          | Item Symbol Min Max Min Max Min Max Min Max Unit Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Table 22.33 Control<br>Signal Timing                                                                                 | 947      | Table title, table and table note amended    HD6417750   HD6417750 |

|                                                                                                                      |          | Notes: 1. $V_{DDQ} = 3.0 \text{ to } 3.6 \text{ V}, V_{DD} = 1.5 \text{ V}, T_a = -20 \text{ to}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                      |          | $+75^{\circ}$ C* <sup>6</sup> , C <sub>L</sub> = 30 pF, PLL2 on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                      |          | 2. $V_{DDQ} = 3.0$ to 3.6 V, $V_{DD} = 1.5$ V, $T_{a} = -20$ to $+75^{\circ}$ C, $C_{L} = 30$ pF, PLL2 on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                      |          | 3. $V_{DDQ} = 3.0 \text{ to } 3.6 \text{ V}, V_{DD} = 1.8 \text{ V}, T_a = -20 \text{ to} +75^{\circ}\text{C}, C_L = 30 \text{ pF}, PLL2 \text{ on}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                      |          | 4. $V_{DDQ} = 3.0 \text{ to } 3.6 \text{ V}, V_{DD} = 1.8 \text{ V}, T_a = -20 \text{ to} +75^{\circ}\text{C}, C_L = 30 \text{ pF}, PLL2 \text{ on}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                      |          | 5. This is the case when the device in use is an HD6417750RBA240HV running at 200 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                      |          | 6. $T_a = -40 \text{ to } 85^{\circ}\text{C} \text{ for the HD6417750RBA240HV}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 22.3.3 Bus Timing 950 Table 22.34 Bus Timing (1)                                               | 2, 953 | Notes: 1.       | table note amended $\frac{\text{HD6417750R}}{\text{BP240}(V)} = \frac{\text{HD6417750R}}{\text{BP240}(V)} = \frac{\text{HD6417750R}}{\text{BP240}(V)} = \frac{\text{HD6417750R}}{\text{BQ200}(V)} = \frac{\text{HD6417750R}}{\text{BQ240}(V)} = \frac{\text{HD6417750R}}{\text{BA240HV}} = \frac{\text{HD6417750R}}{\text{P240}(V)} = \text{H$ |

|------------------------------------------------------------------------------------------------|--------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                | 2, 953 | Notes: 1. 2.    | $V_{\tiny DDO}=3.0$ to 3.6 V, $V_{\tiny DD}=1.5$ V, $T_{\tiny a}=-20$ to $+75^{\circ}\text{C}^{*3}$ , $C_{\tiny L}=30$ pF, PLL2 on This is the case when the device in use is an HD6417750RBA240HV running at 200 MHz. $T_{\tiny a}=-40$ to 85°C for the HD6417750RBA240HV.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                | 2, 953 | 2.<br>3.        | +75°C*³, $C_L = 30$ pF, PLL2 on<br>This is the case when the device in use is an<br>HD6417750RBA240HV running at 200 MHz.<br>$T_a = -40$ to 85°C for the HD6417750RBA240HV.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                | 2, 953 | 3.              | HD6417750RBA240HV running at 200 MHz. $T_a = -40$ to 85°C for the HD6417750RBA240HV.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                | 2, 953 |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

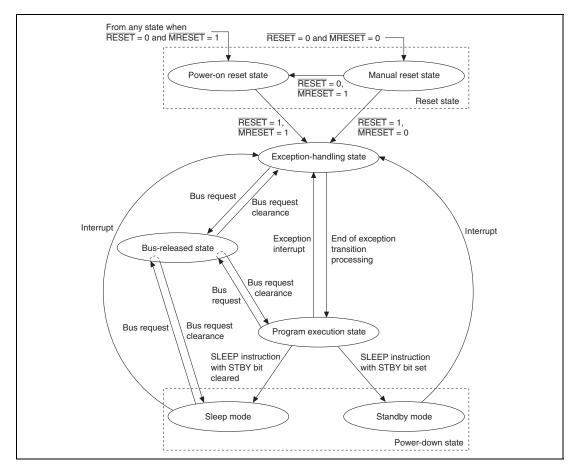

|                                                                                                | 2, 953 | Table ame       | andad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |