# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# **Preliminary User's Manual**

# NU85E

# **32-Bit Microprocessor Core**

# Hardware

# NU85E NU85EA

Document No. A14874EJ3V0UM00 (3rd edition) Date Published March 2002 N CP(N)

© NEC Corporation 2000 Printed in Japan [MEMO]

#### **1** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### **②** HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

The export of this product from Japan is regulated by the Japanese government. To export this product may be prohibited without governmental license, the need for which must be judged by the customer. The export or re-export of this product from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

- The information contained in this document is being issued in advance of the production cycle for the device. The parameters for the device may change before final production or NEC Corporation, at its own discretion, may withdraw the device prior to its production.

- Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

- NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property

rights of third parties by or arising from use of a device described herein or any other liability arising from use

of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other

intellectual property rights of NEC Corporation or others.

- Descriptions of circuits, software, and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software, and information in the design of the customer's equipment shall be done under the full responsibility of the customer. NEC Corporation assumes no responsibility for any losses incurred by the customer or third parties arising from the use of these circuits, software, and information.

- While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

- NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- Ordering information

- Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### NEC Electronics Inc. (U.S.) Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

#### **NEC Electronics (Europe) GmbH**

Duesseldorf, Germany Tel: 0211-65 03 01 Fax: 0211-65 03 327

• Branch The Netherlands Eindhoven, The Netherlands Tel: 040-244 58 45 Fax: 040-244 45 80

• Branch Sweden Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388 NEC Electronics (France) S.A. Vélizy-Villacoublay, France Tel: 01-3067-58-00 Fax: 01-3067-58-99

NEC Electronics (France) S.A. Representación en España Madrid, Spain Tel: 091-504-27-87 Fax: 091-504-28-60

NEC Electronics Italiana S.R.L. Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

**NEC Electronics (UK) Ltd.** Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290 NEC Electronics Hong Kong Ltd. Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

NEC Electronics Hong Kong Ltd. Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

NEC Electronics Singapore Pte. Ltd. Novena Square, Singapore Tel: 253-8311 Fax: 250-3583

NEC Electronics Taiwan Ltd. Taipei, Taiwan Tel: 02-2719-2377 Fax: 02-2719-5951

#### NEC do Brasil S.A.

Electron Devices Division Guarulhos-SP, Brasil Tel: 11-6462-6810 Fax: 11-6462-6829

J01.12

# Major Revisions in This Edition

| Pages       | Description                                                                                               |  |

|-------------|-----------------------------------------------------------------------------------------------------------|--|

| p.30        | Addition of description in 2.2.2 (3) VAPREQ                                                               |  |

| p.33        | Addition of description in 2.2.2 (17) VMLAST, VSLAST                                                      |  |

| p.33        | Addition of description in 2.2.2 (18) VMAHLD, VSAHLD                                                      |  |

| p.34        | Addition of description in 2.2.2 (20) VBDC                                                                |  |

| p.34        | Addition of description in 2.2.2 (21) VBDV                                                                |  |

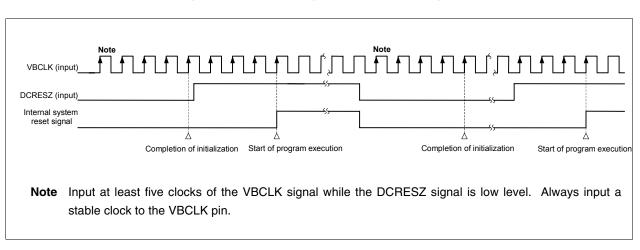

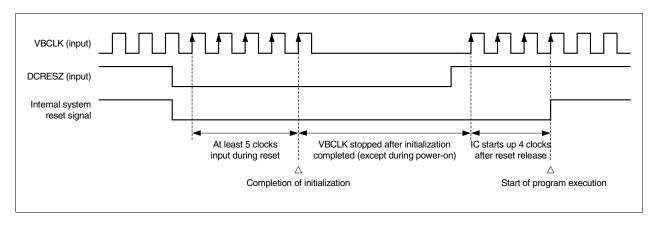

| pp.34, 35   | Addition of description in 2.2.3 (1) DCRESZ<br>Addition of Figure 2-2                                     |  |

| pp.46, 47   | Addition of Notes in 2.3 Recommended Connection of Unused Pins                                            |  |

| p.50        | Status of DBO12 to DBO5 pins after reset modified in Table 2-10 Pin Status in Each Operating Mode         |  |

| p.135       | Addition of 5.5 Precautions                                                                               |  |

| pp.138, 139 | Addition of Remarks 4 and 5 in 6.2.1 Power save control register (PSC)                                    |  |

| p.142       | Addition of Remark in Table 6-3 Operation After Setting Software STOP Mode in Interrupt Servicing Routine |  |

| p.145       | Addition of <4> and Remark in 6.6 (1) (b) When canceling software STOP mode                               |  |

| p.147       | Addition of Remark in 6.6 (2) (b) When canceling hardware STOP mode                                       |  |

| p.157       | Addition of Caution in Figure 7-6 DMA Addressing Control Registers 0 to 3 (DADC0 to DADC3)                |  |

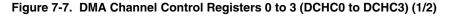

| p.159       | Addition of Caution and descriptions in Figure 7-7 DMA Channel Control Registers 0 to 3 (DCHC0 to DCHC3)  |  |

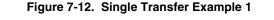

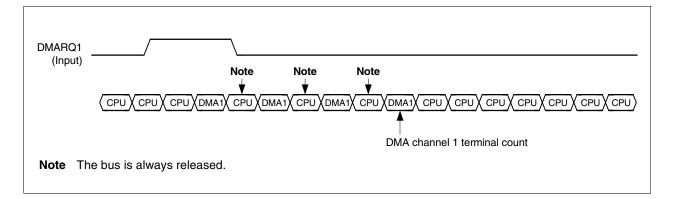

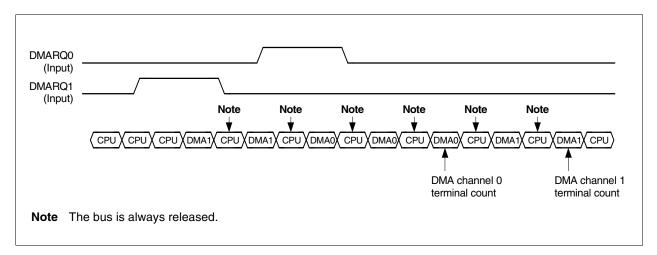

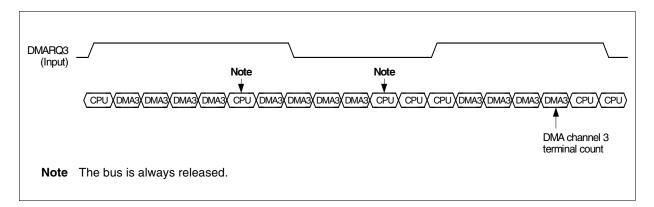

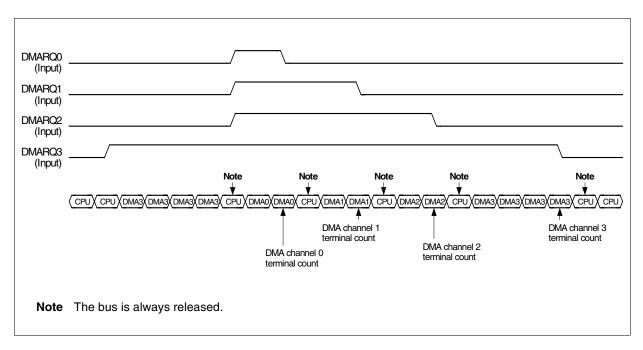

| p.172       | Addition of descriptions in 7.8.5 One-time transfer when executing single transfers using DMARQn signal   |  |

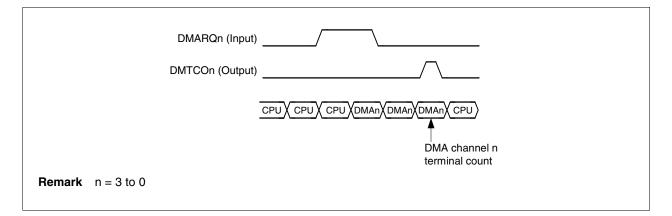

| p.173       | Addition of Figure 7-24 Example of Two-Cycle Transfer                                                     |  |

| p.174       | Addition of descriptions in 7.9.2 Flyby transfer                                                          |  |

| p.174       | Addition of Figure 7-25 Example of Flyby Transfer (Memory to I/O)                                         |  |

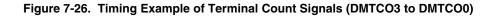

| p.176       | Addition of Figure 7-27 Example of Terminal Count Signal Output (DMTCO3 to DMTCO0)                        |  |

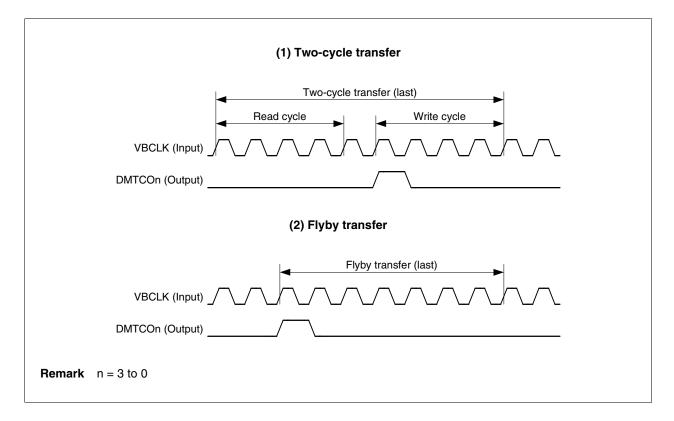

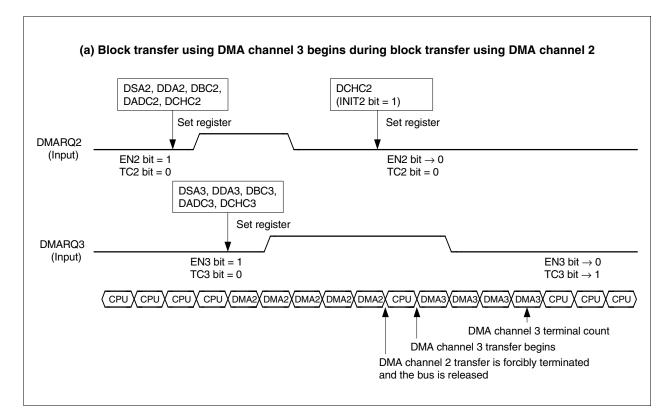

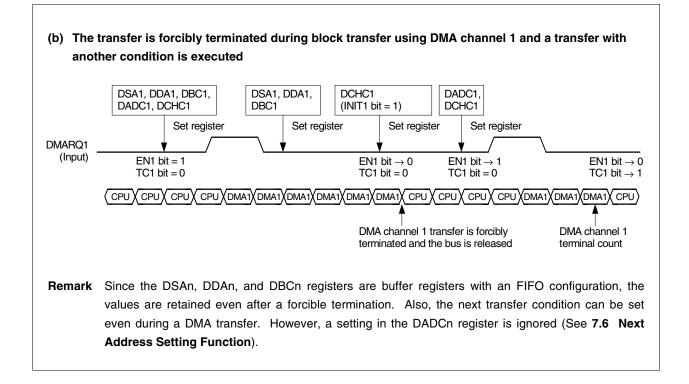

| p.179       | Modification of Remark in Figure 7-29 DMA Transfer Forcible Termination Example                           |  |

| p.204       | Modification and addition of descriptions in 7.15 (3) Intervals related to DMA transfer                   |  |

| p.205       | Addition of descriptions in 7.15 (4) CPU access during DMA transfer                                       |  |

| p.205       | Addition of 7.15 (6) DMARQn signal retention and (7) VMLOCK signal                                        |  |

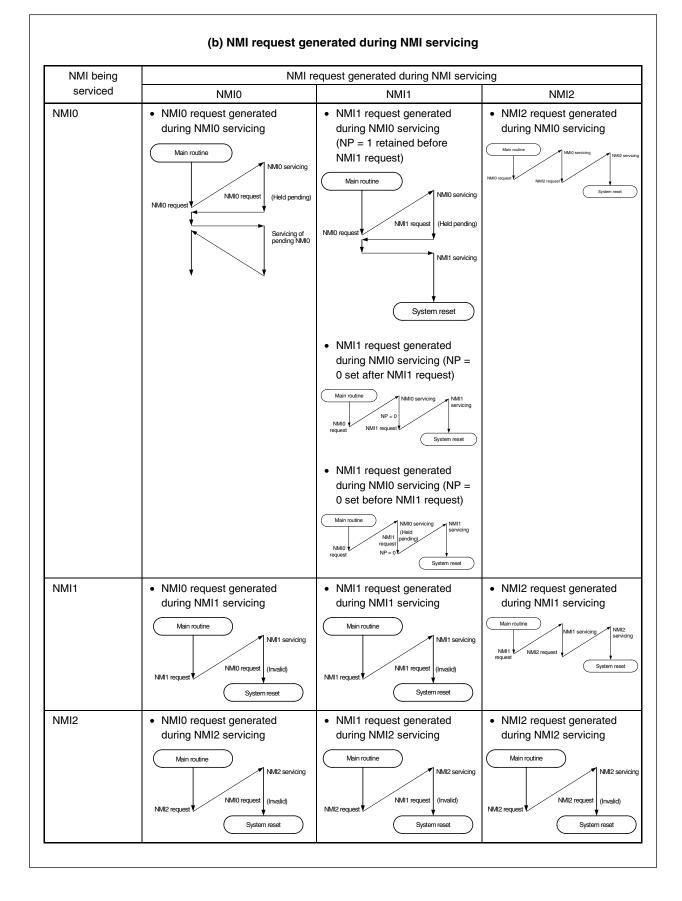

| p.209       | Modification of Caution 1 and addition of Caution 2 in 8.2 Non-Maskable Interrupts (NMI)                  |  |

| p.232       | Modification of Figure 9-1 Peripheral Macro Connection Example                                            |  |

| p.233       | Deletion of When NPB Peripheral Is Connected and modification in 9.4 (2) Test mode pins                   |  |

| p.254       | Addition of APPENDIX C REVISION HISTORY                                                                   |  |

The mark  $\star$  shows major revised points.

#### PREFACE

- **Target Readers** This manual is intended for users who wish to understand the hardware functions of the NU85E and NU85EA, which are the CPU cores of a cell-based IC (CBIC), to design application systems using the NU85E or NU85EA.

- Purpose This manual is designed to help users understand the hardware functions of the NU85E and NU85EA outlined in Organization below.

- Organization This manual describes the hardware functions of the NU85E and NU85EA. For details about the architecture and instruction functions, refer to the "V850E1 User's Manual Architecture." The organization of each manual is as follows:

NU85E User's Manual Hardware (This manual) V850E1 User's Manual Architecture

Register set

- Overview

- CPU function

- Peripheral I/O functions

- Test functions

- Instruction format and instruction set

- Interrupts and exceptions

- Pipeline operation

#### How to Read This Manual

It is assumed that the readers of this manual have general knowledge of electricity, logic circuits, and microcontrollers.

To gain a general understanding of the hardware functions of the NU85E and NU85EA

$\rightarrow$  Read this manual according to the <code>CONTENTS</code>.

To confirm details of a function, etc. when the name is known

$\rightarrow$  Refer to **APPENDIX B INDEX**.

To learn about the details of an instruction function

$\rightarrow$  Refer to the V850E1 Architecture User's Manual (U14559E).

This document describes the NU85E as the representative product. When using the NU85EA, read NU85E as NU85EA.

Conventions Data significance: Higher digits on the left and lower digits on the right xxxZ (Z after pin or signal name) Active low representation: Note: Footnote for item marked with Note in the text Caution: Information requiring particular attention Remark: Supplementary information Binary ... xxxx or xxxxB Numerical representation: Decimal ... xxxx Hexadecimal ... xxxxH Prefix indicating the power of 2 (address space, memory capacity): K (kilo)  $\dots 2^{10} = 1,024$ M (mega) ...  $2^{20} = 1,024^2$ G (giga) ...  $2^{30} = 1,024^{3}$ ... 32 bits Word Data type: Halfword ... 16 bits Byte ... 8 bits

#### **Related Documents**

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

- V850E1 Architecture User's Manual (U14559E)

- Memory Controller NU85E, NU85ET User's Manual (A15019E)

- Instruction Cache, Data Cache NU85E, NU85ET User's Manual (A15241E)

- CB-10 Family VX Type NU85E, NU85ET Design Manual (A15401E)

- CB-10 Family VX Type Core Library CPU Core, Peripheral Design Manual (A15133E)

The related documents listed above are subject to change without notice. Be sure to use the latest version of each document for designing.

#### CONTENTS

| CHAPT | er 1 in  | ITRODUCTION                              | 17 |

|-------|----------|------------------------------------------|----|

| 1.1   | Outline  | e                                        | 17 |

| 1.2   | Applica  | ation System Example                     |    |

| 1.3   | Feature  | es                                       | 19 |

| 1.4   | Symbo    | ol Diagram                               | 21 |

| 1.5   | Function | on Blocks                                | 22 |

|       | 1.5.1    | Internal block diagram                   | 22 |

|       | 1.5.2    | Internal units                           |    |

| 1.6   | Functio  | onal Differences Between NU85E and NB85E | 24 |

| CHAPT | ER 2 PI  | N FUNCTIONS                              | 25 |

| 2.1   | List of  | Pin Functions                            | 25 |

| 2.2   | Explan   | nation of Pin Functions                  | 29 |

|       | 2.2.1    | NPB pins                                 | 29 |

|       | 2.2.2    | VSB pins                                 |    |

|       | 2.2.3    | System control pins                      |    |

|       | 2.2.4    | DMAC pins                                |    |

|       | 2.2.5    | INTC pins                                |    |

|       | 2.2.6    | VFB pins                                 |    |

|       | 2.2.7    | VDB pins                                 |    |

|       | 2.2.8    | Instruction cache pins                   |    |

|       | 2.2.9    | Data cache pins                          |    |

|       | 2.2.10   | RCU pins                                 | 41 |

|       | 2.2.11   | Peripheral evaluation chip mode pins     | 41 |

|       | 2.2.12   | Operation mode setting pins              |    |

|       | 2.2.13   | Test mode pins                           | 44 |

| 2.3   | Recom    | nmended Connection of Unused Pins        |    |

| 2.4   | Pin Sta  | atus                                     |    |

| СНАРТ | ER 3 CI  | PU                                       |    |

| 3.1   |          | es                                       |    |

| 3.2   |          | ers                                      |    |

|       | 3.2.1    | Program registers                        |    |

|       | 3.2.2    | System registers                         |    |

| 3.3   | Addres   | ss Space                                 |    |

|       | 3.3.1    | Program area                             |    |

|       | 3.3.2    | Data area                                |    |

| 3.4   | Areas.   |                                          |    |

|       | 3.4.1    | ROM area                                 |    |

|       | 3.4.2    | RAM area                                 |    |

|       | 3.4.3    | Peripheral I/O area                      | 65 |

|       | 3.4.4    | External memory area                     |    |

| 3.5   | Periph   | eral I/O Registers                       |    |

|       | 3.5.1    | NU85E control registers                  |    |

|    |            | 3.5.2          | Memory controller (MEMC) control registers                                 | 71  |

|----|------------|----------------|----------------------------------------------------------------------------|-----|

|    |            | 3.5.3          | Instruction cache control registers                                        | 72  |

|    |            | 3.5.4          | Data cache control registers                                               | 72  |

|    | 3.6        | RCU Ir         | nterface                                                                   | 73  |

|    |            | 3.6.1          | Outline                                                                    | 73  |

|    |            | 3.6.2          | On-chip debugging                                                          | 73  |

|    |            |                |                                                                            | 74  |

| CH |            |                | CU                                                                         |     |

|    | 4.1<br>4.2 |                |                                                                            |     |

|    | 4.2<br>4.3 |                | ry Banks<br>Immable Chip Select Function                                   |     |

|    | 4.3<br>4.4 | -              | Immable Chip Select Function                                               |     |

|    | 4.4<br>4.5 |                | ze Setting Function                                                        |     |

|    | 4.5<br>4.6 |                | setting Function                                                           |     |

|    | 4.0        | 4.6.1          | Endian configuration register (BEC)                                        |     |

|    |            | 4.6.1<br>4.6.2 | Usage restrictions concerning big endian format with NEC development tools |     |

|    | 4.7        | -              | Configuration                                                              |     |

|    | 4.7<br>4.8 |                | telated Register Setting Examples                                          |     |

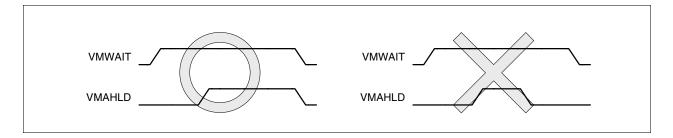

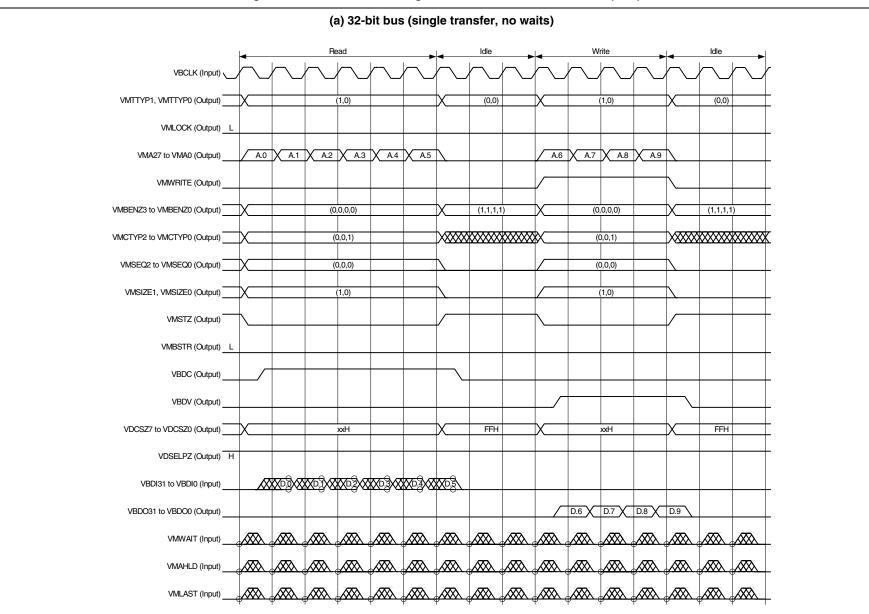

|    | 4.0<br>4.9 |                | ransfer Using VSB                                                          |     |

|    | 4.9        | 4.9.1          | Data transfer example                                                      |     |

|    |            | 4.9.1<br>4.9.2 | Control signals output by bus master                                       |     |

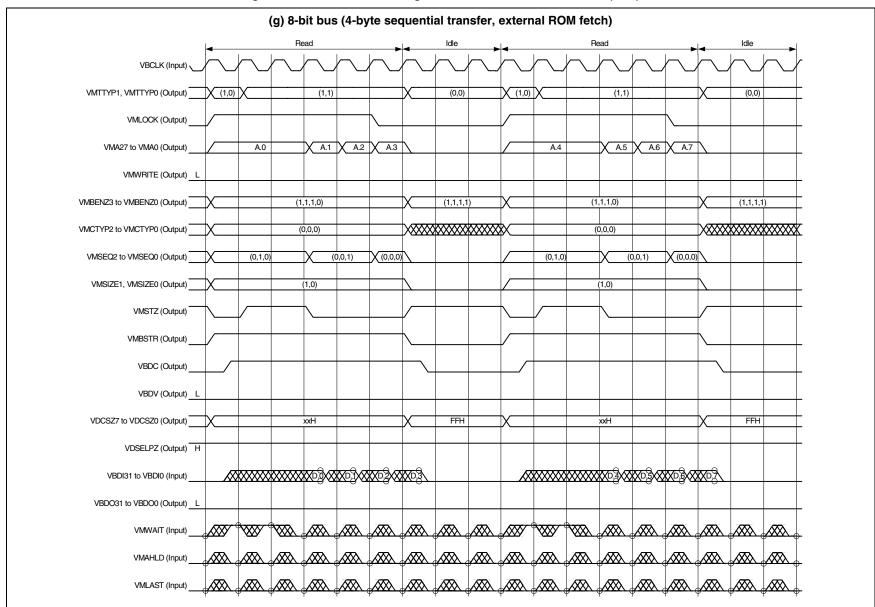

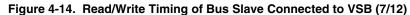

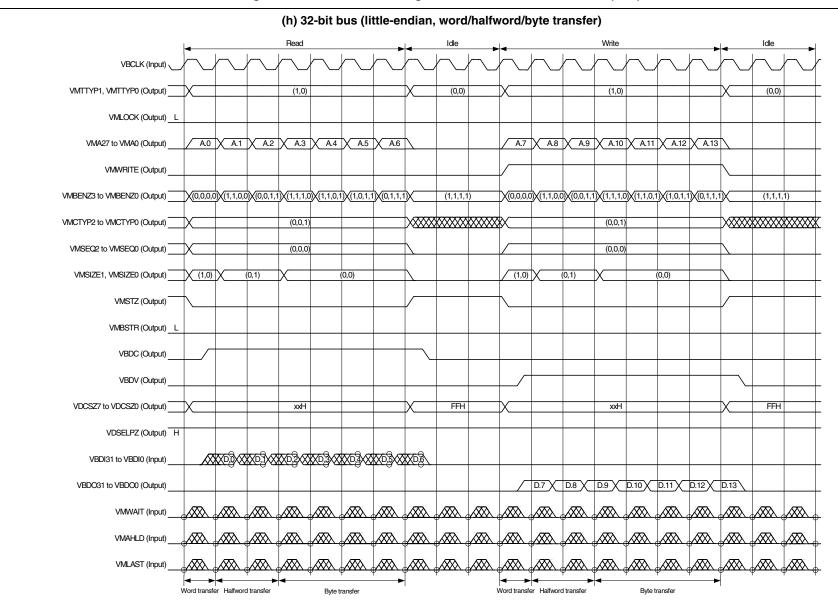

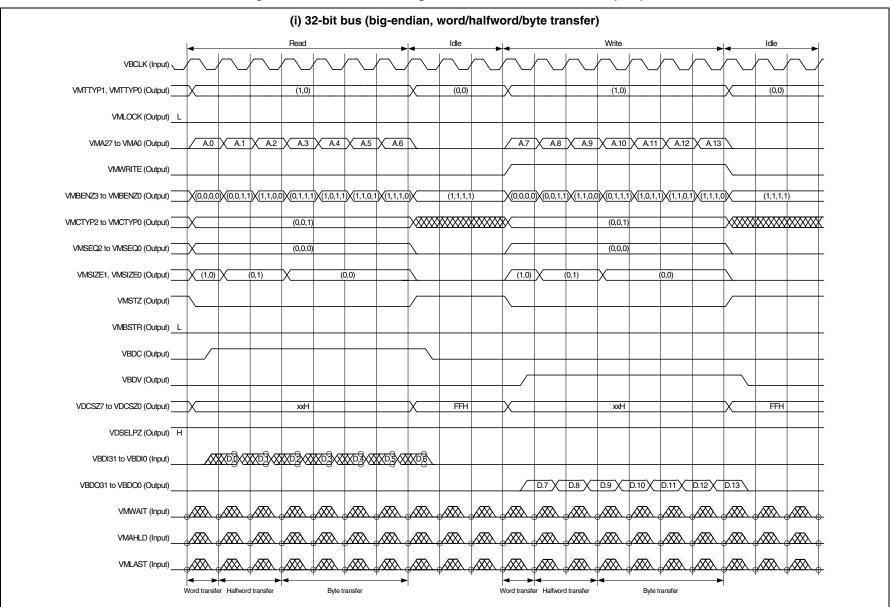

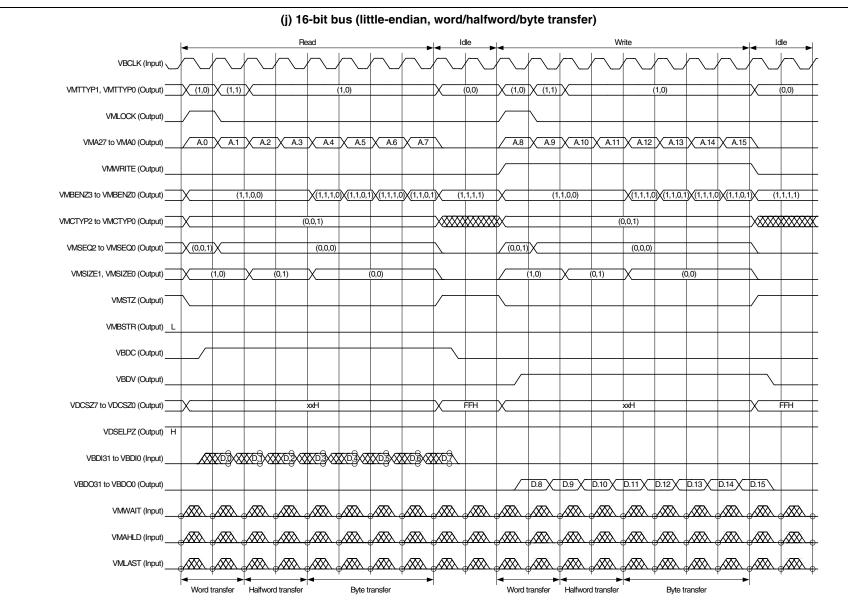

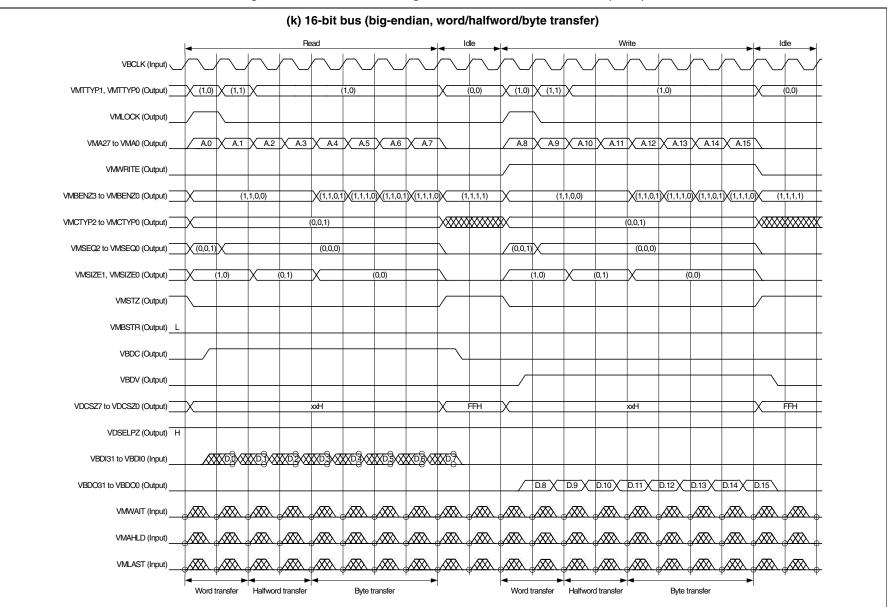

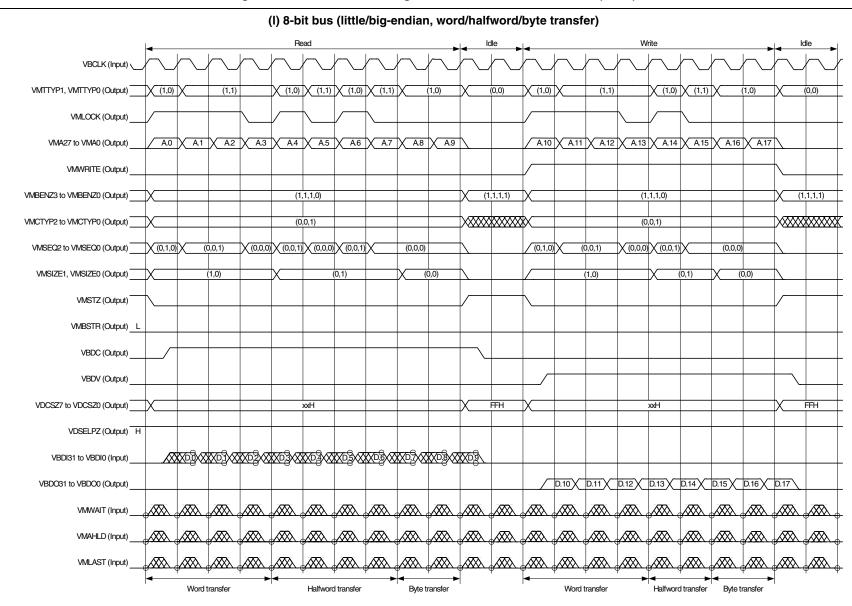

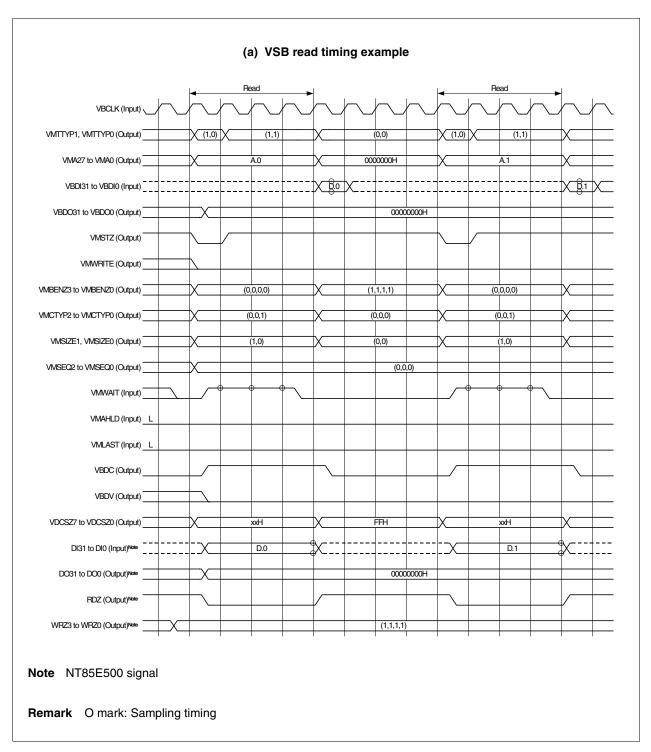

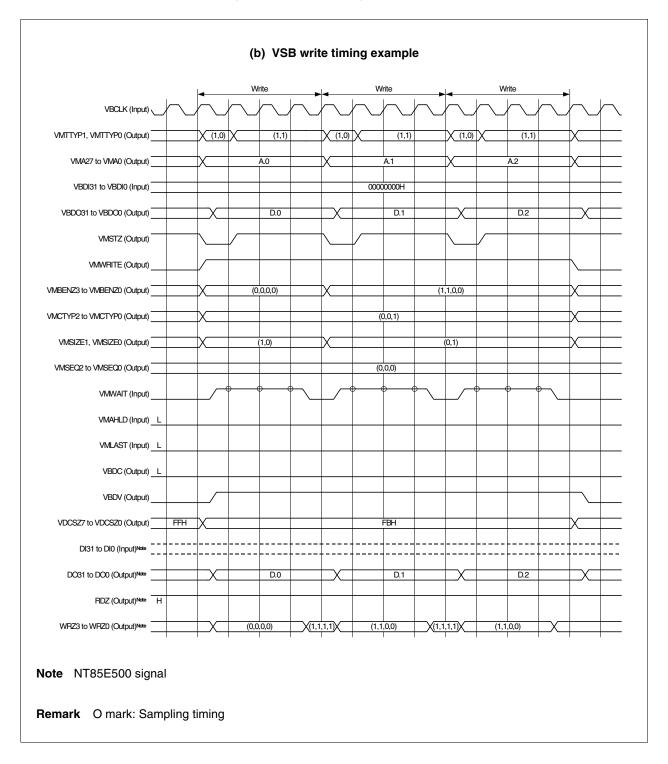

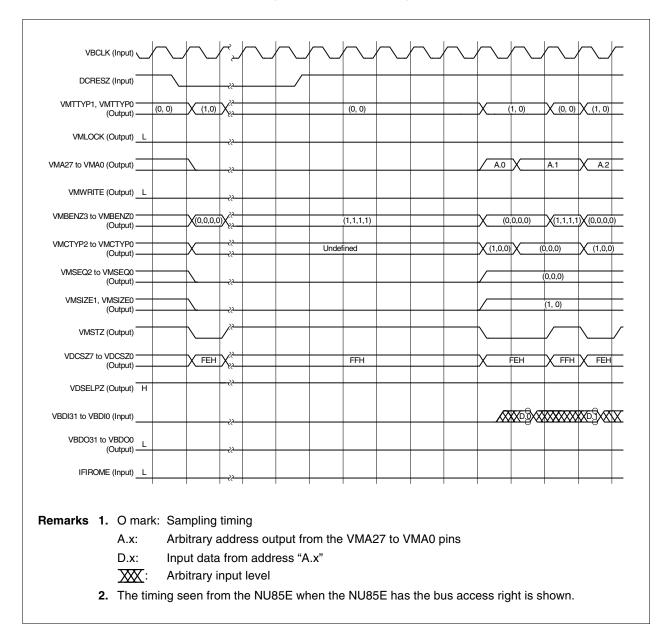

|    |            | 4.9.2<br>4.9.3 | Read/write timing                                                          |     |

|    |            | 4.9.3<br>4.9.4 | VSB read/write timing example                                              |     |

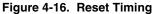

|    |            | 4.9.4<br>4.9.5 | Reset timing                                                               |     |

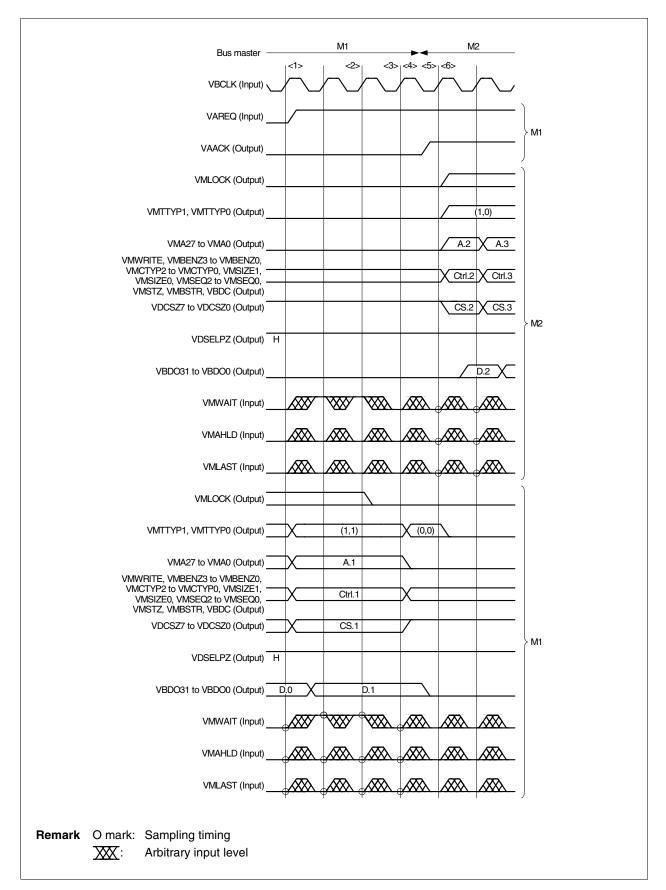

|    |            | 4.9.5<br>4.9.6 | Bus master transition                                                      |     |

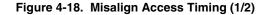

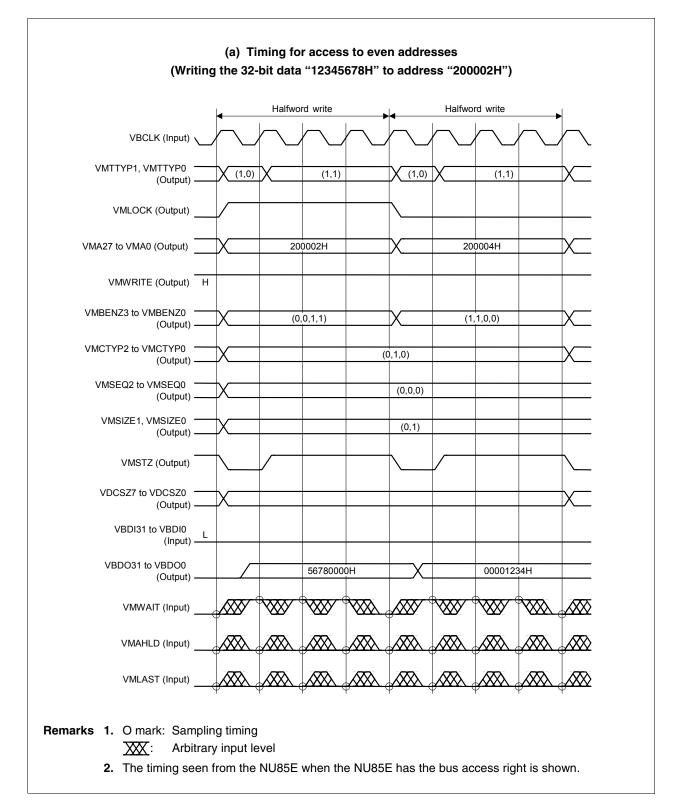

|    |            | 4.9.6<br>4.9.7 | Misalign access timing                                                     |     |

|    |            | 4.9.7          |                                                                            |     |

| СН | IAPT       | ER 5 BI        | BR                                                                         | 118 |

|    | 5.1        | Progra         | Immable Peripheral I/O Area                                                | 120 |

|    | 5.2        | Wait In        | sertion Function                                                           | 123 |

|    | 5.3        | Retry I        | Function                                                                   | 125 |

|    | 5.4        |                | ead/Write Timing                                                           |     |

| *  | 5.5        | Precau         | itions                                                                     | 135 |

| СН |            | ER6S           | ГВС                                                                        | 136 |

|    | 6.1        | Power          | Save Function                                                              | 136 |

|    | 6.2        | Contro         | ol Registers                                                               | 137 |

|    |            | 6.2.1          | Power save control register (PSC)                                          | 137 |

|    |            | 6.2.2          | Command register (PRCMD)                                                   | 139 |

|    | 6.3        | HALT           | Mode                                                                       | 140 |

|    | 6.4        | Softwa         | are STOP Mode                                                              | 141 |

|    | 6.5        | Hardw          | are STOP Mode                                                              | 143 |

|    | 6.6        | Clock          | Control in Software/Hardware STOP Mode                                     | 144 |

| СН |            | ER7DI          | MAC                                                                        | 149 |

|    | 7.1        | Featur         | es                                                                         | 149 |

|    | 7.2        | Config         | uration                                                                    | 150 |

|    | 7.3        | -              | er Objects                                                                 |     |

|    | -          |                | · · · · · · · · · · · · · · · · · · ·                                      |     |

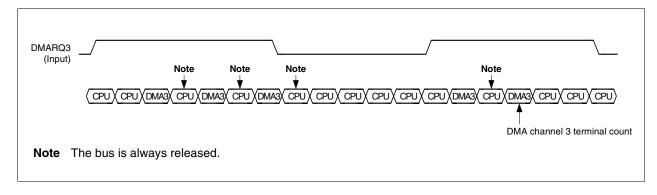

| 7.4   | DMA Channel Priorities                                                      |     |

|-------|-----------------------------------------------------------------------------|-----|

| 7.5   | Control Registers                                                           |     |

|       | 7.5.1 DMA source address registers 0 to 3 (DSA0 to DSA3)                    |     |

|       | 7.5.2 DMA destination address registers 0 to 3 (DDA0 to DDA3)               | 154 |

|       | 7.5.3 DMA transfer count registers 0 to 3 (DBC0 to DBC3)                    |     |

|       | 7.5.4 DMA addressing control registers 0 to 3 (DADC0 to DADC3)              | 157 |

|       | 7.5.5 DMA channel control registers 0 to 3 (DCHC0 to DCHC3)                 | 159 |

|       | 7.5.6 DMA disable status register (DDIS)                                    |     |

|       | 7.5.7 DMA restart register (DRST)                                           | 161 |

| 7.6   | Next Address Setting Function                                               |     |

| 7.7   | DMA Bus State                                                               |     |

|       | 7.7.1 Bus state types                                                       |     |

|       | 7.7.2 DMAC bus cycle state transitions                                      |     |

| 7.8   | Transfer Modes                                                              |     |

|       | 7.8.1 Single transfer mode                                                  |     |

|       | 7.8.2 Single-step transfer mode                                             |     |

|       | 7.8.3 Line transfer mode                                                    |     |

|       | 7.8.4 Block transfer mode                                                   | 171 |

|       | 7.8.5 One-time transfer when executing single transfers using DMARQn signal | 172 |

| 7.9   | Transfer Types                                                              |     |

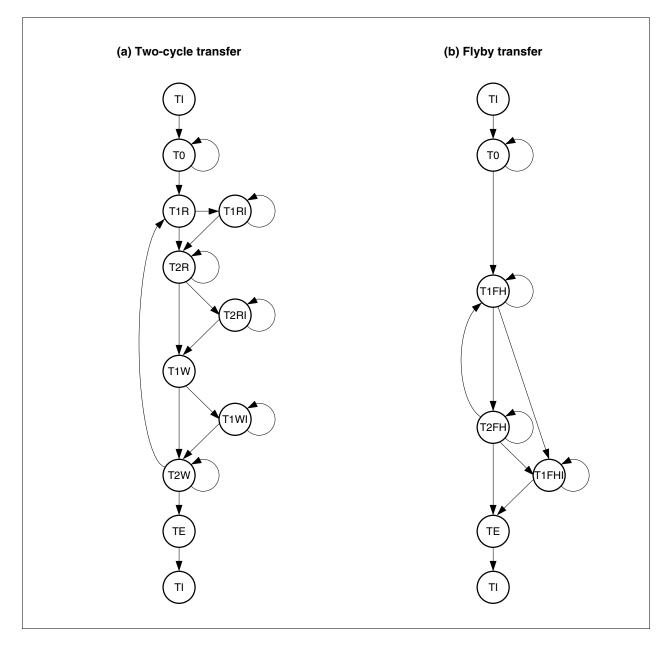

|       | 7.9.1 Two-cycle transfer                                                    |     |

|       | 7.9.2 Flyby transfer                                                        |     |

| 7.10  | DMA Transfer Start Factors                                                  |     |

| 7.11  | Terminal Count Output When DMA Transfer Is Complete                         |     |

| 7.12  | Forcible Interruption                                                       |     |

| 7.13  | Forcible Termination                                                        |     |

| 7.14  | DMA Transfer Timing Examples                                                |     |

| 7.15  | Precautions                                                                 | 204 |

|       |                                                                             |     |

| СНАРТ | ER 8 INTC                                                                   |     |

| 8.1   | Features                                                                    |     |

| 8.2   | Non-Maskable Interrupts (NMI)                                               |     |

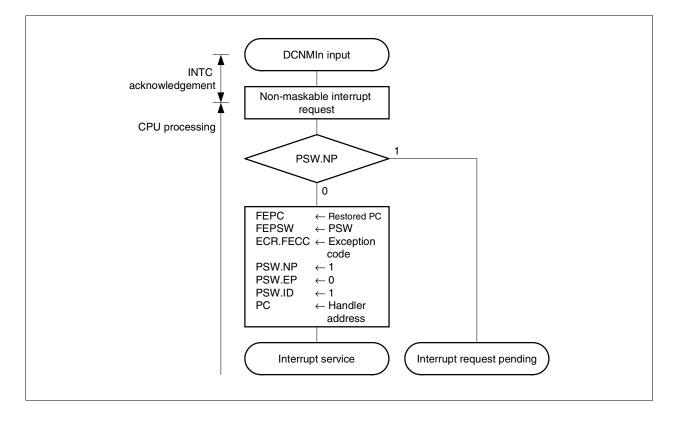

|       | 8.2.1 Operation                                                             | 212 |

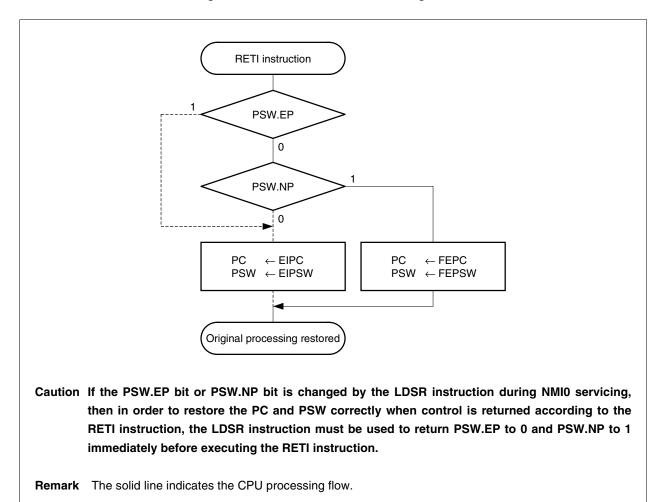

|       | 8.2.2 Restore                                                               | 213 |

| 8.3   | Maskable Interrupts                                                         | 214 |

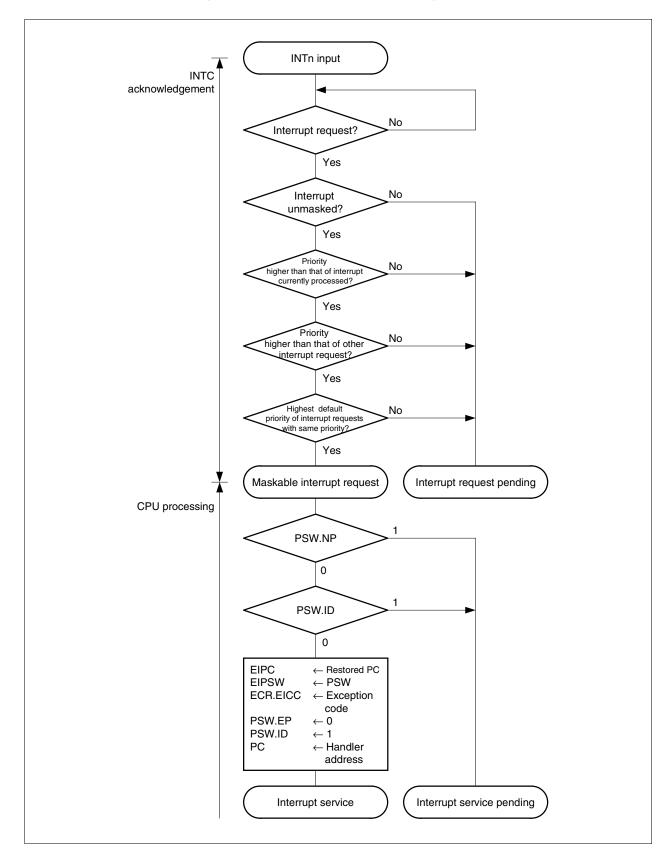

|       | 8.3.1 Operation                                                             | 214 |

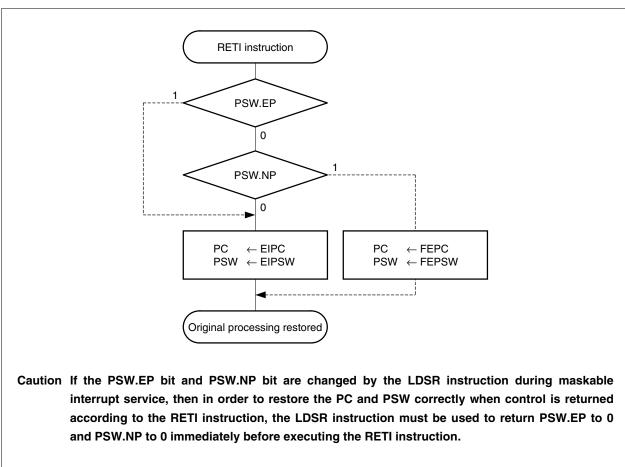

|       | 8.3.2 Restore                                                               | 216 |

|       | 8.3.3 Maskable interrupt priorities                                         | 217 |

|       | 8.3.4 Control registers                                                     | 221 |

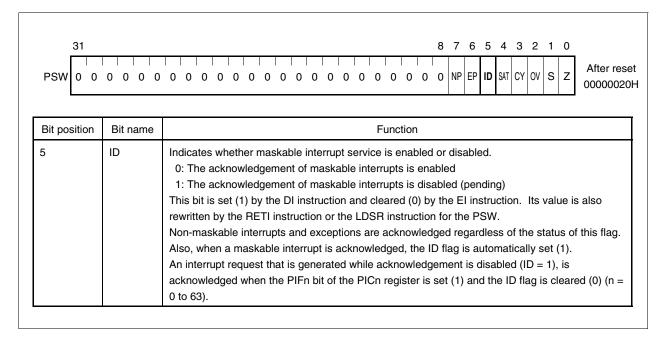

|       | 8.3.5 Maskable interrupt status flag (ID)                                   |     |

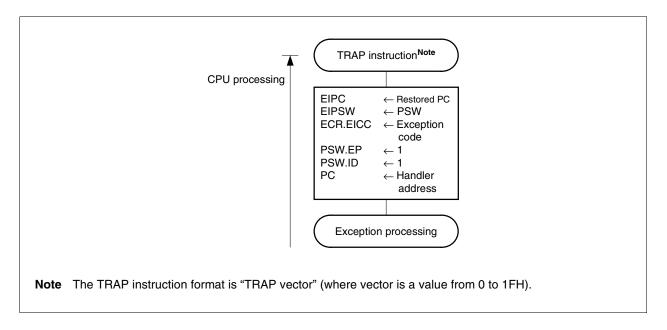

| 8.4   | Software Exception                                                          |     |

|       | 8.4.1 Operation                                                             |     |

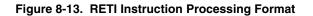

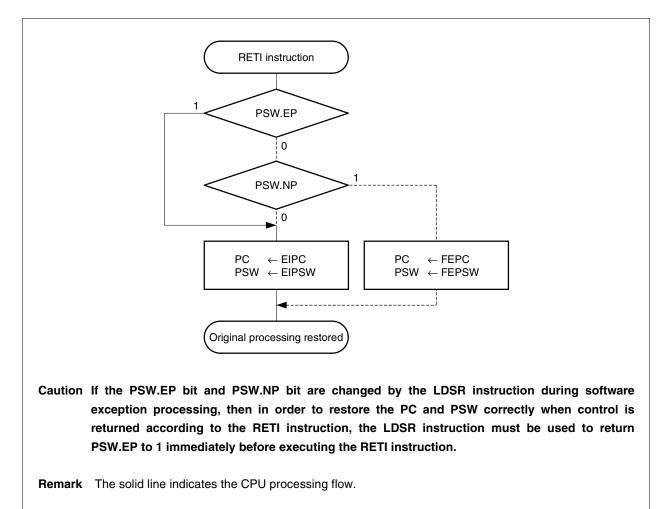

|       | 8.4.2 Restore                                                               |     |

| 8.5   | Exception Trap                                                              |     |

|       | 8.5.1 Illegal opcode                                                        |     |

|       | 8.5.2 Operation                                                             |     |

|       | 8.5.3 Restore                                                               |     |

| 8.6   | Interrupt Response Time                                                     |     |

|       | · · · · · · · · · · · · · · · · · · ·                                       |     |

| 8.7    | Periods  | s When Interrupts Cannot Be Acknowledged                          | 229 |

|--------|----------|-------------------------------------------------------------------|-----|

| СНАРТЕ | ER9 TE   | ST FUNCTION                                                       | 230 |

| 9.1    | Test Pi  | ns                                                                | 230 |

|        | 9.1.1    | Test bus pins (TBI39 to TBI0 and TBO34 to TBO0)                   | 230 |

|        | 9.1.2    | BUNRI and TEST pins                                               | 230 |

|        | 9.1.3    | BUNRIOUT pin                                                      | 231 |

| 9.2    | List of  | Test Interface Signals                                            | 231 |

| 9.3    | Examp    | le of Connection of Peripheral Macro in Test Mode                 | 232 |

| 9.4    | Handlir  | ng of Each Pin in Test Mode                                       | 233 |

| СНАРТЕ | ER 10 N  | B85E901                                                           | 234 |

| 10.1   | Symbo    | I Diagram                                                         | 234 |

| 10.2   | Pin Fur  | nctions                                                           | 235 |

|        | 10.2.1   | Pin function list                                                 | 235 |

|        | 10.2.2   | Pin functions                                                     | 236 |

|        | 10.2.3   | Recommended connection of unused pins                             | 239 |

|        | 10.2.4   | Pin status                                                        | 240 |

| 10.3   | Debug    | Function                                                          | 242 |

| 10.4   | NU85E    | Connection Example                                                | 243 |

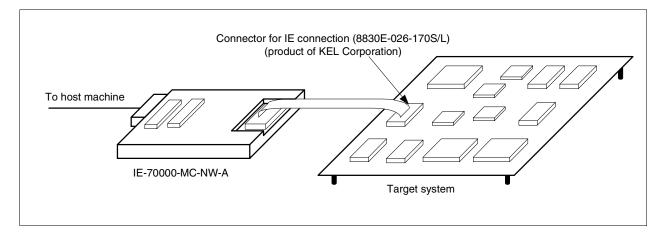

| 10.5   | N-Wire   | Type IE Connection                                                | 244 |

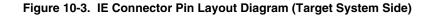

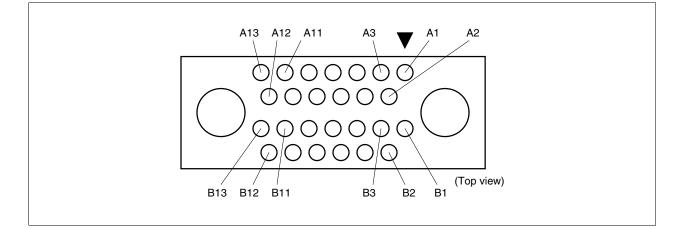

|        | 10.5.1   | IE connector (target system side)                                 | 244 |

|        | 10.5.2   | Example of recommended circuit when connecting NB85E901 and NU85E | 246 |

| APPEN  | DIX A R  | OM/RAM ACCESS TIMING                                              | 247 |

| APPEN  | DIX B IN | IDEX                                                              | 249 |

|        | DIX C R  | EVISION HISTORY                                                   | 254 |

# LIST OF FIGURES (1/3)

| <u>Figure</u> | e No. Title                                                     | Page |

|---------------|-----------------------------------------------------------------|------|

| 2-1           | Acknowledgement of DCRESZ Signal                                |      |

| 2-2           | Stopping VBCLK Oscillation by System Reset                      | 35   |

| 3-1           | List of CPU Registers                                           | 52   |

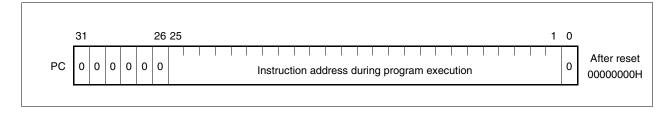

| 3-2           | Program Counter (PC)                                            | 54   |

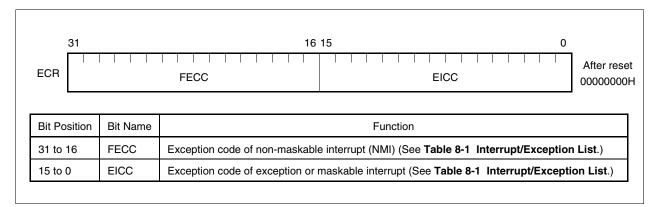

| 3-3           | Interrupt Source Register (ECR)                                 | 56   |

| 3-4           | Program Status Word (PSW)                                       | 57   |

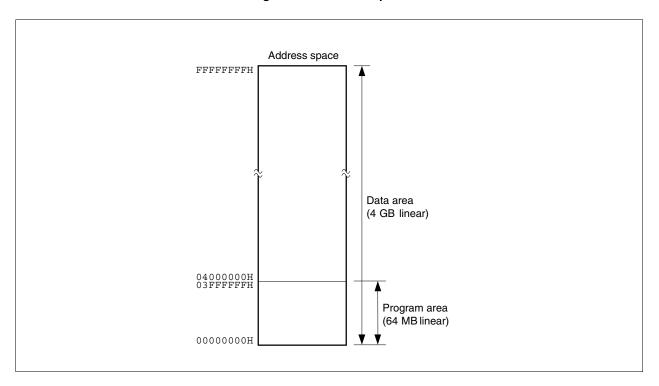

| 3-5           | Address Space                                                   | 58   |

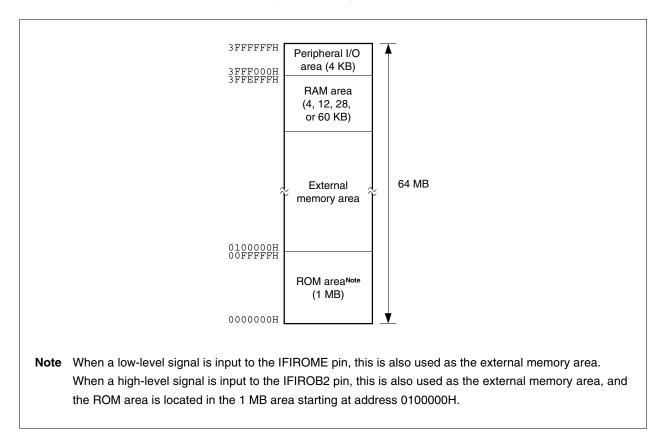

| 3-6           | Program Area                                                    | 59   |

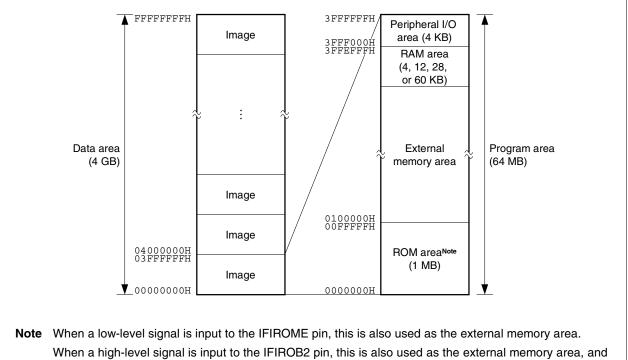

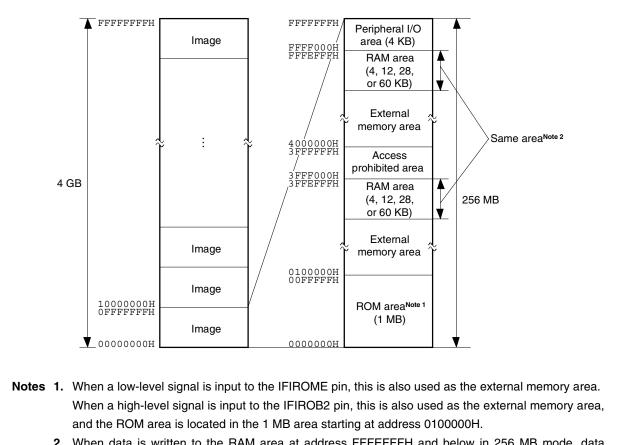

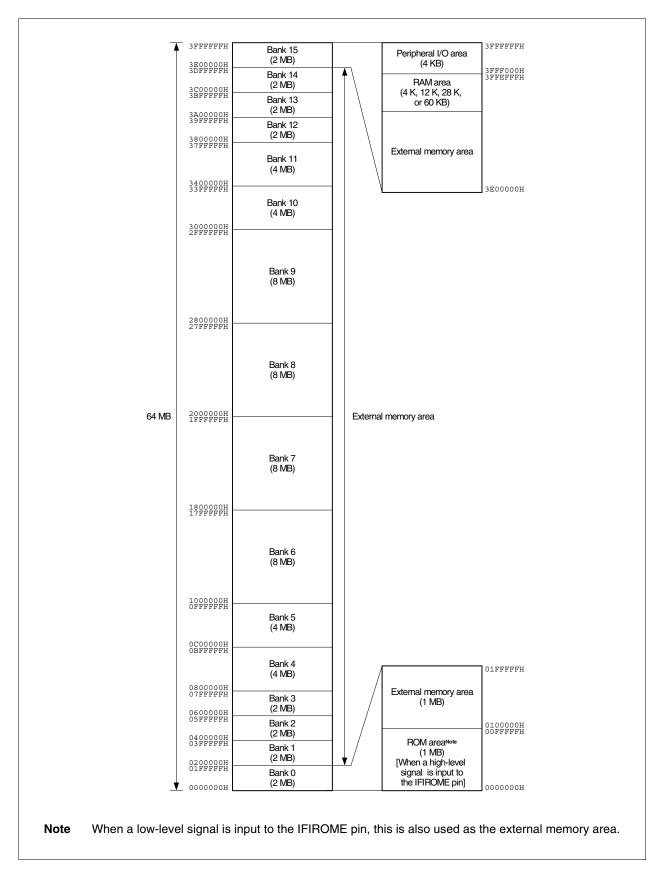

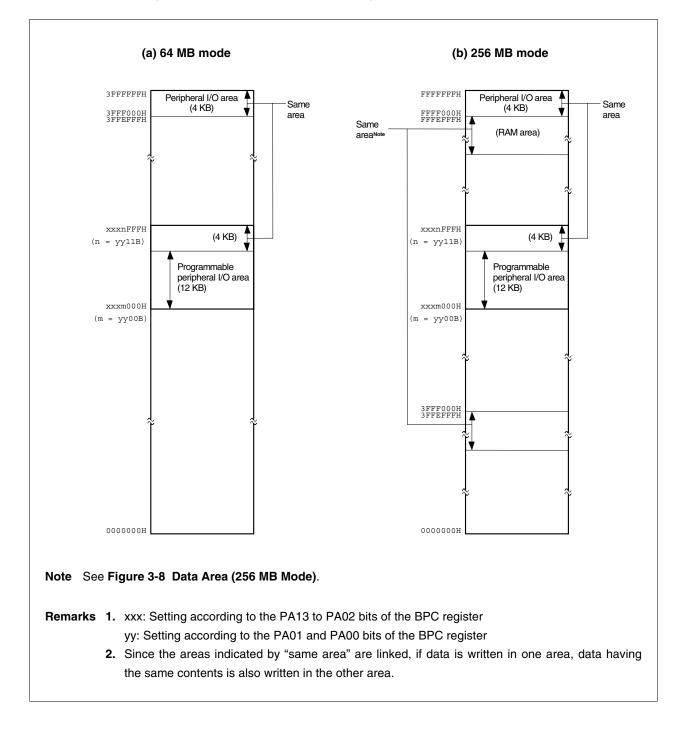

| 3-7           | Data Area (64 MB Mode)                                          | 60   |

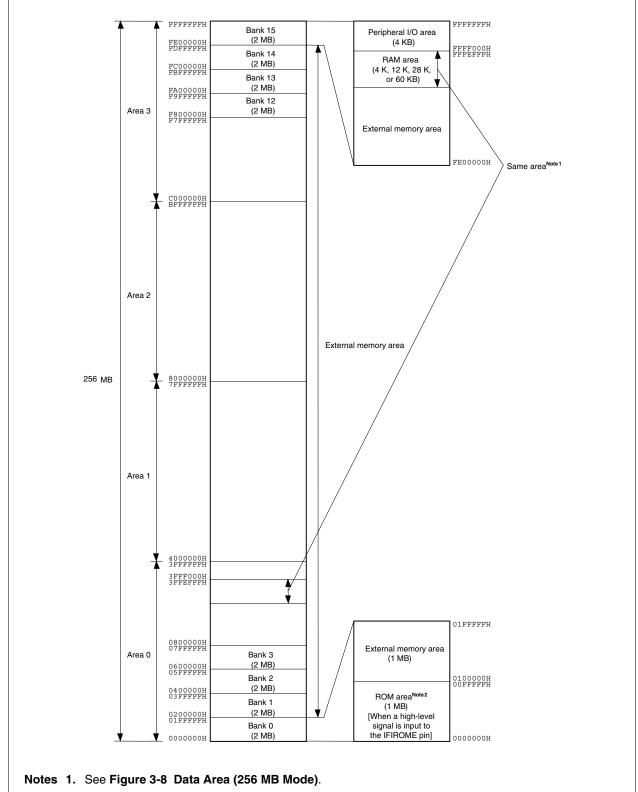

| 3-8           | Data Area (256 MB Mode)                                         | 61   |

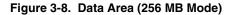

| 3-9           | ROM Area                                                        | 62   |

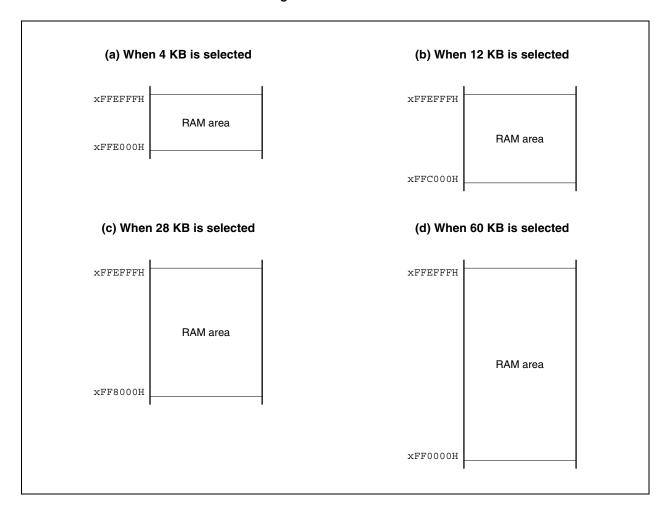

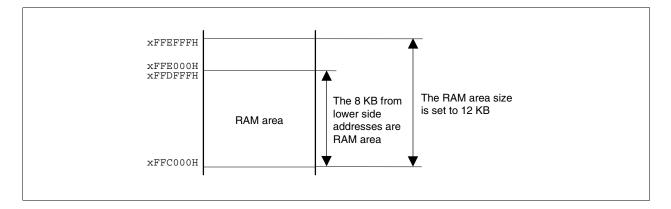

| 3-10          | RAM Area                                                        | 64   |

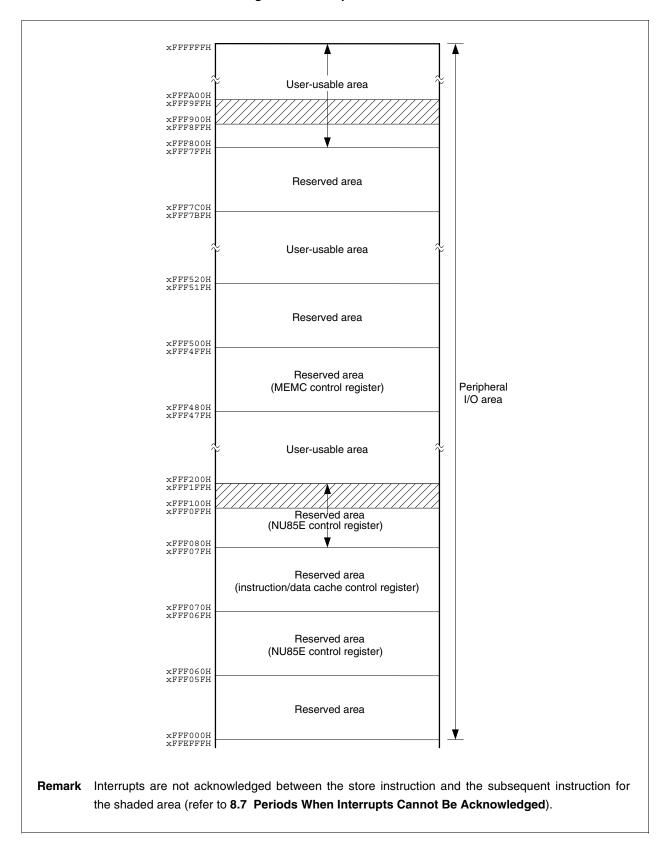

| 3-11          | Peripheral I/O Area                                             | 66   |

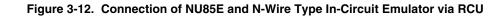

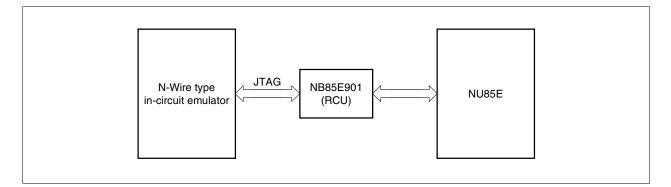

| 3-12          | Connection of NU85E and N-Wire Type In-Circuit Emulator via RCU | 73   |

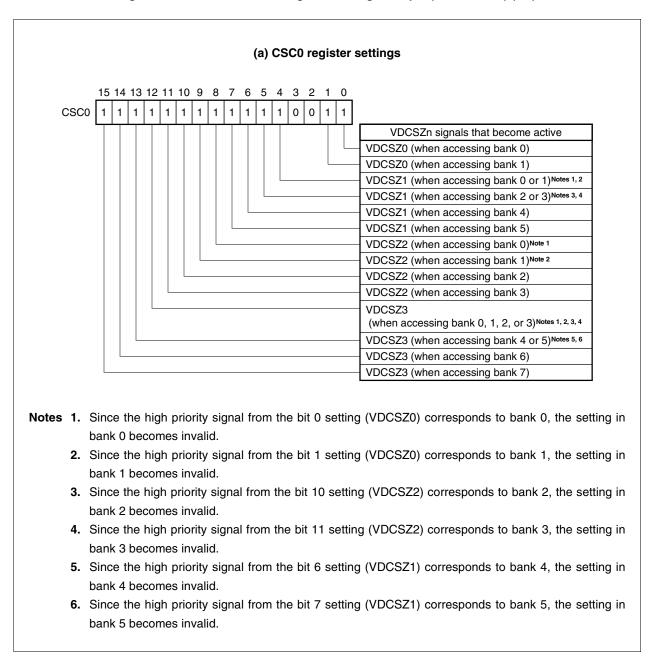

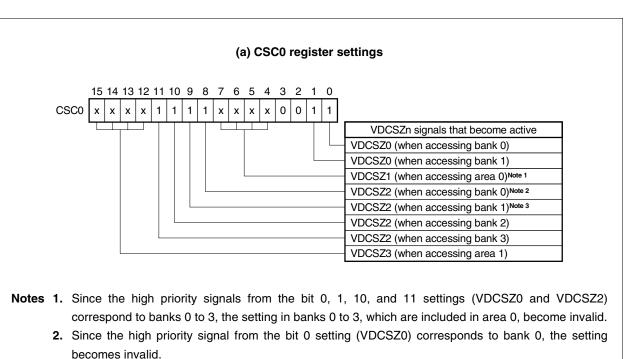

| 4-1           | Chip Area Select Control Register 0 (CSC0)                      | 77   |

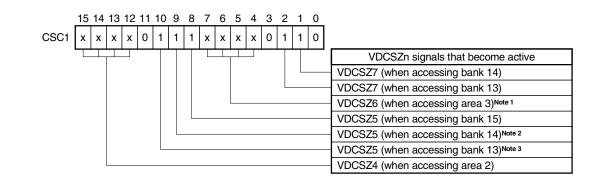

| 4-2           | Chip Area Select Control Register 1 (CSC1)                      | 78   |

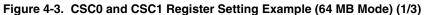

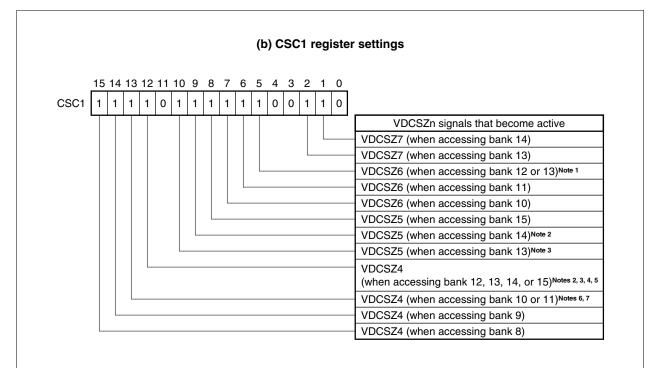

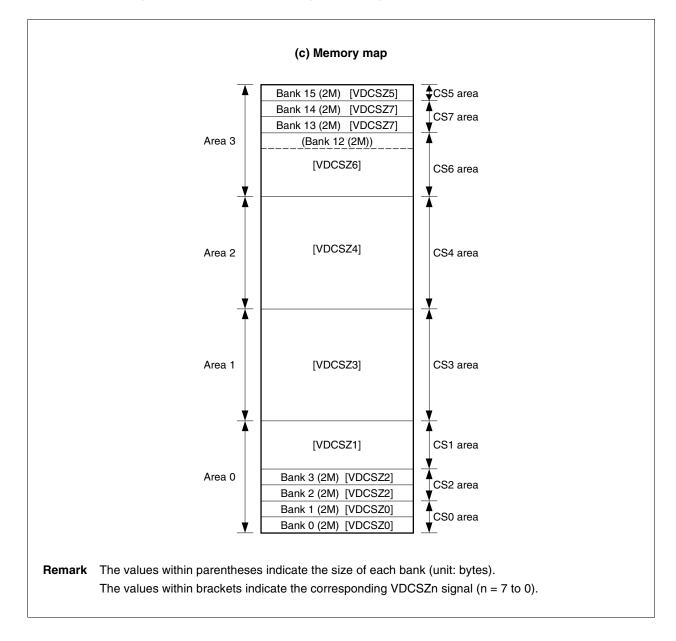

| 4-3           | CSC0 and CSC1 Register Setting Example (64 MB Mode)             | 79   |

| 4-4           | CSC0 and CSC1 Register Setting Example (256 MB Mode)            | 82   |

| 4-5           | Peripheral I/O Area and Programmable Peripheral I/O Area        | 84   |

| 4-6           | Peripheral I/O Area Select Control Register (BPC)               | 85   |

| 4-7           | Bus Size Configuration Register (BSC)                           | 86   |

| 4-8           | Endian Configuration Register (BEC)                             | 87   |

| 4-9           | Word Data Little Endian Format Example                          | 88   |

| 4-10          | Word Data Big Endian Format Example                             | 88   |

| 4-11          | Cache Configuration Register (BHC)                              | 90   |

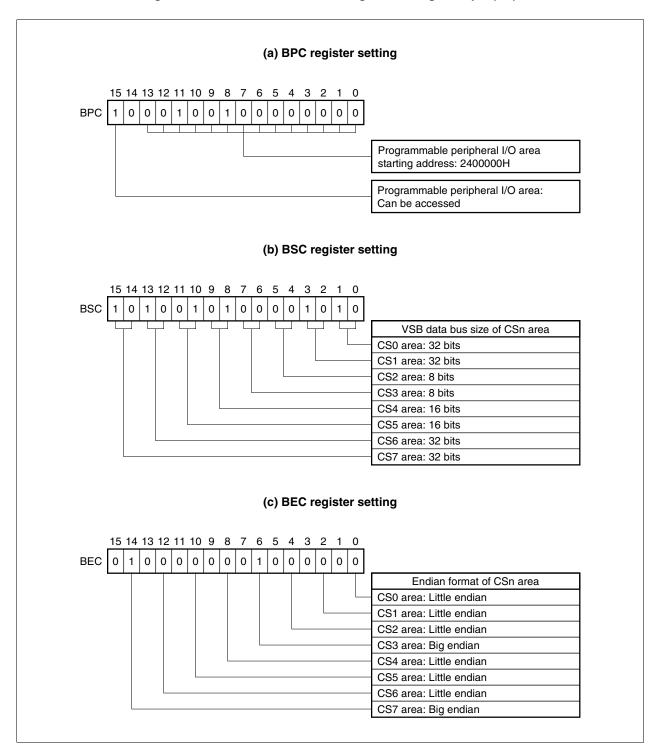

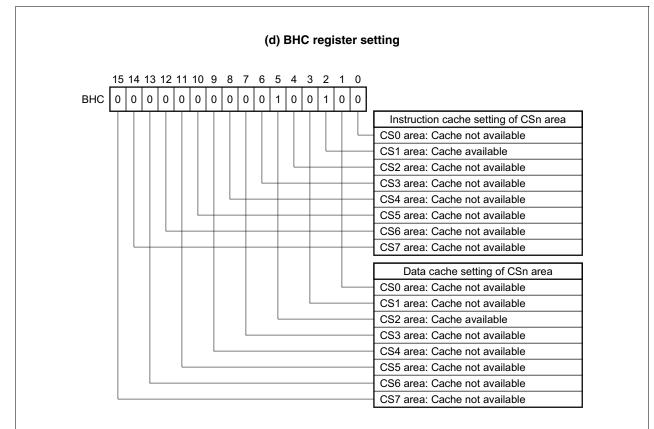

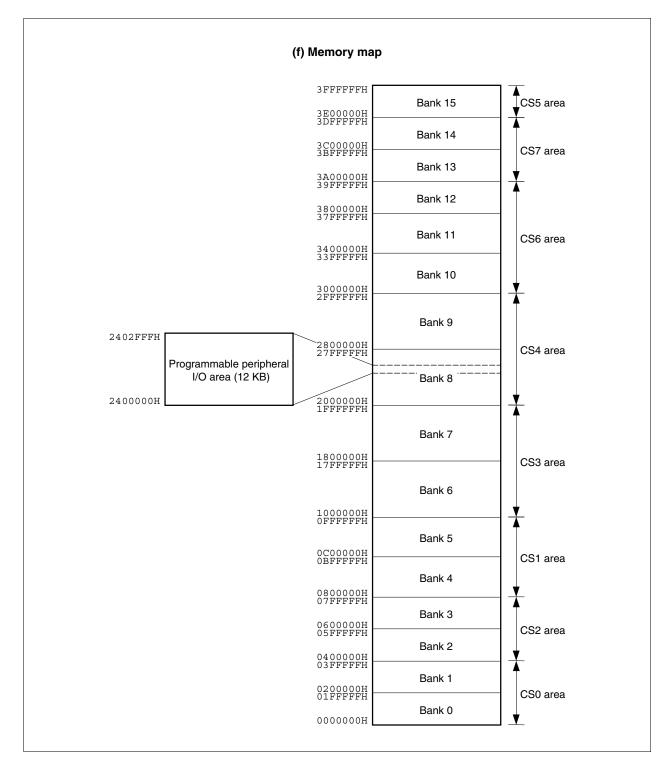

| 4-12          | BPC, BSC, BEC, BHC Register Setting Example                     | 91   |

| 4-13          | Example of Data Transfer Using VSB                              | 94   |

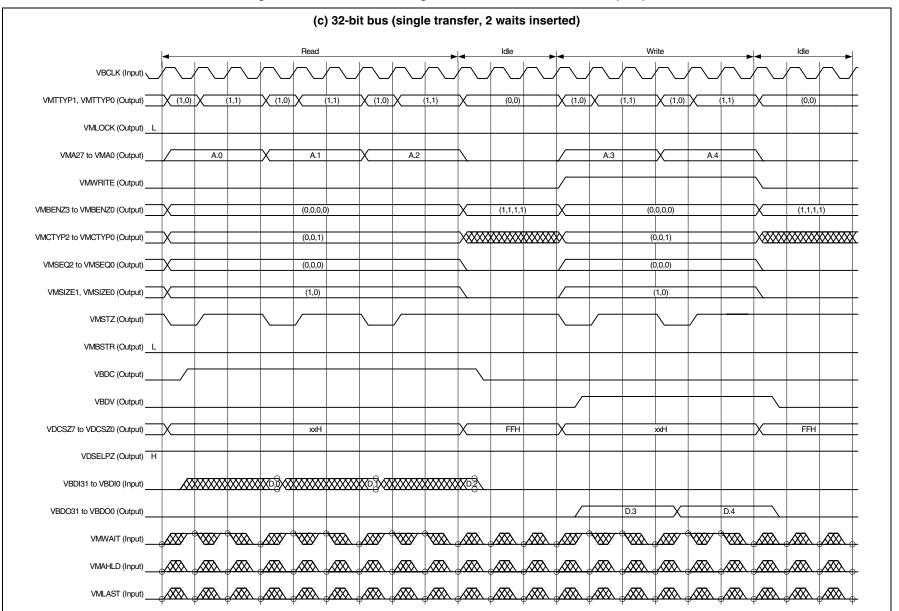

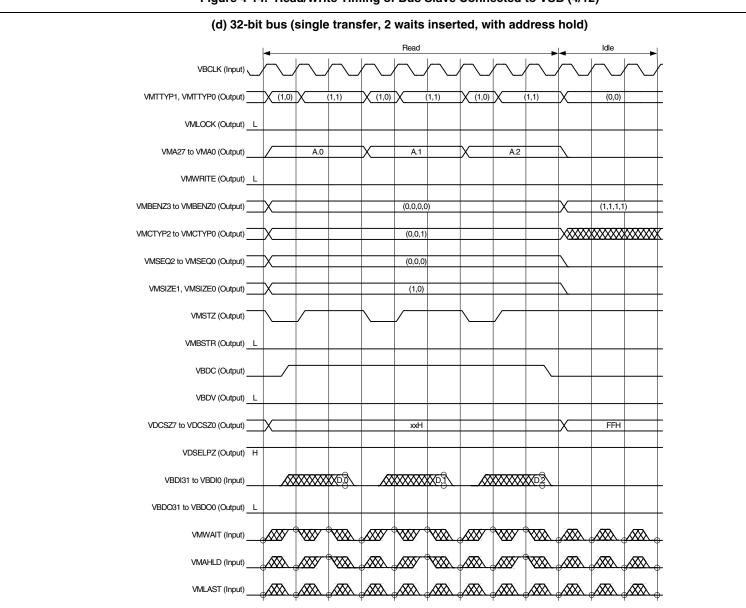

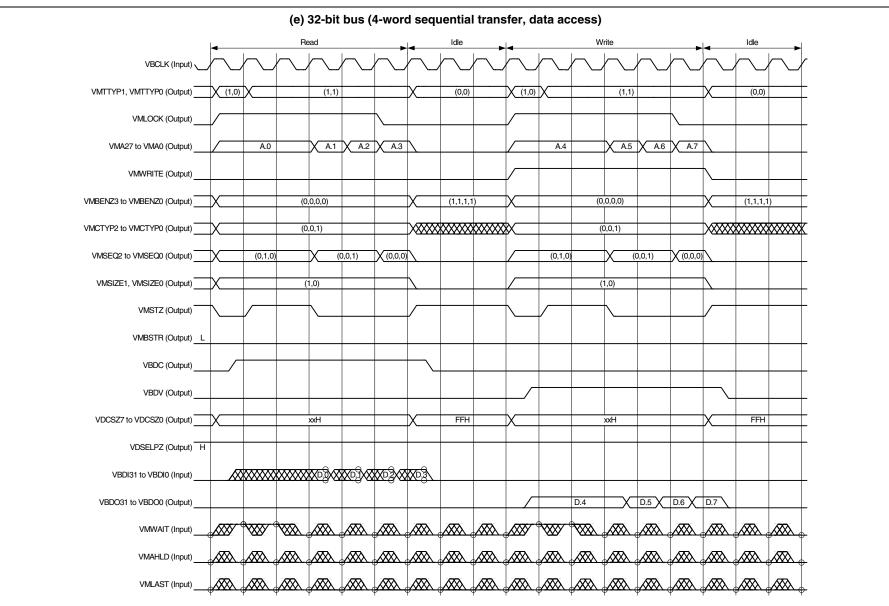

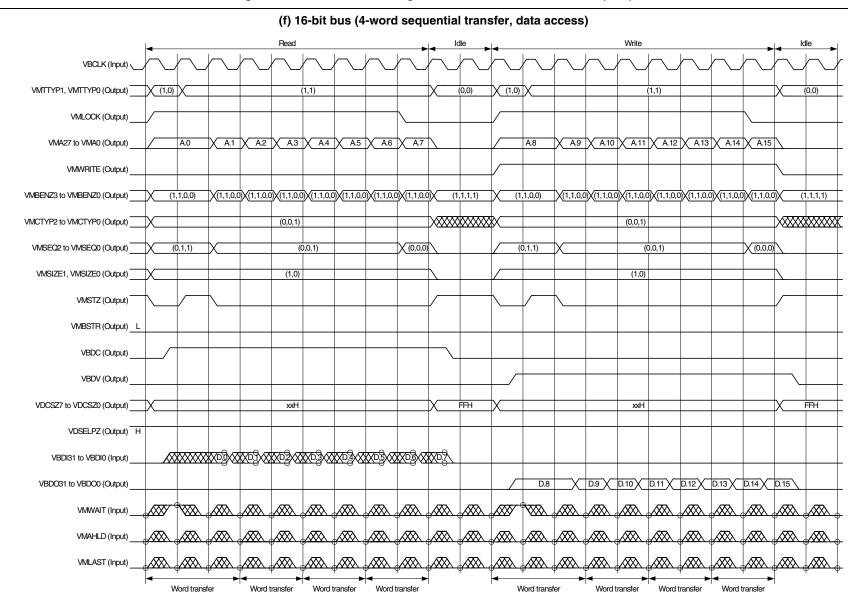

| 4-14          | Read/Write Timing of Bus Slave Connected to VSB                 | 99   |

| 4-15          | VSB Timing Example                                              | 111  |

| 4-16          | Reset Timing                                                    | 113  |

| 4-17          | Bus Master Transition Timing                                    |      |

| 4-18          | Misalign Access Timing                                          | 116  |

| 5-1           | NPB Connection Overview                                         |      |

| 5-2           | NU85E and Peripheral Macro Connection Example                   |      |

| 5-3           | Peripheral I/O Area and Programmable Peripheral I/O Area        |      |

| 5-4           | Peripheral I/O Area Select Control Register (BPC)               |      |

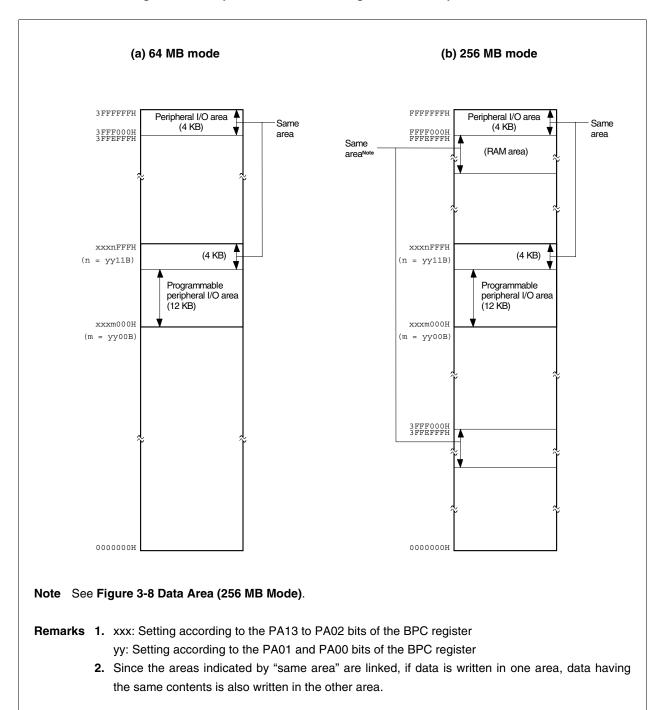

| 5-5           | BPC Register Setting Example                                    |      |

| 5-6           | NPB Strobe Wait Control Register (VSWC)                         |      |

| 5-7           | Retry Function                                                  |      |

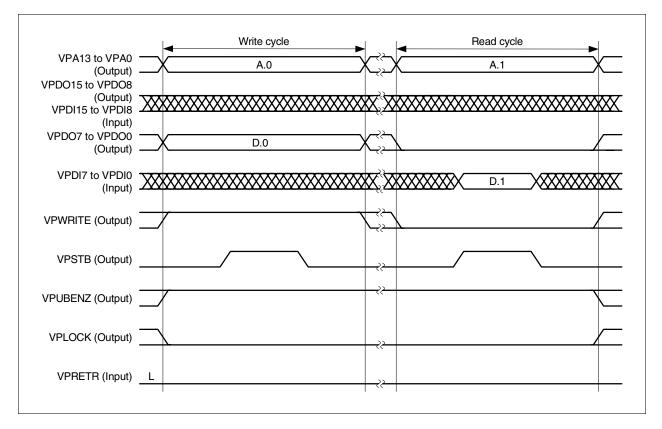

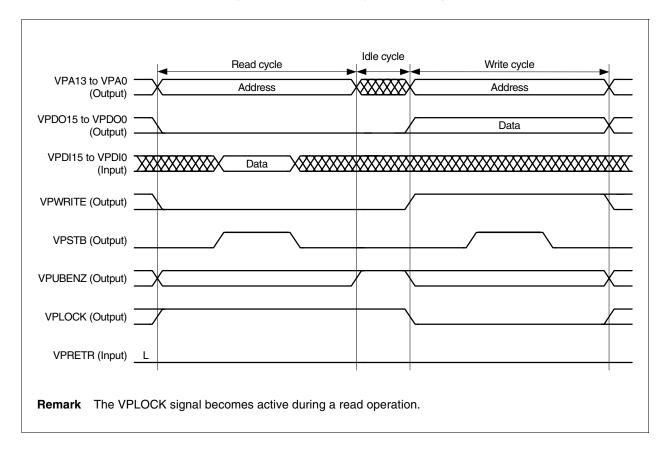

| 5-8           | Halfword Access Timing                                          |      |

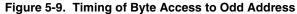

| 5-9           | Timing of Byte Access to Odd Address                            |      |

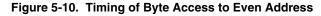

| 5-10          | Timing of Byte Access to Even Address                           |      |

# LIST OF FIGURES (2/3)

| <u>Figure</u> | e No. Title                                                                                    | Page |

|---------------|------------------------------------------------------------------------------------------------|------|

| 5-11          | Read Modify Write Timing                                                                       | 128  |

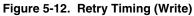

| 5-12          | Retry Timing (Write)                                                                           | 128  |

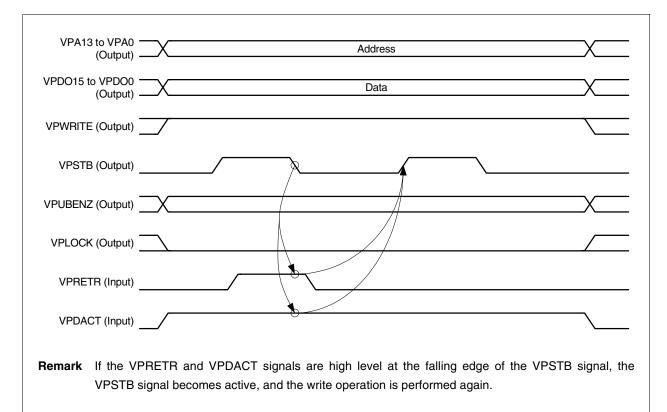

| 5-13          | Retry Timing (Read)                                                                            |      |

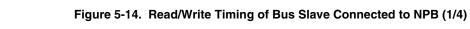

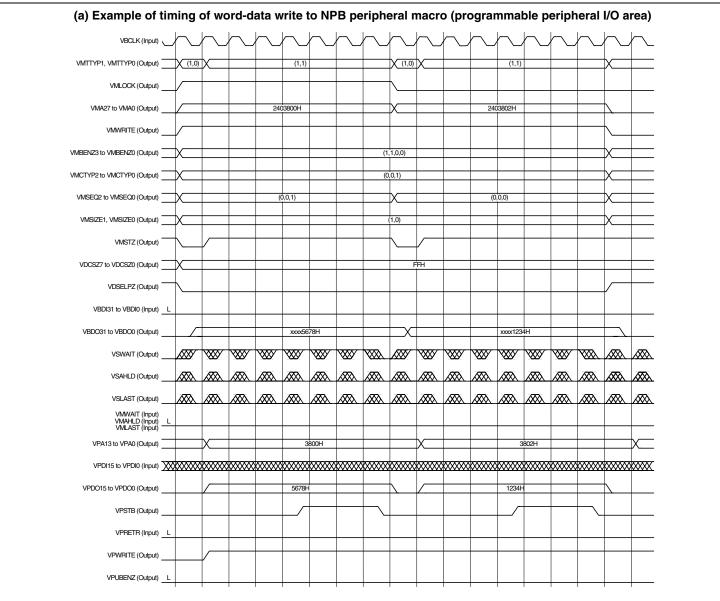

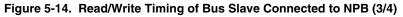

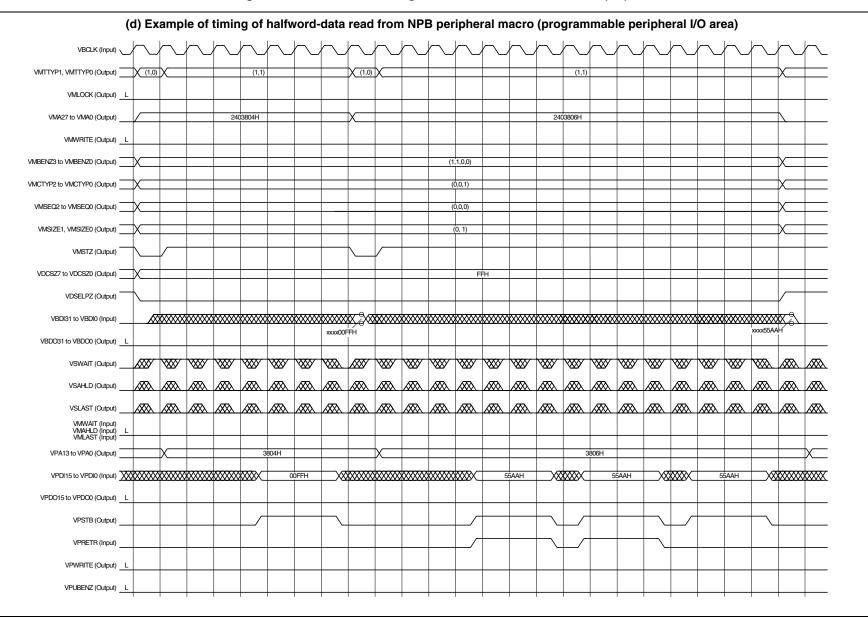

| 5-14          | Read/Write Timing of Bus Slave Connected to NPB                                                |      |

| 5-15          | NPB Write Timing (Example of Timing of Data Write to CSC0 and CSC1 Registers)                  |      |

|               |                                                                                                |      |

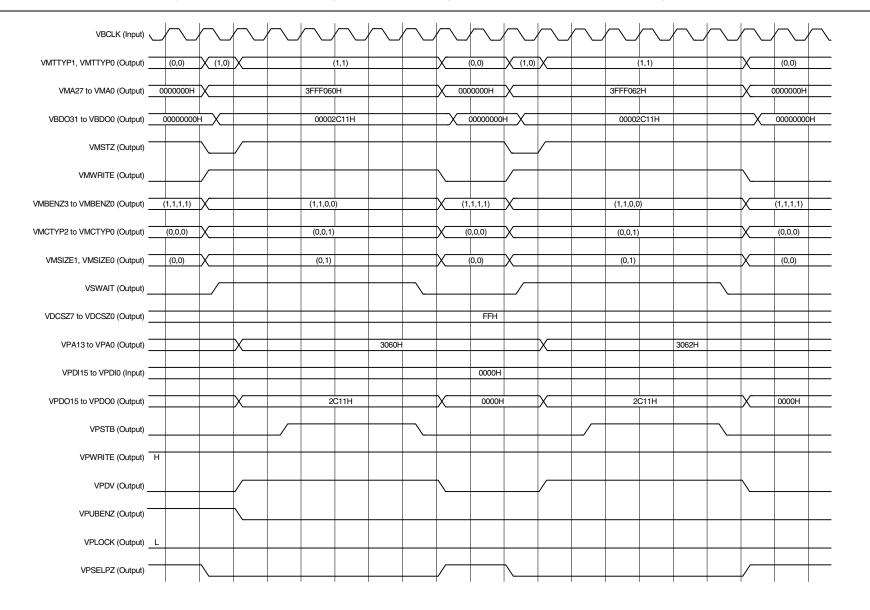

| 6-1           | Power Save Function State Transition Diagram                                                   | 136  |

| 6-2           | Power Save Control Register (PSC)                                                              | 137  |

| 6-3           | Command Register (PRCMD)                                                                       | 139  |

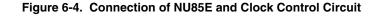

| 6-4           | Connection of NU85E and Clock Control Circuit                                                  | 144  |

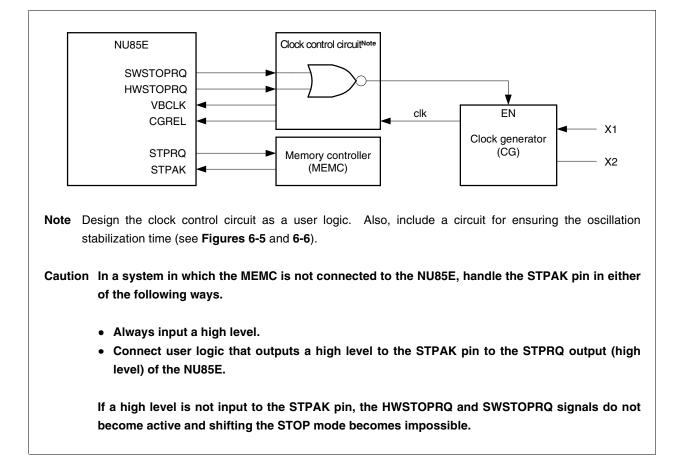

| 6-5           | Software STOP Mode Set/Cancel Timing Example                                                   | 146  |

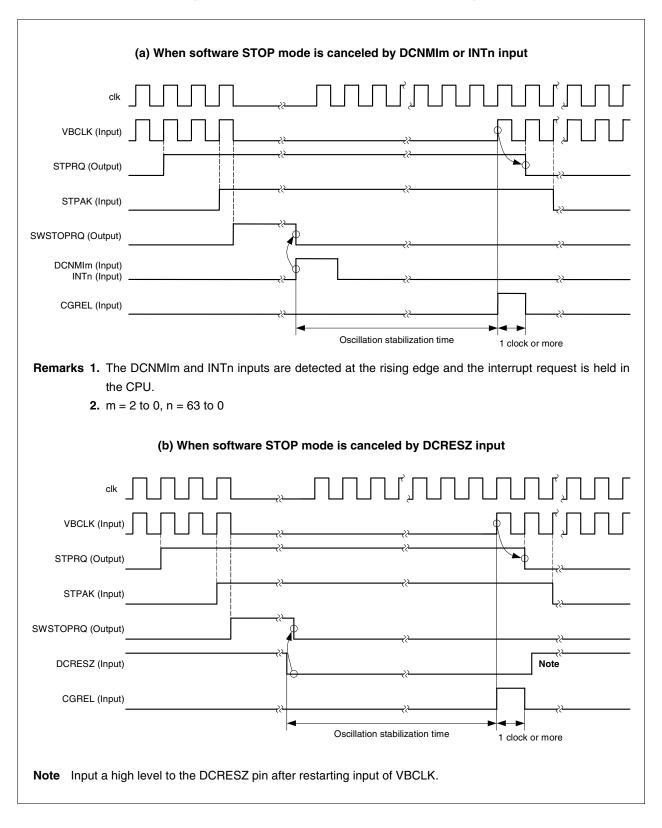

| 6-6           | Hardware STOP Mode Set/Cancel Timing Example                                                   | 148  |

| 7-1           | DMA Source Address Registers 0H to 3H (DSA0H to DSA3H)                                         | 152  |

| <br>7-2       | DMA Source Address Registers 0L to 3L (DSA0L to DSA3L)                                         |      |

| 7-3           | DMA Destination Address Registers 0H to 3H (DDA0H to DDA3H)                                    |      |

| 7-4           | DMA Destination Address Registers 0L to 3L (DDA0L to DDA3L)                                    |      |

| 7-5           | DMA Transfer Count Registers 0 to 3 (DBC0 to DBC3)                                             |      |

| 7-6           | DMA Addressing Control Registers 0 to 3 (DADC0 to DADC3)                                       |      |

| 7-0<br>7-7    | DMA Channel Control Registers 0 to 3 (DCHC0 to DCHC3)                                          |      |

| 7-8           | DMA Challel Control Registers 0 to 3 (DCRC0 to DCRC5)                                          |      |

| 7-8<br>7-9    | DMA Bisable Status Register (DBIS)                                                             |      |

| -             |                                                                                                |      |

| 7-10<br>7-11  | Buffer Register Configuration                                                                  |      |

|               | DMAC Bus Cycle State Transition Diagram                                                        |      |

| 7-12          | Single Transfer Example 1                                                                      |      |

| 7-13          | Single Transfer Example 2                                                                      |      |

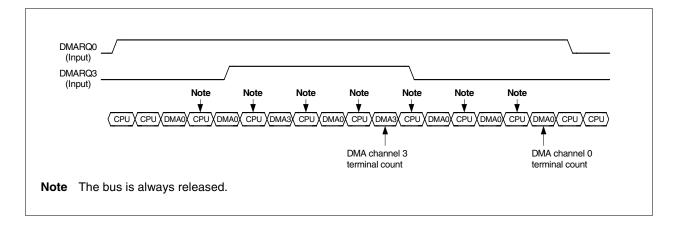

| 7-14          | Single Transfer Example 3                                                                      |      |

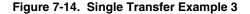

| 7-15          | Single Transfer Example 4                                                                      |      |

| 7-16          | Single-Step Transfer Example 1                                                                 |      |

| 7-17          | Single-Step Transfer Example 2                                                                 |      |

| 7-18          | Line Transfer Example 1                                                                        |      |

| 7-19          | Line Transfer Example 2                                                                        |      |

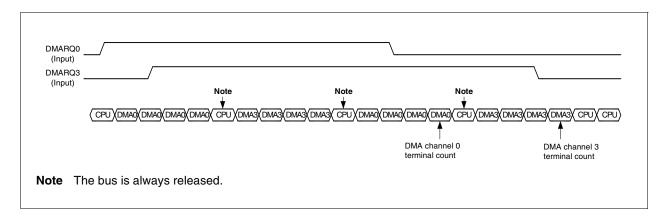

| 7-20          | Line Transfer Example 3                                                                        |      |

| 7-21          | Line Transfer Example 4                                                                        |      |

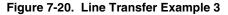

| 7-22          | Block Transfer Example                                                                         |      |

| 7-23          | One-Time Transfer When Executing Single Transfers Using DMARQn Signal                          |      |

| 7-24          | Example of Two-Cycle Transfer                                                                  |      |

| 7-25          | Example of Flyby Transfer (Memory to I/O)                                                      |      |

| 7-26          | Timing Example of Terminal Count Signals (DMTCO3 to DMTCO0)                                    |      |

| 7-27          | Example of Terminal Count Signal Output (DMTCO3 to DMTCO0)                                     |      |

| 7-28          | DMA Transfer Forcible Interruption Example                                                     |      |

| 7-29          | DMA Transfer Forcible Termination Example                                                      |      |

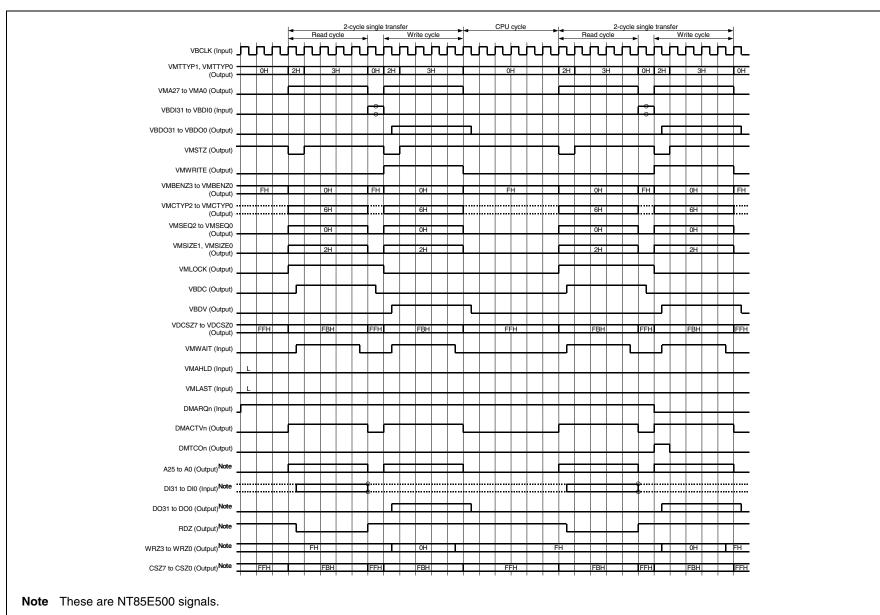

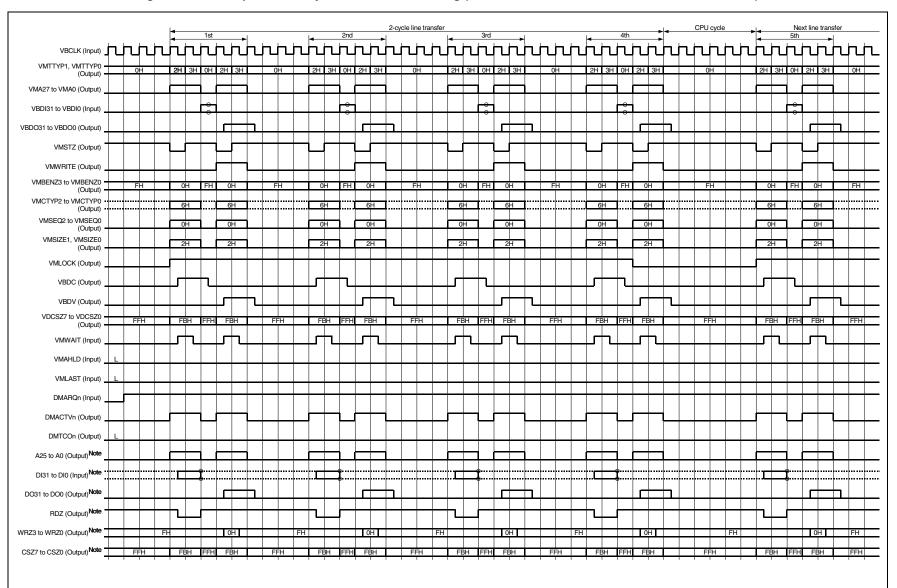

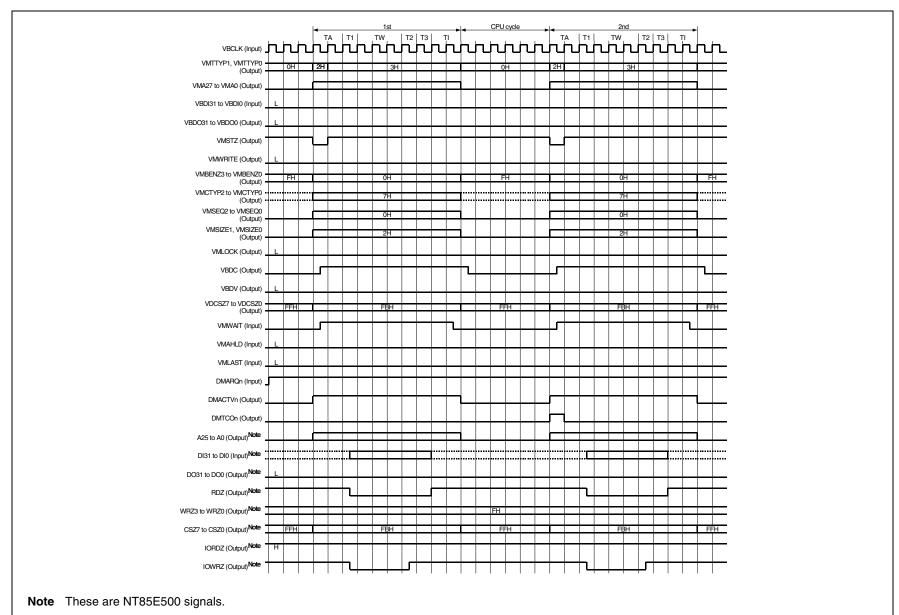

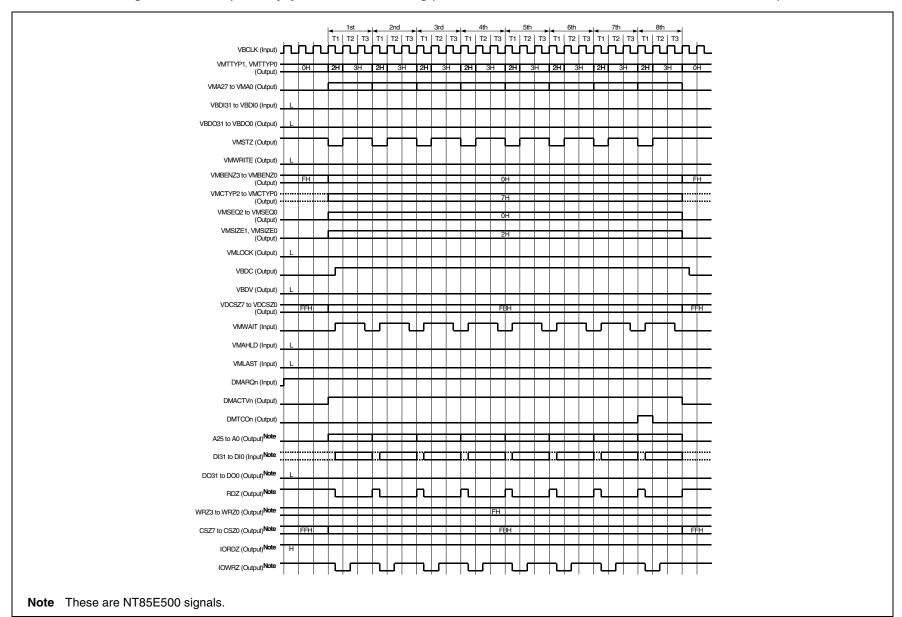

| 7-30          | Example of Two-Cycle Single Transfer Timing (Between External SRAMs Connected to NT85E500)     |      |

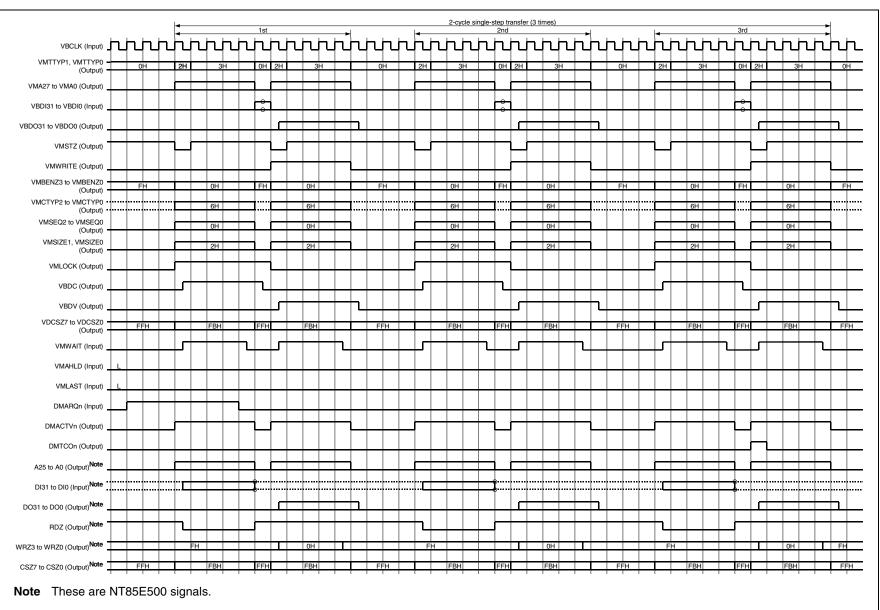

| 7-31          | Example of Two-Cycle Single-Step Transfer Timing (Between External SRAMs Connected to NT85E500 | -    |

| 7-32          | Example of Two-Cycle Line Transfer Timing (Between External SRAMs Connected to NT85E500)       | 185  |

## LIST OF FIGURES (3/3)

| <u>Figure</u> | e No. Title                                                                                       | Page |

|---------------|---------------------------------------------------------------------------------------------------|------|

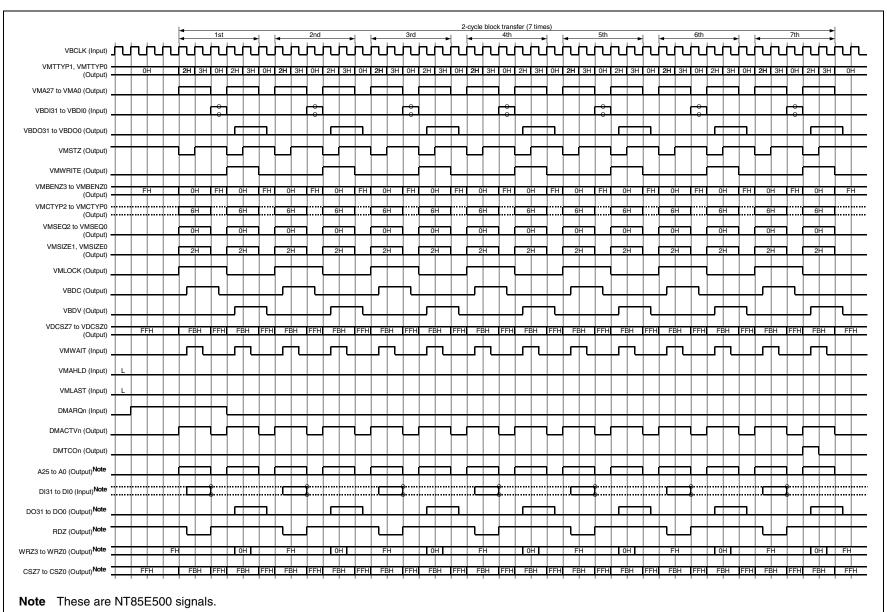

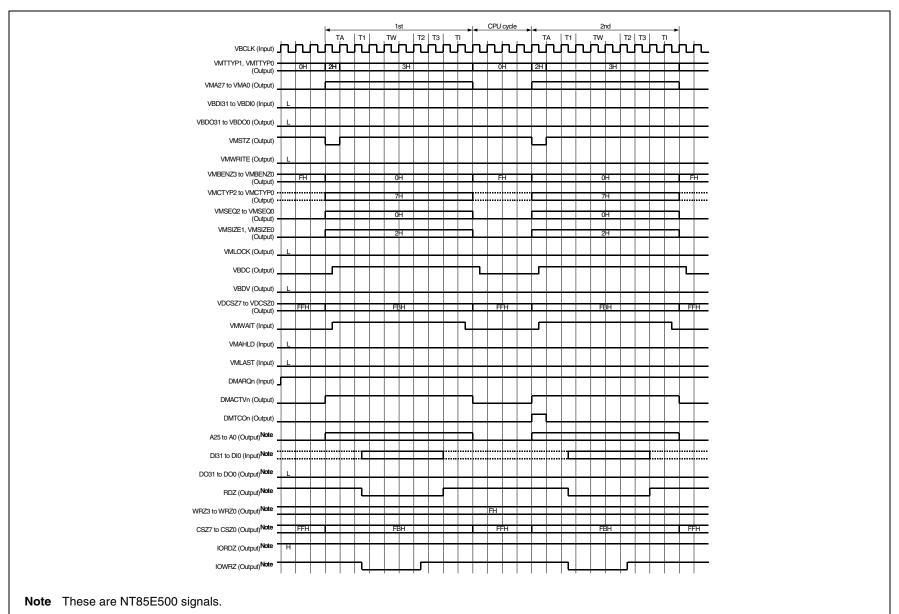

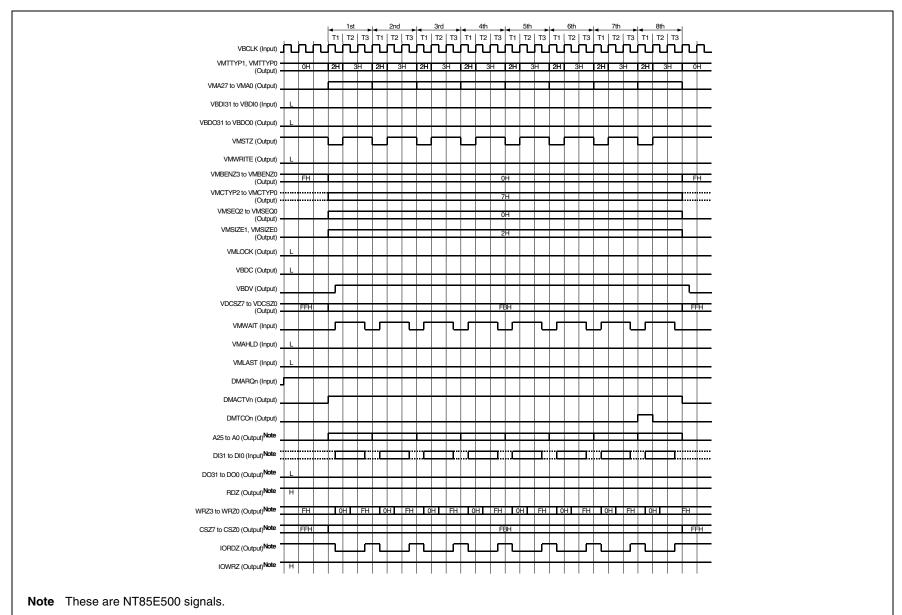

| 7-33          | Example of Two-Cycle Block Transfer Timing (Between External SRAMs Connected to NT85E500)         | 187  |

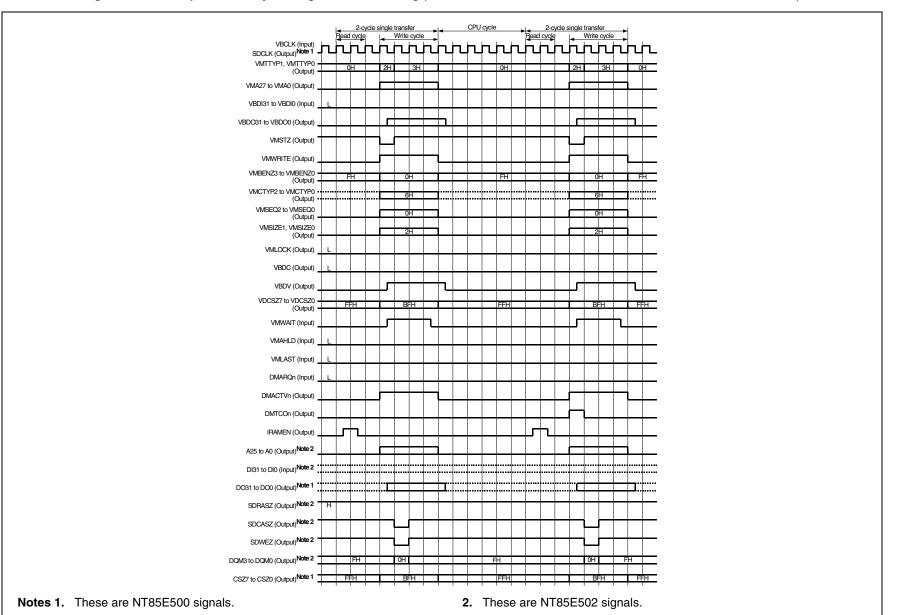

| 7-34          | Example of Two-Cycle Single Transfer Timing                                                       |      |

|               | (from RAM Connected to VDB to SDRAM Connected to NT85E502)                                        | 189  |

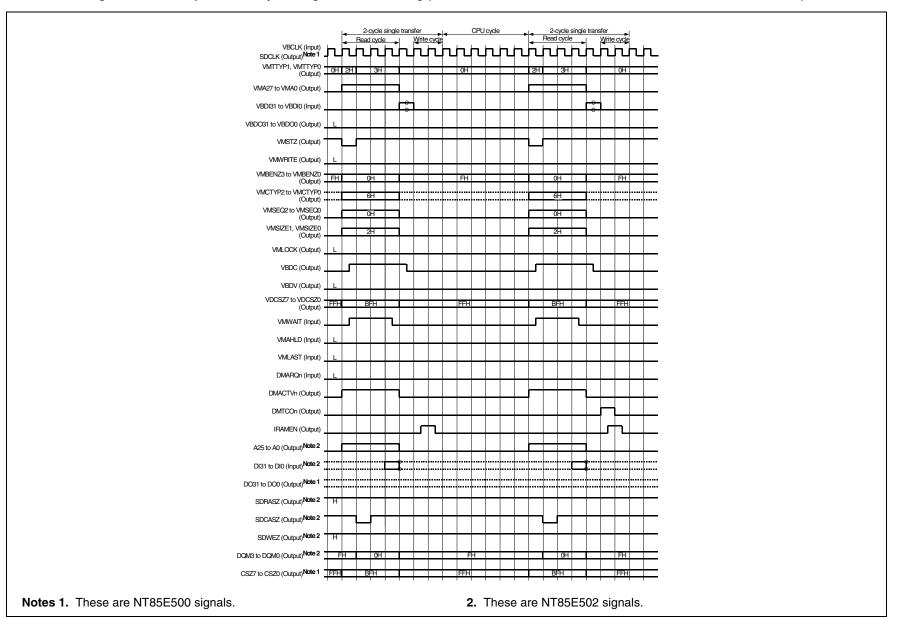

| 7-35          | Example of Two-Cycle Single Transfer Timing                                                       |      |

|               | (from SDRAM Connected to NT85E502 to RAM Connected to VDB)                                        | 191  |

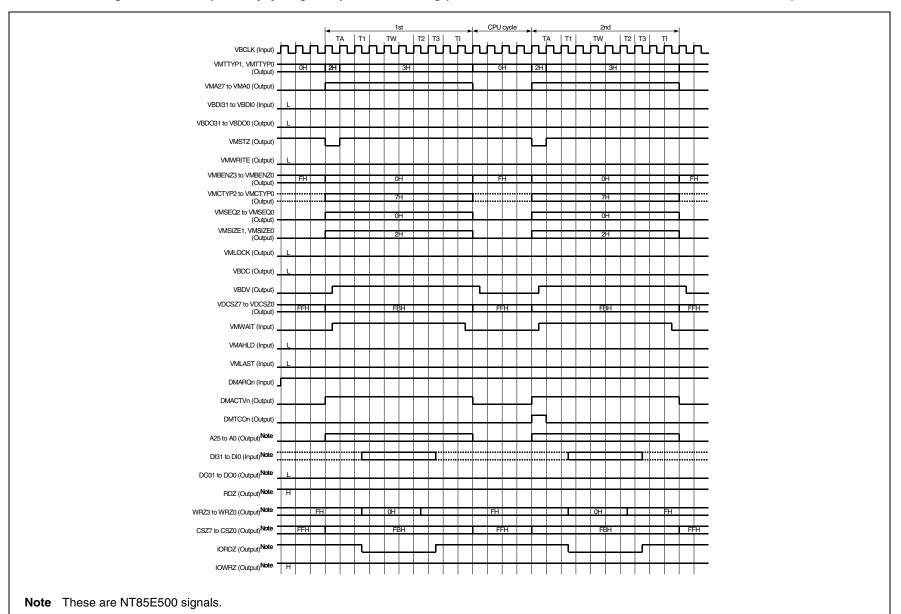

| 7-36          | Example of Flyby Single Transfer Timing (from External SRAM to External I/O Connected to NT85E500 |      |

| 7-37          | Example of Flyby Single-Step Transfer Timing                                                      |      |

|               | (from External SRAM to External I/O Connected to NT85E500)                                        | 195  |

| 7-38          | Example of Flyby Single-Step Transfer Timing                                                      |      |

|               | (from External I/O to External SRAM Connected to NT85E500)                                        | 197  |

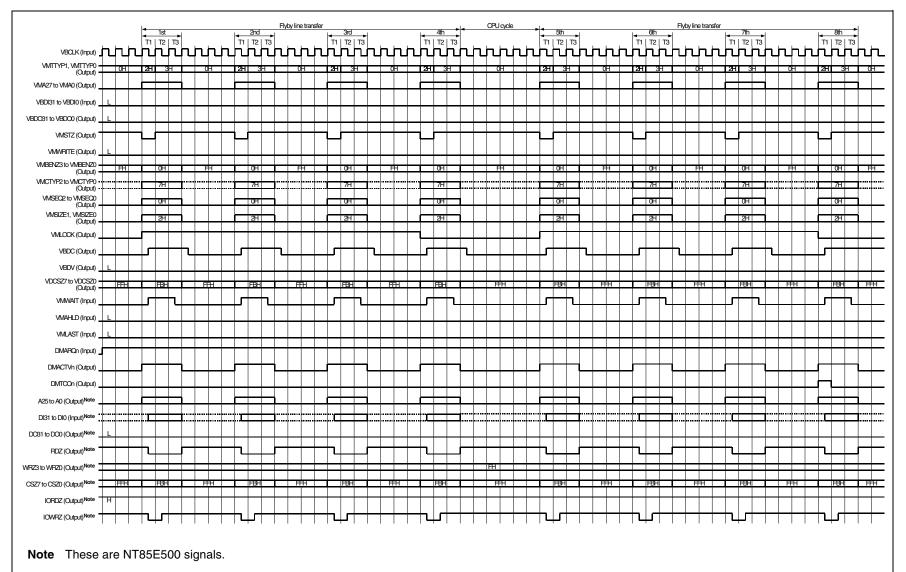

| 7-39          | Example of Flyby Line Transfer Timing (from External SRAM to External I/O Connected to NT85E500). | 199  |

| 7-40          | Example of Flyby Block Transfer Timing (from External SRAM to External I/O Connected to NT85E500  | )201 |

| 7-41          | Example of Flyby Block Transfer Timing (from External I/O to External SRAM Connected to NT85E500  | )203 |

| 8-1           | Example of Non-Maskable Interrupt Request Acknowledgement Operation                               | 210  |

| 8-2           | Non-Maskable Interrupt Processing Format                                                          | 212  |

| 8-3           | RETI Instruction Processing Format                                                                | 213  |

| 8-4           | Maskable Interrupt Processing Format                                                              | 215  |

| 8-5           | RETI Instruction Processing Format                                                                | 216  |

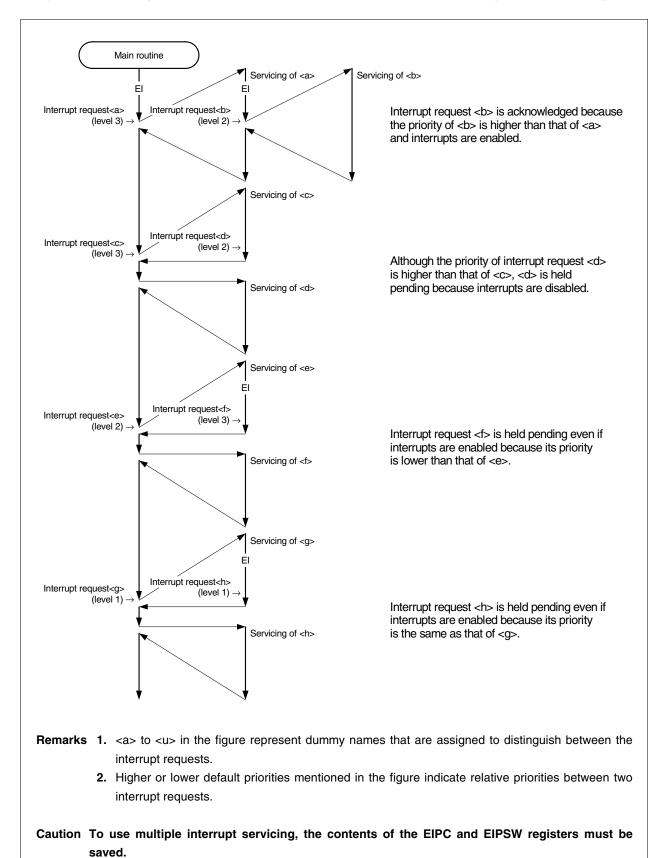

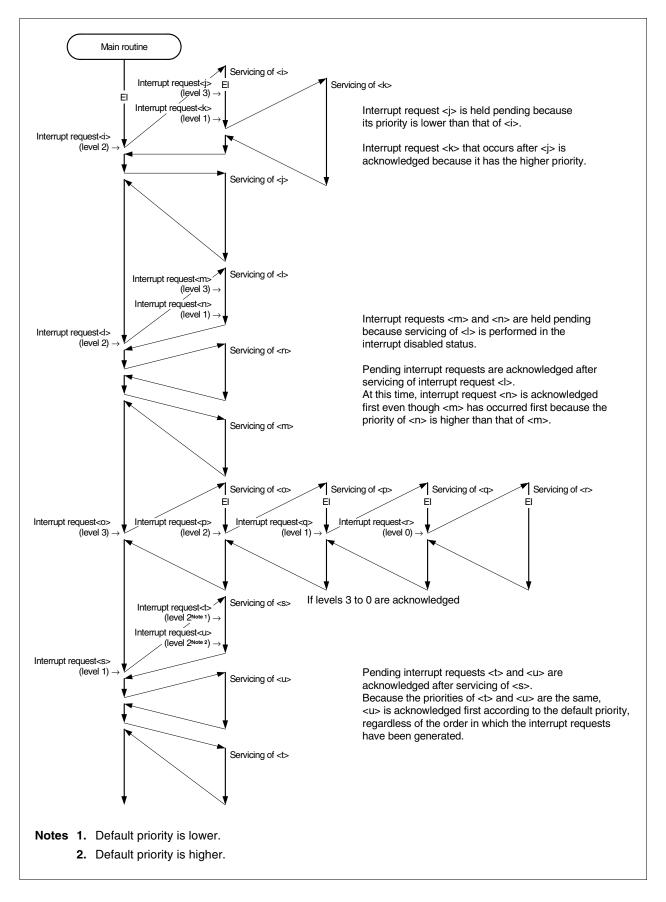

| 8-6           | Servicing Example in Which Another Interrupt Request Is Issued During Interrupt Servicing         | 218  |

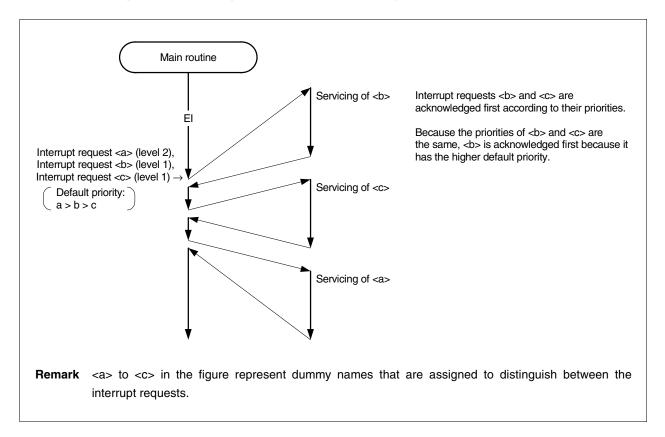

| 8-7           | Servicing Example for Simultaneously Issued Interrupt Requests                                    | 220  |

| 8-8           | Interrupt Control Registers 0 to 63 (PIC0 to PIC63)                                               | 221  |

| 8-9           | Interrupt Mask Registers 0 to 3 (IMR0 to IMR3)                                                    | 222  |

| 8-10          | In-Service Priority Register (ISPR)                                                               | 223  |

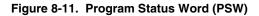

| 8-11          | Program Status Word (PSW)                                                                         | 224  |

| 8-12          | Software Exception Processing Format                                                              | 225  |

| 8-13          | RETI Instruction Processing Format                                                                | 226  |

| 8-14          | Illegal Opcode                                                                                    | 227  |

| 8-15          | Exception Trap Processing Format                                                                  | 228  |

| 8-16          | Example of Pipeline Operation When Interrupt Request Is Acknowledged (Outline)                    | 229  |

| 9-1           | Peripheral Macro Connection Example                                                               | 232  |

| 10-1          | NB85E901 and NU85E Connection Example                                                             | 243  |

| 10-2          | N-Wire Type IE Connection                                                                         | 244  |

| 10-3          | IE Connector Pin Layout Diagram (Target System Side)                                              | 244  |

| 10-4          | Example of Recommended Circuit for IE Connection (NU85E + NB85E901)                               | 246  |

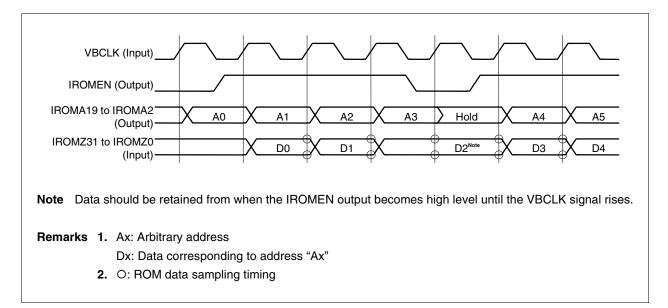

| A-1           | ROM Access Timing                                                                                 |      |

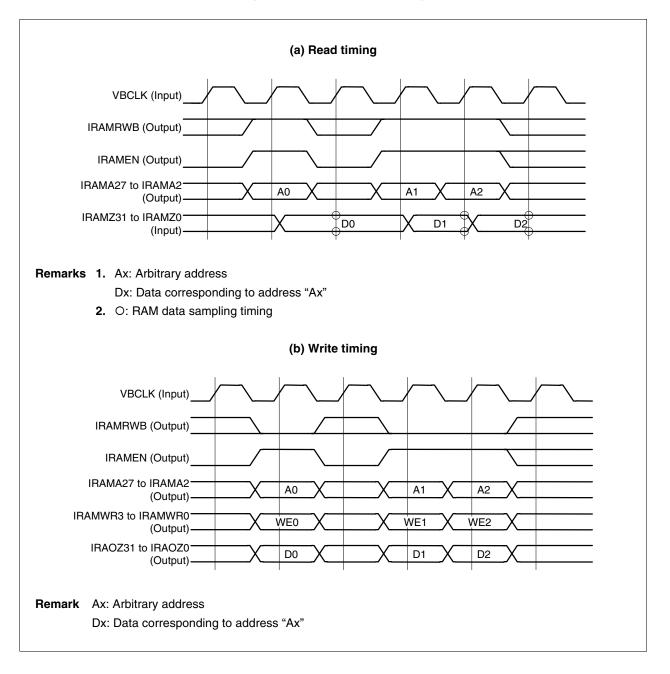

| A-2           | RAM Access Timing                                                                                 | 248  |

### LIST OF TABLES

| Table | No. Title                                                 | Page                |

|-------|-----------------------------------------------------------|---------------------|

| 2-1   | VMTTYP1 and VMTTYP0 Signals                               |                     |

| 2-2   | VMBENZ3 to VMBENZ0 and VSBENZ1 Signals                    |                     |

| 2-3   | VMSIZE1 and VMSIZE0 Signals                               |                     |

| 2-4   | VMCTYP2 to VMCTYP0 Signals                                |                     |

| 2-5   | VMSEQ2 to VMSEQ0 Signals                                  |                     |

| 2-6   | IRAMWR3 to IRAMWR0 Signals                                |                     |

| 2-7   | IDDRRQ, IDDWRQ, IDSEQ4, and IDSEQ2 Signals                |                     |

| 2-8   | IFIRA64, IFIRA32, and IFIRA16 Signals                     |                     |

| 2-9   | IFINSZ1 and IFINSZ0 Signals                               |                     |

| 2-10  | Pin Status in Each Operating Mode                         |                     |

| 3-1   | List of Program Registers                                 | 53                  |

| 3-2   | List of System Registers                                  |                     |

| 3-3   | Interrupt/Exception Table                                 | 63                  |

| 3-4   | RAM Area Size Settings                                    |                     |

| 4-1   | VMTTYP1 and VMTTYP0 Signals                               |                     |

| 4-2   | VMCTYP2 to VMCTYP0 Signals                                |                     |

| 4-3   | VMBENZ3 to VMBENZ0 Signals                                |                     |

| 4-4   | VMSIZE1 and VMSIZE0 Signals                               |                     |

| 4-5   | VMSEQ2 to VMSEQ0 Signals                                  | 96                  |

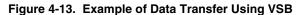

| 4-6   | VMWAIT, VMAHLD, and VMLAST Signals                        |                     |

| 4-7   | VBDC and VBDV Signals                                     |                     |

| 5-1   | Setting of Setup Wait, VPSTB Wait Lengths at Each Opera   | tion Frequency124   |

| 6-1   | Operation After HALT Mode Is Canceled by Interrupt Requi  | əst140              |

| 6-2   | Operation After Software STOP Mode Is Canceled by Inter   | rupt Request141     |

| 6-3   | Operation After Setting Software STOP Mode in Interrupt S | ervicing Routine142 |

| 6-4   | Status After Cancellation of Hardware STOP Mode           |                     |

| 7-1   | Relationships Between Transfer Type and Transfer Object   |                     |

| 7-2   | Relationships Between Wait Function and Transfer Object   |                     |

| 8-1   | Interrupt/Exception List                                  |                     |

| 9-1   | List of Test Mode Settings                                |                     |

| 10-1  | Pin Status in Each Operating Mode                         |                     |

| 10-2  | IE Connector Pin Functions (Target System Side)           |                     |

#### **CHAPTER 1 INTRODUCTION**

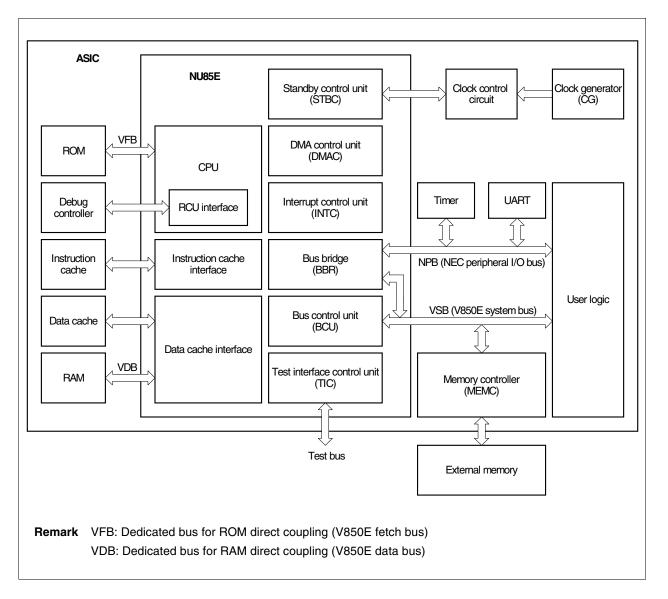

The NU85E Family consists of CPU cores that feature on-chip the "V850E1" 32-/16-bit RISC type CPU and peripheral I/Os, and are designed for embedding in ASICs. The V850E1 can execute almost all instructions in 1 clock through 5-stage pipeline control based on the RISC architecture. Furthermore, the NU85E Family also provides on-chip 2 types of external bus interfaces for connection to high- and low-speed peripheral I/Os, as well as functions to interface with ROM, RAM, an instruction cache, and a data cache. This product, the "NU85E", is a CPU core that has, among other on-chip features, a DMA controller and an interrupt controller.

#### 1.1 Outline

#### (1) "V850E1" CPU

The NU85E is equipped with the "V850E1", which is a RISC type CPU that utilizes a five-stage pipeline technique. Two-byte basic instructions and instructions for high-level language support increase the efficiency of object code generated by the C compiler and reduce the program size.

In addition, to increase the speed of multiplication processing, the NU85E contains an on-chip high-speed hardware multiplier capable of executing 32-bit × 32-bit operations.

#### (2) Bus interfaces

The NU85E provides the following two types of bus interface for connection with peripheral macros or user logic.

- V850E system bus (VSB)

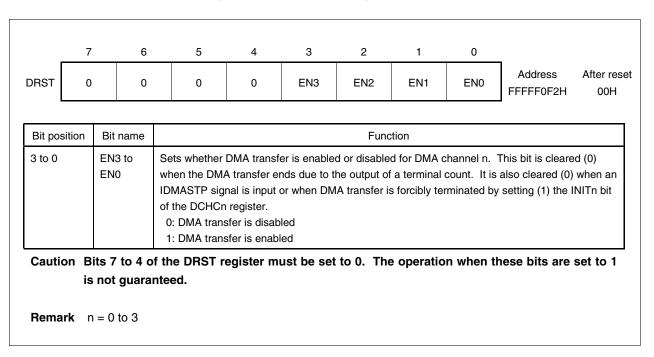

- NEC peripheral I/O bus (NPB)

The VSB, which is synchronized with the system clock, is the bus to be used for connection with high-speed peripheral macros such as a memory controller (MEMC) or macros operating as bus master (DMAC, DSP, etc.). The NPB, which operates asynchronously with the system clock, is to be used for connection with relatively low-speed peripheral macros such as a timer or asynchronous serial interface (UART).

A V850E fetch bus (VFB), which can be directly coupled with ROM, and a V850E data bus (VDB), which can be directly coupled with RAM, are also provided.

In addition, since the NU85E contains on-chip special purpose interfaces for the instruction cache, data cache, and run control unit (RCU), each macro can be directly coupled.

#### (3) On-chip peripheral I/O

The NU85E contains an on-chip DMA control unit (DMAC) for controlling DMA transfers, an on-chip interrupt control unit (INTC) for controlling interrupt requests, and an on-chip standby control unit (STBC) for controlling the power save function.

### 1.2 Application System Example

Caution In this manual, representations related to the memory connected to the NU85E are unified as follows.

- RAM: NU85E direct-coupled RAM (connected to VDB)

- ROM: NU85E direct-coupled ROM (connected to VFB)

- External memory: RAM or ROM connected via the memory controller (MEMC) (connected via VSB)

#### 1.3 Features

- Number of instructions 83

- General-purpose registers 32 bits × 32 registers

| <ul> <li>Instruction set</li> </ul> | Upwardly compatible with V850 CPU                                               |

|-------------------------------------|---------------------------------------------------------------------------------|

|                                     | Signed multiplication (32 bits $	imes$ 32 bits $	o$ 64 bits)                    |

|                                     | Saturated calculation instructions (with overflow/underflow detection function) |

|                                     | 32-bit shift instructions: 1 clock                                              |

|                                     | Bit manipulation instructions                                                   |

|                                     | Load/store instructions with long/short format                                  |

|                                     | Signed load instructions                                                        |

|                                     |                                                                                 |

|                                     |                                                                                 |

Memory space Program area: 64 MB linear address space

Data area: 4 GB linear address space

Memory bank division function: 2, 4, or 8 MB/bank

#### • External bus interface

VSB (V850E system bus)

- Address/data separated bus (28-bit address<sup>Note</sup>/32-bit data bus)

- Data I/O separated bus

- 32-/16-/8-bit bus sizing function

- Bus hold function

- External wait function

- Endian switching function

NPB (NEC peripheral I/O bus)

- Address/data separated bus (14-bit address/16-bit data bus)

- Data I/O separated bus

- Programmable wait function

- Retry function

Note 14-bit address bus when functioning as bus slave

• Interrupt/exception control functions

Non-maskable interrupts: 3 sources Maskable interrupts: 64 sources Exceptions: 1 source Eight levels of priorities can be set (maskable interrupts)

DMA control function 4-channel configuration

Transfer units: 8-bit, 16-bit, or 32-bit

Maximum transfer count: 65,536 (2<sup>16</sup>)

Transfer types: Flyby (1-cycle) transfer or 2-cycle transfer

Transfer modes: Single transfer, single-step transfer, line transfer, or block transfer

Terminal count output signals (DMTCO3 to DMTCO0)

- Power save function HALT mode

Software STOP mode

Hardware STOP mode

- RCU<sup>Note</sup> interface function

- Note The Run Control Unit (RCU) communicates using JTAG and executes debug processing.

### 1.4 Symbol Diagram

| in       | DBI (5:0) IBDRRC                                                                                                     | in         |

|----------|----------------------------------------------------------------------------------------------------------------------|------------|

| in ——    |                                                                                                                      |            |

| out —    | DBO (14:0) IBEA (25:2                                                                                                |            |

| in/out   | DBB (15:0) IBAACH                                                                                                    |            |

| in ——    | IFIROME IBDRDY                                                                                                       |            |

| in ——    | IFIROB2 IBDLE (3:0                                                                                                   | ) out      |

| in ——    | IFIMODE2 IBEDI (31:0                                                                                                 | ) out      |

| in ——    | IFIRA16 IBBTF1                                                                                                       | - in       |

| in ——    | IFIRA32 IIDRRC                                                                                                       |            |

| in ——    |                                                                                                                      |            |

|          |                                                                                                                      |            |

| in ——    | IFIMAEN IIAACH                                                                                                       |            |

| in ——    | IFID256 IIDLEF                                                                                                       |            |

| in —O    | IFINSZ (1:0) IIEDI (31:0                                                                                             | ) —— in    |

| in ——    | IFIWRTH IIBTFT                                                                                                       | out 🖳      |

| in ——    | IFIUNCH (1:0) IIRCAN                                                                                                 | I out      |

| in ——    | PHEVA BCUNCH                                                                                                         |            |

| in ——    | IFIROBE VAACH                                                                                                        |            |

| in ——    | IFIROPR VARE                                                                                                         |            |

|          |                                                                                                                      |            |

| in ——    | IFIRASE VAPREC                                                                                                       |            |

| in ——    | IFIRABE VBDI (31:0                                                                                                   |            |

| in ——    | IFIMODE3 VBDO (31:0                                                                                                  | ) — out    |

| in ——    | IFIUSWE VMA (27:0                                                                                                    | ) out      |

| in ——    | FCOMB VMTTYP (1:0                                                                                                    |            |

| out —    | IDDARQ VMST2                                                                                                         |            |

| in ——    | IDDRRQ VMBENZ (3:0                                                                                                   |            |

|          |                                                                                                                      |            |

| in ——    |                                                                                                                      |            |

| out —    | IDAACK VMWRITE                                                                                                       |            |

| in ——    | IDSEQ2 VMLOCH                                                                                                        |            |

| in ——    | IDSEQ4 VMCTYP (2:0                                                                                                   |            |

| out ——   | IDUNCH VMSEQ (2:0                                                                                                    | ) out      |

| out —    | IRRSA VMBSTF                                                                                                         |            |

| out —    | IDRETR VMWAIT                                                                                                        |            |

| out —    | IDES VMLAST                                                                                                          |            |

| out —    | IDDRDY VMAHLE                                                                                                        |            |

|          |                                                                                                                      |            |

| in ——    | IDRRDY VDSELP2                                                                                                       |            |

| in ——    | IDHUM VSA (13:0                                                                                                      |            |

| in ——    | IDEA (27:0) VSST2                                                                                                    |            |

| in/out — | IDED (31:0) VSBENZ1                                                                                                  | 1 P— in    |

| out —    | IROMA (19:2) VSWRITE                                                                                                 | E —— in    |

| in —O    | IROMZ (31:0) VSLOCH                                                                                                  | ( in       |

| out ——   | IROMEN VSWAIT                                                                                                        | out –      |

| out —    | IROMCS VSLAST                                                                                                        |            |

| out —    | IROMIA VSAHLE                                                                                                        |            |

| out —    | IROMAE VSSELP2                                                                                                       |            |

|          |                                                                                                                      |            |

| in ——    | IROMWT VBDC                                                                                                          |            |

| out —    | IRAMA (27:2) VBD\                                                                                                    |            |

| in —O    | IRAMZ (31:0) VDCSZ (7:0                                                                                              | ) () — out |

| out —C   | IRAOZ (31:0) EVASTE                                                                                                  | 3 —— in    |

| out —    | IRAMEN EVDSTE                                                                                                        | 3 —— in    |

| out —    | IRAMWR (3:0) EVAD (15:0                                                                                              |            |

| out —    | IRAMRWB EVIEN                                                                                                        |            |

| in —     |                                                                                                                      |            |

|          |                                                                                                                      |            |

| in ——    | DCNMI (2:0) EVLKRT                                                                                                   |            |

| in ——    | INT (63:0) EVIREL                                                                                                    |            |

| in ——    | IDMASTP EVCLRIF                                                                                                      |            |

| in ——    | DMARQ (3:0) EVINTAL                                                                                                  | ( in       |

| out —    | DMTCO (3:0) EVINTRO                                                                                                  |            |

| out —    | DMACTV (3:0) EVINTLV (6:0                                                                                            |            |

| in —O    | DCRESZ VPA (13:0                                                                                                     |            |

|          |                                                                                                                      |            |

| in ——    |                                                                                                                      |            |

| in ——    | CGREL VPDO (15:0                                                                                                     |            |

| out ——   | SWSTOPRQ VPWRITE                                                                                                     |            |

| out ——   | HWSTOPRQ VPSTE                                                                                                       | 3 out      |

| in —O    | DCSTOPZ VPLOCH                                                                                                       | c — out    |

| out      | STPRQ VPUBENZ                                                                                                        |            |

| in ——    | STPAK VPRETF                                                                                                         |            |

|          | VPDACT                                                                                                               |            |

|          |                                                                                                                      |            |

|          | VPD\<br>TRI TRO BUNRI PHTDO TMODE PHTDIN                                                                             | / out      |

|          | TBI TBO BUNRI PHTDO TMODE PHTDIN<br>(39:0) (34:0) TEST BUNRI OUT (1:0) (1:0) TBREDZ TESEN PHTEST VPTCLK (1:0) VPRESZ | ,          |

|          |                                                                                                                      | ·          |

|          |                                                                                                                      |            |

|          |                                                                                                                      |            |

|          | in out in in out in out out out out out out                                                                          |            |

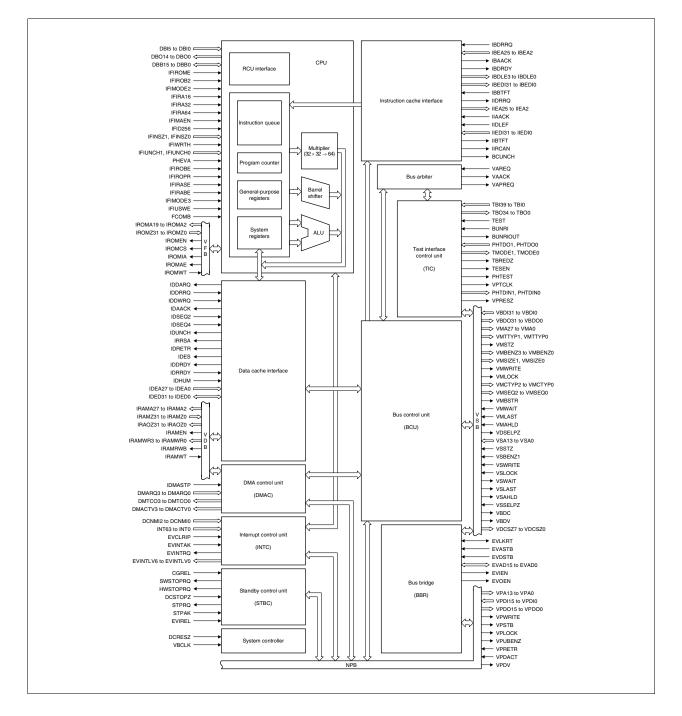

#### 1.5 Function Blocks

#### 1.5.1 Internal block diagram

#### 1.5.2 Internal units

#### (1) CPU

The CPU uses five-stage pipeline control to enable single-clock execution of address calculations, arithmetic and logic operations, data transfers, and almost all other instruction processing.

Other dedicated on-chip hardware, such as a hardware multiplier that enables high-speed processing of 32-bit  $\times$  32-bit multiplication and a barrel shifter, help accelerate the processing of complex instructions.

In addition, the CPU has an on-chip RCU interface for connecting to the RCU (See CHAPTER 3 CPU).

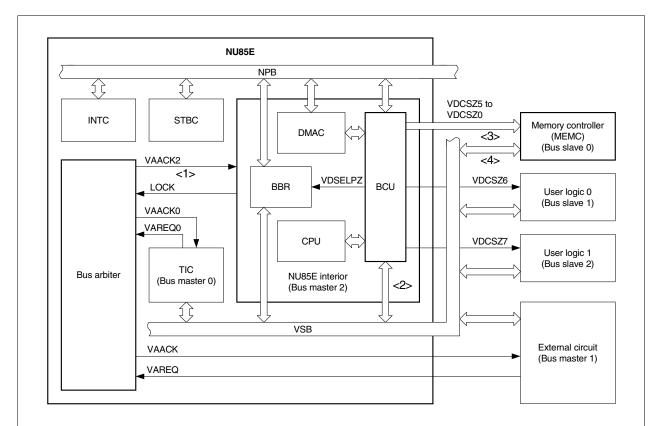

#### (2) BCU

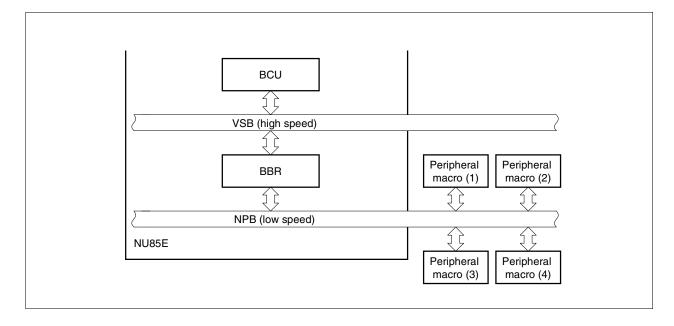

The bus control unit (BCU), which operates as a bus master on the VSB, controls the on-chip bus bridge (BBR), test interface control unit (TIC), and peripheral macros (bus slaves) such as the memory controller (MEMC) connected to the VSB (See **CHAPTER 4 BCU**).

### (3) BBR

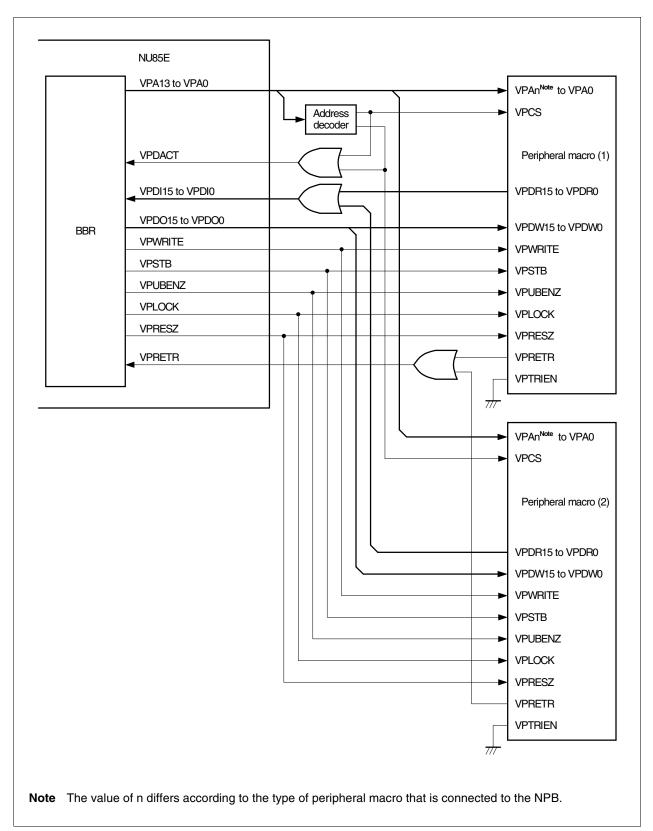

The bus bridge (BBR) converts signals for the VSB to signals for the NPB. The BBR sets up the wait insertion function and retry function for peripheral macros connected to the NPB (See **CHAPTER 5 BBR**).

#### (4) STBC

The standby control unit (STBC) controls the external clock generator (CG) when the power save function (HALT mode, software STOP mode, or hardware STOP mode) is executed (See **CHAPTER 6 STBC**).

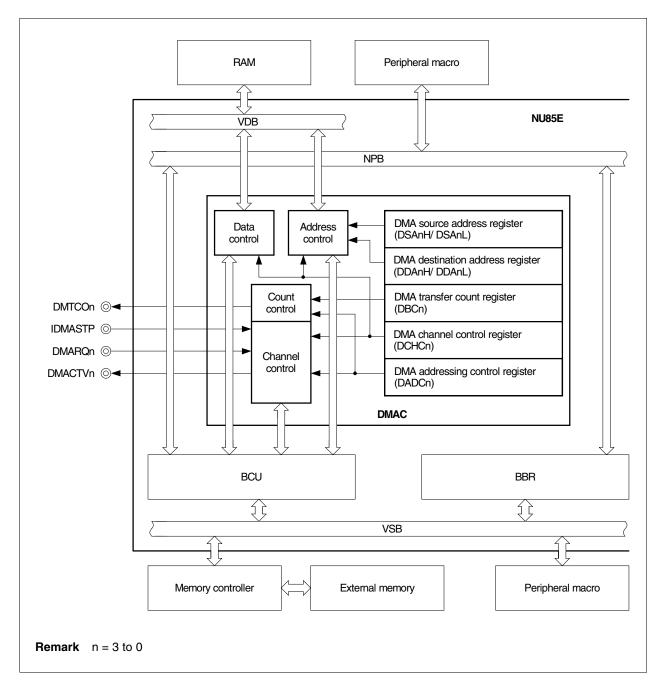

#### (5) DMAC

The DMA control unit (DMAC) is a four-channel control unit that controls data transfers between memory and peripheral macros or between memory and memory based on DMA transfer requests issued by means of the DMARQ3 to DMARQ0 pins or software triggers (See **CHAPTER 7 DMAC**).

#### (6) INTC

The interrupt control unit (INTC) processes various types of interrupt requests (See CHAPTER 8 INTC).

#### (7) TIC

The test interface control unit (TIC) is used for test function control. When the TIC is set to test mode, test control signals become effective (See **CHAPTER 9 TEST FUNCTION**).

#### (8) Bus arbiter

The bus arbiter receives bus control requests from multiple bus masters and arbitrates bus access rights.

### 1.6 Functional Differences Between NU85E and NB85E

|                                        | Item                                                                      | NU85E                                                                                          | NB85E                                                                              |  |

|----------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|

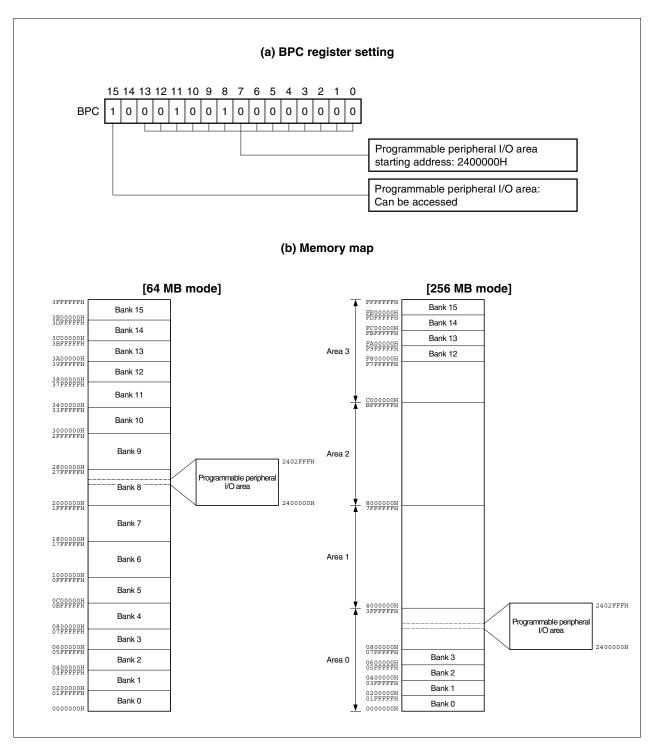

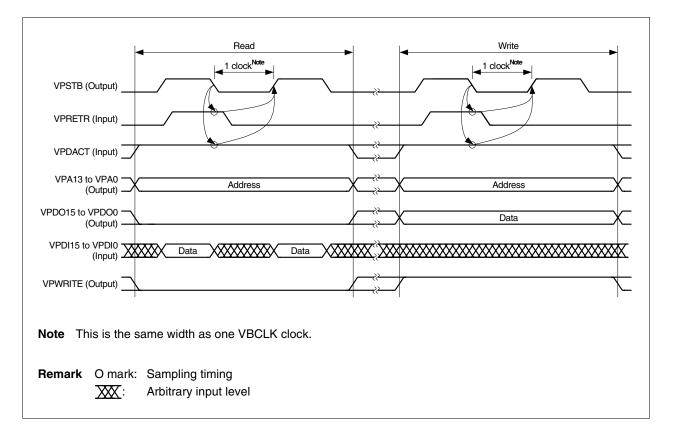

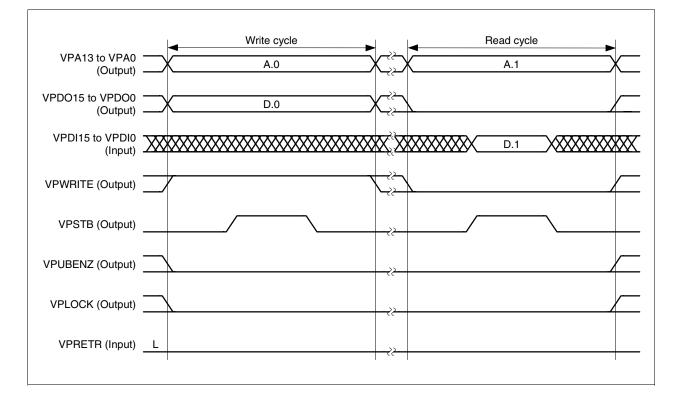

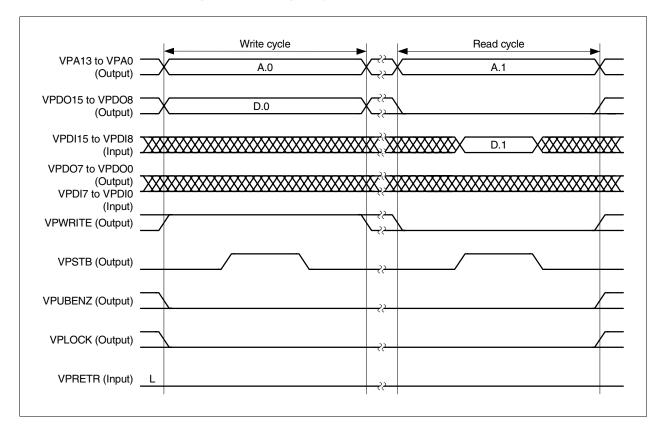

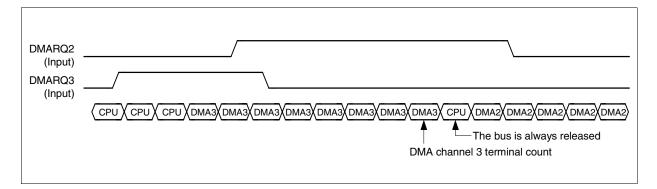

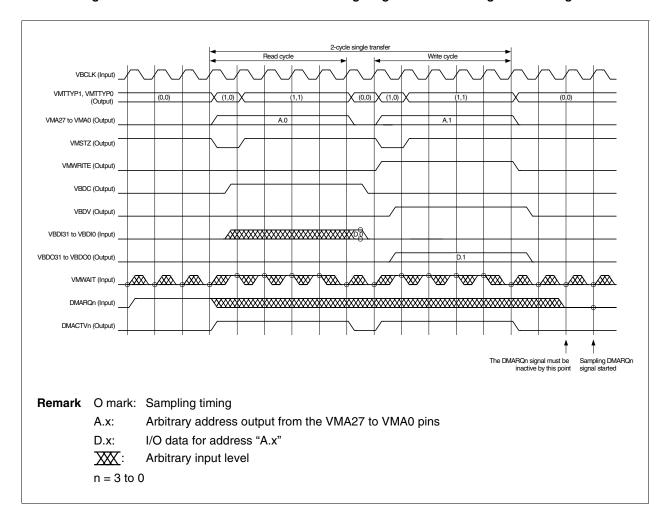

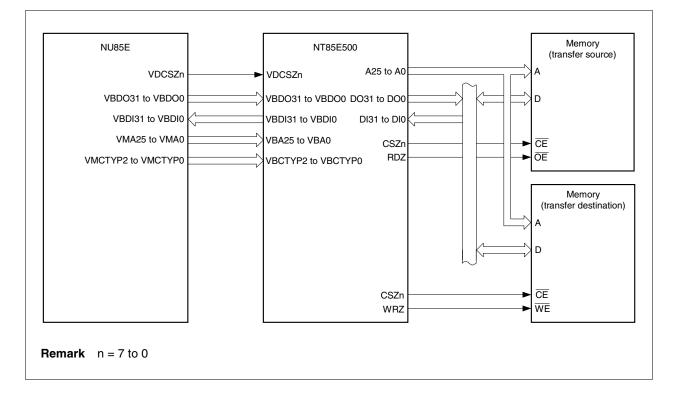

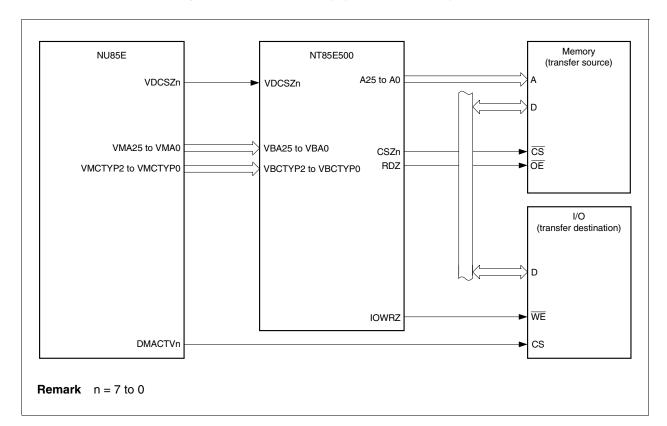

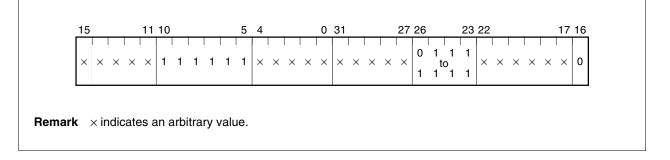

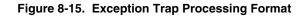

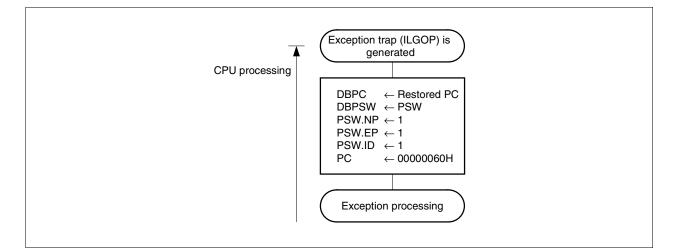

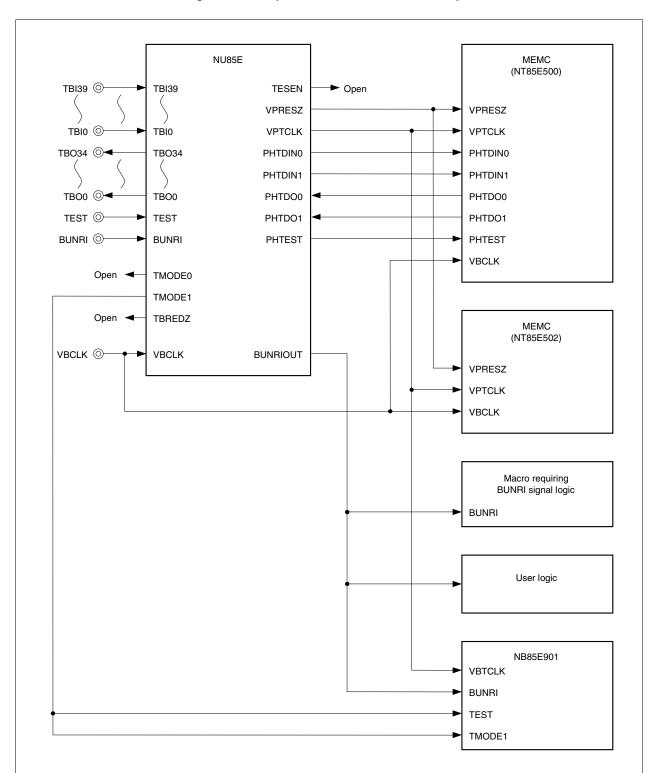

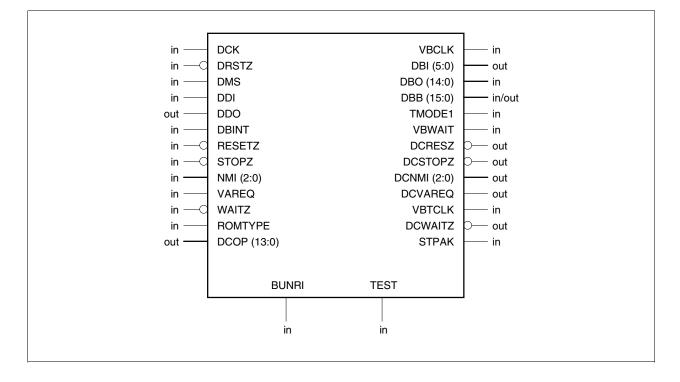

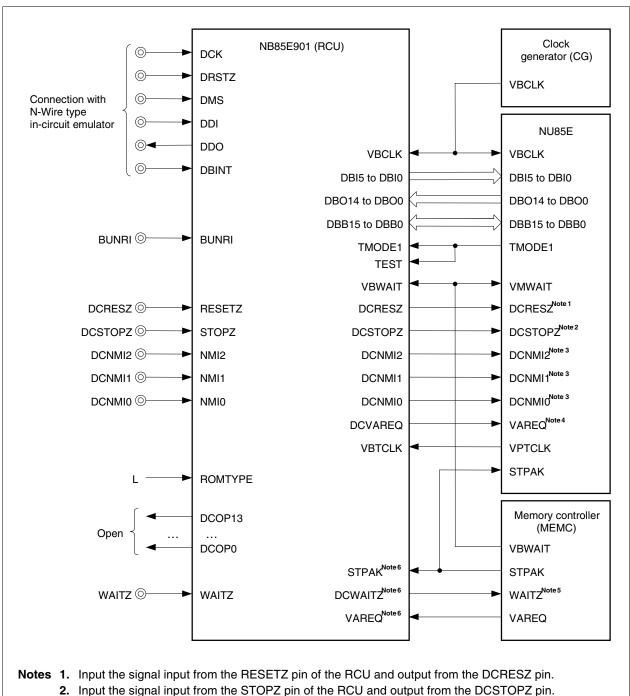

| VSB data bus (                         | n = 31 to 0)                                                              | VBDIn (input), VBDOn (output)                                                                  | VBDn (input/output)                                                                |  |