# M16C/5M Group, M16C/57 Group User's Manual: Hardware

RENESAS MCU M16C Family / M16C/50 Series

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

### General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

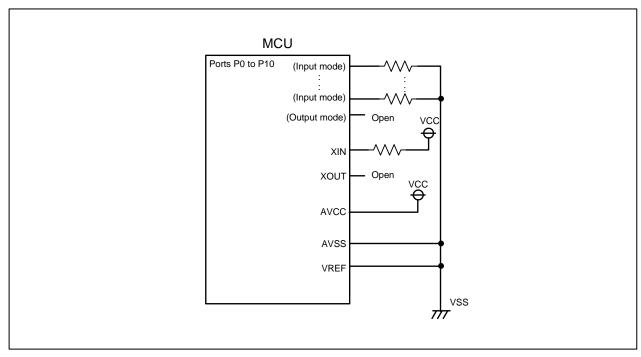

### 1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

### 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

#### 3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

The reserved addresses are provided for the possible future expansion of functions. Do not access these addresses; the correct operation of LSI is not guaranteed if they are accessed.

### 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

— When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

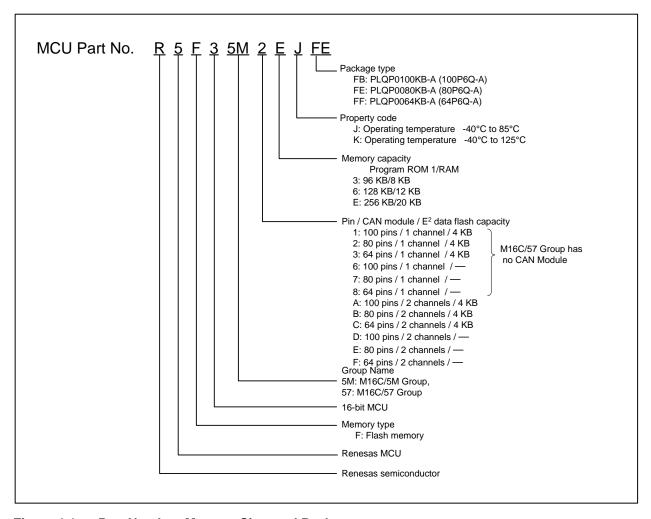

### 5. Differences between Products

Before changing from one product to another, i.e. to one with a different part number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different part numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different part numbers, implement a system-evaluation test for each of the products.

# **About This Manual**

### 1. Purpose and Target User

This manual is designed to be read primarily by application developers who have an understanding of this microcomputer (MCU) including its hardware functions and electrical characteristics. The user should have a basic understanding of electric circuits, logic circuits and, MCUs.

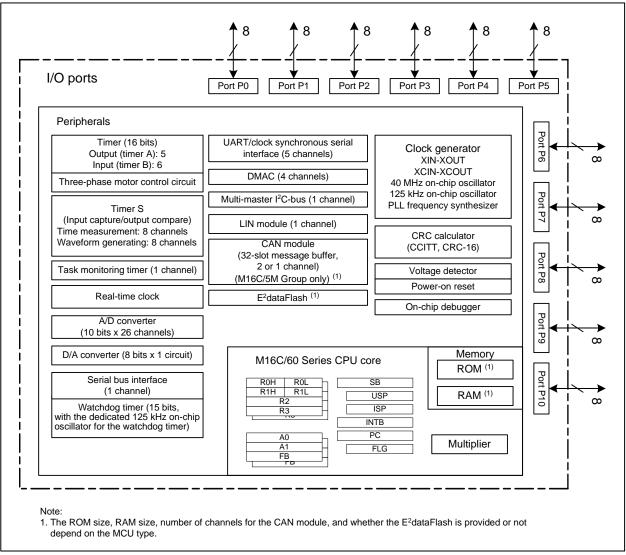

This manual consists of six main categories: Overview, CPU, System Control, Peripherals, Electrical Characteristics, and Usage Notes.

Carefully read all notes in this document prior to use. Notes are found throughout each chapter, at the end of each chapter, and in the dedicated Usage Notes chapter.

The Revision History at the end of this manual summarizes primary modifications and additions to the previous versions. For details, please refer to the relative chapters or sections of this manual.

The M16C/5M Group, M16C/57 Group includes the documents listed below. Verify this manual is the latest version by visiting the Renesas Electronics website.

| Type of Document                              | Contents                                                                                                                                                                                    | Document Name                                                 | Document Number  |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------|

| Datasheet                                     | Overview of Hardware and Electrical Characteristics                                                                                                                                         | M16C/5M Group,<br>M16C/57 Group<br>Datasheet                  | R01DS0019EJ0110  |

| User's Manual:<br>Hardware                    | Specifications and detailed descriptions of: -pin layout -memory map -peripherals -electrical characteristics -timing characteristics Refer to the Application Manual for peripheral usage. | M16C/5M Group,<br>M16C/57 Group<br>User's Manual:<br>Hardware | This publication |

| User's Manual:<br>Software/Software<br>Manual | Descriptions of instruction set                                                                                                                                                             | M16C/60, M16C/20,<br>M16C/Tiny Series<br>Software Manual      | REJ09B0137       |

| Application Note                              | -Usages -Applications -Sample programs -Programming technics using Assembly language or C programming language                                                                              | Available on the Renewebsite.                                 | esas Electronics |

| Renesas Technical<br>Update                   | Bulletins on product specifications, documents, etc.                                                                                                                                        |                                                               |                  |

### 2. Numbers and Symbols

The following explains the denotations used in this manual for registers, bits, pins and various numbers.

(1) Registers, bits, and pins

Registers, bits, and pins are indicated by symbols. Each symbol has a register/bit/pin identifier after the symbol.

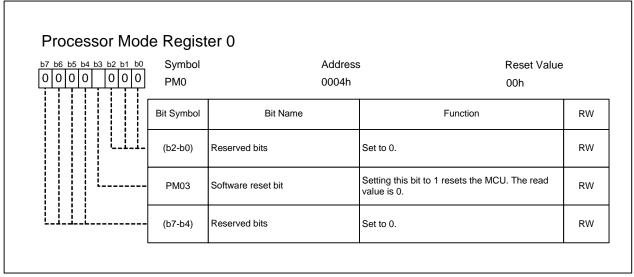

Example: PM03 bit in the PM0 register

P3\_5 pin, VCC pin

(2) Numbers

A binary number has the suffix "b" except for a 1-bit value.

A hexadecimal number has the suffix "h".

A decimal number has no suffix. Example: Binary notation: 11b

Hexadecimal notation: EFA0h

Decimal notation: 1234

### 3. Registers

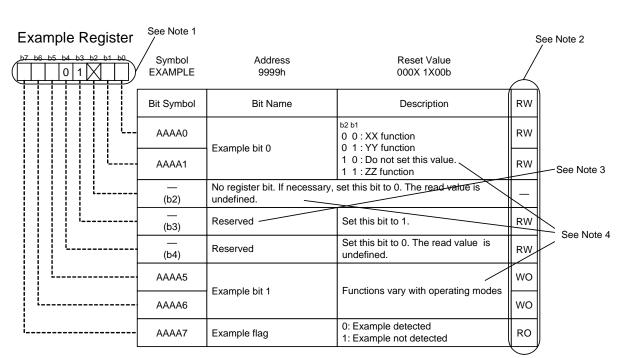

The following illustration describes registers used throughout this manual.

#### Notes:

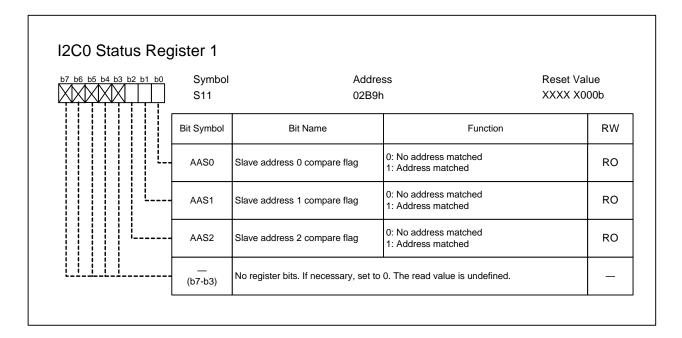

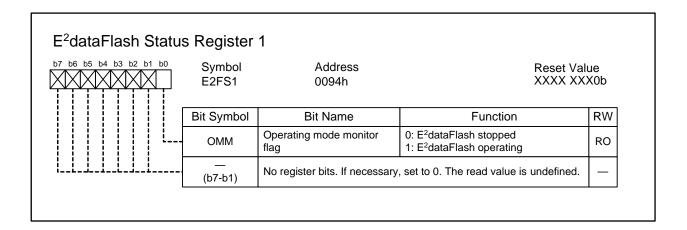

- 1. Blank box: Set this bit to 0 or 1 according to the function.

- 0: Set this bit to 0.

- 1: Set this bit to 1.

- X: Nothing is assigned to this bit.

- 2. RW: Read and write

- RO: Read only

- WO: Write only (the read value is undefined)

- —: Not applicable

- 3. Reserved bit: This bit field is reserved. Set this bit to a specified value. For RW bits, the written value is read unless otherwise noted.

4

- No register bit(s): No register bit(s) is/are assigned to this field. If necessary, set to 0 for possible future implementation.

- Do not use this combination: Proper operation is not guaranteed when this value is set.

- Functions vary with operating modes: Functions vary with peripheral operating modes. Refer to register illustrations of the respective mode.

# 4. Abbreviations and Acronyms

The following acronyms and terms are used throughout this manual.

| Abbreviation/Acronym | Meaning                                      |

|----------------------|----------------------------------------------|

| ACIA                 | Asynchronous Communication Interface Adapter |

| bps                  | bits per second                              |

| CRC                  | Cyclic Redundancy Check                      |

| DMA                  | Direct Memory Access                         |

| DMAC                 | Direct Memory Access Controller              |

| GSM                  | Global System for Mobile Communications      |

| Hi-Z                 | High Impedance                               |

| IEBus                | Inter Equipment Bus                          |

| I/O                  | Input/Output                                 |

| IrDA                 | Infrared Data Association                    |

| LSB                  | Least Significant Bit                        |

| MSB                  | Most Significant Bit                         |

| NC                   | Non-Connection                               |

| PLL                  | Phase Locked Loop                            |

| PWM                  | Pulse Width Modulation                       |

| SIM                  | Subscriber Identity Module                   |

| UART                 | Universal Asynchronous Receiver/Transmitter  |

| VCO                  | Voltage Controlled Oscillator                |

# **Table of Contents**

| Qι | uick Ref | ference                                                    | B-1 |

|----|----------|------------------------------------------------------------|-----|

| 1. | Ove      | erview                                                     | 1   |

|    | 1.1      | Features                                                   | 1   |

|    | 1.1.1    | 1 Applications                                             | 1   |

|    | 1.2      | Specifications                                             | 2   |

|    | 1.3      | Product List                                               | 8   |

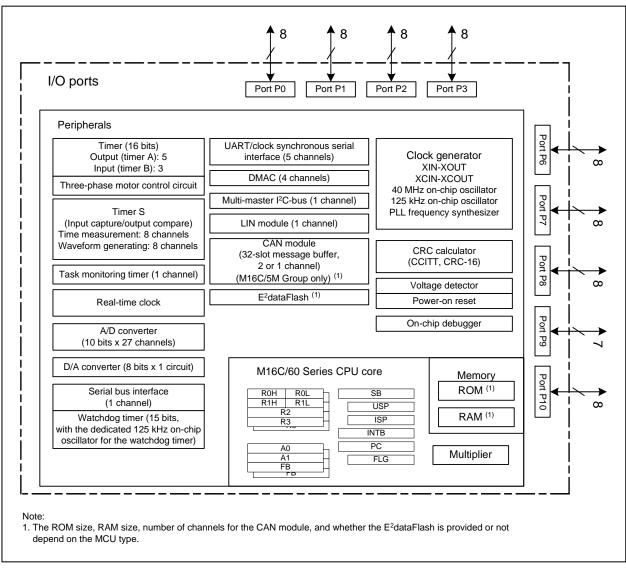

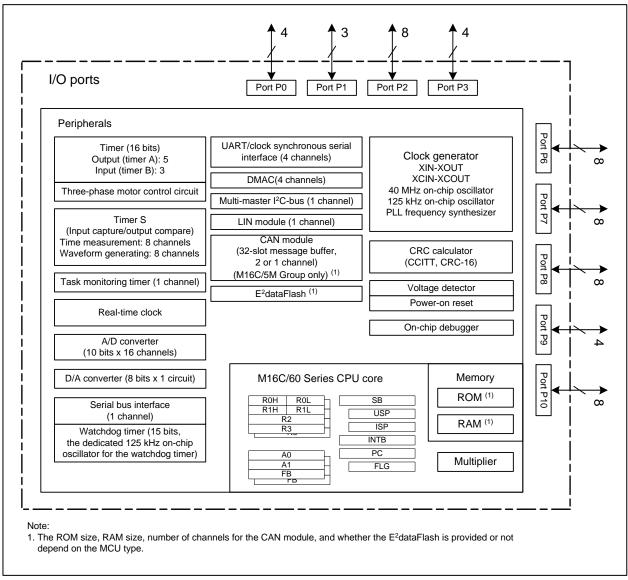

|    | 1.4      | Block Diagrams                                             | 12  |

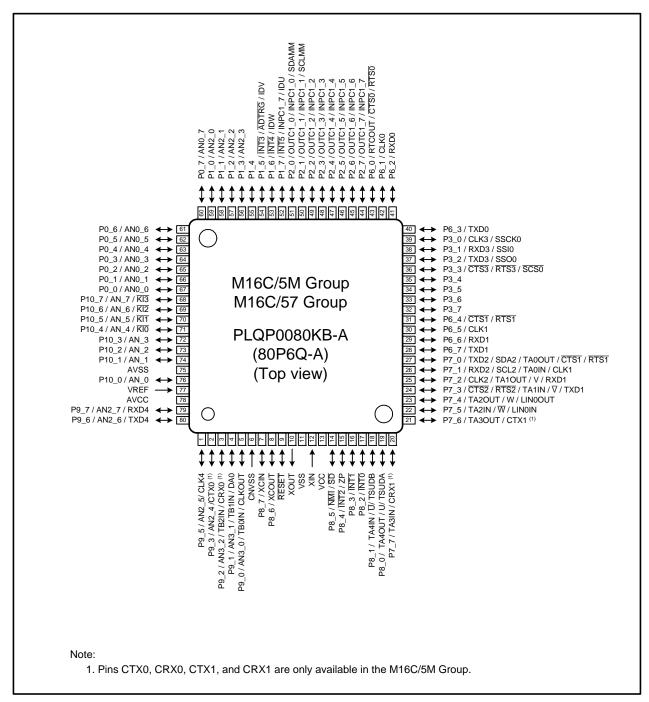

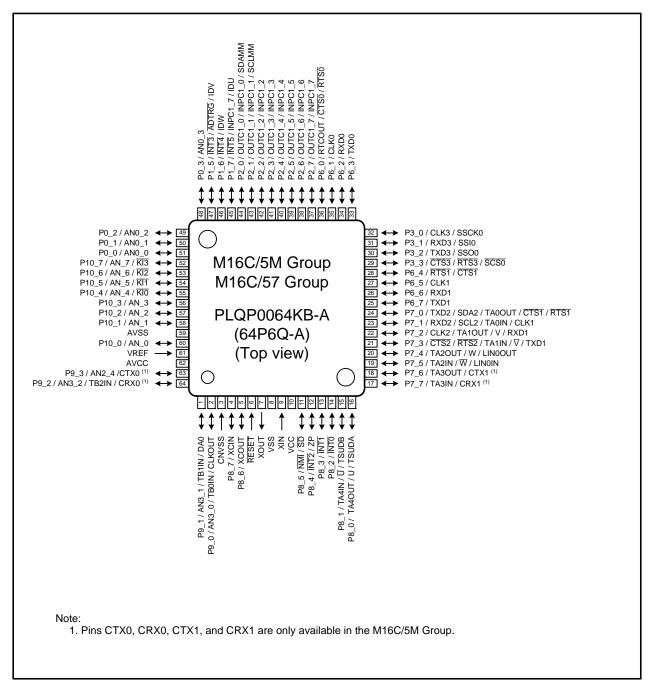

|    | 1.5      | Pin Assignments                                            | 15  |

|    | 1.6      | Pin Functions                                              | 24  |

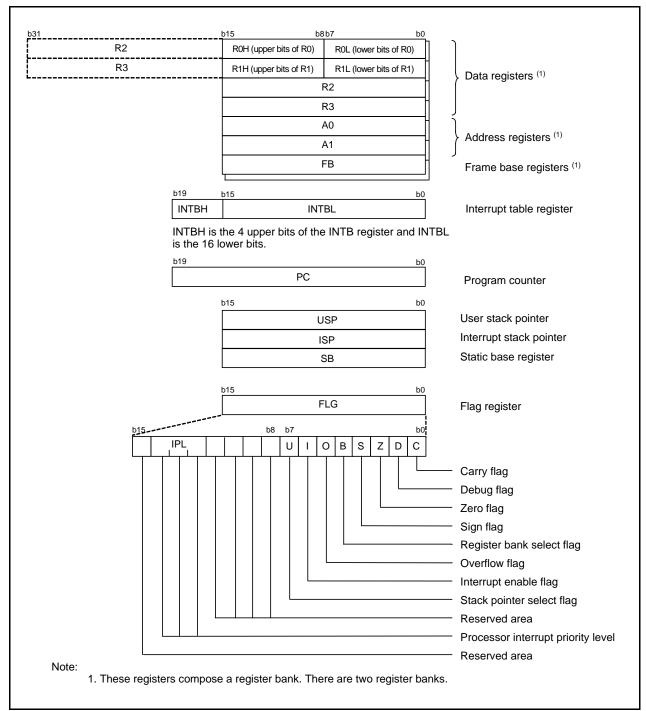

| 2. | Cer      | ntral Processing Unit (CPU)                                | 27  |

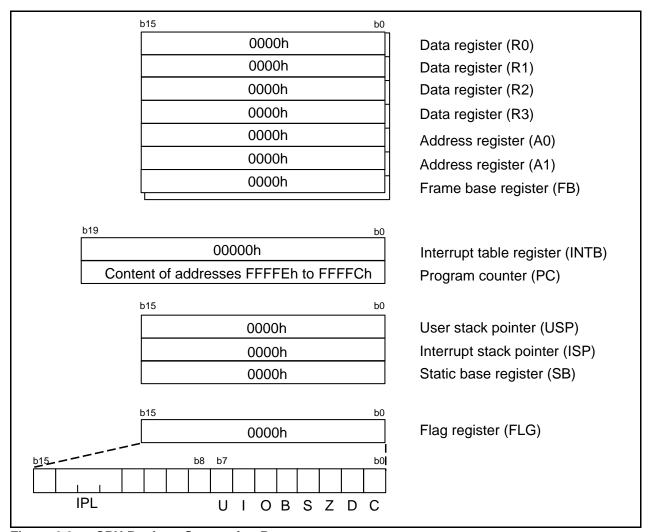

|    | 2.1      | Data Registers (R0, R1, R2, and R3)                        | 28  |

|    | 2.2      | Address Registers (A0 and A1)                              | 28  |

|    | 2.3      | Frame Base Register (FB)                                   | 28  |

|    | 2.4      | Interrupt Table Register (INTB)                            | 28  |

|    | 2.5      | Program Counter (PC)                                       | 28  |

|    | 2.6      | User Stack Pointer (USP) and Interrupt Stack Pointer (ISP) | 28  |

|    | 2.7      | Static Base Register (SB)                                  | 28  |

|    | 2.8      | Flag Register (FLG)                                        | 28  |

|    | 2.8.1    | 1 Carry Flag (C Flag)                                      | 28  |

|    | 2.8.2    | 2 Debug Flag (D Flag)                                      | 28  |

|    | 2.8.3    | 3 Zero Flag (Z Flag)                                       | 28  |

|    | 2.8.4    | 4 Sign Flag (S Flag)                                       | 28  |

|    | 2.8.5    | 5 Register Bank Select Flag (B Flag)                       | 28  |

|    | 2.8.6    | 6 Overflow Flag (O Flag)                                   | 28  |

|    | 2.8.7    | 7 Interrupt Enable Flag (I Flag)                           | 29  |

|    | 2.8.8    | 8 Stack Pointer Select Flag (U Flag)                       | 29  |

|    | 2.8.9    | 9 Processor Interrupt Priority Level (IPL)                 | 29  |

|    | 2.8.1    | 10 Reserved Areas                                          | 29  |

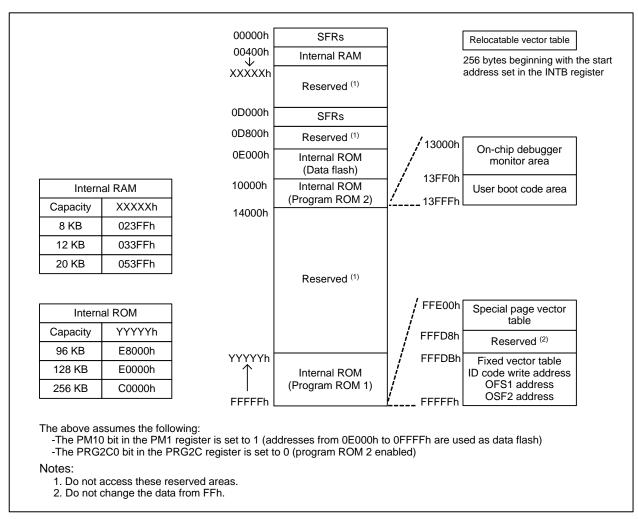

| 3. | Mer      | mory                                                       | 30  |

| 4. | Spe      | ecial Function Registers (SFRs)                            | 32  |

|    | 4.1      | SFRs                                                       | 32  |

|    | 4.2      | Notes on SFRs                                              | 79  |

|    | 4.2.1    | 1 Register Settings                                        | 79  |

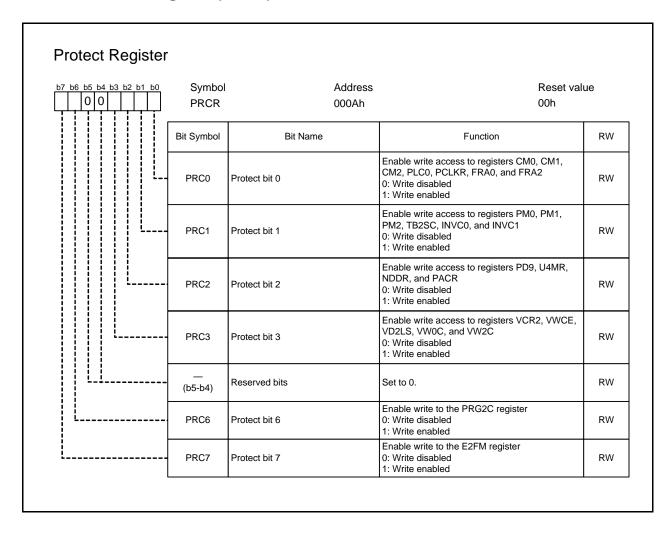

| 5. | Pro      | otection                                                   | 81  |

|    | 5.1      | Introduction                                               | 81  |

|    | 5.2      | Register                                                   |     |

|    | 5.2.1 | Protect Register (PRCR)                           | 81  |

|----|-------|---------------------------------------------------|-----|

|    | 5.3   | Notes on Protection                               | 83  |

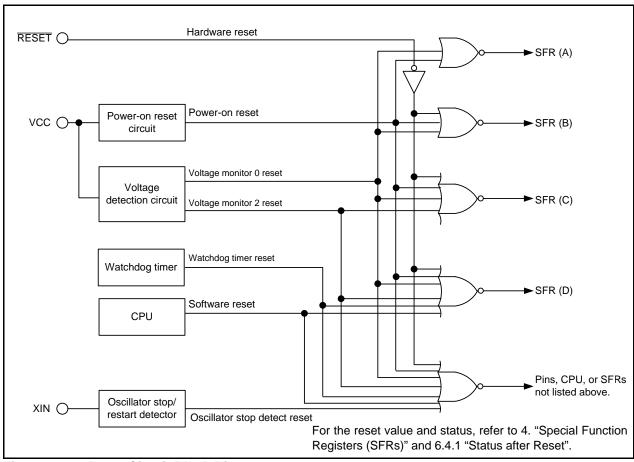

| 6. | Res   | ets                                               | 84  |

|    | 6.1   | Introduction                                      | 84  |

|    | 6.2   | Registers                                         | 86  |

|    | 6.2.1 | Processor Mode Register 0 (PM0)                   | 86  |

|    | 6.2.2 | Reset Source Determine Register (RSTFR)           | 87  |

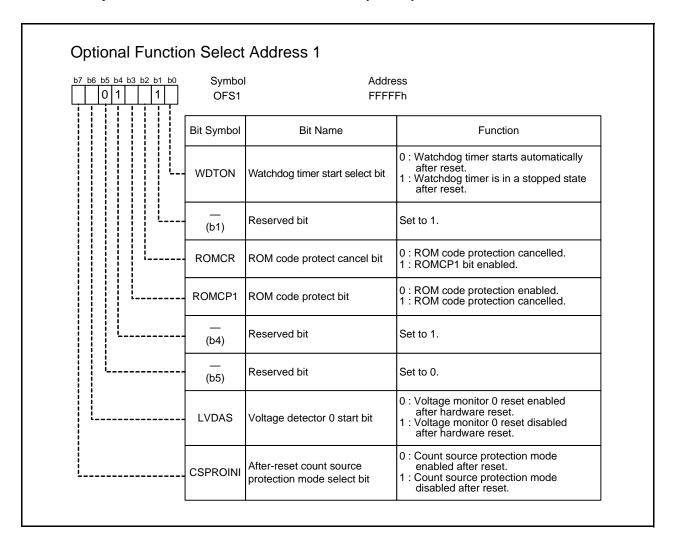

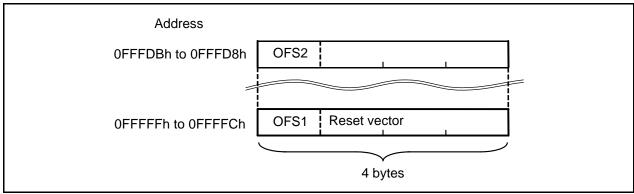

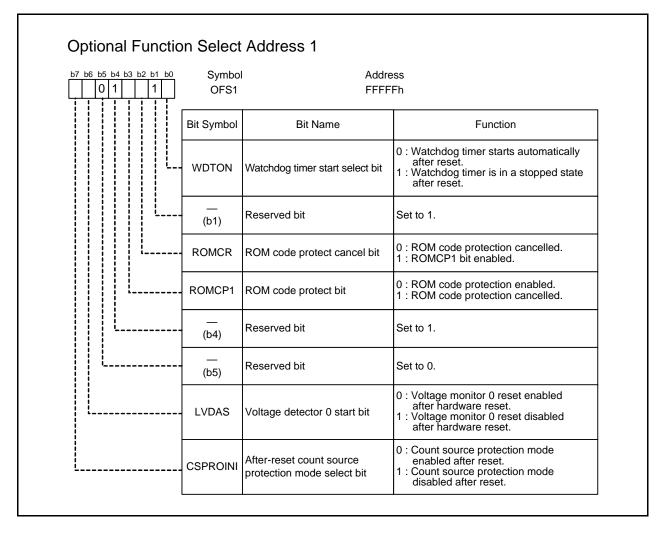

|    | 6.3   | Optional Function Select Area                     | 88  |

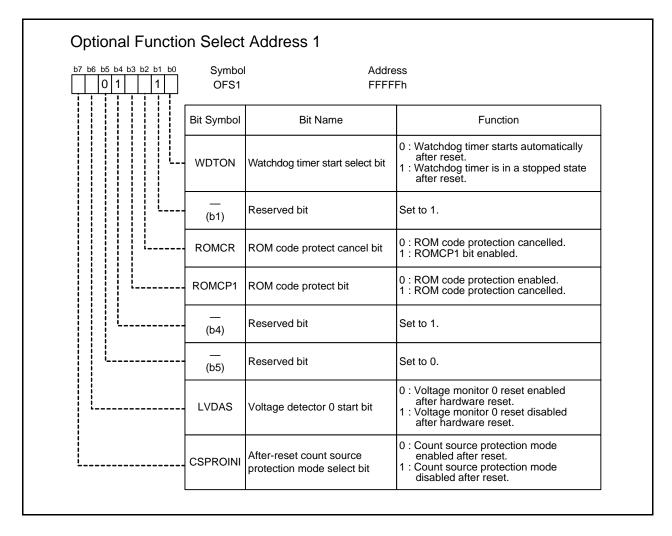

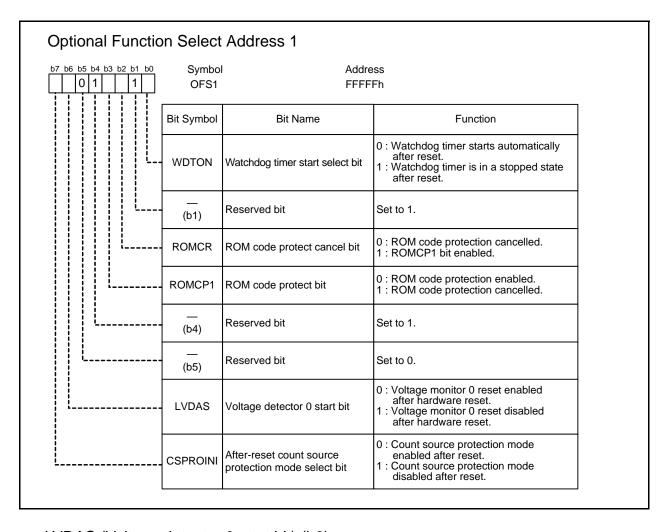

|    | 6.3.1 | Optional Function Select Address 1 (OFS1)         | 88  |

|    | 6.4   | Operations                                        | 90  |

|    | 6.4.1 | Status after Reset                                | 90  |

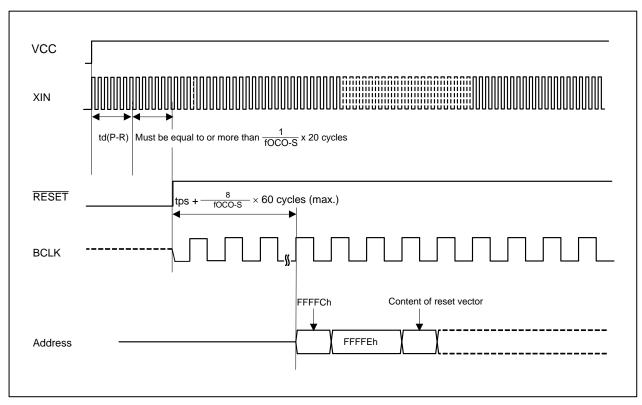

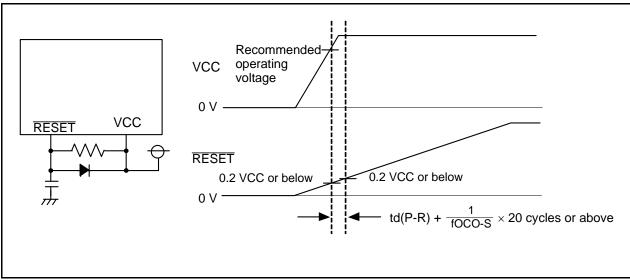

|    | 6.4.2 | 2 Hardware Reset                                  | 92  |

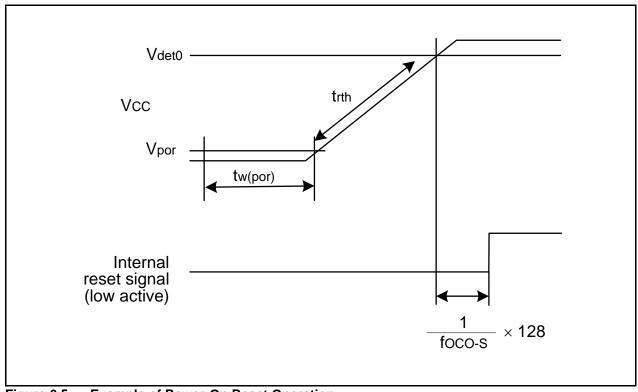

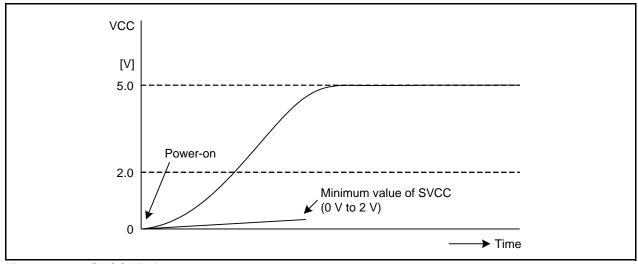

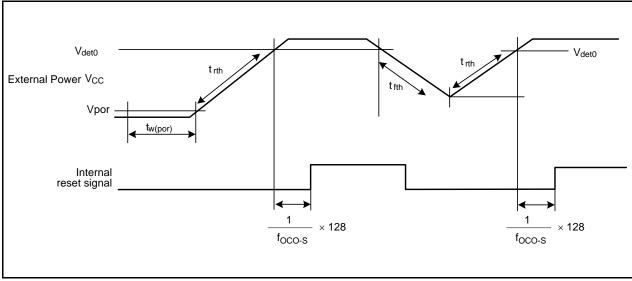

|    | 6.4.3 | Power-On Reset Function                           | 93  |

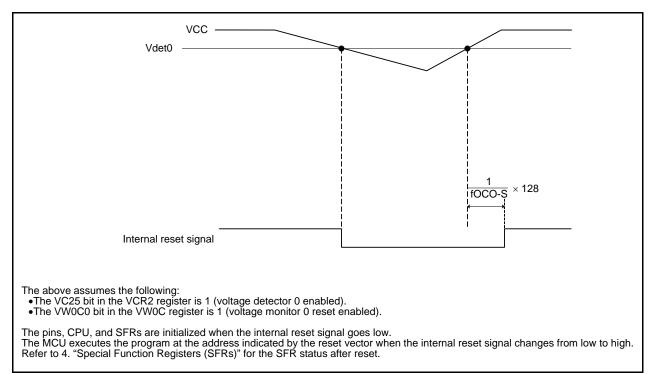

|    | 6.4.4 | Voltage Monitor 0 Reset                           | 94  |

|    | 6.4.5 | Voltage Monitor 2 Reset                           | 94  |

|    | 6.4.6 | Oscillator Stop Detect Reset                      | 94  |

|    | 6.4.7 | Watchdog Timer Reset                              | 94  |

|    | 6.4.8 | Software Reset                                    | 95  |

|    | 6.5   | Notes on Resets                                   |     |

|    | 6.5.1 |                                                   |     |

|    | 6.5.2 |                                                   |     |

|    | 6.5.3 | ,                                                 |     |

|    | 6.5.4 | Hardware Reset When VCC < Vdet0                   | 96  |

| 7. | Volt  | age Detector                                      | 97  |

|    | 7.1   | Introduction                                      | 97  |

|    | 7.2   | Registers                                         | 98  |

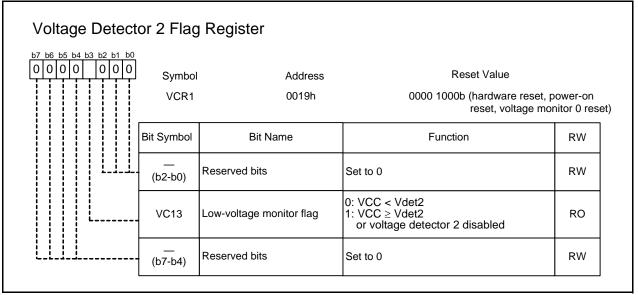

|    | 7.2.1 | Voltage Detector 2 Flag Register (VCR1)           | 99  |

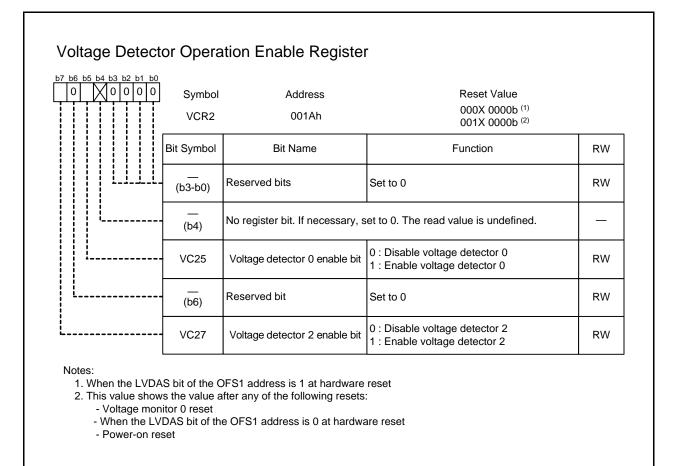

|    | 7.2.2 | Voltage Detector Operation Enable Register (VCR2) | 100 |

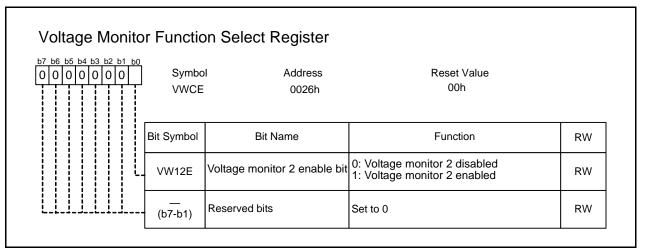

|    | 7.2.3 | Voltage Monitor Function Select Register (VWCE)   | 101 |

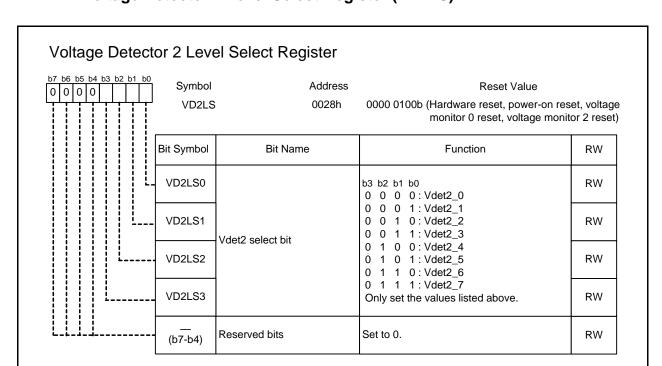

|    | 7.2.4 | Voltage Detector 2 Level Select Register (VD2LS)  | 102 |

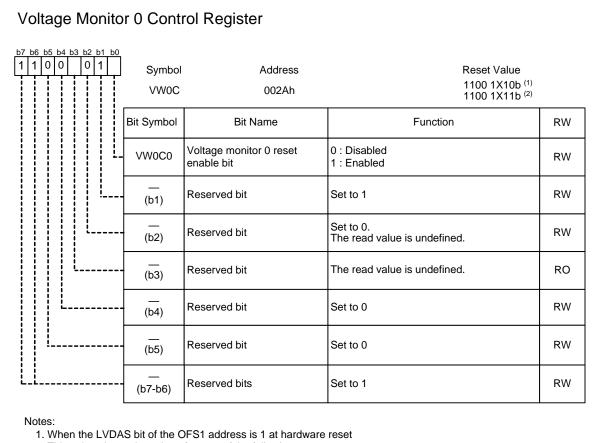

|    | 7.2.5 | Voltage Monitor 0 Control Register (VW0C)         | 103 |

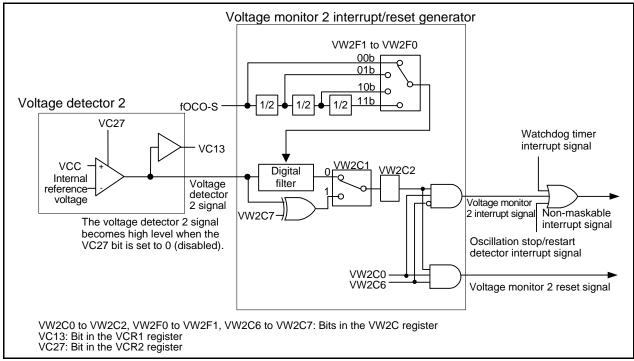

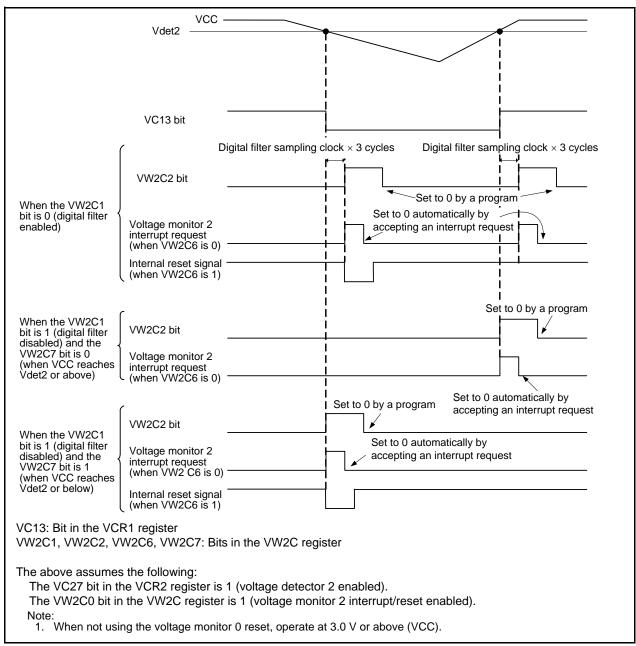

|    | 7.2.6 | Voltage Monitor 2 Control Register (VW2C)         | 104 |

|    | 7.3   | Optional Function Select Area                     | 106 |

|    | 7.3.1 | Optional Function Select Address 1 (OFS1)         | 106 |

|    | 7.4   | Operations                                        | 107 |

|    | 7.4.1 | Digital Filter                                    | 107 |

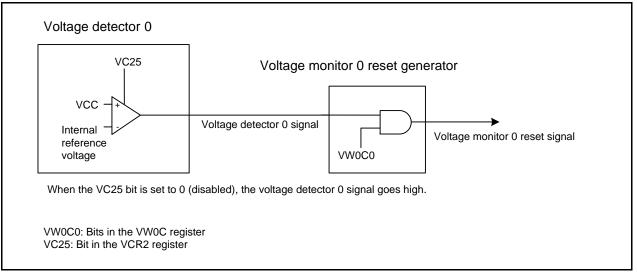

|    | 7.4.2 | Voltage Detector 0                                | 108 |

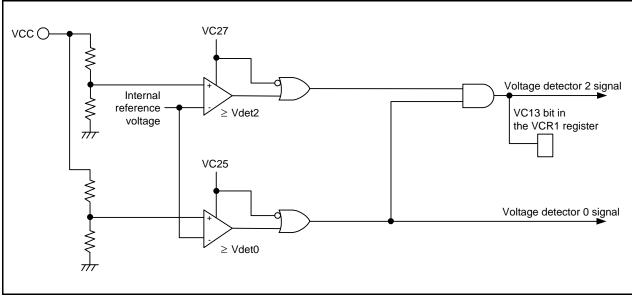

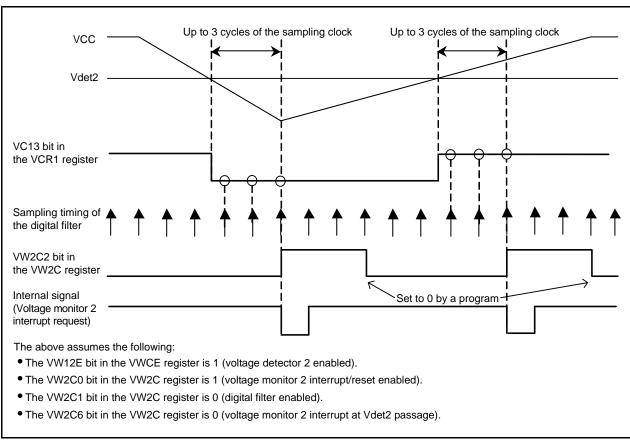

|    | 7.4.3 | Noltage Detector 2                                | 110 |

|    | 7.5   | Interrupte                                        | 112 |

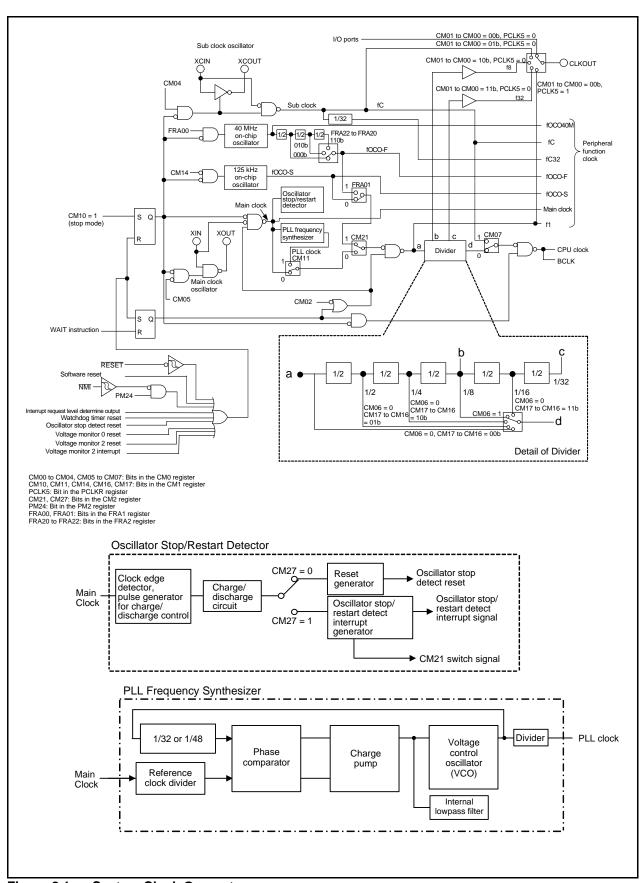

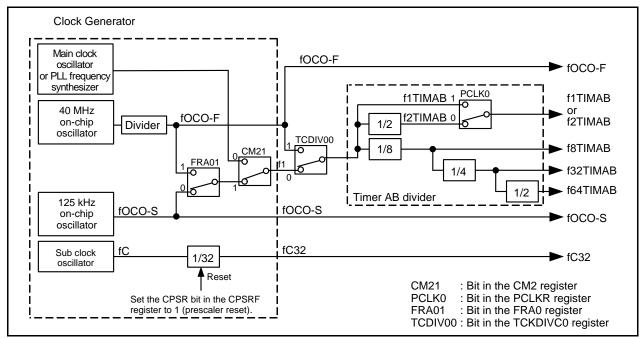

| 3. | Clo   | ck Generator                                                                     | . 114 |

|----|-------|----------------------------------------------------------------------------------|-------|

|    | 8.1   | Introduction                                                                     | 114   |

|    | 8.2   | Registers                                                                        | 116   |

|    | 8.2.1 | System Clock Control Register 0 (CM0)                                            | 117   |

|    | 8.2.2 | System Clock Control Register 1 (CM1)                                            | 119   |

|    | 8.2.3 | Oscillation Stop Detection Register (CM2)                                        | 121   |

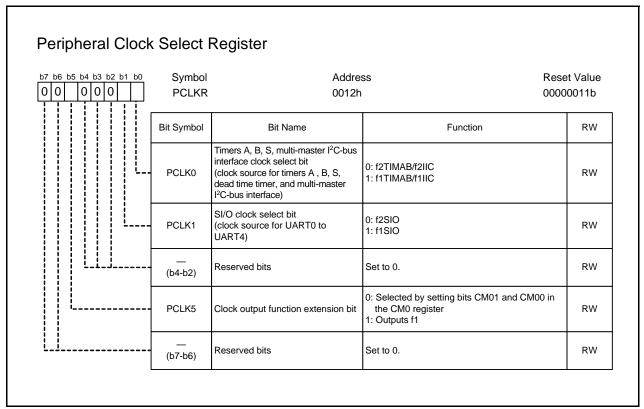

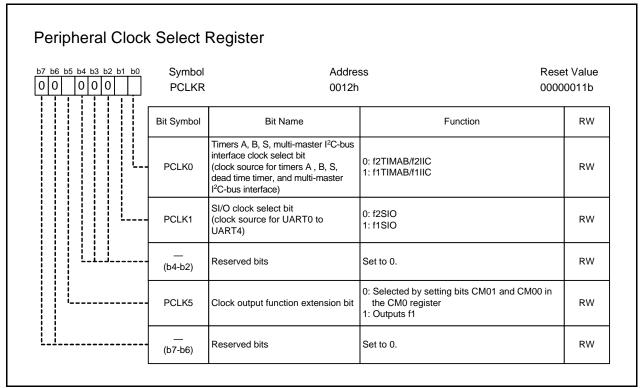

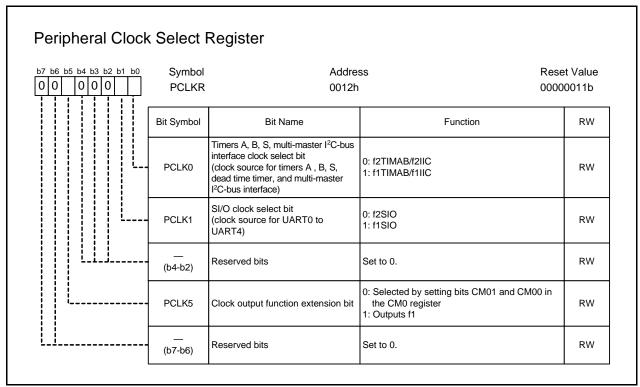

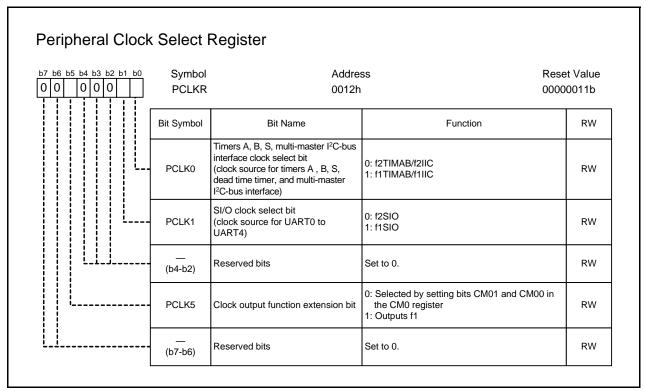

|    | 8.2.4 | Peripheral Clock Select Register (PCLKR)                                         | 123   |

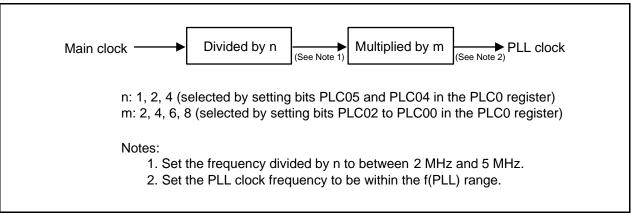

|    | 8.2.5 | PLL Control Register 0 (PLC0)                                                    | 124   |

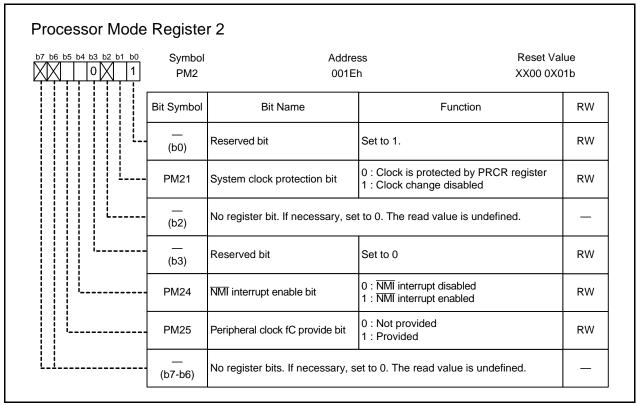

|    | 8.2.6 | Processor Mode Register 2 (PM2)                                                  | 125   |

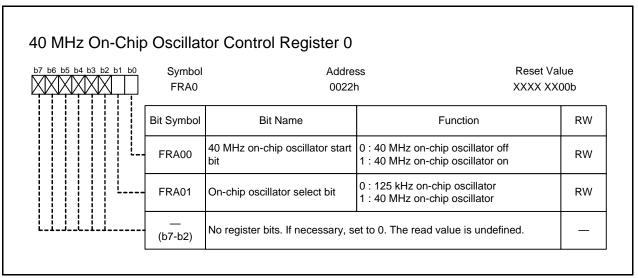

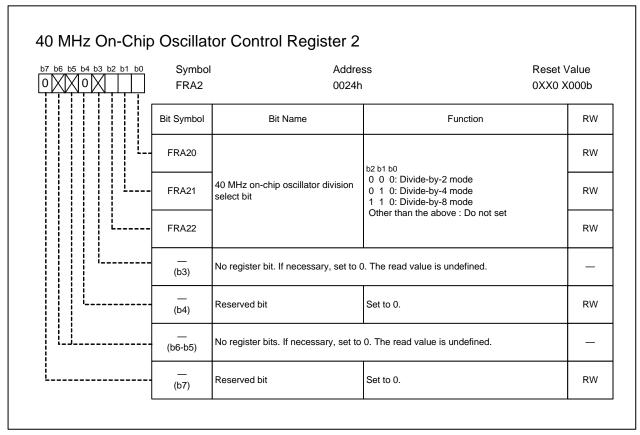

|    | 8.2.7 | 40 MHz On-Chip Oscillator Control Register 0 (FRA0)                              | 126   |

|    | 8.2.8 |                                                                                  |       |

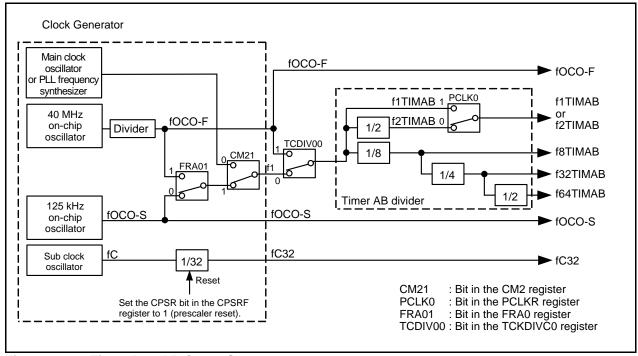

|    | 8.3   | Clocks Generated by Clock Generators                                             | 128   |

|    | 8.3.1 | Main Clock                                                                       | 128   |

|    | 8.3.2 | PLL Clock                                                                        | 129   |

|    | 8.3.3 | fOCO40M                                                                          | 130   |

|    | 8.3.4 | fOCO-F                                                                           | 130   |

|    | 8.3.5 | 125 kHz On-Chip Oscillator Clock (fOCO-S)                                        | 130   |

|    | 8.3.6 | Sub Clock (fC)                                                                   | 131   |

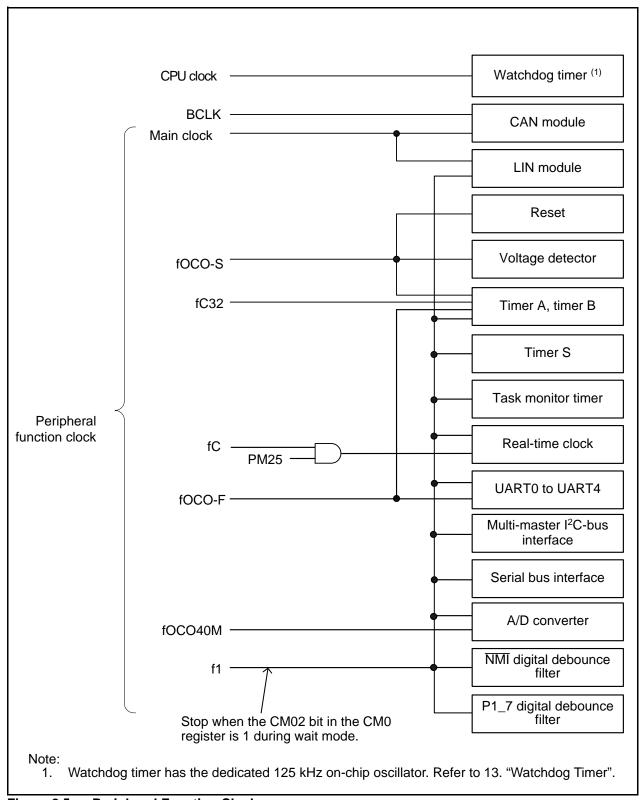

|    | 8.4   | CPU Clock and Peripheral Function Clocks                                         | 132   |

|    | 8.4.1 | CPU Clock and BCLK                                                               | 132   |

|    | 8.4.2 | Peripheral Function Clocks (f1, fOCO40M, fOCO-F, fOCO-S, fC32, fC, Main Clock) . | 132   |

|    | 8.5   | Clock Output Function                                                            | 134   |

|    | 8.6   | System Clock Protection Function                                                 | 134   |

|    | 8.7   | Oscillator Stop/Restart Detect Function                                          | 135   |

|    | 8.7.1 | Operation When CM27 Bit is 0 (Oscillator Stop Detect Reset)                      | 135   |

|    | 8.7.2 |                                                                                  |       |

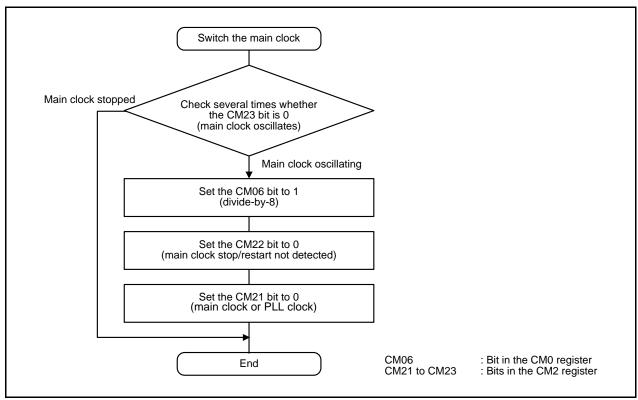

|    | 8.7.3 | Using the Oscillator Stop/Restart Detect Function                                | 137   |

|    | 8.8   | Interrupt                                                                        | 137   |

|    | 8.9   | Notes on Clock Generator                                                         | 138   |

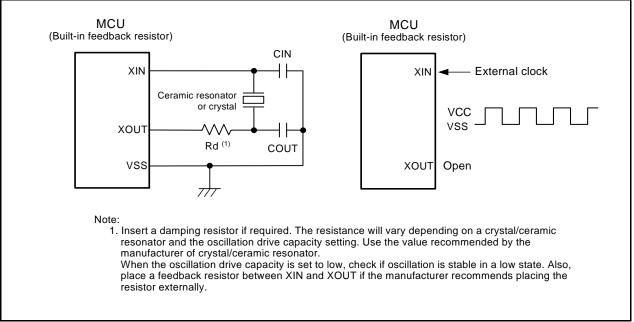

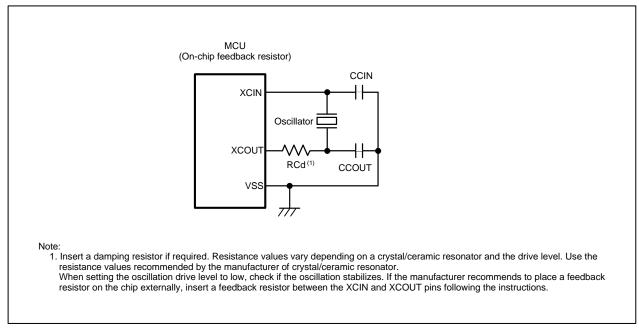

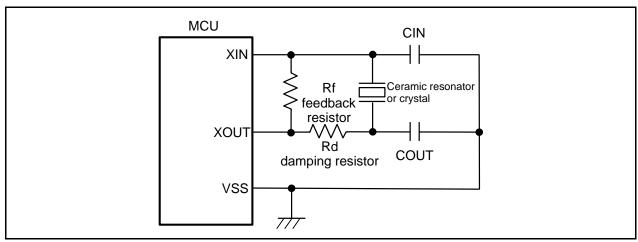

|    | 8.9.1 | Oscillator Using a Crystal or a Ceramic Resonator                                | 138   |

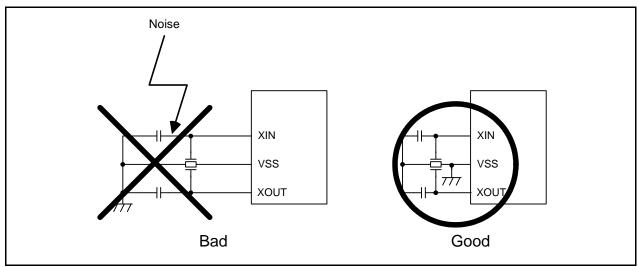

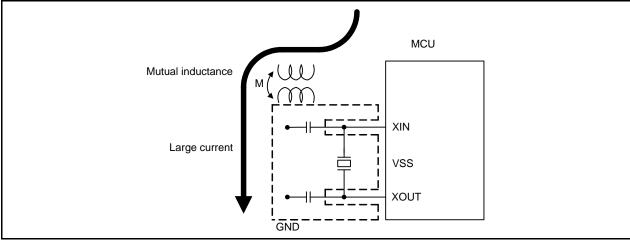

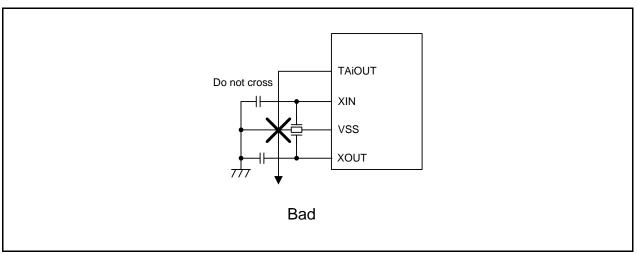

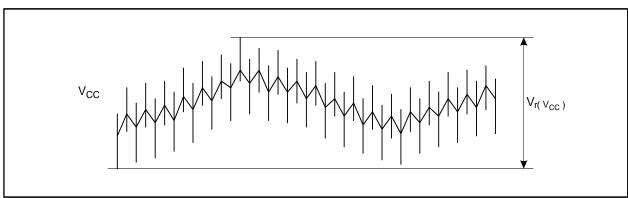

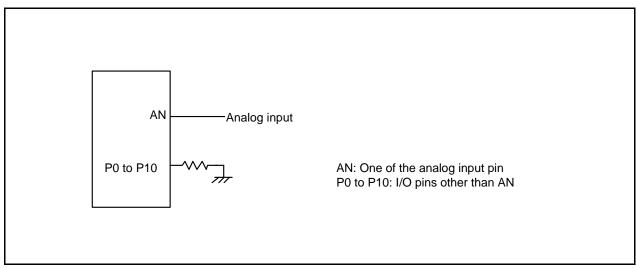

|    | 8.9.2 | Noise Countermeasure                                                             | 139   |

|    | 8.9.3 | CPU Clock                                                                        | 140   |

|    | 8.9.4 | Oscillator Stop/Restart Detect Function                                          | 140   |

|    | 8.9.5 | PLL Frequency Synthesizer                                                        | 141   |

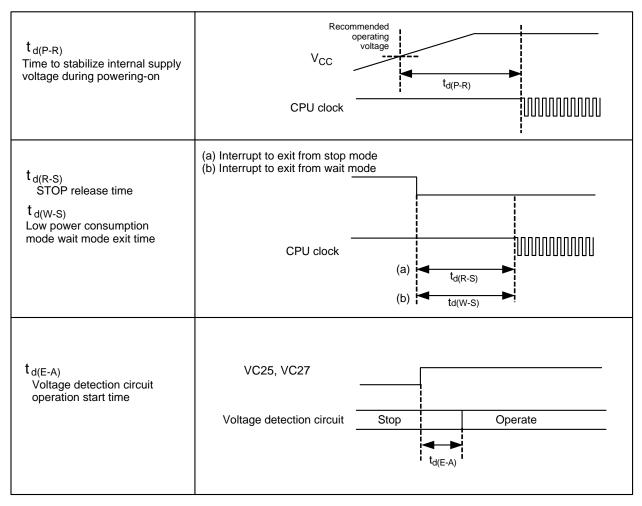

| 9. | Pov   | ver Control                                                                      | . 142 |

|    | 9.1   | Introduction                                                                     | 142   |

|    | 9.2   | Registers                                                                        |       |

|    | 9.2.1 |                                                                                  |       |

|    | 9.2.2 | ,                                                                                |       |

|    | 0.2   | · · · · · · · · · · · · · · · · · · ·                                            | 1/6   |

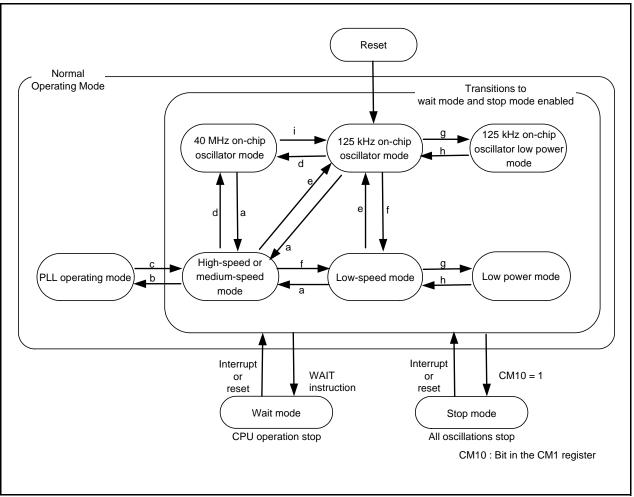

| 9.3.1     | Normal Operating Mode                                               | 146 |

|-----------|---------------------------------------------------------------------|-----|

| 9.3.2     | Clock Mode Transition Procedure                                     | 150 |

| 9.3.3     | Wait Mode                                                           | 153 |

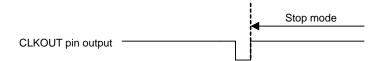

| 9.3.4     | Stop Mode                                                           | 155 |

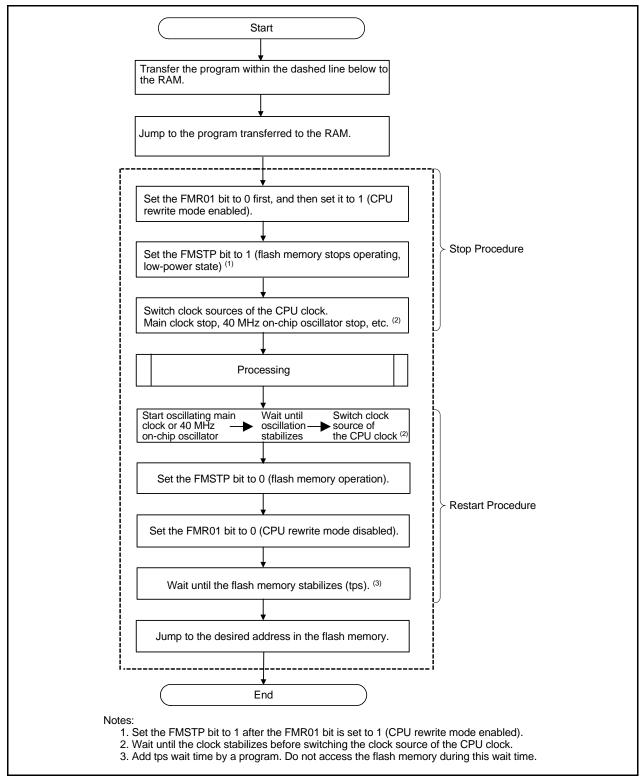

| 9.4 P     | Power Control in Flash Memory                                       | 157 |

| 9.4.1     | Stopping Flash Memory                                               | 157 |

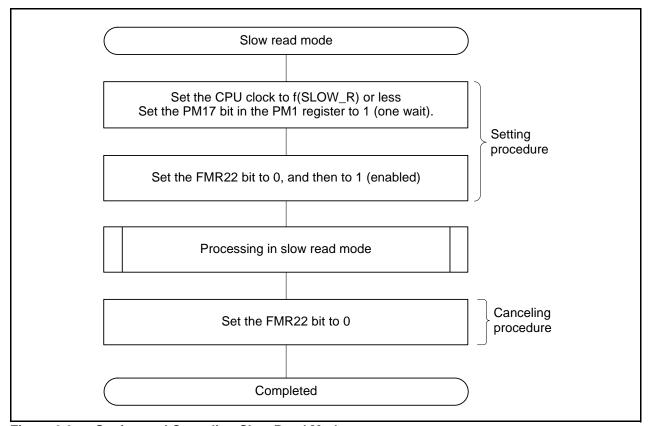

| 9.4.2     | Reading Flash Memory                                                | 158 |

| 9.5 R     | Reducing Power Consumption                                          |     |

| 9.5.1     | Ports                                                               |     |

| 9.5.2     | A/D Converter                                                       |     |

| 9.5.3     | D/A Converter                                                       |     |

| 9.5.4     | Stopping Peripheral Functions                                       | 160 |

| 9.5.5     | Switching the Oscillation-Driving Capacity                          |     |

| 9.6 N     | Notes on Power Control                                              | 161 |

| 9.6.1     | CPU Clock                                                           | 161 |

| 9.6.2     | Wait Mode                                                           | 161 |

| 9.6.3     | Stop Mode                                                           | 161 |

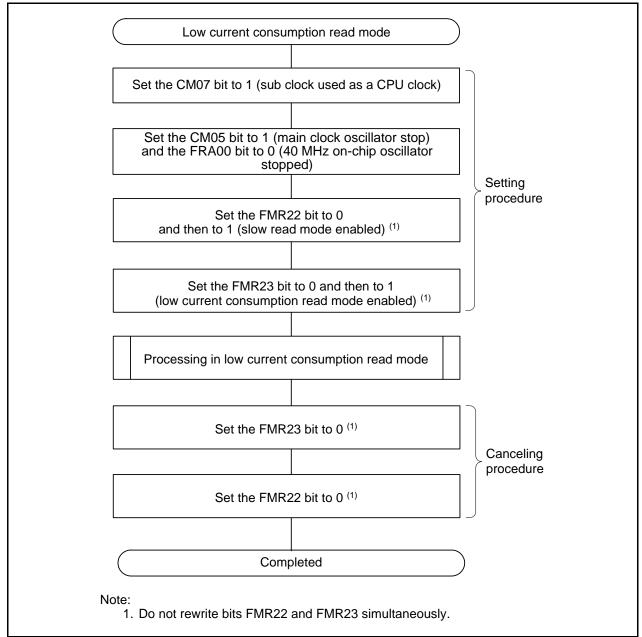

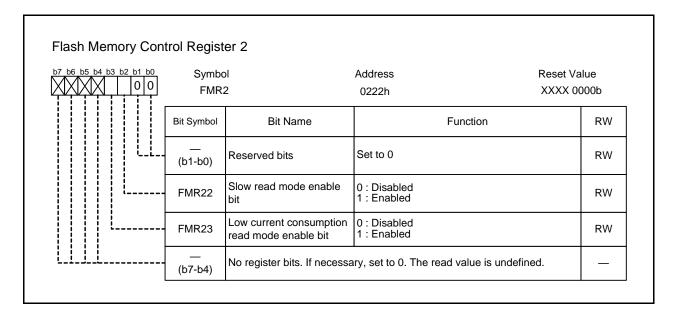

| 9.6.4     | Low Current Consumption Read Mode                                   | 162 |

| 9.6.5     | Slow Read Mode                                                      | 162 |

| 10. Proce | essor Mode                                                          | 163 |

| 10.1 Ir   | ntroduction                                                         | 163 |

| 10.2 R    | Registers                                                           | 164 |

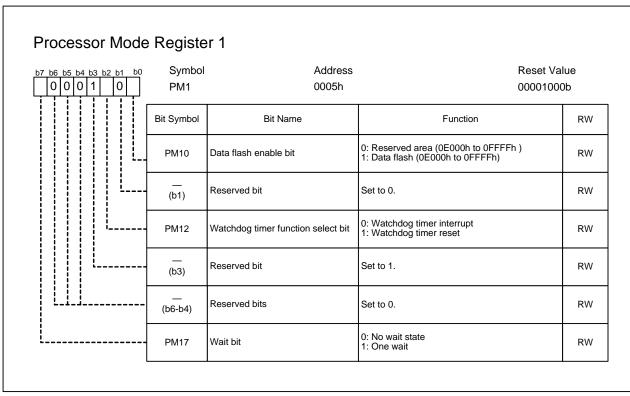

| 10.2.1    | Processor Mode Register 1 (PM1)                                     | 164 |

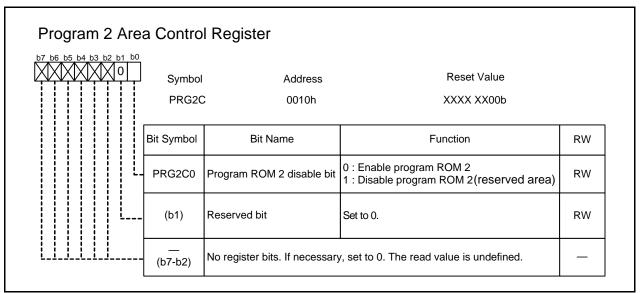

| 10.2.2    | Program 2 Area Control Register (PRG2C)                             |     |

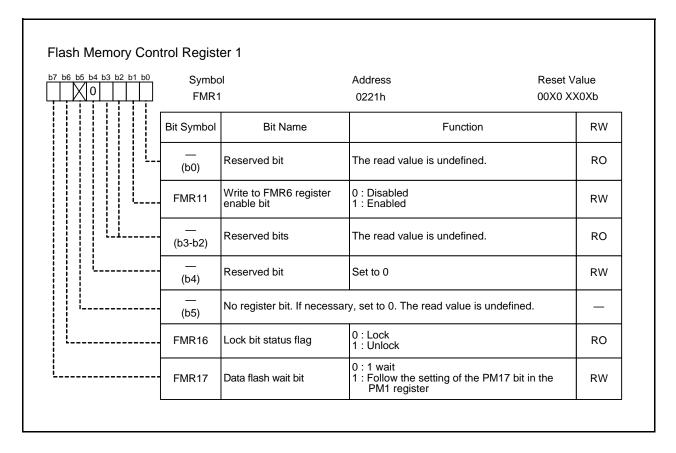

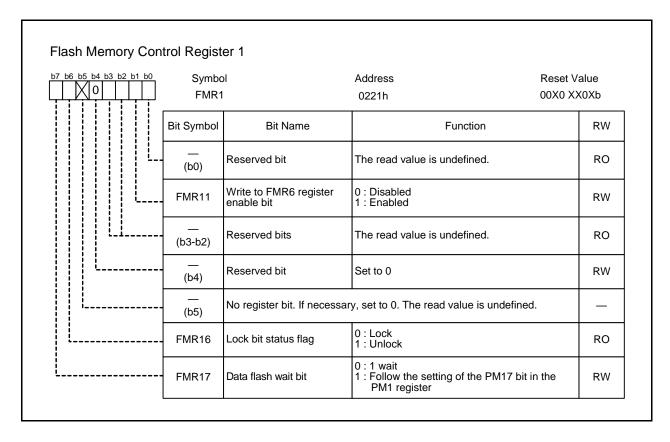

| 10.2.3    | Flash Memory Control Register 1 (FMR1)                              |     |

| 10.3 S    | Software Wait                                                       | 167 |

| 10.4 B    | Bus Hold                                                            | 167 |

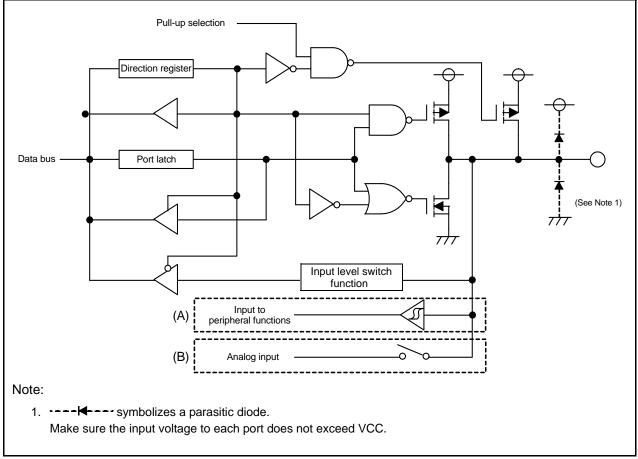

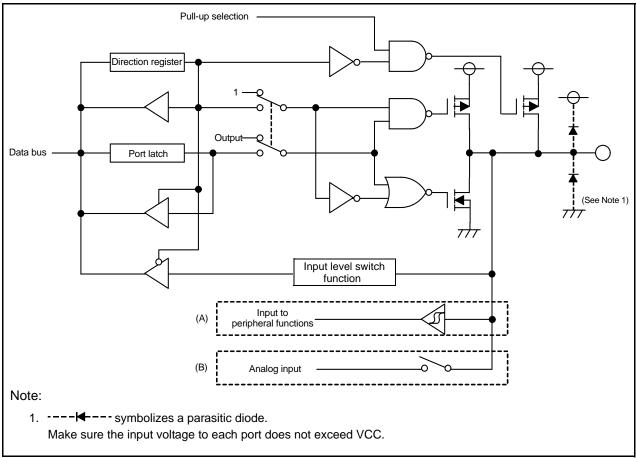

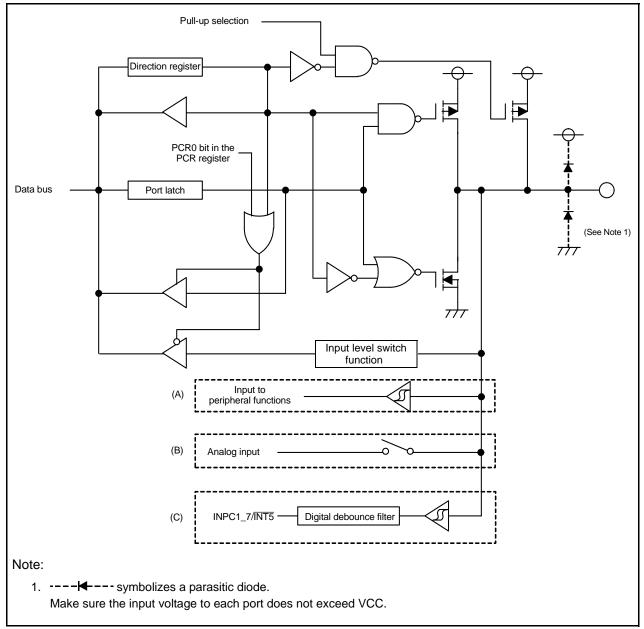

| 11. Progr | rammable I/O Ports                                                  | 168 |

| 11.1 Ir   | ntroduction                                                         | 168 |

| 11.2 l/   | O Ports and Pins                                                    | 169 |

| 11.3 R    | Registers                                                           | 177 |

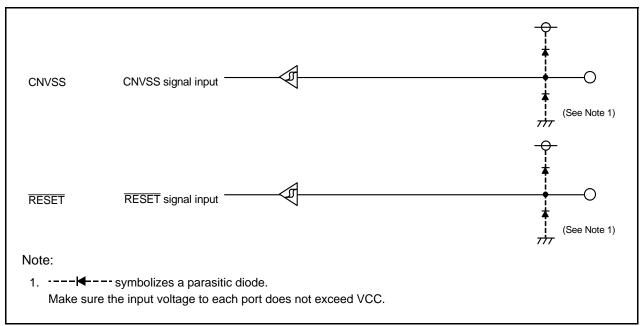

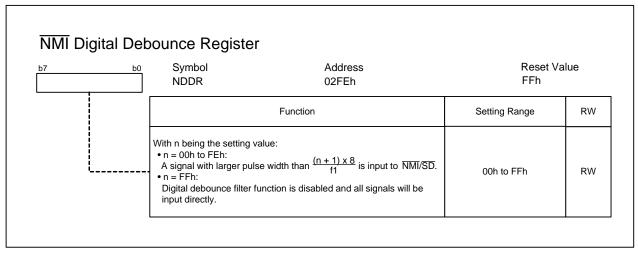

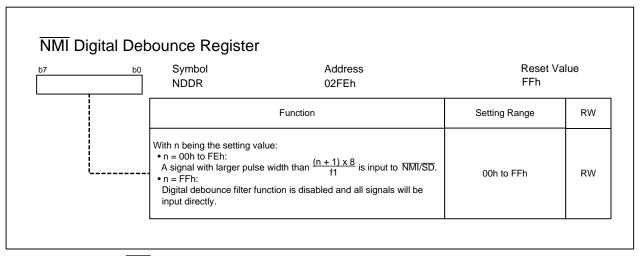

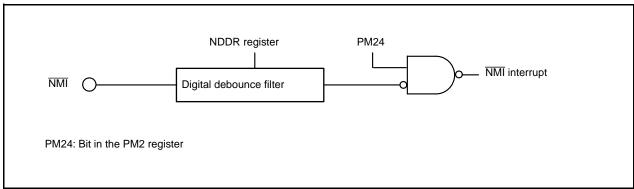

| 11.3.1    | NMI Digital Debounce Register (NDDR)                                | 178 |

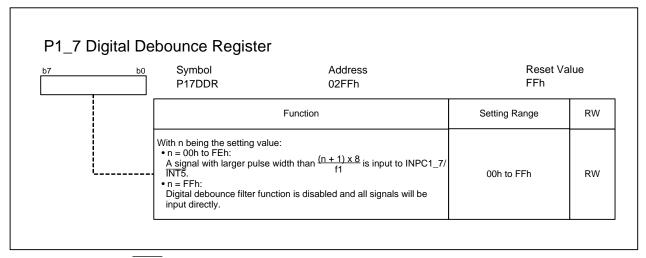

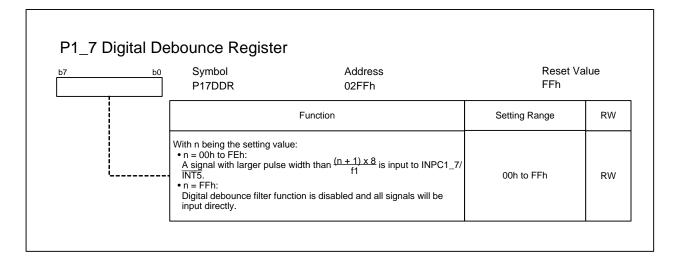

| 11.3.2    | P1_7 Digital Debounce Register (P17DDR)                             | 178 |

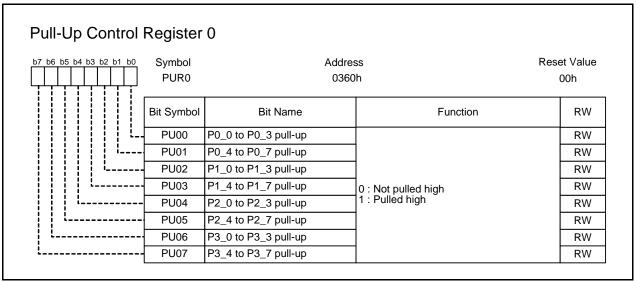

| 11.3.3    | Pull-Up Control Register 0 (PUR0)                                   | 179 |

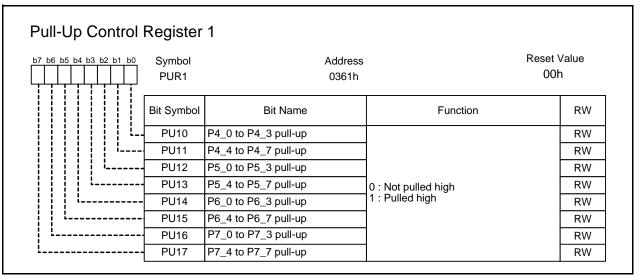

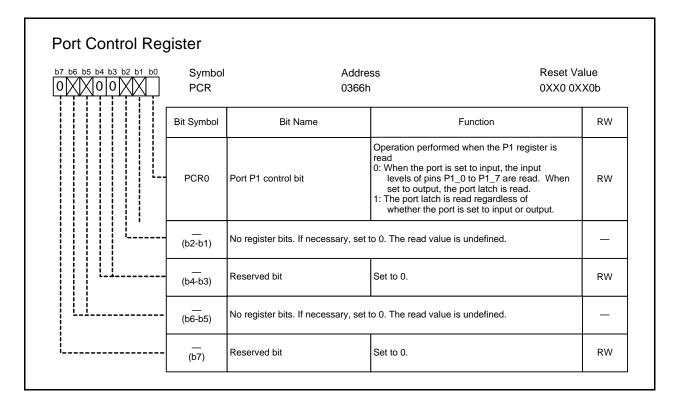

| 11.3.4    |                                                                     |     |

|           | Pull-Up Control Register 1 (PUR1)                                   | 179 |

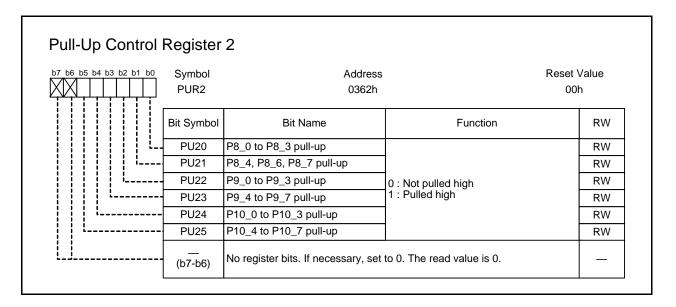

| 11.3.5    | Pull-Up Control Register 1 (PUR1) Pull-Up Control Register 2 (PUR2) |     |

|           |                                                                     | 180 |

| 11.3.5    | Pull-Up Control Register 2 (PUR2)                                   | 180 |

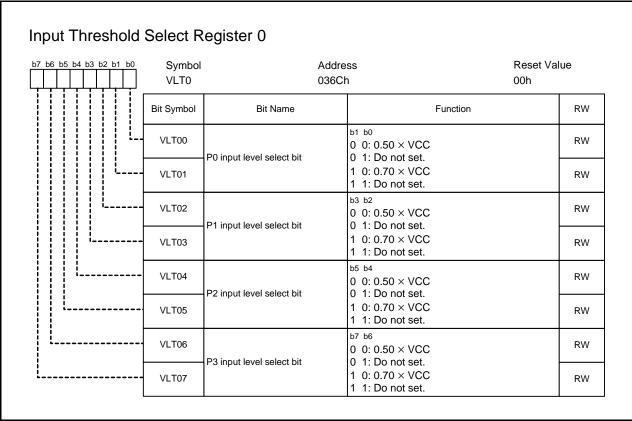

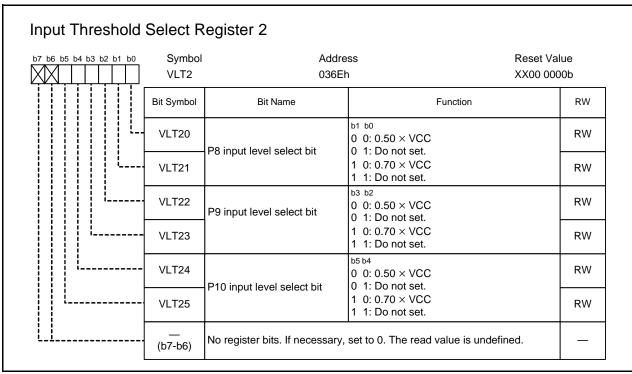

|    | 11.3.9      | Input Threshold Select Register 2 (VLT2)                                                                                                                                                                                                                                                                                                                                 | 183 |

|----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

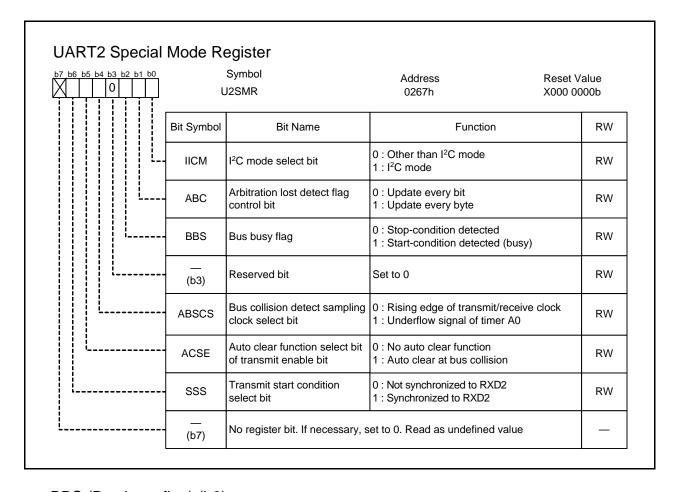

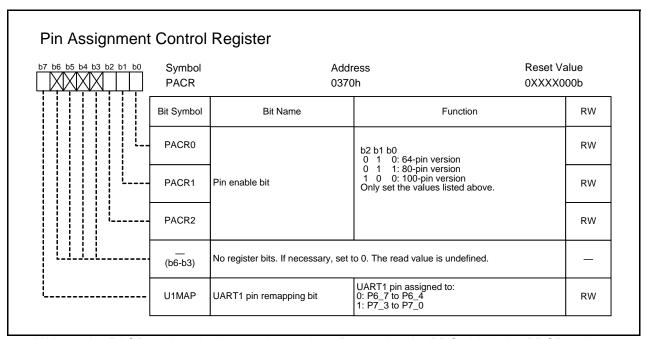

|    | 11.3.10     | Pin Assignment Control Register (PACR)                                                                                                                                                                                                                                                                                                                                   | 184 |

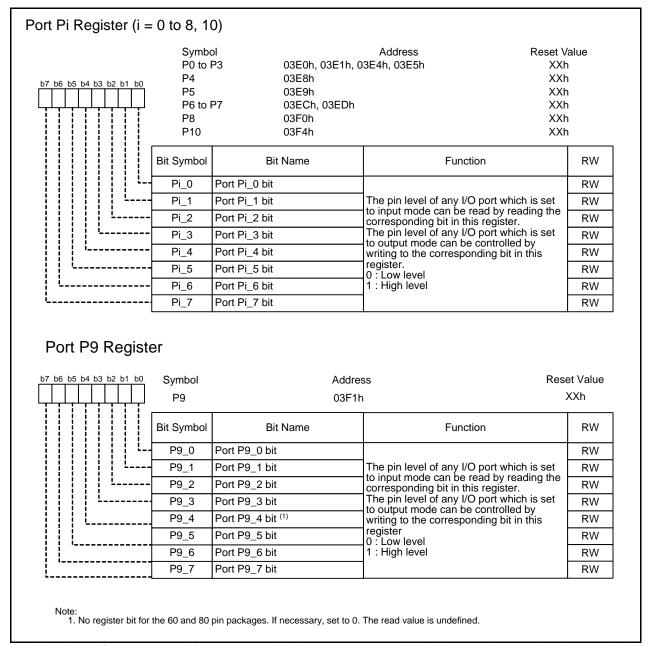

|    | 11.3.11     | Port Pi Register (Pi) (i = 0 to 10)                                                                                                                                                                                                                                                                                                                                      | 185 |

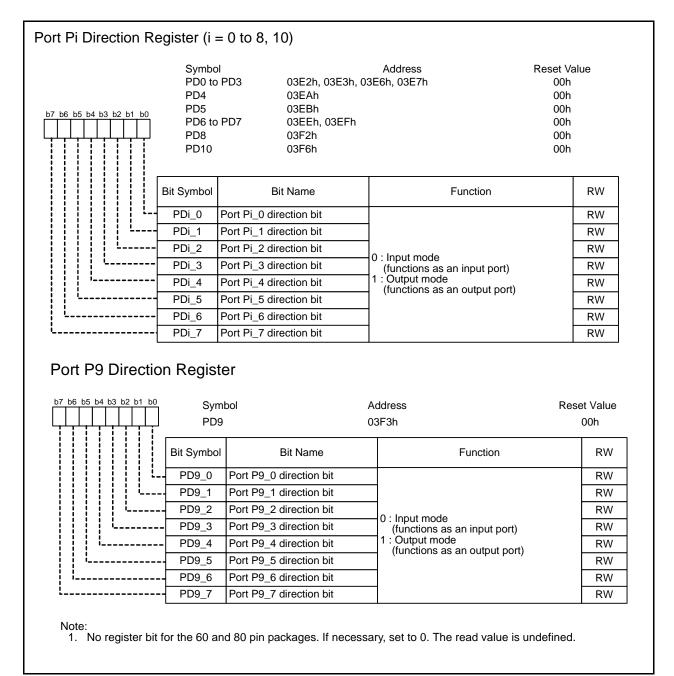

|    | 11.3.12     | Port Pi Direction Register (PDi) (i = 0 to 10)                                                                                                                                                                                                                                                                                                                           | 186 |

|    | 11.4 Per    | ipheral Function I/O                                                                                                                                                                                                                                                                                                                                                     | 187 |

|    | 11.4.1      | Peripheral Function I/O and Port Direction Bits                                                                                                                                                                                                                                                                                                                          | 187 |

|    | 11.4.2      | Priority Level of Peripheral Function I/O                                                                                                                                                                                                                                                                                                                                | 187 |

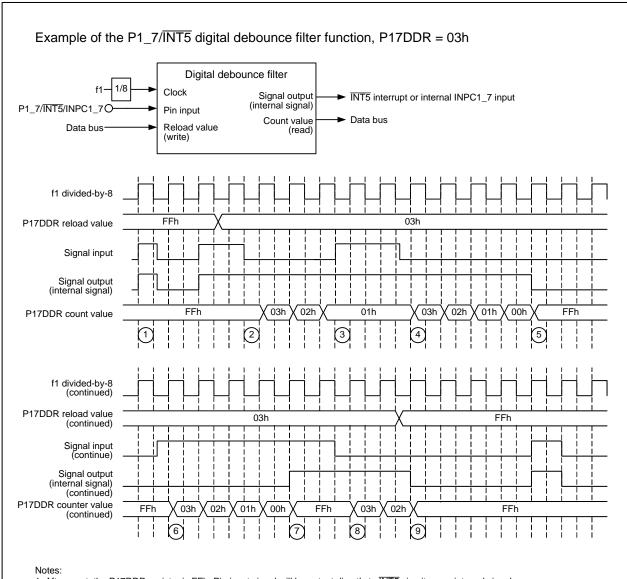

|    | 11.4.3      | Digital Debounce Filters                                                                                                                                                                                                                                                                                                                                                 | 188 |

|    | 11.5 Una    | assigned Pin Handling                                                                                                                                                                                                                                                                                                                                                    | 190 |

|    | 11.6 Not    | es on Programmable I/O Ports                                                                                                                                                                                                                                                                                                                                             | 191 |

|    | 11.6.1      | Pin Assignment Control                                                                                                                                                                                                                                                                                                                                                   | 191 |

|    | 11.6.2      | Influence of SD                                                                                                                                                                                                                                                                                                                                                          | 191 |

|    | 11.6.3      | Input Voltage Threshold                                                                                                                                                                                                                                                                                                                                                  | 191 |

| 12 | 2. Interrup | ots                                                                                                                                                                                                                                                                                                                                                                      | 192 |

|    | 12.1 Intr   | oduction                                                                                                                                                                                                                                                                                                                                                                 | 192 |

|    | 12.2 Reg    | gisters                                                                                                                                                                                                                                                                                                                                                                  | 193 |

|    | 12.2.1      | Processor Mode Register 2 (PM2)                                                                                                                                                                                                                                                                                                                                          | 195 |

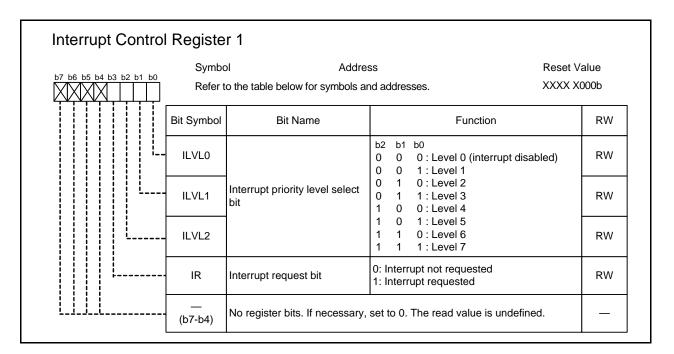

|    | 12.2.2      | Interrupt Control Register 1 (E2FIC, BCNIC/TMOSIC, DM0IC to DM3IC, KUPIC,ADIC, S0TIC/L0WIC, S1TIC, S2TIC, S0RIC to S2RIC, S3RIC/C1WIC, TA0IC to TA4IC, TB0IC to TB5IC, S4TIC/RTCCIC, S4RIC, C0WIC,S3TIC/C0EIC, RTCTIC/C1EIC, C0RIC, C1RIC, C0TIC, C1TIC, C0FRIC, C1FRIC, C0FTIC, C1FTIC, ICOC0IC, ICOCH0IC, ICOC1IC/IICIC, ICOCH1IC/SCLDAIC, ICOCH2IC to ICOCH3IC, BTIC) | 196 |

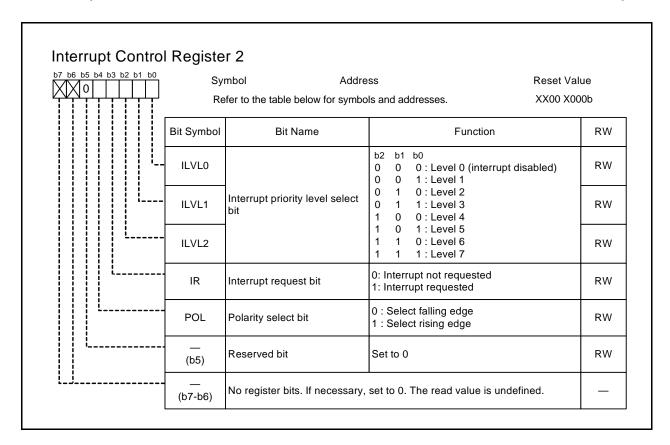

|    | 12.2.3      | Interrupt Control Register 2 (INT7IC/SS0IC, INT6IC/LIN0IC, INT3IC, INT5IC, INT4IC, INT0IC to INT2IC)                                                                                                                                                                                                                                                                     | 197 |

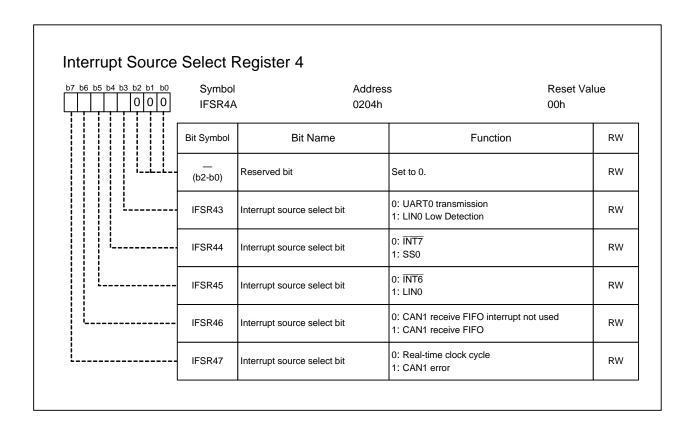

|    | 12.2.4      | Interrupt Source Select Register 4 (IFSR4A)                                                                                                                                                                                                                                                                                                                              | 199 |

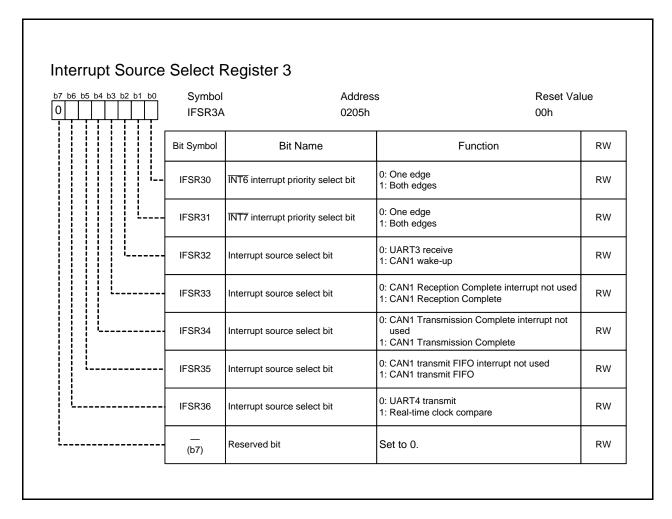

|    | 12.2.5      | Interrupt Source Select Register 3 (IFSR3A)                                                                                                                                                                                                                                                                                                                              | 200 |

|    | 12.2.6      | Interrupt Source Select Register 2 (IFSR2A)                                                                                                                                                                                                                                                                                                                              | 201 |

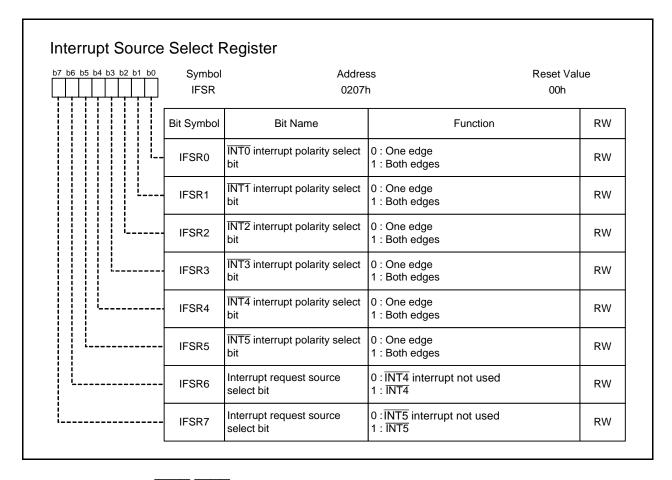

|    | 12.2.7      | Interrupt Source Select Register (IFSR)                                                                                                                                                                                                                                                                                                                                  | 202 |

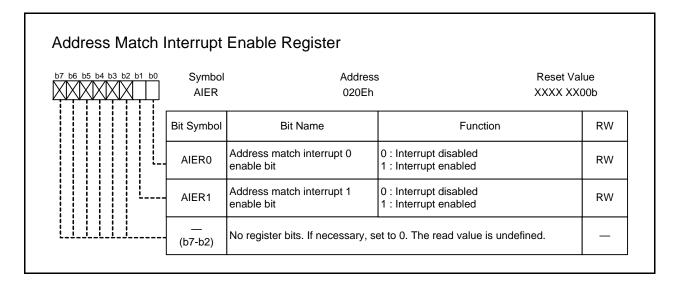

|    | 12.2.8      | Address Match Interrupt Enable Register (AIER)                                                                                                                                                                                                                                                                                                                           | 203 |

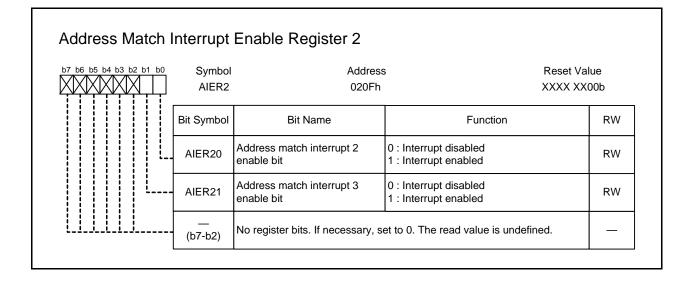

|    | 12.2.9      | Address Match Interrupt Enable Register 2 (AIER2)                                                                                                                                                                                                                                                                                                                        | 203 |

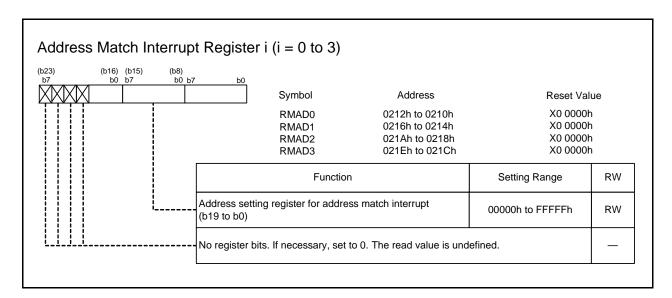

|    | 12.2.10     | Address Match Interrupt Register i (RMADi) (i = 0 to 3)                                                                                                                                                                                                                                                                                                                  | 204 |

|    | 12.2.11     | NMI Digital Debounce Register (NDDR)                                                                                                                                                                                                                                                                                                                                     | 205 |

|    | 12.2.12     | P1_7 Digital Debounce Register (P17DDR)                                                                                                                                                                                                                                                                                                                                  | 205 |

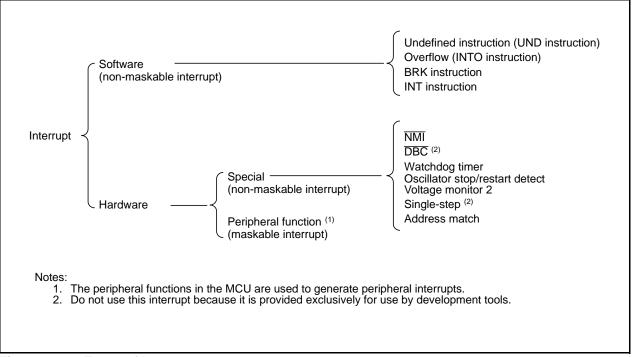

|    | 12.3 Typ    | es of Interrupts                                                                                                                                                                                                                                                                                                                                                         | 206 |

|    | 12.4 Sof    | tware Interrupts                                                                                                                                                                                                                                                                                                                                                         | 207 |

|    | 12.4.1      | Undefined Instruction Interrupt                                                                                                                                                                                                                                                                                                                                          | 207 |

|    | 12.4.2      | Overflow Interrupt                                                                                                                                                                                                                                                                                                                                                       | 207 |

|    | 12.4.3      | BRK Interrupt                                                                                                                                                                                                                                                                                                                                                            | 207 |

|    | 12.4.4      | INT Instruction Interrupt                                                                                                                                                                                                                                                                                                                                                | 207 |

|    | 12.5 Har    | dware Interrupts                                                                                                                                                                                                                                                                                                                                                         | 208 |

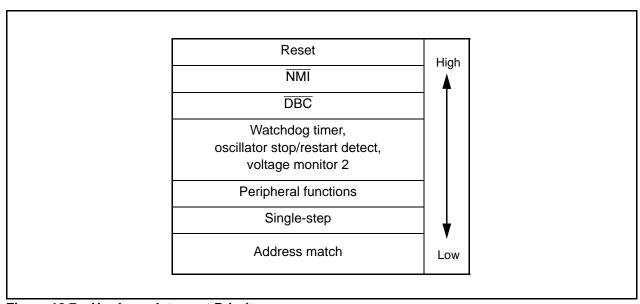

|    | 1251        | Special Interrupte                                                                                                                                                                                                                                                                                                                                                       | 208 |

| 12.5.   | .2 Peripheral Function Interrupts                         | 208 |

|---------|-----------------------------------------------------------|-----|

| 12.6    | Interrupts and Interrupt Vectors                          | 209 |

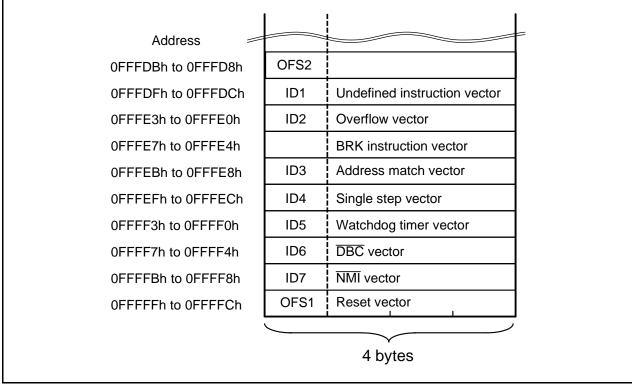

| 12.6.   | .1 Fixed Vector Tables                                    | 209 |

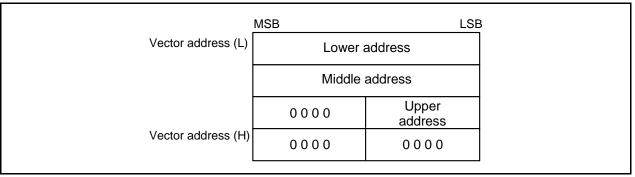

| 12.6.   | .2 Relocatable Vector Tables                              | 210 |

| 12.7    | Interrupt Control                                         | 212 |

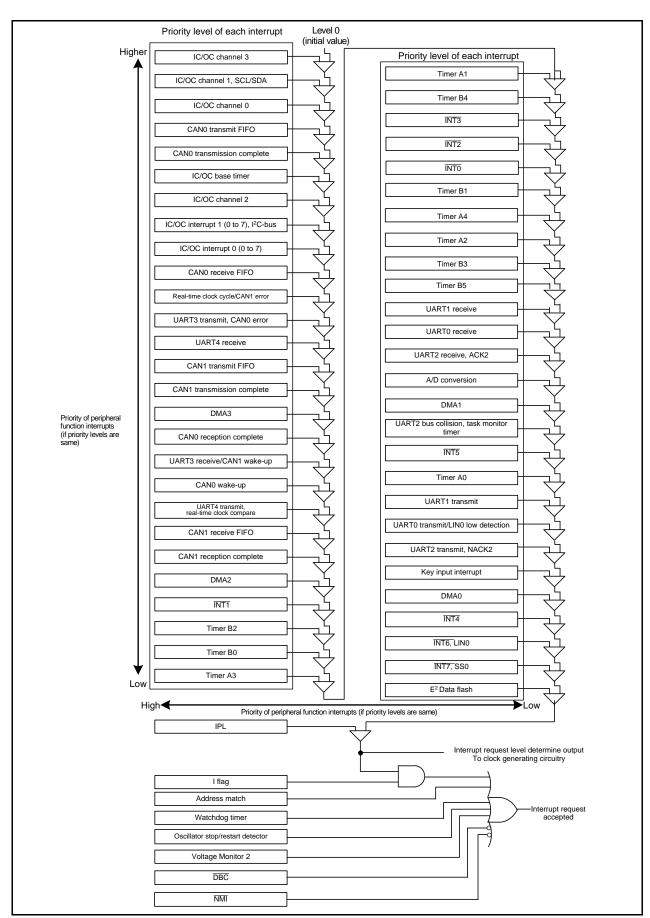

| 12.7.   | .1 Maskable Interrupt Control                             | 212 |

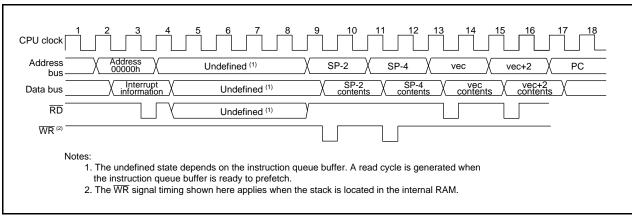

| 12.7.   | .2 Interrupt Sequence                                     | 213 |

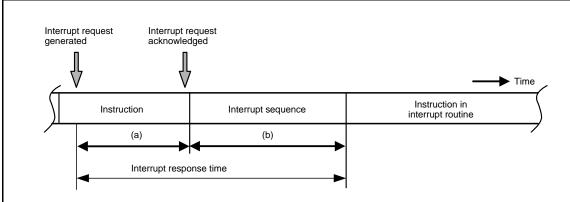

| 12.7.   | .3 Interrupt Response Time                                | 214 |

| 12.7.   | .4 Variation of IPL When Interrupt Request is Accepted    | 214 |

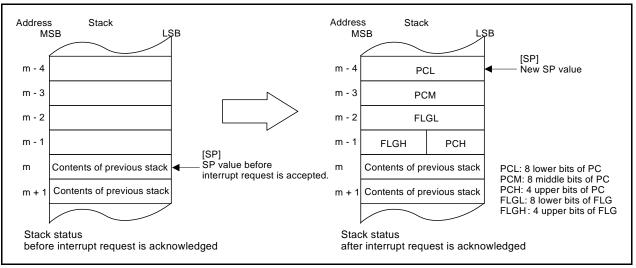

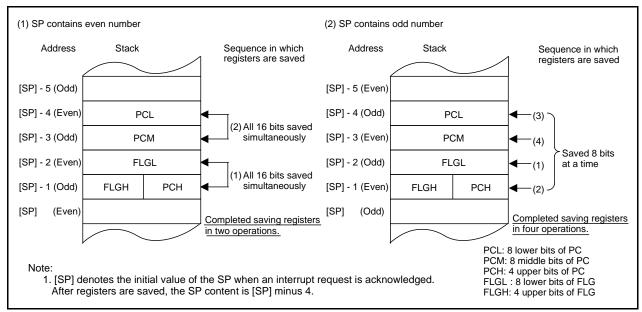

| 12.7.   | .5 Saving Registers                                       | 215 |

| 12.7.   | .6 Returning from an Interrupt Routine                    | 216 |

| 12.7.   | .7 Interrupt Priority                                     | 216 |

| 12.7.   | .8 Interrupt Priority Level Select Circuit                | 216 |

| 12.7.   | .9 Multiple Interrupts                                    | 218 |

| 12.8    | INT Interrupt                                             | 218 |

| 12.9    | NMI Interrupt                                             | 219 |

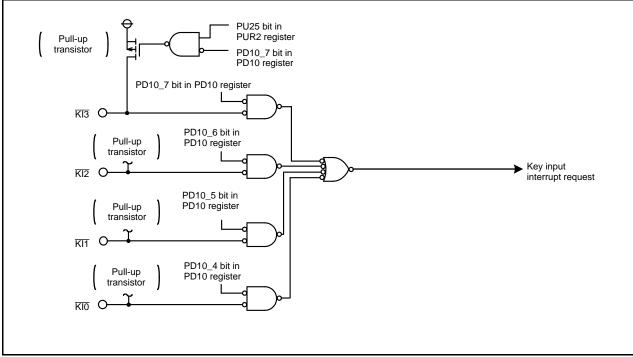

| 12.10   | Key Input Interrupt                                       | 219 |

| 12.11   | Address Match Interrupt                                   | 220 |

| 12.12   | Non-Maskable Interrupt Source Discrimination              | 221 |

| 12.13   | Notes on Interrupts                                       | 222 |

| 12.13   | 3.1 Reading Address 00000h                                | 222 |

| 12.13   | 3.2 SP Setting                                            | 222 |

| 12.13   | 3.3 NMI Interrupt                                         | 222 |

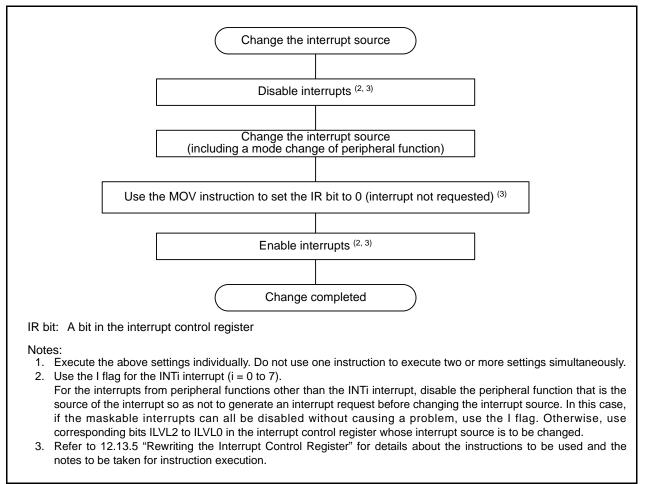

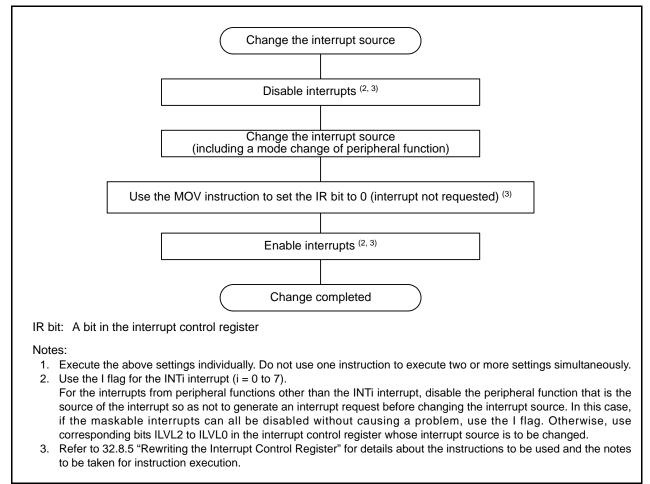

| 12.13   | 3.4 Changing an Interrupt Source                          | 223 |

| 12.13   | 3.5 Rewriting the Interrupt Control Register              | 224 |

| 12.13   | 3.6 Instruction to Rewrite the Interrupt Control Register | 224 |

| 12.13   | 3.7 INT Interrupt                                         | 225 |

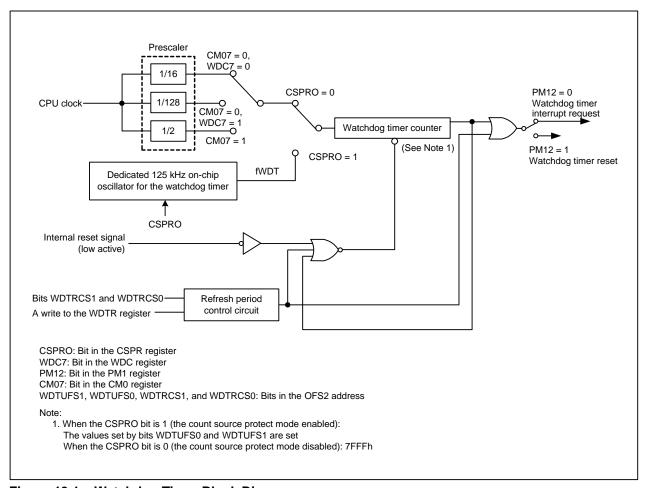

| 13. Wat | chdog Timer                                               | 226 |

| 13.1    | Introduction                                              | 226 |

| 13.2    | Registers                                                 | 228 |

| 13.2.   | .1 Voltage Monitor 2 Control Register (VW2C)              | 229 |

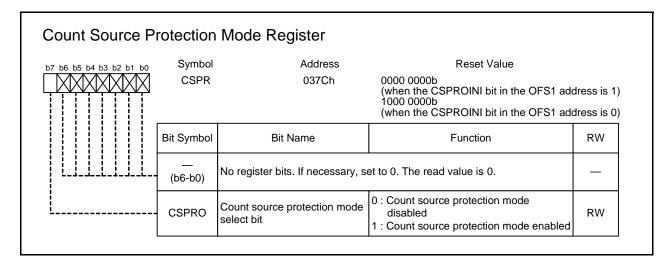

| 13.2.   | .2 Count Source Protection Mode Register (CSPR)           | 230 |

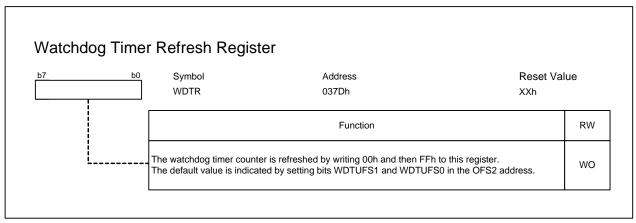

| 13.2.   | .3 Watchdog Timer Refresh Register (WDTR)                 | 230 |

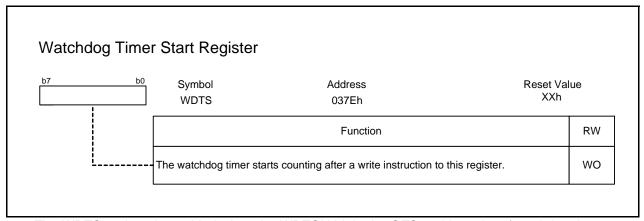

| 13.2.   | .4 Watchdog Timer Start Register (WDTS)                   | 231 |

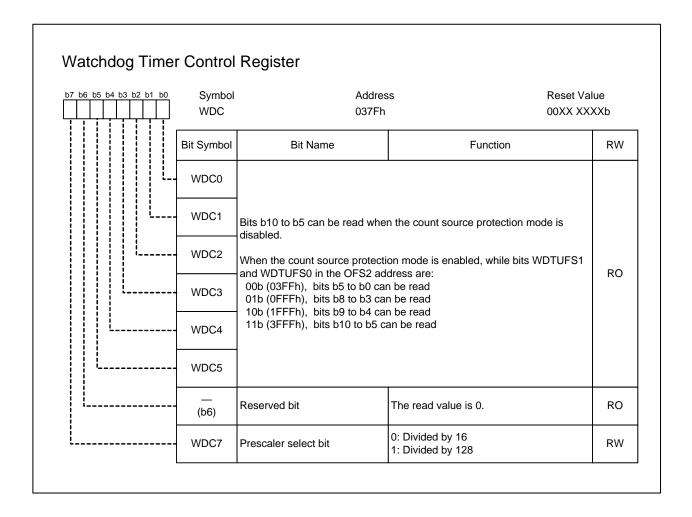

| 13.2.   | .5 Watchdog Timer Control Register (WDC)                  | 231 |

| 13.3    | Optional Function Select Area                             | 232 |

| 13.3.   | .1 Optional Function Select Address 1 (OFS1)              | 232 |

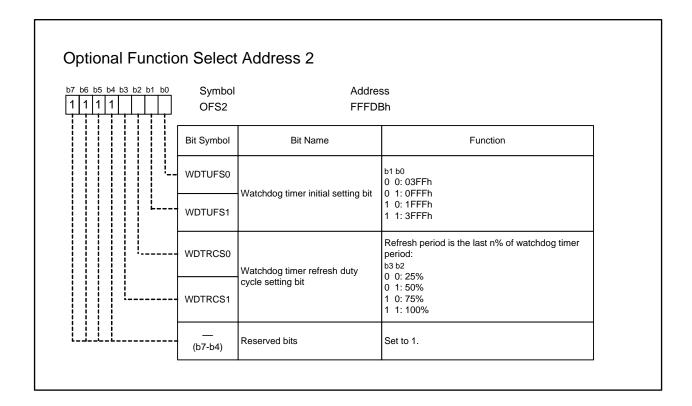

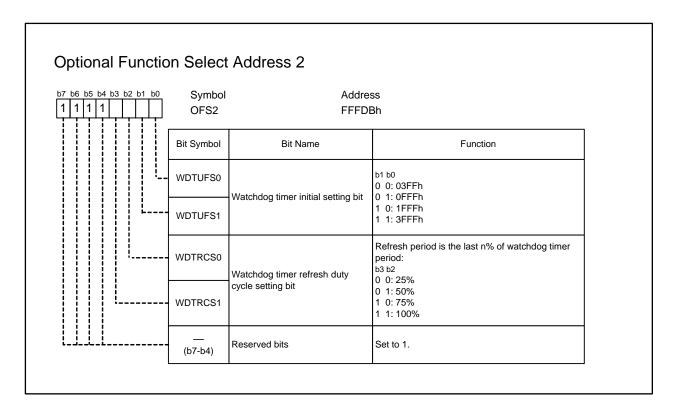

| 13.3.   | .2 Optional Function Select Address 2 (OFS2)              | 233 |

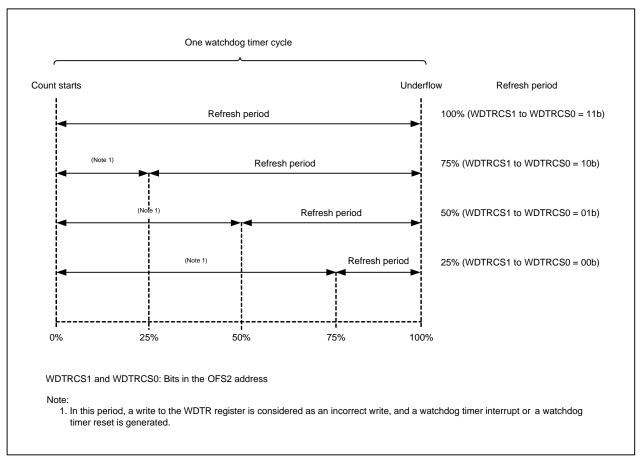

| 13.4    | Operations                                                | 234 |

| 13.4.   | .1 Refresh Operation Period                               | 234 |

| 1     | 3.4.2  | Count Source Protection Mode Disabled                               | 235 |

|-------|--------|---------------------------------------------------------------------|-----|

| 1     | 3.4.3  | Count Source Protection Mode Enabled                                | 236 |

| 13.5  | Inte   | errupts                                                             | 237 |

| 13.6  | Not    | es on the Watchdog Timer                                            | 238 |

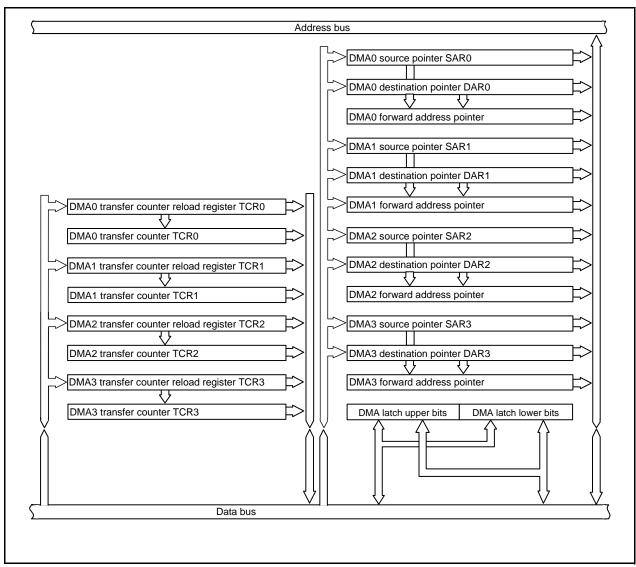

| 14. D | MAC    |                                                                     | 239 |

| 14.1  | Intr   | oduction                                                            | 239 |

| 14.2  | Re     | gisters                                                             | 241 |

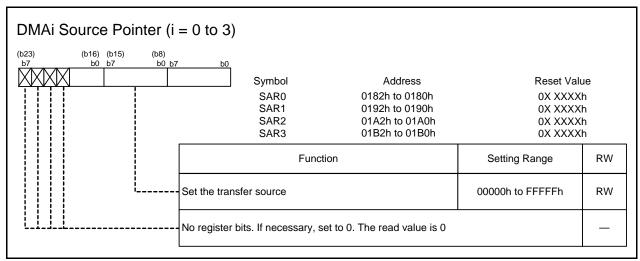

| 1     | 4.2.1  | DMAi Source Pointer (SARi) (i = 0 to 3)                             | 242 |

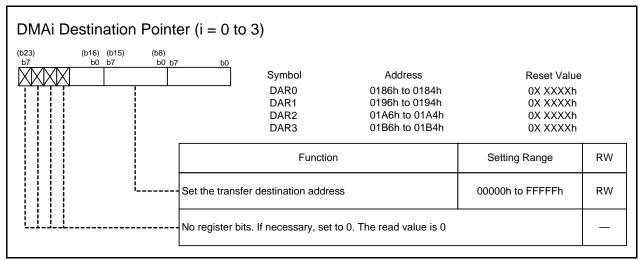

| 1     | 4.2.2  | DMAi Destination Pointer (DARi) (i = 0 to 3)                        | 242 |

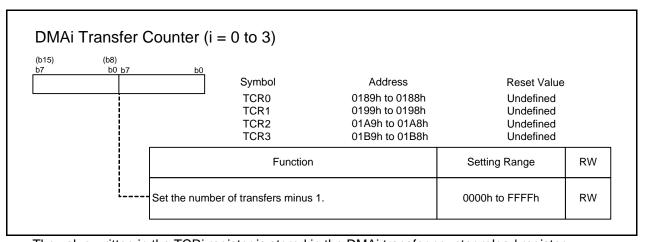

| 1     | 4.2.3  | DMAi Transfer Counter (TCRi) (i = 0 to 3)                           | 243 |

| 1     | 4.2.4  | DMAi Control Register (DMiCON) (i = 0 to 3)                         | 244 |

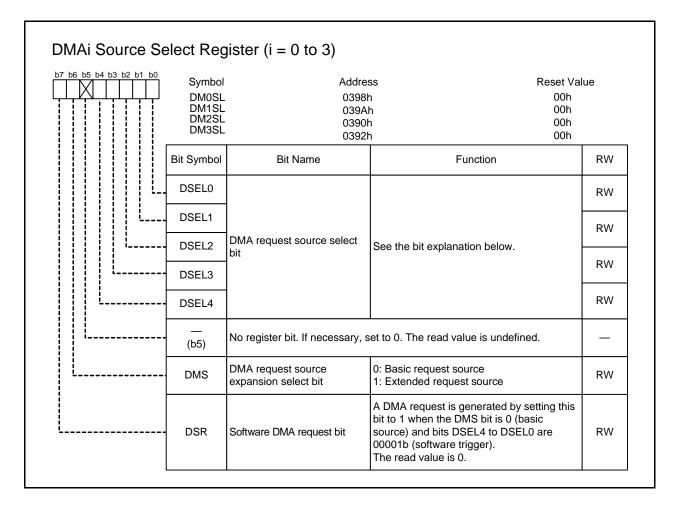

| 1     | 4.2.5  | DMAi Source Select Register (DMiSL) (i = 0 to 3)                    | 245 |

| 14.3  | Оре    | erations                                                            | 248 |

| 1     | 4.3.1  | DMA Enabled                                                         | 248 |

| 1     | 4.3.2  | DMA Request                                                         | 248 |

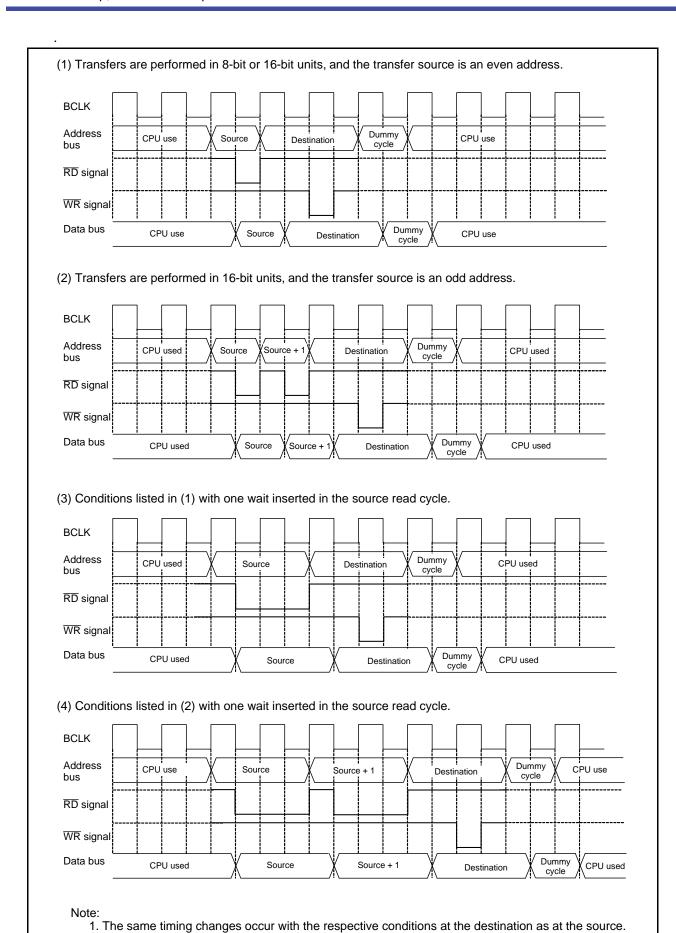

| 1     | 4.3.3  | Transfer Cycles                                                     | 249 |

| 1     | 4.3.4  | DMAC Transfer Cycles                                                | 251 |

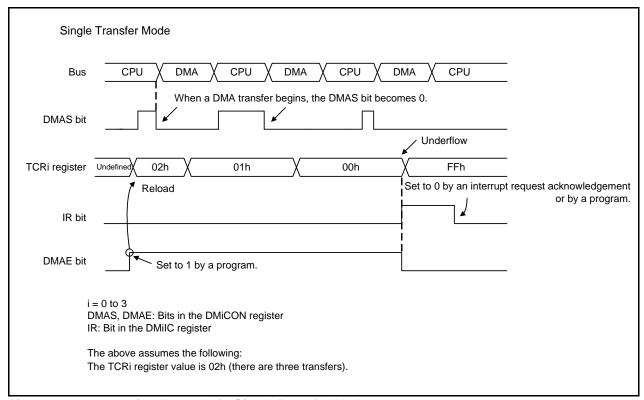

| 1     | 4.3.5  | Single Transfer Mode                                                | 252 |

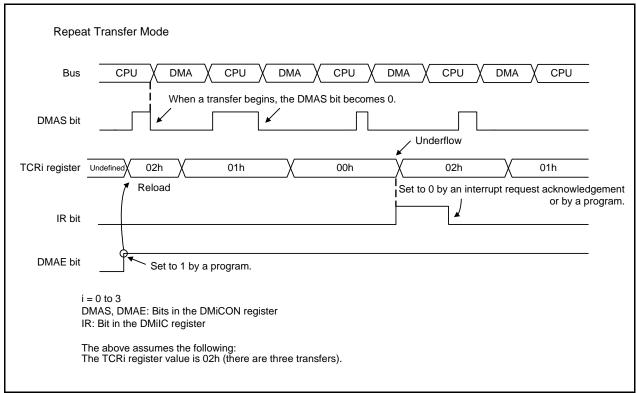

| 1     | 4.3.6  | Repeat Transfer Mode                                                | 253 |

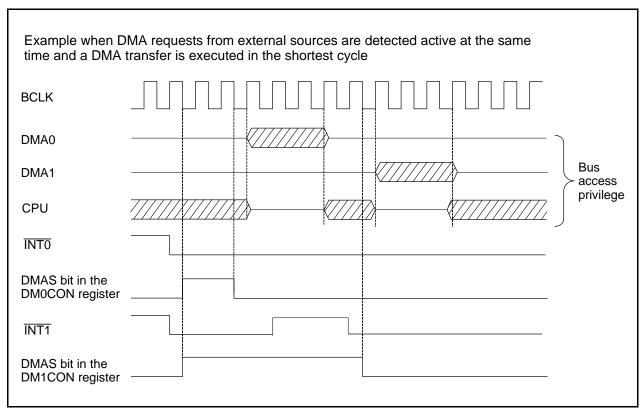

| 1     | 4.3.7  | Channel Priority and DMA Transfer Timing                            | 254 |

| 14.4  | Inte   | errupts                                                             | 255 |

| 14.5  | Not    | es on DMAC                                                          | 256 |

| 1     | 4.5.1  | Write to the DMAE Bit in the DMiCON Register (i = 0 to 3)           | 256 |

| 1     | 4.5.2  | Changing the DMA Request Source                                     | 256 |

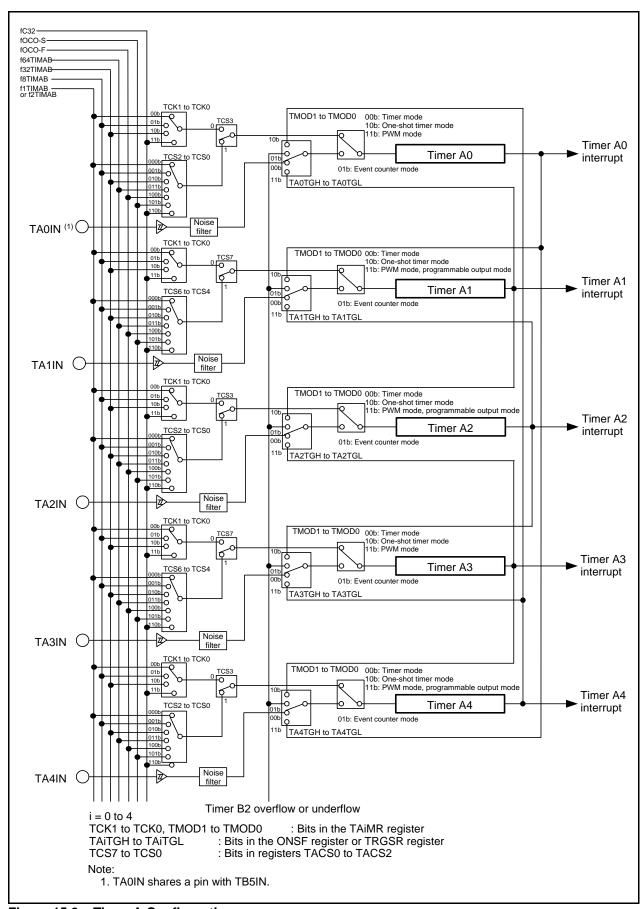

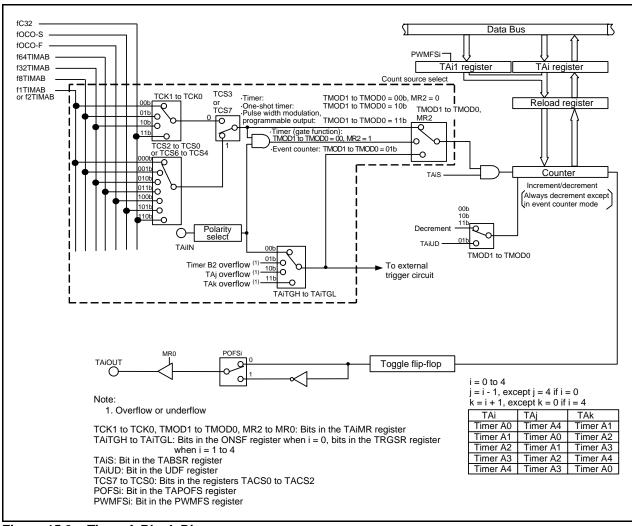

| 15. T | imer A | ١                                                                   | 257 |

| 15.1  | Intr   | oduction                                                            | 257 |

| 15.2  | Reg    | gisters                                                             | 260 |

| 1     | 5.2.1  | Peripheral Clock Select Register (PCLKR)                            | 261 |

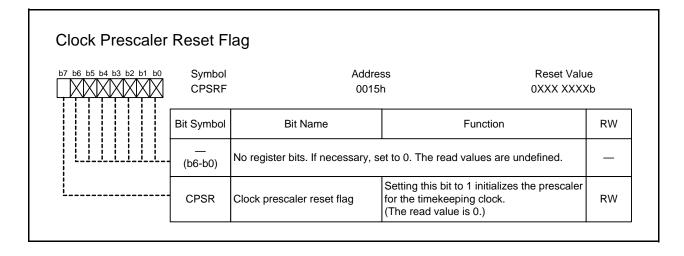

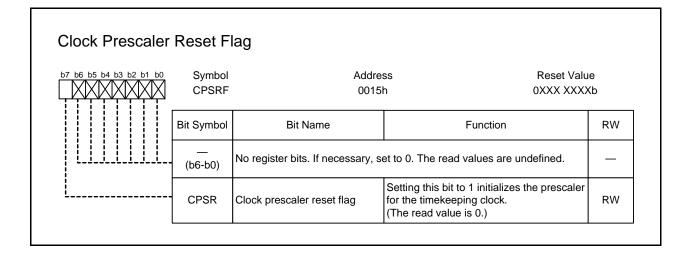

| 1     | 5.2.2  | Clock Prescaler Reset Flag (CPSRF)                                  | 261 |

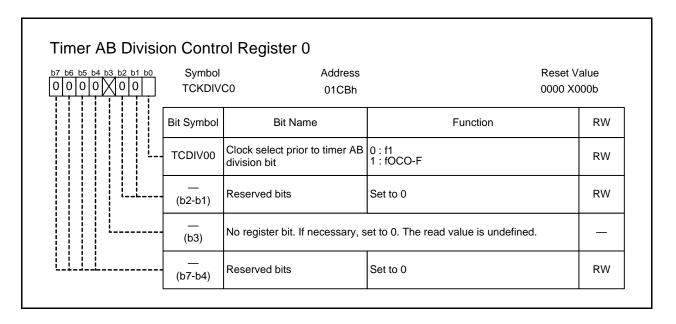

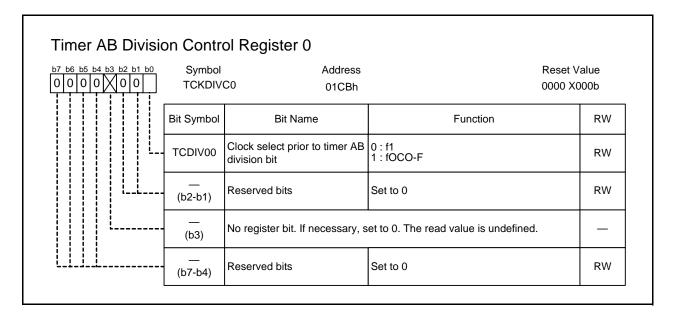

| 1     | 5.2.3  | Timer AB Division Control Register 0 (TCKDIVC0)                     | 262 |

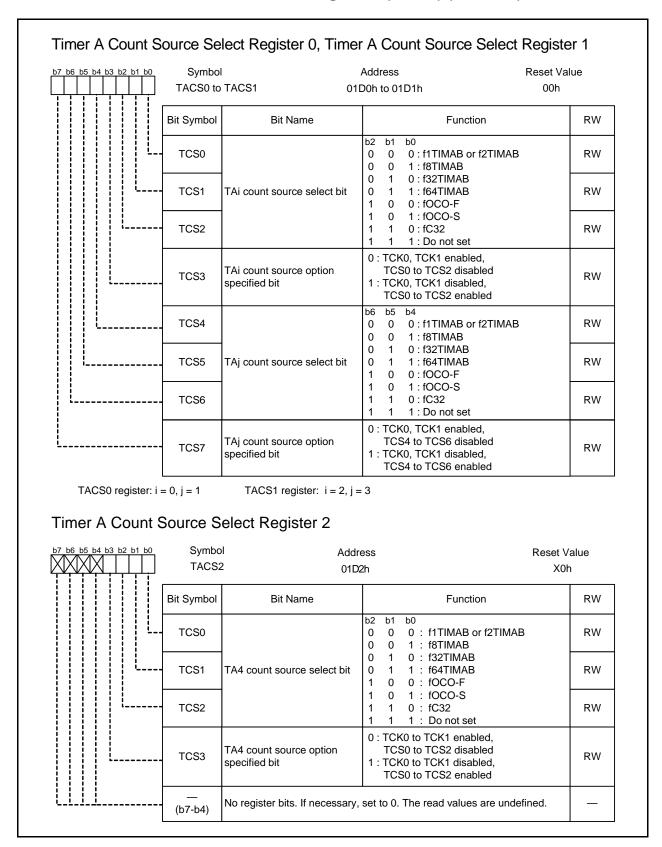

| 1     | 5.2.4  | Timer A Count Source Select Register i (TACSi) (i = 0 to 2)         | 263 |

| 1     | 5.2.5  | 16-bit Pulse Width Modulation Mode Function Select Register (PWMFS) | 264 |

| 1     | 5.2.6  | Timer A Waveform Output Function Select Register (TAPOFS)           | 265 |

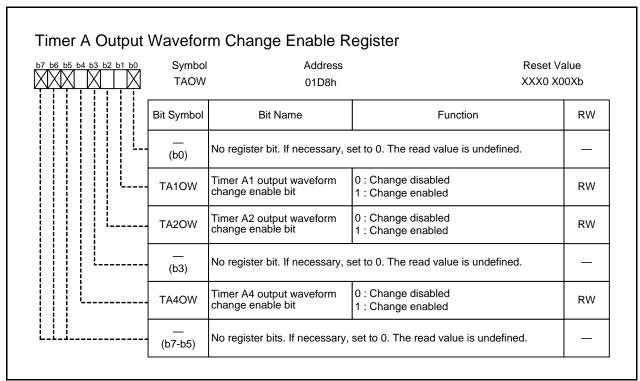

| 1     | 5.2.7  | Timer A Output Waveform Change Enable Register (TAOW)               | 266 |

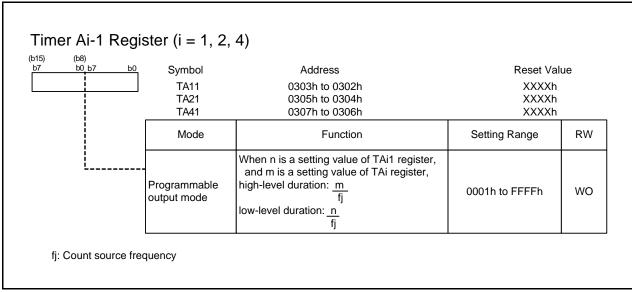

| 1     | 5.2.8  | Timer Ai Register (TAi) (i = 0 to 4)                                | 267 |

| 1     | 5.2.9  | Timer Ai-1 Register (TAi1) (i = 1, 2, 4)                            | 268 |

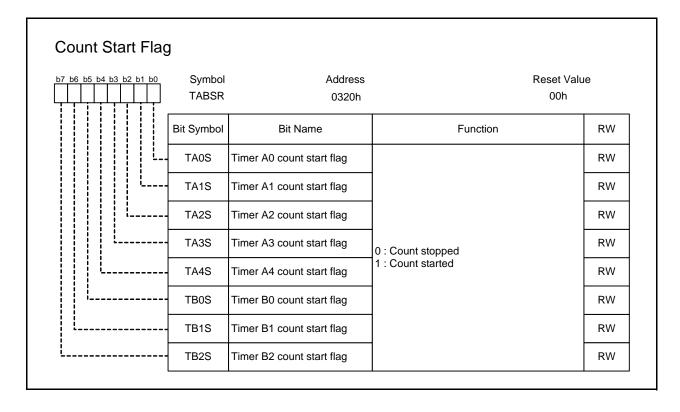

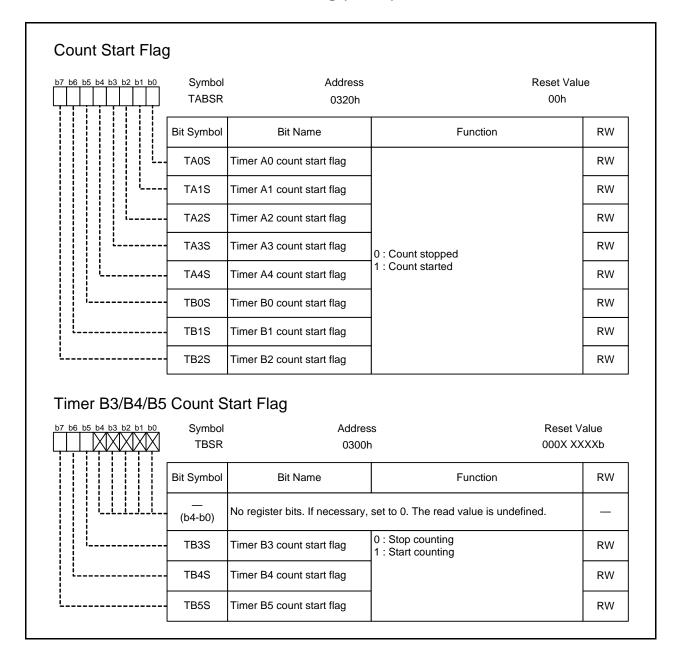

| 1     | 5.2.10 | Count Start Flag (TABSR)                                            | 268 |

| 1     | 5.2.11 | One-Shot Start Flag (ONSF)                                          | 269 |

| 1     | 5 2 12 | Trigger Select Register (TRGSR)                                     | 270 |

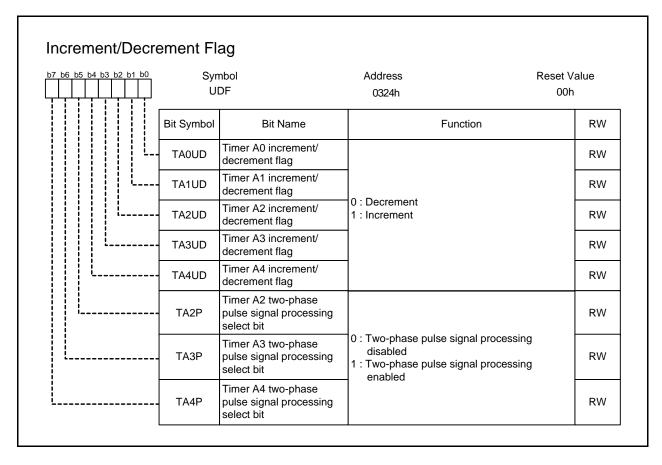

| 15.2.    | 13 Increment/Decrement Flag (UDF)                                                        | 271 |

|----------|------------------------------------------------------------------------------------------|-----|

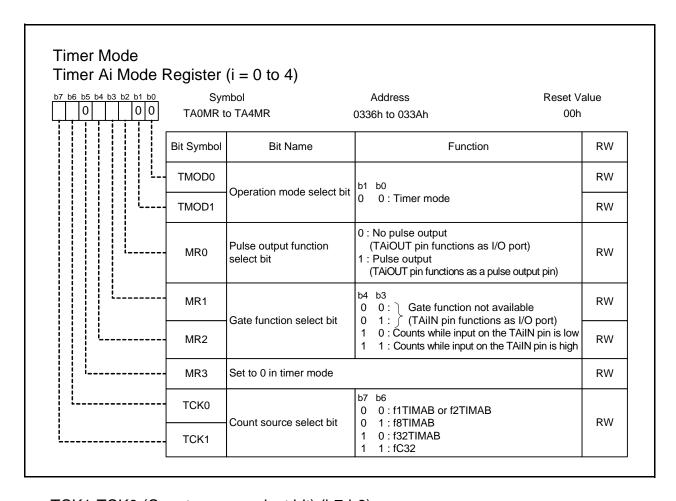

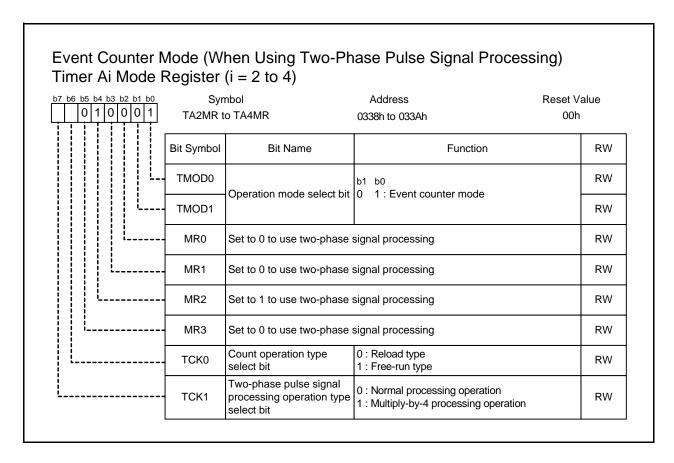

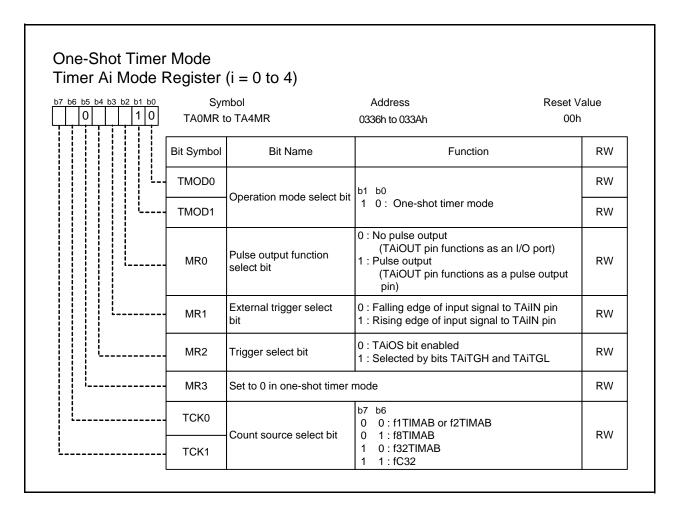

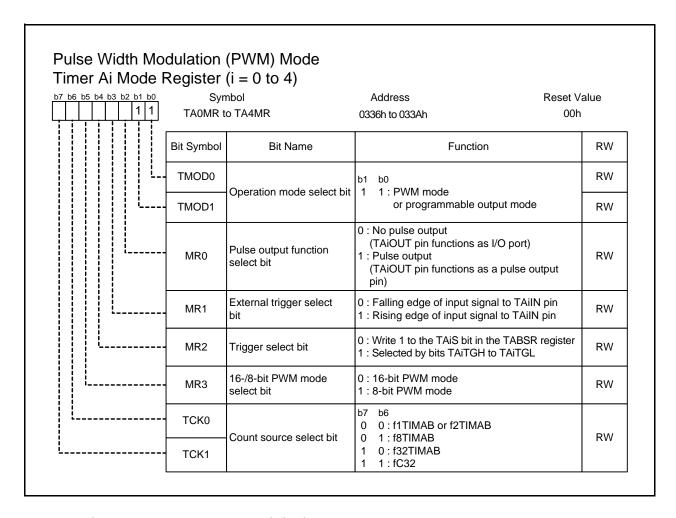

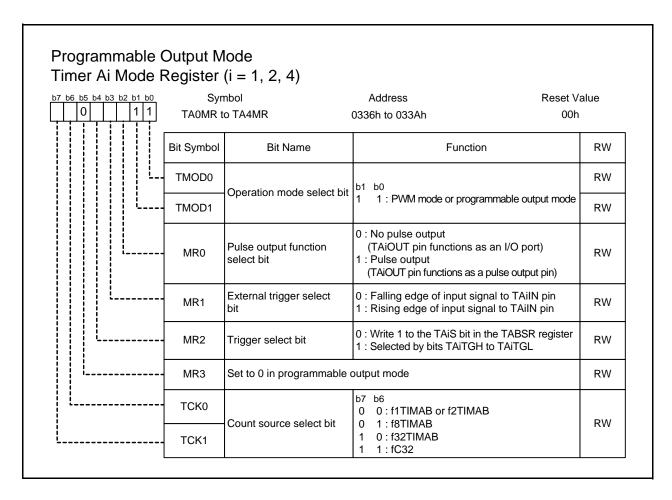

| 15.2.    | 14 Timer Ai Mode Register (TAiMR) (i = 0 to 4)                                           | 272 |

| 15.3     | Operations                                                                               | 273 |

| 15.3.    | 1 Common Operations                                                                      | 273 |

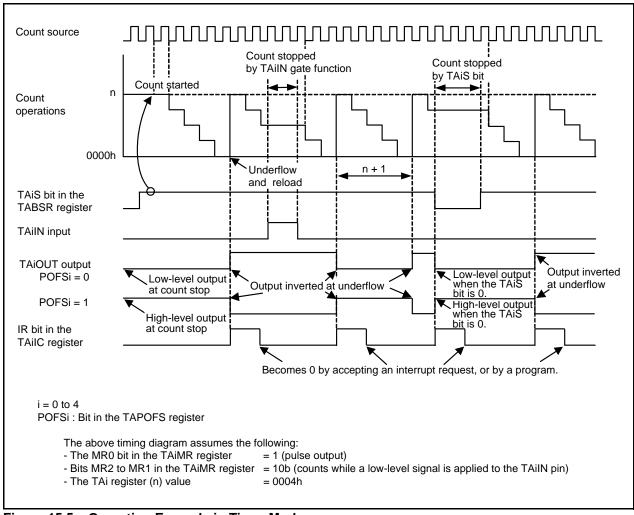

| 15.3.    | 2 Timer Mode                                                                             | 275 |

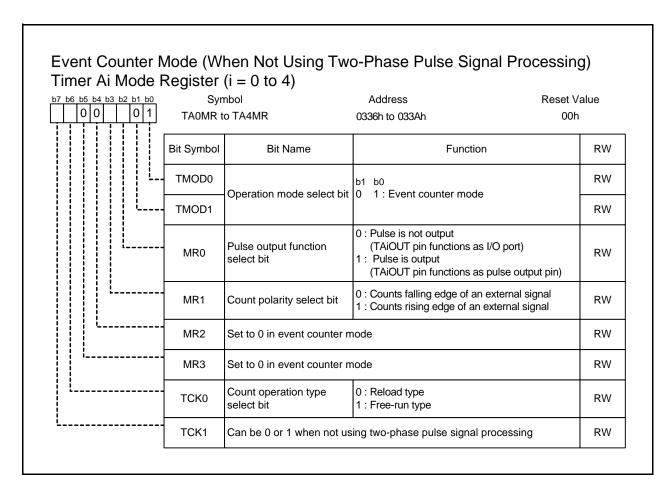

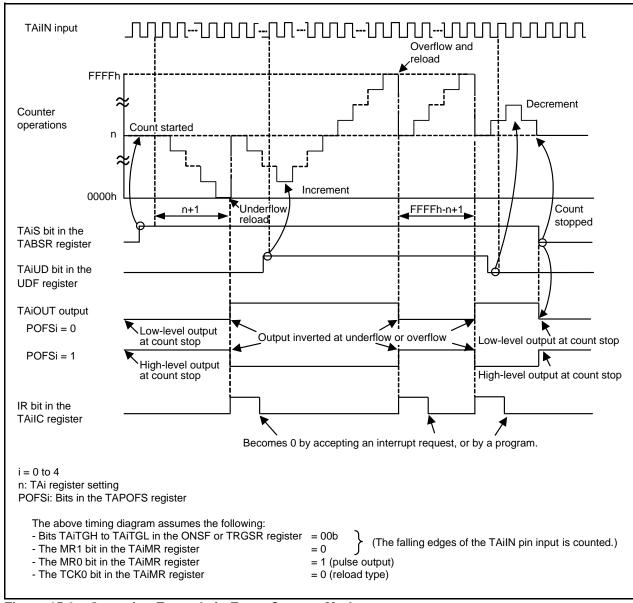

| 15.3.    | 3 Event Counter Mode (When Not Using Two-Phase Pulse Signal Processing)                  | 279 |

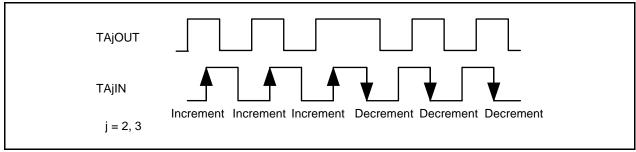

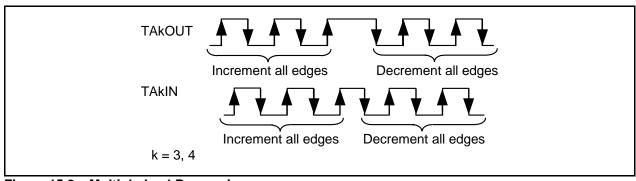

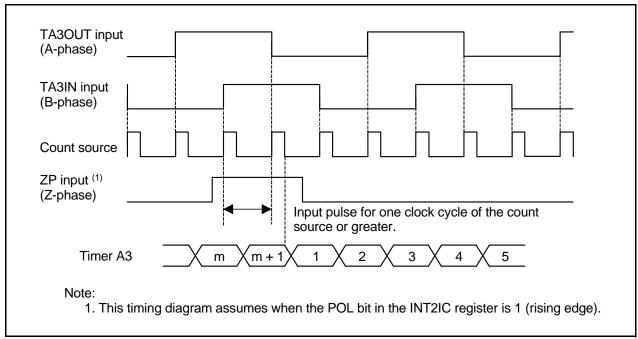

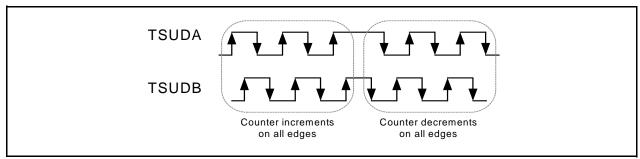

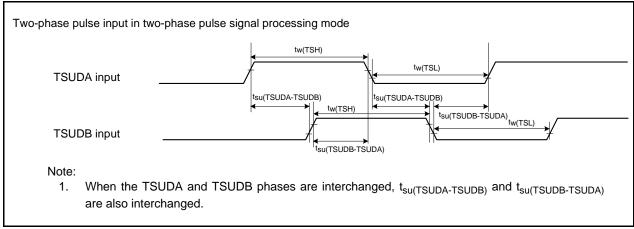

| 15.3.    | Event Counter Mode (When Processing Two-Phase Pulse Signal)                              | 283 |

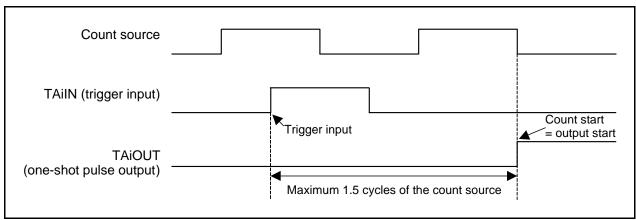

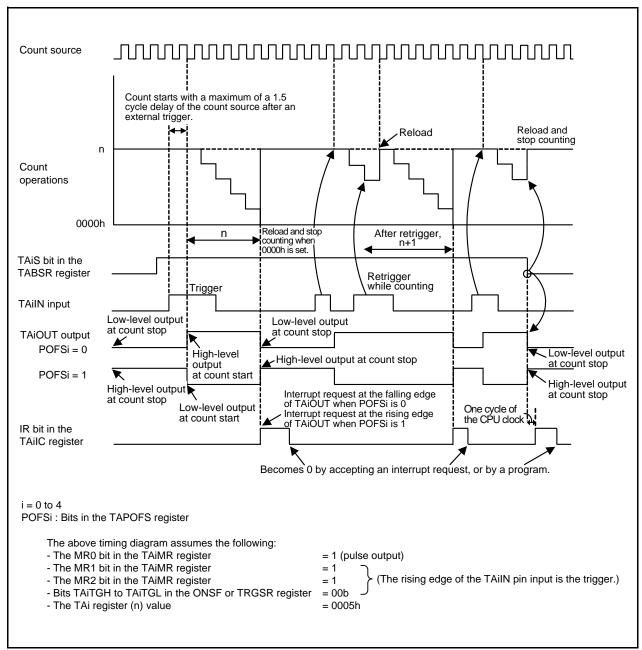

| 15.3.    | 5 One-Shot Timer Mode                                                                    | 288 |

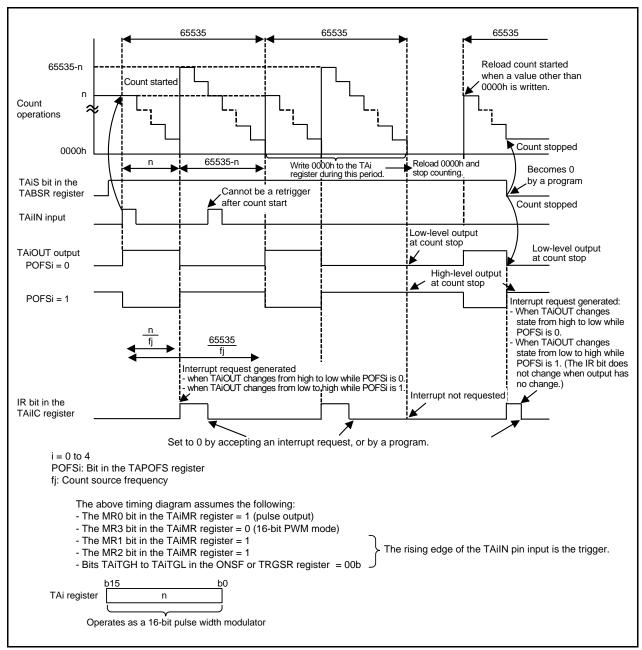

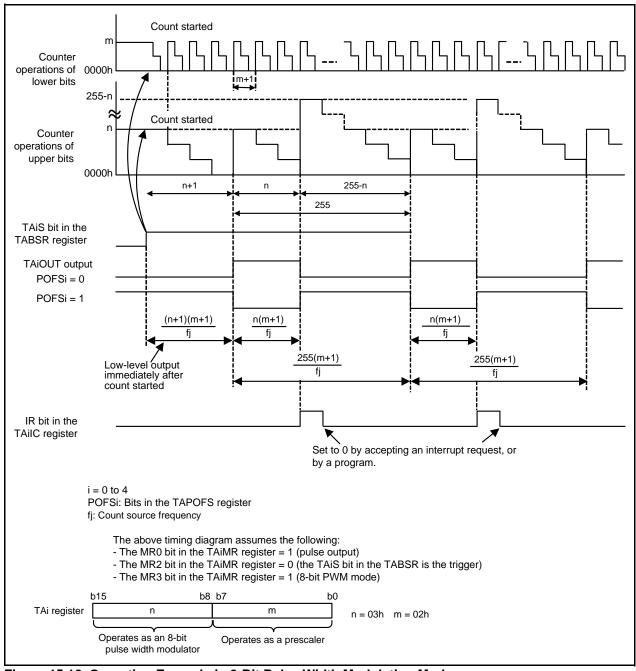

| 15.3.    | Pulse Width Modulation (PWM) Mode                                                        | 292 |

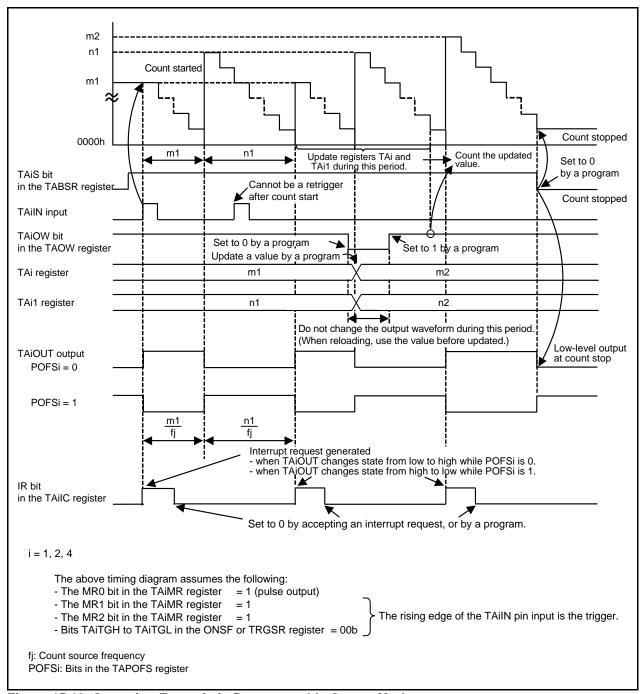

| 15.3.    | Programmable Output Mode (Timers A1, A2, and A4)                                         | 297 |

| 15.4     | Interrupts                                                                               | 301 |

| 15.5     | Notes on Timer A                                                                         | 302 |

| 15.5.    | 1 Common Notes on Multiple Modes                                                         | 302 |

| 15.5.    | 2 Timer A (Timer Mode)                                                                   | 303 |

| 15.5.    | 3 Timer A (Event Counter Mode)                                                           | 303 |

| 15.5.    | 4 Timer A (One-Shot Timer Mode)                                                          | 303 |

| 15.5.    | Timer A (Pulse Width Modulation Mode)                                                    | 304 |

| 15.5.    | Timer A (Programmable Output Mode)                                                       | 305 |

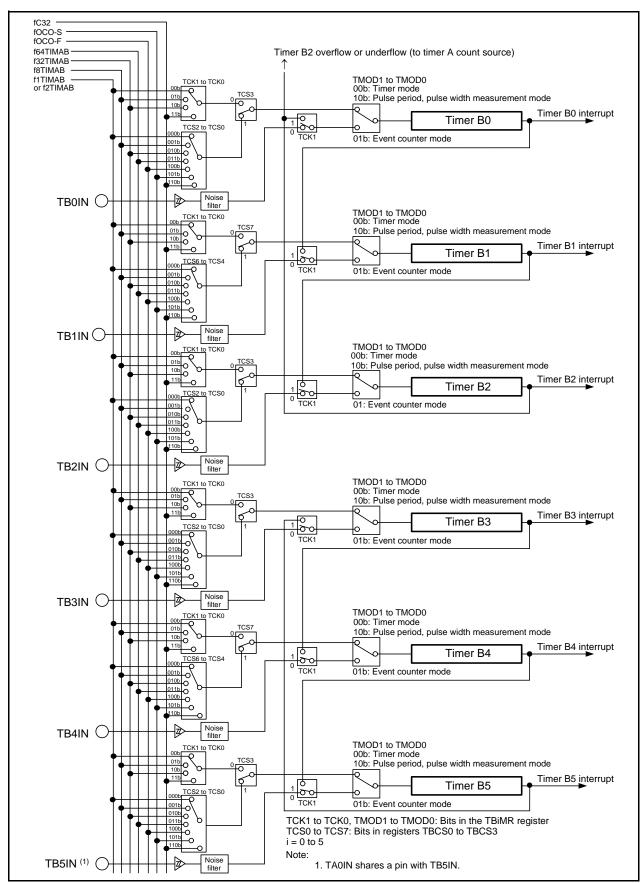

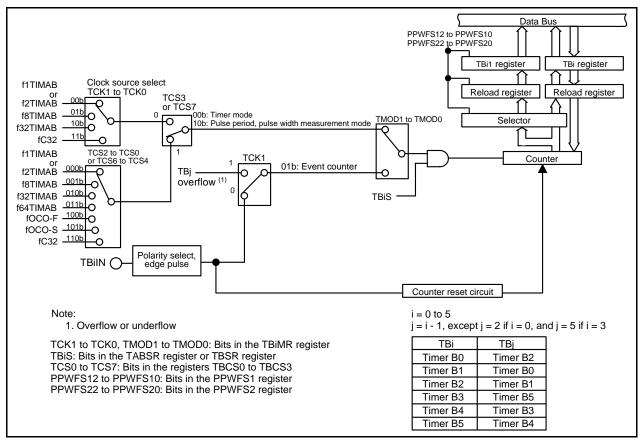

| 16. Time | er B                                                                                     | 306 |

| 16.1     | Introduction                                                                             | 306 |

| 16.2     | Registers                                                                                | 309 |

| 16.2.    |                                                                                          |     |

| 16.2.    |                                                                                          |     |

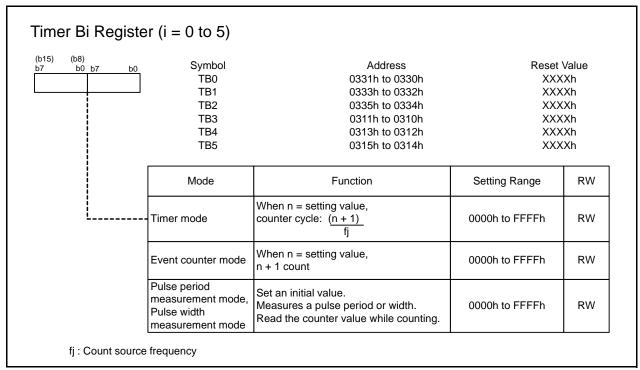

| 16.2.    | 3 Timer Bi Register (TBi) (i = 0 to 5)                                                   | 311 |

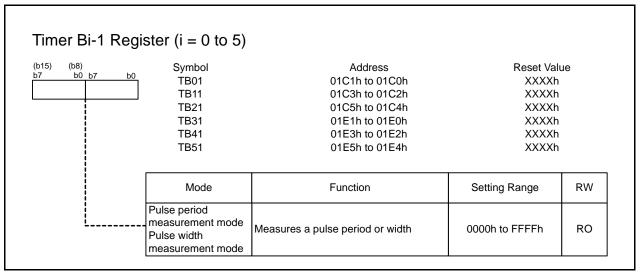

| 16.2.    | 4 Timer Bi-1 Register (TBi1) (i = 0 to 5)                                                | 312 |

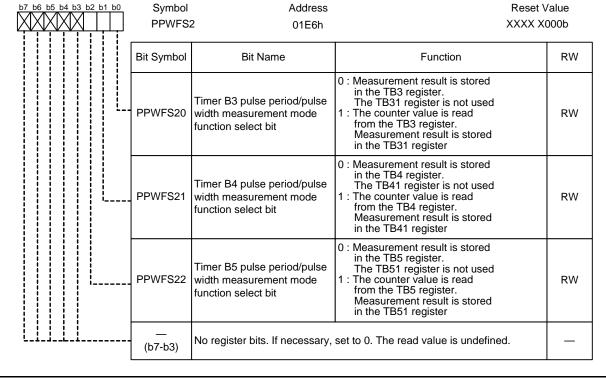

| 16.2.    | Pulse Period/Pulse Width Measurement Mode Function Select Register i (PPWFSi) (i = 1, 2) | 313 |

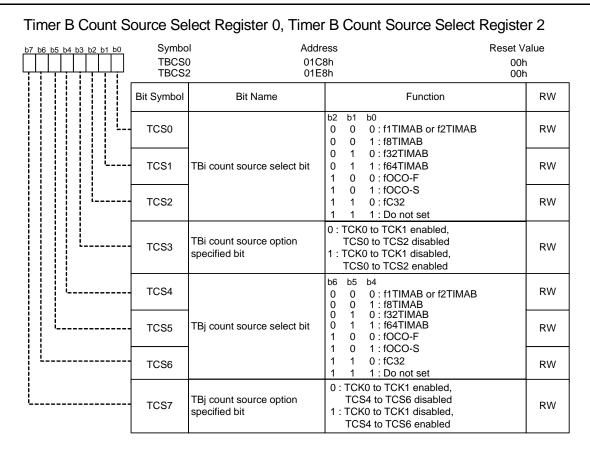

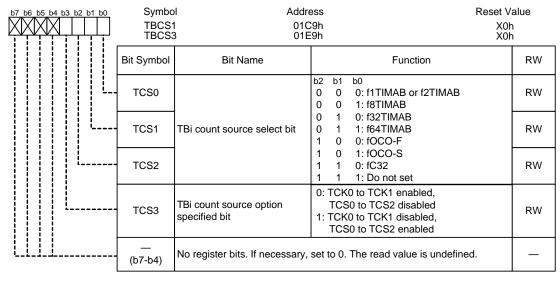

| 16.2.    | 6 Timer B Count Source Select Register i (TBCSi) (i = 0 to 3)                            | 314 |

| 16.2.    | 7 Timer AB Division Control Register 0 (TCKDIVC0)                                        | 315 |

| 16.2.    | 8 Count Start Flag (TABSR) Timer B3/B4/B5 Count Start Flag (TBSR)                        | 316 |

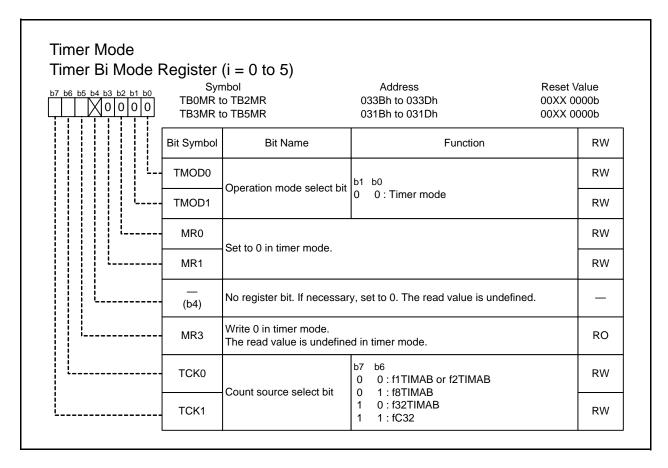

| 16.2.    | 9 Timer Bi Mode Register (TBiMR) (i = 0 to 5)                                            | 317 |

| 16.3     | Operations                                                                               | 318 |

| 16.3.    | 1 Common Operations                                                                      | 318 |

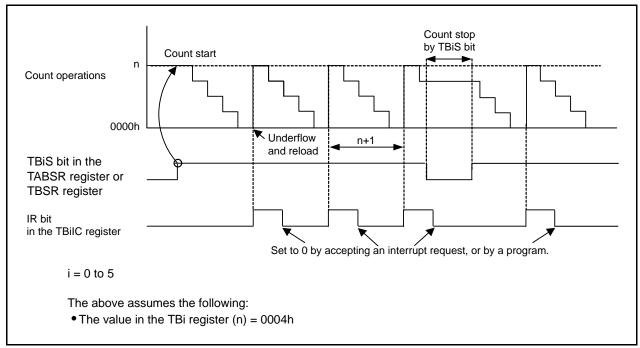

| 16.3.    | 2 Timer Mode                                                                             | 320 |

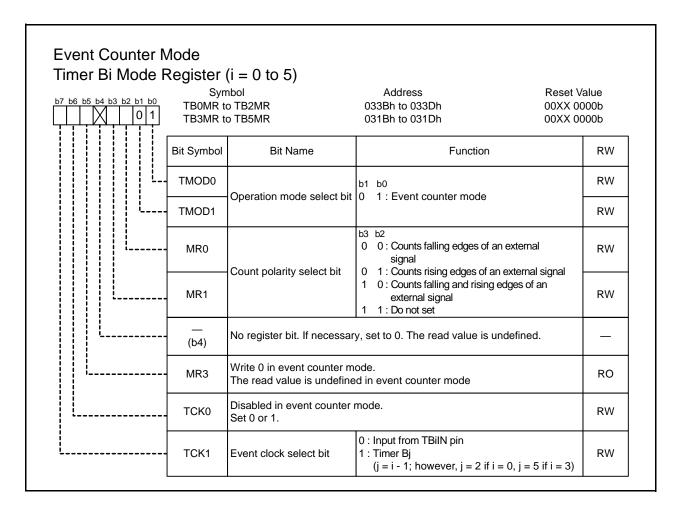

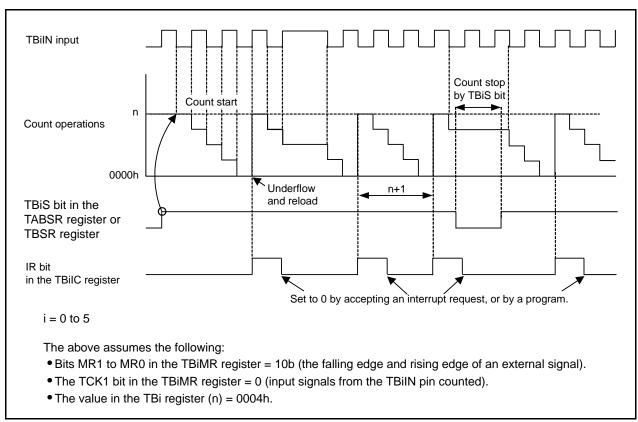

| 16.3.    | 3 Event Counter Mode                                                                     | 322 |

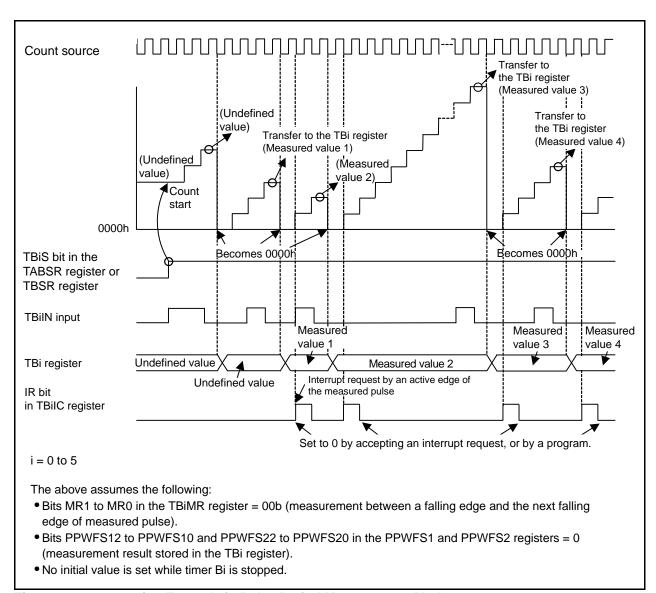

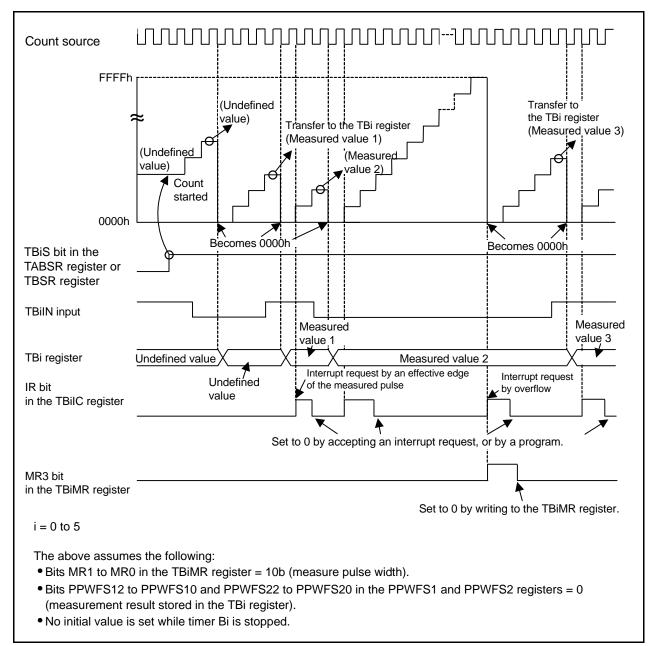

| 16.3.    | 4 Pulse Period/Pulse Width Measurement Modes                                             | 325 |

| 16.4     | Interrupts                                                                               | 330 |

| 16.5     | Notes on Timer B                                                                         | 331 |

| 16.5.    | 1 Common Notes on Multiple Modes                                                         | 331 |

| 16.5.    | 7 Timer B (Timer Mode)                                                                   | 331 |

| 16.5.3      | Timer B (Event Counter Mode)                                  | 331 |

|-------------|---------------------------------------------------------------|-----|

| 16.5.4      | Timer B (Pulse Period/Pulse Width Measurement Modes)          | 332 |

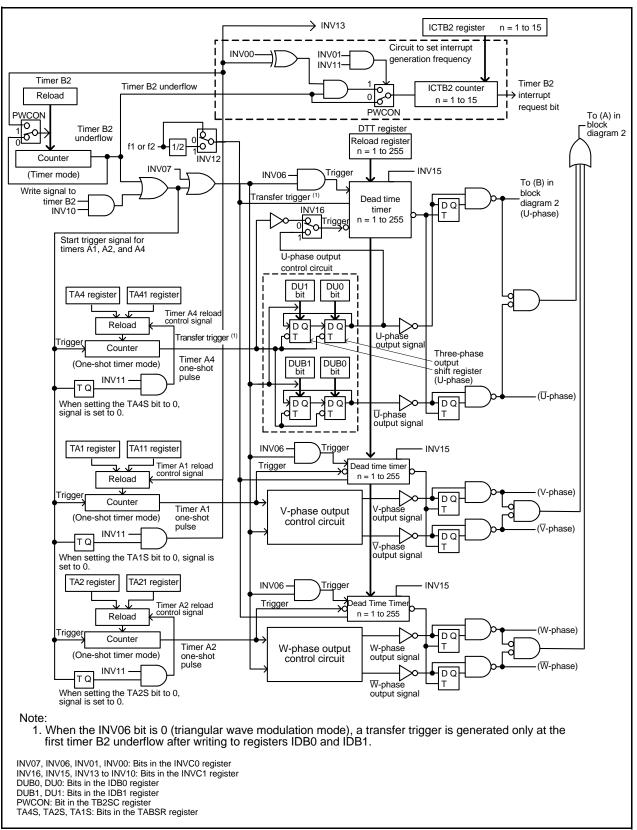

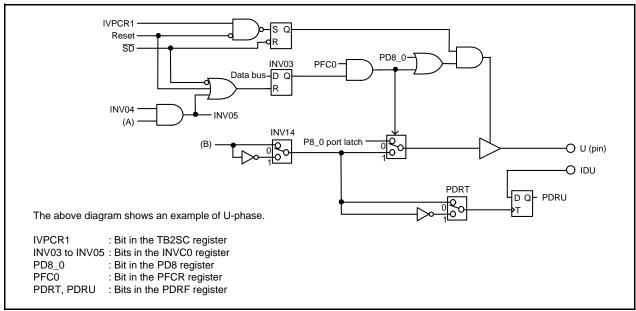

| 17. Three-F | Phase Motor Control Timer Function                            | 333 |

| 17.1 Intro  | oduction                                                      | 333 |

| 17.2 Reg    | jisters                                                       | 337 |

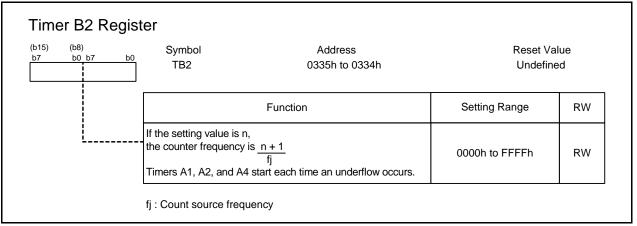

| 17.2.1      | Timer B2 Register (TB2)                                       | 338 |

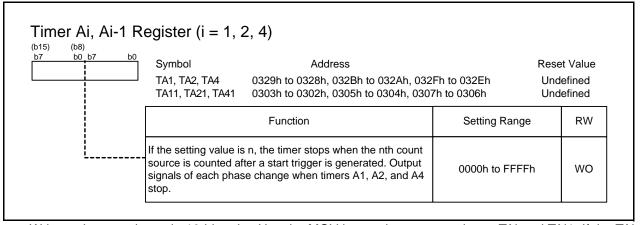

| 17.2.2      | Timer Ai, Ai-1 Register (TAi, TAi1) (i = 1, 2, 4)             | 338 |

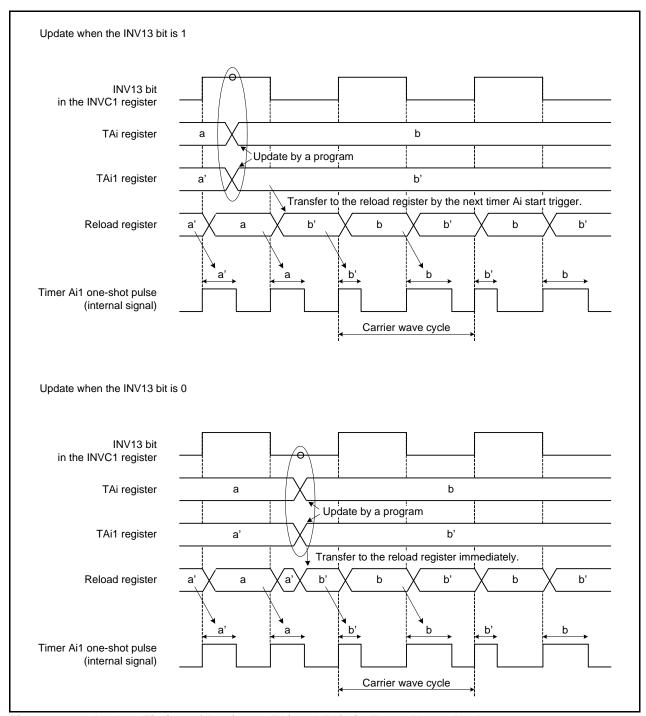

| 17.2.3      | Three-Phase PWM Control Register 0 (INVC0)                    | 339 |

| 17.2.4      | Three-Phase PWM Control Register 1 (INVC1)                    | 341 |

| 17.2.5      | Three-Phase Output Buffer Register i (IDBi) (i = 0, 1)        | 343 |

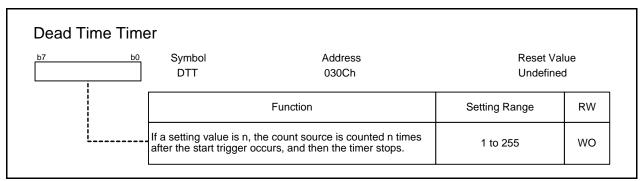

| 17.2.6      | Dead Time Timer (DTT)                                         | 343 |

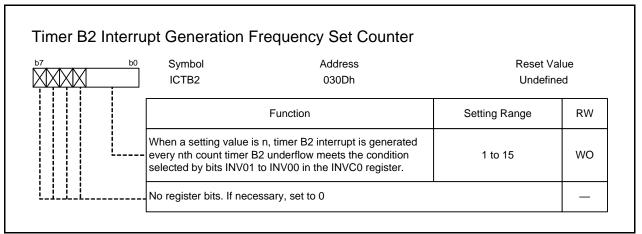

| 17.2.7      | Timer B2 Interrupt Generation Frequency Set Counter (ICTB2)   | 344 |

| 17.2.8      | Timer B2 Special Mode Register (TB2SC)                        | 345 |

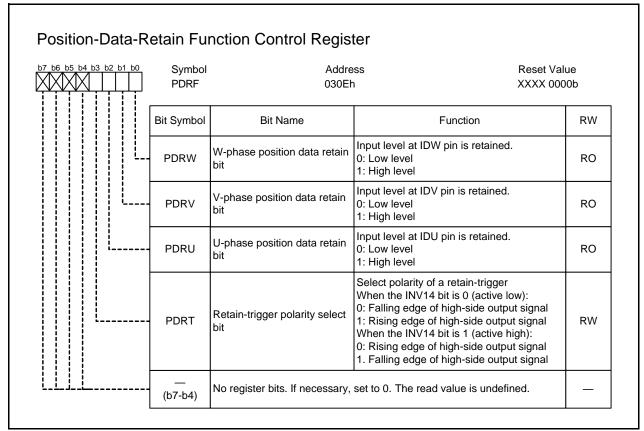

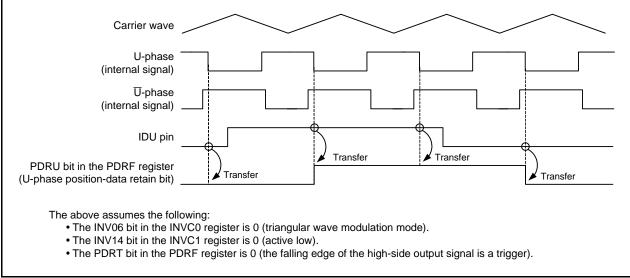

| 17.2.9      | Position-Data-Retain Function Control Register (PDRF)         | 346 |

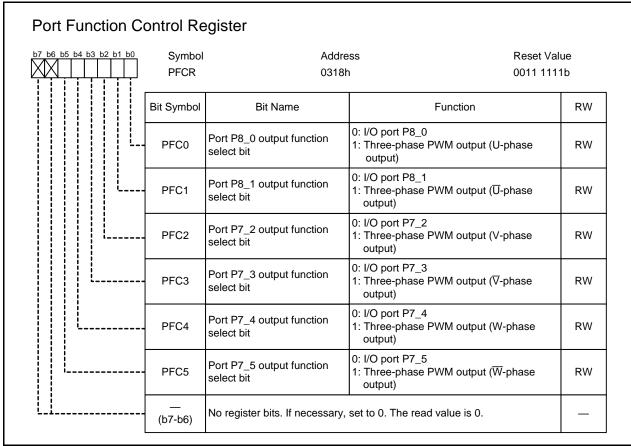

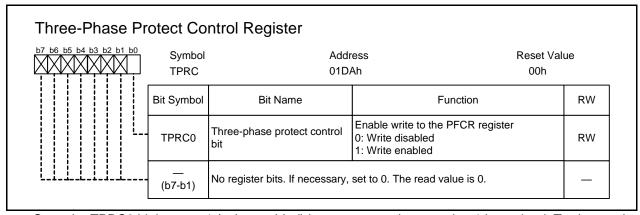

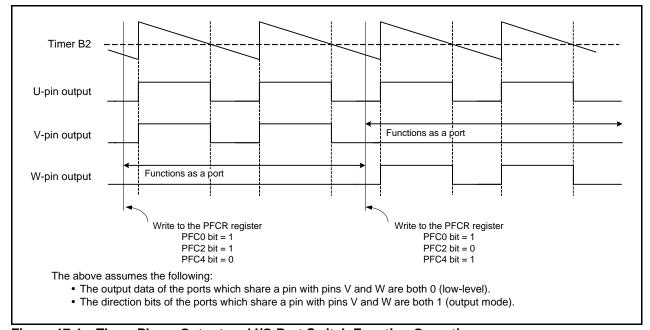

| 17.2.10     | Port Function Control Register (PFCR)                         | 347 |

| 17.2.11     | Three-Phase Protect Control Register (TPRC)                   | 347 |

| 17.3 Ope    | erations                                                      | 348 |

| 17.3.1      | Common Operations in Multiple Modes                           | 348 |

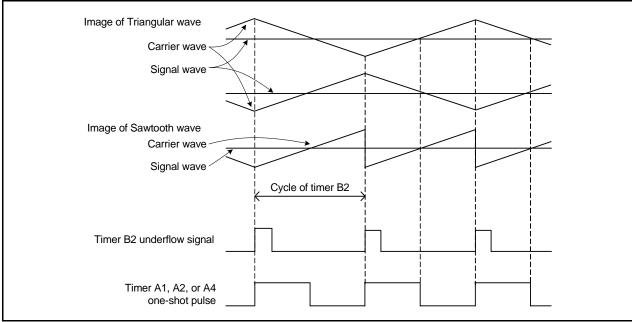

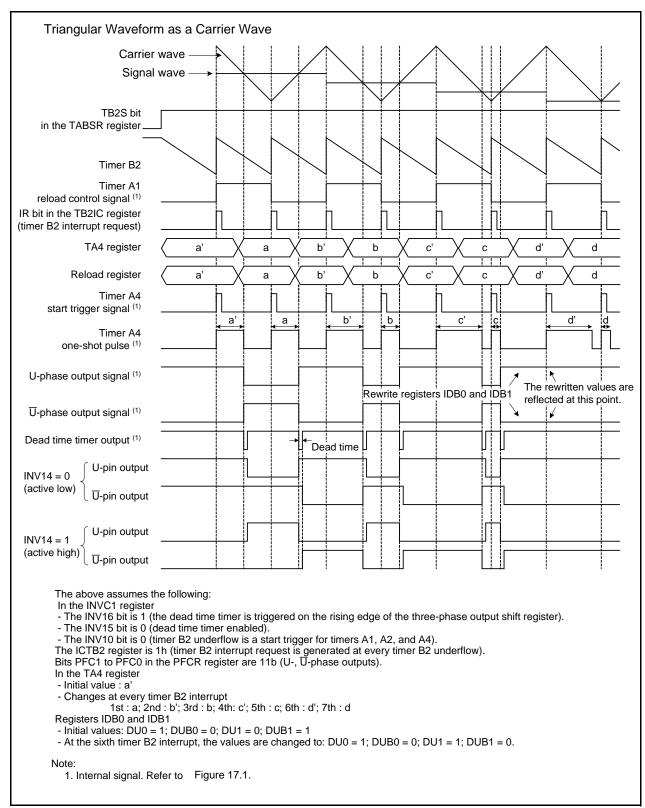

| 17.3.2      | Triangular Wave Modulation Three-Phase Mode 0                 | 354 |

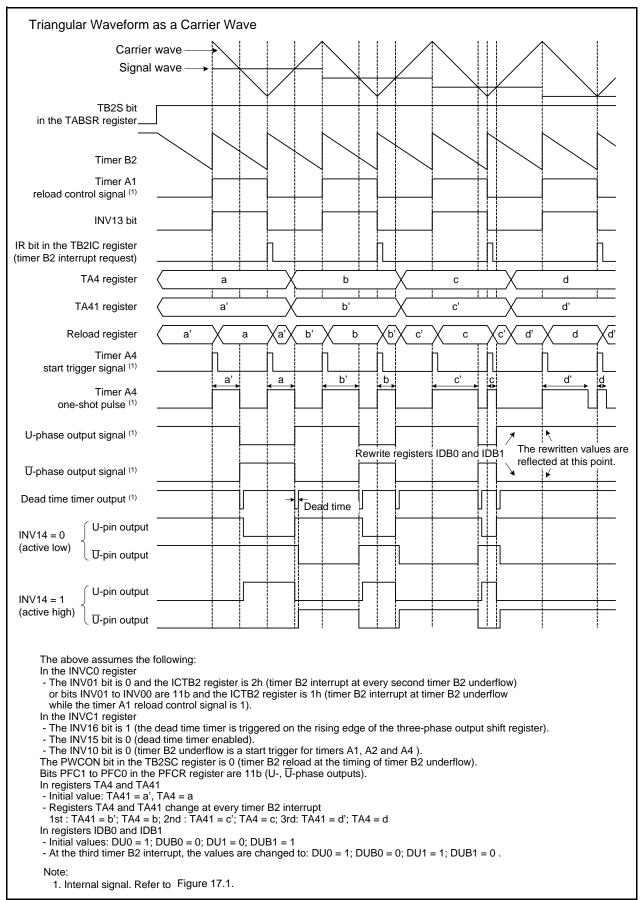

| 17.3.3      | Triangular Wave Modulation Three-Phase Mode 1                 | 359 |

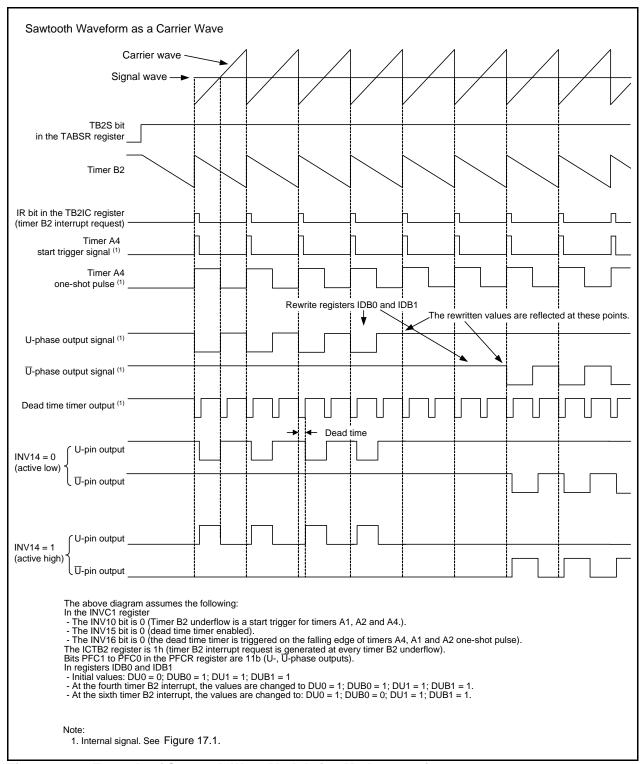

| 17.3.4      | Sawtooth Wave Modulation Mode                                 | 366 |

| 17.4 Inte   | rrupts                                                        | 371 |

| 17.4.1      | Timer B2 Interrupt                                            | 371 |

| 17.4.2      | Timer A1, A2, and A4 Interrupts                               | 371 |

| 17.5 Note   | es on Three-Phase Motor Control Timer Function                | 372 |

| 17.5.1      | Timer A and Timer B                                           | 372 |

| 17.5.2      | Influence of SD                                               | 372 |

| 18. Timer S | S                                                             | 373 |

| 18.1 Intro  | oduction                                                      | 373 |

| 18.2 Reg    | jisters                                                       | 377 |

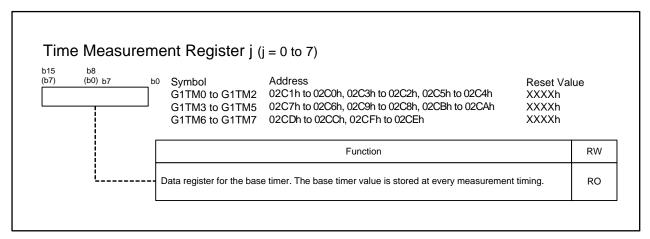

| 18.2.1      | Time Measurement Register j (G1TMj) (j = 0 to 7)              | 379 |

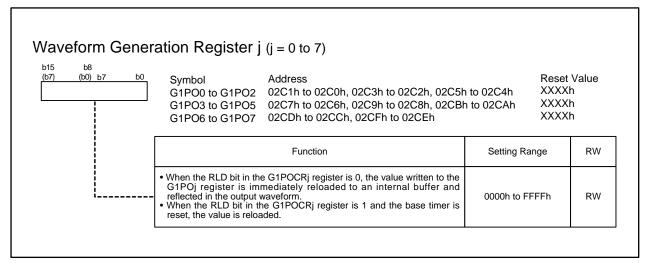

| 18.2.2      | Waveform Generation Register j (G1POj) (j = 0 to 7)           | 380 |

| 18.2.3      | Waveform Generation Control Register j (G1POCRj) (j = 0 to 7) | 381 |

| 18.2.4      | Time Measurement Control Register j (G1TMCRj) (j = 0 to 7)    |     |

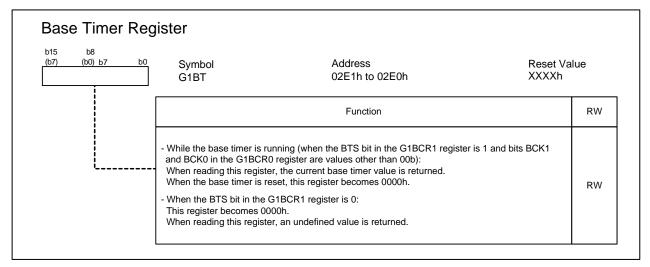

| 18.2.5      | Base Timer Register (G1BT)                                    |     |

| 18.2.6      | Base Timer Control Register 0 (G1BCR0)                        |     |

| 18.2.7      | Base Timer Control Register 1 (G1BCR1)                        |     |

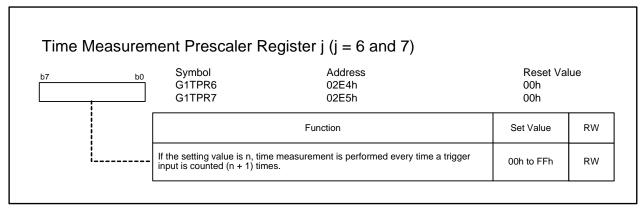

| 18.2.8      | Time Measurement Prescaler Register j (G1TPRj) (j = 6 and 7)  |     |

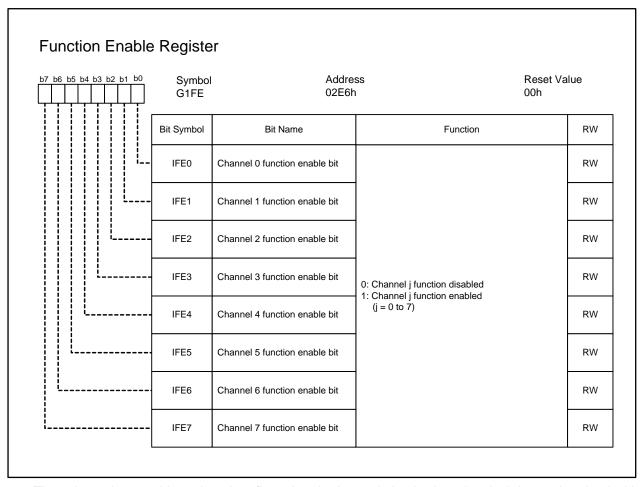

| 18.2.9      | Function Enable Register (G1FE)                               |     |

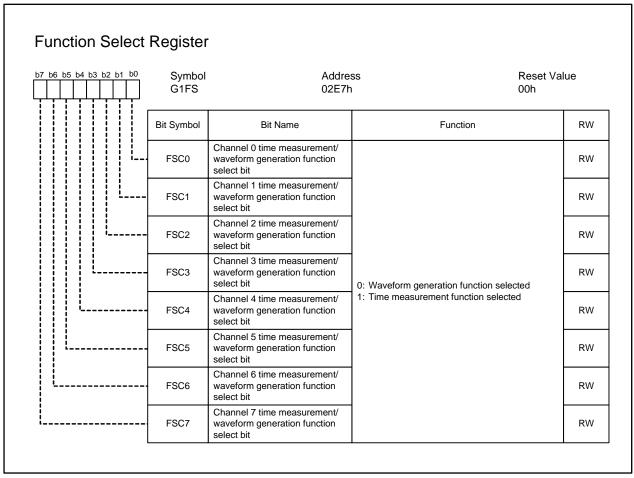

| 18.2.10      | Function Select Register (G1FS)                                        | 389 |

|--------------|------------------------------------------------------------------------|-----|

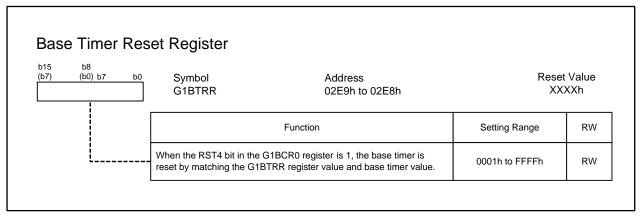

| 18.2.11      | Base Timer Reset Register (G1BTRR)                                     | 390 |

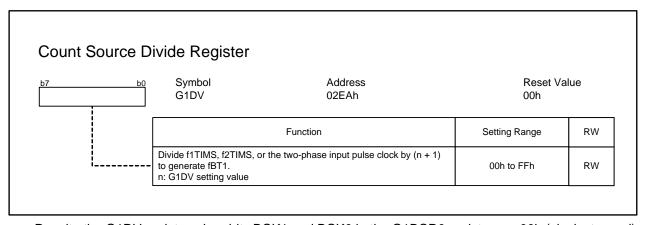

| 18.2.12      | Count Source Divide Register (G1DV)                                    | 390 |

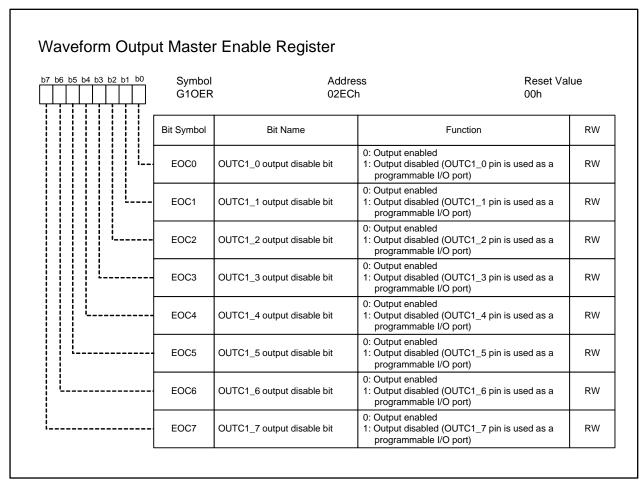

| 18.2.13      | Waveform Output Master Enable Register (G10ER)                         | 391 |

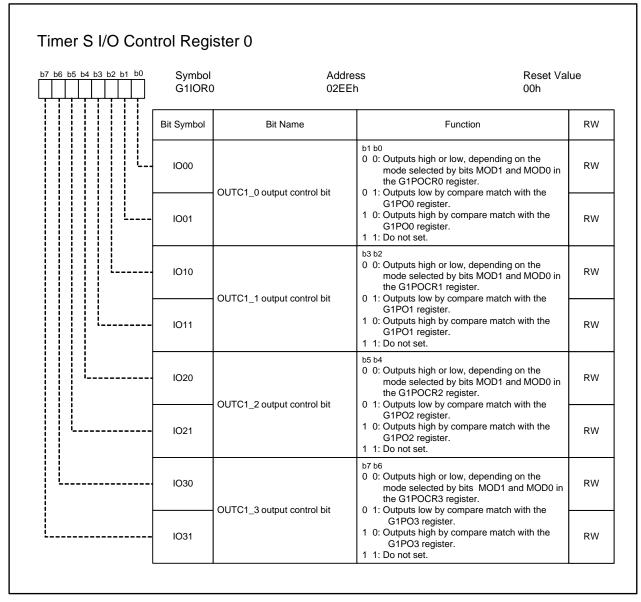

| 18.2.14      | Timer S I/O Control Register 0 (G1IOR0)                                | 392 |

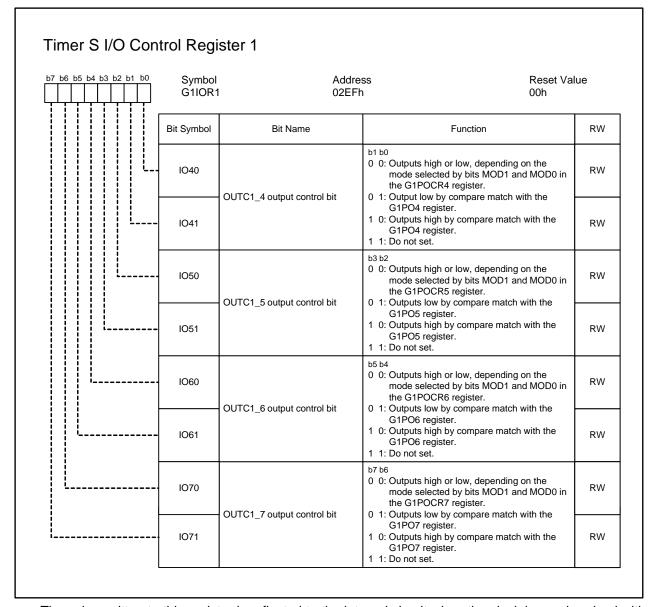

| 18.2.15      | Timer S I/O Control Register 1 (G1IOR1)                                | 393 |

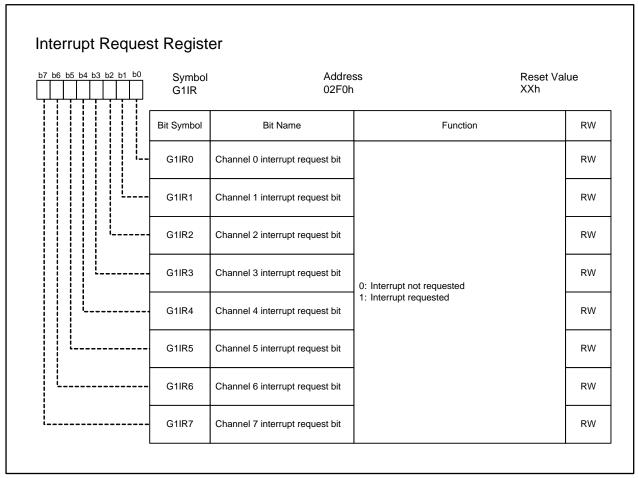

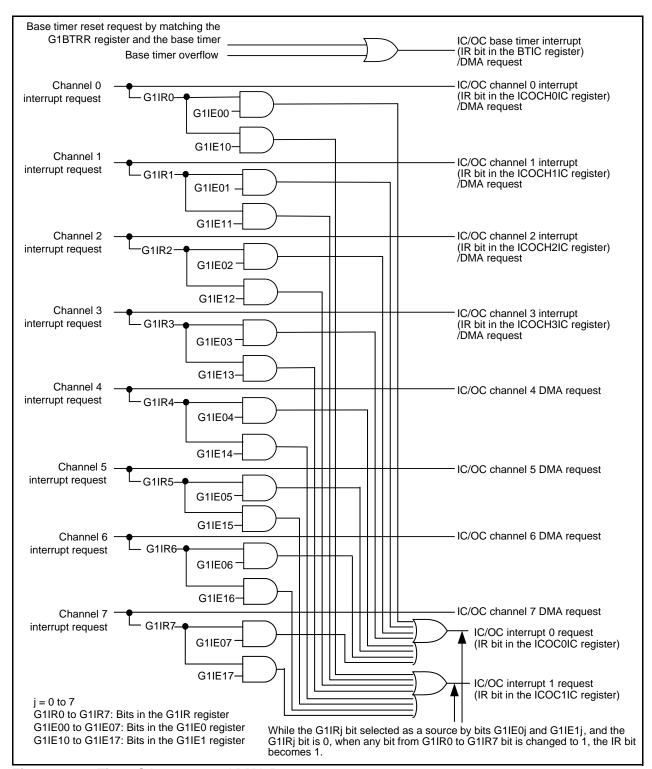

| 18.2.16      | Interrupt Request Register (G1IR)                                      | 394 |

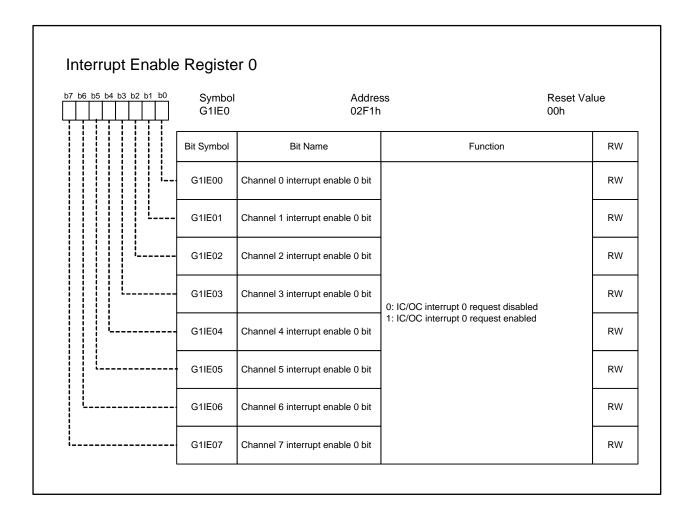

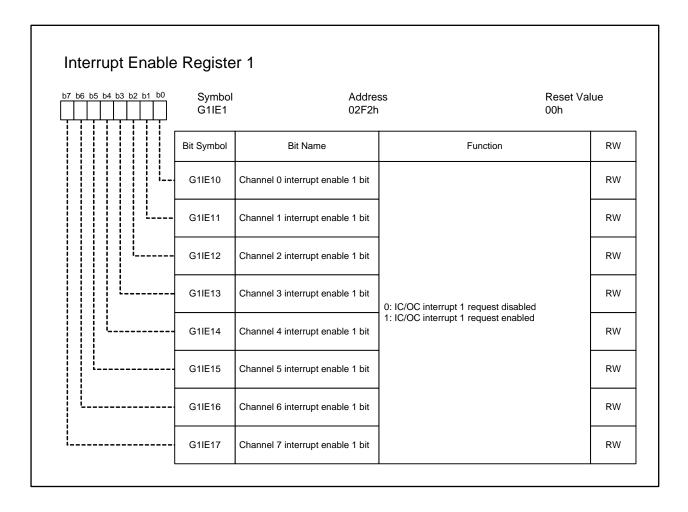

| 18.2.17      | Interrupt Enable Register 0 (G1IE0)                                    | 395 |

| 18.2.18      | Interrupt Enable Register 1 (G1IE1)                                    | 396 |

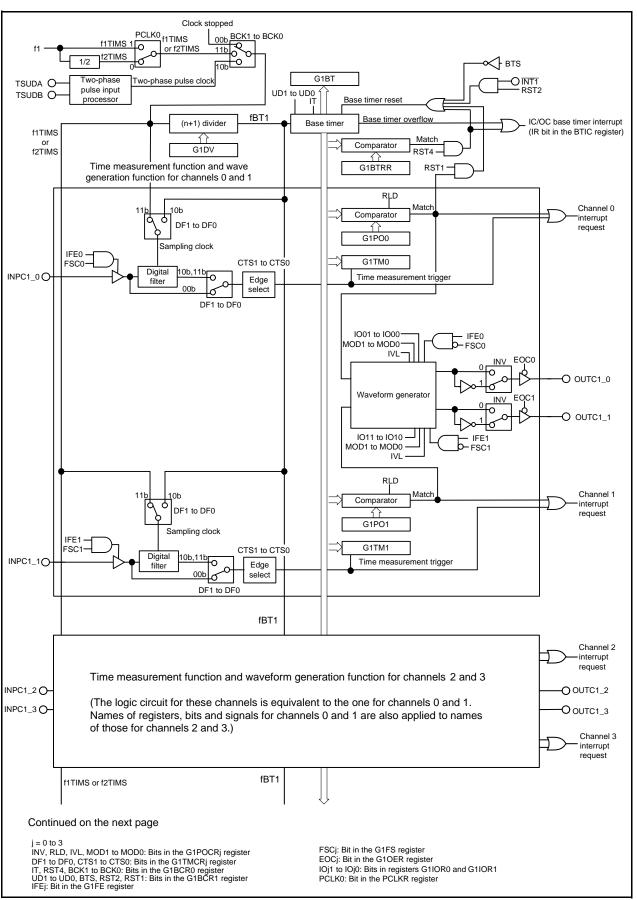

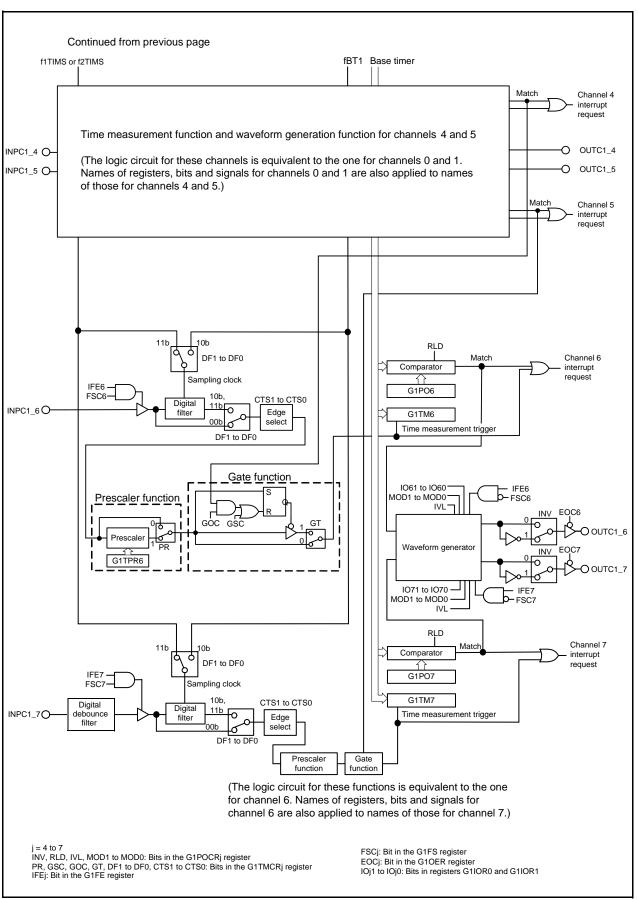

| 18.3 Ope     | rations                                                                | 397 |

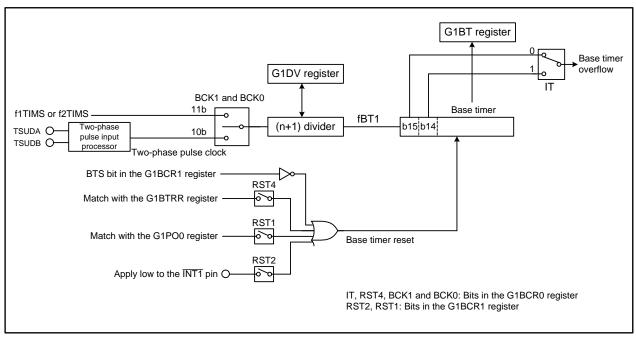

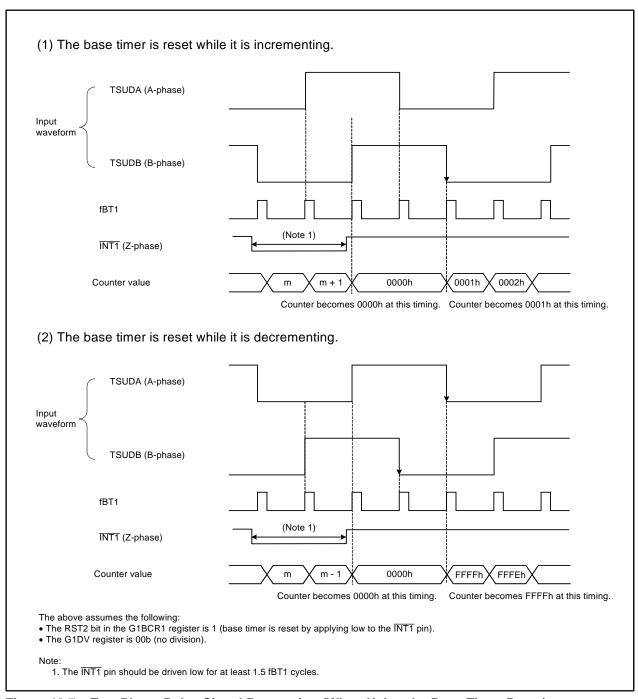

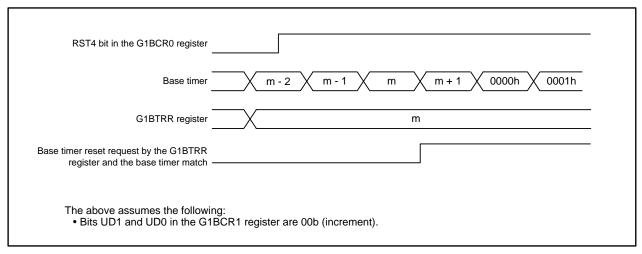

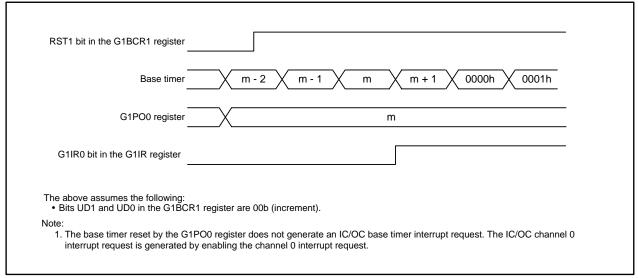

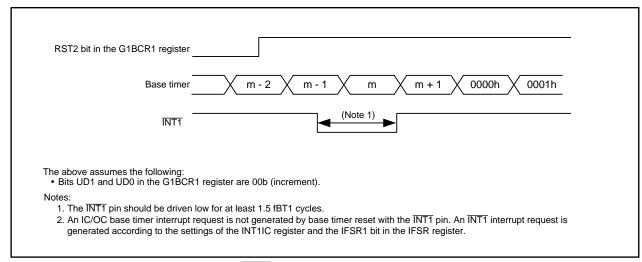

| 18.3.1       | Base Timer                                                             | 397 |

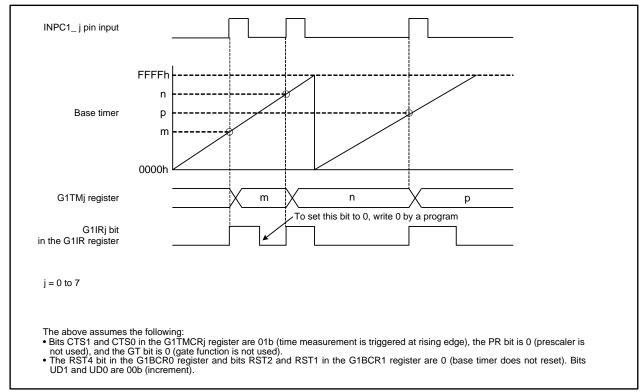

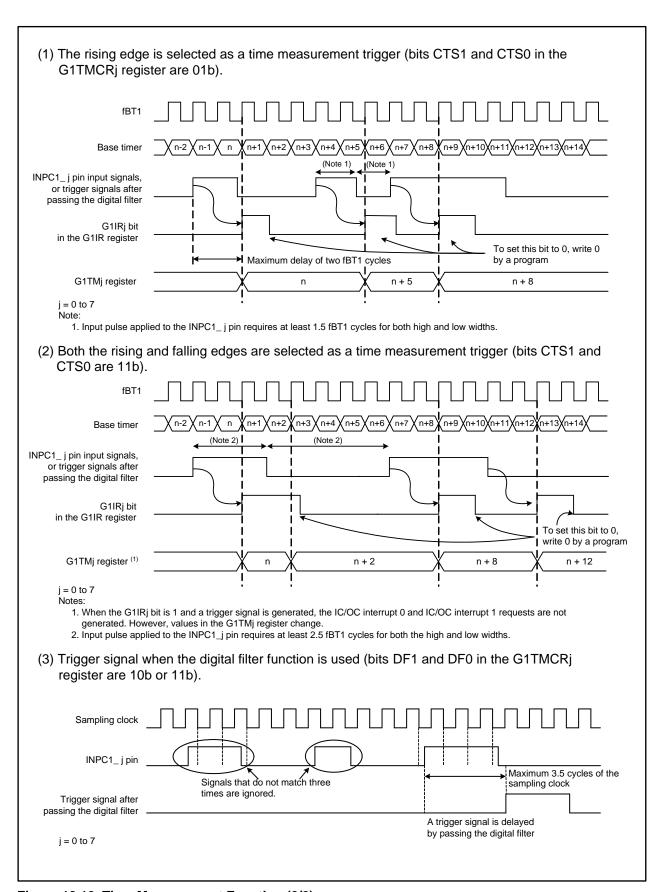

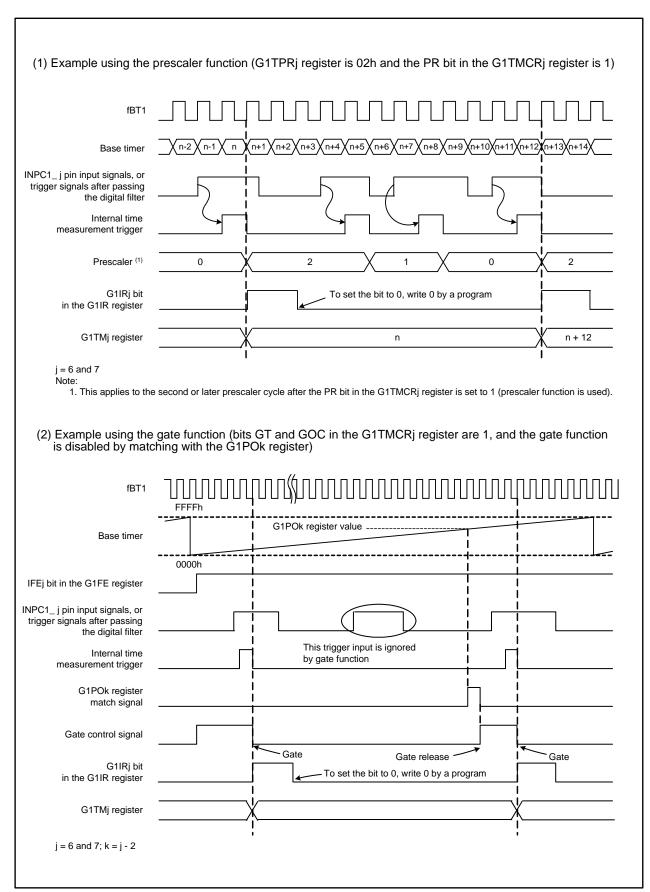

| 18.3.2       | Time Measurement Function                                              | 405 |

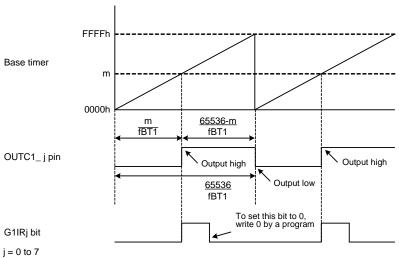

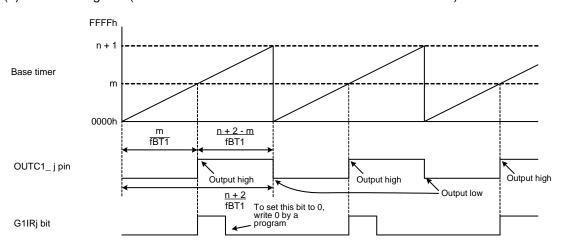

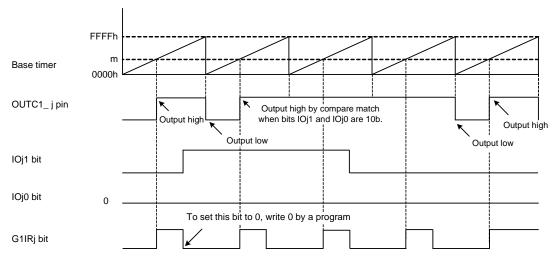

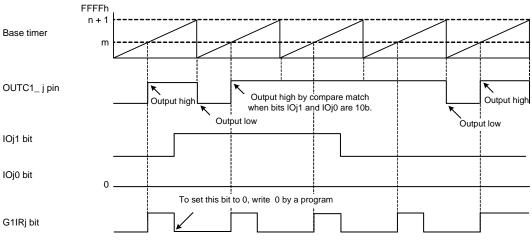

| 18.3.3       | Waveform Generation Function                                           | 409 |

| 18.3.4       | I/O Port Select Function                                               | 421 |

| 18.4 Inter   | rrupts                                                                 | 422 |

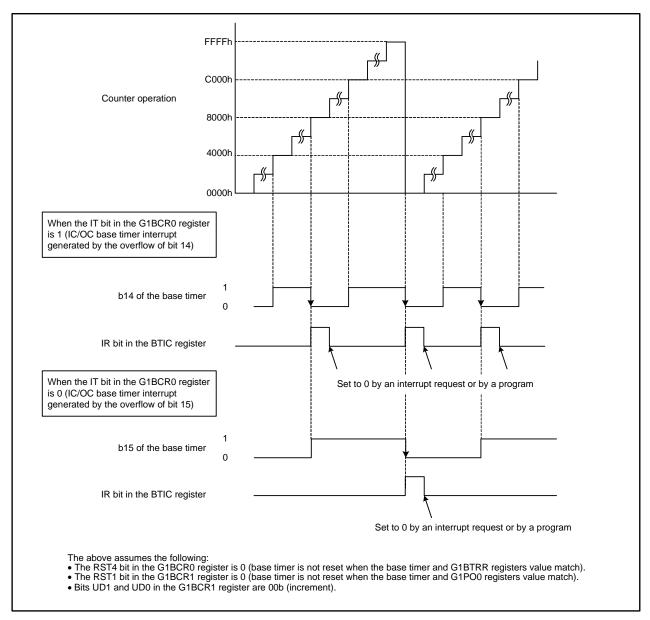

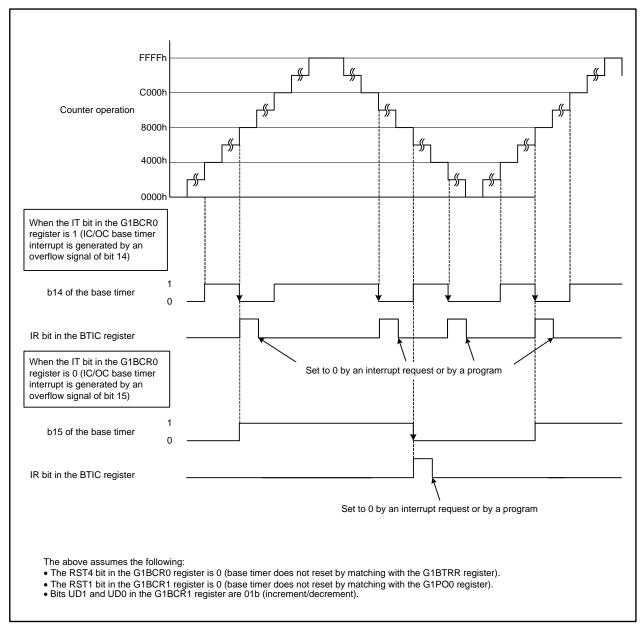

| 18.4.1       | IC/OC Base Timer Interrupt                                             | 423 |

| 18.4.2       | IC/OC Channel 0 Interrupt to IC/OC Channel 3 Interrupt                 | 423 |

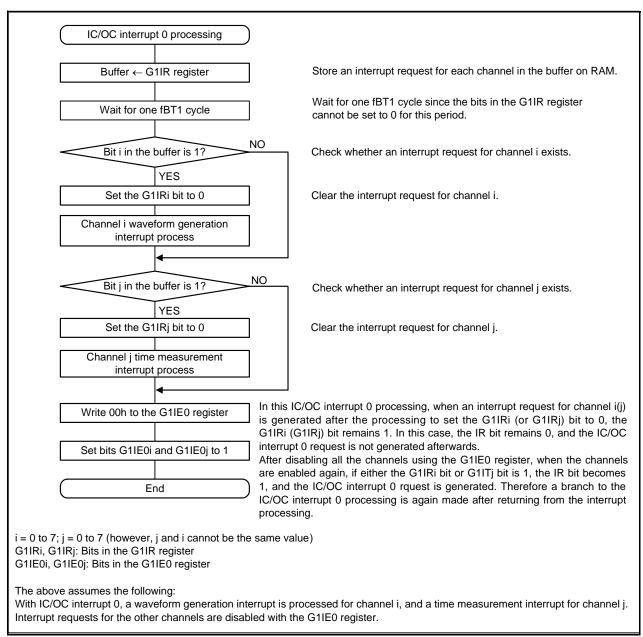

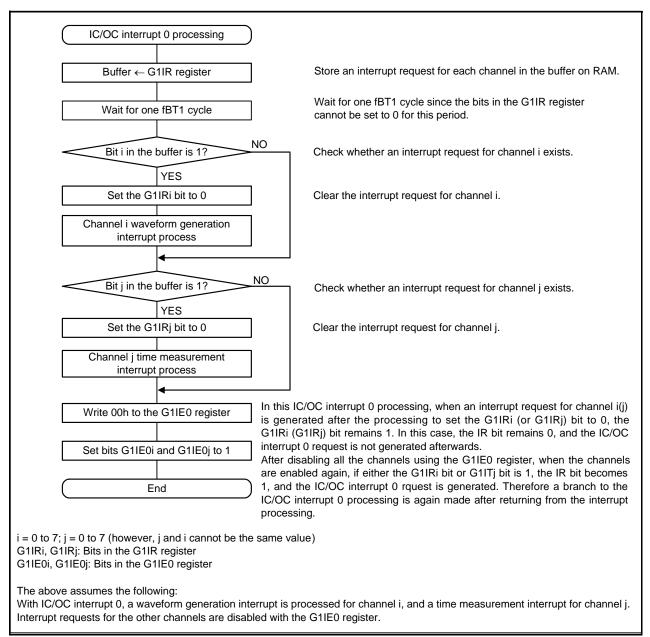

| 18.4.3       | IC/OC Interrupt 0 and IC/OC Interrupt 1                                | 423 |

| 18.5 Note    | es on Timer S                                                          | 424 |

| 18.5.1       | Register Access                                                        | 424 |

| 18.5.2       | Changing the G1IR Register                                             | 424 |

| 18.5.3       | Changing Registers ICOCiIC (i = 0, 1)                                  | 426 |

| 18.5.4       | Output Waveform During the Base Timer Reset with the BTS bit           | 426 |

| 18.5.5       | OUTC1_0 Pin Output During the Base Timer Reset with the G1PO0 register | 426 |

| 18.5.6       | Interrupt Request When Selecting Time Measurement Function             | 426 |

| 19. Task Mo  | onitor Timer                                                           | 427 |

| 19.1 Intro   | oduction                                                               | 427 |

| 19.2 Reg     | isters                                                                 | 428 |

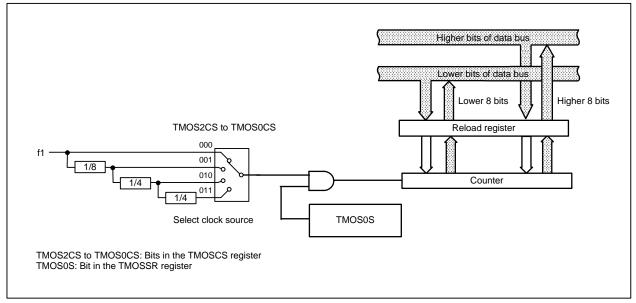

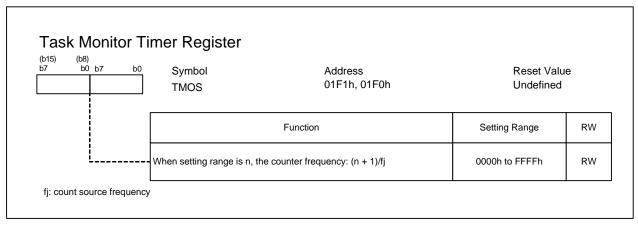

| 19.2.1       | Task Monitor Timer Register (TMOS)                                     | 428 |

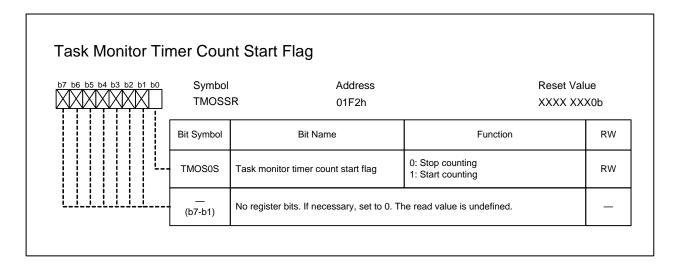

| 19.2.2       | Task Monitor Timer Count Start Flag (TMOSSR)                           | 428 |

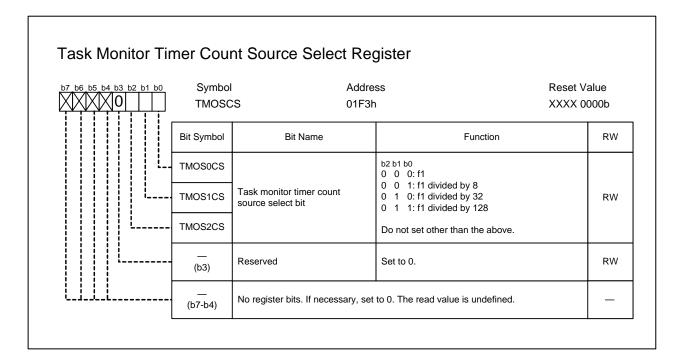

| 19.2.3       | Task Monitor Timer Count Source Select Register (TMOSCS)               | 429 |

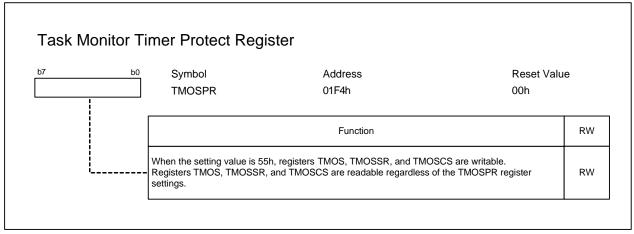

| 19.2.4       | Task Monitor Timer Protect Register (TMOSPR)                           | 429 |

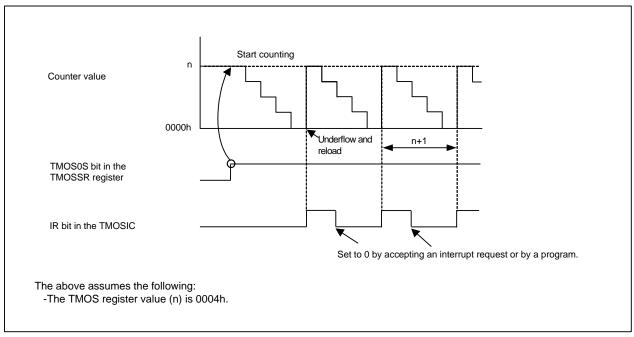

| 19.3 Ope     | ration                                                                 | 430 |

| 19.4 Inter   | rrupt                                                                  | 431 |

| 19.5 Note    | es on Task Monitor Timer                                               | 432 |

| 19.5.1       | Register Settings                                                      | 432 |

| 19.5.2       | Reading the Timer                                                      | 432 |

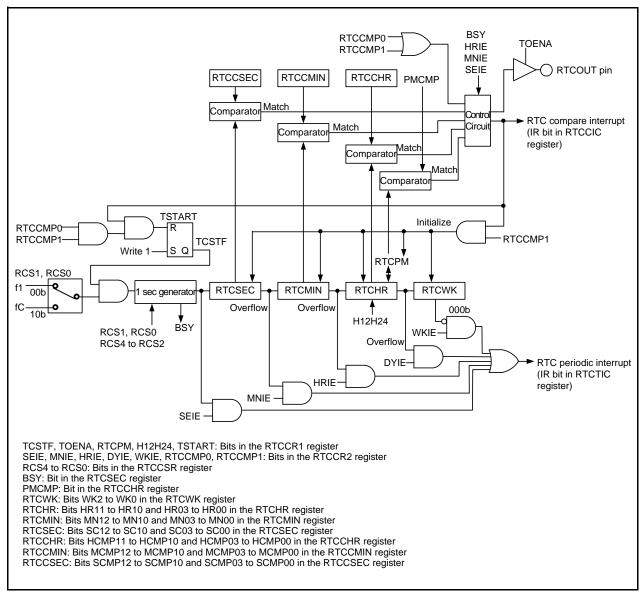

| 20. Real-Tii | me Clock                                                               | 433 |

| 20.1 Intro   |                                                                        | 122 |

| 2   | 20.2                                                                                                                                | Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 435                      |

|-----|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

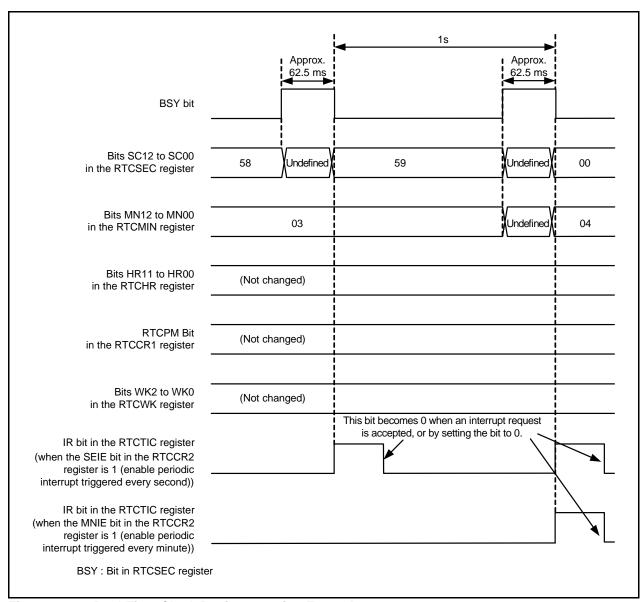

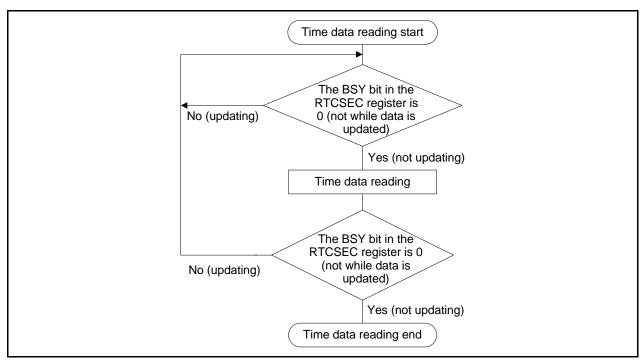

|     | 20.2.1                                                                                                                              | Real-Time Clock Second Data Register (RTCSEC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 436                      |

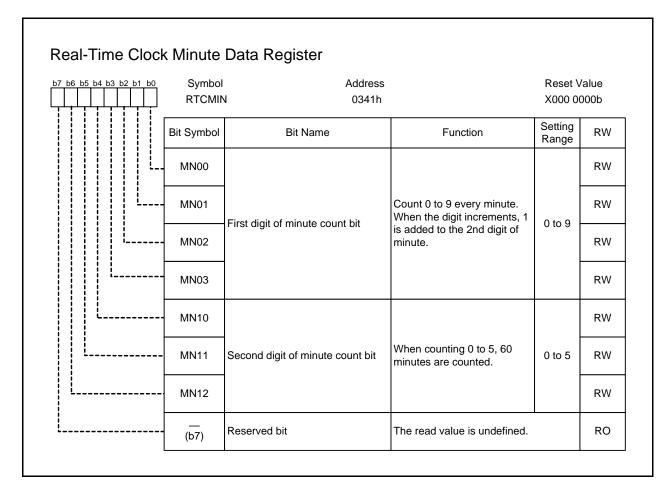

|     | 20.2.2                                                                                                                              | Real-Time Clock Minute Data Register (RTCMIN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 437                      |

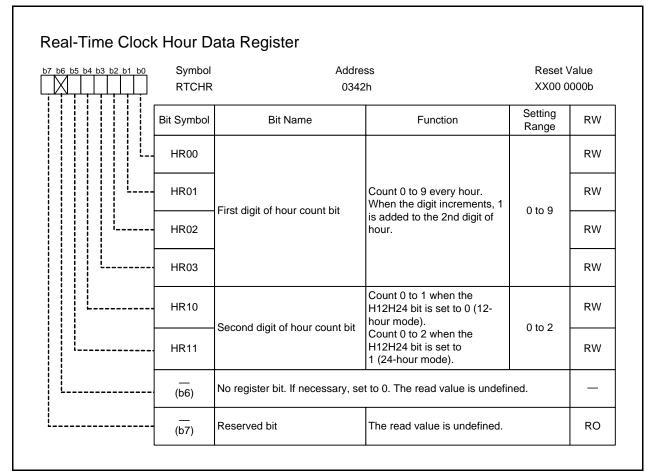

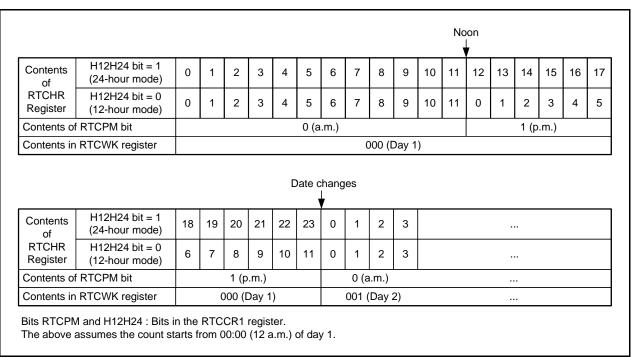

|     | 20.2.3                                                                                                                              | Real-Time Clock Hour Data Register (RTCHR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 438                      |

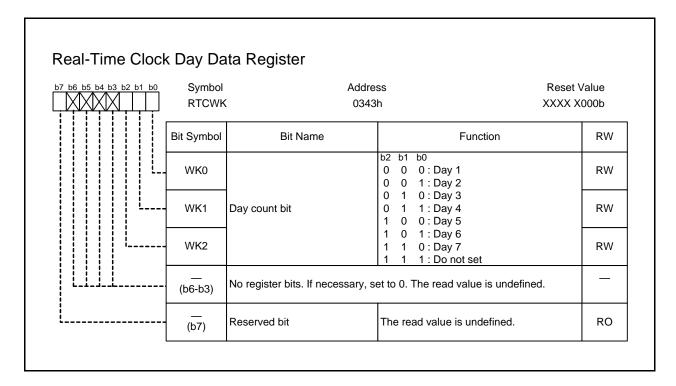

|     | 20.2.4                                                                                                                              | Real-Time Clock Day Data Register (RTCWK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 439                      |

|     | 20.2.5                                                                                                                              | Real-Time Clock Control Register 1 (RTCCR1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 440                      |

|     | 20.2.6                                                                                                                              | Real-Time Clock Control Register 2 (RTCCR2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 442                      |

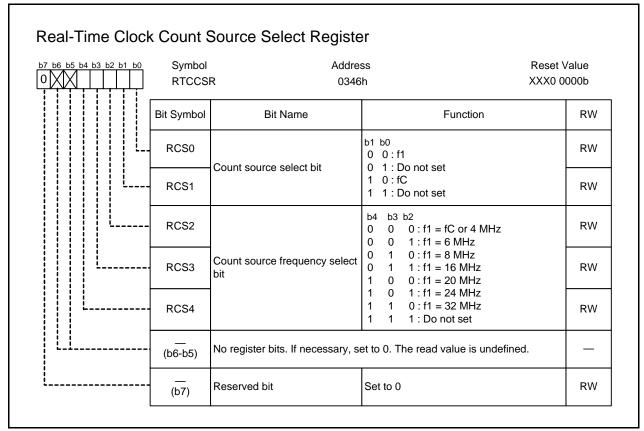

|     | 20.2.7                                                                                                                              | Real-Time Clock Count Source Select Register (RTCCSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 444                      |

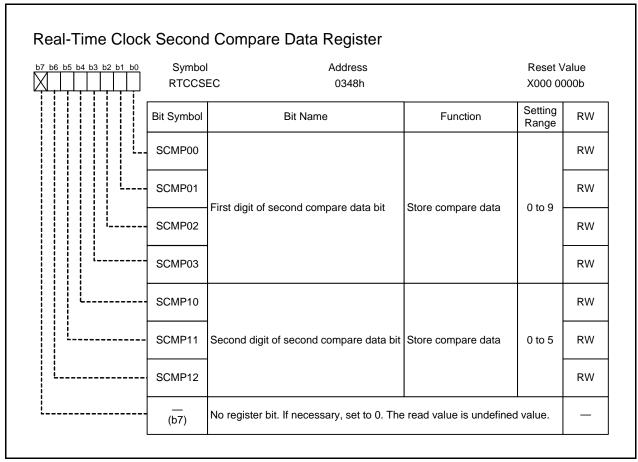

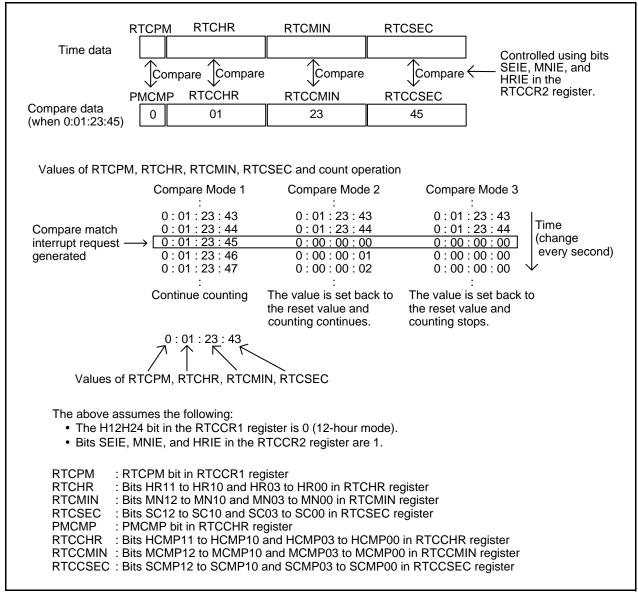

|     | 20.2.8                                                                                                                              | Real-Time Clock Second Compare Data Register (RTCCSEC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 445                      |

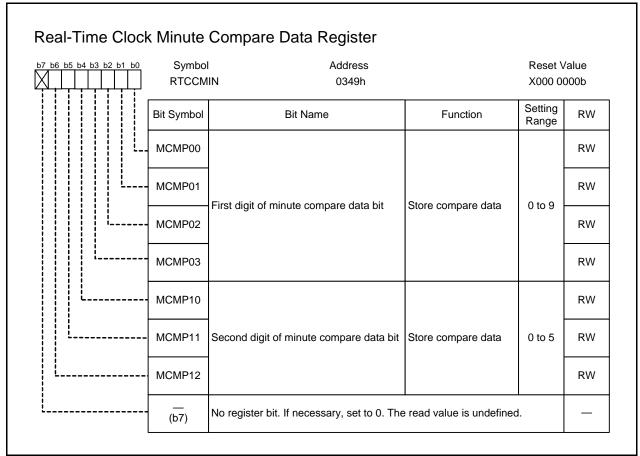

|     | 20.2.9                                                                                                                              | Real-Time Clock Minute Compare Data Register (RTCCMIN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 446                      |

|     | 20.2.1                                                                                                                              | Real-Time Clock Hour Compare Data Register (RTCCHR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 447                      |

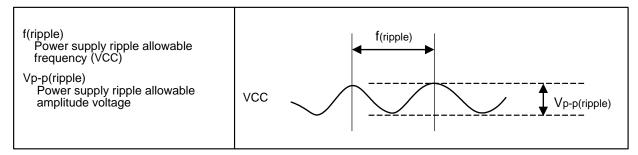

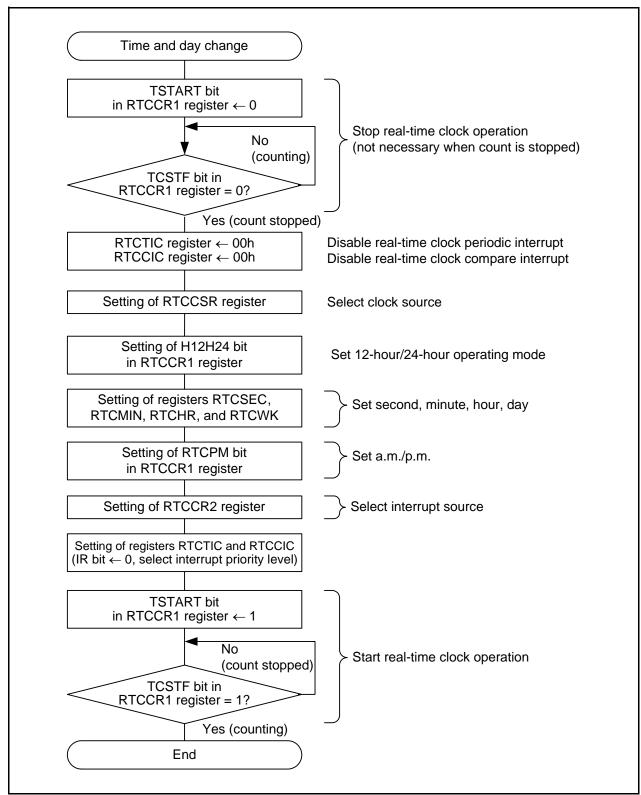

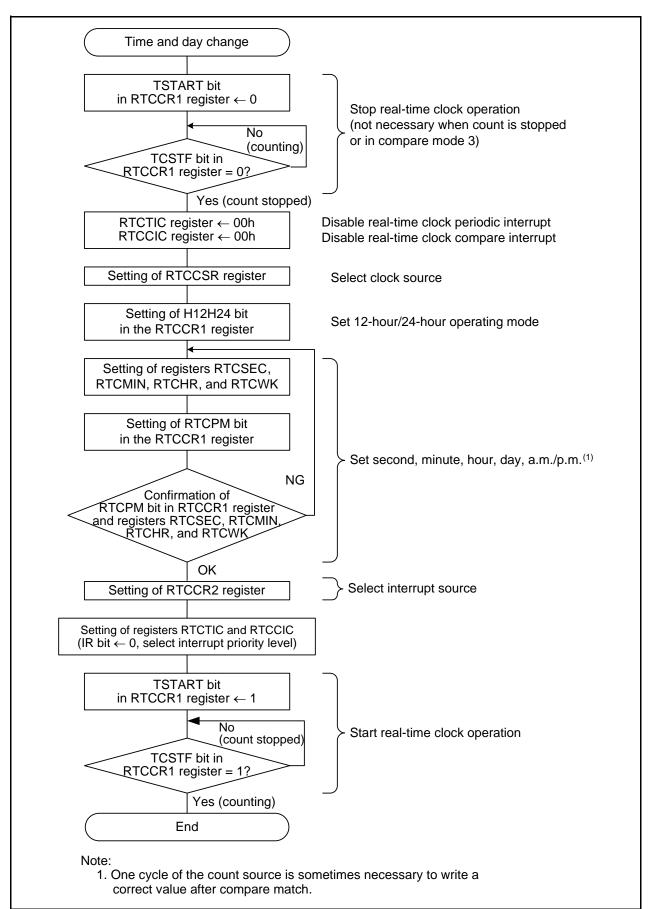

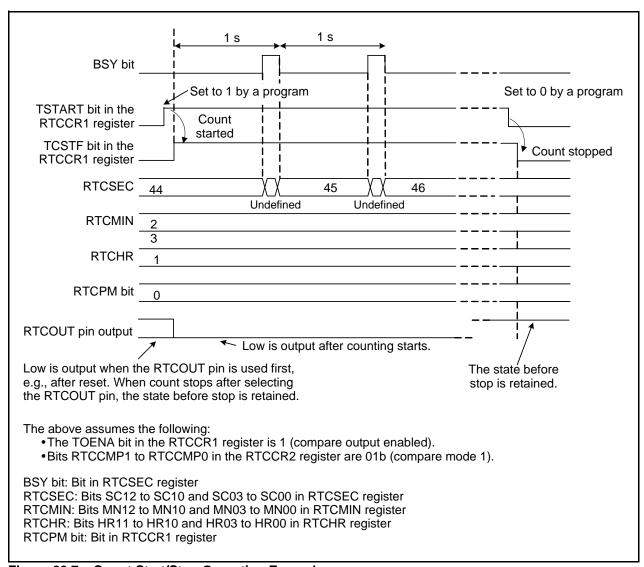

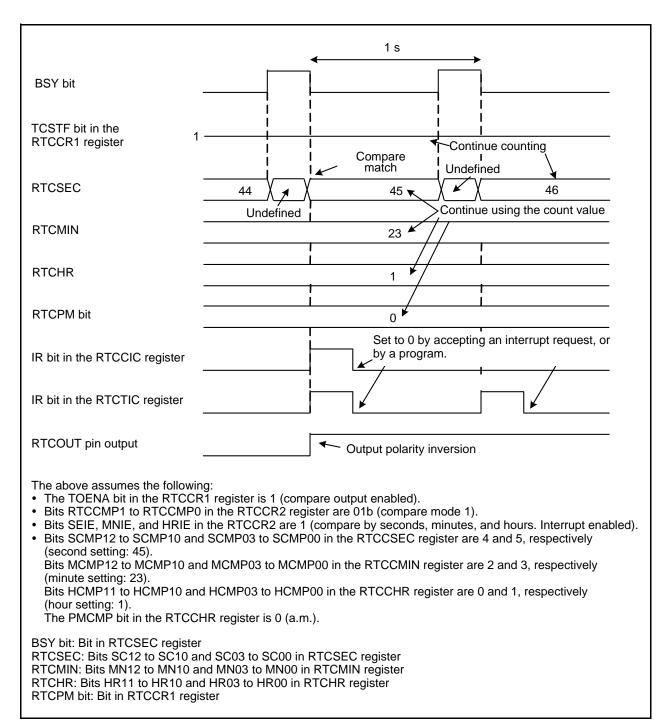

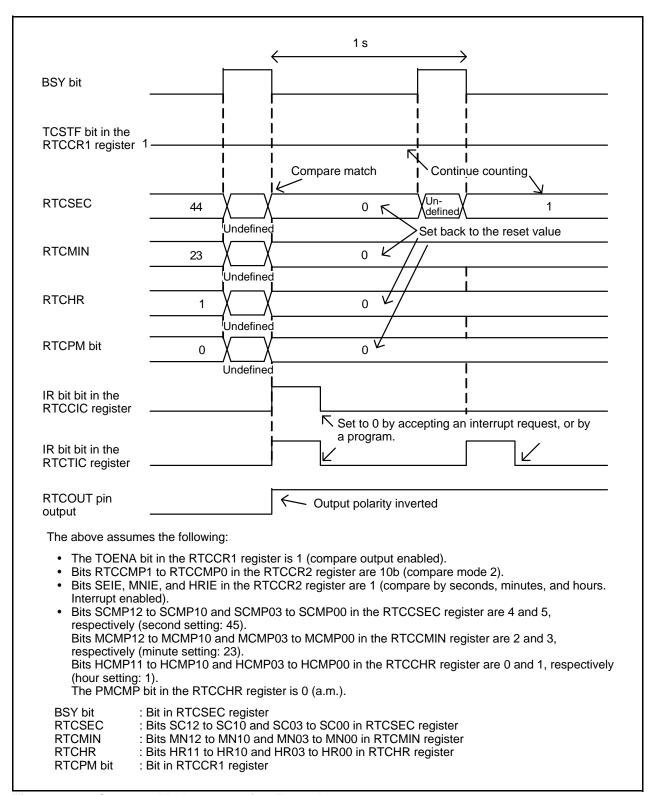

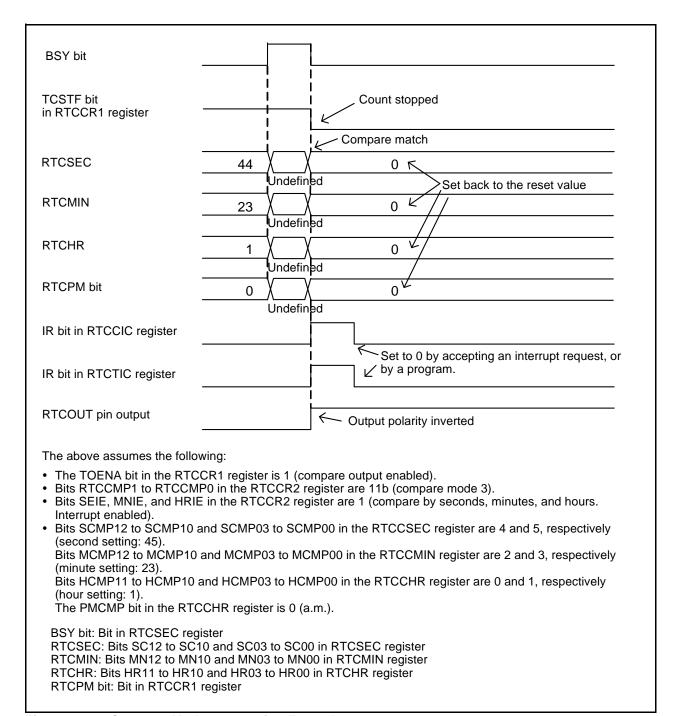

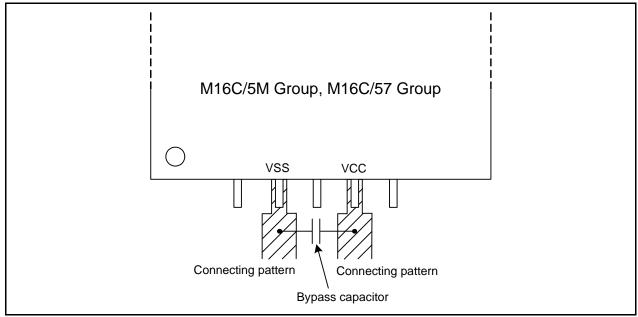

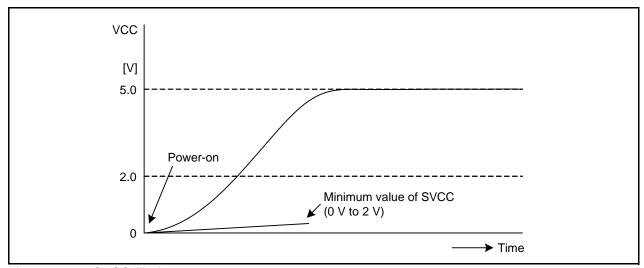

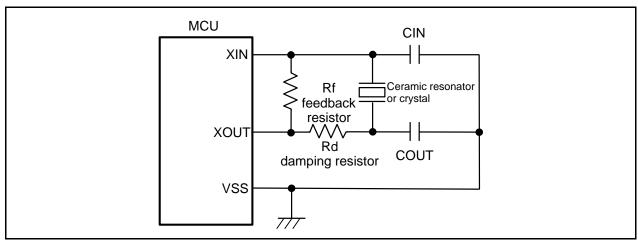

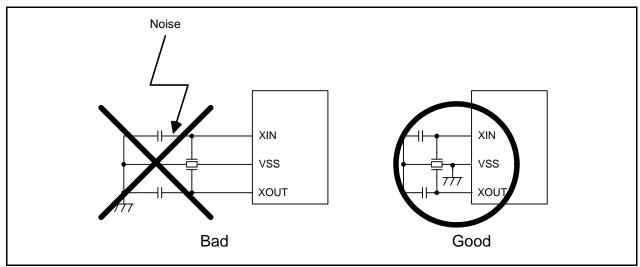

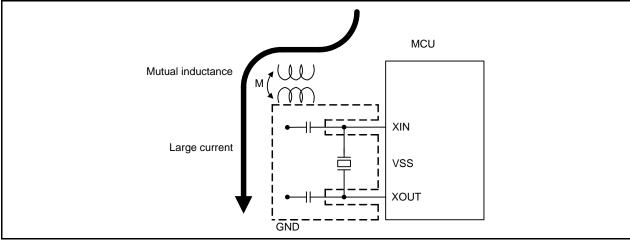

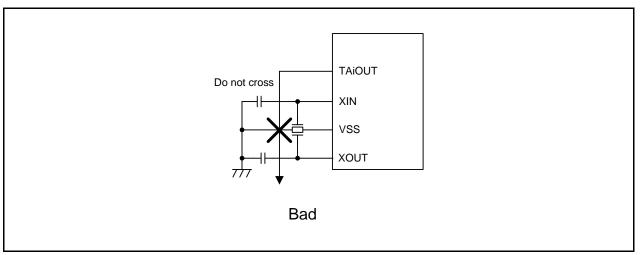

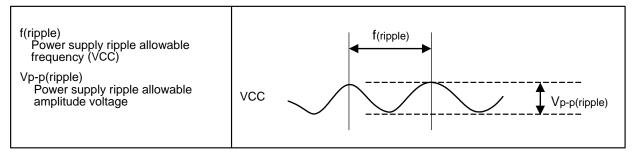

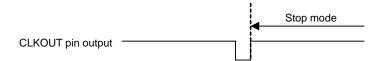

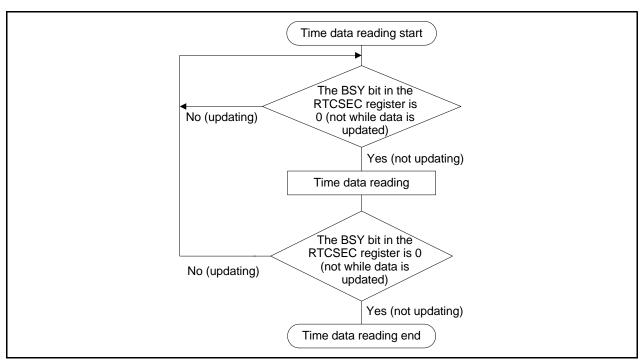

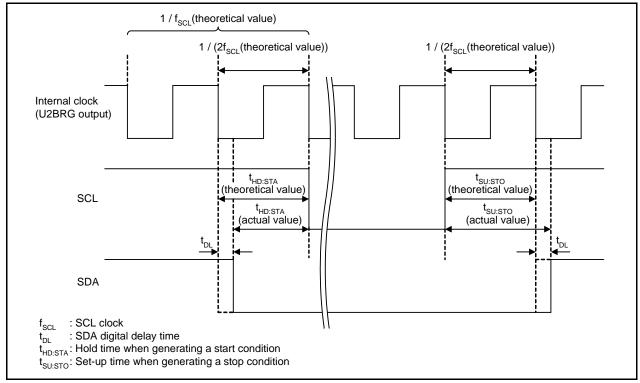

| 2   | 20.3                                                                                                                                | Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 448                      |