# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- All information included in this document is current as of the date this document is issued. Such information, however, is

subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please

confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to

additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# H8S/2144B, H8S/2134B

Hardware Manual

Renesas 16-Bit Single-Chip Microcomputer H8S Family/H8S/2100 Series

> H8S/2144B HD64F2144B H8S/2134B HD64F2134B

### Keep safety first in your circuit designs!

Renesas Technology Corp. puts the maximum effort into making semiconductor products better and

more reliable, but there is always the possibility that trouble may occur with them. Trouble with

semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate

measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or

(iii) prevention against any malfunction or mishap.

### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

### **General Precautions on Handling of Product**

#### 1. Treatment of NC Pins

Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

### 2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a pass-through current flows internally, and a malfunction may occur.

### 3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

#### 4. Prohibition of Access to Undefined or Reserved Addresses

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

# Configuration of This Manual

This manual comprises the following items:

- 1. General Precautions on Handling of Product

- 2. Configuration of This Manual

- 3. Preface

- 4. Contents

- 5. Overview

- 6. Description of Functional Modules

- CPU and System-Control Modules

- On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to the module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each section includes notes in relation to the descriptions given, and usage notes are given, as required, as the final part of each section.

- 7. List of Registers

- 8. Electrical Characteristics

- 9. Appendix

- 10. Main Revisions and Additions in this Edition (only for revised versions)

The list of revisions is a summary of points that have been revised or added to earlier versions. This does not include all of the revised contents. For details, see the actual locations in this manual.

11. Index

### **Preface**

The H8S/2144B and H8S/2134B are microcomputers (MCUs) made up of the H8S/2000 CPU employing Renesas Technology's original architecture as their cores, and the peripheral functions required to configure a system.

This manual was written for users who will be using the H8S/2144B or Target Users:

H8S/2134B in the design of application systems. Target users are expected to

understand the fundamentals of electrical circuits, logical circuits, and

microcomputers.

Objective: This manual was written to explain the hardware functions and electrical

characteristics of the H8S/2144B and H8S/2134B to the target users.

Refer to the H8S/2600 Series, H8S/2000 Series Software Manual for a detailed

description of the instruction set.

Notes on reading this manual:

• In order to understand the overall functions of the chip Read the manual according to the contents. This manual can be roughly categorized into parts on the CPU, system control functions, peripheral functions and electrical characteristics.

In order to understand the details of the CPU's functions Read the H8S/2600 Series, H8S/2000 Series Software Manual.

In order to understand the details of a register when its name is known Read the index that is the final part of the manual to find the page number of the entry on the

register. The addresses, bits, and initial values of the registers are summarized in section 19, List of Registers.

Rules: The following notation is used for cases when the same or a Register name:

similar function, e.g. serial communication interface, is

implemented on more than one channel:

XXX\_N (XXX is the register name and N is the channel

number)

Bit order: The MSB is on the left and the LSB is on the right.

Number notation: Binary is B'xxxx, hexadecimal is H'xxxx, decimal is xxxx.

An overbar is added to a active-low signal:  $\overline{xxxx}$ Signal notation:

Related Manuals: The latest versions of all related manuals are available from our web site.

Please ensure you have the latest versions of all documents you require.

http://www.renesas.com/

### H8S/2144B, H8S/2134B manuals:

| Manual Title                                     | ADE No.     |  |  |

|--------------------------------------------------|-------------|--|--|

| H8S/2144B, H8S/2134B Hardware Manual             | This manual |  |  |

| H8S/2600 Series, H8S/2000 Series Software Manual | REJ09B0139  |  |  |

# User's manuals for development tools:

| Manual Title                                                                                     | ADE No.     |

|--------------------------------------------------------------------------------------------------|-------------|

| H8S, H8/300 Series C/C++ Compiler, Assembler, Optimizing Linkage Editor User's Manual            | REJ10B0058  |

| Microcomputer Development Environment System H8S, H8/300 Series Simulator/Debugger User's Manual | ADE-702-282 |

| H8S, H8/300 Series High-performance Embedded Workshop 3 Tutorial                                 | REJ10B0024  |

| H8S, H8/300 Series High-performance Embedded Workshop 3 User's Manual                            | REJ10B0026  |

# Contents

| Sect | tion 1 (               | Overview                                                              | 1  |

|------|------------------------|-----------------------------------------------------------------------|----|

| 1.1  | Featur                 | es                                                                    | 1  |

| 1.2  | Block                  | Diagram                                                               | 3  |

| 1.3  | Pin Ar                 | rangements and Functions                                              | 5  |

|      | 1.3.1                  | Pin Arrangements                                                      | 5  |

|      | 1.3.2                  | Pin Functions in Each Operating Mode                                  | 7  |

|      | 1.3.3                  | Pin Functions                                                         | 14 |

| Sect | tion 2 C               | CPU                                                                   | 19 |

| 2.1  | Featur                 | es                                                                    | 19 |

|      | 2.1.1                  | Differences between H8S/2600 CPU and H8S/2000 CPU                     | 20 |

|      | 2.1.2                  | Differences from H8/300 CPU                                           | 20 |

|      | 2.1.3                  | Differences from H8/300H CPU                                          | 21 |

| 2.2  | CPU (                  | Operating Modes                                                       | 22 |

|      | 2.2.1                  | Normal Mode                                                           |    |

|      | 2.2.2                  | Advanced Mode                                                         | 24 |

| 2.3  | Addre                  | ss Space                                                              | 26 |

| 2.4  | Register Configuration |                                                                       | 27 |

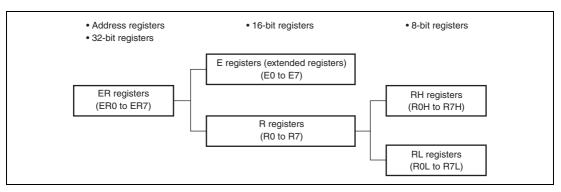

|      | 2.4.1                  | General Registers                                                     | 28 |

|      | 2.4.2                  | Program Counter (PC)                                                  | 29 |

|      | 2.4.3                  | Extended Control Register (EXR)                                       | 29 |

|      | 2.4.4                  | Condition-Code Register (CCR)                                         | 29 |

|      | 2.4.5                  | Initial Register Values                                               | 31 |

| 2.5  | Data Formats           |                                                                       | 31 |

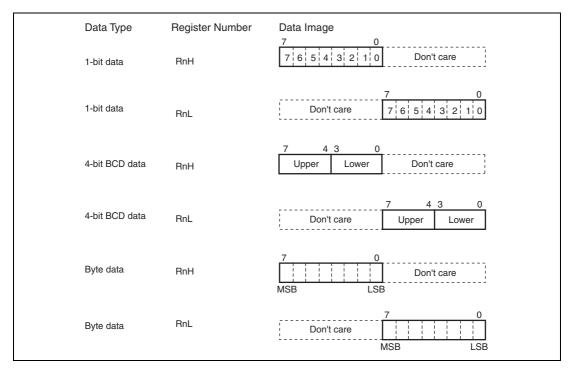

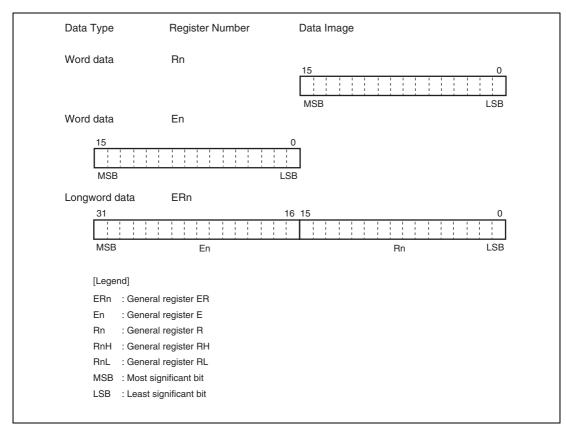

|      | 2.5.1                  | General Register Data Formats                                         | 31 |

|      | 2.5.2                  | Memory Data Formats                                                   | 34 |

| 2.6  | Instruc                | ction Set                                                             | 35 |

|      | 2.6.1                  | Table of Instructions Classified by Function                          | 36 |

|      | 2.6.2                  | Basic Instruction Formats                                             | 46 |

| 2.7  | Addre                  | ssing Modes and Effective Address Calculation                         | 47 |

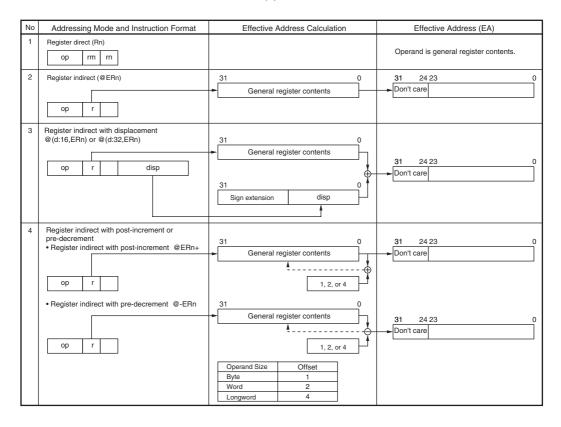

|      | 2.7.1                  | Register Direct—Rn                                                    | 48 |

|      | 2.7.2                  | Register Indirect—@ERn                                                | 48 |

|      | 2.7.3                  | Register Indirect with Displacement—@(d:16, ERn) or @(d:32, ERn)      | 48 |

|      | 2.7.4                  | Register Indirect with Post-Increment or Pre-Decrement—@ERn+ or @-ERn |    |

|      | 2.7.5                  | Absolute Address—@aa:8, @aa:16, @aa:24, or @aa:32                     | 49 |

|      | 2.7.6                  | Immediate—#xx:8, #xx:16, or #xx:32                                    | 50 |

|      |                        |                                                                       |    |

|     | 2.7.7    | Program-Counter Relative—@(d:8, PC) or @(d:16, PC) | 50 |

|-----|----------|----------------------------------------------------|----|

|     | 2.7.8    | Memory Indirect—@@aa:8                             |    |

|     | 2.7.9    | Effective Address Calculation                      | 52 |

| 2.8 | Proces   | ssing States                                       | 54 |

| 2.9 | Usage    | Notes                                              | 56 |

|     | 2.9.1    | Note on TAS Instruction Usage                      | 56 |

|     | 2.9.2    | Note on STM/LDM Instruction Usage                  | 56 |

|     | 2.9.3    | Note on Bit Manipulation Instructions              | 56 |

|     | 2.9.4    | EEPMOV Instruction                                 | 58 |

| Sec | tion 3 N | MCU Operating Modes                                | 59 |

| 3.1 | MCU      | Operating Mode Selection                           | 59 |

| 3.2 | Regist   | er Descriptions                                    | 59 |

|     | 3.2.1    | Mode Control Register (MDCR)                       | 60 |

|     | 3.2.2    | System Control Register (SYSCR)                    | 61 |

|     | 3.2.3    | Serial Timer Control Register (STCR)               | 63 |

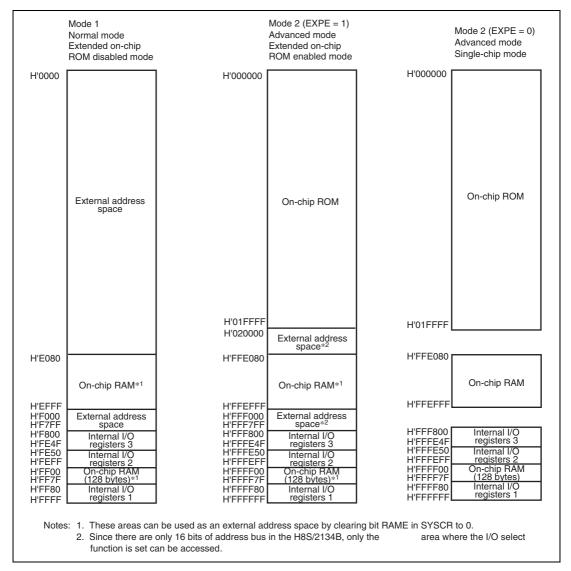

| 3.3 | Operat   | ting Mode Descriptions                             | 65 |

|     | 3.3.1    | Mode 1                                             | 65 |

|     | 3.3.2    | Mode 2                                             | 65 |

|     | 3.3.3    | Mode 3                                             |    |

|     | 3.3.4    | Pin Functions in Each Operating Mode               |    |

| 3.4 | Addre    | ss Map in Each Operating Mode                      | 67 |

| Sec | tion 4 E | Exception Handling                                 | 69 |

| 4.1 |          | tion Handling Types and Priority                   |    |

| 4.2 | Excep    | tion Sources and Exception Vector Table            | 70 |

| 4.3 | Reset .  |                                                    |    |

|     | 4.3.1    | Reset Exception Handling                           |    |

|     | 4.3.2    | Interrupts after Reset                             |    |

|     | 4.3.3    | On-Chip Peripheral Modules after Reset is Released |    |

| 4.4 |          | pt Exception Handling                              |    |

| 4.5 | -        | nstruction Exception Handling                      |    |

| 4.6 |          | Status after Exception Handling                    |    |

| 4.7 | Usage    | Note                                               | 75 |

|     |          | nterrupt Controller                                |    |

| 5.1 |          | es                                                 |    |

| 5.2 |          | Output Pins                                        |    |

| 5.3 | Regist   | er Descriptions                                    | 79 |

|     | 5 3 1    | Interrupt Control Registers A to C (ICRA to ICRC)  | 80 |

|      | 5.3.2    | Address Break Control Register (ABRKCR)                  | 81  |

|------|----------|----------------------------------------------------------|-----|

|      | 5.3.3    | Break Address Registers A to C (BARA to BARC)            |     |

|      | 5.3.4    | IRQ Sense Control Registers (ISCRH, ISCRL)               | 82  |

|      | 5.3.5    | IRQ Enable Register (IER)                                | 83  |

|      | 5.3.6    | IRQ Status Register (ISR)                                | 84  |

|      | 5.3.7    | Keyboard Matrix Interrupt Mask Registers (KMIMRA, KMIMR) | 85  |

| 5.4  | Interru  | ipt Sources                                              | 87  |

|      | 5.4.1    | External Interrupts                                      | 87  |

|      | 5.4.2    | Internal Interrupts                                      | 89  |

| 5.5  | Interru  | pt Exception Handling Vector Table                       | 89  |

| 5.6  | Interru  | upt Control Modes and Interrupt Operation                | 92  |

|      | 5.6.1    | Interrupt Control Mode 0                                 | 92  |

|      | 5.6.2    | Interrupt Control Mode 1                                 | 95  |

|      | 5.6.3    | Interrupt Exception Handling Sequence                    | 98  |

|      | 5.6.4    | Interrupt Response Times                                 |     |

| 5.7  | Addre    | ss Break                                                 | 101 |

|      | 5.7.1    | Features                                                 | 101 |

|      | 5.7.2    | Block Diagram                                            | 101 |

|      | 5.7.3    | Operation                                                | 101 |

|      | 5.7.4    | Usage Notes                                              | 102 |

| 5.8  | Usage    | Notes                                                    | 104 |

|      | 5.8.1    | Conflict between Interrupt Generation and Disabling      | 104 |

|      | 5.8.2    | Instructions that Disable Interrupts                     | 105 |

|      | 5.8.3    | Interrupts during Execution of EEPMOV Instruction        |     |

|      | 5.8.4    | IRQ Status Register (ISR)                                | 105 |

| Sect | tion 6 I | Bus Controller (BSC)                                     | 107 |

| 6.1  |          | es                                                       |     |

| 6.2  |          | Output Pins                                              |     |

| 6.3  |          | er Descriptions                                          |     |

|      | 6.3.1    | Bus Control Register (BCR)                               |     |

|      | 6.3.2    | Wait State Control Register (WSCR)                       |     |

| 6.4  | Bus C    | ontrol                                                   |     |

|      | 6.4.1    | Bus Specifications                                       |     |

|      | 6.4.2    | Advanced Mode                                            |     |

|      | 6.4.3    | Normal Mode                                              |     |

|      | 6.4.4    | I/O Select Signals                                       |     |

| 6.5  | Basic    | Bus Interface                                            |     |

|      | 6.5.1    | Data Size and Data Alignment                             |     |

|      | 652      | e                                                        |     |

|      | 6.5.3    | Basic Operation Timing                      | 119 |

|------|----------|---------------------------------------------|-----|

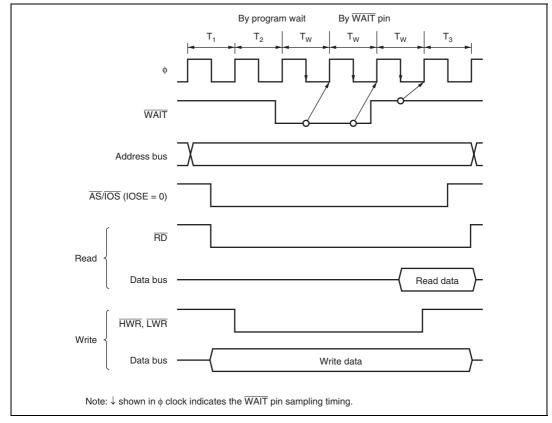

|      | 6.5.4    | Wait Control                                |     |

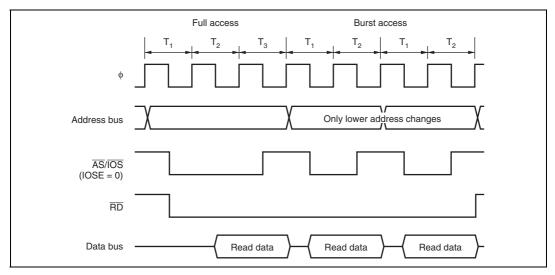

| 6.6  | Burst l  | ROM Interface                               | 129 |

|      | 6.6.1    | Basic Operation Timing                      | 129 |

|      | 6.6.2    | Wait Control                                | 130 |

| 6.7  | Idle C   | ycle                                        | 131 |

| Sect | tion 7 L | /O Ports                                    | 133 |

| 7.1  |          | iew                                         |     |

| 7.2  | Port 1   |                                             | 140 |

|      | 7.2.1    | Port 1 Data Direction Register (P1DDR)      |     |

|      | 7.2.2    | Port 1 Data Register (P1DR)                 |     |

|      | 7.2.3    | Port 1 Pull-Up MOS Control Register (P1PCR) |     |

|      | 7.2.4    | Pin Functions                               | 142 |

|      | 7.2.5    | Port 1 Input Pull-Up MOS                    | 142 |

| 7.3  | Port 2   |                                             | 143 |

|      | 7.3.1    | Port 2 Data Direction Register (P2DDR)      | 143 |

|      | 7.3.2    | Port 2 Data Register (P2DR)                 | 144 |

|      | 7.3.3    | Port 2 Pull-Up MOS Control Register (P2PCR) | 144 |

|      | 7.3.4    | Pin Functions                               | 145 |

|      | 7.3.5    | Port 2 Input Pull-Up MOS                    | 145 |

| 7.4  | Port 3   |                                             | 147 |

|      | 7.4.1    | Port 3 Data Direction Register (P3DDR)      | 147 |

|      | 7.4.2    | Port 3 Data Register (P3DR)                 |     |

|      | 7.4.3    | Port 3 Pull-Up MOS Control Register (P3PCR) | 148 |

|      | 7.4.4    | Pin Functions                               |     |

|      | 7.4.5    | Port 3 Input Pull-Up MOS                    | 148 |

| 7.5  |          |                                             |     |

|      | 7.5.1    | Port 4 Data Direction Register (P4DDR)      |     |

|      | 7.5.2    | Port 4 Data Register (P4DR)                 | 150 |

|      | 7.5.3    | Pin Functions                               | 151 |

| 7.6  | Port 5   |                                             |     |

|      | 7.6.1    | Port 5 Data Direction Register (P5DDR)      |     |

|      | 7.6.2    | Port 5 Data Register (P5DR) P3PCR           |     |

|      | 7.6.3    | Pin Functions                               | 155 |

| 7.7  | Port 6   |                                             | 156 |

|      | 7.7.1    | Port 6 Data Direction Register (P6DDR)      |     |

|      | 7.7.2    | Port 6 Data Register (P6DR)                 |     |

|      | 7.7.3    | Port 6 Pull-Up MOS Control Register (KMPCR) | 157 |

|      | 7.7.4    | System Control Register 2 (SYSCR2)          | 158 |

|      | 7.7.5   | Pin Functions                                   | 159 |

|------|---------|-------------------------------------------------|-----|

|      | 7.7.6   | Port 6 Input Pull-Up MOS                        | 161 |

| 7.8  | Port 7. |                                                 | 162 |

|      | 7.8.1   | Port 7 Input Data Register (P7PIN)              | 162 |

|      | 7.8.2   | Pin Functions                                   | 162 |

| 7.9  | Port 8. |                                                 | 164 |

|      | 7.9.1   | Port 8 Data Direction Register (P8DDR)          | 164 |

|      | 7.9.2   | Port 8 Data Register (P8DR)                     | 165 |

|      | 7.9.3   | Pin Functions                                   | 165 |

| 7.10 | Port 9. |                                                 | 167 |

|      | 7.10.1  | Port 9 Data Direction Register (P9DDR)          | 168 |

|      | 7.10.2  | Port 9 Data Register (P9DR)                     | 169 |

|      | 7.10.3  | Pin Functions                                   | 169 |

| 7.11 | Port A  | (Only for H8S/2144B)                            | 172 |

|      | 7.11.1  | Port A Data Direction Register (PADDR)          | 172 |

|      | 7.11.2  | Port A Output Data Register (PAODR)             | 173 |

|      |         | Port A Input Data Register (PAPIN)              |     |

|      | 7.11.4  | Pin Functions                                   | 174 |

|      | 7.11.5  | Port A Input Pull-Up MOS                        | 178 |

| 7.12 | Port B  | (Only for H8S/2144B)                            | 179 |

|      |         | Port B Data Direction Register (PBDDR)          |     |

|      | 7.12.2  | Port B Output Data Register (PBODR)             |     |

|      | 7.12.3  | 3                                               |     |

|      | 7.12.4  |                                                 |     |

|      | 7.12.5  | Port B Input Pull-Up MOS                        | 181 |

| Sect | ion 8 1 | 4-Bit PWM Timer (PWMX)                          | 183 |

| 8.1  |         | es                                              |     |

| 8.2  | Input/C | Output Pins                                     | 184 |

| 8.3  | Registe | er Descriptions                                 | 184 |

|      | 8.3.1   | PWM (D/A) Counters H and L (DACNTH, DACNTL)     | 184 |

|      | 8.3.2   | PWM (D/A) Data Registers A and B (DADRA, DADRB) | 186 |

|      | 8.3.3   | PWM (D/A) Control Register (DACR)               | 188 |

| 8.4  | Bus M   | aster Interface                                 | 189 |

| 8.5  | Operat  | ion                                             | 190 |

| 8.6  | Usage   | Note                                            | 196 |

|      | 8.6.1   | Module Stop Mode Setting                        | 196 |

| Sect | ion 9 1 | 6-Bit Free-Running Timer (FRT)                  | 197 |

|      | Foature |                                                 |     |

| 9.2  | Input/C | Output Pins                                       | 199 |

|------|---------|---------------------------------------------------|-----|

| 9.3  | Registe | er Descriptions                                   | 199 |

|      | 9.3.1   | Free-Running Counter (FRC)                        | 200 |

|      | 9.3.2   | Output Compare Registers A and B (OCRA, OCRB)     | 200 |

|      | 9.3.3   | Input Capture Registers A to D (ICRA to ICRD)     | 200 |

|      | 9.3.4   | Output Compare Registers AR and AF (OCRAR, OCRAF) | 201 |

|      | 9.3.5   | Output Compare Register DM (OCRDM)                | 201 |

|      | 9.3.6   | Timer Interrupt Enable Register (TIER)            | 202 |

|      | 9.3.7   | Timer Control/Status Register (TCSR)              | 203 |

|      | 9.3.8   | Timer Control Register (TCR)                      | 206 |

|      | 9.3.9   | Timer Output Compare Control Register (TOCR)      | 207 |

| 9.4  | Operat  | ion                                               | 209 |

|      | 9.4.1   | Pulse Output                                      | 209 |

| 9.5  | Operat  | ion Timing                                        | 209 |

|      | 9.5.1   | FRC Increment Timing                              | 209 |

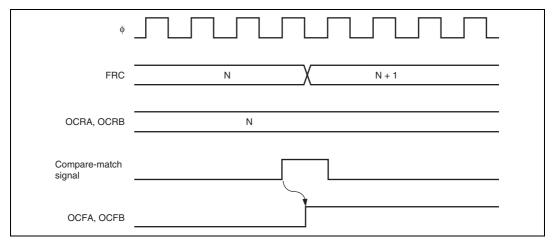

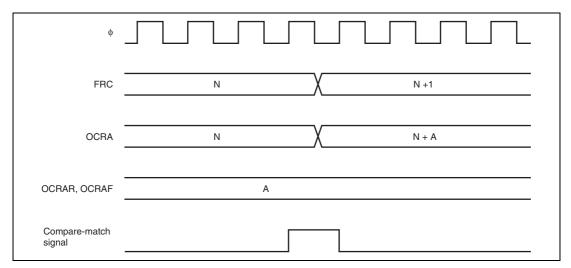

|      | 9.5.2   | Output Compare Output Timing                      | 210 |

|      | 9.5.3   | FRC Clear Timing                                  | 211 |

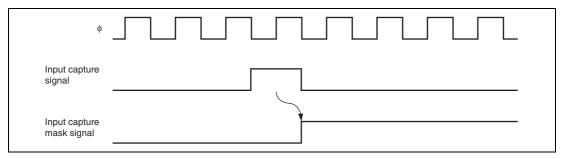

|      | 9.5.4   | Input Capture Input Timing                        | 211 |

|      | 9.5.5   | Buffered Input Capture Input Timing               | 212 |

|      | 9.5.6   | Timing of Input Capture Flag (ICF) Setting        | 214 |

|      | 9.5.7   | Timing of Output Compare Flag (OCF) setting       | 215 |

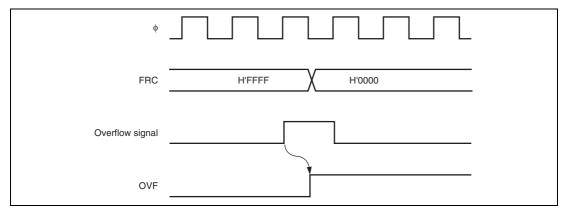

|      | 9.5.8   | Timing of FRC Overflow Flag Setting               | 216 |

|      | 9.5.9   | Automatic Addition Timing                         | 217 |

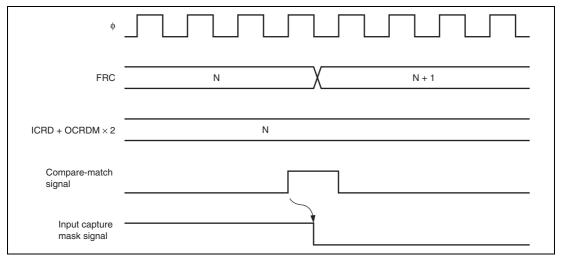

|      | 9.5.10  | Mask Signal Generation Timing                     | 218 |

| 9.6  | Interru | pt Sources                                        | 219 |

| 9.7  | Usage   | Notes                                             | 220 |

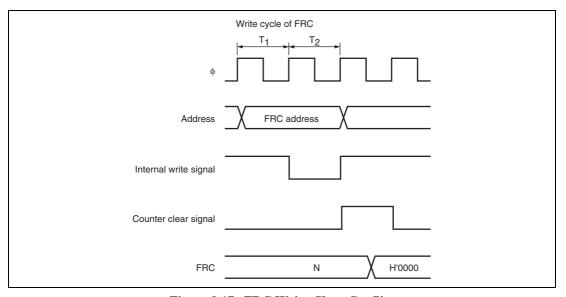

|      | 9.7.1   | Conflict between FRC Write and Clear              | 220 |

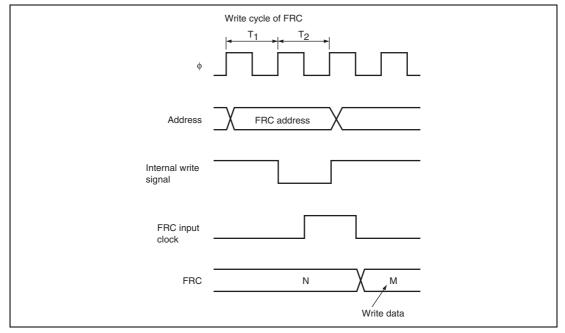

|      | 9.7.2   | Conflict between FRC Write and Increment          | 221 |

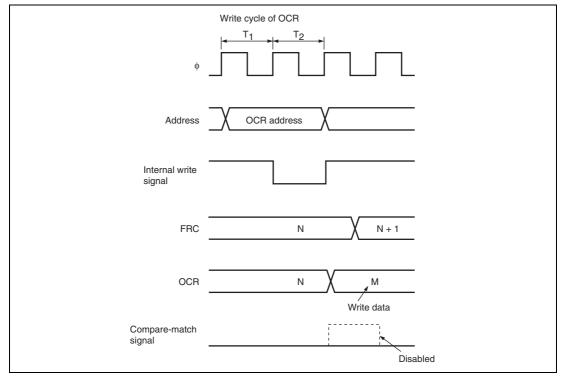

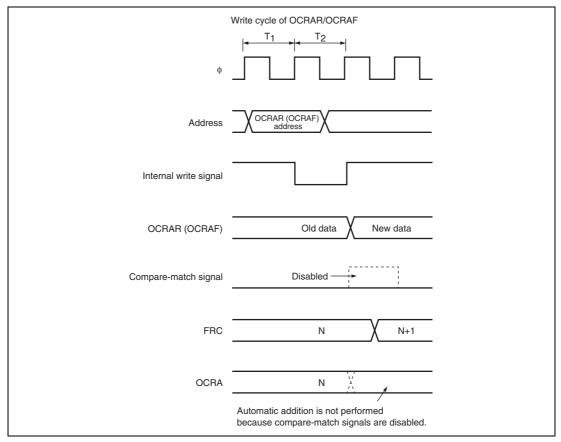

|      | 9.7.3   | Conflict between OCR Write and Compare-Match      | 221 |

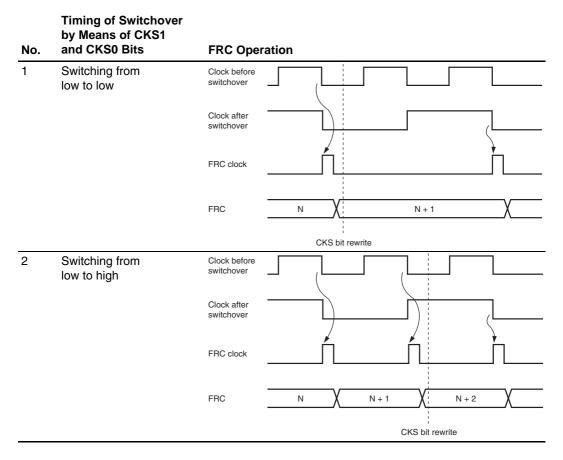

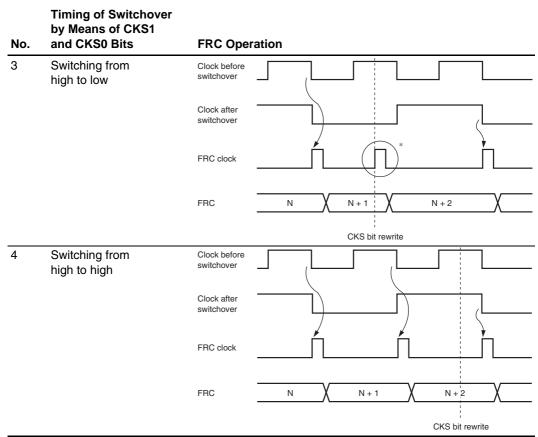

|      | 9.7.4   | Switching of Internal Clock and FRC Operation     | 224 |

|      | 9.7.5   | Module Stop Mode Setting                          | 225 |

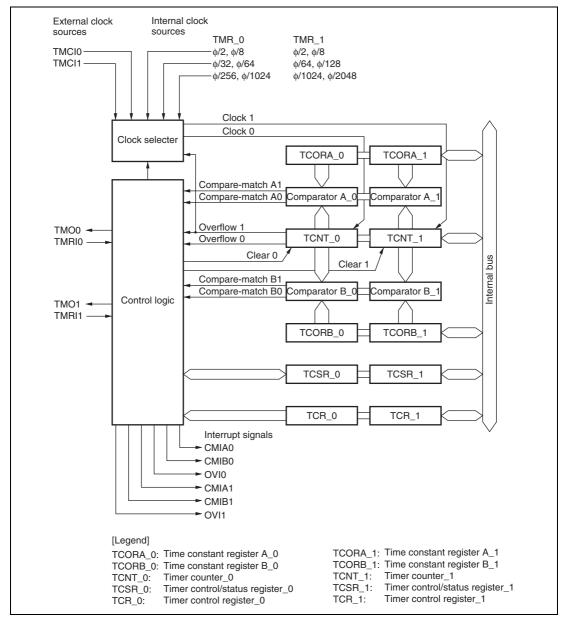

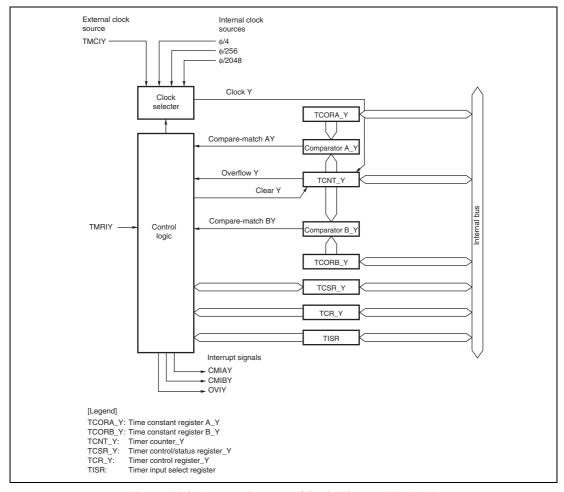

| Sect | ion 10  | 8-Bit Timer (TMR)                                 | 227 |

| 10.1 | Feature | es                                                | 227 |

| 10.2 | Input/C | Output Pins                                       | 230 |

| 10.3 | Registe | er Descriptions                                   | 230 |

|      | 10.3.1  | Timer Counter (TCNT)                              | 231 |

|      |         | Time Constant Register A (TCORA)                  |     |

|      | 10.3.3  |                                                   |     |

|      | 10.3.4  | Timer Control Register (TCR)                      | 232 |

|      | 10.3.5  | Timer Control/Status Register (TCSR)                          | 235 |

|------|---------|---------------------------------------------------------------|-----|

|      | 10.3.6  | Timer Input Select Register (TISR)                            | 240 |

| 10.4 | Operat  | ion                                                           | 240 |

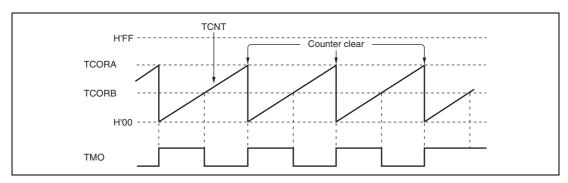

|      | 10.4.1  | Pulse Output                                                  | 240 |

| 10.5 | Operat  | ion Timing                                                    | 242 |

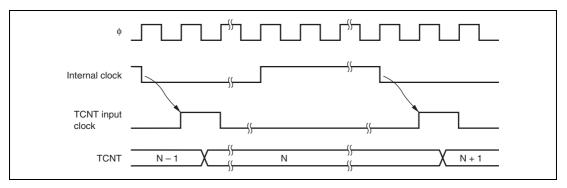

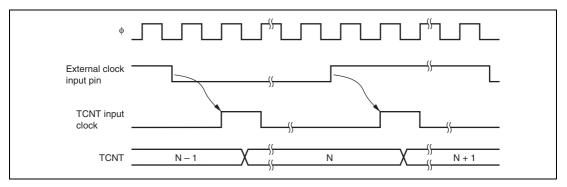

|      | 10.5.1  | TCNT Count Timing                                             | 242 |

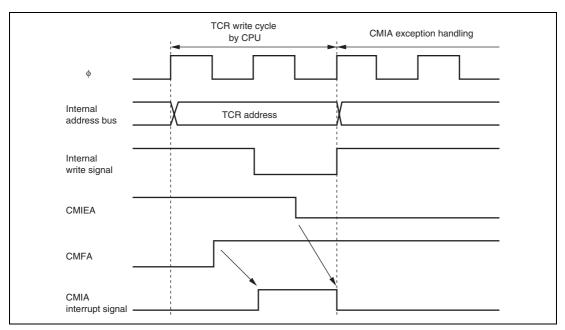

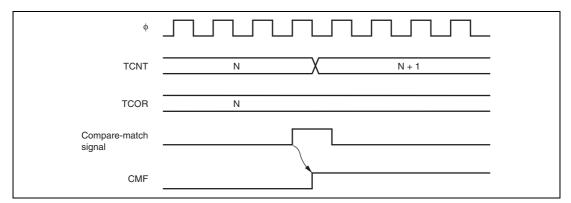

|      | 10.5.2  | Timing of CMFA and CMFB Setting at Compare-Match              | 243 |

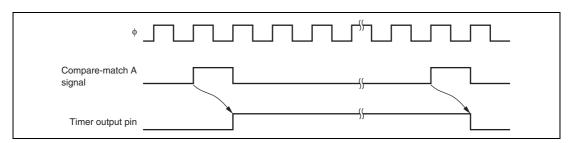

|      | 10.5.3  | Timing of Timer Output at Compare-Match                       | 243 |

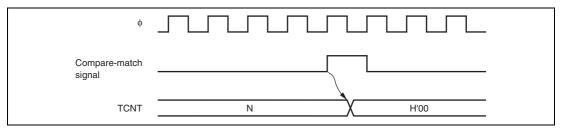

|      | 10.5.4  | Timing of Counter Clear at Compare-Match                      | 244 |

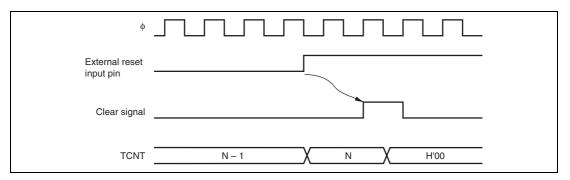

|      | 10.5.5  | TCNT External Reset Timing                                    | 244 |

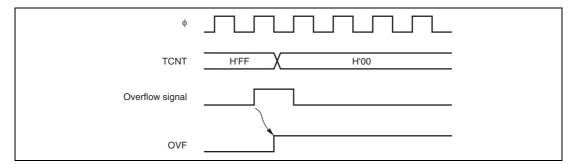

|      | 10.5.6  | Timing of Overflow Flag (OVF) Setting                         | 245 |

| 10.6 | Operat  | ion with Cascaded Connection                                  | 246 |

|      | 10.6.1  | 16-Bit Count Mode                                             | 246 |

|      | 10.6.2  | Compare-Match Count Mode                                      | 247 |

| 10.7 | Interru | pt Sources                                                    | 248 |

| 10.8 | Usage   | Notes                                                         | 249 |

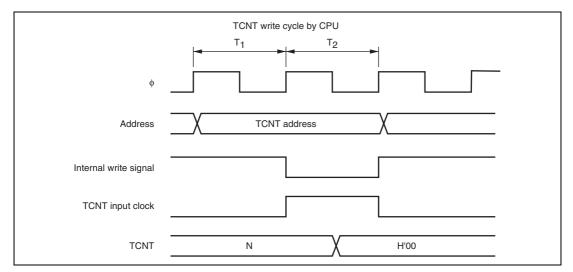

|      | 10.8.1  | Conflict between TCNT Write and Clear                         | 249 |

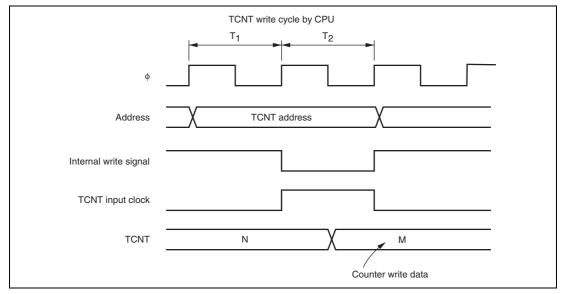

|      | 10.8.2  | Conflict between TCNT Write and Increment                     | 250 |

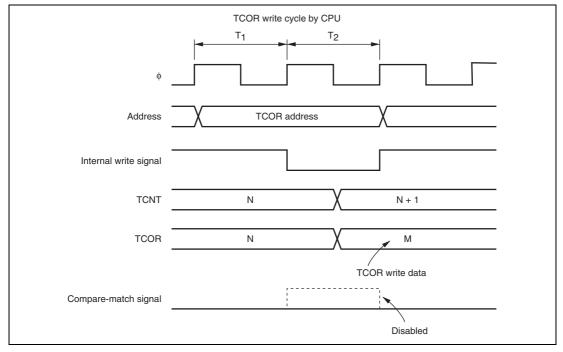

|      | 10.8.3  | Conflict between TCOR Write and Compare-Match                 | 251 |

|      | 10.8.4  | Conflict between Compare-Matches A and B                      | 252 |

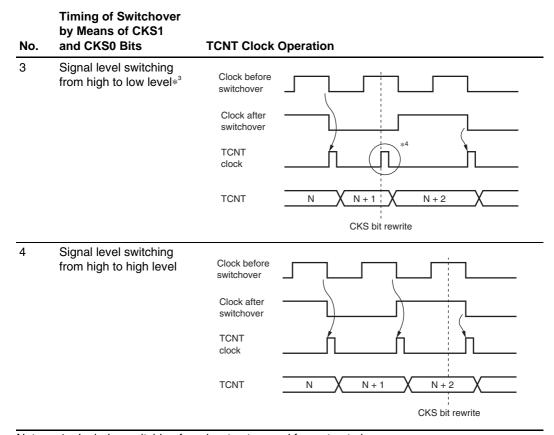

|      | 10.8.5  | Switching of Internal Clocks and TCNT Operation               | 252 |

|      | 10.8.6  | Mode Setting with Cascaded Connection                         | 254 |

|      | 10.8.7  | Module Stop Mode Setting                                      | 255 |

| _    |         |                                                               |     |

|      |         | Watchdog Timer (WDT)                                          |     |

| 11.1 |         | 28                                                            |     |

| 11.2 | -       | Output Pins                                                   |     |

| 11.3 | _       | er Descriptions                                               |     |

|      |         | Timer Counter (TCNT)                                          |     |

|      |         | Timer Control/Status Register (TCSR)                          |     |

| 11.4 |         | ion                                                           |     |

|      |         | Watchdog Timer Mode                                           |     |

|      |         | Interval Timer Mode                                           |     |

|      |         | RESO Signal Output Timing (Available for H8S/2144B)           |     |

| 11.5 |         | pt Sources                                                    |     |

| 11.6 | _       | Notes                                                         |     |

|      |         | Notes on Register Access                                      |     |

|      |         | Conflict between Timer Counter (TCNT) Write and Increment     |     |

|      | 11.6.3  | Changing Values of CKS2 to CKS0 Bits                          | 269 |

|      | 1164    | Switching between Watchdog Timer Mode and Interval Timer Mode | 269 |

|          | 11.6.5  | System Reset by RESO Signal (Available for H8S/2144B)             | 270 |

|----------|---------|-------------------------------------------------------------------|-----|

|          | 11.6.6  | Counter Values during Transitions between High-Speed, Sub-Active, |     |

|          |         | and Watch Modes                                                   | 270 |

| <b>C</b> | . 10    |                                                                   | 271 |

|          |         | Serial Communication Interface (SCI and IrDA)                     |     |

| 12.1     |         | 28                                                                |     |

| 12.2     | -       | Output Pins                                                       |     |

| 12.3     | _       | er Descriptions                                                   |     |

|          |         | Receive Shift Register (RSR)                                      |     |

|          |         | Receive Data Register (RDR)                                       |     |

|          |         | Transmit Data Register (TDR)                                      |     |

|          |         | Transmit Shift Register (TSR)                                     |     |

|          |         | Serial Mode Register (SMR)                                        |     |

|          | 12.3.6  | Serial Control Register (SCR)                                     |     |

|          | 12.3.7  | E ` '                                                             |     |

|          | 12.3.8  | Serial Interface Mode Register (SCMR)                             | 281 |

|          | 12.3.9  | Bit Rate Register (BRR)                                           | 282 |

|          | 12.3.10 | Keyboard Comparator Control Register (KBCOMP)                     | 289 |

| 12.4     | Operat  | ion in Asynchronous Mode                                          | 290 |

|          | 12.4.1  | Data Transfer Format                                              | 290 |

|          | 12.4.2  | Receive Data Sampling Timing and Reception Margin in              |     |

|          |         | Asynchronous Mode                                                 | 292 |

|          | 12.4.3  | Clock                                                             | 293 |

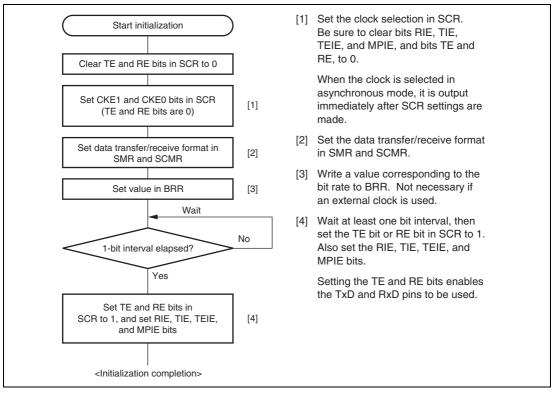

|          | 12.4.4  | SCI Initialization (Asynchronous Mode)                            | 294 |

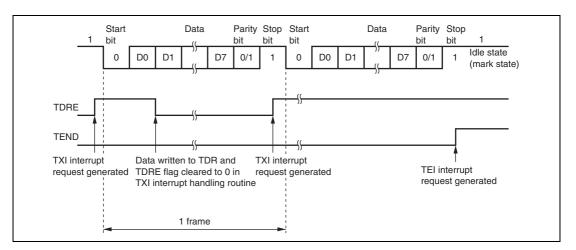

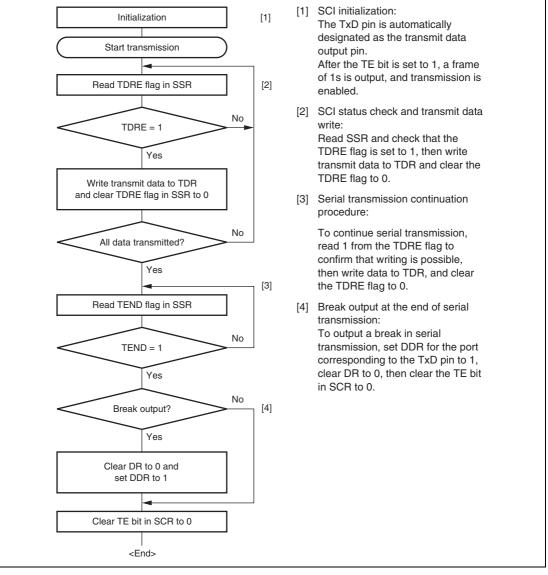

|          | 12.4.5  | Data Transmission (Asynchronous Mode)                             | 295 |

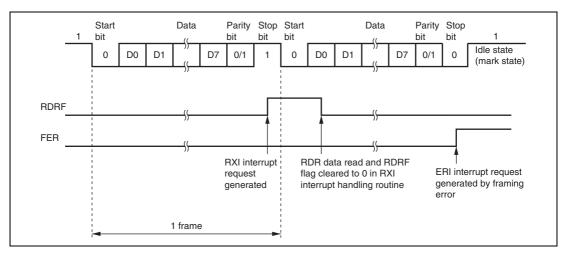

|          |         | Serial Data Reception (Asynchronous Mode)                         |     |

| 12.5     |         | rocessor Communication Function                                   |     |

|          | -       | Multiprocessor Serial Data Transmission                           |     |

|          |         | Multiprocessor Serial Data Reception                              |     |

| 12.6     |         | ion in Clock Synchronous Mode                                     |     |

|          | -       | Clock                                                             |     |

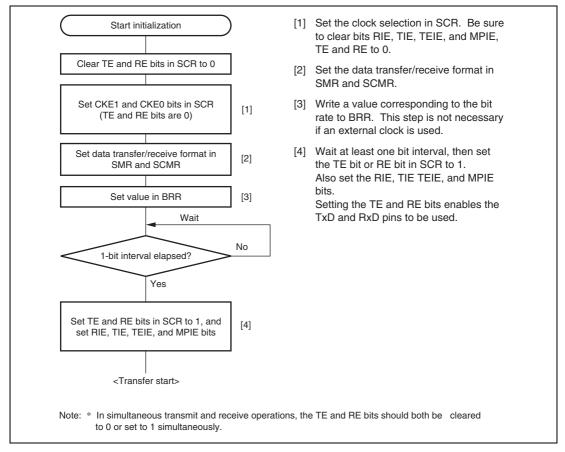

|          |         | SCI Initialization (Clock Synchronous Mode)                       |     |

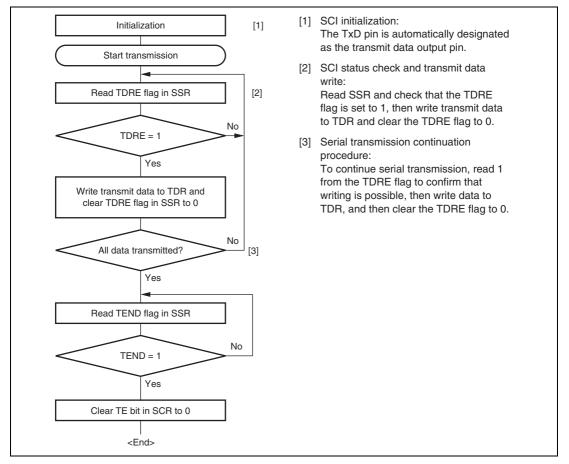

|          | 12.6.3  | •                                                                 |     |

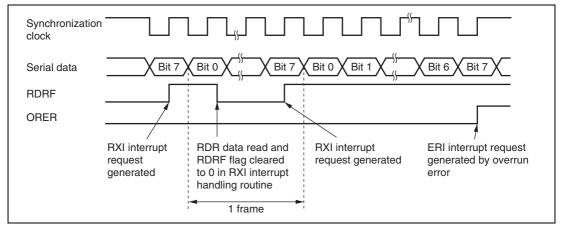

|          | 12.6.4  | Serial Data Reception (Clock Synchronous Mode)                    |     |

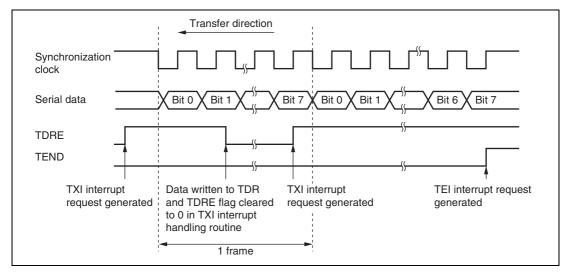

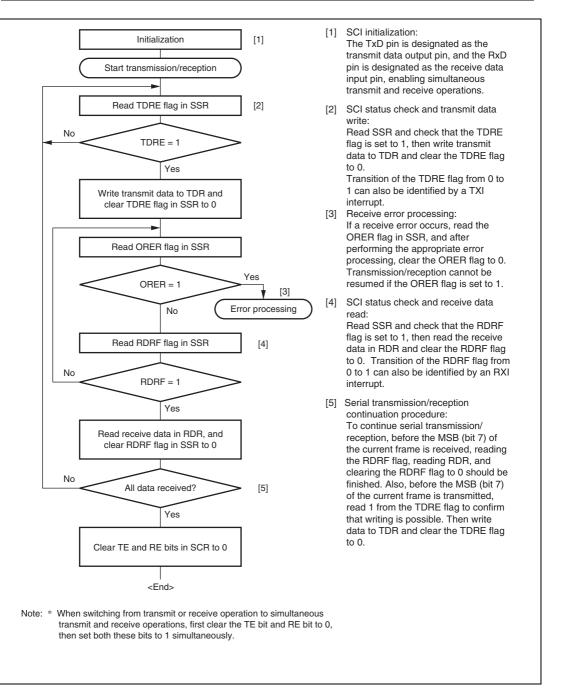

|          | 12.6.5  | Simultaneous Serial Data Transmission and Reception               |     |

|          |         | (Clock Synchronous Mode)                                          | 316 |

| 12.7     | IrDA C  | Operation                                                         |     |

| 12.8     |         | pt Sources                                                        |     |

| 12.9     |         | Notes                                                             |     |

|          | _       | Module Ston Mode Setting                                          |     |

|      | 12.9.2   | Break Detection and Processing                      | 322 |

|------|----------|-----------------------------------------------------|-----|

|      | 12.9.3   | Mark State and Break Detection                      | 322 |

|      | 12.9.4   | Receive Error Flags and Transmit Operations         |     |

|      |          | (Clock Synchronous Mode Only)                       | 322 |

|      | 12.9.5   | Relation between Writing to TDR and TDRE Flag       | 322 |

|      | 12.9.6   | SCI Operations during Mode Transitions              | 323 |

|      | 12.9.7   | Notes on Switching from SCK Pins to Port Pins       | 327 |

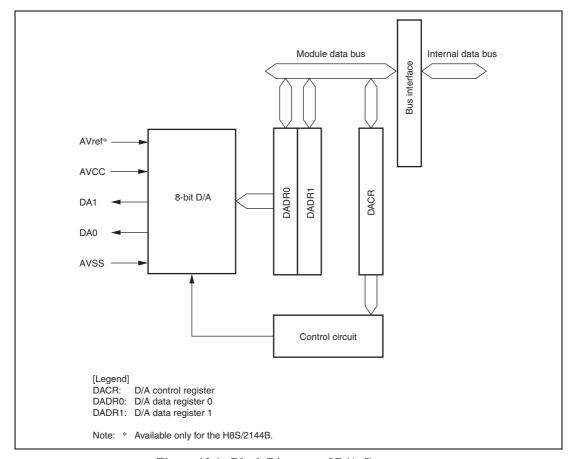

| Sect | ion 13   | D/A Converter                                       | 329 |

| 13.1 | Feature  | es                                                  | 329 |

| 13.2 | Input/C  | Output Pins                                         | 330 |

| 13.3 | Registe  | er Descriptions                                     | 330 |

|      | 13.3.1   | D/A Data Registers 0 and 1 (DADR0, DADR1)           | 330 |

|      | 13.3.2   | D/A Control Register (DACR)                         | 331 |

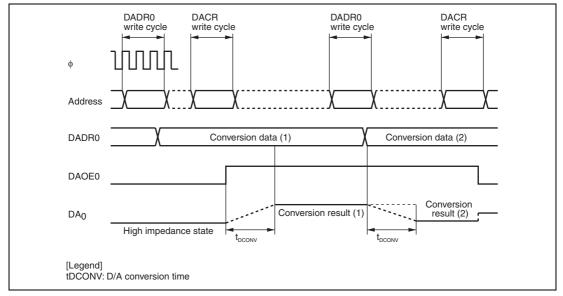

| 13.4 | Operat   | ion                                                 | 332 |

| 13.5 | Usage    | Note                                                | 333 |

|      | 13.5.1   | Module Stop Mode Setting                            | 333 |

| Sect | ion 14 . | A/D Converter                                       | 335 |

| 14.1 | Feature  | es                                                  | 335 |

| 14.2 | Input/C  | Output Pins                                         | 337 |

| 14.3 | Registe  | er Descriptions                                     | 338 |

|      | 14.3.1   | A/D Data Registers A to D (ADDRA to ADDRD)          | 338 |

|      |          | A/D Control/Status Register (ADCSR)                 |     |

|      |          | A/D Control Register (ADCR)                         |     |

|      |          | Keyboard Comparator Control Register (KBCOMP)       |     |

| 14.4 |          | ion                                                 |     |

|      | 14.4.1   | Single Mode                                         | 343 |

|      |          | Scan Mode                                           |     |

|      | 14.4.3   | Input Sampling and A/D Conversion Time              | 345 |

|      |          | External Trigger Input Timing                       |     |

| 14.5 |          | pt Sources                                          |     |

| 14.6 |          | onversion Accuracy Definitions                      |     |

| 14.7 |          | Notes                                               |     |

|      |          | Permissible Signal Source Impedance                 |     |

|      |          | Influences on Absolute Accuracy                     |     |

|      |          | Setting Range of Analog Power Supply and Other Pins |     |

|      |          | Notes on Board Design                               |     |

|      |          | Notes on Noise Countermeasures                      |     |

|      |          | Module Stop Mode Setting                            | 352 |

| Secti | Section 15 RAM |                                             |     |

|-------|----------------|---------------------------------------------|-----|

| Secti | on 16          | ROM                                         | 355 |

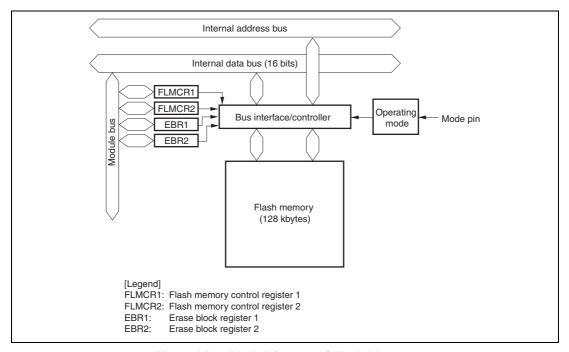

| 16.1  | Feature        | es                                          | 355 |

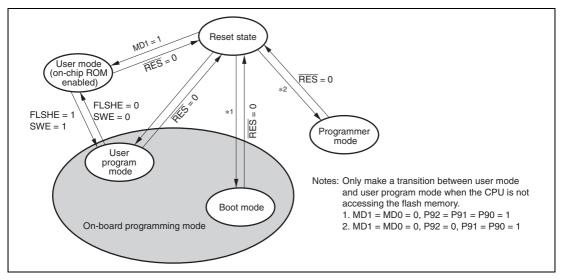

| 16.2  | Mode '         | Transitions                                 | 357 |

| 16.3  | Block          | Configuration                               | 360 |

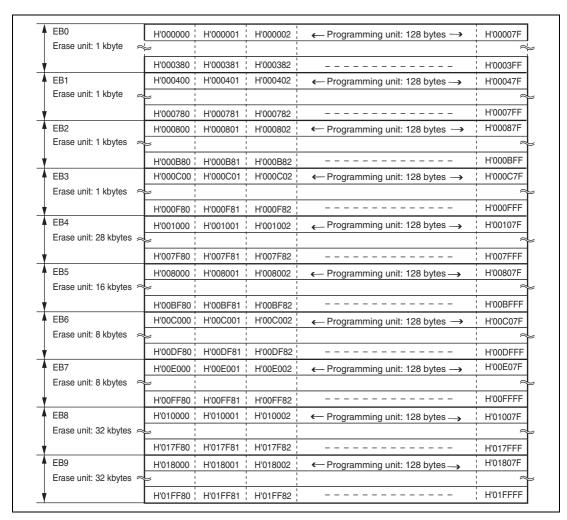

|       | 16.3.1         | Block Configuration                         | 360 |

| 16.4  | Input/C        | Output Pins                                 | 361 |

| 16.5  | Registe        | er Descriptions                             | 361 |

|       | 16.5.1         | Flash Memory Control Register 1 (FLMCR1)    | 362 |

|       | 16.5.2         | Flash Memory Control Register 2 (FLMCR2)    | 363 |

|       | 16.5.3         | Erase Block Registers 1 and 2 (EBR1, EBR2)  | 364 |

| 16.6  | Operat         | ing Modes                                   | 365 |

| 16.7  | On-Bo          | ard Programming Modes                       | 366 |

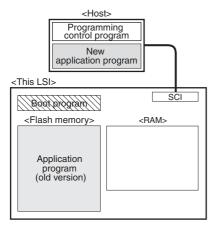

|       | 16.7.1         | Boot Mode                                   | 366 |

|       |                | User Program Mode                           |     |

| 16.8  |                | Memory Programming/Erasing                  |     |

|       | 16.8.1         | Programming/Programming-Verifying           | 371 |

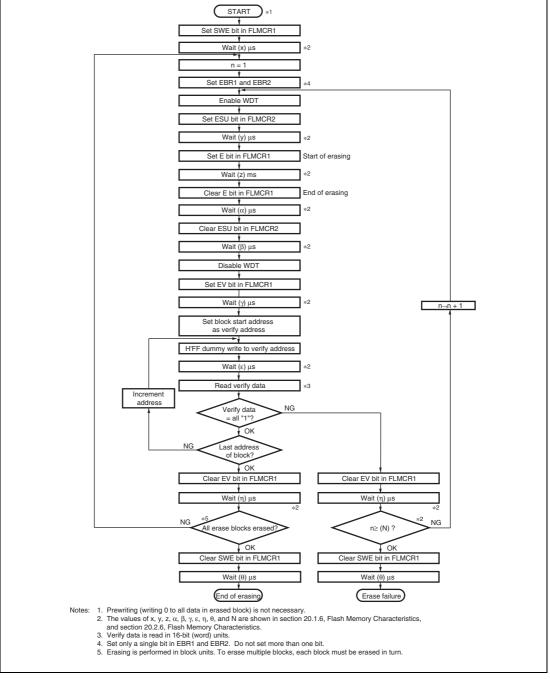

|       |                | Erasing/Erasing-Verifying                   |     |

| 16.9  | Progra         | mming/Eraseing Protection                   | 376 |

|       |                | Hardware Protection                         |     |

|       | 16.9.2         | Software Protection                         | 376 |

|       |                | Error Protection                            |     |

|       |                | pts during Flash Memory Programming/Erasing |     |

|       | _              | mmer Mode                                   |     |

| 16.12 | Usage          | Notes                                       | 378 |

| Secti | on 17          | Clock Pulse Generator                       | 381 |

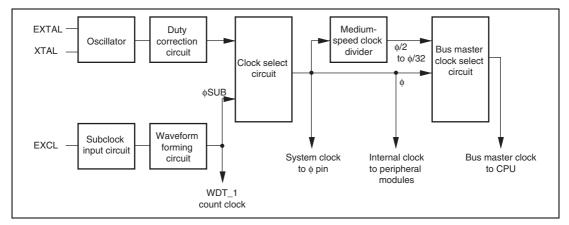

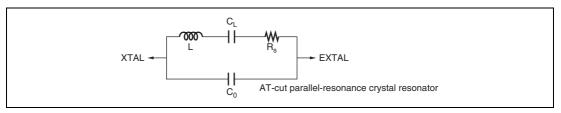

| 17.1  | Oscilla        | itor                                        | 382 |

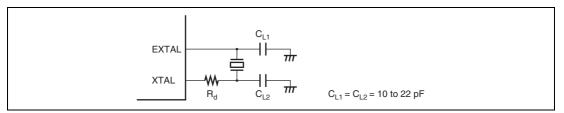

|       | 17.1.1         | Connecting Crystal Resonator                | 382 |

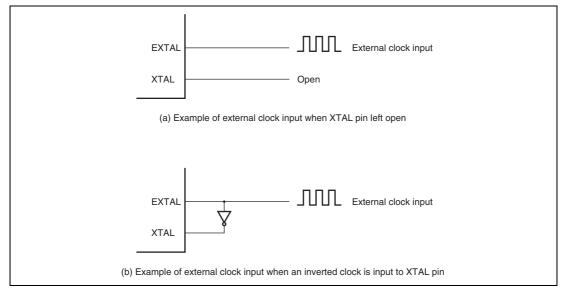

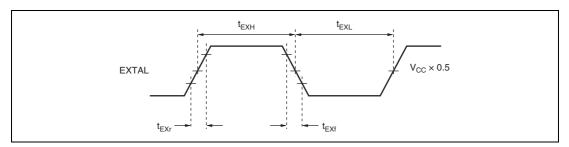

|       | 17.1.2         | External Clock Input Method                 | 383 |

| 17.2  |                | Correction Circuit                          |     |

| 17.3  | Mediu          | m-Speed Clock Divider                       | 386 |

| 17.4  |                | aster Clock Select Circuit                  |     |

| 17.5  |                | ck Input Circuit                            |     |

| 17.6  |                | ck Waveform Forming Circuit                 |     |

| 17.7  |                | Select Circuit                              |     |

| 17.8  |                | Notes                                       |     |

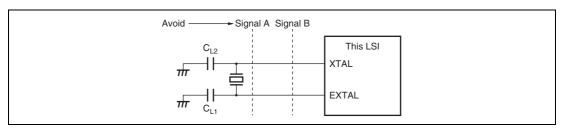

|       | 17.8.1         | Note on Resonator                           | 388 |

|       | 17.8.2         | Notes on Board Design                       | 388 |

| Secti | on 18 Power-Down Modes                                                     | 389 |

|-------|----------------------------------------------------------------------------|-----|

| 18.1  | Register Descriptions                                                      | 389 |

|       | 18.1.1 Standby Control Register (SBYCR)                                    | 390 |

|       | 18.1.2 Low-Power Control Register (LPWRCR)                                 | 392 |

|       | 18.1.3 Module Stop Control Registers H and L (MSTPCRH, MSTPCRL)            | 393 |

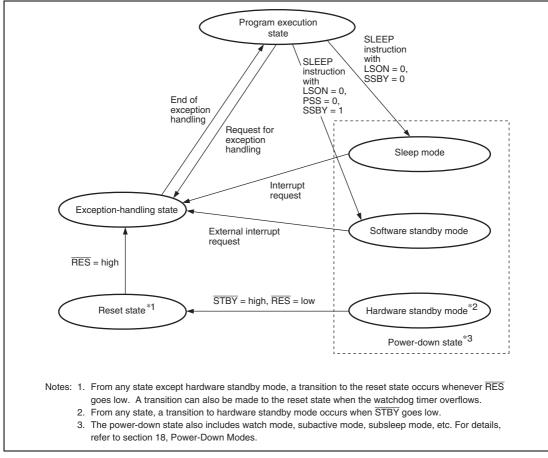

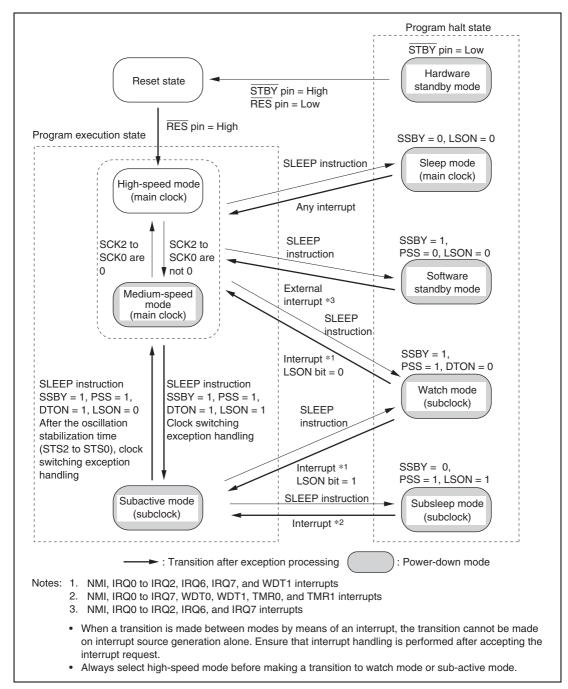

| 18.2  | Mode Transitions and LSI States                                            | 394 |

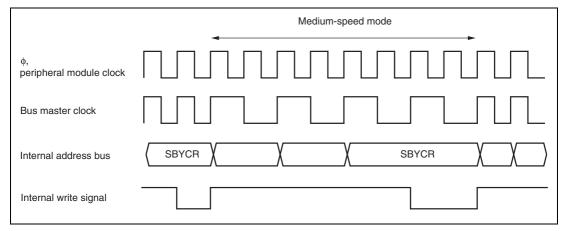

| 18.3  | Medium-Speed Mode                                                          | 397 |

| 18.4  | Sleep Mode                                                                 | 398 |

| 18.5  | Software Standby Mode                                                      | 399 |

| 18.6  | Hardware Standby Mode                                                      | 401 |

| 18.7  | Watch Mode                                                                 | 402 |

| 18.8  | Subsleep Mode                                                              | 403 |

| 18.9  | Subactive Mode                                                             |     |

|       | Module Stop Mode                                                           |     |

|       | Direct Transitions                                                         |     |

| 18.12 | Usage Notes                                                                |     |

|       | 18.12.1 I/O Port Status                                                    |     |

|       | 18.12.2 Current Consumption while Waiting for Oscillation to be Stabilized | 406 |

| Secti | on 19 List of Registers                                                    | 407 |

| 19.1  | Register Addresses (Address Order)                                         | 408 |

| 19.2  | Register Bits                                                              | 414 |

| 19.3  | Register States in Each Operating Mode                                     | 419 |

| 19.4  | Register Select Conditions                                                 | 424 |

| Secti | on 20 Electrical Characteristics                                           | 431 |

| 20.1  | Electrical Characteristics of H8S/2144B.                                   |     |

|       | 20.1.1 Absolute Maximum Ratings                                            |     |

|       | 20.1.2 DC Characteristics                                                  |     |

|       | 20.1.3 AC Characteristics                                                  | 441 |

|       | 20.1.4 A/D Conversion Characteristics                                      | 460 |

|       | 20.1.5 D/A Conversion Characteristics                                      | 462 |

|       | 20.1.6 Flash Memory Characteristics                                        | 463 |

|       | 20.1.7 Usage Note                                                          |     |

| 20.2  | Electrical Characteristics of H8S/2134B                                    | 466 |

|       | 20.2.1 Absolute Maximum Ratings                                            | 466 |

|       | 20.2.2 DC Characteristics                                                  | 467 |

|       | 20.2.3 AC Characteristics                                                  |     |

|       | 20.2.4 A/D Conversion Characteristics                                      | 493 |

|       | 20.2.5 D/A Conversion Characteristics                                      | 495 |

|     | 20.2.6 Flash Memory Characteristics      | 496 |

|-----|------------------------------------------|-----|

|     | 20.2.7 Usage Note                        |     |

| Ap  | ppendix                                  | 499 |

|     | I/O Port States in Each Processing State |     |

|     | Product Codes                            |     |

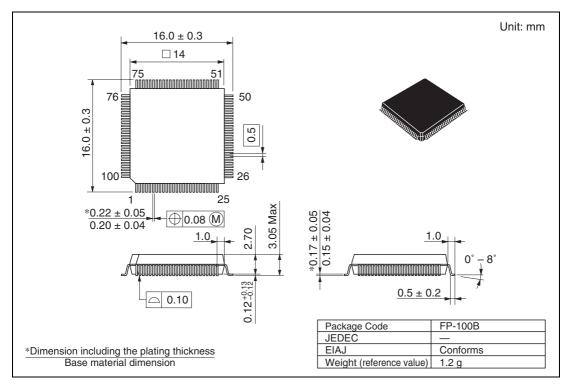

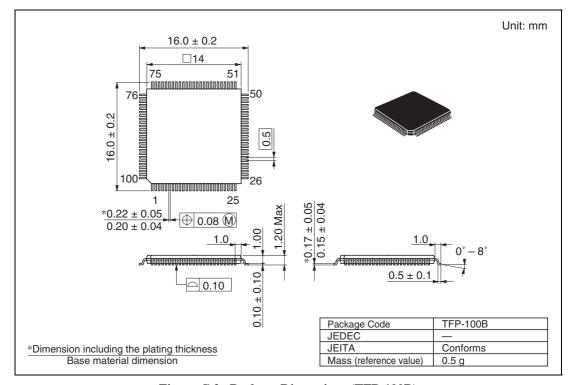

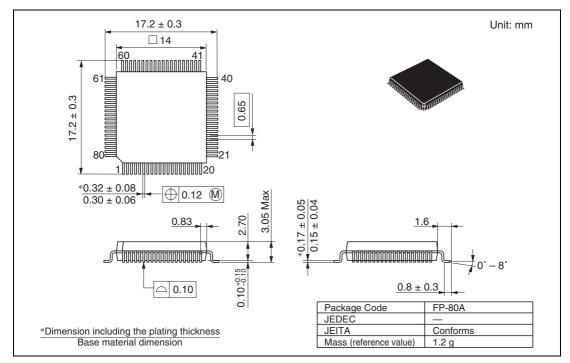

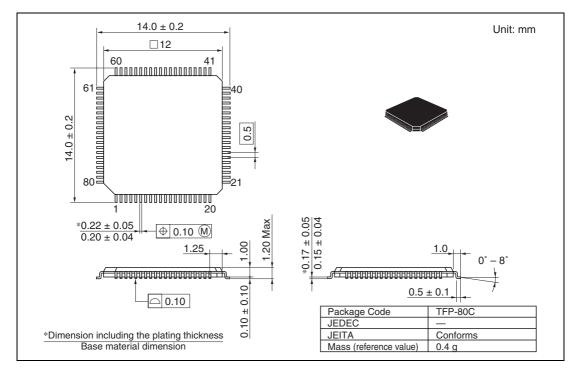

|     | Package Dimensions                       |     |

| Ind | dex                                      | 507 |

# Figures

| Section 1   | Overview                                                                                                |    |

|-------------|---------------------------------------------------------------------------------------------------------|----|

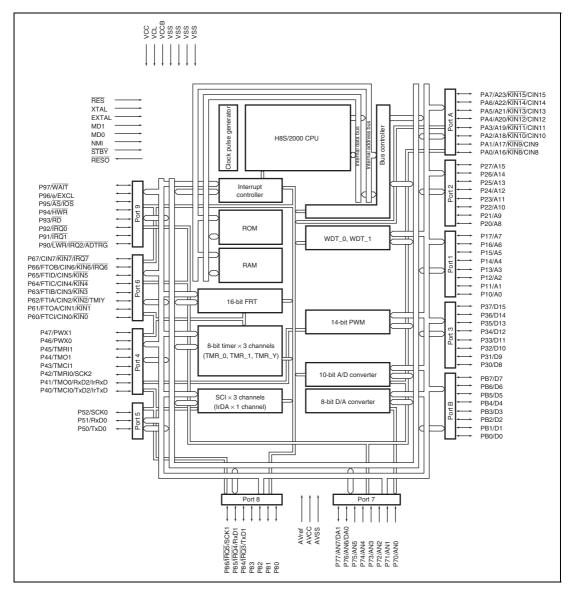

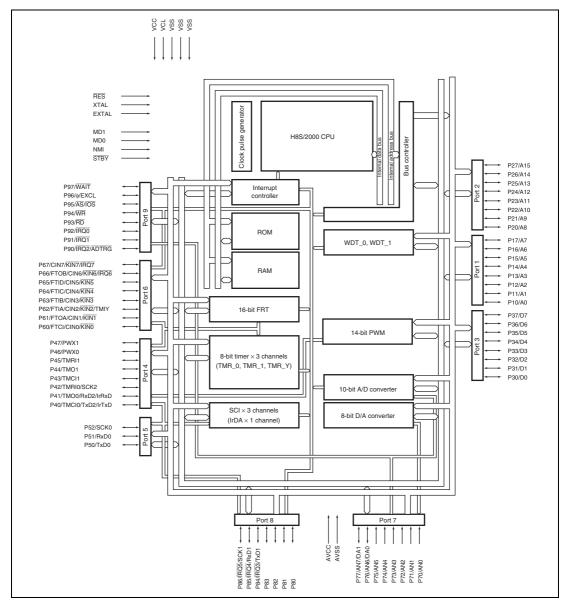

| Figure 1.1  | Block Diagram of H8S/2144B                                                                              | 3  |

| Figure 1.2  | Block Diagram of H8S/2134B                                                                              | 4  |

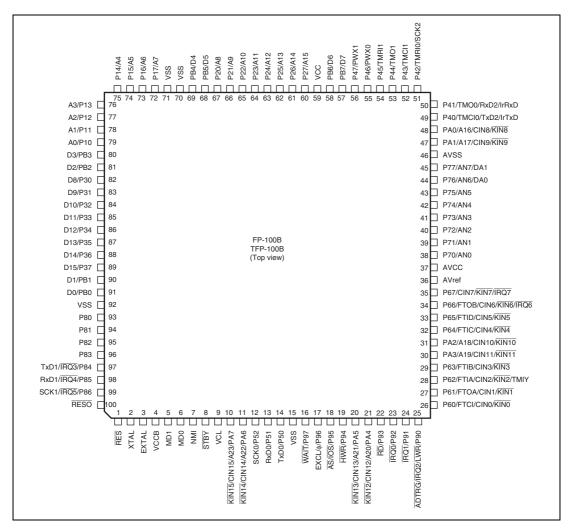

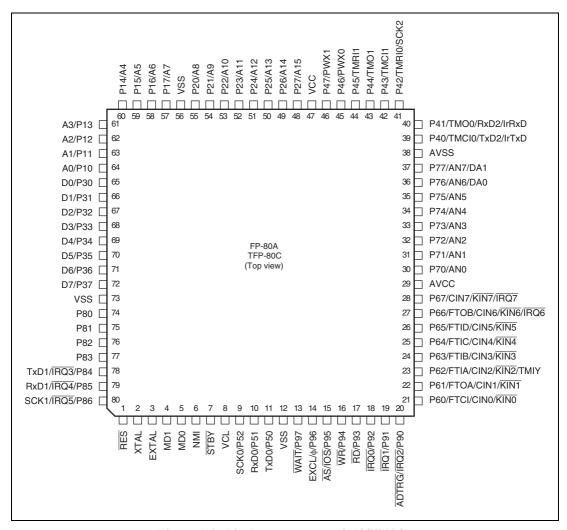

| Figure 1.3  | Pin Arrangements of H8S/2144B                                                                           | 5  |

| Figure 1.4  | Pin Arrangements of H8S/2134B                                                                           | 6  |

| Section 2 ( | CPU                                                                                                     |    |

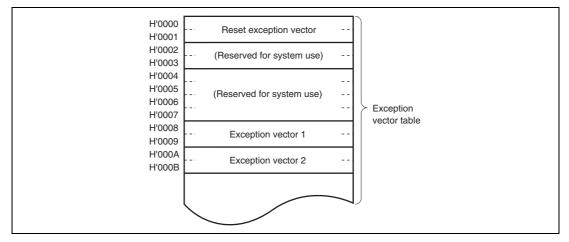

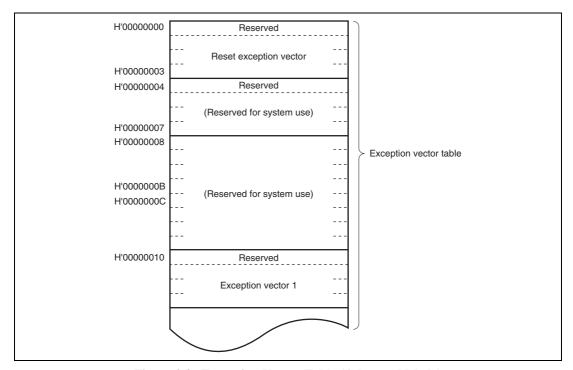

|             | Exception Vector Table (Normal Mode)                                                                    |    |

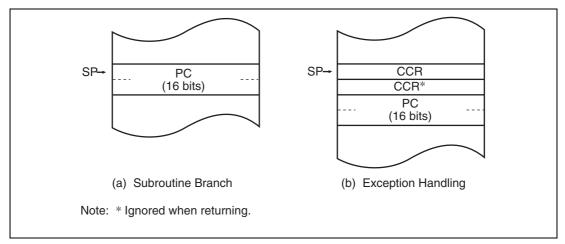

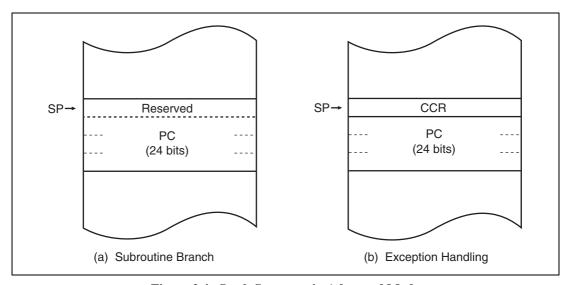

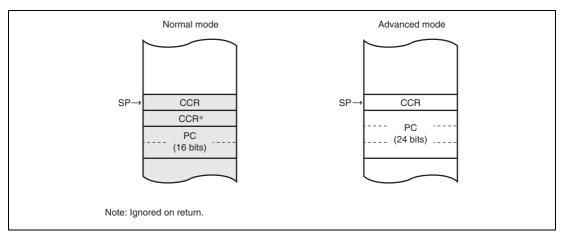

| -           | Stack Structure in Normal Mode                                                                          |    |

|             | Exception Vector Table (Advanced Mode)                                                                  |    |

| Figure 2.4  | Stack Structure in Advanced Mode                                                                        | 25 |

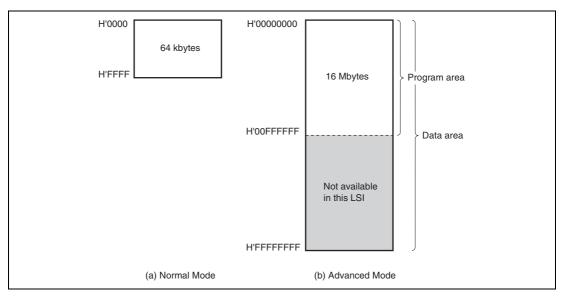

| Figure 2.5  | Memory Map                                                                                              | 26 |

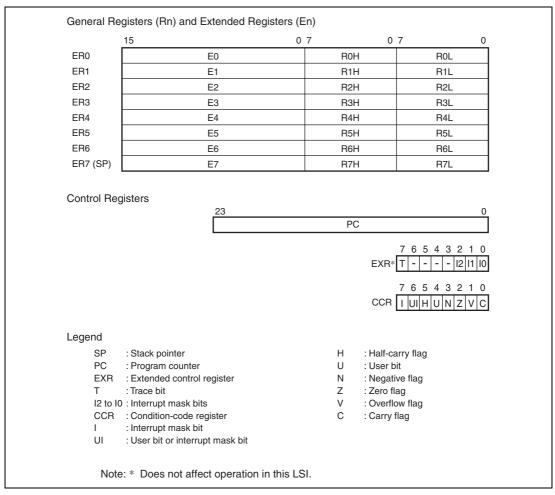

| Figure 2.6  | CPU Internal Registers                                                                                  | 27 |

| Figure 2.7  | Usage of General Registers                                                                              | 28 |

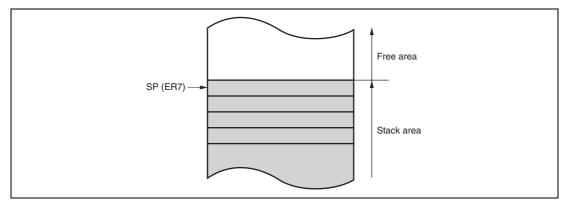

| Figure 2.8  | Stack                                                                                                   | 29 |

| Figure 2.9  | General Register Data Formats (1)                                                                       | 32 |

| Figure 2.9  | General Register Data Formats (2)                                                                       | 33 |

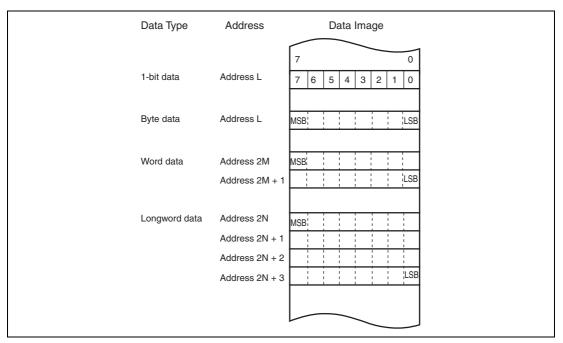

| Figure 2.10 | Memory Data Formats                                                                                     | 34 |

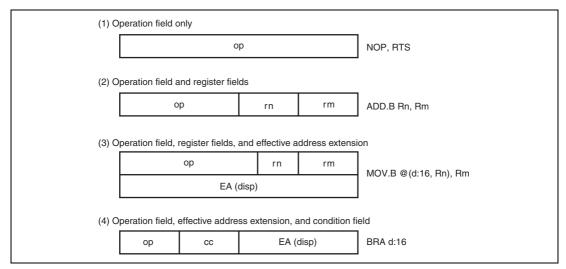

| Figure 2.11 | Instruction Formats (Examples)                                                                          | 47 |

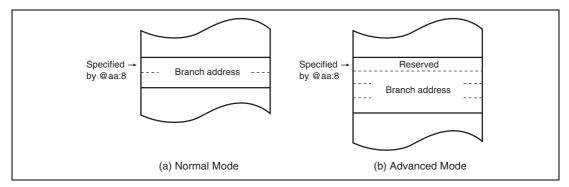

| Figure 2.12 | Branch Address Specification in Memory Indirect Addressing Mode                                         | 51 |

| Figure 2.13 | State Transitions                                                                                       | 55 |

| Section 3 N | ACU Operating Modes                                                                                     |    |

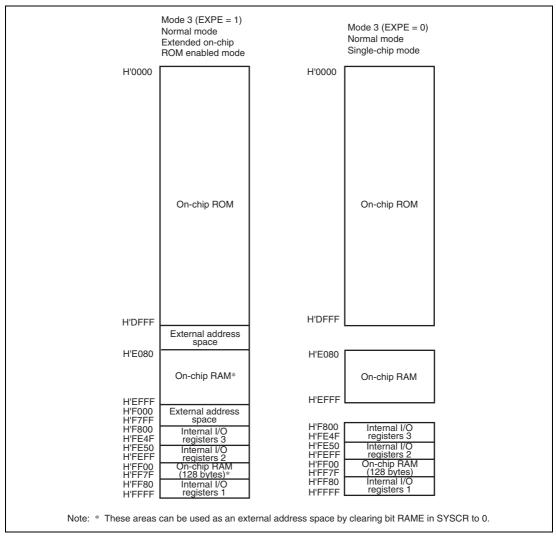

| -           | Address Map (1)                                                                                         |    |

| Figure 3.2  | Address Map (2)                                                                                         | 68 |

|             | Exception Handling                                                                                      |    |

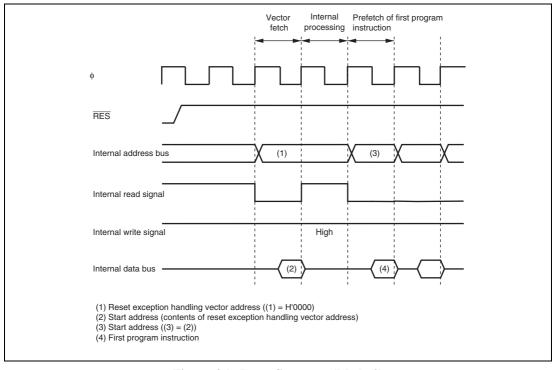

| Figure 4.1  | Reset Sequence (Mode 3)                                                                                 | 72 |

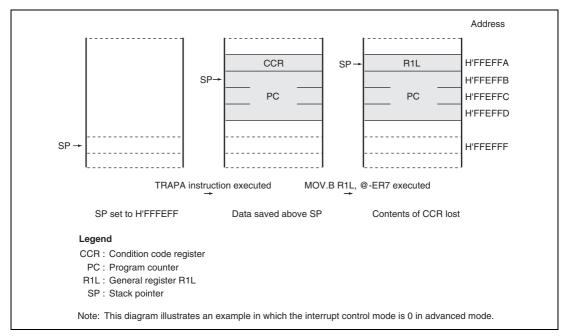

| -           | Stack Status after Exception Handling                                                                   |    |

| Figure 4.3  | Operation when SP Value is Odd                                                                          | 75 |

|             | nterrupt Controller                                                                                     |    |

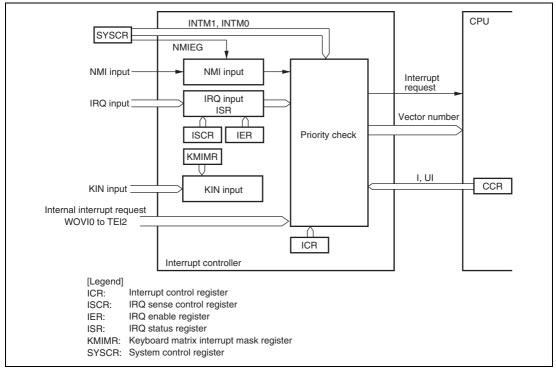

| -           | Block Diagram of Interrupt Controller                                                                   | 78 |

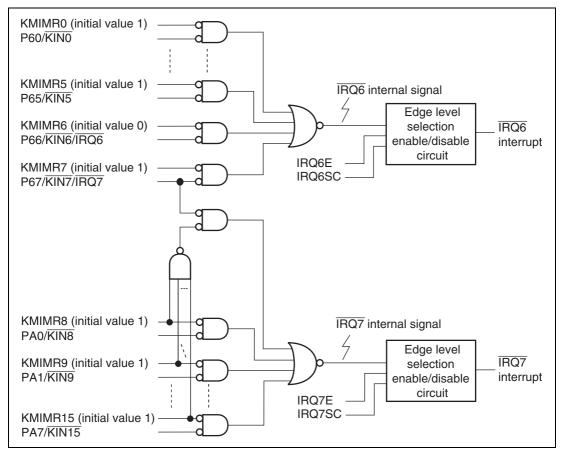

| Figure 5.2  | Relationship between Interrupts IRQ7 and IRQ6, Interrupts KIN15 to KIN0, and Registers KMIMR and KMIMRA | 86 |

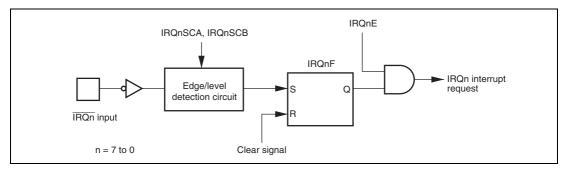

| Figure 5.3  | Block Diagram of Interrupts IRQ7 to IRQ0                                                                |    |

|             | Flowchart of Procedure up to Interrupt Acceptance in Interrupt Control Mode 0                           |    |

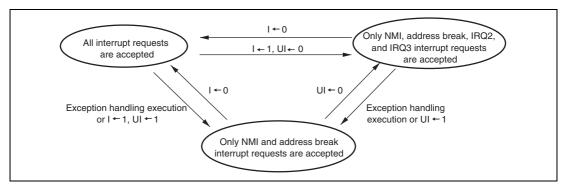

| -           | State Transition in Interrupt Control Mode 1                                                            |    |

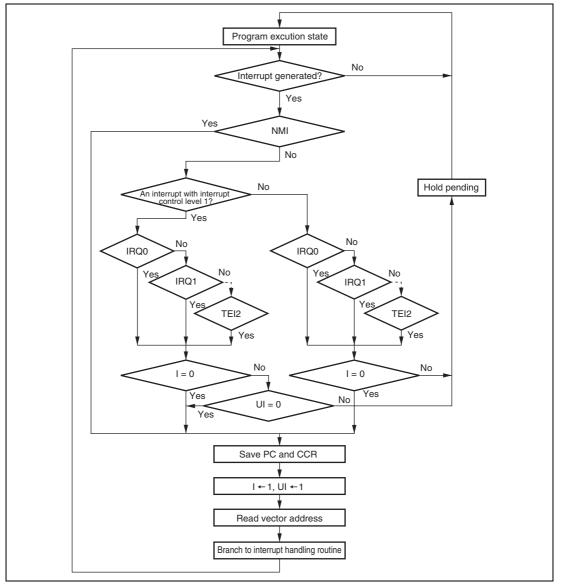

| -           | Flowchart of Procedure Up to Interrupt Acceptance in Interrupt Control Mode 1                           |    |

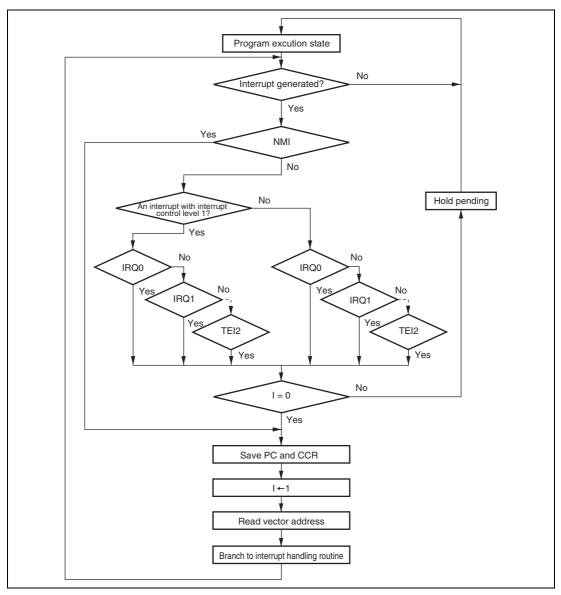

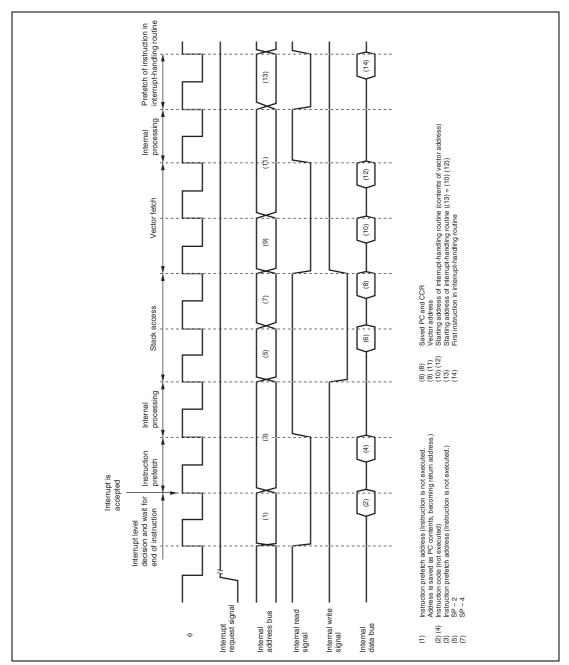

| Figure 5.7  | Interrupt Exception Handling                                   | 99  |

|-------------|----------------------------------------------------------------|-----|

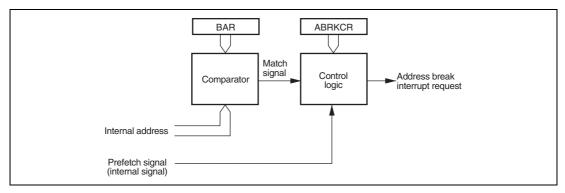

| Figure 5.8  | Address Break Block Diagram                                    | 101 |

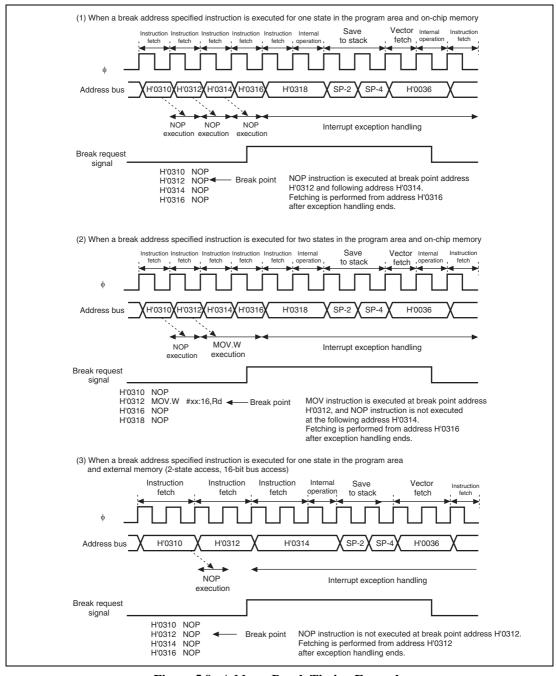

| Figure 5.9  | Address Break Timing Example                                   | 103 |

| Figure 5.10 | Conflict between Interrupt Generation and Disabling            | 104 |

| Section 6 I | Bus Controller (BSC)                                           |     |

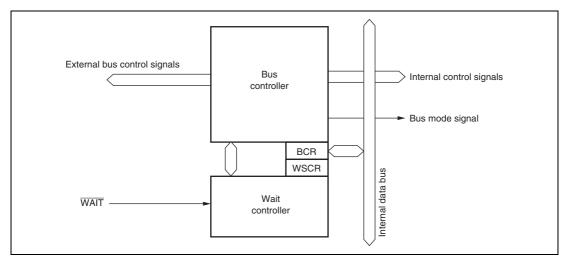

| Figure 6.1  | Block Diagram of Bus Controller                                | 107 |

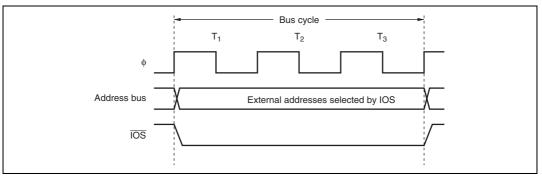

| Figure 6.2  | TOS Signal Output Timing                                       | 114 |

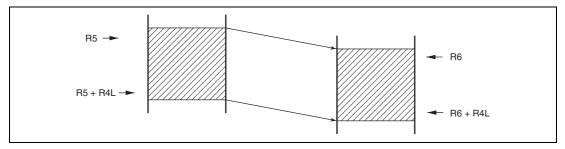

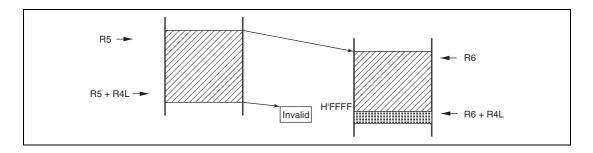

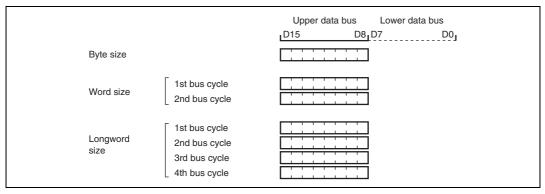

| Figure 6.3  | Access Sizes and Data Alignment Control (8-Bit Access Space)   | 116 |

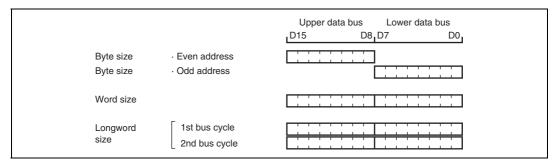

| Figure 6.4  | Access Sizes and Data Alignment Control (16-bit Access Space)  | 117 |

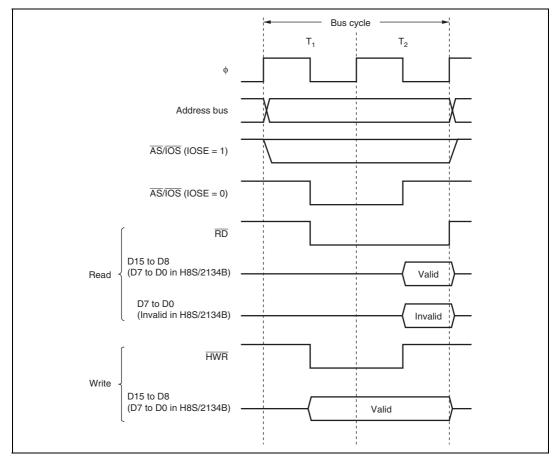

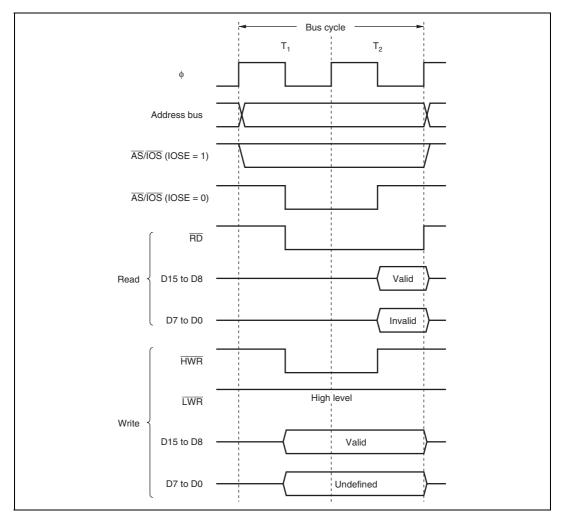

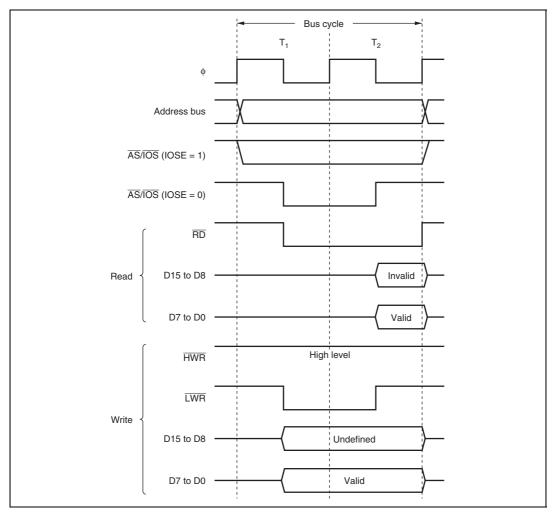

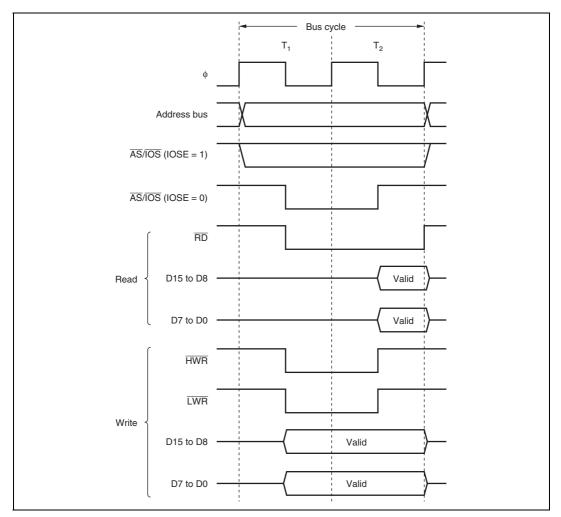

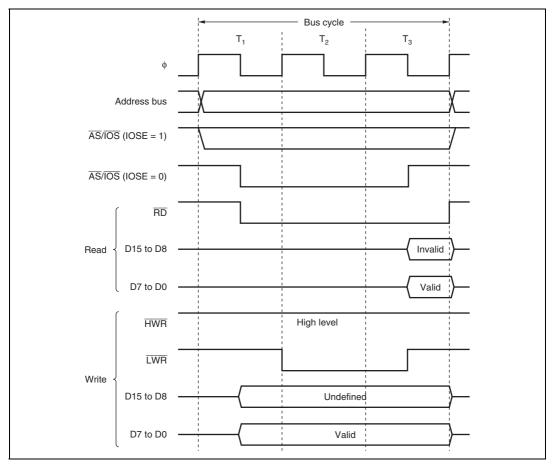

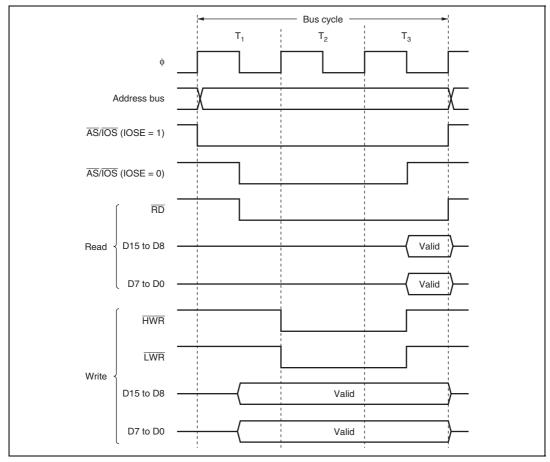

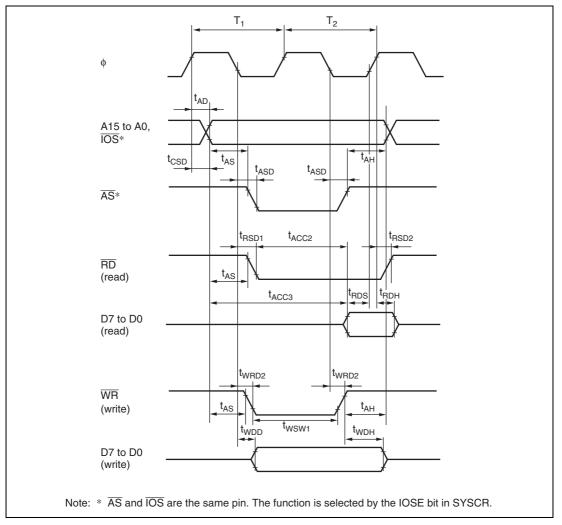

| Figure 6.5  | Bus Timing for 8-Bit, 2-State Access Space                     | 119 |

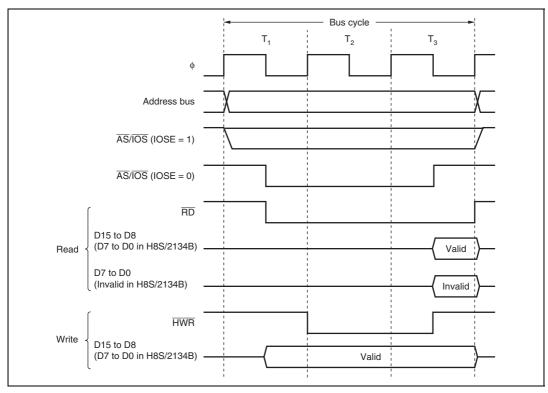

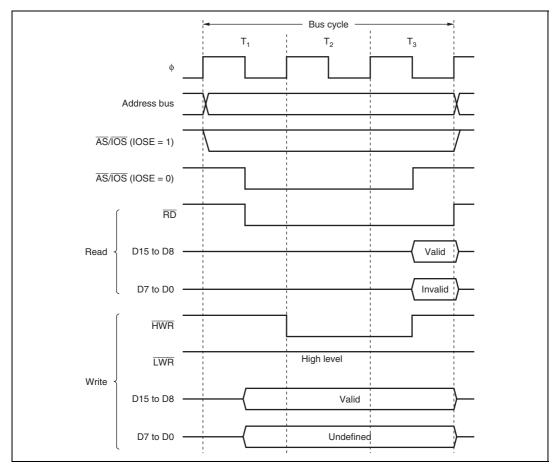

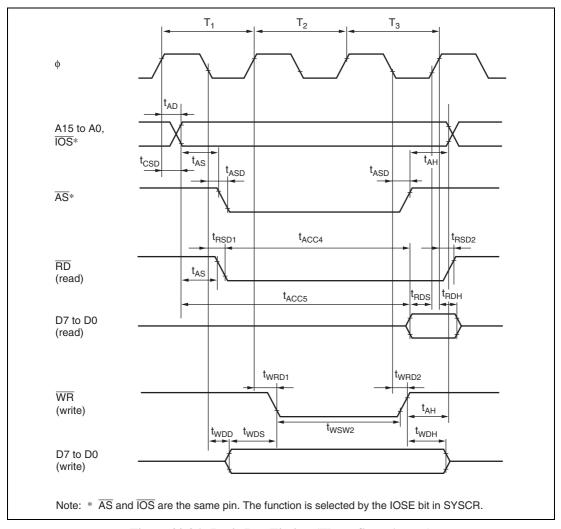

| Figure 6.6  | Bus Timing for 8-Bit, 3-State Access Space                     | 120 |

| Figure 6.7  | Bus Timing for 16-Bit, 2-State Access Space (Even Byte Access) | 121 |

| Figure 6.8  | Bus Timing for 16-Bit, 2-State Access Space (Odd Byte Access)  | 122 |

| Figure 6.9  | Bus Timing for 16-Bit, 2-State Access Space (Word Access)      | 123 |

| Figure 6.10 | Bus Timing for 16-Bit, 3-State Access Space (Even Byte Access) | 124 |

| Figure 6.11 | Bus Timing for 16-Bit, 3-State Access Space (Odd Byte Access)  | 125 |

| Figure 6.12 | Bus Timing for 16-Bit, 3-State Access Space (Word Access)      | 126 |

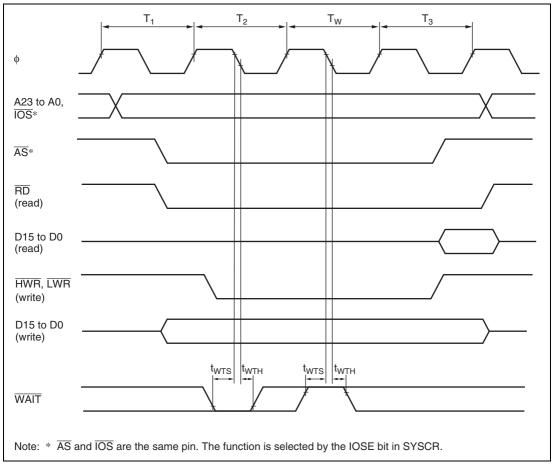

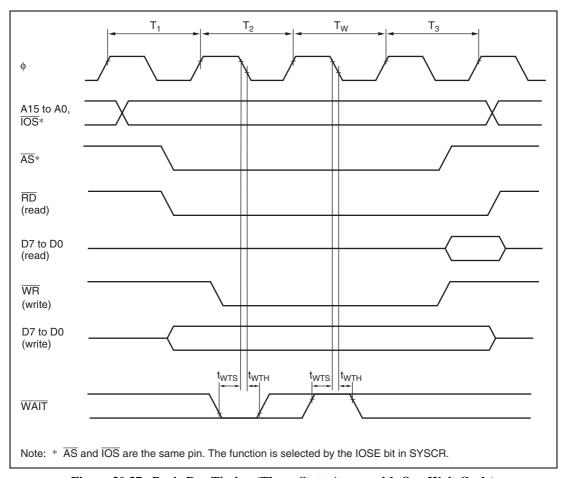

| Figure 6.13 | Example of Wait Cycle Insertion Timing (Pin Wait Mode)         | 128 |

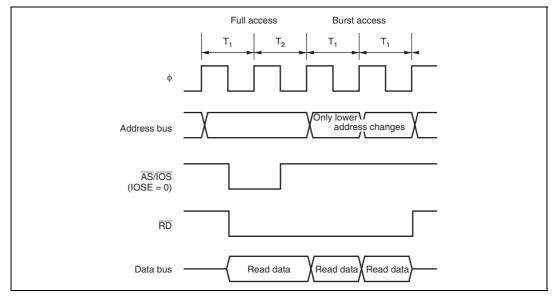

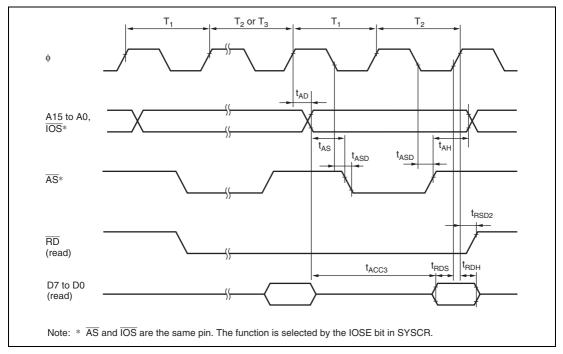

| Figure 6.14 | Access Timing Example in Burst ROM Space (AST = BRSTS1 = 1)    | 129 |

| Figure 6.15 | Access Timing Example in Burst ROM Space (AST = BRSTS1 = 0)    | 130 |

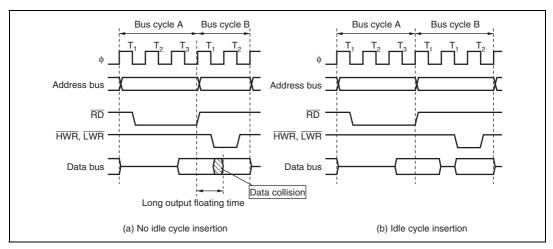

| Figure 6.16 | Examples of Idle Cycle Operation                               | 131 |

| Section 8 1 | 4-Bit PWM Timer (PWMX)                                         |     |

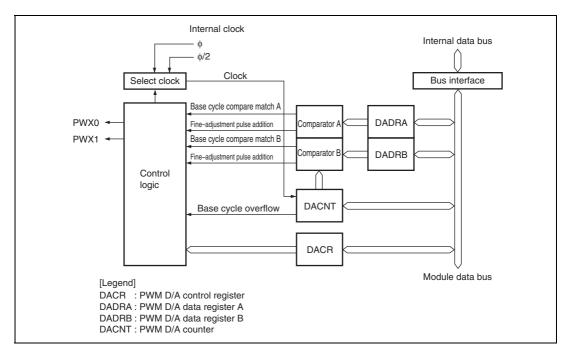

| Figure 8.1  | PWM (D/A) Block Diagram                                        | 183 |

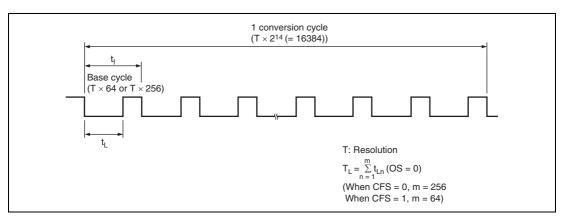

| Figure 8.2  | PWM D/A Operation                                              | 190 |

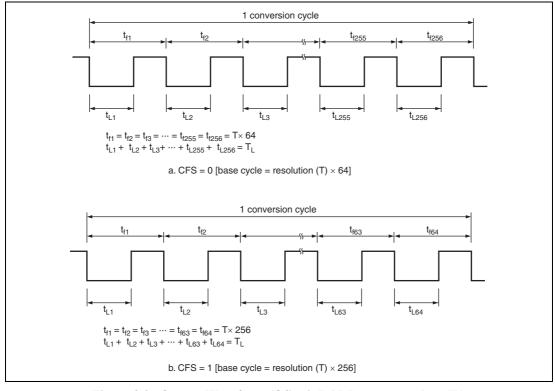

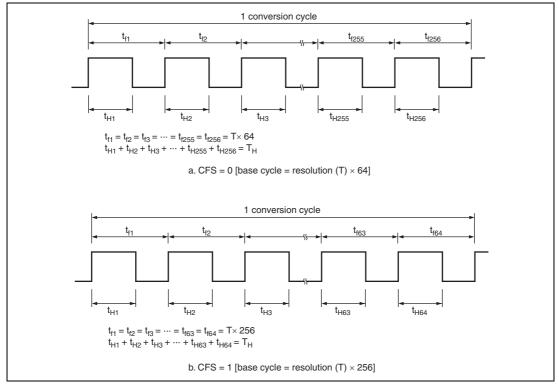

| Figure 8.3  | Output Waveform (OS = $0$ , DADR corresponds to $T_L$ )        | 192 |

|             | Output Waveform (OS = 1, DADR corresponds to $T_H$ )           |     |

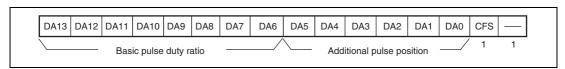

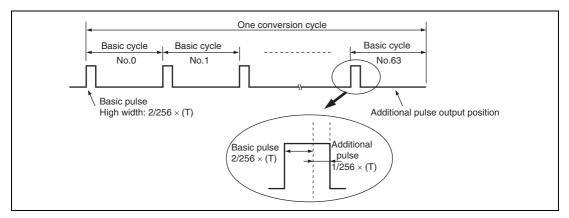

| Figure 8.5  | D/A Data Register Configuration when CFS = 1                   | 193 |

| Figure 8.6  | Output Waveform when DADR = H'0207 (OS = 1)                    | 194 |

| Section 9 1 | 6-Bit Free-Running Timer (FRT)                                 |     |

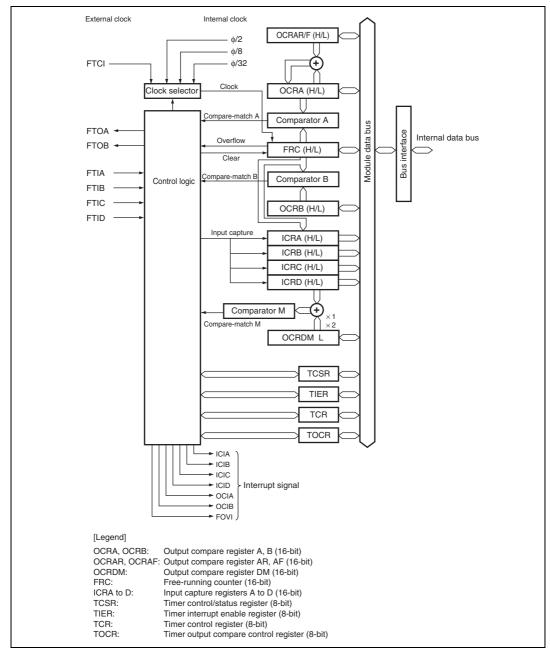

| Figure 9.1  | Block Diagram of 16-Bit Free-Running Timer                     | 198 |

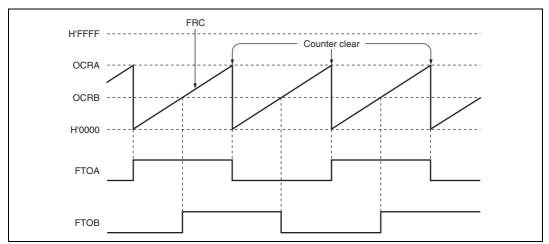

| Figure 9.2  | Example of Pulse Output                                        | 209 |

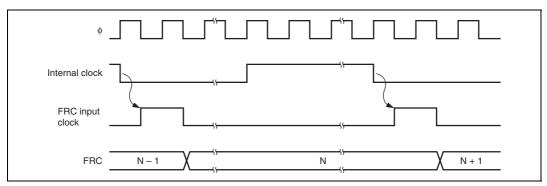

| Figure 9.3  | Increment Timing with Internal Clock Source                    | 209 |

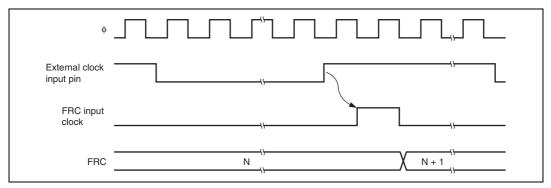

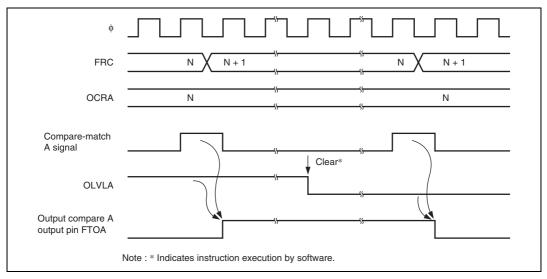

| Figure 9.4  | Increment Timing with External Clock Source                    | 210 |

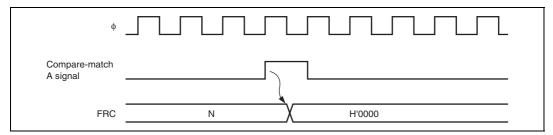

| Figure 9.5  | Timing of Output Compare A Output                              | 210 |

| Figure 9.6  | Clearing of FRC by Compare-Match A Signal                      | 211 |

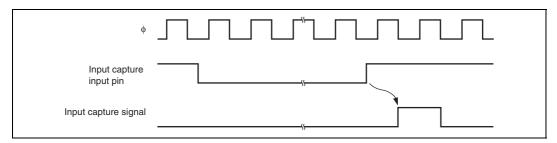

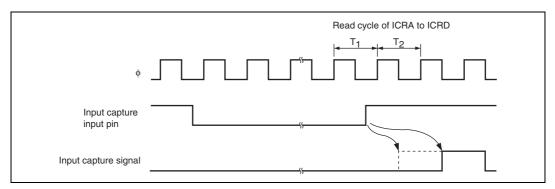

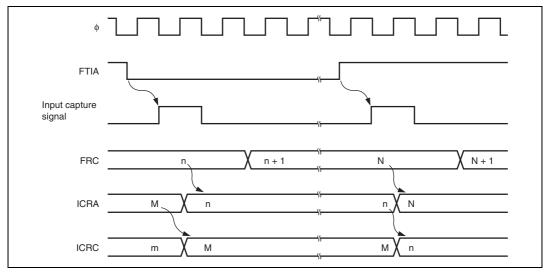

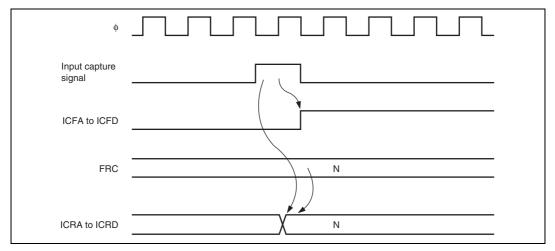

| Figure 9.7  | Input Capture Input Signal Timing (Usual Case)                 | 211 |

|             | Input Capture Input Signal Timing (When ICRA to ICRD are Read) |     |

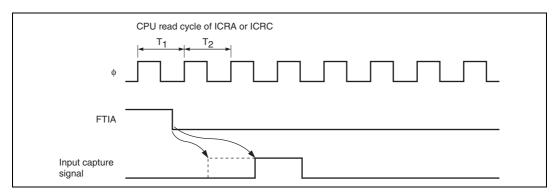

| Figure 9.9  | Buffered Input Capture Timing                                  | 212 |

| Figure 9.10 | Buffered Input Capture Timing (BUFEA = 1)                      | 213 |

| Figure 9.11  | Timing of Input Capture Flag (ICFA, ICFB, ICFC, or ICFD) Setting | 214 |

|--------------|------------------------------------------------------------------|-----|

| Figure 9.12  | Timing of Output Compare Flag (OCFA or OCFB) Setting             |     |

| Figure 9.13  | Timing of Overflow Flag (OVF) Setting                            |     |

| Figure 9.14  | OCRA Automatic Addition Timing                                   | 217 |

| Figure 9.15  | Timing of Input Capture Mask Signal Setting                      |     |

| Figure 9.16  | Timing of Input Capture Mask Signal Clearing                     | 218 |

| Figure 9.17  | FRC Write-Clear Conflict                                         | 220 |

| Figure 9.18  | FRC Write-Increment Conflict                                     | 221 |

| Figure 9.19  | Conflict between OCR Write and Compare-Match                     |     |

|              | (When Automatic Addition Function is Not Used)                   | 222 |

| Figure 9.20  | Conflict between OCRAR/OCRAF Write and Compare-Match             |     |

|              | (When Automatic Addition Function is Used)                       | 223 |

| Section 10 8 | B-Bit Timer (TMR)                                                |     |

|              | Block Diagram of 8-Bit Timers (TMR_0 and TMR_1)                  | 228 |

|              | Block Diagram of 8-Bit Timers (TMR_Y)                            |     |

| Figure 10.3  | Pulse Output Example                                             | 241 |

|              | Count Timing for Internal Clock Input                            |     |

| Figure 10.5  | Count Timing for External Clock Input (Both Edges)               | 242 |

| Figure 10.6  | Timing of CMF Setting at Compare-Match                           | 243 |

| Figure 10.7  | Timing of Toggled Timer Output by Compare-Match A Signal         | 243 |

| Figure 10.8  | Timing of Counter Clear by Compare-Match                         | 244 |

| Figure 10.9  | Timing of Counter Clear by External Reset Input                  | 244 |

| Figure 10.10 | Timing of OVF Flag Setting                                       | 245 |

|              | Conflict between TCNT Write and Clear                            |     |

| Figure 10.12 | 2 Conflict between TCNT Write and Increment                      | 250 |

| Figure 10.13 | 3 Conflict between TCOR Write and Compare-Match                  | 251 |

| Section 11 V | Watchdog Timer (WDT)                                             |     |

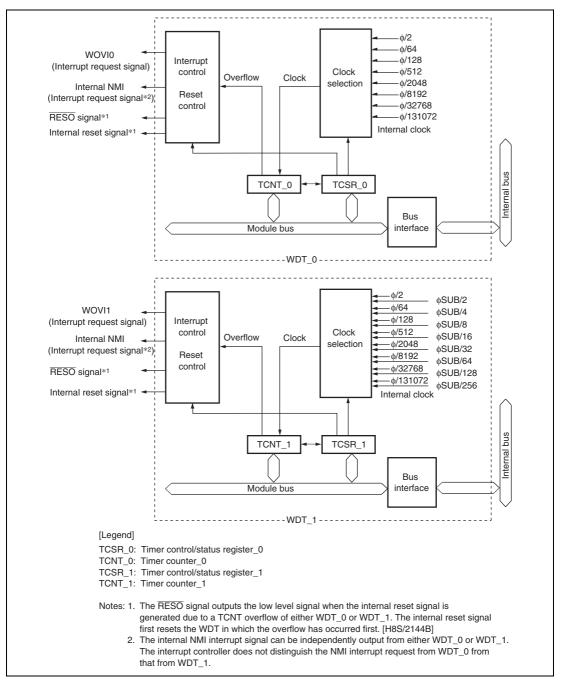

| Figure 11.1  | Block Diagram of WDT                                             | 258 |

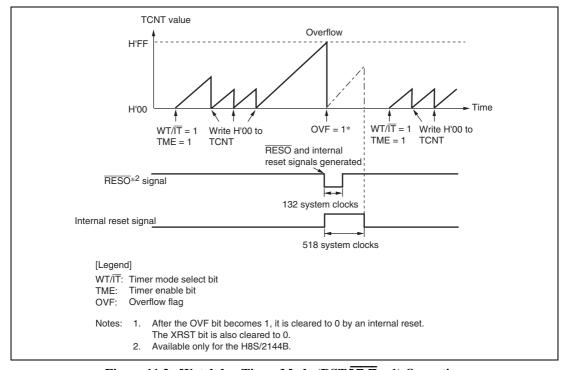

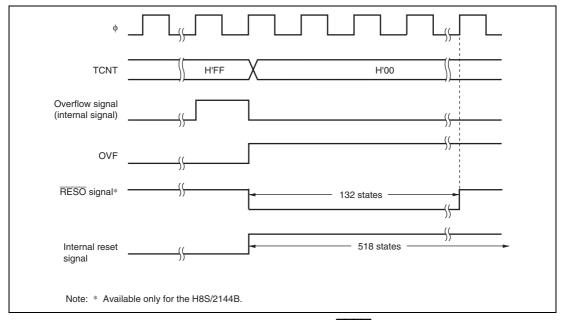

| Figure 11.2  | Watchdog Timer Mode (RST/NMI = 1) Operation                      | 265 |

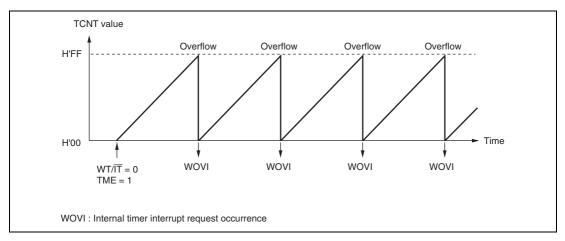

| Figure 11.3  | Interval Timer Mode Operation                                    | 266 |

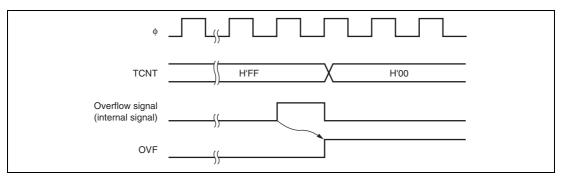

| Figure 11.4  | OVF Flag Set Timing                                              | 266 |

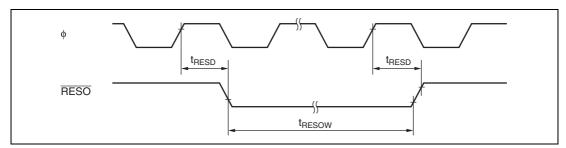

| Figure 11.5  | Output Timing of RESO signal                                     | 267 |

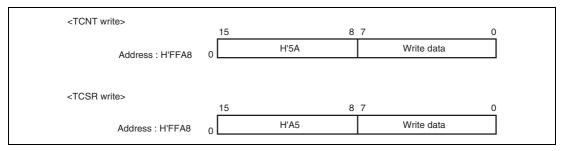

| Figure 11.6  | Writing to TCNT and TCSR (WDT_0)                                 | 268 |

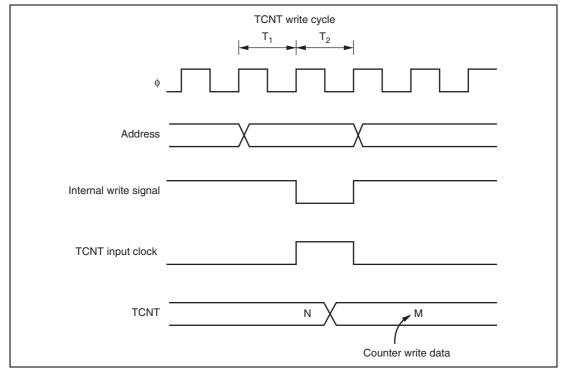

| Figure 11.7  | Conflict between TCNT Write and Increment                        | 269 |

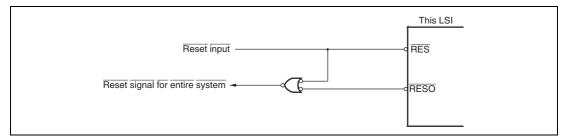

| Figure 11.8  | Sample Circuit for Resetting System by RESO Signal               | 270 |

| Section 12 S | Serial Communication Interface (SCI and IrDA)                    |     |

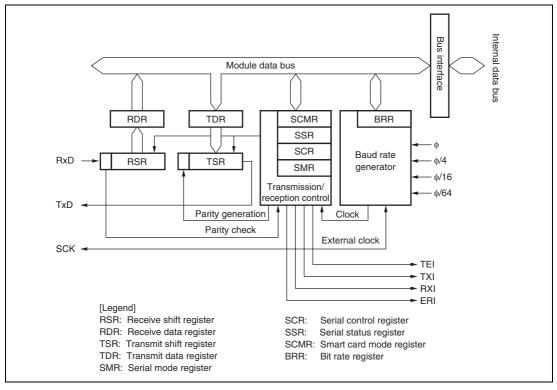

| Figure 12.1  | Block Diagram of SCI                                             | 272 |

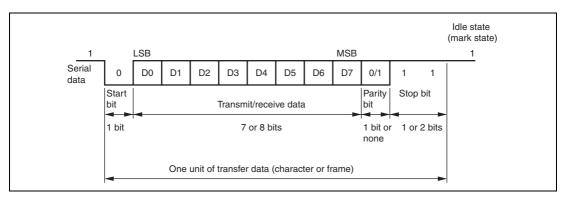

|              | Data Format in Asynchronous Communication                        |     |

|              | (Example with 8-Bit Data, Parity, Two Stop Bits)                 | 290 |

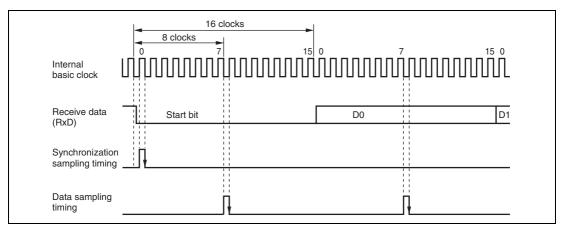

| Figure 12.3  | Receive Data Sampling Timing in Asynchronous Mode                      | 292 |

|--------------|------------------------------------------------------------------------|-----|

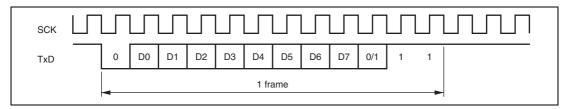

| Figure 12.4  | Relation between Output Clock and Transmit Data Phase                  |     |

|              | (Asynchronous Mode)                                                    | 293 |

| Figure 12.5  | Sample SCI Initialization Flowchart                                    | 294 |

| Figure 12.6  | Example of SCI Transmit Operation in Asynchronous Mode                 |     |

|              | (Example with 8-Bit Data, Parity, One Stop Bit)                        | 295 |

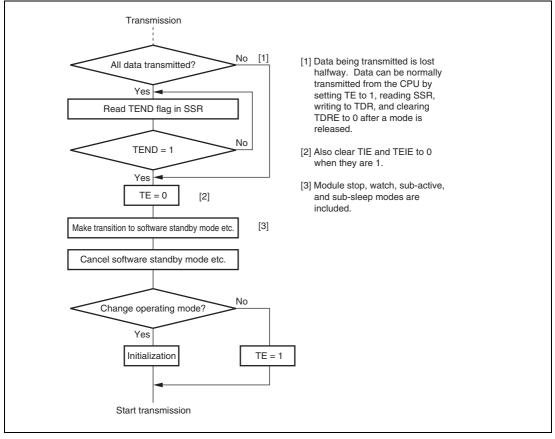

| Figure 12.7  | Sample Serial Transmission Flowchart                                   | 296 |

| Figure 12.8  | Example of SCI Receive Operation in Asynchronous Mode                  |     |

|              | (Example with 8-Bit Data, Parity, One Stop Bit)                        | 297 |

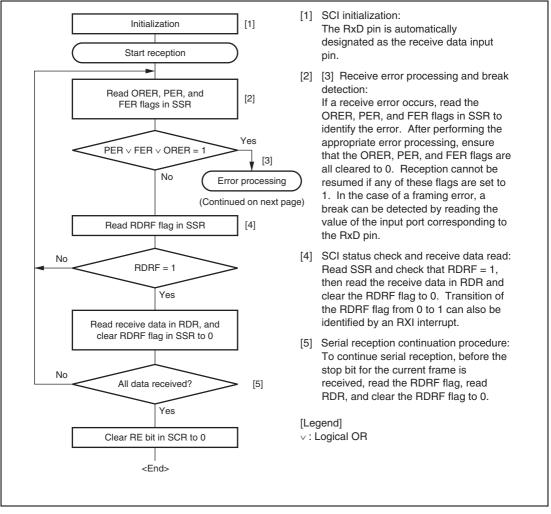

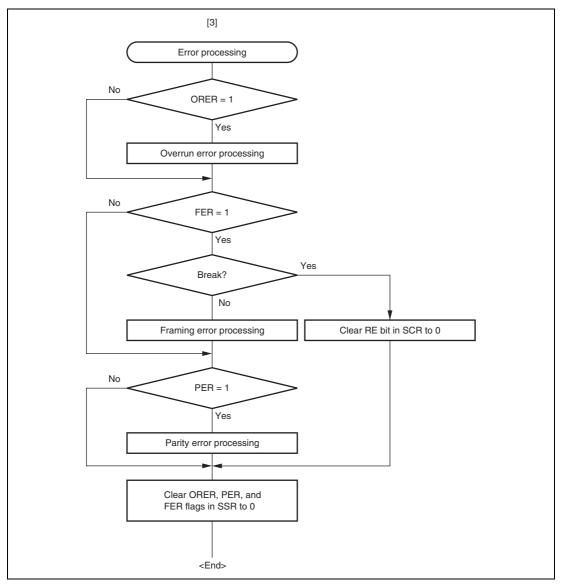

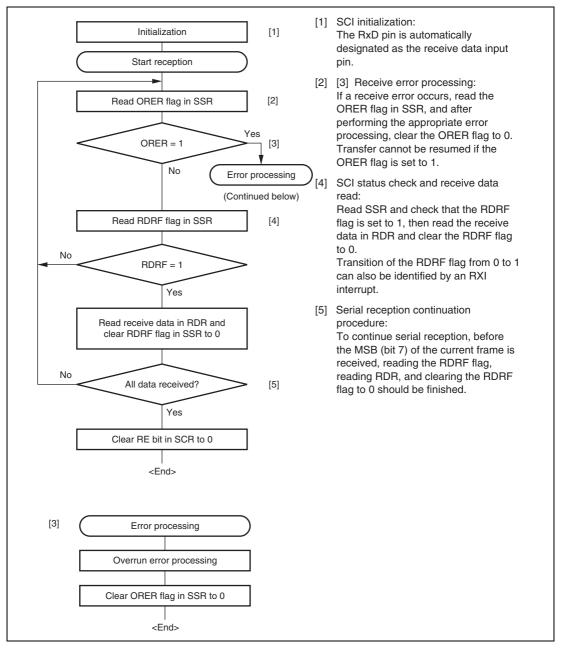

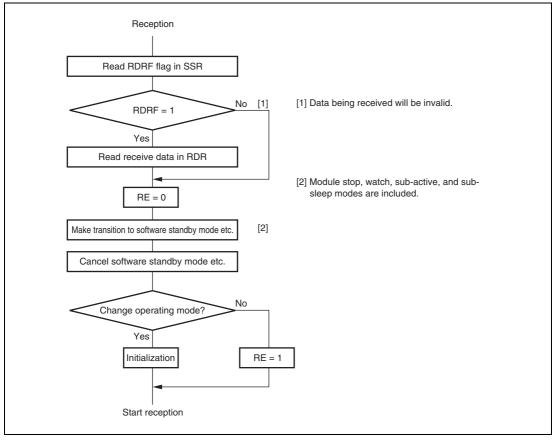

| Figure 12.9  | Sample Serial Reception Flowchart (1)                                  | 299 |

| Figure 12.9  | Sample Serial Reception Flowchart (2)                                  | 300 |

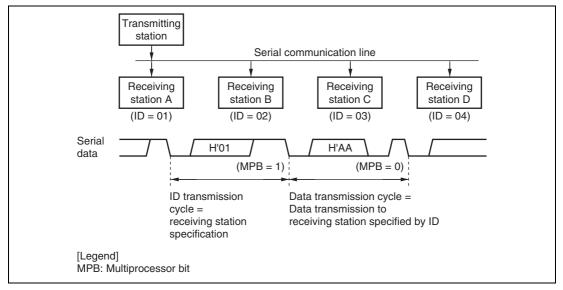

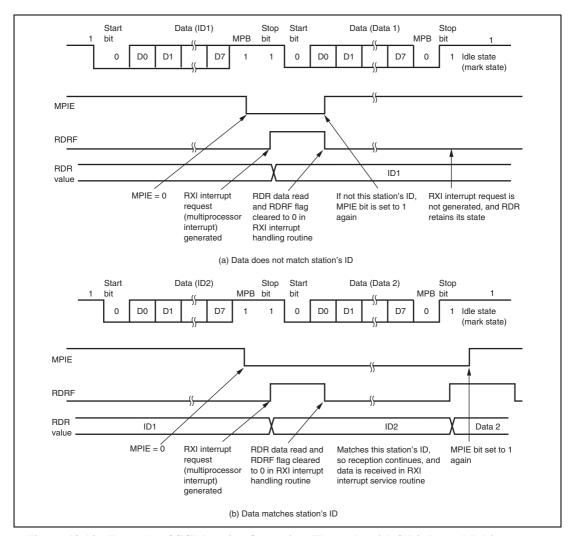

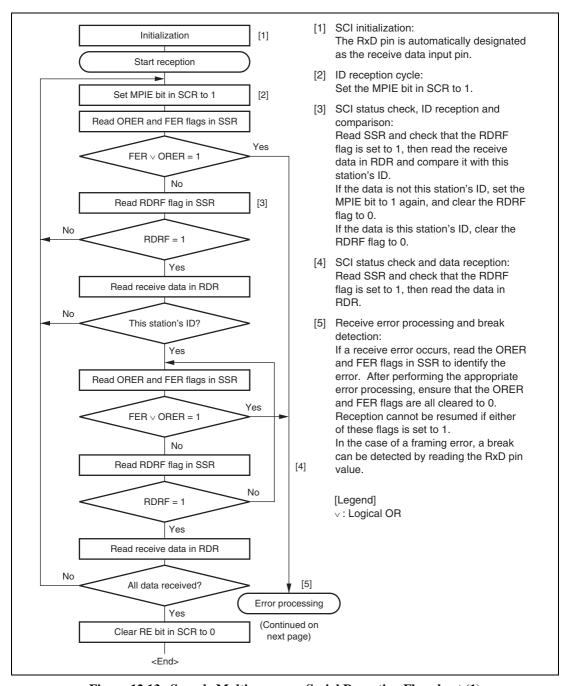

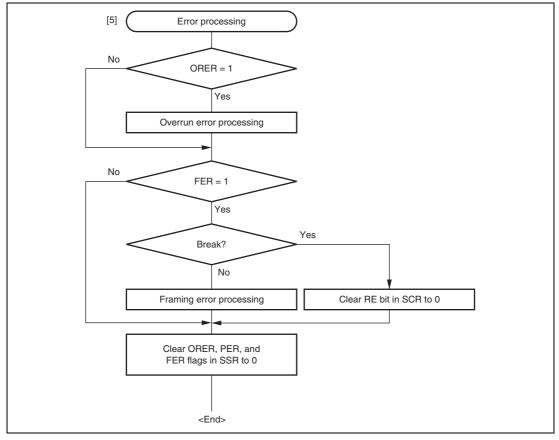

| Figure 12.10 | Example of Communication Using Multiprocessor Format                   |     |

|              | (Transmission of Data H'AA to Receiving Station A)                     | 302 |

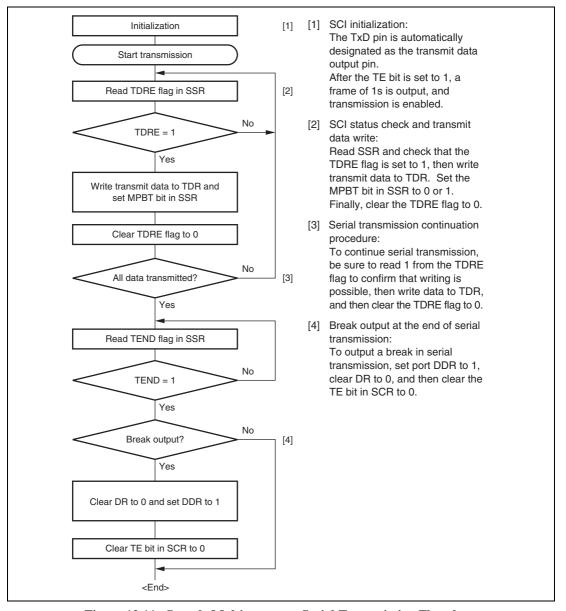

| Figure 12.11 | Sample Multiprocessor Serial Transmission Flowchart                    | 304 |

| Figure 12.12 | •                                                                      |     |

|              | (Example with 8-Bit Data, Multiprocessor Bit, One Stop Bit)            | 305 |

| Figure 12.13 | Sample Multiprocessor Serial Reception Flowchart (1)                   | 306 |

| Figure 12.13 | 1 1                                                                    |     |

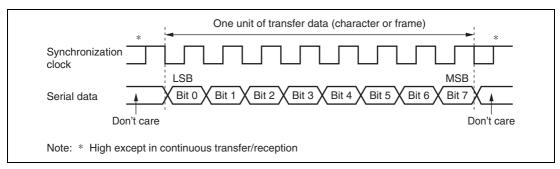

| Figure 12.14 | •                                                                      | 308 |

| Figure 12.15 | <u>.</u>                                                               |     |

| Figure 12.16 | 1                                                                      |     |

| Figure 12.17 | •                                                                      |     |

| Figure 12.18 |                                                                        |     |

| Figure 12.19 | <u>.                                      </u>                         |     |

| Figure 12.20 | 1                                                                      |     |

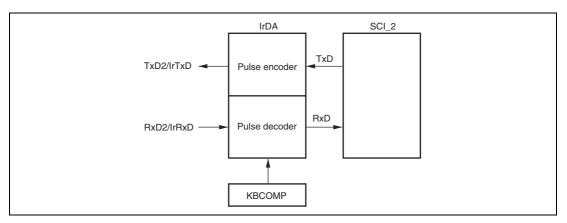

| Figure 12.21 | IrDA Block Diagram                                                     | 318 |

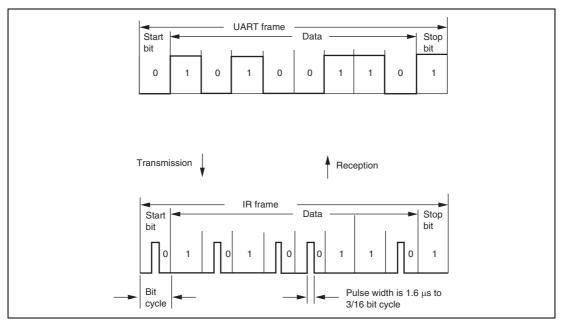

| Figure 12.22 | •                                                                      | 319 |

| Figure 12.23 | 1                                                                      |     |

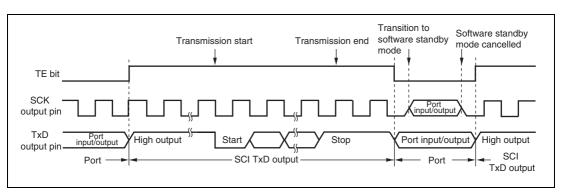

| Figure 12.24 | Pin States during Transmission in Asynchronous Mode (Internal Clock)   | 324 |

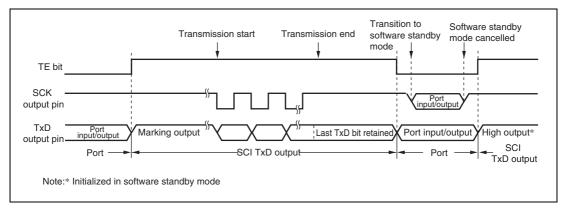

| Figure 12.25 | , ,                                                                    |     |

| Figure 12.26 |                                                                        |     |

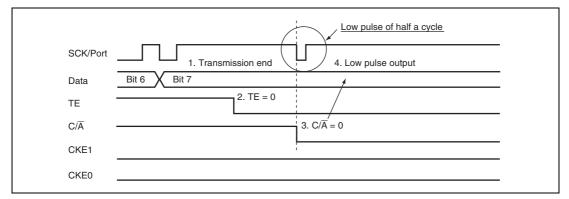

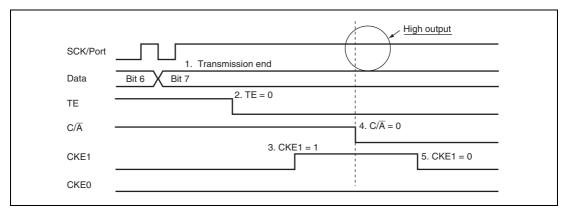

| Figure 12.27 | Switching from SCK Pins to Port Pins                                   | 327 |

| Figure 12.28 | Prevention of Low Pulse Output at Switching from SCK Pins to Port Pins | 328 |

|              | D/A Converter                                                          |     |

| -            | Block Diagram of D/A Converter                                         |     |

| Figure 13.2  | D/A Converter Operation Example                                        | 333 |

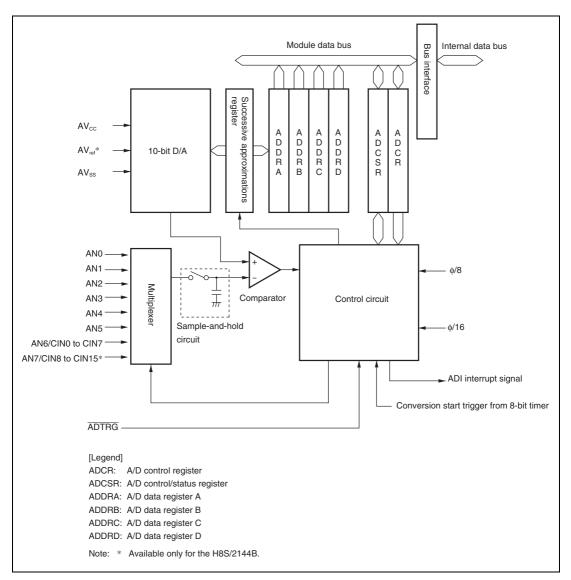

|              | A/D Converter                                                          |     |

| Figure 14.1  | Block Diagram of A/D Converter                                         | 336 |

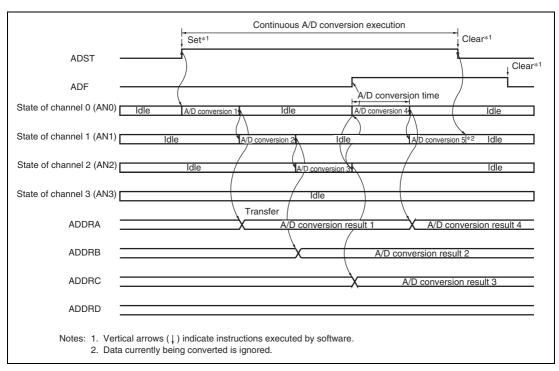

| Figure 14.2  | Example of A/D Converter Operation                         |     |

|--------------|------------------------------------------------------------|-----|

|              | (Scan Mode, Channels AN0 to AN2 Selected)                  | 344 |

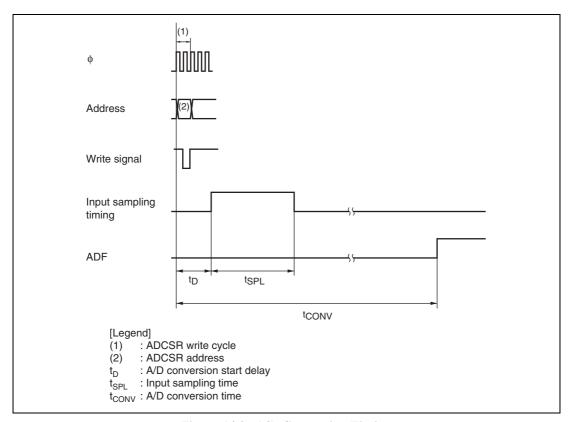

| Figure 14.3  | A/D Conversion Timing                                      | 345 |

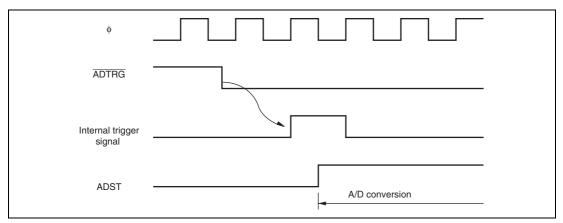

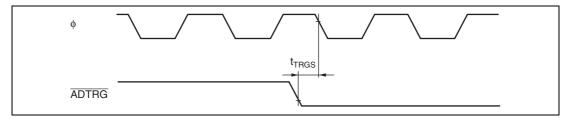

| Figure 14.4  | External Trigger Input Timing                              | 346 |

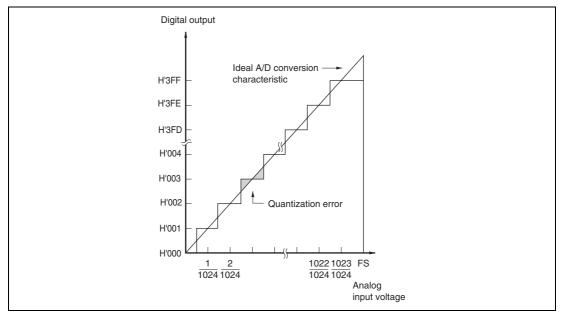

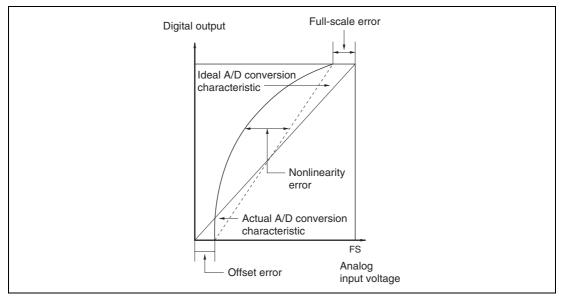

| Figure 14.5  | A/D Conversion Accuracy Definitions                        | 348 |

| Figure 14.6  | A/D Conversion Accuracy Definitions                        | 348 |

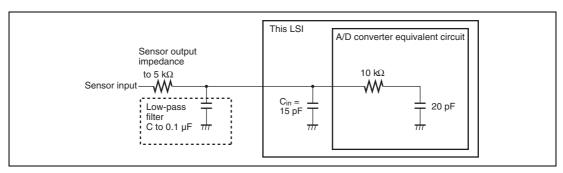

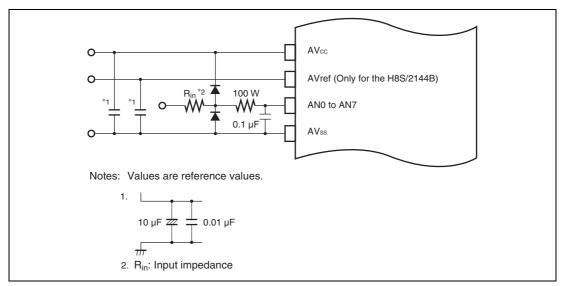

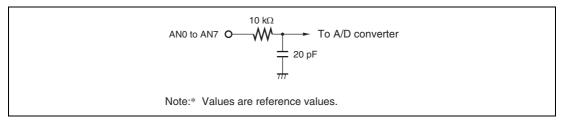

| Figure 14.7  | Example of Analog Input Circuit                            | 349 |

| Figure 14.8  | Example of Analog Input Protection Circuit                 | 351 |

| Figure 14.9  | Equivalent Circuit of Analog Input Pin                     | 352 |

| Section 16 l | ROM                                                        |     |

| Figure 16.1  | Block Diagram of Flash Memory                              | 356 |

| Figure 16.2  | Flash Memory State Transitions                             | 357 |

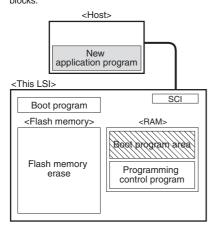

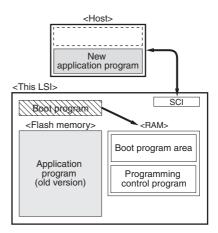

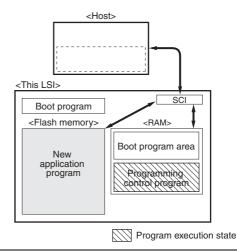

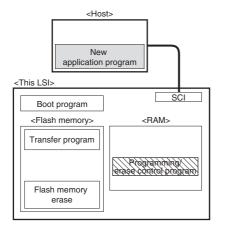

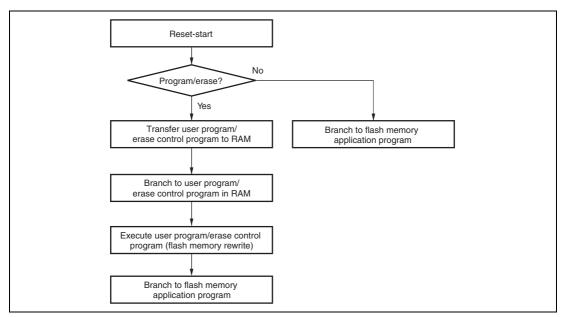

| Figure 16.3  | Boot Mode                                                  | 358 |

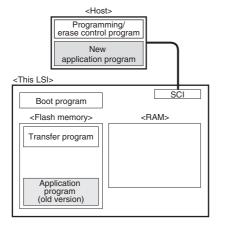

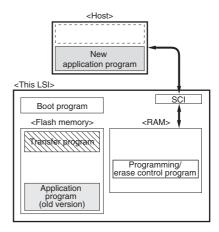

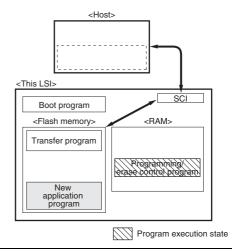

| Figure 16.4  | User Program Mode (Example)                                | 359 |

| Figure 16.5  | Flash Memory Block Configuration                           | 360 |

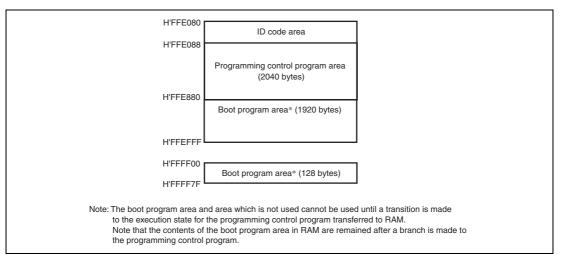

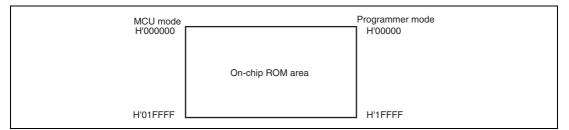

| Figure 16.6  | On-Chip RAM Area in Boot Mode                              | 369 |

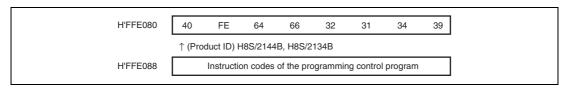

| Figure 16.7  | ID Code Area                                               | 369 |

| Figure 16.8  | Programming/Erasing Flowchart Example in User Program Mode | 370 |

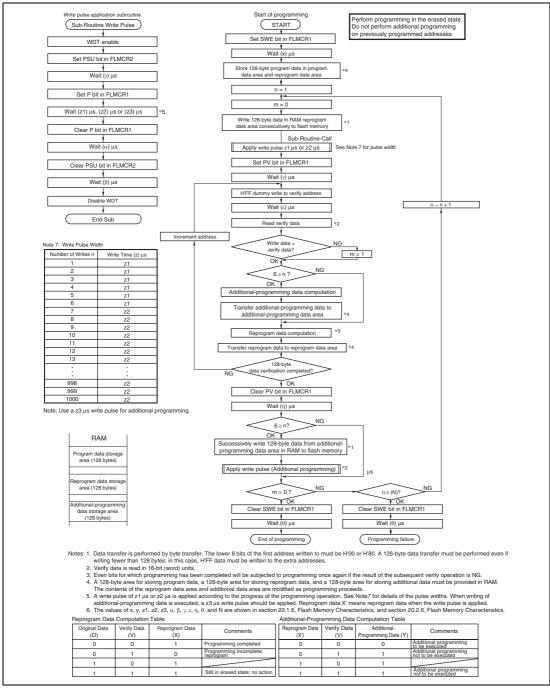

| Figure 16.9  | Programming/Programming-Verifying Flowchart                | 373 |

| Figure 16.10 | Prasing/Erasing-Verifying Flowchart                        | 375 |

| Figure 16.11 | Memory Map in Programmer Mode                              | 378 |

| Section 17   | Clock Pulse Generator                                      |     |

| Figure 17.1  | Block Diagram of Clock Pulse Generator                     | 381 |

| Figure 17.2  | Typical Connection to Crystal Resonator                    | 382 |

| Figure 17.3  | Equivalent Circuit of Crystal Resonator                    | 382 |

| Figure 17.4  | Example of External Clock Input                            | 383 |

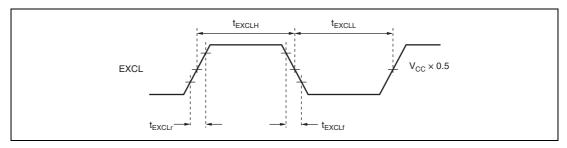

|              | External Clock Input Timing                                |     |

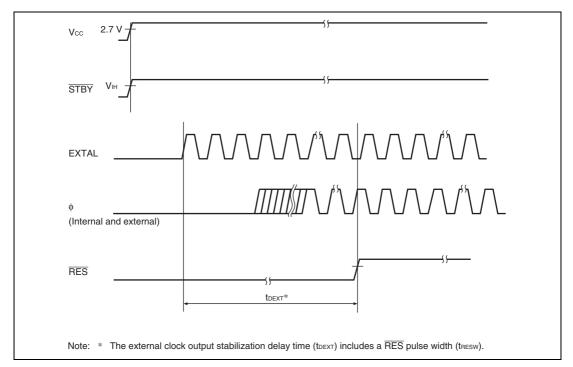

| Figure 17.6  | Timing of External Clock Output Stabilization Delay Time   | 385 |

| Figure 17.7  | Subclock Input Timing                                      | 387 |

| Figure 17.8  | Note on Board Design of Oscillator Circuit Section         | 388 |

| Section 18 l | Power-Down Modes                                           |     |

| Figure 18.1  | Mode Transition Diagram                                    | 395 |

| Figure 18.2  | Medium-Speed Mode Timing                                   | 398 |

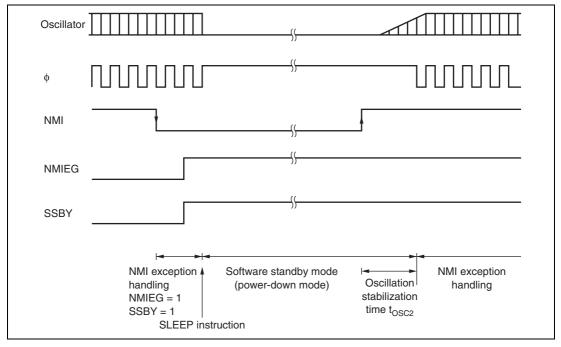

| Figure 18.3  | Application Example in Software Standby Mode               | 400 |

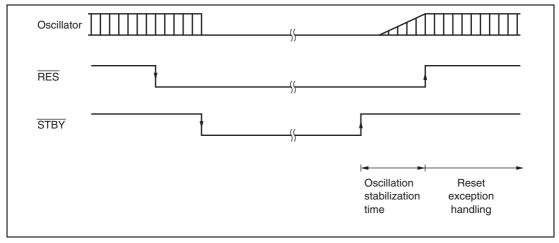

| Figure 18.4  | Hardware Standby Mode Timing                               | 401 |

| Section 20 l | Electrical Characteristics                                 |     |

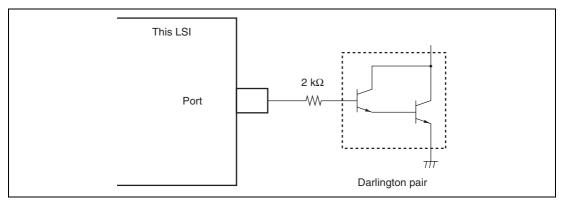

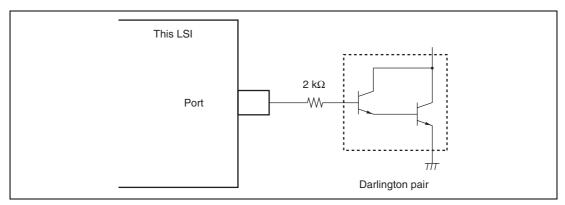

| Figure 20.1  | Darlington Pair Driving Circuit (Example)                  | 440 |

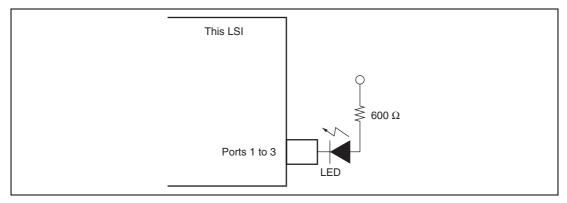

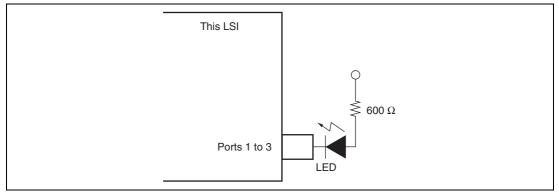

| Figure 20.2  | LED Driving Circuit (Example)                              | 441 |

|              |                                                            |     |

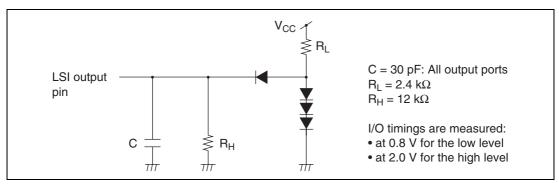

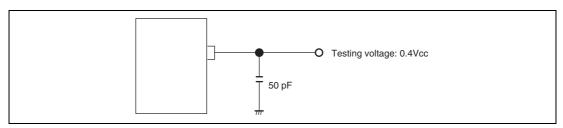

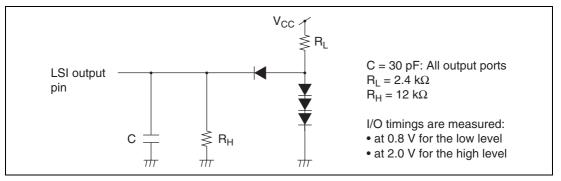

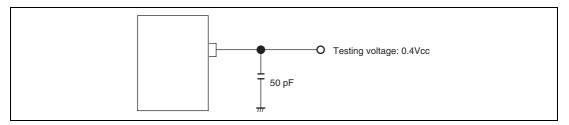

| Figure 20.3  | Output Load Circuit                                              | 441 |

|--------------|------------------------------------------------------------------|-----|

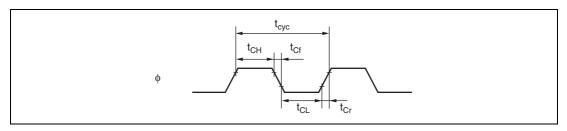

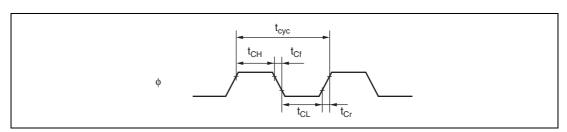

| Figure 20.4  | System Clock Timing                                              | 442 |

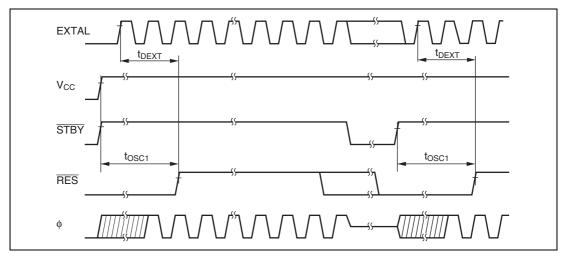

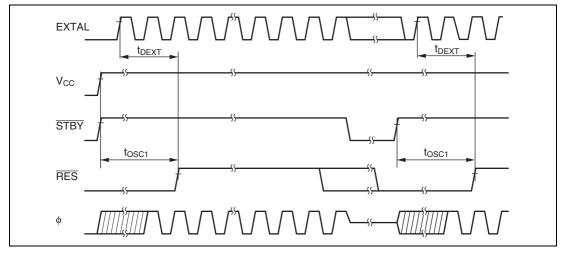

| Figure 20.5  | Oscillation Stabilization Timing                                 | 443 |

| Figure 20.6  | Oscillation Stabilization Timing (Leaving Software Standby Mode) | 443 |

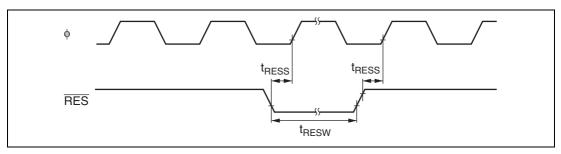

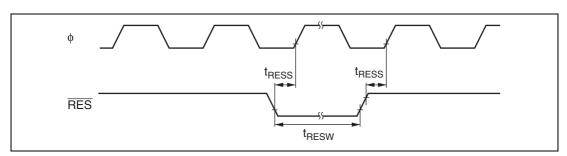

| Figure 20.7  | Reset Input Timing                                               | 444 |

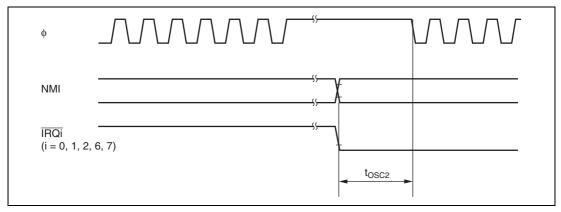

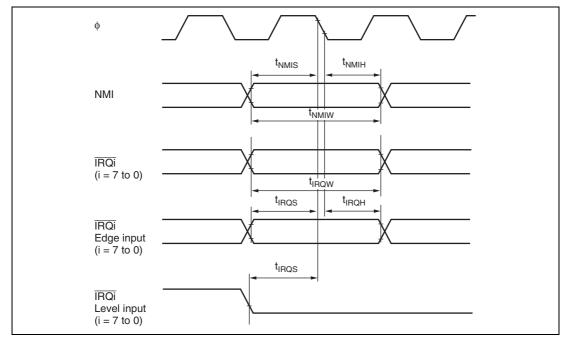

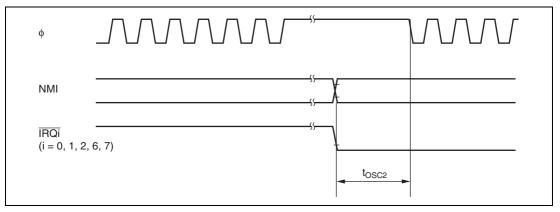

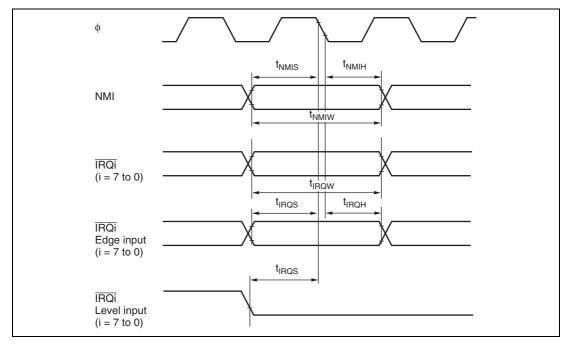

| Figure 20.8  | Interrupt Input Timing.                                          | 445 |

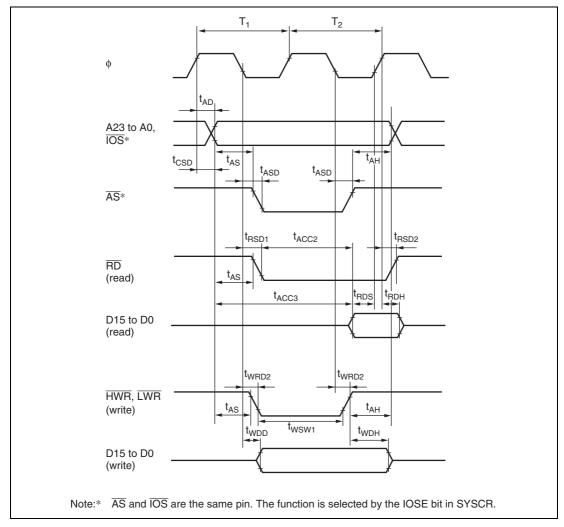

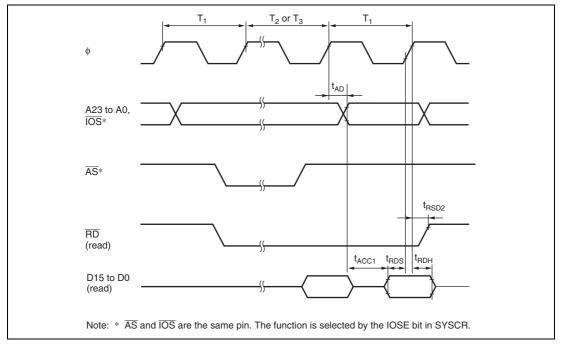

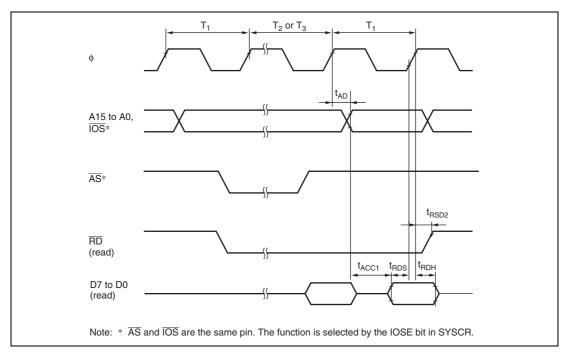

| Figure 20.9  | Basic Bus Timing (Two-State Access)                              | 450 |

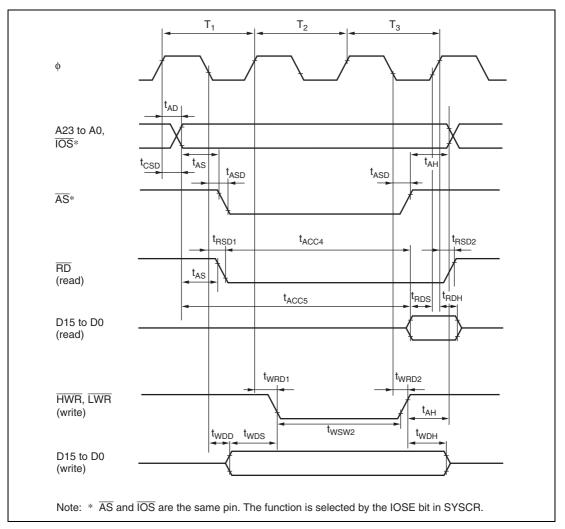

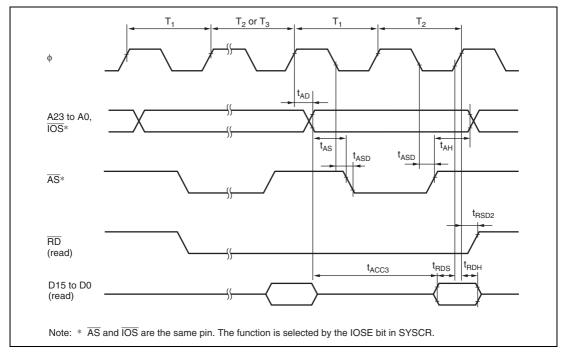

| Figure 20.10 | Basic Bus Timing (Three-State Access)                            | 451 |

| Figure 20.11 | Basic Bus Timing (Three-State Access with One Wait Cycle)        | 452 |

| Figure 20.12 | Burst ROM Access Timing (Two-State Access)                       | 453 |

| Figure 20.13 | Burst ROM Access Timing (One-State Access)                       | 454 |

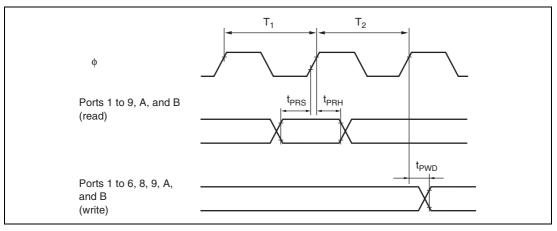

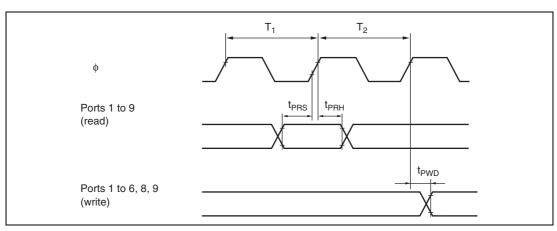

| Figure 20.14 | I/O Port Input/Output Timing                                     | 456 |

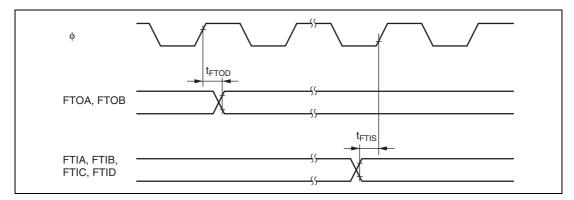

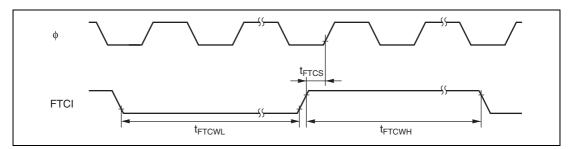

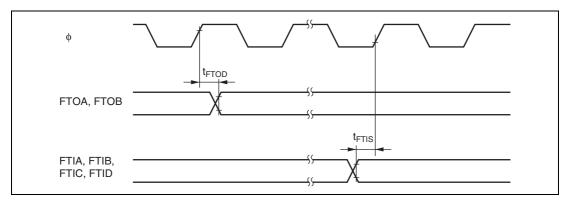

| Figure 20.15 | FRT Input/Output Timing                                          | 457 |

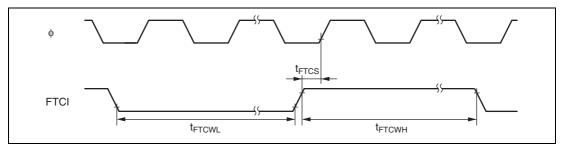

| Figure 20.16 | FRT Clock Input Timing                                           | 457 |

| Figure 20.17 | 8-Bit Timer Output Timing                                        | 457 |

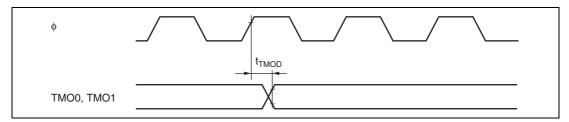

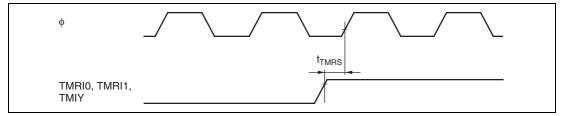

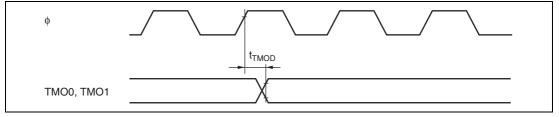

| Figure 20.18 | 8-Bit Timer Clock Input Timing                                   | 458 |

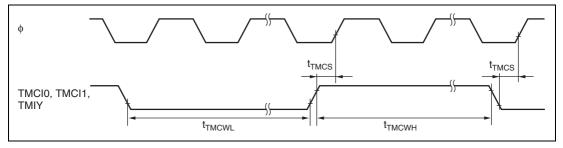

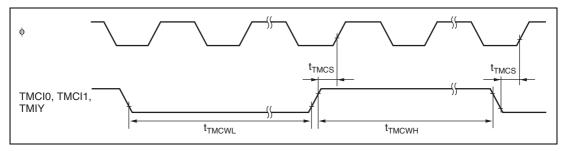

| Figure 20.19 | 8-Bit Timer Reset Input Timing                                   | 458 |

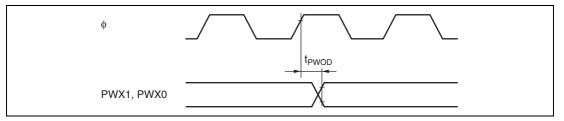

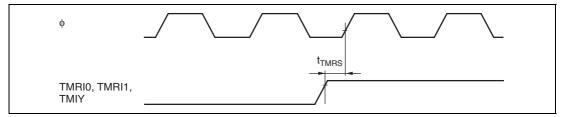

| Figure 20.20 | PWMX Output Timing                                               | 458 |

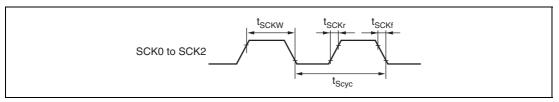

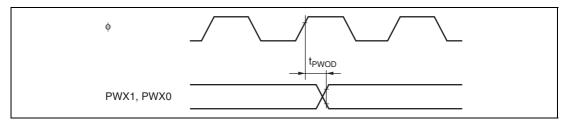

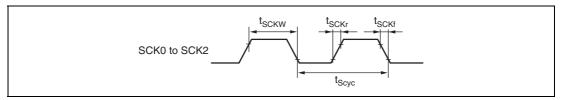

| Figure 20.21 | SCK Clock Input Timing                                           | 458 |

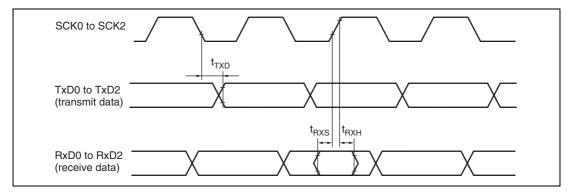

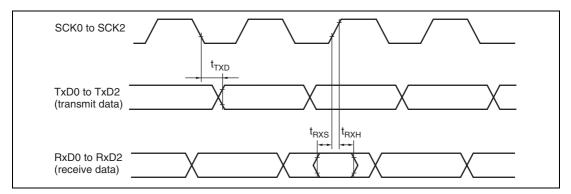

| Figure 20.22 | SCI Input/Output Timing (Synchronous Mode)                       | 459 |

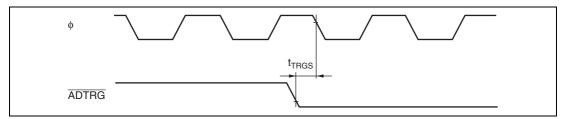

| Figure 20.23 | A/D Converter External Trigger Input Timing                      | 459 |

| Figure 20.24 | WDT Output Timing (RESO)                                         | 459 |