### Introduction

The 9SQ440 Evaluation Board (EVB) is designed to help users evaluate the 9SQ440 PCIe Gen5 clock synthesizer. When the EVB is connected via USB to the user's computer running the Renesas 9SQ440 <u>Timing Commander™ Software</u>, the 9SQ440 can be configured to control frequencies with best-in-class performance. The 9SQ440 offers features of 7 pairs of 100MHz differential LP-HCSL outputs, 9 MXCLK pairs of differential outputs multiplexable between 100MHz/25MHz, and 3 pairs of 25MHz outputs. 9 selectable SMBus addresses available. Board Overview

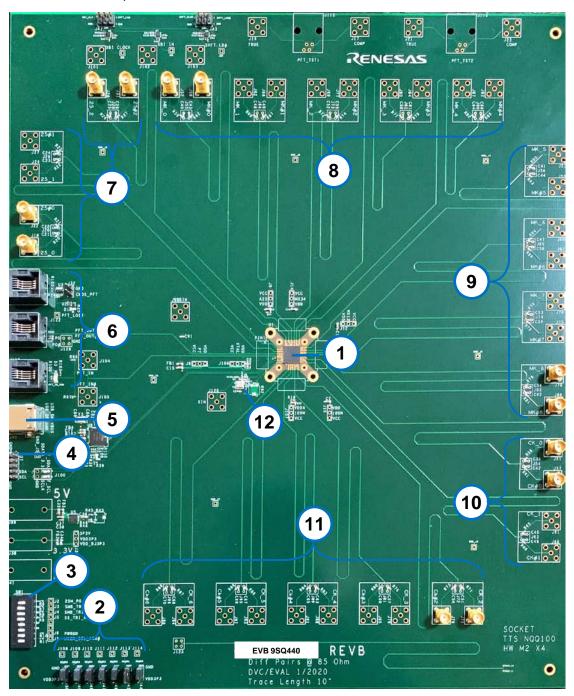

Figure 1. 9SQ440 EVB - Top View

Table 1. 9SQ440 - EVB Pins and Functions

Note: See Figure 1 for reference numbers in the following table.

| Ref. | Name                           | On-Board Connector Label                            | Function                                                                                                                                                                                   |

|------|--------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | 9SQ440                         | U1                                                  | Evaluation device, 8 x 8 mm dual-row 100-pin QFN.                                                                                                                                          |

| 2    | OE# Pins Control               | J44, J45, J46, J47, J48, J49,<br>J50                | Hardware output enable/disable pins for 7 LP-HCSL 85Ω differential outputs. Active low on OE# pins for enabling 100M outputs.  1 = disable output; 0 = enable output.                      |

| 3    | DIP Switch                     | SW1                                                 | DIP switch device is used to setup 9SQ440 device condition. See Figure in below for detail.                                                                                                |

| 4    | SMBus Connector                | J37                                                 | SMBus connector for SCLK and SDATA pins.                                                                                                                                                   |

| 5    | USB Interface                  | J40                                                 | USB type jack for connection with the user's computer and interaction with Renesas Timing Commander software.                                                                              |

| 6    | RJ11 Connector                 | J117, J118, J119                                    | RJ11 connectors for Platform Time input from another 9SQ440 clock synthesizer using ±0.7V 25MHz differential as input clock.                                                               |

| 7    | Test Points for 25M<br>Outputs | J18, J22, J24, J27, J28, J31                        | SMA connectors for 25MHz differential outputs: J18, J22 for 25M0 (populated with a pairs of SMA connectors) J24, J27 for 25M1 J28, J31 for 25M2 (populated with a pairs of SMA connectors) |

| 8    | Test Points for MK<br>Outputs  | J52, J58, J62, J68, J69, J77,<br>J80, J84, J87, J92 | SMA connectors for MK differential outputs:  J52, J58 for MK0 (populated with a pairs of SMA connectors)  J62, J68 for MK1  J69, J77 for MK2  J80, J84 for MK3  J87, J92 for MK4           |

| 9    | Test Points for MK<br>Outputs  | J53, J59, J60, J67, J70, J75,<br>J78, J86           | SMA connectors for MK differential outputs:  J53, J59 for MK5  J60, J67 for MK6  J70, J75 for MK7  J78, J86 for MK8 (populated with a pairs of SMA connectors)                             |

| 10   | Test Points for CK<br>Outputs  | J51, J57, J61, J66                                  | SMA connectors for CK differential outputs: J51, J57 for CK0 (populated with a pairs of SMA connectors) J61, J66 for CK1                                                                   |

| 11   | Test Points for CK<br>Outputs  | J71, J76, J79, J85, J88, J91,<br>J93, J97, J94, J98 | SMA connectors for differential outputs:  J71, J76 for CK2 (populated with a pairs of SMA connectors)  J79, J85 for CK3  J88, J91 for CK4  J93, J97 for CK5  J94, J98 for CK6              |

| 12   | Crystal                        | Y1                                                  | 25MHz Quartz Crystal                                                                                                                                                                       |

# 2. Power and SMBus Connection to a Computer

The evaluation board is connected to a computer via an USB connector. The USB connector is a type-B connector which provides +5V in the USB bus powers the on-board regulators for 3.3V voltage to the entire evaluation board. An on-board USB-to-I2C bridge (FTDI chip) is to handle the data communication between the evaluation board and a computer for a 9SQ440 software (called Timing commander Software). The board can fully function with just the USB cable with a computer.

The evaluation board could also be powered from VDD/GND jacks which is not populated as an option.

#### **Board Power Supply**

To power the board, use a USB type-B cable to connect the board with a computer on a USB port.

Figure 2. Power Source from USB Connector

### Software Connection

Renesas Timing Commander Software can control the 9SQ440 on the board. Timing Commander is compatible using the USB connector or an Aardvark adapter as optional. Timing Commander displays a block diagram for entering the configuration and allows control features into the 9QS440 on the board.

The Bus Source connector J37 can be used to select the source of the communication bus. The bus will be SMBus for most communication. Pins 1 and 2 in J37 are SCL and SDA pins for an Aardvark connector. See Figure 3.

Figure 3. Connect Aardvark Adapter to J37

In Figure 3, the Aardvark Adapter communicates with the 9SQ440 part.

# 3. On-Board Crystal

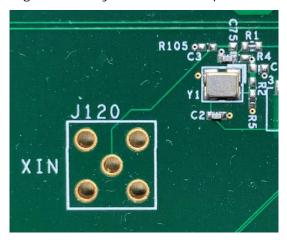

The evaluation board is assembled with a 25MHz crystal populated on Y1 using 3.2 x 2.5 mm size footprint crystal.

Figure 4. Crystal and XIN Input

The XIN input (J120) can be used to overdrive the XIN pin with an external clock but is not assembled with SMA connector. The board is assembled with a 25MHz crystal as default; coupling capacitor C75 is not assembled.

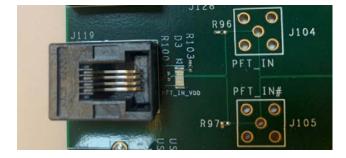

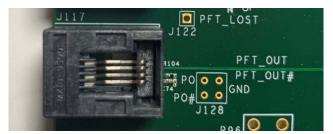

## 4. Platform Time Connectors

The 9SQ440 offers 25MHz differential outputs for platform time clock. The 25MHz frequency can be used to communicate to another 9SQ440 device, keeping the 25MHz frequency the same on all devices. This feature ensures the CPU time stamp counter (TSC) is the same on all devices with the frequency lock. The evaluation board has two RJ11 connectors available to evaluate 25MHz for platform time clock. For PFT\_IN/PFT\_OUT function description, refer to the 9SQ440 datasheet for more information.

Figure 5. RJ11 (J119) Connector for PFT\_IN

Figure 6. RJ11 (J117) Connector for PFT\_OUT

## 5. Miscellaneous Selectors

Figure 7. Output OE Pin Control

The 9SQ440 has two methods for enabling and disabling outputs. The evaluation board offers 7 OE# pins for 9SQ440 in hardware control. There are 3 positions using a jumper to apply either 3-2 on OE# pin to pull-low as output enable, or 2-1 on OE# pin to pull-high as output disable. The list in below summarized the outputs can be controlled by those 7 OE# pins.

- OE#0 on J44 for 100M0 output

- OE#1 on J45 for 100M1 output

- OE#2 on J46 for 100M2 output

- OE#3 on J47 for 100M3 output

- OE#4 on J48 for 100M4 output

- OE#5 on J49 for 100M5 output

- OE#6 on J50 for 100M6 output

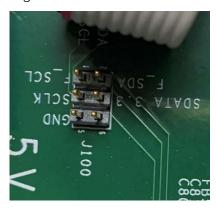

Figure 8. Headers for SCL and SDA Pins

J100 provides headers as another option which can be used to connect with SCL and SDA pins with an Aardvark Adapter.

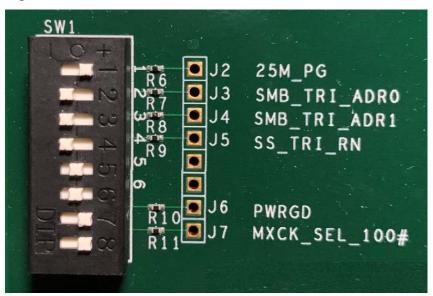

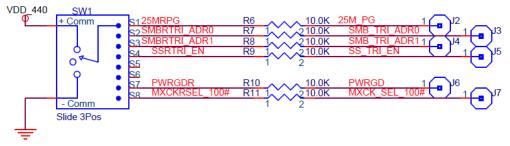

Figure 9. DIP Switch Control

The DIP switch (SW1) connects to pins on the 9SQ440 devices. The middle position leaves the pin open. This is the default for each switch. Move to the "+" side to pull the pin high and move to the "-" side to pull the pin low.

- Switch 1 = 25M\_PG: Connects to the 25MPG pin for 25MHz outputs enable in shut-down operation. Set to High as default on evaluation board

- Switch 2 = SMB\_TRI\_ADR0: Connects to the SMB\_ADR0\_tri pin. Set as Low to be default on evaluation board

- Switch 3 = SMB\_TRI\_ADR1: Connects to the SMB\_ADR1\_tri pin. Set as Low to be default on evaluation board

The main purpose of Switch 2 and Switch3 is to set SMBus addresses for 9SQ440 based on Table 2 below. The evaluation board has set SMBus address to be D2.

Table 2. SMBus Address Selection

| SMB_ADR1_tri | SMB_ADR0_tri | SMBus Address |

|--------------|--------------|---------------|

| L            | L            | D2            |

| L            | M            | D4            |

| L            | Н            | D6            |

| M            | L            | B2            |

| M            | M            | B4            |

| M            | Н            | B6            |

| Н            | L            | ВА            |

| Н            | М            | BC            |

| Н            | Н            | BE            |

- Switch 4 = SS\_TRI\_RN: Connects to the SS\_tri\_En pin. The main purpose of this switch is to control spread modulation on 100MHz outputs to be enabled as pull-up or disabled as pull-low.

- Switch 5 = No Connect.

- Switch 6 = No Connect.

- Switch 7 = PWRGDR: Connects to the PWRGD pin. The main purpose of this switch is to set 9SQ440 operated in a normal operational mode as this switch to set High or in power-down mode as this switch to set Low. Set as High to be default on evaluation board.

- Switch 8 = MXCK\_SEL\_100#: Connects to the MXCK\_SEL\_100# pin. The main purpose of this switch is to control MXCK outputs to run either 100MHz or 25MHz. Pull-low for the outputs to be running at 25MHz. Pull-high for the outputs to be running at 100MHz. The default setting of this switch is to be High for 100MHz on the outputs.

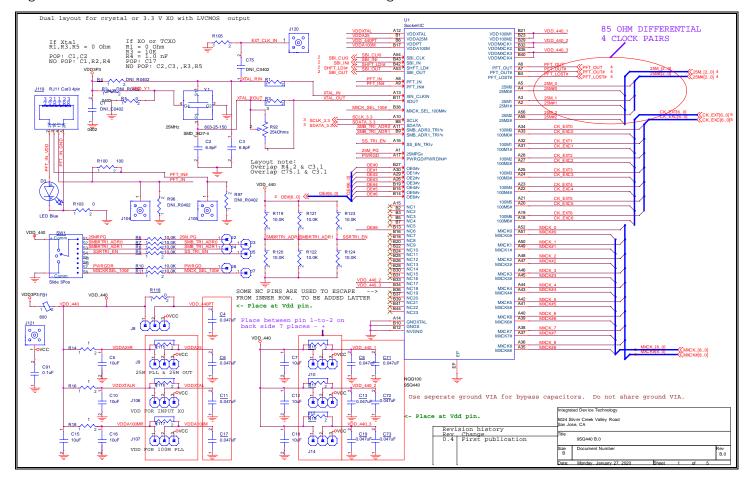

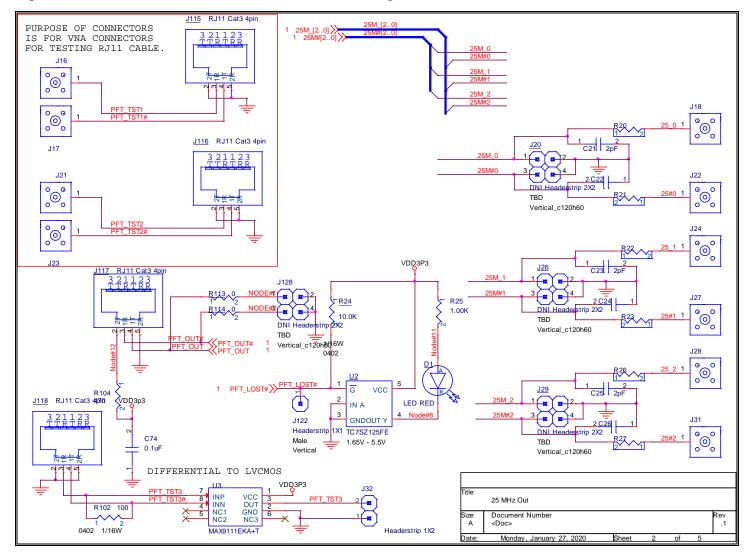

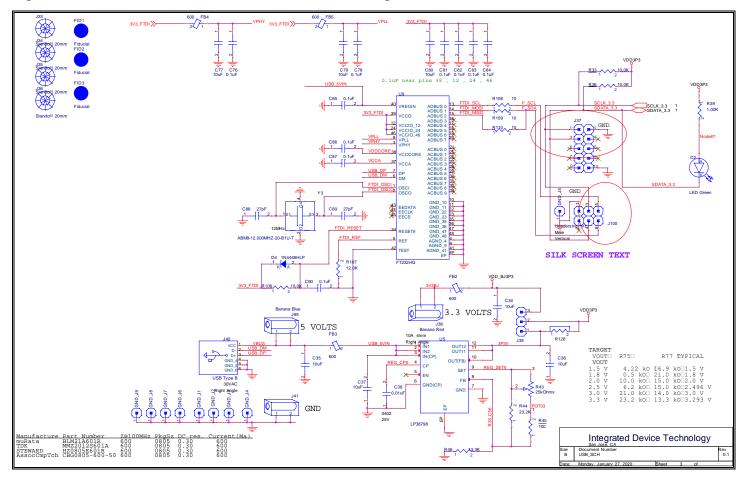

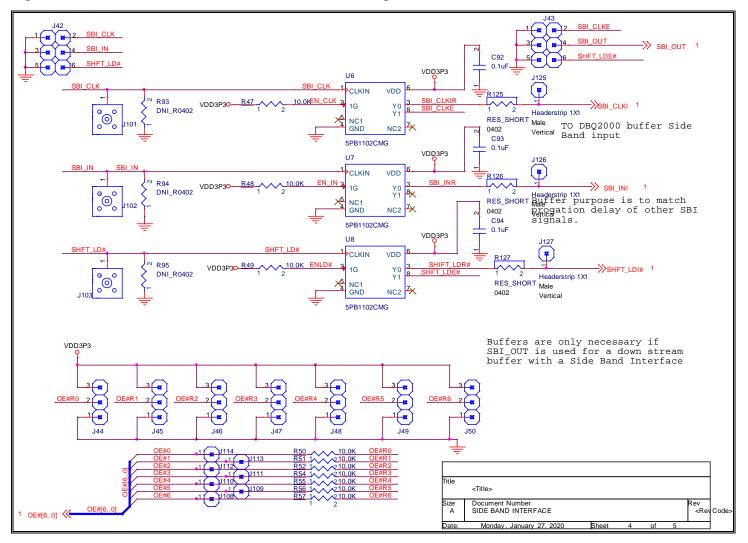

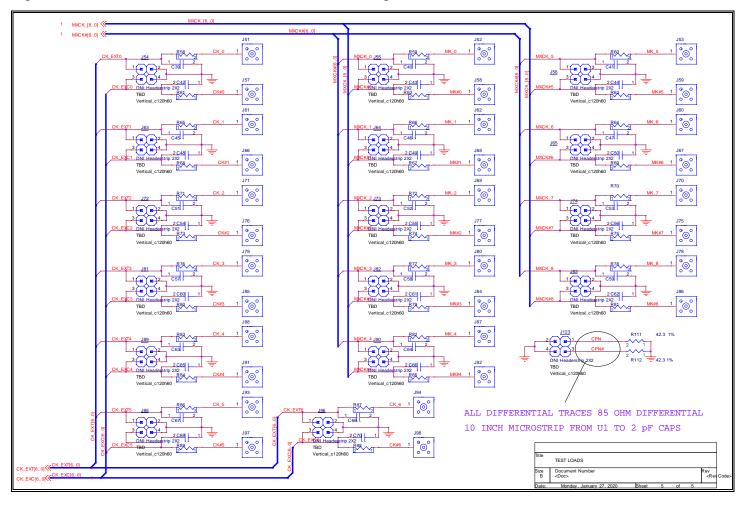

## 6. Board Schematics

Figure 10. 9SQ440 Evaluation Board Schematics - Page 1

Figure 11. 9SQ440 Evaluation Board Schematics - Page 2

Figure 12. 9SQ440 Evaluation Board Schematics - Page 3

Figure 13. 9SQ440 Evaluation Board Schematics - Page 4

Figure 14. 9SQ440 Evaluation Board Schematics - Page 5

# 7. Ordering Information

| Orderable Part Number | Description              |

|-----------------------|--------------------------|

| 9SQ440-EVB            | 9SQ440 Evaluation Board. |

# 8. Revision History

| Revision Date     | Description of Change                                                           |

|-------------------|---------------------------------------------------------------------------------|

| May 19, 2020      | <ul><li>Rebranded document.</li><li>Minor formatting/edits performed.</li></ul> |

| April 09, 2020    | Updated schematic to RevB.                                                      |

| February 09, 2020 | Initial release.                                                                |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.