# ZSSC3240

Sensor Signal Conditioner IC for Resistive Sensors

## **Description**

The ZSSC3240 is a sensor signal conditioning IC (SSC) for highly accurate amplification, digitization, and sensor-specific correction of resistive sensor signals. The ZSSC3240 is suitable for bridge and half-bridge sensors, as well as external voltage-source element and single-element sensors (e.g., Pt100 and external temperature sensor diodes) powered by an on-chip current source. Digital compensation of the sensor offset, sensitivity, temperature drift, and non-linearity is accomplished via a 26-bit math core running a correction algorithm with calibration coefficients stored in a non-volatile, reprogrammable memory. The programmable, integrated sensor front-end allows optimally applying various sensors for a broad range of applications.

The ZSSC3240 provides measurement value readouts and programming capabilities via an I2C, SPI, or one-wire interface (OWI). Three different operation modes allow optimal development of digital, digital-analog, and analog-output smart sensor modules including wake-up on request, continuous-on/fast-response, and automatic/cyclic sensor measurement operations. Absolute and ratiometric voltage, current-loop, or interrupt analog outputs are supported by the ZSSC3240. The analog output options and digital interface options (for calibration and/or a digital application interface) can be combined.

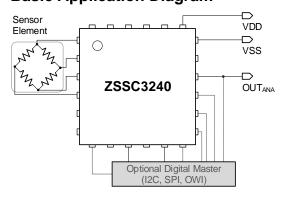

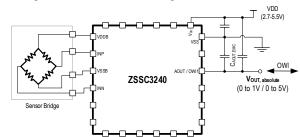

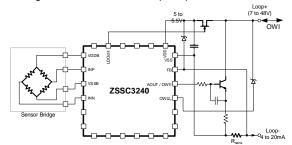

#### **Basic Application Diagram**

#### **Features**

- · Digital communication and calibration interfaces

- 。 SPI up to 10MHz

- <sub>o</sub> I2C (Standard, Fast, and High-Speed Mode)

- one-wire-interface (OWI), up to 100kBit/s

- Accommodates nearly all resistive bridge sensor types (signal spans from 1mV/V up to 500mV/V)

- Supports different sensor element configurations:

- 。 Resistive bridge or half-bridge

- Resistive divider string

- Voltage source

- · On-chip temperature sensor

- External temperature sensing supported, e.g. sensor-bridge as temperature detector, external diode, etc.

- Support for Pt100

- Programmable 16-bit digital-to-analog-converter and output:

- 。 (0V to 1V) or (0V to 5V) absolute voltage output

- 。 V<sub>DD</sub>-ratiometric voltage output

- 。 4mA to 20mA current-loop output supported

- 0V to 10V absolute-voltage output supported

- On-chip voltage regulators for sensor supply, and IC operation

- Support for extra regulation by external transistor, for example JFET

- Programmable 24-bit sensor-signal-conditioning math core

- Reprogrammable, nonvolatile memory (NVM)

- Programmable measurement scheduler for continuous sensing applications, with optimized balance of

- 。 Energy consumption

- Output update rate

- Sensor-signal-conditioning accuracy

- Self-diagnostic coverage and system safety

- · On-chip diagnostics:

- Sensor connection

- Broken-chip-check / chipping-check

- Memory integrity

## **Physical Characteristics**

- Supply voltage, V<sub>DD</sub>: 2.7V to 5.5V; with external transistor, for example JFET: 5V to 48V

- Operating temperature: -40°C to 125°C

- Supported sensor elements:  $0.5k\Omega$  to  $60k\Omega$

- Available as die on wafers or 4 x 4 mm<sup>2</sup> 24-QFN with wettable flanks, allowing visual inspection of QFN reflow quality

### **Typical Applications**

- Calibrated, continuously operating sensors with digital interface and/or analog output: (absolute or ratiometric) voltage or current loop output

- Enables smart, digital sensors for energy-efficient solutions

- · Pressure, flow, and level sensing

- Industrial applications; e.g. process/factory automation

- Consumer / white goods, e.g. HVAC, weight scales

- Medical applications, e.g. blood pressure, continuous smart health monitors

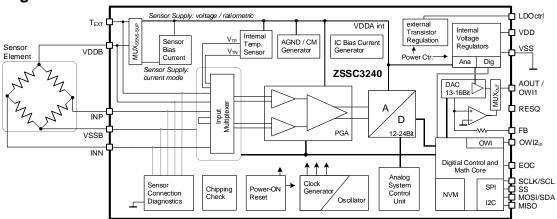

## **Block Diagram**

# **Typical Application Examples**

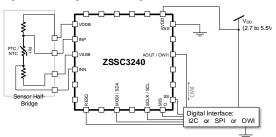

Digital Half-Bridge Sensor, e.g. PT100

Sensor with Ratiometric Voltage Output and Digital Interface

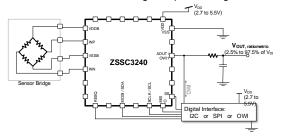

Analog Sensor with Absolute Voltage Out

Analog Sensor with Current Loop Output, OWI, and External JFET

# **Contents**

| 1.  | Pin Assignments6       |            |                                                                                     |    |  |  |  |

|-----|------------------------|------------|-------------------------------------------------------------------------------------|----|--|--|--|

| 2.  | Pin D                  | escriptio  | ons                                                                                 | 7  |  |  |  |

| 3.  | Abso                   | lute Max   | imum Ratings                                                                        | 8  |  |  |  |

| 4.  | Reco                   | mmende     | d Operating Conditions                                                              | 8  |  |  |  |

| 5.  | Elect                  | rical Cha  | racteristics                                                                        | 8  |  |  |  |

| 6.  | Devic                  | ce Descri  | ption                                                                               | 11 |  |  |  |

|     | 6.1                    | Signal F   | low                                                                                 | 12 |  |  |  |

|     | 6.2                    | Analog (   | Sensor) Front-End                                                                   | 12 |  |  |  |

|     |                        | 6.2.1.     | Programmable-Gain Amplifier (PGA)                                                   | 13 |  |  |  |

|     |                        | 6.2.2.     | Analog-to-Digital Converter (ADC)                                                   |    |  |  |  |

|     |                        | 6.2.3.     | Internal Temperature Sensor                                                         | 17 |  |  |  |

|     |                        | 6.2.4.     | Supported Supplies for Sensor Elements and Additional, External Temperature Sensing | 17 |  |  |  |

|     | 6.3                    | On-Chip    | Diagnostics                                                                         | 22 |  |  |  |

|     | 6.4                    | Digital Ir | nterfaces                                                                           | 24 |  |  |  |

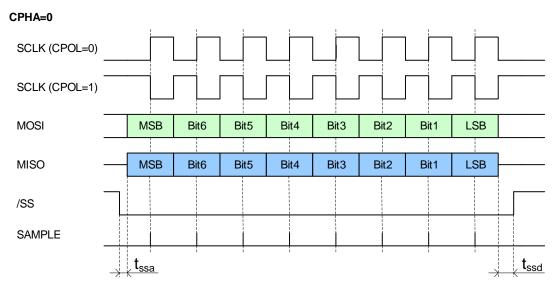

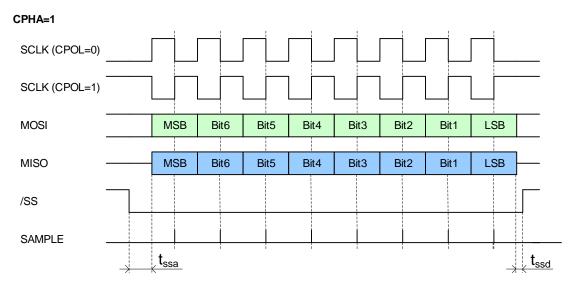

|     |                        | 6.4.1.     | SPI                                                                                 | 24 |  |  |  |

|     |                        | 6.4.2.     | I2C                                                                                 | 27 |  |  |  |

|     |                        | 6.4.3.     | One-Wire-Interface, OWI                                                             | 28 |  |  |  |

|     | 6.5                    | Measure    | ement and Output Options                                                            | 32 |  |  |  |

|     |                        | 6.5.1.     | Single Measurements, Digital Raw Results, and SSC Results                           | 32 |  |  |  |

|     |                        | 6.5.2.     | Cyclic, Continuous, Repeated Measurements – Measurement Scheduler                   | 34 |  |  |  |

|     |                        | 6.5.3.     | Analog Outputs: Digital-to-Analog Converter (DAC)                                   | 35 |  |  |  |

|     |                        | 6.5.4.     | Output Interrupt Signaling                                                          | 38 |  |  |  |

|     | 6.6                    | System     | Setup and Control                                                                   | 40 |  |  |  |

|     |                        | 6.6.1.     | Digital Commands                                                                    | 40 |  |  |  |

|     |                        | 6.6.2.     | Nonvolatile Memory (NVM)                                                            | 43 |  |  |  |

|     |                        | 6.6.3.     | Digital Sensor-Signal-Conditioning Mathematics                                      | 55 |  |  |  |

|     | 6.7                    | External   | , Extra LDO (LDOctrl) for Applications for > 5.5V                                   | 58 |  |  |  |

| 7.  | Calib                  | ration     |                                                                                     | 59 |  |  |  |

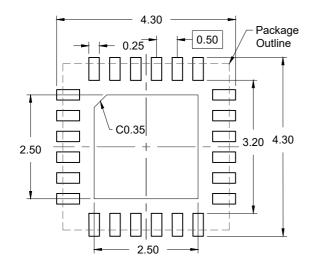

| 8.  | Pack                   | age Outli  | ne Drawings                                                                         | 59 |  |  |  |

| 9.  | Mark                   | ing Diagı  | ram                                                                                 | 59 |  |  |  |

| 10. | Ordering Information60 |            |                                                                                     |    |  |  |  |

| 11. | Glossary               |            |                                                                                     |    |  |  |  |

| 12. | Revis                  | sion Histo | ory                                                                                 | 61 |  |  |  |

# **Figures**

| Figure 1.  | Pin Assignments for 4 × 4 mm <sup>2</sup> 24-QFN Package – Top View                  | 6  |

|------------|--------------------------------------------------------------------------------------|----|

| Figure 2.  | Pin (Pad) Assignments for Bare Die                                                   | 6  |

| Figure 3.  | Main Operating Modes of the ZSSC3240                                                 | 11 |

| Figure 4.  | Analog Sensor Front-End Topology                                                     |    |

| Figure 5.  | SPI Configuration CPHA=0                                                             | 25 |

| Figure 6.  | SPI Configuration CPHA=1                                                             | 25 |

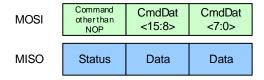

| Figure 7.  | SPI Command Request                                                                  | 26 |

| Figure 8.  | SPI Read Data                                                                        | 26 |

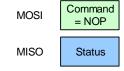

| Figure 9.  | SPI Read Status                                                                      | 26 |

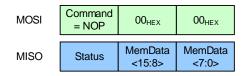

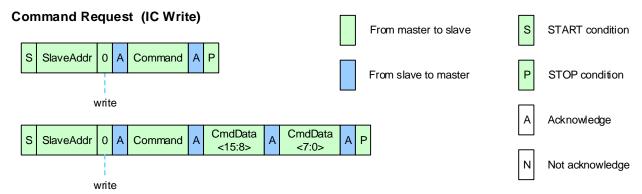

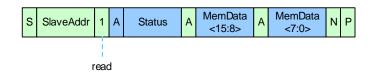

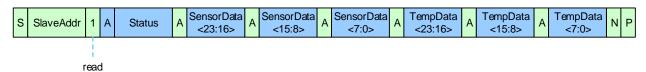

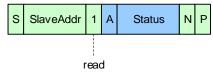

| Figure 10. | I2C Command Request                                                                  | 27 |

| Figure 11. | I2C Read Data                                                                        | 27 |

| Figure 12. | I2C Read Status                                                                      | 27 |

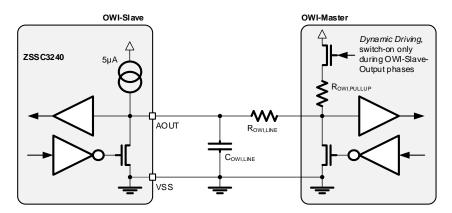

| Figure 13. | General Block Schematic of the OWI Interface                                         | 28 |

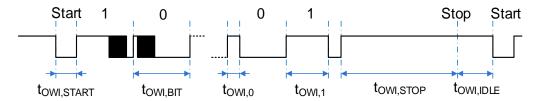

| Figure 14. | OWI Timing Diagram                                                                   | 29 |

| Figure 15. | OWI Extra (Activation) Pulse for Concurrent OWI and Analog Output Configuration      | 29 |

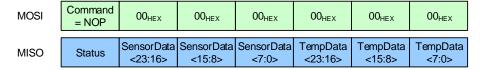

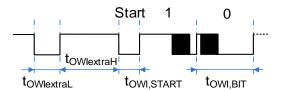

| Figure 16. | OWI Command Request                                                                  | 30 |

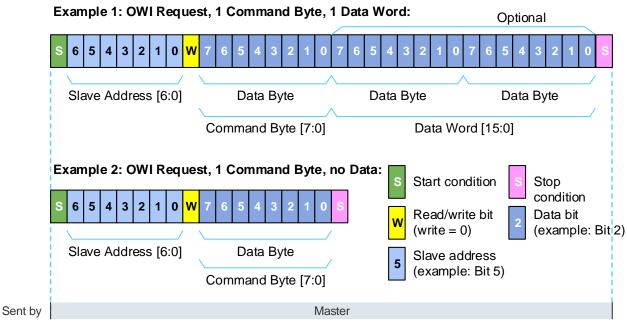

| Figure 17. | OWI Response by ZSSC3240                                                             | 31 |

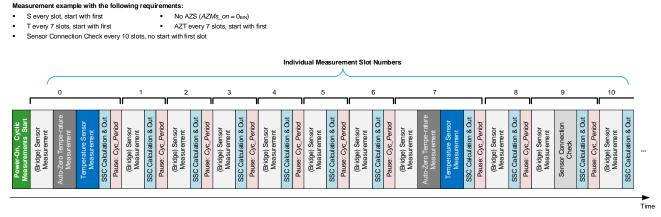

| Figure 18. | Example Configuration for the Measurement Scheduling and Cyclic Mode Operation       | 34 |

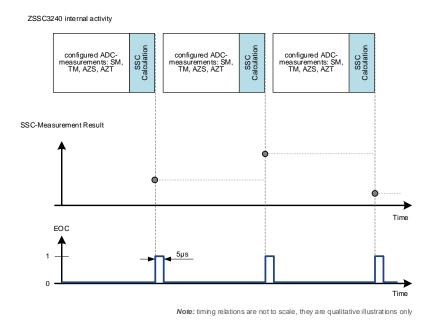

| Figure 19. | Measurement Result Output Update in Cyclic Operation (with "Slow" Interface Polling) | 35 |

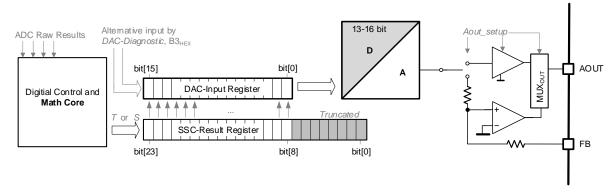

| Figure 20. | DAC and Analog Output Topology                                                       | 35 |

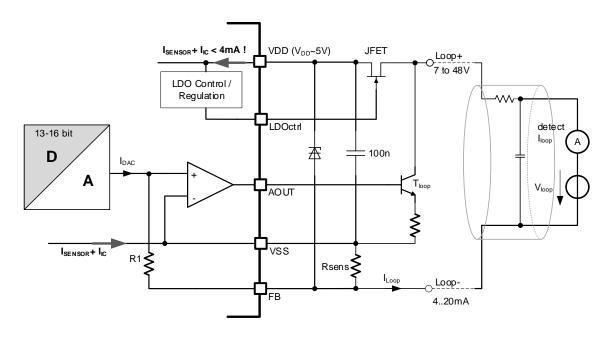

| Figure 21. | Current Loop Configuration                                                           | 38 |

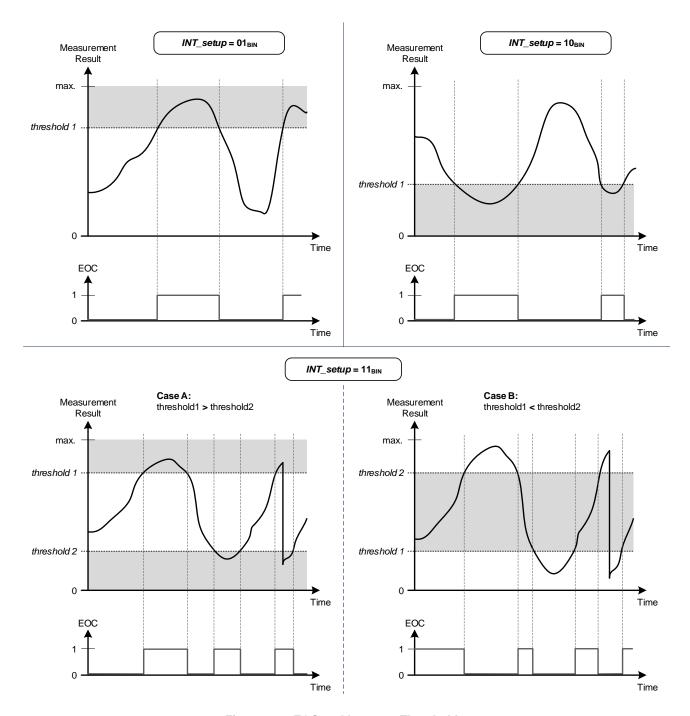

| Figure 22. | EOC-Behavior: Signalization of End-of-Conversion (INT_setup = 00 <sub>BIN</sub> )    | 38 |

| Figure 23. | EOC and Interrupt Thresholds                                                         | 39 |

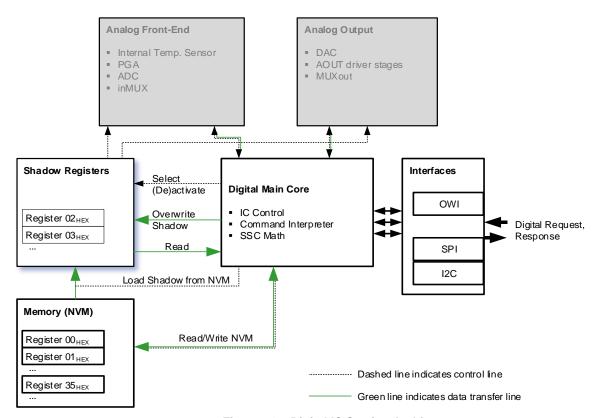

| Figure 24. | Digital IC Section Architecture                                                      | 40 |

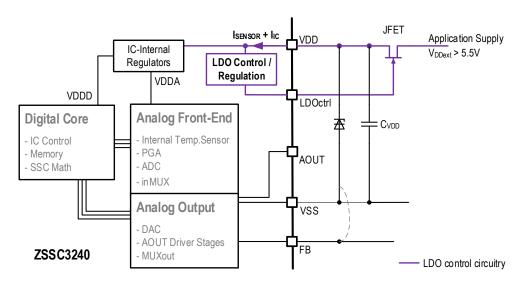

| Figure 25. | LDOctrl Application Topology                                                         | 58 |

# **Tables**

| Table 1.  | Pin Descriptions                                                                     | 7  |

|-----------|--------------------------------------------------------------------------------------|----|

| Table 2.  | Absolute Maximum Ratings                                                             | 8  |

| Table 3.  | Recommended Operating Conditions                                                     | 8  |

| Table 4.  | Electrical Characteristics                                                           | 8  |

| Table 5.  | PGA Gain: Stage 1                                                                    | 13 |

| Table 6.  | PGA Gain: Stage 2                                                                    | 14 |

| Table 7.  | Absolute Offset Shift – Properties                                                   | 14 |

| Table 8.  | Absolute Offset Shift – Differential Sensor Signal's Offset Compensation             | 14 |

| Table 9.  | PGA Input Span Ranges                                                                | 15 |

| Table 10. | Single Analog-to-Digital Conversion                                                  | 16 |

| Table 11. | ADC Offset Shift                                                                     | 16 |

| Table 12. | Sensor Supply Options                                                                | 17 |

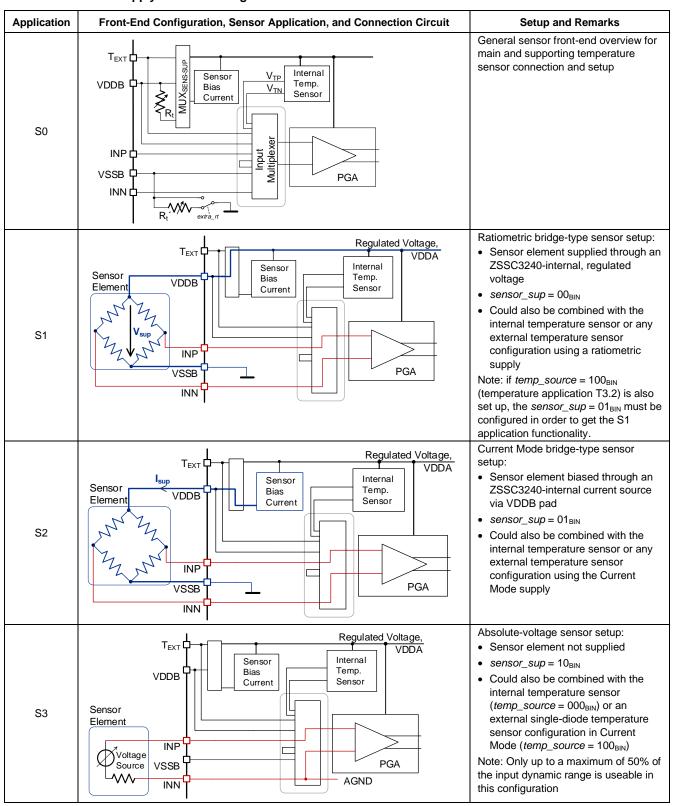

| Table 13. | Sensor Supply – Main Sensing                                                         | 18 |

| Table 14. | Sensor Bias Currents – Sensor Sourcing in Current Mode                               | 19 |

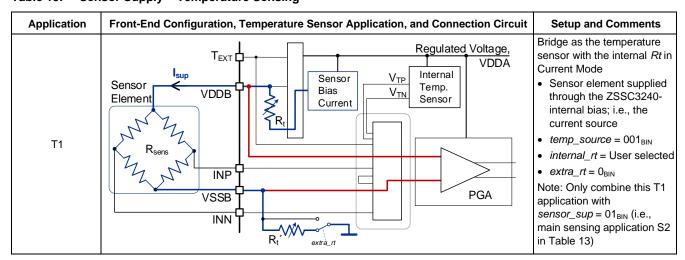

| Table 15. | Sensor Supply – Temperature Sensing                                                  | 19 |

| Table 16. | Diagnostic Signalization Options with ZSSC3240                                       | 22 |

| Table 17. | Information Assignment for CHECK_DIAG Command: Output Register diagnosticreg [15:0]  | 23 |

| Table 18. | General Status Byte                                                                  | 24 |

| Table 19. | Mode Status                                                                          | 24 |

| Table 20. | SPI Interface Parameter                                                              | 26 |

| Table 21. | I2C Interface Parameter                                                              | 27 |

| Table 22. | OWI Dimensioning Examples                                                            | 29 |

| Table 23. | OWI Interface Parameters                                                             | 29 |

| Table 24. | Data Format of Raw ADC Readings                                                      | 32 |

| Table 25. | Data Format of Corrected, SSC Results (S and T)                                      | 32 |

| Table 26. | Typical Conversion Times for Complete SSC Sensor Measurements: SM, TM                | 33 |

| Table 27. | Typical Conversion Times and Noise Performance for Complete SSC Measurements         | 33 |

| Table 28. | DAC Configurations                                                                   | 35 |

| Table 29. | Direct Voltage Outputs                                                               | 36 |

| Table 30. | Recommended Operating Conditions for Voltage Output                                  | 36 |

| Table 31. | ZSSC3240 Current-Loop-Specific Properties                                            | 37 |

| Table 32. | Data Format of Interrupt Thresholds (TRSH1 and TRSH2)                                | 39 |

| Table 33. | Command List                                                                         | 40 |

| Table 34. | Memory (NVM) Content Assignments                                                     | 44 |

| Table 35. | Data Format of 24-bit SSC Coefficients                                               | 55 |

| Table 36. | Data Format of Corrected, SSC Results (S and T)                                      | 56 |

| Table 37. | IC Supply, VDD Target Level Selection with External Voltage Regulation, External LDO | 58 |

| Table 38. | External LDO Operating Conditions                                                    | 58 |

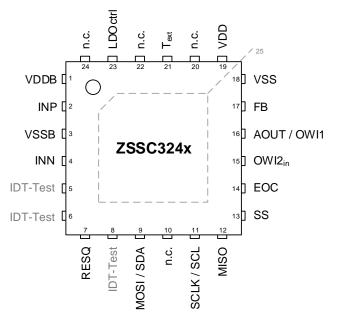

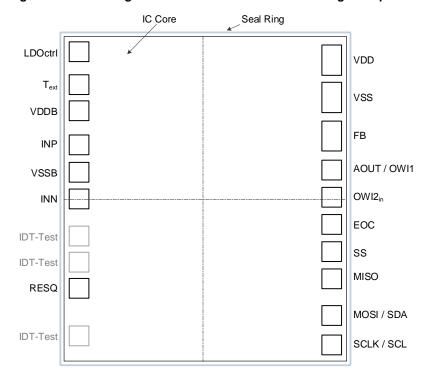

# 1. Pin Assignments

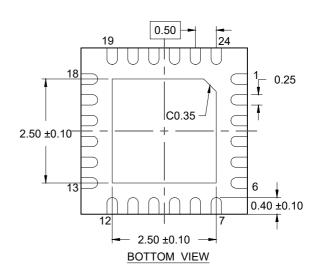

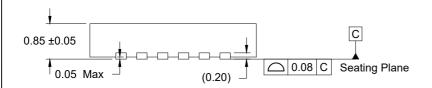

The ZSSC324x is available as 8-inch wafers and in a 24-QFN package. Detailed information about die and wafers is available on request (see last page for contact information).

——— : QFN-bottom plate, Exposed PAD.

Figure 1. Pin Assignments for 4 × 4 mm<sup>2</sup> 24-QFN Package – Top View

Figure 2. Pin (Pad) Assignments for Bare Die

# 2. Pin Descriptions

Table 1. Pin Descriptions

| Pin Number | Name               | Туре                                      | Description                                                                                                                                                                  |

|------------|--------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VDDB               | Analog<br>Input/Output                    | Positive sensor (bridge) supply or sensor-signal input.                                                                                                                      |

| 2          | INP                | Analog Input                              | Positive sensor (bridge) signal.                                                                                                                                             |

| 3          | VSSB               | Analog Input                              | Sensor (bridge) ground or sensor-signal input.                                                                                                                               |

| 4          | INN                | Analog Input                              | Negative sensor (bridge) signal.                                                                                                                                             |

| 5          | IDT-test           | _                                         | Renesas-internal use only. Connect to VSS or no connection; leave pin floating.                                                                                              |

| 6          | IDT-test           | _                                         | Renesas-internal use only. Connect to VSS or no connection; leave pin floating.                                                                                              |

| 7          | RESQ               | Digital Input                             | Digital IC reset (low active); internal pull-up.                                                                                                                             |

| 8          | IDT-test           | _                                         | Renesas-internal use only. Connect to VSS or no connection; leave pin floating.                                                                                              |

| 9          | MOSI/SDA           | Digital<br>Input/Output                   | Digital data input for SPI or bidirectional data I/O for I2C. Pull-up to VDD.                                                                                                |

| 10         | n.c.               | -                                         | No connection. Leave pin floating.                                                                                                                                           |

| 11         | SCLK/SCL           | Digital Input                             | Clock input for SPI or I2C interface. Referenced to applied VDD level.                                                                                                       |

| 12         | MISO               | Digital Output                            | Data output from ZSSC3240 to master for SPI interface. Referenced to applied VDD level.                                                                                      |

| 13         | SS                 | Digital Input                             | Slave select (interface enable) for SPI. Referenced to applied VDD level.                                                                                                    |

| 14         | EOC                | Digital Output                            | End-of-conversion and output interrupt signal.                                                                                                                               |

| 15         | OWI2 <sub>in</sub> | Digital Input                             | Optional OWI interface input line for current-loop applications.                                                                                                             |

| 16         | AOUT/OWI1          | Analog Output;<br>Digital<br>Input/Output | Analog smart-sensor output signal and/or OWI-interface input/output line.  Short-circuit protection, capping the short-circuit current at 10-12mA.                           |

| 17         | FB                 | Analog Output                             | Current-loop application feedback output (level below VSS!). No connection if not used.                                                                                      |

| 18         | VSS                | Ground                                    | Power supply ground.                                                                                                                                                         |

| 19         | $V_{DD}$           | Supply                                    | Power supply.                                                                                                                                                                |

| 20         | n.c.               | _                                         | No connection. Leave pin floating.                                                                                                                                           |

| 21         | T <sub>EXT</sub>   | Analog Output                             | Current drive output for external temperature sensor and/or bridge in Current Mode. A $150\Omega$ serial resistor is built in the IC internally for pad-protection purposes. |

| 22         | n.c.               | _                                         | No connection. Leave pin floating.                                                                                                                                           |

| 23         | LDOctrl            | Analog Output                             | Control output (reference signal) for (optional) external regulator / supply control loop.                                                                                   |

| 24         | n.c.               | _                                         | No connection. Leave pin floating.                                                                                                                                           |

| 25         | Exposed PAD        |                                           | QFN-bottom plate, i.e. Die-bottom/substrate. Connect to VSS, PAD to be used for heat dissipation and additional EMC robustness.                                              |

# 3. Absolute Maximum Ratings

The absolute maximum ratings are stress ratings only. Stresses greater than those listed below can cause permanent damage to the device. Functional operation of the ZSSC3240 at absolute maximum ratings is not implied. Exposure to absolute maximum rating conditions might affect device reliability.

Table 2. Absolute Maximum Ratings

| Symbol        | Parameter                          | Conditions                         | Minimum | Maximum | Units |

|---------------|------------------------------------|------------------------------------|---------|---------|-------|

| TJ            | Junction temperature               |                                    |         | 135     | °C    |

| Ts            | Storage temperature                |                                    | -45     | 150     | °C    |

|               | ESD – Human Body Model             |                                    |         | 4000    | V     |

|               | ESD – Charged Device Model         |                                    |         | 750     | V     |

|               | Latch-up                           |                                    | -100    | +100    | mA    |

| $V_{DD\_max}$ | Maximum allowed for voltage supply | Referenced to VSS.                 | -0.3    | 6.5     | V     |

| $V_{IF\_max}$ | Voltage at digital interface pins  | I2C pins: SDA, SCL                 | -0.3    | 5.5     | V     |

| $V_{FB\_max}$ | Voltage at FB pin                  | 4mA to 20mA current loop interface | -2      | 2       | V     |

# 4. Recommended Operating Conditions

Table 3. Recommended Operating Conditions

| Symbol                    | Parameter                                                                                                     | Minimum | Typical | Maximum | Units   |

|---------------------------|---------------------------------------------------------------------------------------------------------------|---------|---------|---------|---------|

| $V_{DD}$                  | Power supply voltage                                                                                          |         | _       | 5.5     | V       |

| T <sub>A</sub>            | Ambient temperature (depending on the part code)                                                              | -40     | _       | 125     | °C      |

|                           | External (parasitic) capacitance between VDD and VSS, without external supply transistor regulation           | 0       | 10      | _       | nF      |

| $C_{VDD}$                 | External (parasitic) capacitance between VDD and VSS, with (optional) external supply transistor regulation   | 80      | 100     | 120     | nr<br>I |

| $C_{\text{VDDB,EMC}}$     | Recommended, external capacitance between VDDB and VSS for electro-magnetic immunity (EMI)                    | 0       | 6.8     | 8       | nF      |

| $C_{AOUT,EMC}$            | Recommended, external capacitance between AOUT versus VSS, and versus VDD for EMI [a]                         | 0       | 22      | 33      | nF      |

| I <sub>Sensor</sub>       | Load current through external sensor element [b]                                                              | 0.02    | 0.5     | 4       | mA      |

| $V_{DioDrop}$             | External temperature diode and RTD input range, drop over external element referenced to T <sub>EXT</sub> pin | -0.2    | -       | 1       | V       |

| $V_{Sens\_in}$            | Absolute sensor signal input level, INN, INP pins                                                             | 0.5     | _       | 1.2     | V       |

| VDDB <sub>ratio_min</sub> | Minimum level at VDDB [b]                                                                                     | 0.9     | _       | _       | V       |

| VSSB <sub>ratio_max</sub> | Maximum level at VSSB [b]                                                                                     | -       | _       | 0.7     | V       |

| I <sub>max_AOUT_V</sub>   | Maximum current load at AOUT pin for voltage outputs                                                          | -       | -       | 18      | mA      |

| $SR_{VDD\_POR}$           | Recommended V <sub>DD</sub> rise slew rate for power-on-reset (POR) <sup>[c]</sup>                            | 1.5     | _       | _       | V/ms    |

<sup>[</sup>a] For applications with OWI-interface or analog voltage-output.

# 5. Electrical Characteristics

All parameter values are valid only under specified operating conditions. All voltages are referenced to Vss.

Table 4. Electrical Characteristics

Note: See important notes at the end of this table.

| Symbol            | Parameter                                  | Conditions                                                                     | Minimum | Typical | Maximum   | Units |

|-------------------|--------------------------------------------|--------------------------------------------------------------------------------|---------|---------|-----------|-------|

|                   | IC Supply                                  |                                                                                |         |         |           |       |

| I <sub>IC</sub>   | Current consumption, active IC             | Excluding connected sensor elements (with LDOctrl enabled)                     | _       | 2.3     | 2.80      | mA    |

| I <sub>IDLE</sub> | Idle current consumption, IC in Idle State | Typical value at 30°C, maximum value at 85°C (125°C)  OWI and LDOctrl disabled | -       | 1.5     | 6<br>(22) | μА    |

<sup>[</sup>b] With ratiometric sensor supply configuration; e.g. a ratiometric bridge or bridge as temperature sensor with internal or external Rt.

<sup>[</sup>c] Per design, there is no (theoretical) minimum V<sub>DD</sub> slew rate to trigger a clean POR. Nevertheless, a reasonable slew rate is recommended.

| Symbol                         | Parameter                                                                                             | Conditions                                                                                                              | Minimum                  | Typical                  | Maximum                   | Units  |

|--------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|---------------------------|--------|

| I <sub>AVE</sub>               | Average current draw                                                                                  | Mean current consumption for one complete SSC measurement cycle per second at 16-bit digital-only output                | _                        | -                        | 3.5                       | μА     |

| $V_{DD,LDOctrl}$               | Target level regulation range to generate V <sub>DD</sub> after external transistor, for example JFET | Using LDOctrl and external transistor; programmable setup: VDD_ldoctrl_target (see section 6.7)                         | 4.6                      | 5.2                      | 5.5                       | V      |

|                                |                                                                                                       | Sensor Supply                                                                                                           |                          |                          |                           |        |

| I <sub>SUP</sub>               | Sensor bias                                                                                           | In the case of a Current Mode sensor                                                                                    | 5                        | 80                       | 500                       | μA     |

| Err <sub>TBIAS</sub>           | Relative sensor bias current error [a]                                                                | supply; setup in temp_source and sensor_sup (see section 6.2)                                                           | -3.5                     | -1                       | 1.5                       | %      |

| $V_{TBIAS}$                    | Drop over sensor bias current source                                                                  | referenced VDDA <sub>int</sub> from internal analog regulator                                                           | _                        | 200                      | 230                       | mV     |

| VDDB<br>(VDDA <sub>int</sub> ) | Internally regulated analog (bridge) sensor front-end supply                                          | In the case of a ratiometric sensor supply, setup in <i>temp_source</i> and <i>sensor_sup</i>                           | 1.68                     | 1.75                     | 1.80                      | V      |

| PSRR <sub>LOW</sub>            | Power supply rejection ratio <sup>[b]</sup> , only internal                                           | Attenuation of $V_{DD}$ fluctuations in the range of $f_{VDD} = 0$ Hz to 10MHz                                          | 45                       | 50                       | _                         | dB     |

| PSRR <sub>HIGH</sub>           | regulator                                                                                             | $f_{VDD} > 10MHz$                                                                                                       | 20                       | _                        | _                         | dB     |

|                                | T =                                                                                                   | Analog-to-Digital Converter (ADC, A2D                                                                                   |                          |                          | <u> </u>                  |        |

| rADC                           | Resolution                                                                                            |                                                                                                                         | 12                       | 16                       | 24                        | Bit    |

| $f_{S,raw}$                    | Single-conversion rate, conversions per second                                                        | Single external sensor A2D conversion (without auto-zero measurement AZ); resolution dependent                          | 0.21<br>(ADC:<br>24-bit) | 3.39<br>(ADC:<br>16-bit) | 13.00<br>(ADC:<br>12-bit) | kHz    |

| V <sub>ADCmid</sub><br>(AGND)  | Differential ADC input common mode [c]                                                                | With internal regulator supplying VDDB pin, typical: VDDB/2 = 875mV (equals PGA output common mode level)               | _                        | 0.5                      | _                         | VDDB   |

| ENOB [9]                       | Effective number of bits, $3\sigma_{\text{Noise}}$ based                                              | For gain < 78, shorted input, rADC = 24-bit, no oversampling                                                            | 15.8                     | 18.1                     | _                         | Bit    |

|                                |                                                                                                       | ital-to-Analog Converter (DAC) and Analog                                                                               |                          |                          | 1                         | 5      |

| r <sub>DAC</sub>               | Resolution                                                                                            | The a fire as 000% at a site at a track and 1 000% af                                                                   | 13                       | 14                       | 16                        | Bit    |

| t <sub>DACsettle</sub>         | Analog voltage output settling time                                                                   | Time from 30% steady state until 99% of<br>new DAC output (100% out) value is<br>reached; varies with level differences | 0                        | 65                       | 150                       | μs     |

|                                | Addresselle eutput                                                                                    | Absolute output, $Aout\_setup = 010_{BIN}$ (see section 6.5.3.1)                                                        | 0.025                    | _                        | 1                         | V      |

| $V_{DACout}$                   | Addressable output voltage at AOUT pin                                                                | Absolute output, $V_{DD} > 5.01V$ ,<br>$Aout\_setup = 011_{BIN}$                                                        | 0.025                    | _                        | 5                         | V      |

|                                |                                                                                                       | Ratiometric output, Aout_setup = 001 <sub>BIN</sub>                                                                     | 0.1                      | _                        | 100                       | %VDD   |

| BW <sub>DAC</sub>              | Output filter bandwidth                                                                               | Without external components                                                                                             | 12                       | 15                       | 20                        | kHz    |

| $SR_out$                       | Output slew rate                                                                                      | Resistive load > $2k\Omega$ ,<br>capacitive load < $20nF$ at Aout,<br>temperature = $25^{\circ}C$                       | 20                       | 100                      | -                         | mV/µs  |

| I <sub>OUTmax</sub>            | Maximum output current                                                                                | This current level must be overdriven from an OWI-Master, if concurrent DAC-output and OWI communication is configured. | 10                       | 12                       | 18                        | mA     |

| I <sub>DRIoop</sub>            | Current loop driving current                                                                          | Aout_setup = 000 <sub>BIN</sub> ; depends on connected bipolar transistor for current loop application                  | _                        | 100                      | 160                       | μΑ     |

|                                | To:                                                                                                   | Programmable-Gain Amplifier (PGA)                                                                                       |                          | 1                        | F 10                      | 1/2/   |

| G <sub>amp</sub>               | Gain                                                                                                  | 120 steps                                                                                                               | 1.32                     | _                        | 540                       | V/V    |

| G <sub>err</sub>               | Gain error Supported input common mode                                                                | Referenced to nominal gain, T = 25°C  VDDA <sub>int</sub> = 1.75V, valid for ratiometric and current mode sensor supply | -2.5<br>0.70             | 0.85                     | 2.5<br>1.00               | %<br>V |

|                                | 1                                                                                                     | Sensor Signal Conditioning Performan                                                                                    | ce                       | 1                        | 1                         | 1      |

|                                |                                                                                                       | Cyclic operation                                                                                                        | 0.07                     | 1.45                     | 2.91                      | kHz    |

| $f_{\sf SSCout}$               | Output (Update) rate [d]                                                                              | SSC-corrected (S, T) digital output rate, ADC:16-bit (see section 6.5.1)                                                | _                        | 1.20                     | -                         | kHz    |

|                                | (-)                                                                                                   | Complete SSC cycle ( <i>S</i> , <i>T</i> ) including analog output update; ADC: 14-bit; DAC: 14-bit                     | 1.35                     | 1.45                     | 1.60                      | kHz    |

|                                | •                                                                                                     |                                                                                                                         | •                        | •                        | •                         |        |

| Symbol                                                                        | Parameter                                                                     | Conditions                                                                                                          | Minimum | Typical | Maximum | Units    |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------|---------|---------|----------|

| $Err_{A,IC}$                                                                  | error sensor (in temperature and measurand)                                   |                                                                                                                     | _       | -       | 0.01    | % FSO    |

| V <sub>ioffsc</sub> Correctable (in PGA), absolute, differential input offset |                                                                               | Programmable in 1mV steps; accuracy: ±5% referenced to nominal setup                                                | -15     | 0       | 15      | mV       |

| $\Delta_{ADC,c}$                                                              | Correctable (in ADC),<br>relative, differential input<br>offset               | Percentage of sensor signal offset versus maximum sensor signal                                                     | 0       | _       | 98      | %        |

|                                                                               |                                                                               | Input                                                                                                               |         |         |         |          |

| $V_{INP},V_{INN}$                                                             | Absolute sensor input                                                         | Voltages at INP and INN pin; resulting minimum/maximum differential voltages: -700mV < V <sub>INdiff</sub> < 700mV  | 0.5     | _       | 1.20    | V        |

| $V_{TEXT}$                                                                    | External temperature diode or RTD input range                                 | At T <sub>EXT</sub> pin                                                                                             | 0.5     | _       | 1.25    | V        |

| D                                                                             | External sensor (bridge)                                                      | VDDB = 1.75V                                                                                                        | 0.5     | _       | 60      | kΩ       |

| R <sub>SENSOR</sub>                                                           | resistance                                                                    | For 4mA to 20mA current loop output                                                                                 | 1.6     | _       | 60      | kΩ       |

| $ V_{\text{DIFFin}} $                                                         | Differential input signal range                                               | Referenced to sensor supply (VDDA <sub>int</sub> ); leading to full scale analog excitation                         | 2.6     | 50      | 700     | mV       |

|                                                                               |                                                                               | Diagnostics                                                                                                         |         |         |         |          |

| $R_{open}$                                                                    | Sensor connection loss; i.e., open threshold                                  | INP vs. INN                                                                                                         | 70      | _       | _       | kΩ       |

| $R_{short}$                                                                   | Sensor connection short threshold                                             | INP vs. INN; T <sub>EXT</sub> vs. VDDB                                                                              | _       | -       | 100     | Ω        |

| $V_{s,valid}$                                                                 | Valid sensor input signal                                                     | Beyond V <sub>s,valid</sub> , sensor connection checks (such as in-range, etc.) signalize Diagnostic <i>FAULT</i> s | 0.44    | _       | 1.31    | V        |

|                                                                               | •                                                                             | Power-Up                                                                                                            | •       | •       |         | •        |

| t <sub>STA1</sub>                                                             | Start-up Time                                                                 | V <sub>DD</sub> ramp up to interface communication                                                                  | _       | _       | 2       | ms       |

| t <sub>STA2</sub>                                                             | Otart up Time                                                                 | V <sub>DD</sub> ramp up to analog operation                                                                         | _       | _       | 2.5     | ms       |

| t <sub>WUP1</sub>                                                             | Wake-up Time                                                                  | Sleep to Active State interface communication                                                                       | _       | 2       | 10      | μs       |

| t <sub>WUP2</sub>                                                             |                                                                               | Sleep to Active State analog operation                                                                              | _       | _       | 2       | ms       |

|                                                                               | 1                                                                             | Oscillator                                                                                                          | T       | ı       | 1       | 1        |

| $f_{\text{CLK}}$                                                              | Internal oscillator frequency                                                 |                                                                                                                     | 5.9     | 6.0     | 6.1     | MHz      |

|                                                                               |                                                                               | Temperature Sensor(s)                                                                                               |         |         |         |          |

| $\mathbf{r}_{Temp}$                                                           | Internal temperature sensor resolution                                        | Setup: ADT <sub>Tsens,int</sub> = 13-bit                                                                            | 12      | 35      | _       | Counts/K |

| Rt, Rt'                                                                       | Internal low TC <sup>[f]</sup> top/bottom resistance for external temperature | Programmable with internal_rt and extra_rt; applied if temp_source ε {010; 110} (see section 6.2.4)                 | 1.34    | _       | 40      | kΩ       |

|                                                                               | T                                                                             | Interface and Memory                                                                                                | T       | T .     | I .     | 1        |

| f <sub>C,SPI</sub>                                                            | SPI clock frequency                                                           |                                                                                                                     | 0.05    | 1       | 12      | MHz      |

| f <sub>C,I2C</sub>                                                            | I2C clock frequency                                                           |                                                                                                                     | -       | _       | 3.4     | MHz      |

| CD <sub>owl</sub>                                                             | OWI data rate                                                                 |                                                                                                                     | 0.33    | -       | 10      | kBit/s   |

| t <sub>PROG</sub>                                                             | NVM program time                                                              | Programming time per 16-bit word                                                                                    | -       | 3       | 7       | ms       |

| n <sub>NVM</sub>                                                              | NVM endurance                                                                 | Number of reprogramming cycles                                                                                      | 1000    | 10000   | _       | Numeric  |

| t <sub>RET,NVM</sub>                                                          | Data retention                                                                |                                                                                                                     | 10      | _       | _       | Years    |

- [a] Referenced to nominal value. Relative errors are typically < 1% for sensor bias current setups > 20µA.

- [b] PSRR = 20·log<sub>10</sub>(V<sub>DD</sub>/V<sub>DDB</sub>): will be improved when applying external filter elements at V<sub>DD</sub> and/or also using an external JFET regulator.

- [c] This parameter must be taken into account if automatic common mode regulation in the PGA is switched off (pga\_en\_shift; see section 6.2.1) and a non-symmetric sensor supply and input to the PGA ADC path have been configured.

- [d] There are several setups and parameters that allow optimizing and maximizing the output update rate; e.g., ADC and DAC resolutions, configurations for the measurement sequence, usage of the internal or an external temperature sensor.

- [e]  $V_{\text{loffsc}}$  and  $\Delta_{\text{ADC,c}}$  can be arbitrarily set up and combined. They work independently on each other.

- [f] Typical residual temperature variation of voltage across Rt, Rt': 10ppm/K; maximum deviation: 150ppm/K at 40kΩ and >100°C, all other setups and conditions < 60ppm/K.

- [g] ENOB =  $log_2(2^{rADC} / 3\sigma_{Noise})$  with, for example rADC[Bit] = 24.

# 6. Device Description

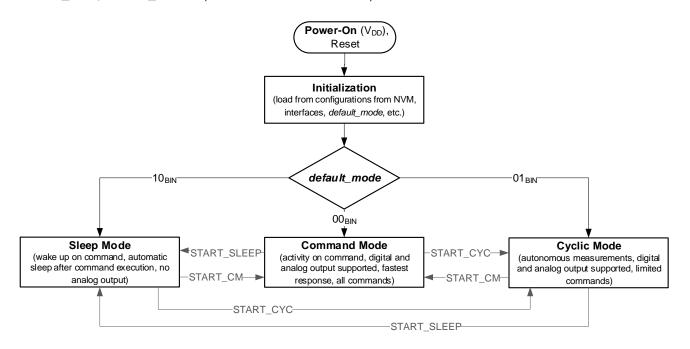

The ZSSC3240 can be set up to for one of three main operating modes:

Sleep Mode

The Sleep Mode is recommended for smart sensors with purely digital output. The ZSSC3240 automatically enters the idle state after command execution for minimum current consumption, whereas the interface is still listening and accepts commands. After receiving a valid command, the ZSSC3240 wakes up, executes the command, provides the results at the digital interface, where the results must be read, and returns to idle state after the data fetch. The results are only available once; repeated data fetch is not supported. In Sleep Mode, sensor measurement results cannot be provided at the analog output of ZSSC3240.

**Command Mode**

The Command Mode is most appropriate for evaluation, test, and calibration purposes. In this mode, all commands are available, both digital and analog outputs are supported and all functionality is available. Command Mode can be used for applications requiring re-occurring (or even continuous) digital interaction, potential analog output, and minimum latency. Applications in Command Mode are only active on command request.

**Cyclic Mode**

In Cyclic Mode, autonomous, cyclically repeated sensor measurements are performed and related digital and/or analog output updates are provided. Cyclic Mode is recommended for analog output applications. The cyclic sequence for measurements, diagnostics, and hence the output update rate is configurable.

The ZSSC3240 always enters the programmed *default\_mode* after power-on (reset). One of the three operating modes can be set up as the default. After the ZSSC3240 is powered and has entered its default mode, changing to one of the other operating modes is possible via the mode change and start commands: *START\_CM*, *START\_SLEEP* (see section 6.6.1 for details).

Figure 3. Main Operating Modes of the ZSSC3240

The ZSSC3240 supports three different types of digital interfaces: I2C, SPI, and OWI. All interface types allow application and control of each of the main operating modes.

Exception: The combination of Sleep Mode as the default mode (see the *default\_mode* bit in the *SSF1* register in Table 34) and the OWI interface is not supported. The OWI interface must be disabled (*owi\_off* = 1, bit[13] in the *SSF1* register) for correct Sleep Mode operation.

When using commands to change the operating mode, e.g. *START\_CM* or *START\_SLEEP*, validation of the new operating mode is recommended; e.g., by reading an NVM register or simply retrieving the status byte.

Note: The ZSSC3240 always requires two or more interface command interactions after an operating mode change prior to any additional changes in the mode.

#### 6.1 Signal Flow

See the figures on page 2 for the ZSSC3240 block diagram and circuit diagrams for different input sensors. The ZSSC3240 supports two sensor supplies: ratiometric voltage and current mode, i.e., sensor current bias. In the ratiometric sensor-supply configuration, VDDB and the power supply for analog circuitry are provided by an onchip voltage regulator, which is optimized for power supply disturbance rejection (PSRR). To improve noise suppression, the digital blocks are powered by a separate voltage regulator. A power supervision circuit monitors all supply voltages and generates appropriate reset signals for initializing the digital blocks.

The System Control Unit controls the analog circuitry to perform the measurement types: external sensor, external or internal temperature, and offset measurement. The multiplexer selects the signal input to the amplifier, which can be the external signals from the input pins INP, INN, T<sub>EXT</sub>, VDDB, and VSSB or the internal temperature reference sensor signals. A full measurement request will trigger an automatic sequence of all measurement types and all input signals. The basic sensor signal source configuration is set up in the *SSF1* register (see Table 34) in the on-chip memory.

The programmable gain amplifier (PGA) consists of two stages with programmable gain values. The ZSSC3240 employs a programmable analog-to-digital converter (ADC) optimized for conversion speed and noise suppression. The programmable resolution from 12 to 24 bits provides flexibility for adapting the conversion characteristics. To improve power supply noise suppression, the ADC uses the external sensor supply voltage, e.g., VDDB for the ratiometric supply of a connected full-bridge sensor element, as its reference voltage leading to a ratiometric measurement topology. The remaining IC-internal offset and the sensor element offset, i.e., the overall system offset for the amplifier and ADC, can be canceled via an offset and auto-zero measurement, respectively.

The math core accomplishes the auto-zero, span, and 1<sup>st</sup> and 2<sup>nd</sup> order temperature compensation of the measured external sensor signal. The correction coefficients are stored in the non-volatile memory.

The ZSSC3240 supports SPI, OWI, and I2C interface communication for controlling the ZSSC3240, configuration, and measurement result output. Analog output signals can be provided, which are proportional to the sensor signal that has been compensated for nonlinearity and temperature. The ZSSC3240 can also check and signalize numerous sensor and self-check diagnostic values.

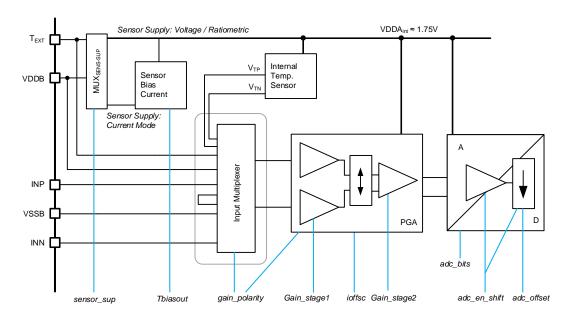

# 6.2 Analog (Sensor) Front-End

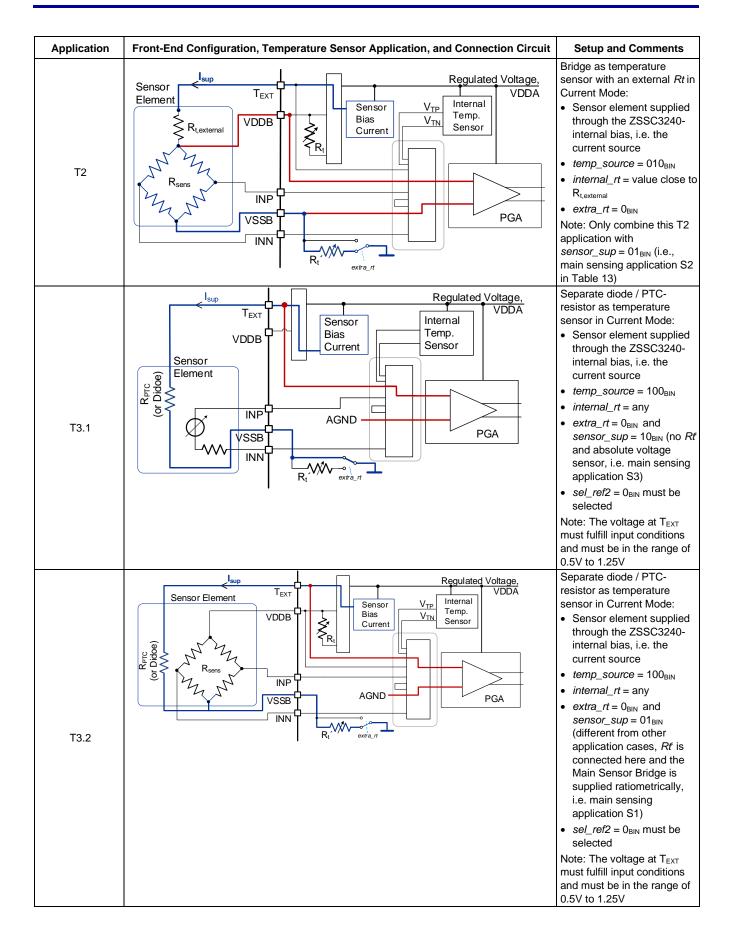

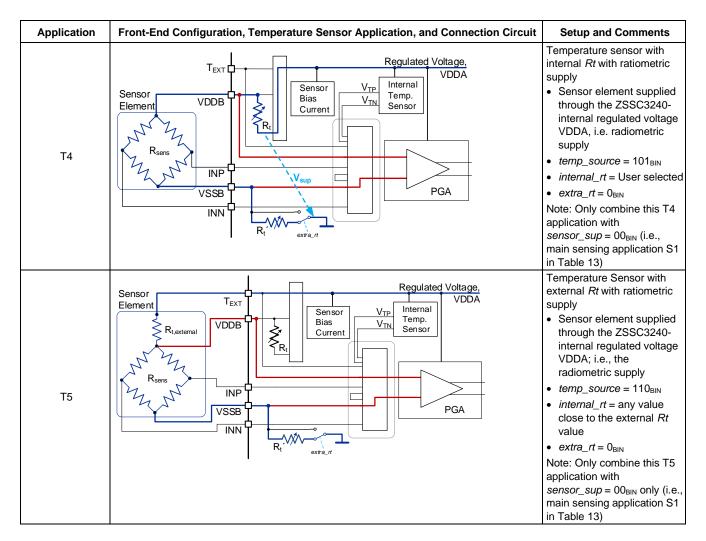

The main blocks and functions of the analog sensor front-end of the ZSSC3240 are illustrated in Figure 4. As a typical first setup, the type and supply of the connected (external) sensor element should be determined and configured. The *sensor\_sup* and *temp\_source* bits in the *SSF1* register (03<sub>HEX</sub>; see Table 34) of the NVM must be set up according to the connected sensor configuration.

Important: If using the current mode sensor biasing via the "Sensor Bias Current" block, which is configured with the *Tbiasout* bit field (see section 6.2.4), ensure that the selection for bias current combined with the dimensioning for the connected external sensor is within the input common mode constraints, V<sub>CMin</sub> (typical 0.85V) as defined in Table 4.

Figure 4. Analog Sensor Front-End Topology

#### 6.2.1. Programmable-Gain Amplifier (PGA)

The amplifier has a fully differential architecture and consists of two stages. The amplification of each stage and the external sensor gain polarity are programmable via settings in the measurement configuration register:

- For the main sensor element: SM\_config1 and SM\_config2 (NVM addresses 14HEX and 15HEX; see Table 34)

- For an optional external temperature sensor: extTemp\_config1 and extTemp\_config2 (NVM addresses 16HEX and 17HEX; see Table 34).

The first 7 bits of the \*\_config1 registers are the programmable gain settings Gain\_stage1 and Gain\_stage2. The options for the programmable gain settings are listed in Table 5 and Table 6. The resulting analog gain is the linear product of the stage 1 and stage 2 selection: Gain<sub>PGA</sub> = Gain<sub>1</sub> · Gain<sub>2</sub>. With the programmable Gain\_polarity bit in the \*\_config1 registers, the sign of the effective PGA gain can be swapped; e.g., to invert the sensor characteristic's slope and invert signal processing of the differential signal between INP and INN.

| Table 5. | PGA | Gain: | Stage ' | 1 |

|----------|-----|-------|---------|---|

|          |     |       |         |   |

|        | Gain_stage1[3:0] |        |        |              |  |

|--------|------------------|--------|--------|--------------|--|

| bit[3] | bit[2]           | bit[1] | bit[0] | Gain₁ [V/V]  |  |

| 0      | 0                | 0      | 0      | 1.2          |  |

| 0      | 0                | 0      | 1      | 2            |  |

| 0      | 0                | 1      | 0      | 4            |  |

| 0      | 0                | 1      | 1      | 6            |  |

| 0      | 1                | 0      | 0      | 12           |  |

| 0      | 1                | 0      | 1      | 20           |  |

| 0      | 1                | 1      | 0      | 30           |  |

| 0      | 1                | 1      | 1      | 40           |  |

| 1      | 0                | 0      | 0      | 60           |  |

| 1      | 0                | 0      | 1      | 80           |  |

| 1      | 0                | 1      | 0      | 120          |  |

| 1      | 0                | 1      | 1      | 150          |  |

| 1      | 1                | 0      | 0      | 200          |  |

| 1      | 1                | 0      | 1      | 240          |  |

| 1      | 1                | 1      | 0      | 300          |  |

| 1      | 1                | 1      | 1      | Not assigned |  |

Table 6. PGA Gain: Stage 2

|        | Gain_stage2[2:0]           bit[2]         bit[1]         bit[0] |   |     |  |  |

|--------|-----------------------------------------------------------------|---|-----|--|--|

| bit[2] |                                                                 |   |     |  |  |

| 0      | 0                                                               | 0 | 1.1 |  |  |

| 0      | 0                                                               | 1 | 1.2 |  |  |

| 0      | 1                                                               | 0 | 1.3 |  |  |

| 0      | 1                                                               | 1 | 1.4 |  |  |

| 1      | 0                                                               | 0 | 1.5 |  |  |

| 1      | 0                                                               | 1 | 1.6 |  |  |

| 1      | 1                                                               | 0 | 1.7 |  |  |

| 1      | 1                                                               | 1 | 1.8 |  |  |

In addition to the amplification of the sensor input signals, the PGA's first stage can perform an absolute offset shifting of the differential sensor signal. This shift operation can be programmed in 1mV steps with the configuration setup *ioffsc* bit field in the S*M\_config2* and *extTemp\_config2* registers. The effective voltage-shift depends on the selected Gain<sub>1</sub>, *Gain\_stage1*. The V<sub>IOFFSC</sub> values (in Table 8) correspond to the higher Gain<sub>1</sub> values, i.e. Gain<sub>1</sub> > 100. The PGA-operation including shift effect for a differential input signal, V<sub>DIFFin</sub> can be described as:

$$V_{ADC,IN} = Gain_2 \cdot Gain_1 \cdot (V_{DIFFin} + V_{IOFFSC}) - Gain_2 \cdot V_{IOFFSC}$$

**Equation 1**

Table 7. Absolute Offset Shift - Properties

| Symbol                | Parameter                                                                                                                                                  | Minimum | Typical | Maximum | Units |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|-------|

| $\Delta_{IOFFSC}$     | Relative accuracy of the effectively applied Offset Shift referenced to the selected setup per <code>ioffsc[4:0]</code> , IC-to-IC variation               | 0.89    | 0.98    | 1.07    | -     |

| $TC_{neg,IOFFSC}$     | 1st order temperature coefficient for the change of the effective Offset Shift voltage for negative-voltage shift effects, i.e.<br>ioffsc[4]=0             | -0.25   | -0.21   | 0       | PPT/K |

| $TC_{pos,IOFFSC}$     | 1 <sup>st</sup> order temperature coefficient for the change of the effective Offset Shift voltage for positive-voltage shift effects, i.e.<br>ioffsc[4]=1 | 0       | 0.21    | 0.25    | PPT/K |

| SNR <sub>IOFFSC</sub> | Fluctuation of output offset signal (V <sub>IOFFSC</sub> ) versus nominal value at 25°C; 20-log10(V <sub>IOFFSC</sub> /ΔV <sub>IOFFSC</sub> )              | -       | 74      | _       | dB    |

The shifting can be configured independently for the main sensor and the optional, external temperature sensor. If the absolute offset shifting is enabled, then the ZSSC3240 current consumption increases by 100µA. The advantage of absolute offset shifting is an increase of analog dynamic range in the ZSSC3240's sensor frontend, which results in higher measurement result quality (less noise/fluctuations).

Table 8. Absolute Offset Shift – Differential Sensor Signal's Offset Compensation

|        |        | ioffsc[4:0] |        |        | Olive Ewart M                     |

|--------|--------|-------------|--------|--------|-----------------------------------|

| bit[4] | bit[3] | bit[2]      | bit[1] | bit[0] | Shift Effect, V <sub>IOFFSC</sub> |

| 0      | 0      | 0           | 0      | 0      | 0mV, no shift                     |

| 0      | 0      | 0           | 0      | 1      | -1mV                              |

| 0      | 0      | 0           | 1      | 0      | -2mV                              |

| 0      | 0      | 0           | 1      | 1      | -3mV                              |

| 0      | 0      | 1           | 0      | 0      | -4mV                              |

| 0      | 0      | 1           | 0      | 1      | -5mV                              |

| 0      | 0      | 1           | 1      | 0      | -6mV                              |

| 0      | 0      | 1           | 1      | 1      | -7mV                              |

| 0      | 1      | 0           | 0      | 0      | -8mV                              |

| 0      | 1      | 0           | 0      | 1      | -9mV                              |

| 0      | 1      | 0           | 1      | 0      | -10mV                             |

| 0      | 1      | 0           | 1      | 1      | -11mV                             |

| 0      | 1      | 1           | 0      | 0      | -12mV                             |

| 0      | 1      | 1           | 0      | 1      | -13mV                             |

| 0      | 1      | 1           | 1      | 0      | -14mV                             |

| 0      | 1      | 1           | 1      | 1      | -15mV                             |

|        |        | ioffsc[4:0] |        |        | Chitt Etta et V                   |

|--------|--------|-------------|--------|--------|-----------------------------------|

| bit[4] | bit[3] | bit[2]      | bit[1] | bit[0] | Shift Effect, V <sub>IOFFSC</sub> |

| 1      | 0      | 0           | 0      | 0      | 0mV, no shift                     |

| 1      | 0      | 0           | 0      | 1      | 1mV                               |

| 1      | 0      | 0           | 1      | 0      | 2mV                               |

| 1      | 0      | 0           | 1      | 1      | 3mV                               |

| 1      | 0      | 1           | 0      | 0      | 4mV                               |

| 1      | 0      | 1           | 0 1    |        | 5mV                               |

| 1      | 0      | 1           | 1      | 0      | 6mV                               |

| 1      | 0      | 1           | 1      | 1      | 7mV                               |

| 1      | 1      | 0           | 0      | 0      | 8mV                               |

| 1      | 1      | 0           | 0      | 1      | 9mV                               |

| 1      | 1      | 0           | 1      | 0      | 10mV                              |

| 1      | 1      | 0           | 1      | 1      | 11mV                              |

| 1      | 1      | 1           | 0      | 0      | 12mV                              |

| 1      | 1      | 1           | 0      | 1      | 13mV                              |

| 1      | 1      | 1           | 1      | 0      | 14mV                              |

| 1      | 1      | 1           | 1      | 1      | 15mV                              |

The PGA can perform an automatic adjustment for the PGA input to ADC input common mode. This can be enabled via the *pga\_en\_shift* bit in the \*\_config2 registers. The supportable input common mode range at the PGA, i.e. at the sensor front-end input, is constant per IC because it is derived from the internally regulated voltage VDDA<sub>int</sub>.

Table 9. PGA Input Span Ranges

| Total Gain, G <sub>AMP</sub> Examples | Gain₁ | Gain <sub>2</sub> | Max. Input Span, Differential Signal Range [mV] |

|---------------------------------------|-------|-------------------|-------------------------------------------------|

| 540                                   | 300   | 1.8               | 5.0                                             |

| 420                                   | 300   | 1.4               | 6.4                                             |

| 330                                   | 300   | 1.1               | 8.1                                             |

| 280                                   | 200   | 1.4               | 9.6                                             |

| 220                                   | 200   | 1.1               | 12.2                                            |

| 144                                   | 120   | 1.2               | 18.5                                            |

| 103                                   | 80    | 1.3               | 25.9                                            |

| 88                                    | 80    | 1.1               | 30.5                                            |

| 72                                    | 60    | 1.2               | 37.5                                            |

| 60                                    | 40    | 1.5               | 45                                              |

| 48                                    | 40    | 1.2               | 56                                              |

| 39                                    | 30    | 1.3               | 69                                              |

| 30                                    | 20    | 1.5               | 90                                              |

| 19.2                                  | 12    | 1.6               | 140                                             |

| 13.2                                  | 12    | 1.1               | 204                                             |

| 10.2                                  | 6     | 1.7               | 264                                             |

| 5.2                                   | 4     | 1.3               | 519                                             |

| 3.0                                   | 2     | 1.5               | 900                                             |

| 1.32 <sup>[a]</sup>                   | 1.2   | 1.1               | 1400                                            |

<sup>[</sup>a] There is a general PGA-input range constraint to support  $V_{\text{INdiff}}$  of  $\pm 700 \text{mV}$  at maximum, which is especially dominating for  $G_{\text{AMP}} < 2$ .

### 6.2.2. Analog-to-Digital Converter (ADC)

An analog-to-digital converter (ADC) is used to digitize the amplifier signal. To allow optimizing the trade-off between conversion time and resolution, the resolution can be programmed from 12-bit to 24-bit (adc\_bits bit fields in the SM\_config1, and extTemp\_config1 registers; see section 6.6.2.1). The ADC processes differential input signals around its input common mode level: VADCmid. Table 10 lists the ADC resolution, signal ranges, conversion times for a single Analog-to-Digital conversion.

| Table 10. | Single  | Analog-to  | -Digital         | Conversion  |

|-----------|---------|------------|------------------|-------------|

| Table IV. | Siliule | Alialog-it | <i>-</i> Digital | COLIVERSION |

|        | adc_b  | its[3:0] |        | ADC                  | Ratiometric ADC                                         | Absolute ADC                                            | Conversion            | Conversion             |

|--------|--------|----------|--------|----------------------|---------------------------------------------------------|---------------------------------------------------------|-----------------------|------------------------|

| Bit[3] | Bit[2] | Bit[1]   | Bit[0] | Resolution<br>[Bits] | Input Range <sup>[a]</sup> ,<br>V <sub>ADC,IN</sub> [V] | Input Range <sup>[b]</sup> ,<br>V <sub>ADC,IN</sub> [V] | Time, Typical<br>[µs] | Rate, Typical<br>[kHz] |

| 0      | 0      | 0        | 0      | 12                   | ±1.42                                                   | ±1.07                                                   | 162                   | 6.1                    |

| 0      | 0      | 0        | 1      | 13                   | ±1.43                                                   | ±1.08                                                   | 192                   | 5.2                    |

| 0      | 0      | 1        | 0      | 14                   | ±1.41                                                   | ±1.06                                                   | 235                   | 4.2                    |

| 0      | 0      | 1        | 1      | 15                   | ±1.42                                                   | ±1.07                                                   | 294                   | 3.4                    |

| 0      | 1      | 0        | 0      | 16                   | ±1.41                                                   | ±1.06                                                   | 380                   | 2.6                    |

| 0      | 1      | 0        | 1      | 17                   | ±1.42                                                   | ±1.07                                                   | 497                   | 2.0                    |

| 0      | 1      | 1        | 0      | 18                   | ±1.41                                                   | ±1.06                                                   | 670                   | 1.4                    |

| 0      | 1      | 1        | 1      | 19                   | ±1.42                                                   | ±1.07                                                   | 903                   | 1.1                    |

| 1      | 0      | 0        | 0      | 20                   | ±1.41                                                   | ±1.06                                                   | 1245                  | 0.8                    |

| 1      | 0      | 0        | 1      | 21                   | ±1.42                                                   | ±1.07                                                   | 1715                  | 0.5                    |

| 1      | 0      | 1        | 0      | 22                   | ±1.41                                                   | ±1.06                                                   | 2400                  | 0.4                    |

| 1      | 0      | 1        | 1      | 23                   | ±1.42                                                   | ±1.07                                                   | 3335                  | 0.3                    |

| 1      | 1      | 0        | 0      | 24                   | ±1.40                                                   | ±1.06                                                   | 4705                  | 0.2                    |

| 1      | 1      | 0        | 1      | Not assigned         | _                                                       | _                                                       | _                     | _                      |

| 1      | 1      | 1        | 0      | Not assigned         | _                                                       | -                                                       | _                     | _                      |

| 1      | 1      | 1        | 1      | Not assigned         | _                                                       | -                                                       | _                     | _                      |

<sup>[</sup>a] With the following settings: ratiometric reference, sel\_ref\* = 1, and no ADC-shift (adc\_en\_shift = 0) nor extra ADC-gain, i.e. Gain\_ADC=1

The ADC can perform an additional offset shift (independent of the PGA shifting with *ioffsc*) in order to adapt input signals with offsets to the ADC input range. The shift feature is enabled by setting  $adc\_en\_shift = 1$  (bit[8] in the  $SM\_config2$  or  $extTemp\_config2$  registers). As defined in Table 11, the respective analog offset shift can be selected with bits [14:12],  $adc\_offset$  in  $SM\_config1$  or  $extTemp\_config1$ .

Note: Enabling the offset shift causes the ADC to perform an additional amplification of the ADC's input signal by factor 2. This must be considered for a correct analog sensor setup by means of the PGA's gain, the absolute offset shift in the PGA, the ADC offset shift, and the potential ADC gain.