## **Brief Description**

The ZLED7001, one of our ZLED family of LED control ICs, is a peak current-mode control LED driver IC that is optimal for buck LED driver applications. The ZLED7001 operates in constant off-time mode. Capable of operating efficiently with voltage sources ranging from 8 VDC to 450 VDC or rectified 110 VAC/ 220 VAC, it is ideal for High Brightness (HB) LED applications. The ZLED7001 provides a PWM input for an external dimming control signal. The ZLED7001's linear dimming input can be used both for linear dimming (0 to 240 mV) and temperature compensation of the LED current.

Because the ZLED7001's response time is limited only by the rate of change in the inductor current, it attains a high performance pulse-width modulation (PWM) dimming response. The ZLED7001 ensures proper output current regulation, without loop compensation, via peak current-mode operation.

#### **ZLED7001** Features

- Wide input range from 8 VDC to 450 VDC or 110 VAC/220 VAC

- Temperature compensation to protect the LEDs and extend LED lifetime

- · Operates in constant off-time mode

- Both PWM and linear dimming control signal inputs available

- Very few external components needed for operation

- Broad range of applications: outputs greater than 1A

## **Application Examples**

- Line-powered replacement LED lighting

- Illuminated LED signs and other displays

- LED street and traffic lighting

- Constant-current source for general purposes

- Architecture / building LED lighting

- LED backlighting

- Line powered LED flood lighting

- Interior / exterior LED lighting

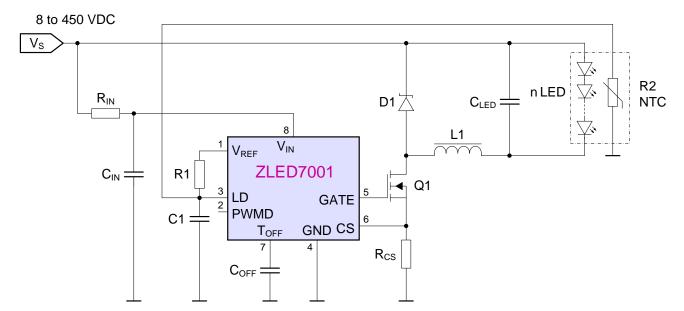

## ZLED7001 Application Circuit

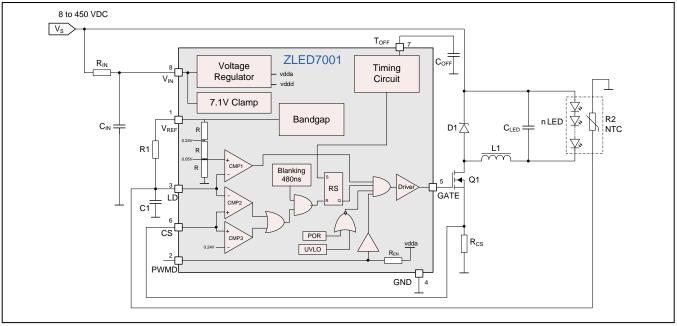

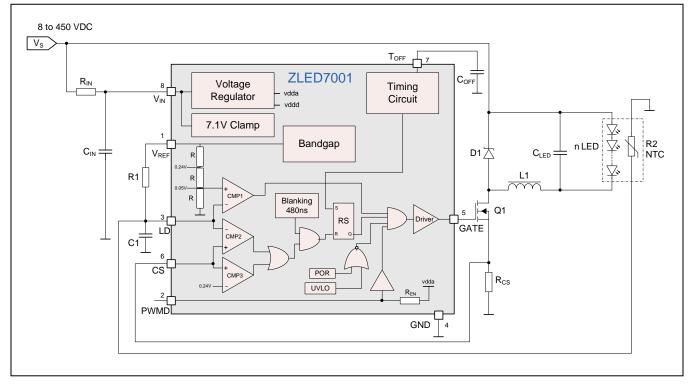

## ZLED7001 Block Diagram

| SOP-8 Package Dimensions (mm, except θ) |               |    |                           |  |

|-----------------------------------------|---------------|----|---------------------------|--|

| Α                                       | 1.550 ± 0.200 | Е  | 3.900 ± 0.100             |  |

| A1                                      | 0.175 ± 0.075 | E1 | 6.020 ± 0.220             |  |

| A2                                      | 1.450 Typical | е  | 1.270 Typical             |  |

| b                                       | 0.420 ± 0.070 | L  | 0.835 ± 0.435             |  |

| С                                       | 0.214 ± 0.036 | θ  | $4^{\circ} \pm 4^{\circ}$ |  |

| D                                       | 4.900 ± 0.100 |    |                           |  |

# **Ordering Information**

| Sales Code     | Description                                                                           | Package               |

|----------------|---------------------------------------------------------------------------------------|-----------------------|

| ZLED7001ZI1R   | ZLED7001 – Universal LED Driver with Temperature Compensation                         | SOP8 (Tape & Reel)    |

| ZLED7001Kit-E1 | ZLED7001 Evaluation Board up to 24VAC / 40VDC, including 1 ZLED-PCB1                  | Kit                   |

| ZLED-PCB1      | Test PCB with one 3W white HB-LED, cascadable to one multiple LED string              | Printed Circuit Board |

| ZLED-PCB2      | 10 unpopulated test _ for modular LED string with footprints of 9 common HB-LED types | Printed Circuit Board |

# Contents

| 1 | IC C | Characteristics                    | 4 |

|---|------|------------------------------------|---|

| 1 | .1.  | Absolute Maximum Ratings           | 4 |

| 1 | .2.  | Operating Conditions               | 4 |

| 1 | .3.  | Electrical Parameters              | 4 |

| 2 | Circ | cuit Description                   | 6 |

| 2 | 2.1. | ZLED7001 Block Diagram             | 6 |

| 2 | 2.2. | Application Signal Flow            | 6 |

| 2 | 2.3. | Input Voltage Regulator            | 7 |

| 2 | 2.4. | Current Sensing                    | 8 |

| 2 | 2.5. | Timing Circuit                     | 8 |

| 2 | 2.6. | PWM Dimming Application Circuit    | 8 |

| 2 | 2.7. | Linear Dimming Application Circuit | 8 |

| 2 | 2.8. | Temperature Compensation           |   |

| 2 | 2.9. | Design Example                     | 9 |

| 3 | ESE  | D/Latch-Up-Protection 1            | 1 |

| 4 |      | Configuration and Package 1        |   |

| 5 | Ord  | ering Information 1                | 3 |

| 6 | Doc  | ument Revision History 1           | 4 |

# List of Figures

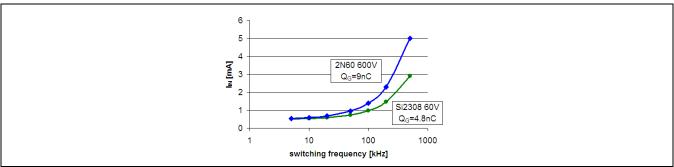

| Figure 2.1 | Input Current               | 7 |

|------------|-----------------------------|---|

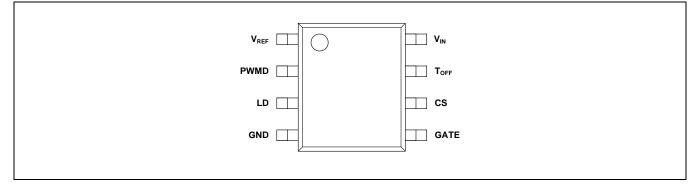

|            | Pin Configuration ZLED70011 |   |

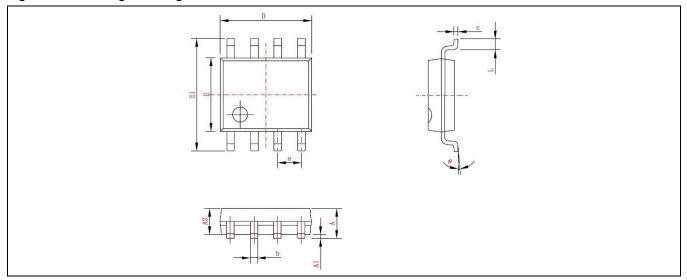

| Figure 4.2 | Package Drawing SOP-8 1     | 3 |

# List of Tables

| Table 1.1 | Absolute Maximum Ratings   | 4 |

|-----------|----------------------------|---|

| Table 1.2 | Operating Conditions       | 4 |

| Table 1.3 | Electrical Conditions      | 4 |

| Table 4.1 | Pin Description SOP-81     | 2 |

| Table 4.2 | Package Dimensions SOP-8 1 | 3 |

# **1** IC Characteristics

#### 1.1. Absolute Maximum Ratings

#### Table 1.1Absolute Maximum Ratings

| No.   | PARAMETER                                                       | SYMBOL                                                                                         | CONDITIONS | MIN  | ТҮР | MAX | UNIT |

|-------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------|------|-----|-----|------|

| 1.1.1 | Input voltage                                                   | V <sub>IN</sub>                                                                                |            | -0.3 |     | 8   | V    |

| 1.1.2 | Voltage to GND at pin CS, LD, PWMD, GATE, $T_{OFF}$ , $V_{REF}$ | $\begin{array}{c} V_{CS}, V_{LD}, \\ V_{PWMD}, \\ V_{GATE}, V_{TOFF}, \\ V_{VREF} \end{array}$ |            | -0.3 |     | 6   | V    |

| 1.1.3 | Input current V <sub>IN</sub> pin <sup>1</sup>                  | I <sub>VIN</sub>                                                                               |            | 1    |     | 10  | mA   |

| 1.1.4 | Junction temperature                                            | T <sub>j MAX</sub>                                                                             |            |      |     | 150 | °C   |

| 1.1.5 | Storage temperature                                             | T <sub>ST</sub>                                                                                |            | -55  |     | 150 | °C   |

#### **1.2.** Operating Conditions

#### Table 1.2Operating Conditions

| No.   | PARAMETER               | SYMBOL          | CONDITIONS                                                                                                                                                                   | MIN | ТҮР | MAX | UNIT |

|-------|-------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| 1.2.1 | Operating temperature   | T <sub>OP</sub> |                                                                                                                                                                              | -40 |     | +85 | °C   |

| 1.2.2 | Input DC supply voltage | VINDC           | Resistor $R_{IN}$ required<br>between DC supply<br>voltage and $V_{IN}$ pin with<br>resistance determined by<br>equation (2) and with<br>proper voltage rating. <sup>2</sup> | 8   |     | 450 | V    |

#### **1.3. Electrical Parameters**

Production testing of the chip is performed at 25°C. Functional operation of the chip and specified parameters at other temperatures are guaranteed by design, characterization, and process control.

Test conditions:  $V_{IN} = 12V$ ;  $T_{amb} = 25^{\circ}C$ ;  $R_{IN}=2k\Omega$ ; unless otherwise noted.

#### Table 1.3Electrical Conditions

| No.   | PARAMETER                           | SYMBOL            | CONDITIONS                                         | MIN  | ТҮР | MAX      | UNIT |

|-------|-------------------------------------|-------------------|----------------------------------------------------|------|-----|----------|------|

| 1.3.1 | V <sub>IN</sub> clamp voltage       | V <sub>INCL</sub> | Always higher than under voltage lockout threshold | 6.6  | 7.1 | .1 7.6 V |      |

| 1.3.2 | Operation current                   | I <sub>IN</sub>   | V <sub>IN</sub> = 6V, GATE floating                | 0.33 | 0.5 | 0.64     | mA   |

| 1.3.3 | Under voltage lockout<br>threshold  | V <sub>ULO</sub>  | V <sub>IN</sub> rising                             | 6.1  | 6.5 | 6.8      | V    |

| 1.3.4 | Under voltage lockout<br>hysteresis | $\Delta V_{ULO}$  | V <sub>IN</sub> falling                            |      | 500 |          | mV   |

| 1.3.5 | PWMD pin input low voltage          | $V_{\text{ENL}}$  |                                                    |      |     | 1.2      | V    |

<sup>&</sup>lt;sup>1</sup> Beyond the input current range,  $V_{IN}$  might not clamp at 7.1V

<sup>2</sup> This parameter limit is guaranteed by design, characterization, and application check. See equation (2) on page 8

| No.    | PARAMETER                               | SYMBOL               | CONDITIONS                                     | MIN  | ТҮР  | MAX  | UNIT |

|--------|-----------------------------------------|----------------------|------------------------------------------------|------|------|------|------|

| 1.3.6  | PWMD pin input high voltage             | V <sub>ENH</sub>     |                                                | 2    |      |      | V    |

| 1.3.7  | PWMD pin pull-up resistance             | R <sub>EN</sub>      |                                                |      | 100  |      | kΩ   |

| 1.3.8  | Current sense threshold voltage         | V <sub>CSTH</sub>    |                                                | 215  | 240  | 265  | mV   |

| 1.3.9  | LD pin voltage low<br>threshold         | V <sub>LDL</sub>     |                                                |      | 50   |      | mV   |

| 1.3.10 | LD pin voltage high threshold           | V <sub>LDH</sub>     |                                                |      | 240  |      | mV   |

| 1.3.11 | Current sense blanking interval         | T <sub>BLANK</sub>   |                                                | 400  | 480  | 550  | ns   |

| 1.3.12 | Output delay                            | t <sub>DELAY</sub>   | $V_{CS} = V_{CSTH} + 50mV$ , after $T_{BLANK}$ |      | 30   |      | ns   |

| 1.3.13 | OFF time                                | T <sub>OFF</sub>     | T <sub>OFF</sub> pin floating                  | 480  | 510  | 550  | ns   |

| 1.3.14 | GATE output rise time                   | t <sub>RISE</sub>    | $C_{GATE} = 500 pF$                            |      | 19   |      | ns   |

| 1.3.15 | GATE output fall time                   | t <sub>FALL</sub>    | C <sub>GATE</sub> = 500pF                      |      | 29   |      | ns   |

| 1.3.16 | REF pin voltage                         | V <sub>REF</sub>     |                                                | 1.12 | 1.20 | 1.30 | V    |

| 1.3.17 | REF pin load current                    | I <sub>REF</sub>     |                                                |      |      | 0.5  | mA   |

| 1.3.18 | Load regulation of<br>reference voltage | V <sub>REFLOAD</sub> | $I_{REF} = 0$ to 500µA, PWMD<br>= 5.0V         |      | 0.5  | 5    | mV   |

# 2 Circuit Description

The ZLED7001 is a peak current-mode-control LED driver IC that operates in constant off-time mode, enabling proper LED current control without additional loop compensation or high-side current sensing. The ZLED7001 supports both linear and PWM control of the LED current. Only a few external components are needed for typical applications. It is well-suited for buck LED driver applications.

## 2.1. ZLED7001 Block Diagram

## 2.2. Application Signal Flow

A capacitor between the  $T_{OFF}$  pin and ground determines the internal timer's off-time. The timer pulses set flip-flop in the ZLED7001, turning on the GATE pin driver, which is connected to the Q1 external MOSFET. When Q1 turns on, a ramp current flows through the LED(s), the L1 external inductor, and the external sense resistor R<sub>CS</sub>. This results in a ramp voltage applied at the CS pin, which the ZLED7001's two internal comparators continually compare to the voltage at its LD pin and its internal 240mV reference. If either comparator goes high and the blanking time is expired (see Table 1.3), the flip-flop is reset, causing the GATE pin output to go low, shutting off the current through the LED(s).

The peak current control scheme with constant off-time can easily operate at duty cycles higher than 0.5 and also gives inherent input voltage rejection, making the LED current almost insensitive to input voltage variations.

## 2.3. Input Voltage Regulator

The value and rating of the  $R_{IN}$  input resistor must be selected as needed to drop the application supply voltage  $(V_s)$  to the proper operating voltage for the ZLED7001 specified in section 0 (see equation (2) below). When these conditions are met, the ZLED7001's internal input voltage regulator maintains a stable 7.1V (typical) at the  $V_{IN}$  pin to power the ZLED7001. A low-equivalent-series-resistance (ESR) bypass capacitor is required on the  $V_{IN}$  pin to provide a low-impedance path for the GATE pin output driver's high frequency current.

The V<sub>IN</sub> pin draws an input current that is the sum of the 0.5mA (typical) required by the internal circuit and the average current drawn by the GATE driver. The GATE driver current is primarily determined by the GATE charge ( $Q_G$ ) and switching frequency ( $f_s$ ) of the external MOSFET as shown in equation (1).

$$I_{IN} \approx 0.5mA + (Q_G * f_S) \tag{1}$$

Where

f<sub>S</sub> = Switching frequency

Q<sub>G</sub> = External MOSFET gate charge (refer to the MOSFET data sheet)

The input resistor  $R_{IN}$  value is given by equation (2).

$$R_{IN} = \frac{V_{INDC} - V_{IN}}{I_{IN}}$$

(2)

For two typical MOSFET types, the following I<sub>IN</sub> diagram will result:

#### Figure 2.1 Input Current

## 2.4. Current Sensing

Assuming a 30% current ripple in the inductor, the sense resistor R<sub>CS</sub> can be calculated as shown in equation (3):

$$R_{CS} = \frac{V_{CSTH}}{1.15 * I_{LED}}$$

(3)

Where

$V_{CSTH} = 240 mV$  (typical)

The current sense input of the ZLED7001 is connected to the non-inverting inputs of two comparators. The inverting terminal of one comparator is tied to an internal 240mV reference and the inverting terminal of the other comparator is connected to the LD pin. The outputs of both comparators are fed into an OR gate, and the output of the OR gate is connected to the reset pin of the flip-flop. Thus, the comparator that has the lower voltage at the inverting input determines when the GATE output is turned off.

The comparator outputs also include a typical 480ns blanking time that prevents spurious turn-offs of the external MOSFET due to the turn-on spike normally present as a result of transistor gate-source capacitance. In rare cases, this internal blanking time might not be enough to filter out the turn-on spike. If so, an external RC filter must be added between the external sense resistor ( $R_{CS}$ ) and the CS pin.

Note that the comparators are relatively fast: 80ns typical response time. Invalid triggering by these comparators could result if the layout fails to minimize external inductances.

#### 2.5. Timing Circuit

The timing circuit in the ZLED7001 is controlled by a single capacitor connected from  $T_{OFF}$  to ground.  $T_{OFF}$ , the time of the cycle period, is given by equation (4):

$$T_{OFF\_TIME} = 510ns * \left(1 + \frac{C_{OFF}}{10\,pF}\right) \tag{4}$$

#### 2.6. PWM Dimming Application Circuit

For PWM dimming applications, the ZLED7001's PWMD pin is driven with a low-frequency square-wave control signal. The GATE pin's driver is enabled when the control signal is high and disabled when the control signal is low. The LED current's rise and fall rate is controlled only by the inductance value, the supply voltage, and LED forward voltage.

If the PWMD pin is allowed to float, the PWM dimming function is disabled.

#### 2.7. Linear Dimming Application Circuit

For linear dimming applications, an external voltage ranging from 50mV (typical) to 240mV (typical) is applied to the LD (linear dimming) pin to control the LED current during operation. Linear dimming can be used to adjust the LED current level to reduce the LED's brightness. In this case, connect a resistor between the VREF pin and the LD pin and connect a negative-temperature-coefficient (NTC) thermistor between the LD pin and ground. The ZLED7001 can also provide temperature compensation, (see the application circuit on page 1 and section 2.8).

A group of modules based on the ZLED7001 can be matched in LED brightness using the linear dimming input with the PWM dimming feature still available for overall brightness control.

If the LD pin is not used, it must be connected to the PWMD pin, which is internally pulled-up. When the LD pin voltage drops below 50mV, the GATE output is switched off.

## 2.8. Temperature Compensation

ZLED7001 provides thermal protection for the connected LEDs. Applying an NTC thermistor close to the LED string will enable the temperature compensation of the LED current. Refer to the application circuit on page 1. If the temperature of the LEDs rises, the resistance of the NTC thermistor decreases until the voltage of the LD pin falls below 240mV. Then the average current is controlled by the LD pin and the temperature compensation function starts. The upper threshold to start compensation is given by equation (5):

$$V_{LDH} = \sim 240 mV = V_{REF} * \left(\frac{R_{NTC}}{R_{NTC} + RI}\right)$$

(5)

Considering the limit for  $I_{REF}$ , under all conditions R1 must be selected larger than 2.2k $\Omega$ . Assuming a 30% inductor current ripple, the temperature compensated continuous current can be computed as shown in equation (6):

$$I_{OUT} = \left(\frac{V_{REF}}{1.15 * R_S}\right) * \left(\frac{R_{NTC}}{R_{NTC} + RI}\right)$$

(6)

When the LD pin voltage drops below 50mV (typical), the GATE output is switched off. The transition to dimming as well as the switch-off is reversible as soon as the respective thresholds are exceeded after the LED assembly cools. Adding a capacitor C1 from the LD pin to ground will reduce noise on the LD input.

## 2.9. Design Example

A common application for an AC-line-powered ZLED7001 is luminants with a string of several LEDs operated by one driver. For the example, the following constraints are assumed:

| Application:                | 15W LED luminant with 13 HB LEDs in 1 string                                                                                                    |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| AC supply voltage:          | $V_{INAC} = 230 \text{ VAC}$                                                                                                                    |

| Average DC supply voltage:  | $V_{INDC} \approx 280$ VDC resulting after bridge rectification and filtering with a 10µF capacitor; power factor correction is not considered. |

| LED string forward voltage: | $\Sigma V_{F} = 13^{*}3.3 V \approx 43 V$                                                                                                       |

| LED string average current: | $I_{LED} = 350 \text{mA}$                                                                                                                       |

## IC Input Resistor ( $R_{IN}$ ) and Hold Capacitor ( $C_{IN}$ ):

For a given 2N60 MOSFET and a maximum expected switching frequency of 100kHz, the IC input current will be  $I_{IN} \approx 0.5 mA + (Q_G \cdot f_S) = 0.5 mA + (9nC \cdot 100 kHz) = 1.4 mA$

Resulting in a supply resistor of

$$R_{IN} = \frac{V_{INDC} - V_{IN}}{I_{IN}} = \frac{280V - 7V}{1.4mA} \approx 195 k\Omega$$

An 180k $\Omega$  type can be chosen with a power rating of  $\geq 0.5$ W. C<sub>IN</sub> is chosen to be a 10 $\mu$ F/ $\geq$ 10V capacitor.

#### T<sub>OFF</sub> Time Capacitor (C<sub>OFF</sub>)

The selection of the operation frequency is based on a tradeoff between higher frequencies allowing for smaller and less expensive inductors and lower frequencies incurring lower losses in the power switch.

An estimation of the duty cycle D is based on the ratio of output voltage over input voltage:

$$D = \frac{T_{ON\_TIME}}{T_{ON\_TIME} + T_{OFF\_TIME}} \approx \frac{\Sigma V_F}{V_{INDC}} = \frac{43V}{280V} \approx 0.15$$

A timing capacitor of 220pF yields

$$T_{OFF\_TIME} = 0.51 \mu s \cdot \left(1 + \frac{C_{OFF}}{10 pF}\right) = 0.51 \mu s \cdot \left(1 + \frac{220 pF}{10 pF}\right) = 11.7 \mu s$$

Resulting in an operation frequency of

$$f_{\rm O} = \frac{1 - D}{T_{OFF\_TIME}} = \frac{1 - 0.15}{11.7\,\mu s} \approx 72\,kHz$$

#### Inductor (L1)

The inductance L1 is determined by the LED string's forward voltage, the off-time, and the acceptable current ripple. Assuming a ripple of 30% of the average current yields

$$L = \frac{\Sigma V_F \cdot T_{OFF\_TIME}}{I_{Ripple}} = \frac{43V \cdot 11.7\,\mu s}{30\% \cdot 350\,mA} \approx 4.8\,mH$$

Lower ripple at the same average current will increase the lifetime of the LEDs but requires a more expensive higher value inductor and increased thermal losses since the inductor's DC resistance will increase as well. The DC resistance of the inductor is an important design parameter, too. A capacitor placed in parallel with the array of LEDs can be used to reduce the LED current ripple while keeping the same average current.

The inductor chosen must have a saturation current higher than the peak output current and a continuous current rating above the required mean output current. The circuit design must also consider the decrease of inductance and saturation current with rising temperature.

#### Current Sense Resistor (R<sub>cs</sub>)

With peak current-mode control, the output is switched off when the LED current reaches its maximum value summing up the average LED current and half of the defined current ripple, yielding for the given example

$$I_{O_{PEAK}} = I_{LED(AVG)} + \frac{I_{Ripple}}{2} = 350 mA + \frac{30\% \cdot 350 mA}{2} = 402.5 mA$$

The current sense resistor can now be calculated from the internal comparator threshold  $V_{\mbox{\scriptsize CSTH}}$  and the peak current as

$$R_{CS} = \frac{V_{CSTH}}{I_{O-PEAK}} = \frac{240 mV}{402.5 mA} = 0.596 \Omega$$

This value can be built by a  $0.68\Omega$  in parallel with a  $4.7\Omega$  type.

#### MOSFET (Q1) and Diode (D1)

The MOSFET and diode must be dimensioned with a minimum 50% safety rating of their relevant voltage and current parameters. Thus a FET with minimum 500V drain-source breakdown voltage and 0.6A drain current as well as a fast recovery diode with at least 500V reverse voltage and a 0.6A forward current may be selected.

# 3 ESD/Latch-Up-Protection

All pins have an ESD protection of >± 2000V according human body model (HBM). The ESD test follows the Human Body Model with 1.5 k $\Omega$ /100 pF based on MIL 883-G, Method 3015.7

Latch-up protection of >± 100mA has been proven based on JEDEC No. 78A Feb. 2006, temperature class 1.

# 4 Pin Configuration and Package

Figure 4.1 Pin Configuration ZLED7001

| Table 4.1 | Pin Description SOP-8 |

|-----------|-----------------------|

|-----------|-----------------------|

| Pin Name         | NO. | Description                                                                                                                                                                                     |

|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>REF</sub> | 1   | 1.2V reference voltage. No bypass capacitor needed.                                                                                                                                             |

| PWMD             | 2   | PWM dimming input. The gate driver operates normally if PWMD is pulled high. The gate driver is turned off if PWMD is pulled to GND or open.                                                    |

| LD               | 3   | Linear dimming input. If the voltage at LD is < 240mV (typical), LD controls the current sense threshold.<br>Can also be used as temperature compensation threshold voltage.                    |

| GND              | 4   | Internal circuit ground reference. Electrical connection to ground is required.                                                                                                                 |

| GATE             | 5   | Output for external N-channel power MOSFET gate driver.                                                                                                                                         |

| CS               | 6   | Current sense pin that senses the Q1 MOSFET drain current through external resistor $R_{CS}$ . The GATE output goes low if the voltage at CS > the voltage at the LD pin or the internal 240mV. |

| T <sub>OFF</sub> | 7   | Sets the off-time of the power MOSFET. If left floating, off-time will be 510ns. For increased off-time, a capacitor must be connected between $T_{OFF}$ and GND.                               |

| V <sub>IN</sub>  | 8   | Supply input of 8V to 450V through a resistor, clamped at 7.1V internally. Low-ESR bypass capacitor to GND is required.                                                                         |

# RENESAS

Figure 4.2 Package Drawing SOP-8

#### Table 4.2 Package Dimensions SOP-8

| Symbol | Dimension (mm) |       | Symbol | <b>Dimension</b> (mm, except θ) |       |

|--------|----------------|-------|--------|---------------------------------|-------|

|        | Min            | Max   | Symbol | Min                             | Max   |

| А      | 1.350          | 1.750 | Е      | 3.800                           | 4.000 |

| A1     | 0.100          | 0.250 | E1     | 5.800                           | 6.240 |

| A2     | 1.450 Typical  |       | е      | 1.270 Typical                   |       |

| b      | 0.350          | 0.490 | L      | 0.400                           | 1.270 |

| с      | 0.178          | 0.250 | θ      | 0°                              | 8°    |

| D      | 4.800          | 5.000 |        |                                 |       |

The SOP-8 package has a thermal resistance (junction to ambient) of  $R_{\theta JA} = 80$  K/W.

# 5 Ordering Information

| Product Sales Code | Description                                                                              | Package               |

|--------------------|------------------------------------------------------------------------------------------|-----------------------|

| ZLED7001ZI1R       | ZLED7001 – Universal LED Driver with Temperature Compensation                            | SOP8 (Tape & Reel)    |

| ZLED7001Kit-E1     | ZLED7001 Evaluation Board up to 24VAC / 40VDC, including 1 ZLED-PCB1                     | Kit                   |

| ZLED-PCB1          | Test PCB with one 3W white HB-LED, cascadable to one multiple LED string                 | Printed Circuit Board |

| ZLED-PCB2          | 10 unpopulated test PCBs for modular LED string with footprints of 9 common HB-LED types | Printed Circuit Board |

# 6 Document Revision History

| Revision | Date            | Description                                                                                                                                                                                    |

|----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | June 2, 2010    | Production release version                                                                                                                                                                     |

| 1.1      | August 12, 2010 | Removed references to thermal shutdown protection in "Features" section and in section 2.9. Updated contact information Updated block diagram connection for correct PWMD internal connection. |

|          | April 20, 2016  | Changed to IDT branding.                                                                                                                                                                       |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.