# μPD48011318 μPD48011336

# 1.1G-BIT Low Latency DRAM-III Common I/O Burst Length of 2

R10DS0012EJ0200 Rev.2.00 Feb 01, 2013

#### **Description**

The  $\mu$ PD48011318 is a 67,108,864-word by 18-bit and the  $\mu$ PD48011336 is a 33,554,432-word by 36-bit synchronous double data rate Low Latency RAM fabricated with advanced CMOS technology using one-transistor eDRAM memory cell.

The Low Latency DRAM-III chip is a 1.1Gbit DRAM capable of a sustained throughput of approximately 43.2 Gbps for burst length of 2 (approximately 51.2 Gbps for applications implementing error correction), excluding refresh overhead and data bus turn-around

With a bus speed of 600 MHz, a burst length of 2, and a tRC of 13.3 ns, the Low Latency DRAM-III chip is capable of achieving this rate when accesses to at least 6 banks of memory are overlapped.

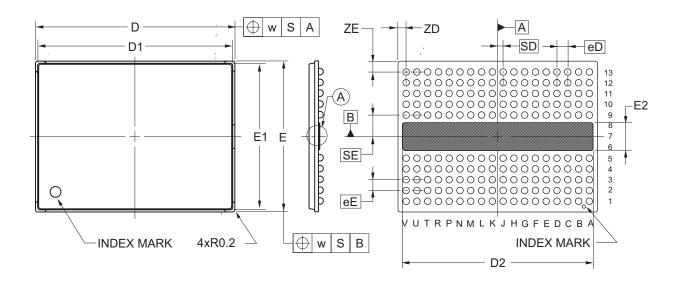

These products are packaged in 180-pin TAPE FBGA.

# **Specification**

- Density: 1,1Gbit

- Organization: 8M words x 18 bits x 8 banks

4M words x 36 bits x 8 banks

- Operating frequency

600MHz (MAX.) @ trc=13.3 ns

- trc

13.3 ns tRC ( and 13.3 ns tRFC )

- Burst length: 2

- Address bus

1 cycle DDR address

Package

180-pin FBGA (Ball Array: 1 mm x 1 mm Pitch)

Package size: 18.5 mm x 14 mm

ROHS 6/6 compliance

- Power supply

- 2.5 V VEXT

- 1.5 V V<sub>DD</sub>

- 1.0 V VDDQ

- Refresh command

- Auto Refresh : 16384 cycles / 2 ms for each bank

- Overlapped Refresh with DPR# pin

- Operating case temperature: 0 to 95 °C

# **Features**

- 1 cycle 600MHz DDR Muxed Address

- Optional data bus inversion to reduce SSO, SSN, maximum I/O current, and average I/O power

- Training sequence for per-bit deskew

- Selectable Refresh Mode: Auto or Overlapped Refresh

- Programmable PVT-compensated output impedance

- Programmable PVT-compensated on-die input termination

- PLL for improved input jitter tolerance and wide output data valid window

# **Ordering Information**

| Part number              | Cycle | Clock     | Random | <b>Output Supply</b> | Burst  | Address | Organization | Package    |

|--------------------------|-------|-----------|--------|----------------------|--------|---------|--------------|------------|

|                          | Time  | Frequency | Cycle  | Voltage              | Length | Туре    | (word x bit) |            |

|                          |       |           |        | (V <sub>DD</sub> Q)  |        |         |              |            |

|                          | ns    | MHz       | ns     | V                    |        |         |              |            |

| μPD48011318FF-FH16-FF1-A | 1.66  | 600       | 13.3   | 1.0                  | 2      | DDR     | 64 M x 18    | 180-pin    |

| μPD48011318FF-FH19-FF1-A | 1.90  | 525       |        |                      |        |         |              | TAPE FBGA  |

| μPD48011336FF-FH16-FF1-A | 1.66  | 600       |        |                      |        |         | 32 M x 36    | (18.5 x14) |

| μPD48011336FF-FH19-FF1-A | 1.90  | 525       |        |                      |        |         |              | Lead-free  |

#### **Pin Configurations**

# 180-pin TAPE FBGA (18.5 x 14) (Top View) [μPD48011318] ( x18 )

|   | 1               | 2                 | 3           | 4                 | 5               | 6 | 7           | 8 | 9               | 10                | 11          | 12                | 13              |

|---|-----------------|-------------------|-------------|-------------------|-----------------|---|-------------|---|-----------------|-------------------|-------------|-------------------|-----------------|

| Α | TMS             | $V_{DD}$          | TCK         | VddQ              | Vss             |   |             |   | Vss             | V <sub>DD</sub> Q | VEXT        | V <sub>DD</sub>   | QK0             |

| В | Vss             | DNU,<br>Vss       | Vss         | DQ6               | V <sub>DD</sub> |   | x18         |   | V <sub>DD</sub> | DNU,<br>Vss       | Vss         | DQ8               | Vss             |

| С | QVLD            | V <sub>DD</sub> Q | DNU,<br>Vss | V <sub>DD</sub> Q | DQ4             |   | Burst of 2  |   | DNU,<br>Vss     | V <sub>DD</sub> Q | DQ7         | V <sub>DD</sub> Q | QK0#            |

| D | Vss             | DNU,<br>Vss       | Vss         | DQ2               | Vss             |   | 259 sq. mm  |   | Vss             | DNU,<br>Vss       | Vss         | DQ5               | Vss             |

| Е | DNU,<br>Vss     | VddQ              | DNU,<br>Vss | V <sub>DD</sub> Q | DQ0             |   |             |   | DNU,<br>Vss     | V <sub>DD</sub> Q | DQ1         | V <sub>DD</sub> Q | DQ3             |

| F | Vss             | DINV0             | Vss         | A12               | Vss             |   |             |   | Vss             | A13               | Vss         | DNU,<br>Vss       | Vss             |

| G | V <sub>DD</sub> | V <sub>DD</sub> Q | A10         | V <sub>DD</sub> Q | A8              |   |             |   | A7              | V <sub>DD</sub> Q | A11         | V <sub>DD</sub> Q | V <sub>DD</sub> |

| Н | Vss             | RST#              | Vss         | A6                | Vss             |   | Top<br>View |   | Vss             | A5                | Vss         | DM                | Vss             |

| J | MF              | V <sub>DD</sub> Q | DK0         | Vss               | V <sub>DD</sub> |   |             |   | СК              | Vss               | DNU,<br>Vss | V <sub>DD</sub> Q | LBK#            |

| К | VREF            | Vss               | DK0#        | V <sub>DD</sub> Q | V <sub>DD</sub> |   |             |   | CK#             | V <sub>DD</sub> Q | DNU,<br>Vss | Vss               | VREF            |

| L | TRST#           | CS#               | Vss         | A4                | Vss             |   |             |   | Vss             | А3                | Vss         | WE#               | Vss             |

| М | V <sub>DD</sub> | V <sub>DD</sub> Q | DPR#        | $V_{DD}Q$         | A2              |   |             |   | REF#            | V <sub>DD</sub> Q | A9          | V <sub>DD</sub> Q | V <sub>DD</sub> |

| N | Vss             | DINV1             | Vss         | A0                | Vss             | l |             |   | Vss             | A1                | Vss         | DNU,<br>Vss       | Vss             |

| Р | DNU,<br>Vss     | V <sub>DD</sub> Q | DNU,<br>Vss | V <sub>DD</sub> Q | DQ9             |   |             |   | DNU,<br>Vss     | V <sub>DD</sub> Q | DQ10        | V <sub>DD</sub> Q | DQ12            |

| R | Vss             | DNU,<br>Vss       | Vss         | DQ11              | Vss             |   |             |   | Vss             | DNU,<br>Vss       | Vss         | DQ14              | Vss             |

| Т | QK1#            | V <sub>DD</sub> Q | DNU,<br>Vss | V <sub>DD</sub> Q | DQ13            |   |             |   | DNU,<br>Vss     | V <sub>DD</sub> Q | DQ16        | V <sub>DD</sub> Q | TDO             |

| U | Vss             | DNU,<br>Vss       | Vss         | DQ15              | V <sub>DD</sub> |   |             |   | V <sub>DD</sub> | DNU,<br>Vss       | Vss         | DQ17              | Vss             |

| ٧ | QK1             | V <sub>DD</sub>   | ZQ          | V <sub>DD</sub> Q | Vss             |   |             |   | Vss             | V <sub>DD</sub> Q | VEXT        | V <sub>DD</sub>   | TDI             |

|   |                 |                   |             |                   |                 |   |             |   |                 |                   |             |                   |                 |

DQ0-DQ17: Data inputs / outputREF#: Refresh EnableDINV0-DINV1: Data inversionLBK#: Loopback ModeDM: Write data maskMF: Mirror Function

A0-A13 : Address **TMS** : IEEE 1149.1 Test input CK, CK# : Input clock TDI : IEEE 1149.1 Test input DK0, DK0# : Input data clock **TCK** : IEEE 1149.1 Clock input QVLD : Read Data Valid TDO : IEEE 1149.1 Test output TRST# QK0-QK1, : Output data clock : IEEE 1149.1 Test reset input QK0#-QK1# VREF : HSTL input reference input

ZQ : Output impedance & Input  $V_{DD}$  : Power Supply, 1.5 V nominal termination control  $V_{DD}Q$  : DQ Power Supply, 1.0 V nominal

RST# : Master reset VEXT : Power Supply, 2.5 V nominal

CS# : Chip select Vss : Ground

WE# : Write Enable DNU,  $V_{SS}$  : Must not be used, or must be connected to  $V_{SS}$  DQ0-DQ17 : Data inputs / output DNU,  $V_{DD}Q$  : Must not be used, or must be connected to  $V_{DD}Q$

DPR# : Overlapped Refresh

# 180-pin TAPE FBGA (18.5 x 14) (Top View) [μPD48011336] ( x36 )

|   | 1               | 2                 | 3    | 4                 | 5               | 6 | 7           | 8 | 9               | 10                | 11   | 12                | 13              |

|---|-----------------|-------------------|------|-------------------|-----------------|---|-------------|---|-----------------|-------------------|------|-------------------|-----------------|

| Α | TMS             | $V_{DD}$          | TCK  | VddQ              | Vss             |   |             |   | Vss             | VddQ              | VEXT | $V_{\text{DD}}$   | QK0             |

| В | Vss             | DQ9               | Vss  | DQ6               | V <sub>DD</sub> |   | x36         |   | V <sub>DD</sub> | DQ11              | Vss  | DQ8               | Vss             |

| С | QVLD            | V <sub>DD</sub> Q | DQ10 | V <sub>DD</sub> Q | DQ4             |   | Burst of 2  |   | DQ13            | V <sub>DD</sub> Q | DQ7  | V <sub>DD</sub> Q | QK0#            |

| D | Vss             | DQ12              | Vss  | DQ2               | Vss             |   | 259 sq. mm  |   | Vss             | DQ15              | Vss  | DQ5               | Vss             |

| Е | DQ16            | VddQ              | DQ14 | V <sub>DD</sub> Q | DQ0             |   |             |   | DQ17            | VDDQ              | DQ1  | VDDQ              | DQ3             |

| F | Vss             | DINV0             | Vss  | A12               | Vss             |   |             |   | Vss             | A13               | Vss  | DINV1             | Vss             |

| G | V <sub>DD</sub> | V <sub>DD</sub> Q | A10  | V <sub>DD</sub> Q | A8              |   |             |   | A7              | V <sub>DD</sub> Q | A11  | V <sub>DD</sub> Q | V <sub>DD</sub> |

| Н | Vss             | RST#              | Vss  | A6                | Vss             |   | Top<br>View |   | Vss             | A5                | Vss  | DM                | Vss             |

| J | MF              | V <sub>DD</sub> Q | DK0  | Vss               | V <sub>DD</sub> |   |             |   | СК              | Vss               | DK1  | V <sub>DD</sub> Q | LBK#            |

| К | VREF            | Vss               | DK0# | V <sub>DD</sub> Q | V <sub>DD</sub> |   |             |   | CK#             | V <sub>DD</sub> Q | DK1# | Vss               | VREF            |

| L | TRST#           | CS#               | Vss  | A4                | Vss             |   |             |   | Vss             | A3                | Vss  | WE#               | Vss             |

| М | V <sub>DD</sub> | V <sub>DD</sub> Q | DPR# | V <sub>DD</sub> Q | A2              |   |             |   | REF#            | V <sub>DD</sub> Q | A9   | V <sub>DD</sub> Q | V <sub>DD</sub> |

| N | Vss             | DINV2             | Vss  | A0                | Vss             |   |             |   | Vss             | A1                | Vss  | DINV3             | Vss             |

| Р | DQ35            | V <sub>DD</sub> Q | DQ34 | V <sub>DD</sub> Q | DQ18            |   |             |   | DQ33            | V <sub>DD</sub> Q | DQ19 | V <sub>DD</sub> Q | DQ21            |

| R | Vss             | DQ32              | Vss  | DQ20              | Vss             |   |             |   | Vss             | DQ31              | Vss  | DQ23              | Vss             |

| Т | QK1#            | V <sub>DD</sub> Q | DQ30 | V <sub>DD</sub> Q | DQ22            |   |             |   | DQ29            | V <sub>DD</sub> Q | DQ25 | V <sub>DD</sub> Q | TDO             |

| U | Vss             | DQ28              | Vss  | DQ24              | V <sub>DD</sub> |   |             |   | V <sub>DD</sub> | DQ27              | Vss  | DQ26              | Vss             |

| ٧ | QK1             | V <sub>DD</sub>   | ZQ   | V <sub>DD</sub> Q | Vss             |   |             |   | Vss             | V <sub>DD</sub> Q | VEXT | V <sub>DD</sub>   | TDI             |

|   |                 |                   |      |                   |                 |   |             |   |                 |                   |      |                   |                 |

DQ0-DQ35: Data inputs / outputREF#: Refresh EnableDINV0-DINV3: Data inversionLBK#: Loopback ModeDM: Write data maskMF: Mirror Function

A0-A13 : Address TMS : IEEE 1149.1 Test input

CK, CK# : Input clock TDI : IEEE 1149.1 Test input

DK0-DK1, : Input data clock TCK : IEEE 1149.1 Clock input

DK0#-DK1# TDO : IEEE 1149.1 Test output

OVID: : Read Data Valid

QVLD : Read Data Valid TRST# : IEEE 1149.1 Test reset input QK0-QK1, : Output data clock  $V_{\mathsf{REF}}$ : HSTL input reference input QK0#-QK1#  $V_{DD}$ : Power Supply, 1.5 V nominal ZQ : Output impedance & Input  $V_{DD}Q$ : DQ Power Supply, 1.0 V nominal termination control  $V_{EXT}$ : Power Supply, 2.5 V nominal

RST# : Master reset Vss : Ground

CS# : Chip select DNU, Vss : Must not be used, or must be connected to Vss

WE# : Write Enable DNU, VDDQ : Must not be used, or must be connected to VDDQ

DPR# : Overlapped Refresh

Pin Identification (1/2)

| Symbol      | Direction | I/O Type   | Freq MHz  | Description                                                           |

|-------------|-----------|------------|-----------|-----------------------------------------------------------------------|

| CK, CK#     | Input     | 1.0 V HSIO | 600 / 525 | Clock inputs:                                                         |

|             |           |            |           | CK and CK# are differential clock inputs. This input clock pair       |

|             |           |            |           | registers address and control inputs on the rising edge of CK. CK# is |

|             |           |            |           | ideally 180 degrees out of phase with CK.                             |

| DK0-DK1,    | Input     | 1.0 V HSIO | 600 / 525 | Differential clocks for DQ inputs:                                    |

| DK0#-DK1#   |           |            |           | DK0, DK0# => DQ0-DQ17, DM                                             |

|             |           |            |           | DK1, DK1# => DQ18-DQ35                                                |

|             |           |            |           | Note that DK1,DK1# are only active on x36 parts.                      |

| CS#         | Input     | 1.0 V HSIO | 600 / 525 | Chip select                                                           |

|             |           |            |           | CS# enables the commands when CS# is LOW and disables them            |

|             |           |            |           | when CS# is HIGH. When the command is disabled, new commands          |

|             |           |            |           | are ignored, but internal operations continue.                        |

| WE#, REF#   | Input     | 1.0 V HSIO | 600 / 525 | Write enable, Refresh enable :                                        |

|             |           |            |           | WE#, REF# are sampled at the positive edge of CK, WE#, and REF#       |

|             |           |            |           | define (together with CS#) the command to be executed.                |

| RST#        | Input     | 1.0 V HSIO | -         | Master reset                                                          |

|             |           | (no ODT)   |           | Note that this pin has no on-die termination.                         |

| DPR#        | Input     | 1.0 V HSIO | 600 / 525 | Overlapped Refresh                                                    |

| LBK#        | Input     | 1.0 V HSIO | -         | Loopback mode for control pin de-skew training                        |

|             |           | (no ODT)   |           | Note that this pin has no on-die termination.                         |

| MF          | Input     | 1.0 V HSIO | DC        | Causes "mirroring" of certain pins as described in                    |

|             |           | (no ODT)   |           | 2.14 Clam-shell support.                                              |

|             |           |            |           | Note that this pin has no on-die termination.                         |

| A0-A13      | Input     | 1.0 V HSIO | 600 / 525 | Address inputs for DDR Address                                        |

|             |           |            | DDR       | Address bus, including bank select bits.                              |

|             |           |            |           | A13 is veserved for future use.                                       |

| DQ0-DQ35    | Input     | 1.0 V HSIO | 600 / 525 | Data input/output:                                                    |

|             | /Output   |            |           | The DQ signals form the 36 bit data bus. During READ commands,        |

|             |           |            |           | the data is referenced to both edges of QKx. During WRITE             |

|             |           |            |           | commands, the data is sampled at both edges of DKx.                   |

| DINV0-DINV3 | Input     | 1.0 V HSIO | 600 / 525 | Data inversion state for DQ inputs:                                   |

|             | /Output   |            |           | DINV0 => DQ0-DQ8                                                      |

|             |           |            |           | DINV1 => DQ9-DQ17                                                     |

|             |           |            |           | DINV2 => DQ18-DQ26                                                    |

|             |           |            |           | DINV3 => DQ27-DQ35                                                    |

|             |           |            |           | Note that DINV2-DINV3 are only active on x36 parts                    |

| DM          | Input     | 1.0 V HSIO | 600 / 525 | Write data mask;disables writing of the corresponding data value.     |

|             | 1         |            |           | Clocked by DK0.                                                       |

(2/2)

| Symbol            | Direction | I/O Type   | Freq MHz  | Description                                                                  |

|-------------------|-----------|------------|-----------|------------------------------------------------------------------------------|

| QK0-QK1,          | Output    | 1.0 V HSIO | 600 / 525 | Output data clocks:                                                          |

| QK0#-QK1#         |           |            |           | Differential clocks for DQ, QVLD outputs:                                    |

|                   |           |            |           | QK0/QK0# => x36: DQ0-DQ17, x18: DQ0-DQ8, QVLD                                |

|                   |           |            |           | QK1/QK1# => x36: DQ18-DQ35, x18: DQ9-DQ17                                    |

| QVLD              | Output    | 1.0 V HSIO | 600 / 525 | Data valid;                                                                  |

|                   |           |            |           | The QVLD indicates valid output data. QVLD is edge-aligned with QKx and      |

|                   |           |            |           | QKx#.                                                                        |

| TMS, TDI          | Input     | 1.0 V HSIO |           | JTAG function pins:                                                          |

|                   |           |            |           | IEEE 1149.1 test inputs: These balls may be left as no connects if the       |

|                   |           |            |           | JTAG function is not used in the circuit                                     |

| TCK               | Input     | 1.0 V HSIO |           | JTAG function pin;                                                           |

|                   |           |            |           | IEEE 1149.1 clock input: This ball must be tied to Vss if the JTAG function  |

|                   |           |            |           | is not used in the circuit.                                                  |

| TDO               | Output    | 1.0 V HSIO |           | JTAG function pin;                                                           |

|                   |           |            |           | IEEE 1149.1 test output: JTAG output.                                        |

|                   |           |            |           | This ball may be left as no connect if JTAG function is not used.            |

| TRST#             | Input     | 1.0 V HSIO |           | JTAG reset;                                                                  |

|                   |           |            |           | IEEE 1149.1 test rest: This ball must be tied to Vss if the JTAG function is |

|                   |           |            |           | not used in the circuit.                                                     |

| ZQ                | Analog    |            |           | Output impedance and input termination control                               |

| V <sub>REF</sub>  | Ref       |            |           | VddQx0.7 V I/O reference voltage.                                            |

| VEXT              | Supply    |            |           | Power supply; 2.5 V nominal. See Recommended DC Operating                    |

|                   |           |            |           | Conditions for range.                                                        |

| V <sub>DD</sub>   | Supply    |            |           | Power supply; 1.5 V nominal. See Recommended DC Operating                    |

|                   |           |            |           | Conditions for range.                                                        |

| V <sub>DD</sub> Q | Supply    |            |           | DQ power supply;                                                             |

|                   |           |            |           | Nominally, 1.0 V. Isolated on the device for improved noise immunity.        |

|                   |           |            |           | See Recommended DC Operating Conditions for range.                           |

| Vss               | Supply    |            |           | Ground                                                                       |

| DNU, Vss          |           |            |           | Do Not Use, Or must not be used, or must be connected to Vss.                |

| DNU, VDDQ         |           |            |           | Do Not Use, Or must not be used, or must be connected to V <sub>DD</sub> Q   |

$\label{eq:hsions} \mbox{HSIO} \mbox{ is a single-ended 1.0 V high-side terminated I/O described in \textbf{1. Electrical Specifications}.$

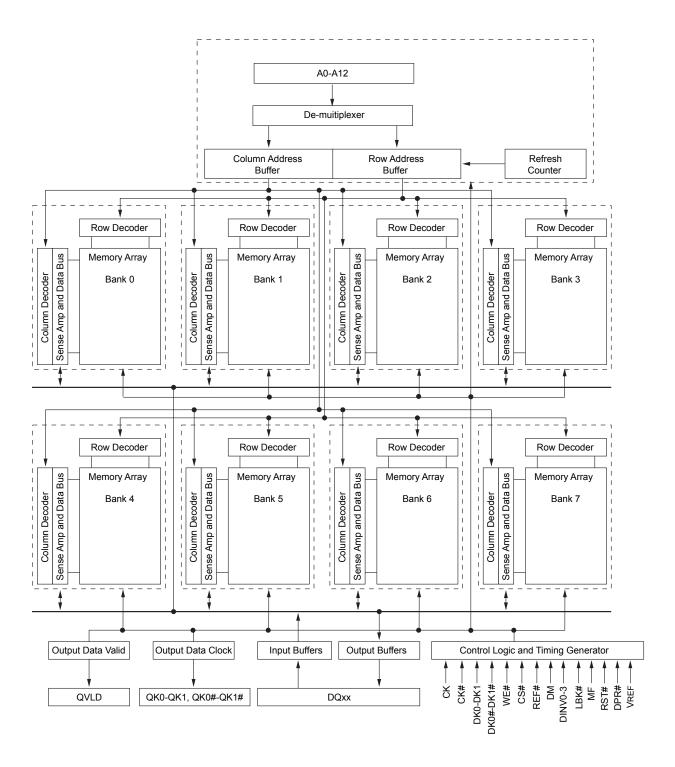

# **Block Diagram**

# **Contents**

| 1. | Elec  | trical Specifications             | 9    |

|----|-------|-----------------------------------|------|

| 2. | Ope   | ration                            | 17   |

|    | 2.1   | Interface Overview                | 17   |

|    | 2.2   | Clocking                          | 17   |

|    | 2.3   | Address bus                       | 18   |

|    | 2.4   | Command encoding                  | 18   |

|    | 2.5   | Data mask                         | 21   |

|    | 2.6   | Data inversion                    | 21   |

|    | 2.7   | Data bus turn-around              | 21   |

|    | 2.8   | Command cycles                    | 21   |

|    | 2.9   | Write data cycles                 | 21   |

|    | 2.10  | Read data cycles                  | . 22 |

|    | 2.11  | READ and WRITE command protocol   | 22   |

|    | 2.12  | Automatic Refresh                 | .24  |

|    | 2.13  | Overlapped Refresh pin (DPR#)     | . 25 |

|    | 2.14  | Clam-shell support                | .26  |

|    |       |                                   |      |

| 3. |       | alization                         |      |

|    |       | Power-on                          |      |

|    |       | Reset                             |      |

|    |       | nitial impedance settings         |      |

|    |       | Per-bit de-skew training sequence |      |

|    | 3.5 ( | Configuration                     | .33  |

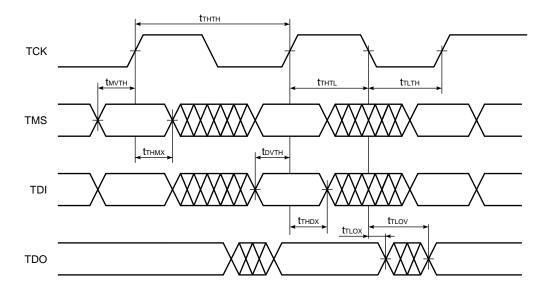

| 4. | JTA   | G Specification                   | . 38 |

|    |       | Fest Pins                         |      |

|    |       | JTAG AC Test Conditions           |      |

|    |       | Boundary Scan                     |      |

|    |       | ITAG Instructions                 |      |

|    |       | FAP Controller State Diagram      |      |

|    | 7.0 1 | - Controllor Cutto Diagram        | . 70 |

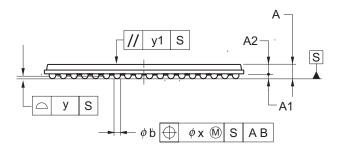

| 5. | Pacl  | kage Drawing                      | 49   |

#### 1. Electrical Specifications

**Absolute Maximum Ratings**

| Parameter                             | Symbol              | Conditions    | Rating         | Unit |

|---------------------------------------|---------------------|---------------|----------------|------|

| Supply voltage                        | VEXT                | 2.5 V nominal | -0.3 to +2.8   | V    |

| Supply voltage                        | V <sub>DD</sub>     | 1.5 V nominal | -0.3 to +1.95. | V    |

| Output supply voltage,                | V <sub>DD</sub> Q   | 1.0 V nominal | –0.3 to +1.35  | V    |

| Input voltage, Input / Output voltage |                     |               |                |      |

| Input / Output voltage                | VIH / VIL           | 1.0 V nominal | –0.3 to +1.35  | V    |

| Junction temperature                  | T <sub>j</sub> MAX. |               | 105            | °C   |

| Storage temperature                   | Tstg                |               | -55 to +125    | °C   |

Caution Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

# **Recommended DC Operating Conditions**

$0^{\circ}C \le T_{C} \le 95^{\circ}C$

| Parameter                  | Symbol            | MIN.                    | TYP.                  | MAX.                   | Unit | Comments               | Note  |

|----------------------------|-------------------|-------------------------|-----------------------|------------------------|------|------------------------|-------|

| Supply voltage             | VEXT              | 2.3                     | 2.5                   | 2.7                    | V    |                        | 1     |

| Supply voltage             | V <sub>DD</sub>   | 1.395                   | 1.5                   | 1.605                  | V    |                        | 1     |

| Output supply voltage      | V <sub>DD</sub> Q | 0.95                    | 1.0                   | 1.05                   | ٧    |                        | 1     |

| Reference voltage          | VREF              | VDDQ*0.69               | V <sub>DD</sub> Q*0.7 | V <sub>DD</sub> Q*0.71 | V    |                        | 1,2,4 |

| High level output voltage  | Voh (DC)          | V <sub>DD</sub> Q-0.025 |                       |                        | V    |                        | 1     |

| Low level output voltage   | Vol (DC)          |                         | V <sub>DD</sub> Q*0.4 |                        | V    | Z <sub>ol</sub> =40 Ω, | 1     |

|                            |                   |                         |                       |                        |      | RL=60 Ω                |       |

| High level input voltage   | VIH (DC)          | V <sub>REF</sub> +0.07  |                       | V <sub>DD</sub> Q+0.3  | V    |                        | 1,4   |

| Low level input voltage    | VIL (DC)          | -0.3                    |                       | VREF-0.07              | V    |                        | 1,4   |

| Clock input voltage        | VIn               | -0.3                    |                       | V <sub>DD</sub> Q+0.3  | V    |                        |       |

| Clock differential voltage | VID               | 0.2                     |                       | V <sub>DD</sub> Q+0.6  | V    |                        |       |

| Output Impedance HIGH      | Zoh               |                         | 60                    |                        | Ω    |                        | 3     |

| Output Impedance LOW       | Zol               |                         | 40                    |                        | Ω    |                        | 3     |

| Input Impedance LOW        | Zi                |                         | 60                    |                        | Ω    |                        | 4     |

**Notes 1.** All voltage referenced to Vss (GND)

- 2. Peak to Peak AC noise on VREF must not exceed +/- 2 % VDDQ (DC)

- 3. Programmable via ZQ and Reset Impedance Control

- 4. High-side termination (programmable via ZQ and Reset/MRS)

#### **DC Characteristics**

$0^{\circ}C \leq T_{\text{C}} \leq 95^{\circ}C; \ \ 1.395 \ V \leq V_{\text{DD}} \leq 1.605 \ V, \ unless \ otherwise \ noted$

| Parameter               | Symbol | Test condition | MIN. | MAX. | Unit | Note |

|-------------------------|--------|----------------|------|------|------|------|

| Input leakage current   | lu     |                | 0    | 50   | μΑ   | 1    |

| Output leakage current  | Іьо    |                | 0    | 50   | μΑ   | 1    |

| 3 state leakage current | loz    |                | 0    | 50   | μΑ   | 1    |

Notes 1. Outputs Driver High-Z and ODT Disabled.

# Capacitance (TA = 25 °C, f = 1MHz)

| Parameter                               | Symbol           | Test conditions        | MIN. | MAX. | Unit |

|-----------------------------------------|------------------|------------------------|------|------|------|

| Input capacitance                       | Cin              | V <sub>IN</sub> = 0 V  |      | 1.5  | pF   |

| (CK,DK, CS#, WE#, REF#, A, DM)          |                  |                        |      |      |      |

| I/O, Output, Other capacitance          | C <sub>I/O</sub> | V <sub>I/O</sub> = 0 V |      | 1.8  | pF   |

| (DQ, DINV, QVLD)                        |                  |                        |      |      |      |

| Input capacitance delta between         | Срск             | V <sub>IN</sub> = 0 V  |      | 0.15 | pF   |

| differential clock pins                 |                  |                        |      |      |      |

| Input capacitance delta between DQ pins | CDDQ             | V <sub>I/O</sub> = 0 V |      | 0.2  | pF   |

| Input capacitance delta between CS#,    | CDCTL            | V <sub>IN</sub> = 0 V  |      | 0.2  | pF   |

| WE#, REF#, A, DM pins                   |                  |                        |      |      |      |

**Remark** These parameters are periodically sampled and not 100% tested.

Capacitance is not tested on ZQ pin.

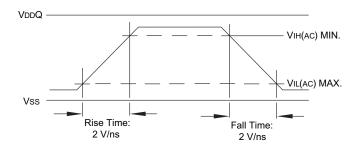

# **Recommended AC Operating Conditions**

$0^{\circ}C \leq T_{\text{C}} \leq 95^{\circ}C; \ 1.395 \ V \leq V_{\text{DD}} \leq 1.605 \ V,$  unless otherwise noted

| Parameter          | Symbol   | Conditions | MIN.                   | MAX.      | Unit | Note |

|--------------------|----------|------------|------------------------|-----------|------|------|

| Input HIGH voltage | VIH (AC) |            | V <sub>REF</sub> +0.13 | VDDQ+0.3  | V    | 1    |

| Input LOW voltage  | VIL (AC) |            | -0.3                   | VREF-0.13 | V    | 1    |

**Note 1.** Overshoot:  $V_{IH (AC)} \le V_{DD}Q + 0.3 V$  for  $t \le t_{CK}/5$

Undershoot: VIL (AC)  $\geq -0.3$  V for  $t \leq t \text{ck/}5$

Control input signals may not have pulse widths less than tckH (MIN.) or operate at cycle rates less than tck (MIN.).

# **DC Characteristics**

| Parameter               | Symbol | Test condition                                                                                                                                                                                                              |            | Max   | Unit | Note |

|-------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|------|------|

| Total power consumption | PD     | Nominal supply voltage Sequential bank access Overlapped refresh mode Data inversion enabled Half address and data transitions 30% Write and 70% Read operation ODT= $60\Omega$ , Zoh/Zol = $60\Omega/40\Omega$ Tc= $95$ °C | x18<br>x36 | - 2.4 | w    | 1    |

Note 1. Including all the power supply ( $V_{DD}$ ,  $V_{DD}Q$  and  $V_{EXT}$ )

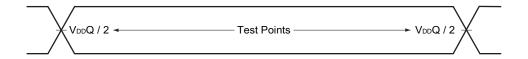

#### **AC Characteristics**

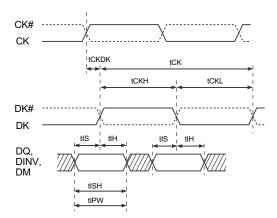

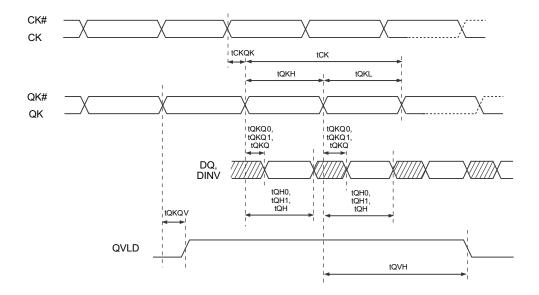

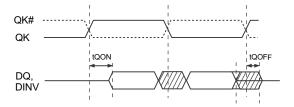

#### Normal bus timing

Standard bus timing waveforms and values for command and data are shown in Figure 1-1 through Figure 1-6 and Interface AC Parameters. All timing is measured to/from the crossing point on differential clocks and to/from the VREF crossing point on single-ended signals.

tCK tCKH tCKL CK#

Figure 1-1 Command and DDR Address Input Timing Waveforms

tAS tASH tASH tCS CS#, WE#, REF#, DPR# tCSH

**Figure 1-2 Data Input Timing Waveforms**

**Figure 1-3 Data Output Timing Waveforms**

Figure 1-4 Output Driver Enable/Disable Timing

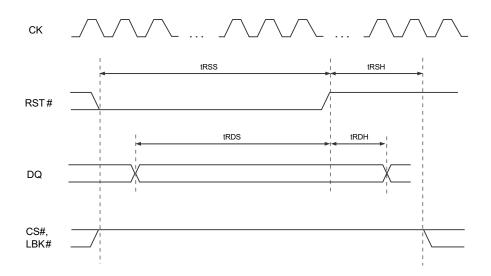

Figure 1-5 Reset Timing Waveforms

**Note** The clock must be with specification and all other chip inputs must be driven to legal values throughout the tass period.

# **Interface AC Parameters**

(1/2)

|                                               |               |        |       |        |       |          | (1/2) |

|-----------------------------------------------|---------------|--------|-------|--------|-------|----------|-------|

| Parameter                                     | Symbol        |        | H16   |        | H19   | Unit     | Note  |

|                                               |               | ( 600  | MHz ) | ( 525  | MHz)  |          |       |

|                                               |               | MIN.   | MAX.  | MIN.   | MAX.  |          |       |

| CK, DK, QK clock period (maximum 600 MHz      | tск           | 1.587  | 2.500 | 1.813  | 2.500 | ns       |       |

| clock frequency, minimum 400 MHz)             |               |        |       |        |       |          |       |

| CK, DK LOW time (assumes 5% duty cycle        | <b>t</b> ckL  | 0.45*  |       | 0.45*  |       | tcк(avg) | 5     |

| distortion at 600 MHz)                        |               |        |       |        |       |          |       |

| CK, DK HIGH time (assumed 5% duty cycle       | <b>t</b> скн  | 0.45*  |       | 0.45*  |       | tcк(avg) | 5     |

| distortion at 600 MHz)                        |               |        |       |        |       |          |       |

| Clock period jitter                           | tлт(per)      | -0.070 | 0.070 | -0.070 | 0.070 | ns       | 6,7   |

| Cycle-to-cycle clock jitter                   | tлт(cc)       |        | 0.140 |        | 0.140 | ns       |       |

| A to CK setup                                 | tas           | 0.213  |       | 0.244  |       | ns       | 2     |

| CK to A hold                                  | tан           | 0.213  |       | 0.244  |       | ns       | 1     |

| CK to A setup/hold window                     | <b>t</b> ash  | 0.213  |       | 0.244  |       | ns       | 4     |

| A input pulse width                           | <b>t</b> apw  | 0.266  |       | 0.305  |       | ns       |       |

| CS#, WE#, REF#, DPR# to CK setup              | tcs           | 0.240  |       | 0.275  |       | ns       | 2     |

| CK to CS#, WE#, REF#, DPR# hold               | tсн           | 0.240  |       | 0.275  |       |          | 1     |

| CK to CS#, WE#, REF#, DPR# setup/hold         | <b>t</b> csH  | 0.400  |       | 0.458  |       | ns       | 4     |

| window                                        |               |        |       |        |       |          |       |

| CS#, WE#, REF#, DPR# input pulse width        | <b>t</b> cpw  | 0.533  |       | 0.610  |       | ns       |       |

| CK to DK skew                                 | <b>t</b> CKDK | -0.266 | 0.266 | -0.304 | 0.304 | ns       |       |

| DQ, DINV, DM to DK setup                      | tıs           | 0.213  |       | 0.244  |       | ns       | 2     |

| DK to DQ, DINV, DM hold                       | tıн           | 0.213  |       | 0.244  |       | ns       | 1     |

| DK to DQ, DINV, DM setup/hold window          | <b>t</b> ısh  | 0.213  |       | 0.244  |       | ns       | 4     |

| DQ, DINV, DM input pulse width                | tıpw          | 0.266  |       | 0.305  |       | ns       |       |

| Output signal rise time [See note]            | tRise         | 2      | 5     | 2      | 5     | V/ns     | 3     |

| Output signal rise time [See note]            | <b>t</b> Fall | 2      | 5     | 2      | 5     | V/ns     | 3     |

| QK LOW time                                   | <b>t</b> QKL  | 0.45*  |       | 0.45*  |       | tcк(avg) | 5     |

| (assumes 5% duty cycle distortion at 600 MHz) |               |        |       |        |       |          |       |

| QK HIGH time                                  | tqкн          | 0.45*  |       | 0.45*  |       | tcк(avg) | 5     |

| (assumed 5% duty cycle distortion at 600 MHz) |               |        |       |        |       |          |       |

| CK to QK skew                                 | <b>t</b> ckqk | -0.400 | 0.400 | -0.458 | 0.458 | ns       |       |

| Additional t <sub>RL</sub> delay in loopback  | <b>t</b> cD   |        | 5     |        | 5     | ns       |       |

| QK0 to DQ[17:0], DINV[1:0] (x36) or DQ[8:0],  | takao         |        | 0.133 |        | 0.152 | ns       | 8     |

| DINV[0] (x18)                                 |               |        |       |        |       |          |       |

| QK0 to DQ[17:0], DINV[1:0] (x36) or DQ[8:0],  | tано          | 0.4*   |       | 0.4*   |       | tcк(avg) | 5     |

| DINV[0] (x18)                                 |               |        |       |        |       |          |       |

| QK1 to DQ[35:18], DINV[3:2] (x36) or          | <b>t</b> QKQ1 |        | 0.133 |        | 0.152 | ns       | 8     |

| DQ[17:9],DINV[1] (x18)                        |               |        |       |        |       |          |       |

| QK1 to DQ[35:18], DINV[3:2] (x36) or          | <b>t</b> QH1  | 0.4*   |       | 0.4*   |       | tск(avg) | 5     |

| DQ[17:9],DINV[1] (x18)                        |               |        |       |        |       |          |       |

| 1 | 1 | 10 | ١ |

|---|---|----|---|

| l | _ | ız | J |

| Parameter                             | Symbol        | –FI<br>( 600) | 116<br>MHz ) | –FI<br>( 525l | 119<br>MHz ) | Unit        | Note |

|---------------------------------------|---------------|---------------|--------------|---------------|--------------|-------------|------|

|                                       |               | MIN.          | MAX.         | MIN.          | MAX.         |             |      |

| Any QK to any DQ, DINV                | <b>t</b> ακα  |               | 0.200        |               | 0.288        | ns          | 8    |

| Any QK to any DQ, DINV                | <b>t</b> QH   | 0.35*         |              | 0.35*         |              | tск(avg)    | 5    |

| Any QK to QVLD                        | <b>t</b> ακαν |               | 0.200        |               | 0.288        | ns          |      |

| Any QK to QVLD                        | tqvн          | 0.85*         |              | 0.85*         |              | tск(avg)    | 5    |

| QK to DQ output driver turn-on time   | <b>t</b> QON  |               | 0.133        |               | 0.152        | ns          |      |

| and ODT turn-on time                  |               |               |              |               |              |             |      |

| QK to DQ output driver turn-off time  | <b>t</b> qoff | -0.1*         | 0.133        | -0.1*         | 0.152        | tск(avg)    | 5    |

| and ODT turn-on time                  |               |               |              |               |              |             |      |

| DQ to RST# setup                      | <b>t</b> RDS  | 1000 *        |              | 1000 *        |              | <b>t</b> cĸ | 2    |

| DQ to RST# hold                       | <b>t</b> RDH  | 5 *           |              | 5 *           |              | <b>t</b> cĸ | 1    |

| RST# pulse length                     | trss          | 200           |              | 200           |              | μs          |      |

| RST# deasserted to CS#, DPR#,         | <b>t</b> rsh  | 400000 *      |              | 400000 *      |              | <b>t</b> cĸ |      |

| or LBK# asserted                      |               |               |              |               |              |             |      |

| Time for PLL to stabilize after being | <b>t</b> PLL  |               | 20           |               | 20           | μs          |      |

| enabled                               |               |               |              |               |              |             |      |

| MRS command start to next CS#, DPR#,  | <b>t</b> MRD  | 24 *          |              | 24 *          |              | tск         |      |

| or LBK# assertion                     |               |               |              |               |              |             |      |

Notes 1. All input hold timing assumes rising edge slew rate of 2 V/ns measured from ViL/ViH (DC) to VREF.

- 2. All input setup timing assumes falling edge slew rate of 2 V/ns measured from VREF to VIL/VIH(AC)

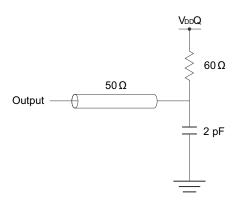

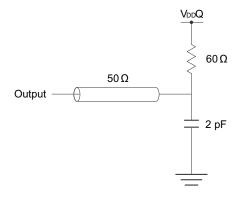

- 3. All output timing assumes the load shown in Figure 1-6.

- **4.** Setup/hold windows, tash, tcsh, tish are used for de-skew timing budgeting and are based on electrical simulations. These cannot be directly measured without performing de-skew training.

- 5. tck (avg) is the value of tck averaged over 200 clock cycles.

- **6.** Clock phase jitter is the variance from clock rising edge to the next expected clock rising edge.

- 7. Frequency drift is not allowed.

- 8. taka, takax are guaranteed by design.

Figure 1-6 Output Load

#### **Temperature and Thermal Impedance**

#### **Temperature Limits**

| Parameter                        | Symbol | MIN. | MAX. | Unit | Note |

|----------------------------------|--------|------|------|------|------|

| Reliability junction temperature | TJ     | 0    | +105 | °C   | 1    |

| Operating junction temperature   | TJ     | 0    | +100 | °C   | 2    |

| Operating case temperature       | Tc     | 0    | +95  | °C   | 3    |

- **Notes 1.** Temperatures greater than 105°C may cause permanent damage to the device. This is a stress rating only and functional operation of the device at or above this is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability of the part.

- 2. Junction temperature depends upon cycle time, loading, ambient temperature, and airflow.

- **3.** MAX operating case temperature; Tc is measured in the center of the package. Device functionality is not guaranteed if the device exceeds maximum Tc during operation.

#### Thermal Impedance

| Substrate |                  | θja (°C/W)       | θjb              | θjc    |        |  |

|-----------|------------------|------------------|------------------|--------|--------|--|

|           | Air Flow = 0 m/s | Air Flow = 1 m/s | Air Flow = 2 m/s | (°C/W) | (°C/W) |  |

| 4 - Layer | 17.5             | 14.0             | 13.1             | 8.2    | 0.8    |  |

#### **Impedance Controls**

The Low Latency DRAM-III includes programmable impedance control that affects the output impedance of all output and bidirectional pins, as well as the termination of all input and bidirectional pins. The output impedance control affects all output pins and the input termination control affects those pins grouped together as shown in **Table 3-5** and **Table 3-6**. The impedance control affects the drive strengths of both high and low values, as well as the high-side termination impedance. The impedance is controlled via a precision resistor connected between the ZQ and Vss pins. The nominal value of the precision (1%) resistor is 240  $\Omega$ , with a supported range of 200 to 240  $\Omega$ .

The output impedance accuracy is within 15% of the programmed nominal value, with the linearity measured at the points described in **Impedance Test Parameters**. The actual impedance must remain within the range specified by the linear interpolation of the values at those points.

Normally, the input termination and output impedance are continuously adjusted, such that only minor instantaneous variations in the impedance occur. However, when the FZ bit in the configuration register is set, then the input termination and output impedance will be "frozen" at their current values. If the IM bit in the configuration register is set, then the output impedance will have a nominal value that is not dependent on the value of the resistor connected to the ZQ pin. In this mode, the ZQ pin is ignored by the Low Latency DRAM-III, and the output impedances will not be PVT compensated

#### **Impedance Test Parameters**

| Parameter                                                  | Symbol | MIN.  | NORM. | MAX.  | Unit |

|------------------------------------------------------------|--------|-------|-------|-------|------|

| Output HIGH voltage with forced Ioh = -(VDDQ -0.85 V)/ Zoh | Voh    | 0.723 | 0.85  | 0.978 | V    |

| Output HIGH voltage with forced Ioh = -(VDDQ -0.7 V) / Zoh | Voh    | 0.595 | 0.7   | 0.805 | V    |

| Output LOW voltage with forced Iol = 0.7 V / Zol           | Vol    | 0.595 | 0.7   | 0.805 | V    |

| Output LOW voltage with forced Iol = 0.55 V / Zol          | Vol    | 0.468 | 0.55  | 0.633 | V    |

# 2. Operation

#### 2.1 Interface Overview

The primary Low Latency DRAM-III interface consists of a unidirectional command and address bus and a bidirectional data bus. This type of data bus is often referred to as common I/O or CIO. **Pin Identification** contains the list of pins on the Low Latency DRAM-III.

The command bus is a single data rate (SDR) bus consisting of CS#, WE#, and REF#. The  $\mu$ PD480113xx have a double data rate (DDR) address bus consisting of multiplexed. Both the command bus and address bus are clocked by the differential clock pair CK and CK#. READ and WRITE commands can be issued at a rate of one every cycle in burst length 2 mode.

The data interface is a double-rate (DDR) interface that transfers 36 bits of data Note on each clock edge for 36-bit parts and 18 bits of data on each clock edge for 18-bit parts. The data interface also includes 4 data inversion pins. In addition to 36 data bits, the inputs to the Low Latency DRAM -III include a DDR data mask, DM, and two differential clock pairs, DK0-DK1 and DK0#-DK1#. The Low Latency DRAM -III outputs two differential clock pairs, QK0-QK1 and QK0#-QK1# that are associated with read data, and a data valid signal, QVLD. Because the data bus is bidirectional, idle cycles are required to implement data bus turn-around as described in **2.7 Data bus turn-around**.

**Note** For parts with 18-bit data bus, all references in this section should refer to DQ0-DQ17 and DINV0- DINV1 unless otherwise noted. DQ0-DQn is used to represent DQ0-DQ35 or DQ0-DQ17 for 36-bit and 18-bit parts, respectively, and DINV0-DINVm is used to represent either DINV0-DINV3 or DINV0-DINV1 for 36-bit and 18-bit parts.

# 2.2 Clocking

There are three groups of clock signals: CK/CK#, DK0-DK1/DK0#-DK1#, and QK0-QK1/QK0#-QK1#.

The CK/CK# clock is associated with the address and command pins: A0-A13, CS#, WE#, REF#, and DPR#. At the Low Latency DRAM-III pins, the CK/CK# transitions are nominally centered with respect to address and command signal transitions.

The DK0-DK1/DK0#-DK1# clocks are associated with write data. DK0/DK0# is used as a source-centered clock for the double data rate DQ0-DQ17, DINV0-DINV1, and DM pins. DK1/DK1# is used as a source-centered clock for the double data rate DQ18-DQ35 and DINV2-DINV3 pins.

The DK0-DK1/DK0#-DK1# clocks must meet the specified toxdx skew with respect to the CK/CK# clock in order to ensure proper timing relationship between command and data cycles and to enable proper data bus turn-around. The QK0-QK1/QK0#-QK1# clocks are associated with read data. At the Low Latency DRAM-III pins, and for x36 devices, QK0/QK0# must be source-synchronous with the read data DQ0-DQ17, DINV0-DINV1, and QVLD pins. Similarly, for x36 devices, QK1/QK1# is used as a source-synchronous clock for the read data DQ18-DQ35 and DINV2-DINV3 pins. For x18 devices, QK0/QK0# must be source-synchronous with DQ0-DQ8, DINV0, and QVLD. Similarly, for x18 devices, QK1/QK1# must be source-synchronous with DQ9-DQ17 and DINV1.

The QK0-QK1/QK0#-QK1# clocks must meet the specified tokok skew with respect to the CK/CK# clock in order to ensure proper timing relationship between command and data cycles and to enable proper data bus turn-around.

#### 2.3 Address bus

In Burst of 2 mode one clock cycle is required to load an address. In DDR Address mode address inputs are captured by the RAM in two beats per cycle. Three of the bits in the address field select which of the 8 banks in the RAM will be accessed. Note that a 4th bank address bit has been identified anticipating that a 16 bank version of the RAM might someday reach the market. The bit functions as an ordinary address bit in the devices described in this data sheet.

Device A13 Note1 A12 Note1 Command Beat A11 A10 Α9 **A2** Α1 A0 **A8** Α7 **A6** Α5 Α4 А3 Width **Addres READ or WRITE** x36 0 9.7Gb 2.4Gb Bank s X 4.8Gb 1 **Address Addres** A Note2 READ or WRITE x18 0 4.8Gb Bank 9.7Gb 2.4Gb Address AUTO REFRESH ANY Χ Χ Χ Χ Х Χ Χ X X Bank 0 X X

Table 2-1 Address Bit Encoding

- **Note 1.** A13 are reserved for future expansion. For smaller capacity devices, the value is a don't care, but for devices of the designated capacity or larger, the value will be used.

- **2.** Address bit A3 in beat zero is used as an address bit in the current devices, but may be used as a bank address bit in future generations of the part.

#### 2.4 Command encoding

The Low Latency DRAM-III supports five types of command cycles as show in Table 2-3.

The NOP command must be used on any cycle where no other commands are requested.

The READ command is used to initiate a burst read from the Low Latency DRAM -III.

The WRITE command is used to initiate a burst write from the Low Latency DRAM -III.

The AUTO REFRESH command is used to initiate a refresh operation on a particular bank of the memory.

The OVERLAPPED REFRESH command is used to initiate a refresh operation, but may be overlapped with other commands.

The MRS command is used to configure the Low Latency DRAM -III following a reset.

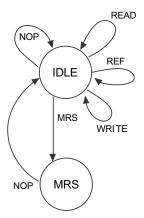

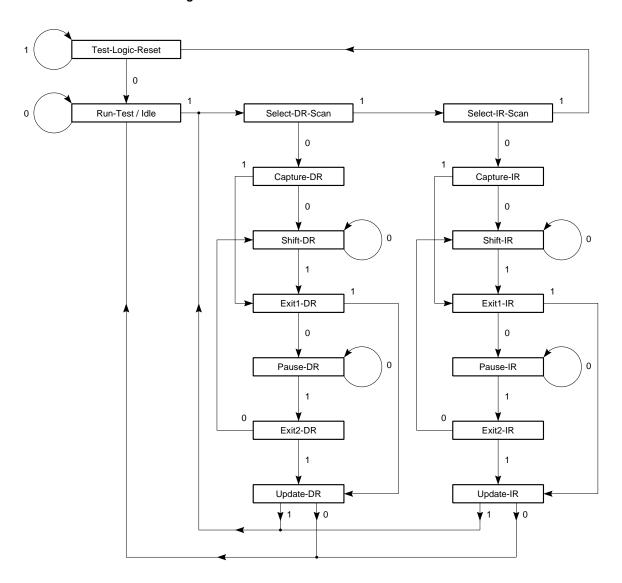

Because the overlapped refresh feature can be enabled or disabled, the command decoding and it's associated state diagram have two different forms. **Table 2-2** and **Figure 2-1** show the command encoding for the case when the overlapped refresh feature is disabled. **Figure 2-1** only shows the state diagram for the command decoder; there may be many other states internal to the device.

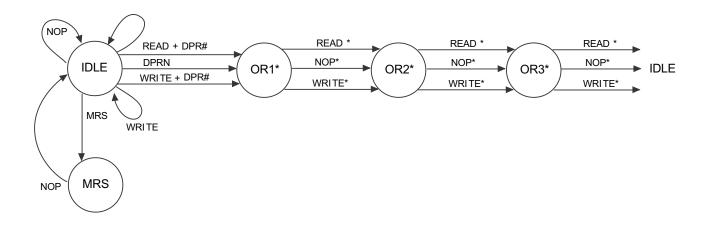

Because READ and WRITE commands only require a single cycle. When overlapped refresh is enabled, the modified command encoding is described in **Table 2-3** and the state diagram in **Figure 2-2**. In burst length 2 mode, overlapped refresh is accomplished using the DPR# pin, and is independent of other command encodings.

Table 2-2 Command Encoding (Overlapped Refresh Disabled)

| State | Command         | CS# | WE# | REF# | LBK# | RST# | Length (cycles) | Description              |

|-------|-----------------|-----|-----|------|------|------|-----------------|--------------------------|

| IDLE  | NOP             | 1   | -   | -    | 1    | 1    | 1               | No operation             |

|       | READ            | 0   | 1   | 1    | 1    | 1    | 1               | Read                     |

|       | WRITE           | 0   | 0   | 1    | 1    | 1    | 1               | Write                    |

|       | AUTO<br>REFRESH | 0   | 1   | 0    | 1    | 1    | 1               | Auto refresh             |

|       | MRS             | 0   | 0   | 0    | 1    | 1    | 2               | Mode register set        |

| MRS   | NOP             | 1   | -   | -    | 1    | 1    | -               | No operation             |

|       | LOOPBACK        | -   | -   | -    | 0    | 1    | -               | Address/control loopback |

|       | RESET           | -   | -   | -    | -    | 0    | -               | Reset                    |

Figure 2-1 Command Decode State Diagram ( Overlapped Refresh Disabled )

Table 2-3 Command Encoding (Overlapped Refresh Enabled)

| State | Command               | CS# | WE# | REF# | DPR#   | LBK# | RST# | Length (cycles) | Description                  |

|-------|-----------------------|-----|-----|------|--------|------|------|-----------------|------------------------------|

| IDLE  | NOP                   | 1   | 1   | -    | 1      | 1    | 1    | 1               | No operation                 |

|       | READ                  | 0   | 1   | 1    | 1      | 1    | 1    | 1               | Read                         |

|       | WRITE                 | 0   | 0   | 1    | 1      | 1    | 1    | 1               | Write                        |

|       | OVERLAPPED<br>REFRESH | 1   | -   | -    | 0      | 1    | 1    | 1               | Overlapped refresh           |

|       | READ + 0 1 REFRESH    |     | 1   | 1    | 0      | 1 1  |      | 1               | Read and overlapped refresh  |

|       | WRITE +<br>REFRESH    | 0   | 0   | 1    | 0      | 1    | 1    | 1               | Write and overlapped refresh |

|       | MRS                   | 0   | 0   | 0    | 1      | 1    | 1    | 2               | Mode register set            |

| OR1,  | NOP Note              | 1   | -   | -    | _ Note | 1    | 1    | -               | No operation                 |

| OR2,  | READ Note             | 0   | 1   | 1    | _ Note | 1    | 1    | 1               | Read (overlapped)            |

| OR3   | WRITE Note            | 0   | 0   | 1    | _ Note | 1    | 1    | 1               | Write (overlapped)           |

| MRS   | NOP                   | 1   | -   | -    | 1      | 1    | 1    | -               | No operation                 |

|       | LOOPBACK              | -   | 1   | -    | -      | 0    | 1    | -               | Address/control loopback     |

|       | RESET                 | -   | -   | -    | -      | -    | 0    | -               | Reset                        |

**Note** These indicate that the value of the DPR# pin is ignored for the purpose of command decoding (the pin is used for conveying bank number during this cycle).

Figure 2-2 Command Decode State Diagram (Overlapped Refresh Enabled)

#### 2.5 Data mask

The DM pin is used during write cycles to indicate that the corresponding data are to be masked off from writing to the memory. The value of the DM pin is sampled on both edges of DK0/DK0#, and corresponds to the data sampled on that same edge of either DK0/DK0# or DK1/DK1#.

When the DM pin has a logic 0 value, the data will be written to the memory. When the DM pin has a logic 1 value, the data will be ignored and no update to the corresponding memory data will be made.

The value of the DM pin is ignored in all other circumstances. Thus, driving a constant logic 0 to the DM pin can be used in systems where all data cycles in a burst result in writes to the memory.

When the Auto-DM Function (ADM) bit is set via an MRS command, the value of the DM pin is ignored and the device will behave as if it were a logic 0 on only the clock edge specified by the value of the DMP field.

#### 2.6 Data inversion

In order to reduce simultaneous switch noise, I/O current and average I/O power, the Low Latency DRAM-III provides the ability to invert all data pins. Because the nominal design for Low Latency DRAM-III I/O signals is high-side termination to V<sub>DD</sub>Q, signals driven to a logic high state will consume less power than those in a logic low state.

The DINVm-DINV0 pins indicate whether corresponding DQn-DQ0 pins, in groups of nine, represent the true logic value or an inverted logic value. With the ability to invert DQn-DQ0 pins in groups of nine, each group is guaranteed to be driving no more than five pins low on any given cycle. As a result, no more than five pins in each group can switch in the same direction during each bit time, reducing simultaneous switching noise effects.

When data inversion is enabled (DI=1) and a DINV pin is a logic 1, the corresponding DQ pins have been inverted. When data inversion is disabled (DI=0) then the Atris device will ignore the value of the DINV pins for write data and will drive DINV pins to logic 1 for read data; however, in such a case, the DQ pins are not inverted, regardless of the values of the DINV pins.

#### 2.7 Data bus turn-around

Because the DQn-DQ0 and DINVm-DINV0 pins are bidirectional, care must be taken to ensure that the Low Latency DRAM-III and the system chip connected to it do not drive these pins simultaneously. In order to guarantee this, a rapid DQ and DINV turn-off time is required. The actual bus turn-around time is dependent on many system parameters, including BL, RL, WL, pre-amble, post-amble, controller I/O timing, DRAM I/O timing, PCB delays; and the system must ensure that neither the Low Latency DRAM-III, nor the system chip is driving the bus during that time. This is accomplished by inserting a sufficient number of NOP commands between each READ-to-WRITE command transition and between each WRITE-to-READ transition. Additional NOP commands may be required to allow settling of the bus in order to insure no adverse effect on I/O timing.

Note that a REFRESH command can be used in place of a NOP command to effect the insertion of an idle cycle on the data bus.

# 2.8 Command cycles

A command to the Low Latency DRAM-III is initiated by driving the CS# pin low at the rising edge of CK and simultaneously driving the WE#, REF#, and A0-A13 to the appropriate state corresponding to the command.

READ and WRITE commands require only a single cycle. The NOP and AUTO REFRESH commands are each a single cycle in length. The OVERLAPPED REFRESH command is four cycles in length.

#### 2.9 Write data cycles

DQ0-DQn, DINV0-DINVm, and DM associated with a WRITE command are received by the Low Latency DRAM-III in a DDR burst, starting on a rising edge of DK that is offset WL clock cycles from rising edge of the CK signal corresponding

to the first cycle that the WRITE command was initiated. This delay of WL cycles is intended to ensure that the write data are not driven at the same time that data from a previous READ command are being driven from the Low Latency DRAM-III.

#### 2.10 Read data cycles

DQ0-DQn and DINV0-DINVm associated with a READ command are driven by the Low Latency DRAM-III in a DDR burst by the Low Latency DRAM-III RL clock cycles from the rising edge of the CK signal corresponding to the first cycle that the READ command was initiated. This delay of RL cycles is equal to the delay required for the internal logic and memory within the Low Latency DRAM-III to read data and make it available on the bus.

#### 2.11 READ and WRITE command protocol

Figure 2-3 through Figure 2-4 show the READ and WRITE command sequences.

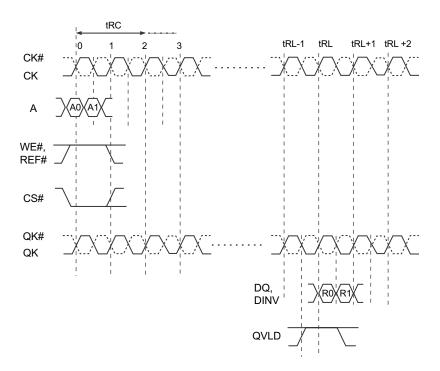

Figure 2-3 READ Command Sequence

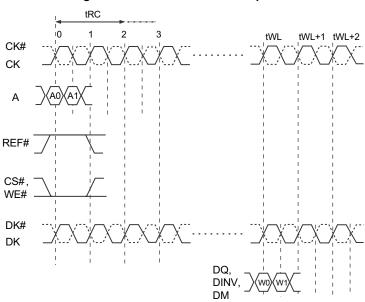

Figure 2-4 WRITE Command Sequence

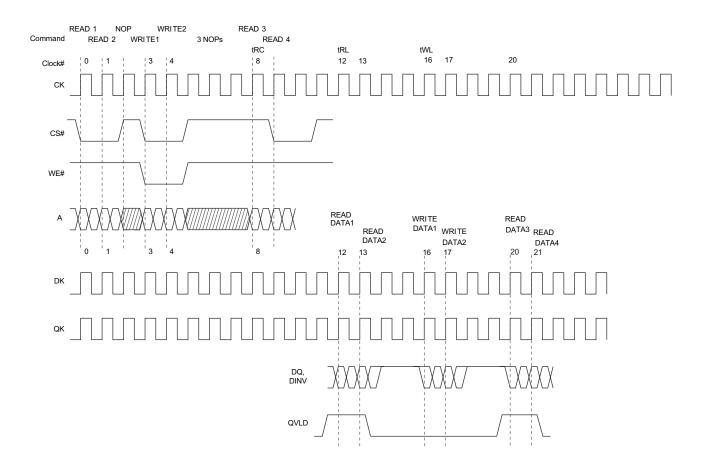

**Figure 2-5** shows an example of a sequence of 2 READ, 2 WRITE, and 2 READ commands, with the following configuration:

Burst length 2

Speed Config 3: trc=8, trL=12, twL=13

Data inversion is enabled

Some observations of this sequence are:

A NOP is inserted between READ2 and WRITE1 to allow for read-to-write bus turn-around

3 NOPs are inserted between WRITE2 and READ3 to allow for write-to-read bus turn-around Because tRc is 8, READ3 may access the same bank as READ1; however, none of READ2, WRITE1, or WRITE2 may access the same bank as READ1

Figure 2-5 READ/WRITE/READ Command Sequence (Speed Config 3, trc=8, trl=12, twl=13, DI=1)

#### 2.12 Automatic Refresh

Refresh cycles of the internal memory are initiated via the AUTO REFRESH command. Each refresh command causes a single refresh cycle to occur on the bank specified in the command.

The minimum data retention time is 2 ms over the temperature range specified in **1. Electrical Specifications**, and there are 16384 words in each bank. Therefore, each bank must receive 16384 refresh commands every 2 ms in order to ensure proper data retention.

This means that a refresh command must be received at an average rate of one every 13.3 ns. At a frequency of 600 MHz, this represents 8.2% of the usable bandwidth to the Low Latency DRAM-III.

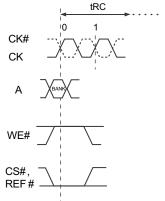

The refresh command waveforms are shown in Figure 2-6.

Figure 2-6 Automatic Refresh Command Sequence

#### 2.13 Overlapped Refresh pin (DPR#)

In burst length 2 mode, overlapped refresh is accomplished using the DPR# pin, instead of the REF# pin. This extra pin is required, in order to allow READ and WRITE commands to completely consume the standard command bus (pins CS#, WE#, and REF#).

The DPR# pin uses the same protocol as the REF# pin does for burst length 4 mode.

The DPR# pin can only be used in burst length 2 mode and when the MRS register specifies overlapped refresh mode. In all other cases, the DPR# pin must be connected to VDDQ.

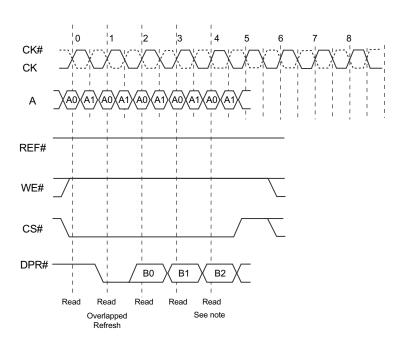

An example of Overlapped Refresh overlapped with five READ commands can be seen in Figure 2-7.

Figure 2-7 Overlapped Refresh with READ Commands

$\textbf{Note} \ \ \text{tRc for overlapped refresh begins 3 cycles after the start of the command}.$

# 2.14 Clam-shell support

In order to support clam-shell mounting on the board, the pin-out of the Low Latency DRAM-III is designed so that most pins that will be interchanged via mirroring are functionally interchangeable. A few pins require their function to be swapped, however. The MF pin causes the pin assignment to be modified to effect those pin swaps. In order to support proper signal integrity, package trace lengths for mirrored pins are matched to within +/- 0.1mm. **Table2-4** shows the pins that are mirrored by the MF pin.

Due to the mirroring of A5 and A6, all devices are required to include an I/O cell on A6 in order to support the mirror function. For lower capacity devices, the A6 pin would remain DNU, VDDQ from a memory controller standpoint, so the system need not actively drive this functionally unused pin.

Similarly, for devices that require A12, pin A13 is also required to include an I/O cell.

A3 and A4 are mirrored to support future devices that may use A3 as an additional bank select bit.

All of A0 through A5 must be mirrored in order for MRS commands to be interpreted correctly.

Table 2-4 Pins Affected by MF Pin

| Pin | MF=0 | MF=1 |

|-----|------|------|

| N4  | A0   | A1   |

| N10 | A1   | A0   |

| L4  | A4   | A3   |

| L10 | A3   | A4   |

| M5  | A2   | REF# |

| M9  | REF# | A2   |

| L2  | CS#  | WE#  |

| L12 | WE#  | CS#  |

| H10 | A5   | A6   |

| H4  | A6   | A5   |

| F4  | A12  | A13  |

| F10 | A13  | A12  |

| M11 | A9   | DPR# |

| M3  | DPR# | A9   |

| H2  | RST# | DM   |

| H12 | DM   | RST# |

#### 3. Initialization

Prior to functional use, the Low Latency DRAM-III must be initialized and configured. The steps described in this chapter will ensure that the internal logic of the Low Latency DRAM-III has been properly reset and that the functional timing parameters of the chip have been configured.

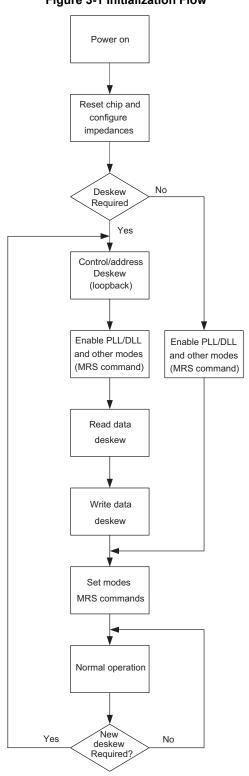

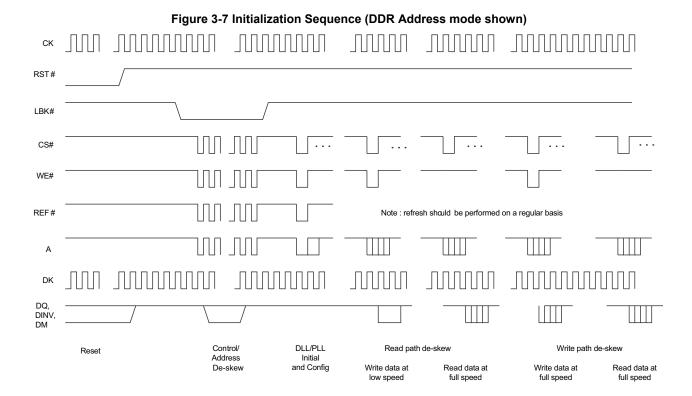

**Figure 3-1** shows the overall initialization sequence required by the Low Latency DRAM-III. An example of an initialization sequence, showing each of the different phases, is shown in **Figure 3-7**.

Figure 3-1 Initialization Flow

#### 3.1 Power-on

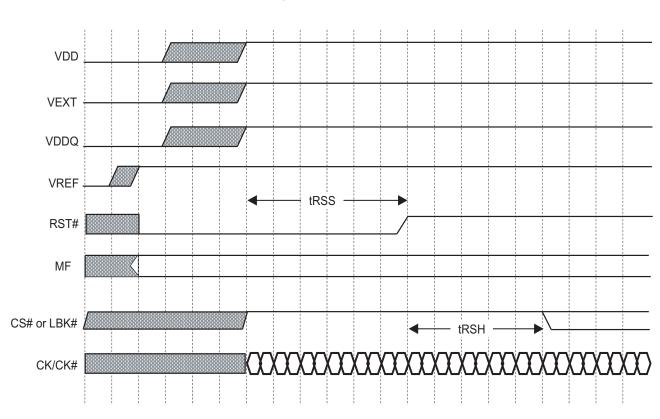

- 1 There are no restrictions on the sequence of applying the V<sub>DD</sub>, V<sub>EXT</sub>, and V<sub>DD</sub>Q power supplies as long as maintaining RST# = Low and fix MF input state before and during any of the power supplies ramp up.

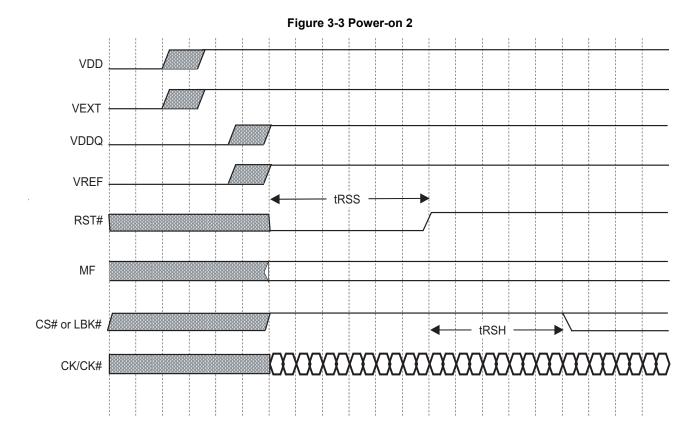

- 2 In case when RST# can not be asserted Low and fixed MF input state before and during any of the power supplies ramp up, make sure to ramp up following manners.

- (1) Ramp up VDD and VEXT(no ramp up sequence restriction on VDD and VEXT)

- (2) Ramp up VDDQ and VREF following to the VDD and VEXT (no ramp up sequence restriction on VDDQ and VREF)

- (3) Make sure to assert RST# for tRSS specified period before initiating any operations

Figure 3-2 Power-on 1

#### 3.2 Reset

Before the Low Latency DRAM-III can be configured, it must be properly reset, to ensure that the Low Latency DRAM-III is in a known and functional state, regardless of any power on anomalies and power supply ramp rates. Reset requires the assertion of the RST# pin for at least 200  $\mu$ s, during which time the device logic is reset to a known state, and the I/O impedances are programmed as described in **3.3 Initial impedance settings**.

The contents of memory are not guaranteed to be retained when the chip is reset.

# 3.3 Initial impedance settings

When the RST# pin is deasserted, the value of specific DQ pins is used to configure the input termination and output impedance as shown in **Table 3-1**. The meaning of the bits is the same as the corresponding bits described in **3.5 Configuration**, although their positions in the DQ pins are unrelated to their positions in the corresponding MRS registers.

While RST# is asserted, the impedance values are continuously updated based on the values of the DQ pins and on the sampled value of the ZQ impedance programming pin. On the rising edge of RST#, the values will be latched into the device and stored in the appropriate positions in the MRS registers. **Figure 3-4** shows the waveforms associated with this function.

Note that the DINV pins are ignored during reset time and the values of the DQ pins are considered to never be inverted during this time.

D12 Pins U12 T11 U4 R12 T5 P13 R4 P11 P5 B12 C11 B4 C5 E13 D4 E11 E5 DQ (x18) 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 0 DQ (x36) 18 7 4 26 25 24 23 22 21 20 19 8 6 5 3 2 0 Reset Reg 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 0  $\mathsf{MSB} \to \mathsf{LSB}$ Cell ID KD KU CD CU DD DU ODT QD QU IM

**Table 3-1 Reset Impedance Control Assignments**

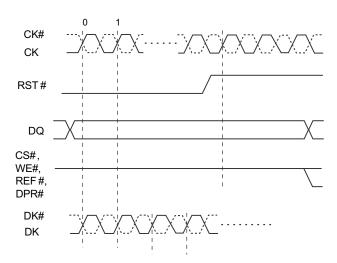

Figure 3-4 Reset Sequence

#### 3.4 Per-bit de-skew training sequence

The Low Latency DRAM-III device provides support that allows a memory controller to de-skew signals for high-speed operation. If per-bit de-skew is desired, the memory controller must provide the actual de-skew functionality. Per-pin de-skew is normally performed after deassertion of the RST# pin, but may be performed at any time, without affecting the contents of the memory within the device. Furthermore, resetting the device does not necessarily affect the skew characteristics of the device pins; therefore, a reset of the device does not necessarily require repeating the de-skew training sequence that was previously performed.

Per-pin de-skew training is anticipated to be implemented in three steps:

De-skew of the control, address, and clock pins: A0-A13, CS#, WE#, REF#, DPR#, and DK0-DK1 with respect to CK De-skew of the read path: DQ0-DQn, DINV0- DINVm and QVLD with respect to QK0-QK1

De-skew of the write path: DQ0-DQn, DINV0- DINVm and DM with respect to DK0-DK1

The first phase, de-skew of the control and related pins, requires support from the device by driving the LBK# pin to a logic 0. When the LBK# pin is a logic 0, the DK0-DK1, CS#, WE#, REF#, DPR#, and A0-A13 pins are looped back to the various DQ and DINV pins. All pins are sampled by the CK clock, including DK0-DK1. The specific mapping of input pins to output pins during loopback mode is shown in **Table 3-2**.

x36 part x18 part Input Output Input Output **Output Pin Input Pin** MF=0 MF=1 MF=0 MF=1 G5 C5 Α8 Α8 DQ4 DQ4 Α8 Α8 H4 E5 Α6 A5 DQ0 Α6 A5 DQ0 DK0, DK0# DK0, DK0# DK0, DK0# DK0, DK0# J1, K1 E11 DQ1 DQ1 L4 P5 A4 A3 DQ18 A4 A3 DQ9 L2 R4 CS# WE# DQ20 CS# WE# DQ11 REF# REF# М5 T5 A2 DQ22 A2 **DQ13** N4 U4 A0 Α1 DQ24 A0 DQ15 A1 H10 E13 Α5 A6 DQ3 Α5 A6 DQ3 DNU, Vss E3 DK1, DK1# DK1, DK1# DNU, Vss DNU, Vss J11, K11 **DQ14** L10 P11 A3 A4 **DQ19** A3 A4 DQ10 CS# CS# L12 P13 WE# DQ21 WE# DQ12 M9 T11 REF# A2 DQ25 REF# A2 DQ16

Table 3-2 Control/Address Pin Mapping When LBK#=0

|           |            |      | x36 part |        | x18 part |        |       |  |  |

|-----------|------------|------|----------|--------|----------|--------|-------|--|--|

|           |            | Inj  | out      | Output | Inj      | Output |       |  |  |

| Input Pin | Output Pin | MF=0 | MF=1     |        | MF=0     | MF=1   |       |  |  |

| N10       | U12        | A1   | A0       | DQ26   | A1       | A0     | DQ17  |  |  |

| F4        | B4         | A12  | A13      | DQ6    | A12      | A13    | DQ6   |  |  |

| G3        | D4         | A10  | A10      | DQ2    | A10      | A10    | DQ2   |  |  |

| M3        | N2         | DPR# | A9       | DINV2  | DPR#     | A9     | DINV1 |  |  |

| F10       | B12        | A13  | A12      | DQ8    | A13      | A12    | DQ8   |  |  |

| G9        | C11        | A7   | A7       | DQ7    | A7       | A7     | DQ7   |  |  |

| G11       | D12        | A11  | A11      | DQ5    | A11      | A11    | DQ5   |  |  |

| M11       | R12        | A9   | DPR#     | DQ23   | A9       | DPR#   | DQ14  |  |  |

#### Notes:

DK0, DK0# and DK1, DK1# have differential receivers, so the output of the receiver is used as signal being looped back.

For each pin that is looped back, the input pin is sampled on both the rising edge and falling edges of the corresponding input clock. The value output on the rising edge of the corresponding output clock will be the value that was sampled on the rising edge of the input clock. The value output on the falling edge of the corresponding output clock will be the inverted value that was sampled on the falling edge of the input clock. Data inversion is not used during loopback mode and the value of the corresponding MRS bits are ignored.

The delay from input pins to DQ/DINV output pins, when loopback mode is enabled, is 5 cycles of CK.

In burst length 4 mode, while LBK# pin is a logic 0, the DQ/DINV output pins corresponding to unused input pins (see Table 3-2) will still meet the AC timing specification (See Interface AC Parameters), but they may have arbitrary logic state and may or may not have a constant logic value.

While the LBK# pin is a logic 0, the device will ignore any apparent commands being presented on the CS#, WE#, REF#, and DPR# pins and will perform self refresh operations to prevent loss of data during extended periods of de-skew training. In order to ensure that commands are not inadvertently received during entry and exit from de-skew training, no commands may be sent to the device for a period of 16 cycles of CK prior to the LBK# pin being driven to 0, nor for 16 cycles after the LBK# pin is returned to a logic 1. Also, no valid input signals for looped back must be inserted for 16 cycles after LBK# pin being driven to 0 when device just enters into loopback mode.

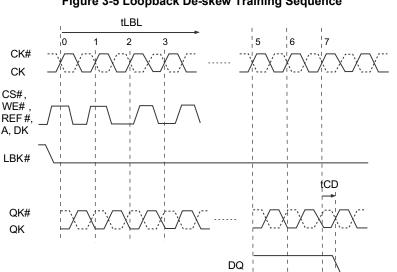

While LBK# is asserted, the on-chip PLL is ignored; therefore the phase of the QK output clock will be undefined with respect to the CK input clock. However, the QK to DQ timing will still meet its specifications. Note that the PLL will remain enabled or disabled, per its state prior to LBK# being asserted, and after LBK# is deasserted. An example of a loopback sequence is show in Figure 3-5.

Figure 3-5 Loopback De-skew Training Sequence

Following de-skew of the control, address, and DK pins, the memory controller drives the LBK# pin to a logic 1, then will likely perform read data and write data de-skew training.

Prior to beginning read path de-skew, the memory controller should issue an MRS command to the Low Latency DRAM-III device to enable the PLL. After the PLL is enabled, the timing of the QK, DQ outputs, and QVLD will be unspecified for a period of tpll. The MRS command is described in **3.5 Configuration**. While the PLL is stabilizing, refresh commands must continue to be issued to the device in order to ensure proper retention of data.

Read data de-skew requires that a training pattern be written to Low Latency DRAM-III memory. Complex data patterns can be written to the Low Latency DRAM-III memory using the non-de-skewed DQ signals and the auto-DM functions. Auto-DM functions are enabled through MRS, as described in **3.5 Configuration**.

Read data de-skew can be performed by using the de-skewed control and related pins, including the DK pin, and non-switching DQ and DINV pins to write 36-bit values to memory locations in the device. Because the data are held at constant values, the auto-DM modes of the device are used to specify which 36-bit beat (or 18-bit beat for x18 devices) of data on the bus is to be written to the memory. Once written to the memory, these data can then be read out using standard BL2, READ commands to effect any desired pattern on the DQ bus. This permits the system to de-skew the DQ, DINV, and QVLD signals with respect to the QK clocks.

Write data de-skew can be performed by issuing WRITE commands to the device, then using the de-skewed read bus to determine whether or not data were correctly received by the device. This permits the system to de-skew the DQ, DINV, and DM signals with respect to the DK clocks.

#### 3.5 Configuration

The MRS command is used to configure the Low Latency DRAM-III. Configuration is used to specify the following parameters:

Address Mode

The Address Mode of Low Latency DRAM-III devices from some vendors may be electrically configurable. The default Address Mode may vary from vendor-to-vendor as well. Therefore, systems must configure the desired Address Mode prior to issuing READ or WRITE commands

Mode select for READ latency, WRITE latency, and tRC

The version of the Low Latency DRAM-III covered by this specification only supports modes 0 through 5

Select driver pull-up impedance of 1/4 or 1/6 of reference resistor (default 1/4)

Select driver pull-down impedance of 1/4 or 1/6 reference resistor (default 1/6)

Select DQ, DINV, DM, DK, DKN, CK, CK#, RST# terminator pull-up impedance of OFF, 1x, 1/2, or 1/4 of reference resistor (default 1/4)

Select DQ, DINV, DM, DK, DKN, CK, CK#, RST# terminator pull-down impedance of OFF, 1x, 1/2, or 1/4 of reference resistor (default OFF)

Select CS#, WE#, REF#, A, LBK#, terminator pull-up impedance of OFF, 1x, 1/2, or 1/4 of reference resistor (default 1/4) Select CS#, WE#, REF#, A, LBK#, terminator pull-down impedance of OFF, 1x, 1/2, or 1/4 of reference resistor (default OFF)

Enable/freeze dynamic PVT compensation (default enabled)

Enable/disable PLL (default disabled)

Enable/disable read/write data inversion (default disabled)

Refresh mode (default AUTO REFRESH)

Select auto-DM modes (default disabled)

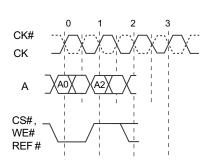

The MRS command allows the configuration of one of eight different registers to be configured using SDR timing on the address pins. The MRS command waveforms are shown in **Figure 3-5** and the values of the MRS registers are described in **Table 3-3** through **Table 3-6**. Because an MRS command may change values that significantly affect the behavior of the device, no other commands should be issued to the device for a period of tmrD clock cycles following the MRS command.

MRS commands use the address pins specified in **Table 3-3**. The actual pins used depend on the value of the mirror function (MF) pin.

**Table 3-3 MRS Configuration Register Bit Assignments**

|                          |     |               |     | Beat 0 |    |         |     |     |     |     | Beat 2 |    |     |     |

|--------------------------|-----|---------------|-----|--------|----|---------|-----|-----|-----|-----|--------|----|-----|-----|