# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# MOS INTEGRATED CIRCUIT $\mu$ PD161830

## 240-OUTPUT TFT-LCD SOURCE DRIVER (COMPATIBLE WITH 64-GRAY SCALES)

## DESCRIPTION

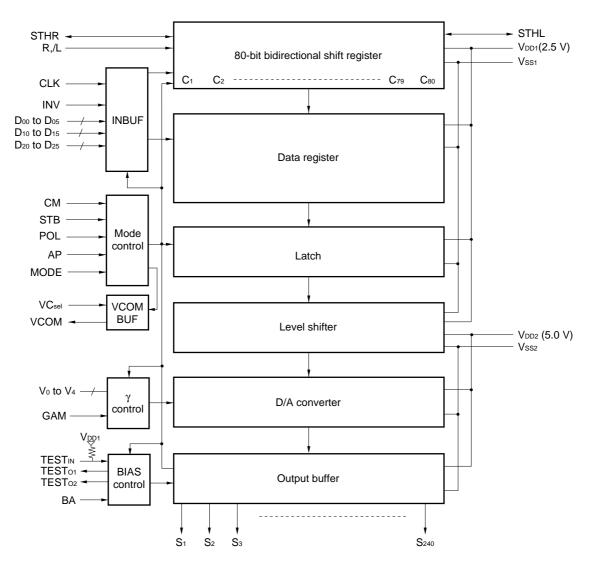

The  $\mu$  PD161830 is a source driver for TFT-LCDs supporting 64 gray-scale display and can operate with a supply voltage of 2.5 V for the logic block and 5.0 V for the driver block. Data input as 6-bit x 3-dot digital data is output as 64  $\gamma$ -corrected values using an internal D/A converter and 5 external power modules, thus achieving a 260,000-color (full-color) display.

## **FEATURES**

- CMOS level input

- 240 outputs

- Input of 6 bits (gray-scale data) by 3 dots

- Capable of outputting 64 values by means of 5 external power modules and a D/A converter

- Output dynamic range: Vss2 to VDD2

- High-speed data transfer: fcLK = 15 MHz MAX. (internal data transfer speed when operating at VDD1 = 2.5 V)

- Level inversion  $\gamma$ -correction power supply is possible

- Logic power supply voltage (VDD1): 2.2 to 3.6 V

- Driver power supply voltage (VDD2): 4.5 to 5.5 V

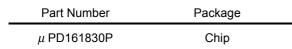

## **ORDERING INFORMATION**

**Remark** Purchasing the above chip entail the exchange of documents such as a separate memorandum or product quality, so please contact one of our sales representatives.

The information contained in this document is being issued in advance of the production cycle for the device. The parameters for the device may change before final production or NEC Corporation, at its own discretion, may withdraw the device prior to its production. Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

## 1. BLOCK DIAGRAM

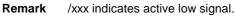

## 2. PIN CONFIGURATION (Pad Layout)

Chip size:  $15.84 \times 1.11 \text{ mm}^2$ Bump size (Input/VCOM/test/dummy):  $80 \times 86 \mu \text{m}^2$ Bump size (Output):  $29 \times 103 \mu \text{m}^2$ Alignment Mark ( $\mu$ m) X: 7716.45 Y: 347.04 X: -7716.45 Y: 347.04

#### Alignment mark shape (unit: $\mu$ m)

| No.      | Name     | X [μm]               | Υ [μm]  | No.      | Name         | X [μm]   | Υ [μm]  | No. | Name | X [μm]    | Y [µm]  |

|----------|----------|----------------------|---------|----------|--------------|----------|---------|-----|------|-----------|---------|

| 1        | S1       | 7170.000             | 396.480 | 61       | S61          | 3570.000 | 396.480 | 121 | S121 | -30.000   | 396.480 |

| 2        | S2       | 7110.000             | 396.480 | 62       | S62          | 3510.000 | 396.480 | 122 | S122 | -90.000   | 396.480 |

| 3        | S3       | 7050.000             | 396.480 | 63       | S63          | 3450.000 | 396.480 | 123 | S123 | -150.000  | 396.480 |

| 4        |          | 6990.000             | 396.480 | 64       | S64          | 3390.000 | 396.480 | 124 | S124 | -210.000  | 396.480 |

| 5        | S5       | 6930.000             | 396.480 | 65       | S65          | 3330.000 | 396.480 | 125 | S125 | -270.000  | 396.480 |

| 6        |          | 6870.000             | 396.480 | 66       | S66          | 3270.000 | 396,480 | 126 |      | -330.000  | 396.480 |

| 7        |          | 6810.000             | 396.480 | 67       | S67          | 3210.000 | 396.480 | 127 | S127 | -390.000  | 396.480 |

| . 8      | -        | 6750.000             | 396.480 | 68       |              | 3150.000 | 396.480 | 128 | -    | -450.000  | 396.480 |

| 9        |          | 6690.000             | 396.480 | 69       | S69          | 3090.000 | 396.480 | 120 |      | -510.000  | 396.480 |

| 10       |          | 6630.000             | 396.480 | 70       |              | 3030.000 | 396.480 | 123 |      | -570.000  | 396.480 |

|          | S10      | 6570.000             | 396.480 | 70       |              | 2970.000 | 396.480 |     | S130 | -630.000  | 396.480 |

| 12       |          |                      | 396.480 | 72       | S71<br>S72   | 2910.000 | 396.480 | 131 |      | -690.000  | 396.480 |

|          | -        | 6510.000<br>6450.000 | 396.480 |          | -            | 2910.000 | 396.480 | 132 |      | -750.000  |         |

| 13<br>14 |          |                      |         | 73<br>74 |              |          |         | 133 |      |           | 396.480 |

|          | ÷.       | 6390.000             | 396.480 |          | <b>Q</b>     | 2790.000 | 396.480 |     |      | -810.000  | 396.480 |

|          | S15      | 6330.000             | 396.480 | 75       |              | 2730.000 | 396.480 | 135 |      | -870.000  | 396.480 |

| 16       |          | 6270.000             | 396.480 | 76       |              | 2670.000 | 396.480 | 136 |      | -930.000  | 396.480 |

| 17       | <b>Q</b> | 6210.000             | 396.480 | 77       | S77          | 2610.000 | 396.480 | 137 | •••• | -990.000  | 396.480 |

|          | S18      | 6150.000             | 396.480 | 78       |              | 2550.000 | 396.480 | 138 |      | -1050.000 | 396.480 |

| 19       |          | 6090.000             | 396.480 | 79       |              | 2490.000 | 396.480 | 139 |      | -1110.000 | 396.48  |

| 20       | S20      | 6030.000             | 396.480 |          | S80          | 2430.000 | 396.480 | 140 |      | -1170.000 | 396.480 |

| 21       | S21      | 5970.000             | 396.480 | 81       | S81          | 2370.000 | 396.480 | 141 | S141 | -1230.000 | 396.480 |

| 22       | S22      | 5910.000             | 396.480 | 82       | S82          | 2310.000 | 396.480 | 142 | S142 | -1290.000 | 396.480 |

| 23       | S23      | 5850.000             | 396.480 | 83       | S83          | 2250.000 | 396.480 | 143 | S143 | -1350.000 | 396.480 |

| 24       | S24      | 5790.000             | 396.480 | 84       | S84          | 2190.000 | 396.480 | 144 | S144 | -1410.000 | 396.48  |

| 25       | S25      | 5730.000             | 396.480 | 85       | S85          | 2130.000 | 396.480 | 145 | S145 | -1470.000 | 396.48  |

| 26       | S26      | 5670.000             | 396.480 | 86       |              | 2070.000 | 396.480 | 146 |      | -1530.000 | 396.480 |

| 27       |          | 5610.000             | 396.480 | 87       | S87          | 2010.000 | 396.480 | 147 | S147 | -1590.000 | 396.480 |

| 28       | -        | 5550.000             | 396.480 | 88       | S88          | 1950.000 | 396.480 | 148 | -    | -1650.000 | 396.480 |

| 29       |          | 5490.000             | 396.480 | 89       |              | 1890.000 | 396.480 | 149 |      | -1710.000 | 396.48  |

| 30       |          | 5430.000             | 396.480 | 90       |              | 1830.000 | 396.480 | -   | S150 | -1770.000 | 396.480 |

|          | S31      | 5370.000             | 396.480 | 91       |              | 1770.000 | 396.480 | 150 |      | -1830.000 | 396.480 |

| 32       |          | 5310.000             | 396.480 | 92       | S92          | 1710.000 | 396.480 | 151 |      | -1890.000 | 396.480 |

|          |          |                      |         |          |              |          |         |     |      |           |         |

| 33       |          | 5250.000             | 396.480 | 93       |              | 1650.000 | 396.480 | 153 |      | -1950.000 | 396.48  |

| 34       | 2.2      | 5190.000             | 396.480 | 94       |              | 1590.000 | 396.480 | 154 |      | -2010.000 | 396.48  |

| 35       |          | 5130.000             | 396.480 | 95       | S95          | 1530.000 | 396.480 | 155 |      | -2070.000 | 396.48  |

| 36       |          | 5070.000             | 396.480 | 96       | S96          | 1470.000 | 396.480 | 156 |      | -2130.000 | 396.48  |

| 37       | 2.2      | 5010.000             | 396.480 | 97       |              | 1410.000 | 396.480 | 157 |      | -2190.000 | 396.48  |

| 38       |          | 4950.000             | 396.480 | 98       |              | 1350.000 | 396.480 | 158 |      | -2250.000 | 396.48  |

| 39       |          | 4890.000             | 396.480 | 99       |              | 1290.000 | 396.480 | 159 |      | -2310.000 | 396.48  |

| 40       |          | 4830.000             | 396.480 | 100      |              | 1230.000 | 396.480 | 160 |      | -2370.000 | 396.48  |

| 41       |          | 4770.000             | 396.480 | 101      |              | 1170.000 | 396.480 | 161 |      | -2430.000 | 396.480 |

| 42       | S42      | 4710.000             | 396.480 | 102      | S102         | 1110.000 | 396.480 | 162 | S162 | -2490.000 | 396.480 |

| 43       | S43      | 4650.000             | 396.480 | 103      | S103         | 1050.000 | 396.480 | 163 | S163 | -2550.000 | 396.48  |

| 44       | S44      | 4590.000             | 396.480 | 104      | S104         | 990.000  | 396.480 | 164 | S164 | -2610.000 | 396.48  |

| 45       | S45      | 4530.000             | 396.480 | 105      | S105         | 930.000  | 396.480 | 165 | S165 | -2670.000 | 396.48  |

| 46       | S46      | 4470.000             | 396.480 | 106      | S106         | 870.000  | 396.480 | 166 | S166 | -2730.000 | 396.48  |

| 47       | S47      | 4410.000             | 396.480 | 107      | S107         | 810.000  | 396.480 | 167 | S167 | -2790.000 | 396.48  |

| 48       | S48      | 4350.000             | 396.480 | 108      | S108         | 750.000  | 396.480 | 168 | S168 | -2850.000 | 396.48  |

| 49       | S49      | 4290.000             | 396.480 | 109      |              | 690.000  | 396.480 | 169 |      | -2910.000 | 396.48  |

| 50       |          | 4230.000             | 396.480 | 110      |              | 630.000  | 396.480 | 170 |      | -2970.000 | 396.48  |

|          | S51      | 4170.000             | 396.480 |          | S111         | 570.000  | 396.480 | 170 |      | -3030.000 | 396.48  |

| 52       |          | 4110.000             | 396.480 | 112      | -            | 510.000  | 396.480 | 172 | S172 | -3090.000 | 396.48  |

| 53       |          | 4050.000             | 396.480 | 112      |              | 450.000  | 396.480 | 172 |      | -3150.000 | 396.48  |

| 53<br>54 |          | 3990.000             | 396.480 | -        | S113<br>S114 | 390.000  | 396.480 | 173 |      | -3150.000 | 396.48  |

| -        |          |                      |         |          |              |          |         |     | -    |           |         |

| 55       |          | 3930.000             | 396.480 | 115      |              | 330.000  | 396.480 | 175 | S175 | -3270.000 | 396.48  |

| 56       |          | 3870.000             | 396.480 | 116      |              | 270.000  | 396.480 | 176 |      | -3330.000 | 396.48  |

| 57       |          | 3810.000             | 396.480 |          | S117         | 210.000  | 396.480 | 177 | S177 | -3390.000 | 396.48  |

| 58       |          | 3750.000             | 396.480 |          | S118         | 150.000  | 396.480 | 178 |      | -3450.000 | 396.48  |

| 59       |          | 3690.000             | 396.480 |          | S119         | 90.000   | 396.480 | 179 |      | -3510.000 | 396.48  |

| 60       | S60      | 3630.000             | 396.480 | 120      | S120         | 30.000   | 396.480 | 180 | S180 | -3570.000 | 396.480 |

Table 2–1. Pad Layout (1/2)

| No.        | Name         | X [μm]                 | Υ [μm]             | No.        | Name    | X [μm]                 |

|------------|--------------|------------------------|--------------------|------------|---------|------------------------|

| 181        | S181         | -3630.000              | 396.480            | 241        | DUMMY1  | -7311.420              |

| 182        | S182         | -3690.000              | 396.480            | 242        | DUMMY2  | -7772.010              |

| 183        | S183         | -3750.000              | 396.480            | 243        | DUMMY3  | -7772.010              |

| 184        | S184         | -3810.000              | 396.480            | 244        | DUMMY4  | -7772.010              |

| 185        | S185         | -3870.000              | 396.480            | 245        | DUMMY5  | -7772.010              |

|            | S186         | -3930.000              | 396.480            | 246        | DUMMY6  | -7772.010              |

| 187        | S187         | -3990.000              | 396.480            | 247        | DUMMY7  | -7654.530              |

|            | S188         | -4050.000              | 396.480            | 248        |         | -7479.510              |

|            | S189         | -4110.000              | 396.480            | 249        | 0=      | -7229.490              |

|            | S190         | -4170.000              | 396.480            |            | DUMMY8  | -7054.440              |

|            | S191         | -4230.000              | 396.480            | 251        |         | -6793.050              |

| -          | S192         | -4290.000              | 396.480            | 252        |         | -6693.090              |

|            | S193         | -4350.000              | 396.480            | 253        |         | -6593.130              |

|            | S194         | -4410.000              | 396.480            | -          | VDD1    | -6331.710              |

|            | S195         | -4470.000              | 396.480            | 255        |         | -6231.750              |

|            | S196         | -4530.000              | 396.480            | 256        |         | -6131.790              |

| -          | S197         | -4590.000              | 396.480            | 257        |         | -5878.440              |

|            | S198         | -4650.000              | 396.480            | 258        |         | -5778.480              |

|            | S199         | -4710.000              | 396.480            | 259        |         | -5678.520              |

| 200<br>201 | S200         | -4770.000              | 396.480            | 260<br>261 |         | -5428.500              |

|            | S201<br>S202 | -4830.000<br>-4890.000 | 396.480<br>396.480 | 261        |         | -5328.540<br>-5228.580 |

| -          | S202<br>S203 | -4890.000              | 396.480            | 262        |         | -4975.260              |

|            | S203         | -5010.000              | 396.480            |            | R,/L    | -4725.240              |

| -          | S204         | -5070.000              | 396.480            |            | MODE    | -4475.220              |

|            | S205         | -5130.000              | 396.480            | 265        |         | -4225.200              |

|            | S207         | -5190.000              | 396.480            |            | GAM     | -3975.180              |

|            | S208         | -5250.000              | 396.480            |            | CM      | -3725.160              |

|            | S209         | -5310.000              | 396.480            |            | POL     | -3475.140              |

|            | S210         | -5370.000              | 396.480            | 270        |         | -3225.120              |

|            | S211         | -5430.000              | 396.480            | 271        |         | -2975.100              |

| 212        | S212         | -5490.000              | 396.480            | 272        | D25     | -2725.080              |

| 213        | S213         | -5550.000              | 396.480            | 273        | D24     | -2475.060              |

| 214        | S214         | -5610.000              | 396.480            | 274        | D23     | -2225.040              |

| 215        | S215         | -5670.000              | 396.480            | 275        | D22     | -1975.020              |

| -          | S216         | -5730.000              | 396.480            |            | D21     | -1725.000              |

|            | S217         | -5790.000              | 396.480            |            | D20     | -1474.980              |

|            | S218         | -5850.000              | 396.480            |            | CLK     | -1224.960              |

|            | S219         | -5910.000              | 396.480            |            | DUMMY9  | -1049.910              |

|            | S220         | -5970.000              | 396.480            | 280        |         | -874.860               |

|            | S221         | -6030.000              | 396.480            | 281        |         | -774.900               |

|            | S222         | -6090.000              | 396.480            | 282        |         | -674.940               |

| -          | S223         | -6150.000              | 396.480            | 283        | -       | -424.920               |

|            | S224         | -6210.000              | 396.480            | 284        | -       | -324.960               |

|            | S225         | -6270.000              | 396.480            | 285<br>286 |         | -225.000               |

| -          | S226<br>S227 | -6330.000<br>-6390.000 | 396.480<br>396.480 | 280        |         | 25.080<br>125.040      |

|            | S227<br>S228 | -6450.000              | 396.480            | 288        |         | 225.000                |

|            | S220         | -6510.000              | 396.480            | 289        |         | 475.020                |

| -          | S230         | -6570.000              | 396.480            | 200        |         | 574.980                |

|            | S231         | -6630.000              | 396.480            | 291        |         | 674.940                |

|            | S232         | -6690.000              | 396.480            | 292        |         | 925.020                |

|            | S233         | -6750.000              | 396.480            | 293        | -       | 1024.980               |

|            | S234         | -6810.000              | 396.480            | 294        | -       | 1124.940               |

| -          | S235         | -6870.000              | 396.480            | 295        | DUMMY10 | 1299.990               |

|            | S236         | -6930.000              | 396.480            |            | INV     | 1475.010               |

| 237        | S237         | -6990.000              | 396.480            | 297        | D15     | 1725.030               |

| -          | S238         | -7050.000              | 396.480            | 298        | -       | 1975.050               |

| 239        | S239         | -7110.000              | 396.480            |            | D13     | 2225.070               |

| 240        | S240         | -7170.000              | 396.480            | 300        | D12     | 2475.090               |

|            |              |                        |                    |            |         |                        |

Table 2–1. Pad Layout (2/2)

Y [µ m] 407.010

164 880

64.860

-35.160

-135.180

-235.200

407.010

-407.010

-407.010 -407.010

-407.010 -407.010-407.010

-407.010

-407.010-407.010

-407.010

-407.010

-407.010

-407.010

-407.010

-407.010 -407.010

-407.010

-407.010

-407.010

-407.010

-407.010

-407.010 -407.010

-407.010 -407.010

-407.010

-407.010

-407.010 -407.010

-407.010

-407.010-407.010

-407.010

-407.010

-407.010

-407.010

-407.010

-407.010

-407.010 -407.010

-407.010 -407.010

-407.010

-407.010

-407.010

-407.010

-407.010

-407.010

-407.010

-407.010 -407.010

-407 010

-407.010

| No. | Name    | X [μ m]  | Υ [ <i>μ</i> m] |

|-----|---------|----------|-----------------|

| 301 | D11     | 2725.110 | -407.010        |

| 302 | D10     | 2975.130 | -407.010        |

| 303 | D05     | 3225.150 | -407.010        |

| 304 | D04     | 3475.170 | -407.010        |

| 305 | D03     | 3725.190 | -407.010        |

| 306 | D02     | 3975.210 | -407.010        |

| 307 | D01     | 4225.230 | -407.010        |

| 308 | D00     | 4475.250 | -407.010        |

| 309 | TESTO1  | 4725.270 | -407.010        |

| 310 | TESTO2  | 4975.290 | -407.010        |

| 311 | TESTIN  | 5225.310 | -407.010        |

| 312 | VDD1    | 5475.360 | -407.010        |

| 313 | VDD1    | 5575.320 | -407.010        |

| 314 | VDD1    | 5675.280 | -407.010        |

| 315 | VSS1    | 5853.630 | -407.010        |

| 316 | VSS1    | 5953.590 | -407.010        |

| 317 | VSS1    | 6053.550 | -407.010        |

| 318 | VSS2    | 6303.570 | -407.010        |

| 319 | VSS2    | 6403.530 | -407.010        |

| 320 | VSS2    | 6503.490 | -407.010        |

| 321 | VDD2    | 6843.180 | -407.010        |

| 322 | VDD2    | 6943.140 | -407.010        |

| 323 | VDD2    | 7043.100 | -407.010        |

| 324 | DUMMY11 | 7304.490 | -407.010        |

| 325 | STHR    | 7479.540 | -407.010        |

| 326 | DUMMY12 | 7654.560 | -407.010        |

| 327 | DUMMY13 | 7772.010 | -235.200        |

| 328 | DUMMY14 | 7772.010 | -135.180        |

| 329 | DUMMY15 | 7772.010 | -35.160         |

| 330 | DUMMY16 | 7772.010 | 64.860          |

| 331 | DUMMY17 | 7772.010 | 164.880         |

| 332 | DUMMY18 | 7311.420 | 407.010         |

## 3. PIN FUNCTIONS

|            | 1                    |            |             | (1/2)                                                                                                                                                                               |

|------------|----------------------|------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Symbol | Pin Name             | Pad No.    | I/O         | Description                                                                                                                                                                         |

| S1 to S240 | Driver output        | 1 to 240   | Output      | The D/A converted 64-gray-scale analog voltage is output.                                                                                                                           |

| Doo to Dos | Display data input   | 308 to 303 | Input       | The display data is input with a width of 18 bits, viz., the gray scale data (6 bits) by 3                                                                                          |

| D10 to D15 | -                    | 302 to 297 |             | dots (1 pixels).                                                                                                                                                                    |

| D20 to D25 |                      | 277 to 272 |             | Dx0: LSB, Dx5: MSB                                                                                                                                                                  |

| R,/L       | Shift direction      | 264        | Input       | These refer to the shift direction control input.                                                                                                                                   |

|            | control input        |            |             | The shift directions of the shift registers are as follows.                                                                                                                         |

|            |                      |            |             | R,/L = L (left shift): STHL (input), $S_{240} \rightarrow S_1 \rightarrow STHR$ (output)                                                                                            |

|            |                      |            |             | R,/L = H (right shift) : STHR (input), S <sub>1</sub> $\rightarrow$ S <sub>240</sub> $\rightarrow$ STHL (output)                                                                    |

| STHR       | Right shift start    | 325        | I/O         | These refer to the start pulse I/O pins when driver ICs are connected in cascade.                                                                                                   |

|            | pulse input/output   |            |             | Fetching of display data starts when H is read at the rising edge of CLK.                                                                                                           |

| STHL       | Left shift start     | 249        | I/O         | $R_{1}/L = L$ (left shift): STHL input, STHR output                                                                                                                                 |

|            | pulse input/output   |            |             | R,/L = H (right shift): STHR input, STHL output                                                                                                                                     |

| CLK        | Shift clock input    | 278        | Input       | This pin is the shift clock input of the shift register.                                                                                                                            |

|            |                      |            |             | Display data is captured into the data register at the rising edge.                                                                                                                 |

|            |                      |            |             | The start pulse output enters high level at the rising edge of the 80 th clock following                                                                                            |

|            |                      |            |             | the start pulse input, and becomes the start pulse of the next level driver. The 81th                                                                                               |

| OTD        | Latab innut          | 074        | الم مر مر ا | clock of the first driver becomes the start pulse input of the next driver                                                                                                          |

| STB        | Latch input          | 271        | Input       | A timing signal that latches the contents of the data register. When an H level is read<br>at the rising edge of CLK, the contents of the data register are latched and transferred |

|            |                      |            |             | to the D/A converter, and analog voltage corresponding to the display data is output.                                                                                               |

|            |                      |            |             | Also, because the internal operation via CLK continues even after the STB latch, do                                                                                                 |

|            |                      |            |             | not stop CLK. The contents of the shift register are cleared at the rising edge of STB.                                                                                             |

|            |                      |            |             | Following a 1-pulse input at startup, this IC will operate normally. Note that the output                                                                                           |

|            |                      |            |             | switch is turned off at the rising edge of STB.                                                                                                                                     |

|            |                      |            |             | For the STB input timing, refer to Switching Characteristics Waveform.                                                                                                              |

| POL        | Polarity inversion   | 269        | Input       | This pin inverts the output polarity. The polarity inversion signal data is captured at the                                                                                         |

|            | signal               |            |             | rising edge of STB. The $\gamma$ -resistor is switched in accordance with the positive/negative                                                                                     |

|            |                      |            |             | polarity.                                                                                                                                                                           |

|            |                      |            |             | POL = L: Negative polarity                                                                                                                                                          |

|            |                      |            |             | POL = H: Positive polarity                                                                                                                                                          |

| INV        | Data inversion       | 296        | Input       | This pin inverts the input data. Input data in synchronization with the shift clock.                                                                                                |

|            |                      |            |             | INV = L: Normal input                                                                                                                                                               |

|            |                      |            |             | INV = H: Data inversion input                                                                                                                                                       |

| VCOM       | COM amplitude        | 248        | Output      | This pin inverts the signal input from the POL pin and outputs it following conversion to                                                                                           |

|            | output               |            |             | the $V_{DD2}$ potential at the rising edge of STB. When the VCOM output is not used, $VC_{Se}$                                                                                      |

|            |                      |            |             | must be fixed to L.                                                                                                                                                                 |

| VCsel      | COM amplitude        | 263        | Input       | The VCOM output is fixed to L. When the VCOM output is not used, $VC_{sel}$ needs to be                                                                                             |

|            | output fixing signal |            |             | fixed to L.                                                                                                                                                                         |

|            |                      |            |             | $VC_{sel} = L$ : VCOM output fixed to L                                                                                                                                             |

|            |                      |            |             | VCsel = H: VCOM signal output in correspondence with POL signal                                                                                                                     |

| CM         | 8-color display      | 268        | Input       | The operating mode is switched to 8-color mode. Input data MSB leads display data.                                                                                                  |

|            | mode switching       |            |             | In this mode, turn off the $\gamma$ -resistor, amplifier, and BIAS circuit. However, when the $\gamma$ -                                                                            |

|            |                      |            |             | correction power supply is input externally, the $\gamma$ -circuit current will flow continuously.                                                                                  |

|            |                      |            |             | CM = L: Normal display mode                                                                                                                                                         |

|            |                      |            |             | CM = H: 8-color display mode                                                                                                                                                        |

| Pin Symbol           | Pin Name                               | Pad No.                                          | I/O    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------|----------------------------------------|--------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AP                   | Output SW<br>ON/OFF                    | 270                                              | Input  | <ul> <li>MODE = L</li> <li>This pin turns ON/OFF the BIAS circuit and turns on the output SW and amplifier.</li> <li>When AP is H, the amplifier is set and the LCD is driving.</li> <li>The amplifier output and output SW are turned on at the rising edge of AP, starting the LCD drive. Note that the output SW is turned off at the rising edge of STB and the output becomes Hi-Z (Hi-Z: High impedance). For details, refer to 4.1</li> <li>Drive Timing by MODE and AP Signal.</li> <li>For the AP input timing, refer to Switching Characteristics Waveform.</li> <li>MODE = H</li> <li>A sauce driver output circuit is changed to an amplifier output by grand fixation.</li> <li>For details, refer to 4.1 Drive Timing by MODE and AP Signal.</li> </ul> |

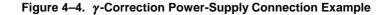

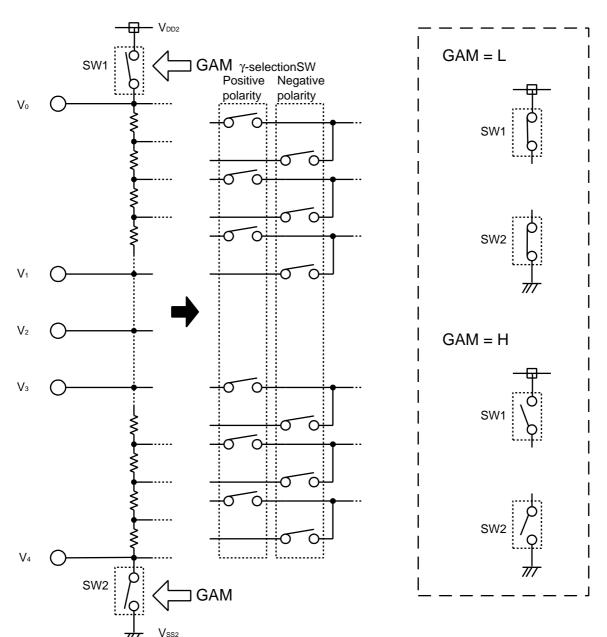

| GAM                  | External γ-usage selection             | 267                                              | Input  | When the $\gamma$ -correction power supply is input externally, switch GAM to H. If two or<br>more chips are used, be sure to input the $\gamma$ -correction power supply externally.<br>Figure 4–4 shows an input example of the $\gamma$ -correction power supply.<br>GAM = L: External $\gamma$ -correction power supply not input (open)<br>GAM = H: External $\gamma$ -correction power supply input                                                                                                                                                                                                                                                                                                                                                             |

| MODE                 | Driver output<br>functional change     | 265                                              | Input  | The drive mode of the sauce driver output by AP pin is set up as follows.<br>For details, please refer to <b>4.1 Drive Timing by MODE and AP Signal.</b><br>MODE = L: Normal drive mode<br>MODE = H: Grand output drive mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $V_0$ to $V_4$       | $\gamma$ -corrected power supplies     | 294 to 280                                       | _      | These pins input the $\gamma$ -corrected power supplies from outside, the relationship below must be observed. Also, be sure to stabilize the gray-scale-level power supply during gray-scale voltage output.<br>Vss2 $\leq V_4 \leq V_3 \leq V_2 \leq V_1 \leq V_0 \leq V_{DD2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BA                   | BIAS current<br>adjustment<br>function | 266                                              | Input  | This pin adjusts the BIAS current and through rate of amplifier inside IC.<br>Select either the high power mode or low power mode.<br>In addition, as compared with the time of the low power mode, twice about as<br>many bias current as this flows at the time of high power mode.<br>BA = L: Low power mode<br>BA = H: high power mode                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TESTIN               | TEST input pin                         | 311                                              | Input  | Set to H or leave open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TEST01,<br>TEST02    | TEST output pin                        | 309,<br>310                                      | Output | Leave open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Vdd1                 | Logic power<br>supply                  | 254 to 256,<br>312 to 314                        | _      | 2.2 to 3.6 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Vdd2                 | Driver power<br>supply                 | 251 to 253,<br>321 to 323                        | -      | 4.5 to 5.5 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>SS1</sub>     | Logic ground                           | 257 to 259,<br>315 to 317                        | -      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Vss2                 | Driver ground                          | 260 to 262,<br>318 to 320                        | _      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Dummy1 to<br>dummy18 | Dummy                                  | 241 to 247, 250,<br>279, 295, 324,<br>326 to 332 | -      | This pin is dummy.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Caution To avoid latchup failure, the sequence when turning on the power must be  $V_{DD1} \rightarrow \text{logic input} \rightarrow V_{DD2} \rightarrow \text{gray-scale power supply}$  (V<sub>0</sub> to V<sub>4</sub>), and the reverse sequence when turning off the power. Follow this sequence during shift periods as well.

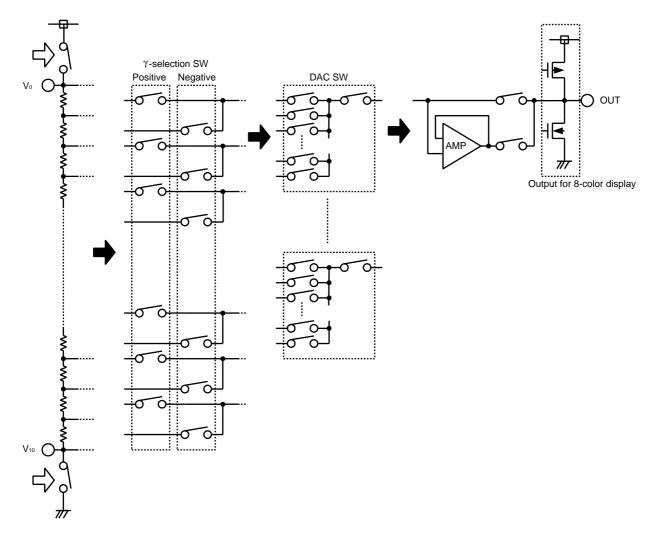

## 4. DISPLAY DRIVING CIRCUIT

The display driving circuit of  $\mu$ PD161830 consists of  $\gamma$ -resistance and  $\gamma$ -selection switch (SW) which are shown below, a D/A converter, and an output stage.

The function of each block is as follows.

$\gamma$ -resistance : It is string resistance for  $\gamma$ -curve.

$\gamma$ -selection switch (SW): Change  $\gamma$ -curve at the time of a positive and a negative drive.

D/A converter : Choose an output voltage level from display data.

Output stage : It consists of amplifier for a drive and a switch for a voltage maintenance drive, and an inverter for 8 color displays.

Figure 4–1. Output Circuit Image

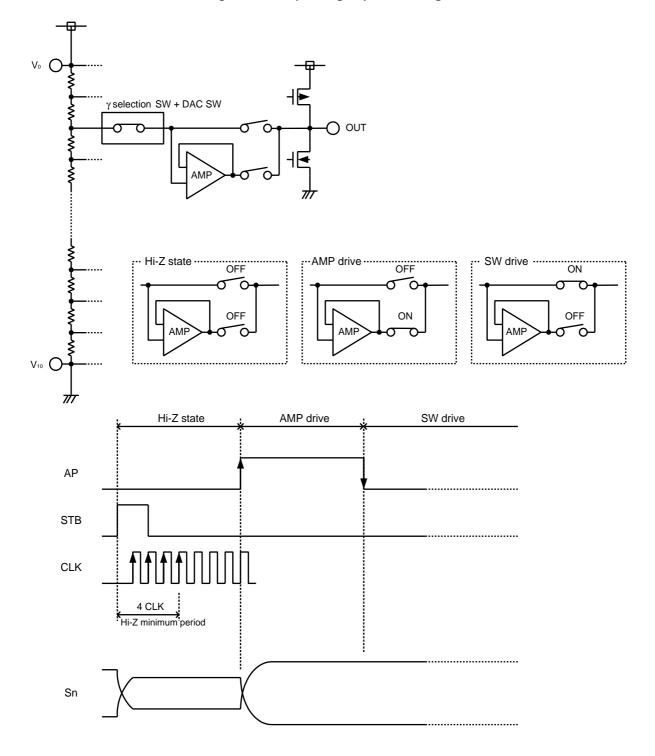

#### 4.1 Drive Timing by MODE and AP Signal

·MODE = L

Normal drive is selected when a MODE pin is set as L.

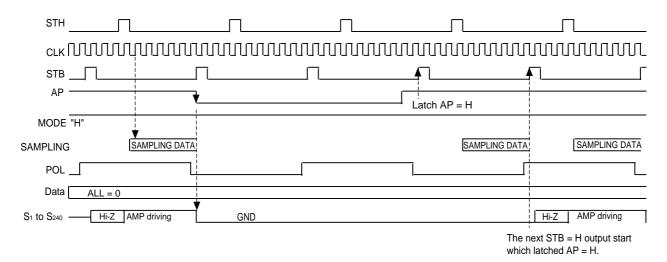

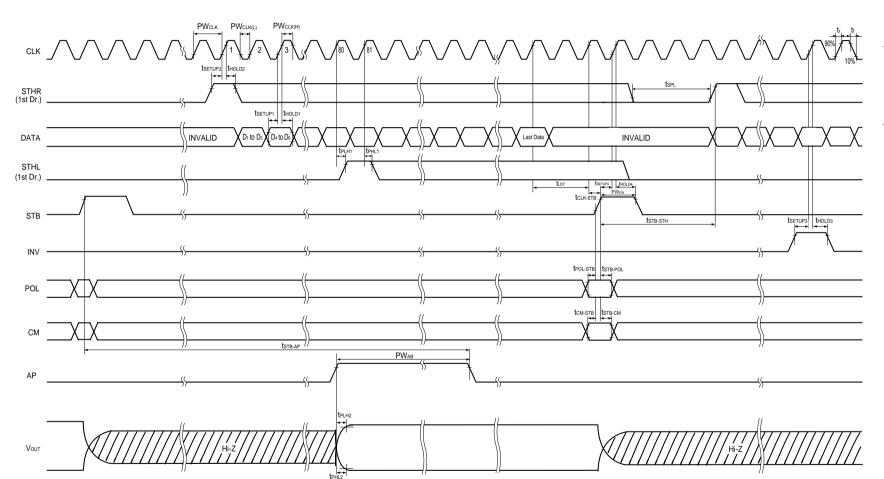

Based on output stage construction, AP pin, STB pin, CLK pin signal, and the relation of Sn (sauce output) state are shown in the next figure.

From 1 clock of a CLK signal to 4 clock is used for the output stage after a STB standup, it carries out decoding to the latch output voltage level of display data, and transmits to an output circuit.

The output circuit's having prevented from Sn pin output compulsorily the output of the level which is not decided as a Hi-Z state from the standup of a STB signal to the standup of a CLK signal 4 clock.

When AP pin is L input after 4 clock rises, as for Sn pin output, Hi-Z state is maintained, and an output circuit changes from the standup of AP pin input to an AMP drive state. Moreover, Sn pin outputs that the notes 1 which pull up to the voltage (display data) level which requires the potential of a TFT drain line, or are reduced<sup>Note1</sup>.

When low power consumption is required, AMP pin is switched from H to L, after a voltage level attain to requirement voltage level L, output circuit stage operation is changed into SW drive<sup>Note2</sup>, and it stabilizes a voltage level.

Since liquid crystal load is driven only by SW drive of  $\gamma$ -resistance direct file when referred to as AP = L before attainment of the level to demand, most time is needed for level attainment.

Since this timing (AP = H period) is dependent on the load conditions of liquid crystal, it is a real use TFT panel and fully needs to be evaluated.

Notes 1. When it is always set as AP = H, Sn pin starts an AMP drive automatically after the standup of 4 clock.

**2.** At the time of SW drive, stop the bias current of an output stage amplifier circuit, and stop the consumption current of the output stage.

#### Figure 4–2. Output Stage Operation Image

Preliminary Product Information S16240EJ2V0PM

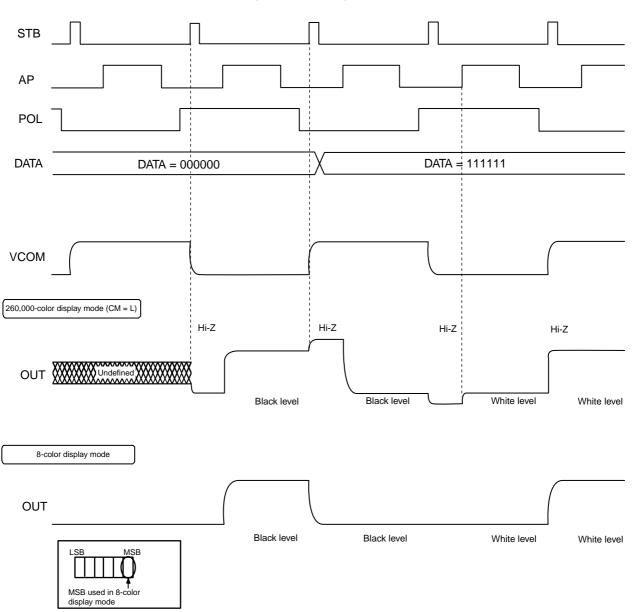

Examples of the input/output timing of each signal during white and black display in normal mode are shown below.

Figure 4–3. Timing Chart

#### ·MODE = H (GND output driving)

When a MODE pin is set as H, the output change function by AP pin is changed as follows.

| AP Pin | Sn Pin (source output) Drive |

|--------|------------------------------|

| L      | GND output (Vss fixed)       |

| Н      | Normal AMP operation         |

As for sauce output, output is fixed to ground (Vss) in falling of AP signal at the time of GND output drive (MODE = H). Moreover, the return to an APM drive usually returns from the next STB = H period which latched AP = H by the rising edge of STB signal. The relationship of the CLK signal at the time of a GND output drive, a STB signal, AP signal, and Sn state is shown as follows.

#### 4.2 *r*Correction Power Supply Connection Example

The  $\mu$  PD161830 enables customization of the  $\gamma$ -correction power supply on both the positive and negative polarity sides (refer to **6. RELATIONSHIP BETWEEN INPUT DATA AND OUTPUT VOLTAGE VALUE**). Consequently, a  $\gamma$ -correction power supply does not have to be input externally when a single source-driver chip is being used in the panel.

Multiple chips can also be used without having to input a  $\gamma$ -correction power supply externally because the error between the chips can be absorbed by shorting the  $\gamma$ -correction power supply pins, as shown in Figure 4–4.

Preliminary Product Information S16240EJ1V0PM

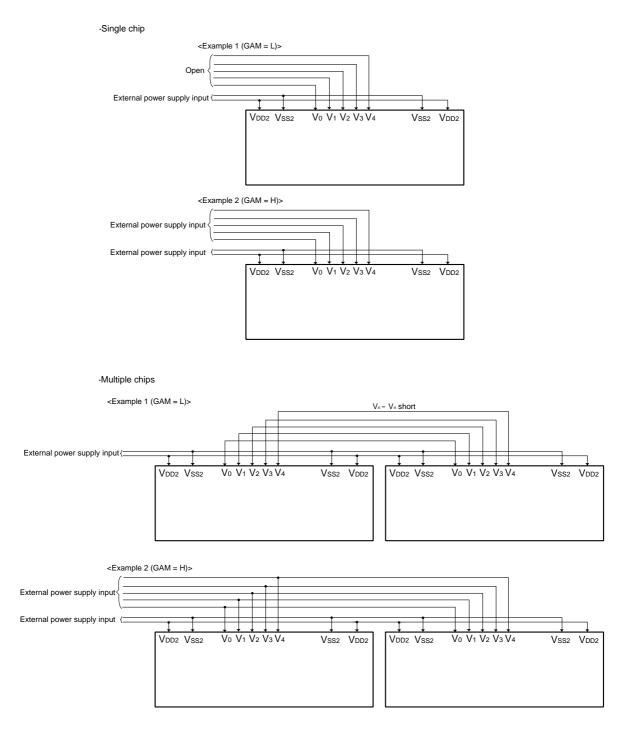

## 4.3 CLK Signal Input

Input at least 4 clocks of the CLK signal after the rising of the STB signal.

Note Internal latch signal : It is the signal that do latch the display data put in data register in output latch circuit.

## 5. MODE EXPLANATION

| СМ | POL | Data        | Driver Output Status | Driver Output (in normally white) |

|----|-----|-------------|----------------------|-----------------------------------|

| Н  | н   | MSB = H     | 8-color mode         | White level display               |

|    |     | MSB = L     |                      | Black level display               |

|    | L   | MSB = H     |                      | White level display               |

|    |     | MSB = L     |                      | Black level display               |

| L  | н   | All bit = H | 260,000-color mode   | White level display               |

|    |     | All bit = L |                      | Black level display               |

|    | L   | All bit = H |                      | White level display               |

|    |     | All bit = L |                      | Black level display               |

Normal Mode/ 8-clor Display Mode

## 6. RELATIONSHIP BETWEEN INPUT DATA AND OUTPUT VOLTAGE VALUE

The relationship between input data and output voltage are shown in Table 6–2.

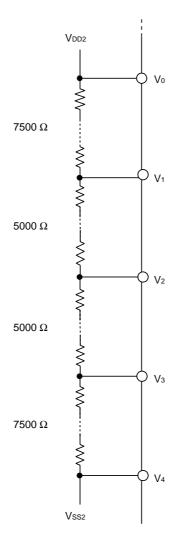

Any 3 major points V<sub>1</sub> to V<sub>3</sub> from the LCD panel  $\gamma$  characteristics curve can be used as the external power supplies. The relationship V<sub>0</sub> to V<sub>4</sub> external power supplies and  $\gamma$  correction resistance is shown in Table 6–1, Figure 6–1.

| Pin Name       | Voltage (V) | Resistance ( $\Omega$ ) |

|----------------|-------------|-------------------------|

| Vo             | 5.0         | 0                       |

| V1             | 3.5         | 7,500                   |

| V2             | 2.5         | 12,500                  |

| V <sub>3</sub> | 1.5         | 17,500                  |

| V4             | 0           | 25,000                  |

Table 6–1. Relationship between External Power Supply Pins and  $\gamma$  correction Resistance

This external power supply pins (V<sub>0</sub> to V<sub>4</sub>) can customize the  $\gamma$ -correction voltage by selecting the desired voltage from one of 250 divisions of the string resistor between V<sub>SS2</sub> and V<sub>DD2</sub>, which generated  $\gamma$ -correction voltage. Note that the voltage can be selected individually for both positive and negative polarity.

## Table 6–2. Relationship of Input Data and Output Voltage in the $\mu$ PD161830

T.B.D.

Remark T.B.D. (To be determined.)

## 6.1 Connection between $\gamma$ correction Resistance, Power Supply, and GND Pin

Connection of  $\gamma$  compensation resistance power supply (V<sub>0</sub> to V<sub>4</sub>) and a power supply pin (V<sub>DD2</sub> and V<sub>SS2</sub>) is indicated below to be  $\gamma$  compensation resistance of  $\mu$ PD161830.

By setup of a GAM pin, as for  $\gamma$ -compensation resistance, connection changes the highest minimum potential between V<sub>DD2</sub> to V<sub>SS2</sub> or among V<sub>0</sub> to V<sub>4</sub>.

#### Figure 6–2. GAM Pin Function

Preliminary Product Information S16240EJ1V0PM

## 7. RELATIONSHIP BETWEEN INPUT DATA AND OUTPUT PIN

Data format: 6 bits x RGBs (3 dots) Input width: 18 bits (1-pixel data)

R,/L = H (Right shift)

| Output | S1         | S2         | S₃         | S4         | <br><b>S</b> 239 | <b>S</b> 240 |

|--------|------------|------------|------------|------------|------------------|--------------|

| Data   | Doo to Dos | D10 to D15 | D20 to D25 | Doo to Dos | <br>D10 to D15   | D20 to D25   |

#### R,/L = L (Left shift)

| Output | S1         | S <sub>2</sub> | S3 S4      |            | <br>S239       | <b>S</b> 240 |

|--------|------------|----------------|------------|------------|----------------|--------------|

| Data   | Doo to Dos | D10 to D15     | D20 to D25 | Doo to Dos | <br>D10 to D15 | D20 to D25   |

## 8. ELECTRICAL SPECIFICATIONS

| Parameter                     | Symbol | Rating                           | Unit |

|-------------------------------|--------|----------------------------------|------|

| Logic Part Supply Voltage     | VDD1   | -0.3 to +4.5                     | V    |

| Driver Part Supply Voltage    | Vdd2   | -0.3 to +6.0                     | V    |

| Input Voltage                 | Vi     | -0.3 to V <sub>DD1,2</sub> + 0.3 | V    |

| Output Voltage                | Vo     | -0.3 to V <sub>DD1,2</sub> + 0.3 | V    |

| Operating Ambient Temperature | TA     | -20 to +75                       | °C   |

| Storage Temperature           | Tstg   | -55 to +125                      | °C   |

## Absolute Maximum Ratings (TA = 25°C, Vss1 = Vss2 = 0 V)

Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

#### Recommended Operating Range (T<sub>A</sub> = -20 to +75°C, Vss1 = Vss2 = 0 V)

| Parameter                   | Symbol         | Condition | MIN.     | TYP. | MAX.     | Unit |

|-----------------------------|----------------|-----------|----------|------|----------|------|

| Logic Part Supply Voltage   | VDD1           |           | 2.2      |      | 3.6      | V    |

| Driver Part Supply Voltage  | Vdd2           |           | 4.5      | 5.0  | 5.5      | V    |

| High-Level Input Voltage    | Vih            |           | 0.7 Vdd1 |      | Vdd1     | V    |

| Low-Level Input Voltage     | VIL            |           | 0        |      | 0.3 VDD1 | V    |

| $\gamma$ -Corrected Voltage | $V_0$ to $V_4$ |           | Vss2     |      | Vdd2     | V    |

| Clock Frequency             | fclk           |           |          |      | 15       | MHz  |

| Parameter                                                       | Symbol            | Condition                                                                                               | MIN.        | TYP. | MAX.        | Unit |

|-----------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------|-------------|------|-------------|------|

| Input Leak Current                                              | lı.               | D00-D05, D10-D15, D20-D25, R,/L, STB, CLK,<br>STHR(L), INV, CM, AP, BA, POL, GAM,<br>VCsel              |             |      | ±1.0        | μA   |

| Input Current                                                   | IIL2              | TESTIN                                                                                                  | 10          | 40   | 200         | μA   |

| High-Level Output Voltage                                       | Vон               | STHR (STHL), Іон = –1.0 mA                                                                              | VDD1 - 0.5  | .5   |             | V    |

| Low-Level Output Voltage                                        | Vol               | STHR (STHL), Io∟ = +1.0 mA                                                                              |             | 0.5  |             | V    |

| VCOM Output Voltage                                             | Vон2              | VDD2 = 5.0 V, Io = -1.0 mA                                                                              | VDD2 - 0.5  |      |             | V    |

|                                                                 | Vol2              | VDD2 = 5.0 V, Io = +1.0 mA                                                                              |             |      | 0.5         | V    |

| $\gamma$ -Correction Power-supply<br>Static Current Consumption | Iγ                | $V_0 = 5.0 \text{ V}, V_4 = 0 \text{ V}$<br>(when in $\gamma$ -correction power mode)                   | 100         | 200  | 400         | μA   |

| Driver Output Current<br>(AMP drive)                            | Ivoн1             | $V_{DD2} = 5.0 \text{ V}, V_{OUT} = V_X - 1.0 \text{ V}$ Note1<br>Input data: 1FH                       |             | -0.5 | -0.15       | mA   |

|                                                                 | Ivol1             | V <sub>DD2</sub> = 5.0 V, V <sub>OUT</sub> = V <sub>X</sub> + 1.0 V <sup>Note1</sup><br>Input data: 20H | 0.15        | 0.50 |             | mA   |

| Driver Output Current<br>(Switch drive)                         | Ілона             | $V_{DD2} = 5.0 \text{ V}, \text{ V}_{OUT} = \text{V}_{X} - 1.0 \text{ V}$ Note1<br>Input data: 1FH      |             | -50  | -15         | μA   |

|                                                                 | Ivol2             | V <sub>DD2</sub> = 5.0 V, V <sub>OUT</sub> = V <sub>X</sub> + 1.0 V <sup>Note1</sup><br>Input data: 20H | 15          | 40   |             | μA   |

| Driver Output Current                                           | Vvoh3             | $V_{DD2} = 5.0 \text{ V}, \text{ Io} = -50 \ \mu\text{A}$                                               | Vdd2 - 0.5  |      |             | V    |

| (8-color display mode)                                          | V <sub>VOL3</sub> | $V_{DD2} = 5.0 \text{ V}, \text{ Io} = +50 \ \mu\text{A}$                                               |             |      | 0.5         | V    |

| Output Voltage Deviation                                        | ΔVo               | $V_{DD1} = 2.5 \text{ V}, V_{DD2} = 5.0 \text{ V},$<br>$V_{OUT} = 2.5 \text{ V}^{Note1}$                |             | ±10  | ±20         | mV   |

| Output Voltage Range                                            | Vo                | Input data: 00H to 3FH                                                                                  | Vss2 + 0.05 |      | Vdd2 - 0.05 | V    |

| Logic Part Dynamic Current<br>Consumption                       | IDD1              | With no load <sup>Note2</sup>                                                                           |             | 0.4  | 0.8         | mA   |

| Driver Part Dynamic<br>Current Consumption                      | IDD2              | $V_{DD} = 5.0 \text{ V}$ , with no load $^{\text{Note2}}$                                               |             | 0.9  | 1.5         | mA   |

Notes 1. Vx refers to the output voltage of analog output pins  $S_1$  to  $S_{240}$ .

Vout refers to the voltage applied to analog output pins  $S_1$  to  $S_{240}.$

**2.** fcLK = 15 MHz, STB cycle = 60  $\mu$ s, AP pulse width = 15  $\mu$ s, BA=L (low power mode)

| Parameter                | Symbol | Condition                                                                                 | MIN. | TYP. | MAX. | Unit |

|--------------------------|--------|-------------------------------------------------------------------------------------------|------|------|------|------|

| Start Pulse Delay Time   | tPLH1  | C∟ = 15 pF                                                                                |      |      | 25   | ns   |

|                          | tPHL1  |                                                                                           |      |      | 25   | ns   |

| Driver Output Delay Time | tplH2H | C∟ = 30 pF                                                                                |      |      | 12   | μs   |

| (High power mode)        | tPHL2H | $AP^{\uparrow} \rightarrow V_{OUT} - 100 \text{ mV} \text{ or } V_{OUT} + 100 \text{ mV}$ |      |      | 12   | μs   |

| Driver Output Delay Time | tPLH2L | C∟ = 30 pF                                                                                |      |      | 15   | μs   |

| (Low power mode)         | tPHL2L | $AP^{\uparrow} \rightarrow V_{OUT} - 100 \text{ mV or } V_{OUT} + 100 \text{ mV}$         |      |      | 15   | μs   |

| Input Capacitance        | CI1    | V <sub>0</sub> to V <sub>4</sub> , T <sub>A</sub> = 25°C                                  |      | 5    | 15   | pF   |

|                          | CI2    | Excluded V <sub>0</sub> to V <sub>4</sub> , $T_A = 25^{\circ}C$                           |      | 10   | 15   | pF   |

#### Switching Characteristics (TA = -20 to +75°C, VDD1 = 2.2 to 3.6 V, VDD2 = 5.0 V $\pm$ 0.5 V, VSS1 = VSS2 = 0 V)

## Timing Requirements (T<sub>A</sub> = -20 to +75°C, V<sub>DD1</sub> = 2.2 to 3.6 V, V<sub>SS1</sub> = 0 V, t<sub>r</sub> = t<sub>f</sub> = 10 ns)

| Parameter                        | Symbol           | Condition                  | MIN. | TYP. | MAX. | Unit |

|----------------------------------|------------------|----------------------------|------|------|------|------|

| Clock Pulse Width                | PWCLK            |                            | 65   |      |      | ns   |

| Clock Pulse High Period          | PWclk(H)         |                            | 20   |      |      | ns   |

| Clock Pulse Low Period           |                  |                            | 20   |      |      | ns   |

| Data Setup Time                  | tsetup1          |                            | 20   |      |      | ns   |

| Data Hold Time                   |                  |                            | 20   |      |      | ns   |

| Start Pulse Setup Time           | tSETUP2          |                            | 20   |      |      | ns   |

| Start Pulse Hold Time            | tHOLD2           |                            | 20   |      |      | ns   |

| Start Pulse Low Period           | t <sub>SPL</sub> |                            | 3    |      |      | CLK  |

| Last Data Timing                 | <b>t</b> LDT     |                            | 2    |      |      | CLK  |

| CLK-STB Time                     | tclk-stb         | CLK↑ →STB↑                 | 20   |      |      | ns   |

| STB Pulse Width                  | PWstb            |                            | 40   |      |      | ns   |

| Start Pulse Rising Time          | tsтв-sтн         | STB↑ →STH↑                 | 3    |      |      | CLK  |

| INV Set-up Time                  | tsetup3          |                            | 20   |      |      | ns   |

| INV Hold Time                    | thold3           |                            | 20   |      |      | ns   |

| STB Set-up Time                  | tsetup4          |                            | 20   |      |      | ns   |

| STB Hold Time                    | tHOLD4           |                            | 20   |      |      | ns   |

| POL-STB Time                     | tpol-stb         |                            | 0    |      |      | ns   |

| STB-POL Time                     | tstb-pol         |                            | 40   |      |      | ns   |

| CM-STB Time                      | <b>t</b> см-sтв  |                            | 0    |      |      | ns   |

| STB-CM Time                      | tsтв-см          |                            | 40   |      |      | ns   |

| STB-AP Time                      | tstb-ap          | STB↑ →AP↓                  | 20   |      |      | μs   |

| AP Pulse Width (High power mode) | PWAPH            |                            | 12   |      |      | μs   |

| AP Pulse Width (Low power mode)  | PWAPL            | STB cycle 40µs, C∟ = 30 pF | 15   |      |      | μs   |

| AP Set-up Time                   | tsetup5          | STB↑, MODE = H             | 0    |      |      | ns   |

| AP Hold Time                     | tHOLD5           | STB↑, MODE = H             | 40   |      |      | ns   |

Unless otherwise specified, the input level is defined to be V<sub>IH</sub> = 0.7 V<sub>DD1</sub>, V<sub>IL</sub> = 0.3 V<sub>DD1</sub>.

22

Preliminary Product Information S16240EJ2V0PM

#### NOTES FOR CMOS DEVICES

#### **①** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### **(2)** HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

# NEC

**Reference Documents**

NEC Semiconductor Device Reliability/Quality Control System (C10983E) Quality Grades On NEC Semiconductor Devices (C11531E)

- The information contained in this document is being issued in advance of the production cycle for the device. The parameters for the device may change before final production or NEC Corporation, at its own discretion, may withdraw the device prior to its production.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

- NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

- Descriptions of circuits, software, and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software, and information in the design of the customer's equipment shall be done under the full responsibility of the customer. NEC Corporation assumes no responsibility for any losses incurred by the customer or third parties arising from the use of these circuits, software, and information.

- While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

- NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.