# **RAA270000KFT**

# (RAA270000KFT#BA2)

# General purpose Power Management IC

R02DS0021EJ0100 Rev1.00 2020.1

# Description

The RAA270000KFT is a general purpose Power Management IC (PMIC), and suitable for RENESAS' microcontroller RH850 series. The features and detail information of the PMIC are described in this document.

The PMIC contains two current mode DCDC converters, four low dropout linear regulators (LDO) and two linear trackers. The switching frequency of DCDC is typical 2.1MHz.

In order to monitor internal status, monitor function is implemented. The input voltage, output of all regulators, and internal analog voltage corresponding to temperature are monitored through ADC in microcontroller. For testing ADC in microcontroller, reference voltage can be monitored as well. Since this PMIC includes a power-up/down sequence controller, it allows user not to build external sequence circuit.

## **Features**

Input range: 6.0V to 18.5V to perform specified characteristics.

5.4V~: Power rails, 5V/3.3V/1.25V and trackers functional (Not detect low voltage)

3.9V~: Not issues reset.

· 2 switching regulators,

For point of load: 5.7V/1000mA For MCU core: 1.25V/700mA

4 linear regulators,

For MCU: 3.3V/10mA, 5.0V/300mA, 3.3V/160mA, 5.0V/60mA

· 2 linear trackers,

150mA ability with short protection to battery

- Automatic power sequence

- Watchdog timer

- Analog multiplexer

- Interrupt request

- Thermal shut down

- Reset generator

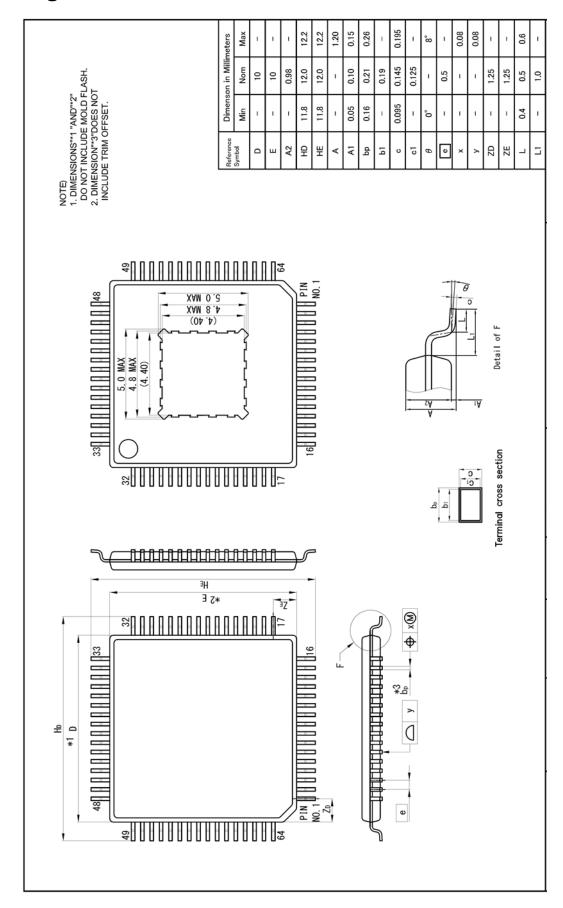

- Exposed die pad, QFP package, 64pin 12mm x 12mm

# **Applications**

- Automotive applications

- Industrial applications

- Ideal power supply for RENESAS' microcontroller, RH850 E1x and C1x series.

# **Table of Contents**

| 1 | Absolute Maximum Rating           |    |

|---|-----------------------------------|----|

|   | 1.1 Absolute maximum rating       | 4  |

| 2 | Pin Configuration                 | 5  |

|   | 2.1 Pin configuration             |    |

|   | 2.2 Pin list                      |    |

| 3 | Internal Block Diagram            | 9  |

| 4 | PMIC Function                     | 11 |

|   | 4.1 Abstract of the PMIC          | 11 |

|   | 4.1.1 PMIC operation              | 11 |

|   | 4.1.2 Pin setting                 | 12 |

|   | 4.1.3 Operating input voltage     | 13 |

|   | 4.1.4 Configuration register      | 13 |

|   | 4.1.5 Product code                |    |

|   | 4.1.6 Pin monitor                 | 14 |

|   | 4.2 Serial Interface              | 15 |

|   | 4.2.1 Signal format               | 15 |

|   | 4.2.2 Ensuring communication      | 16 |

|   | 4.2.3 Secured request             | 16 |

|   | 4.2.4 Register                    | 16 |

|   | 4.2.5 Register table              | 17 |

|   | 4.2.6 Electrical characteristics  | 18 |

|   | 4.3 Reference Voltage             | 19 |

|   | 4.3.1 Electrical characteristics  | 19 |

|   | 4.4 LDO                           | 20 |

|   | 4.4.1 Output protect function     | 21 |

|   | 4.4.2 Electrical characteristics  |    |

|   | 4.5 Tracker                       |    |

|   | 4.5.1 Register                    |    |

|   | 4.5.2 Electrical characteristics  |    |

|   | 4.6 DCDC                          |    |

|   | 4.6.1 Output protect function     |    |

|   | 4.6.2 Register                    |    |

|   | 4.6.3 Electrical characteristics  |    |

|   | 4.7 Power Rail Sequence           |    |

|   | 4.7.1 Power up sequence           |    |

|   | 4.7.2 Power down sequence         |    |

|   | 4.8 Watchdog (WD) Timer           |    |

|   | 4.8.1 Window WDT                  |    |

|   | 4.8.2 WDT operation               |    |

|   | 4.8.3 Advanced mode               |    |

|   | 4.8.4 Register                    |    |

|   | 4.8.5 Electrical characteristics  |    |

|   | 4.9 Reset                         |    |

|   | 4.9.1 Reset factor                |    |

|   | 4.9.2 Reset factor register       |    |

|   | 4.9.3 Software reset              |    |

|   | 4.9.4 External reset              |    |

|   | 4.9.5 Electrical characteristics  |    |

|   | 4.10 Specified Output Pins        |    |

|   | 4.10.1 Register                   |    |

|   | 4.10.2 Electrical characteristics | 48 |

|   | 4.11 Interi | upt Signal                            | 49 |

|---|-------------|---------------------------------------|----|

|   | 4.11.1      | Interrupt control                     | 49 |

|   | 4.11.2      | Interrupt factor                      | 49 |

|   | 4.11.3      | Register                              |    |

|   | 4.12 Fund   | tional Safety                         | 55 |

|   | 4.12.1      | Voltage detection                     |    |

|   | 4.12.2      | PMIC behavior after unusual detection | 56 |

|   | 4.12.3      | Self-diagnosis                        | 56 |

|   | 4.12.4      | Electrical characteristics            |    |

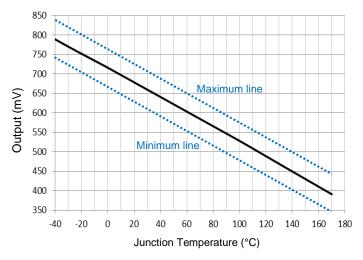

|   | 4.13 Tem    | perature Sensor                       | 59 |

|   |             | Thermal shut down                     |    |

|   | 4.13.2      | Register                              | 59 |

|   | 4.14 Moni   | toring Function                       |    |

|   | 4.14.1      | Monitoring internal analog voltage    | 61 |

|   | 4.14.2      | Monitoring digital output             |    |

|   | 4.14.3      | Register                              |    |

|   | 4.14.4      | Electrical characteristics            | 63 |

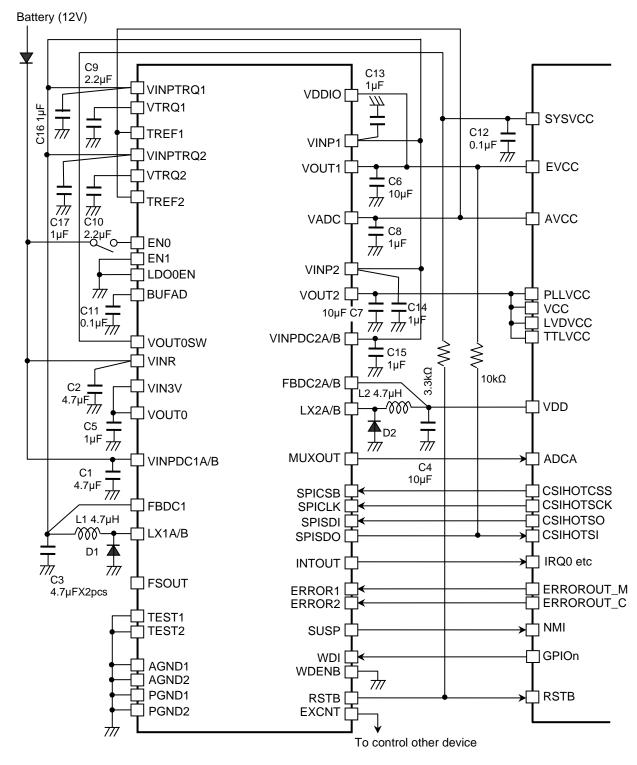

| 5 |             | Diagram                               |    |

|   |             | guide lines                           |    |

| 6 |             | Characteristics                       |    |

|   | 6.1 Recom   | mended operating condition            | 66 |

|   |             | cal characteristics                   |    |

|   |             | C characteristics                     |    |

| 7 | Package In  | formation                             | 67 |

# 1 Absolute Maximum Rating

# 1.1 Absolute maximum rating \*

| Items                                              | Comment                            | MIN     | MAX                | Unit |

|----------------------------------------------------|------------------------------------|---------|--------------------|------|

| VINR, VINPDC1A/B                                   |                                    | -0.3    | 26 ***             | V    |

| VDDIO                                              | Supply power for internal circuits | -0.3    | 6.0                | V    |

| VIN3V                                              | Supply power for internal circuits | -0.3    | 4.0                | V    |

| VINP1/2, VINPTRQ1/2,<br>VINPDC2A/B                 |                                    | -0.3    | 19                 | V    |

| PGND1/2, AGND1/2                                   | All ground pins                    | -0.3    | 0.3                | V    |

| FBDC1, FBDC2A/B                                    | Feedback pins for DCDC             | -0.3    | 19                 | V    |

| LX1A/B                                             |                                    | -1.0 ** | VINPDC1A/B<br>+0.3 | V    |

| LX2A/B                                             |                                    | -1.0 ** | VINPDC2A/B<br>+0.3 | V    |

| TREF1/2                                            | Input pins for trackers            | -0.3    | 6.0                | V    |

| EN0/1, LDO0EN                                      |                                    | -0.3    | VINR+0.3           | V    |

| VOUT0                                              |                                    | -0.3    | VINR+0.3           | V    |

| VOUT1, VADC                                        |                                    | -0.3    | VINP1+0.3          | V    |

| VOUT2                                              |                                    | -0.3    | VINP2+0.3          | V    |

| VOUT0SW, BUFAD                                     |                                    | -0.3    | VIN3V+0.3          | V    |

| VTRQ1                                              |                                    | -0.3    | VINPTRQ1<br>+0.3   | V    |

| VTRQ2                                              |                                    | -0.3    | VINPTRQ2<br>+0.3   | V    |

| MUXOUT                                             | Analog output pin                  | -0.3    | VADC+0.3           | V    |

| ERROR1/2, WDI, WDENB,<br>SPISDI,<br>SPICLK, SPICSB | Digital input pins                 | -0.3    | VDDIO+0.3          | V    |

| SPISDO, RSTB, INTOUT, SUSP<br>FSOUT, EXCNT         | Digital output pins                | -0.3    | VDDIO+0.3          | V    |

|                                                    | Junction to ambient                |         | 0.4 ****           |      |

| Thermal resistance (Typical)                       | Junction to case (Top)             |         | '.3 ****           | °C/W |

|                                                    | Junction to case (Bottom)          | 0.9     | 98 ****            |      |

| Junction Temperature *****                         |                                    | -40     | 150                | °C   |

| Storage Temperature Range                          |                                    | -55     | 150                | °C   |

<sup>\*:</sup> Stress beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

<sup>\*\*:</sup> Not allowed to apply continuous voltage.

<sup>\*\*\*:</sup> Maximum voltage is 40V under load dump condition. (Duration time is 400ms.)

<sup>\*\*\*\*:</sup> Simulation value based on JEDEC-2S2P condition.

<sup>\*\*\*\*\*:</sup> The PMIC includes over temperature protection that is intended to protect the device during momentary over load condition. Junction temperature will exceed the maximum operating junction temperature when over temperature is achieved. Continuous operating above specified maximum operating junction temperature may impair device reliability.

# 2 Pin Configuration

# 2.1 Pin configuration

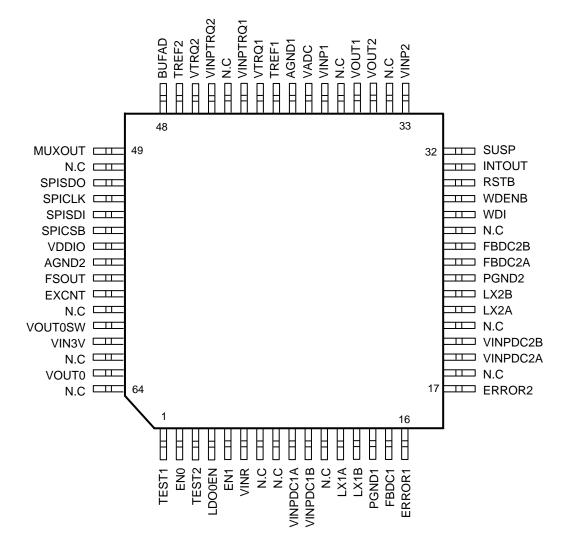

Pin configuration is shown in below figure. The package is 64pin exposed die pad QFP.

Fig. 2 Pin configuration (Top view)

# 2.2 Pin list

The pin list table is shown below.

| #<br>N | PIN name | Pin function                                                                       | Analog or<br>Digital | I/O/P/G | Interface | Protect ( | Protect circuit to | Remarks                      |

|--------|----------|------------------------------------------------------------------------------------|----------------------|---------|-----------|-----------|--------------------|------------------------------|

| 1      | TEST1    | For test. It should be connected to ground.                                        |                      | ı       | 1         | VIN3V     | AGND1/2            | Should be connected to GND.  |

| 2      | ENO      | Power enable of the PMIC.<br>(High: Enable the PMIC, Low: Disable the PMIC)        | Digital              | Input   | NMOS      | VINR      | AGND1/2            | Included pull-down resister. |

| 3      | TEST2    | For test. It should be connected to ground.                                        | -                    | ı       | -         | VIN3V     | AGND1/2            | Should be connected to GND.  |

| 4      | LD00EN   | Power enable of LDO0 without EN0 or EN1.<br>(High: Enable LDO0, Low: Disable LDO0) | Digital              | Input   | NMOS      | VINR      | AGND1/2            | Included pull-down resister. |

| 5      | EN1      | Power enable of the PMIC.<br>(High: Enable the PMIC, Low: Disable the PMIC)        | Digital              | Input   | NMOS      | VINR      | AGND1/2            | Included pull-down resister. |

| 9      | VINR     | Power supply for LDO0.                                                             | -                    | Power   | •         | -         | PGND1/2            |                              |

| 7      | N.C      | Not connected.                                                                     | -                    | ı       | •         | -         | -                  | Should be open.              |

| 8      | N.C      | Not connected.                                                                     | -                    | ı       |           | -         |                    | Should be open.              |

| 6      | VINPDC1A | Power supply for DCDC1.                                                            | •                    | Power   | 1         | •         | PGND1/2            |                              |

| 10     | VINPDC1B | Power supply for DCDC1.                                                            | -                    | Power   | ,         | •         | PGND1/2            |                              |

| 11     | N.C      | Not connected.                                                                     | •                    | 1       | •         | -         |                    | Should be open.              |

| 12     | LX1A     | DCDC1 Inductor driver output.                                                      | Analog               | Output  | •         | -         | PGND1/2            |                              |

| 13     | LX1B     | DCDC1 Inductor driver output.                                                      | Analog               | Output  | 1         | -         | PGND1/2            |                              |

| 14     | PGND1    | Ground.                                                                            | -                    | Ground  | 1         | •         |                    |                              |

| 15     | FBDC1    | DCDC1 Feedback from VD1.                                                           | Analog               | Input   | •         | -         | AGND1/2            |                              |

| 16     | ERROR1   | Input for monitor signal of microcontroller.                                       | Digital              | Input   | CMOS      | VDDIO     | AGND1/2            | Included pull-down resister. |

| 17     | ERROR2   | Input for monitor signal of microcontroller.                                       | Digital              | Input   | CMOS      | VDDIO     | AGND1/2            | Included pull-down resister. |

| 18     | N.C      | Not connected.                                                                     |                      | 1       | •         | -         |                    | Should be open.              |

| 19     | VINPDC2A | Power supply for DCDC2.                                                            |                      | Power   | •         |           | PGND1/2            |                              |

| 20     | VINPDC2B | Power supply for DCDC2.                                                            |                      | Power   | 1         | -         | PGND1/2            |                              |

Note: AGND1/2 and PGND1/2 are connected in the PMIC.

Pin list (Continued)

| # NIA | PIN name | Pin function                   | Analog or<br>Digital | I/O/P/G | Interface<br>level | Protect (VDD name | Protect circuit to D name GND name | Remarks                      |

|-------|----------|--------------------------------|----------------------|---------|--------------------|-------------------|------------------------------------|------------------------------|

| 21    | N.C      | Not connected.                 | -                    | -       | 1                  | -                 | -                                  | Should be open.              |

| 22    | LX2A     | DCDC2 Inductor driver output.  | Analog               | Output  | •                  | -                 | PGND1/2                            |                              |

| 23    | LX2B     | DCDC2 Inductor driver output.  | Analog               | Output  | 1                  | -                 | PGND1/2                            |                              |

| 24    | PGND2    | Ground.                        | -                    | Ground  | 1                  | -                 | -                                  |                              |

| 25    | FBDC2A   | DCDC2 Feedback from VD2.       | Analog               | Input   | 1                  | -                 | AGND1/2                            |                              |

| 26    | FBDC2B   | DCDC2 Feedback from VD2.       | Analog               | Input   | 1                  | -                 | AGND1/2                            |                              |

| 27    | N.C      | Not connected.                 | -                    | -       | -                  | -                 | -                                  | Should be open.              |

| 28    | WDI      | Clear watch dog timer.         | Digital              | Input   | CMOS               | VDDIO             | AGND1/2                            | Included pull-down resister. |

| 29    | WDENB    | Watch dog enable.              | Digital              | Input   | CMOS               | VDDIO             | AGND1/2                            | Included pull-down resister. |

| 30    | RSTB     | Reset output.                  | Digital              | Output  | Open drain         | VDDIO             | AGND1/2                            |                              |

| 31    | INTOUT   | Interrupt signal output.       | Digital              | Output  | CMOS               | VDDIO             | AGND1/2                            |                              |

| 32    | SUSP     | Low voltage indicator of LDO1. | Digital              | Output  | CMOS               | VDDIO             | AGND1/2                            |                              |

| 33    | VINP2    | Power supply for LDO2.         | -                    | Power   | 1                  | -                 | AGND1/2                            |                              |

| 34    | N.C      | Not connected.                 | -                    | -       | 1                  | -                 | -                                  | Should be open.              |

| 35    | VOUT2    | LDO2 output.                   | Analog               | Output  | •                  | VINP2             | AGND1/2                            |                              |

| 36    | VOUT1    | LDO1 output.                   | Analog               | Output  | •                  | VINP1             | AGND1/2                            |                              |

| 37    | N.C      | Not connected.                 |                      |         | 1                  | -                 | -                                  | Should be open.              |

| 38    | VINP1    | Power supply for LDO1.         |                      | Power   | •                  | -                 | AGND1/2                            |                              |

| 39    | VADC     | LDOAD output.                  | Analog               | Output  | ,                  | VINP1             | AGND1/2                            |                              |

| 40    | AGND1    | Ground.                        |                      | Ground  | •                  | -                 | -                                  |                              |

| 41    | TREF1    | Input reference for TRACK1.    | Analog               | Input   |                    | -                 | AGND1/2                            |                              |

| 42    | VTRQ1    | TRACK1 output.                 | Analog               | Output  | 1                  | -                 | AGND1/2                            |                              |

Note: AGND1/2 and PGND1/2 are connected in the PMIC.

Pin list (Continued)

| #<br>ZI<br>D | PIN name | Pin function                         | Analog or | 5/d/0/l | Interface | Protect  | Protect circuit to | Remarks                      |

|--------------|----------|--------------------------------------|-----------|---------|-----------|----------|--------------------|------------------------------|

| =            |          |                                      | Digital   |         | level     | VDD name | GND name           |                              |

| 43           | VINPTRQ1 | Power supply for TRACK1.             | 1         | Power   | ı         |          | AGND1/2            |                              |

| 44           | N.C      | Not connected.                       | -         | 1       | •         |          | -                  | Should be open.              |

| 45           | VINPTRQ2 | Power supply for TRACK2.             | ı         | Power   | ı         | ı        | AGND1/2            |                              |

| 46           | VTRQ2    | TRACK2 output.                       | Analog    | Output  | 1         |          | AGND1/2            |                              |

| 47           | TREF2    | Input reference for TRACK2.          | Analog    | Input   | ı         | •        | AGND1/2            |                              |

| 48           | BUFAD    | Voltage reference output.            | Analog    | Output  | •         | •        | AGND1/2            |                              |

| 49           | MUXOUT   | Analog multiplexer output.           | Analog    | Output  | •         | VADC     | AGND1/2            |                              |

| 20           | N.C      | Not connected.                       | -         | 1       | •         | -        | -                  | Should be open.              |

| 51           | SPISDO   | Serial interface data output.        | Digital   | Output  | CMOS      | VDDIO    | AGND1/2            |                              |

| 52           | SPICLK   | Serial interface clock input.        | Digital   | Input   | CMOS      | VDDIO    | AGND1/2            | Included pull-down resister. |

| 53           | SPISDI   | Serial interface data input.         | Digital   | Input   | CMOS      | VDDIO    | AGND1/2            | Included pull-down resister. |

| 54           | SPICSB   | Serial interface chip select input.  | Digital   | Input   | CMOS      | VDDIO    | AGND1/2            | Included pull-up resister.   |

| 22           | VDDIO    | Power supply for I/O of the PMIC.    | -         | Power   | •         | -        | AGND1/2            |                              |

| 99           | AGND2    | Ground.                              | -         | Ground  | -         |          | -                  |                              |

| 22           | FSOUT    | Specified digital output.            | Digital   | Output  | CMOS      | VDDIO    | AGND1/2            |                              |

| 28           | EXCNT    | Specified digital output.            | Digital   | Output  | CMOS      | VDDIO    | AGND1/2            |                              |

| 69           | N.C      | Not connected.                       | -         |         | ı         | 1        | -                  | Should be open.              |

| 09           | VOUT0SW  | LDO0 output through internal switch. | Analog    | Output  | ı         |          | AGND1/2            |                              |

| 61           | VIN3V    | Power supply for internal circuit.   | ı         | Power   |           |          | AGND1/2            |                              |

| 62           | N.C      | Not connected.                       | -         | 1       | ,         |          | -                  | Should be open.              |

| 63           | VOUTO    | LDO0 output.                         | Analog    | Output  | •         | VINR     | AGND1/2            |                              |

| 64           | N.C      | Not connected.                       |           | 1       | 1         | •        | AGND1/2            | Should be open.              |

Note: AGND1/2 and PGND1/2 are connected in the PMIC.

# 3 Internal Block Diagram

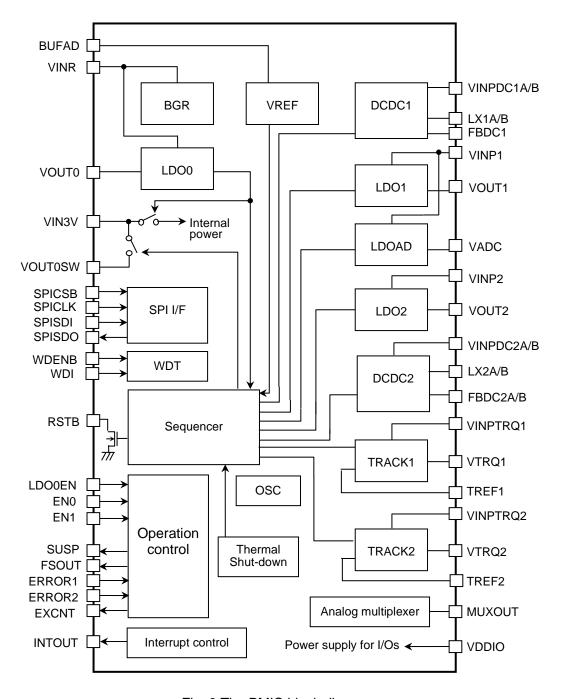

The PMIC block diagram is shown in below figure.

Fig. 3 The PMIC block diagram

The abstractive descriptions are here. Please refer to each section for more detail.

- ♦ LDO0

- LDO0 is a low drop output regulator. It generates 3.3V power. The output current ability is 10mA.

- ◆ LDO1

- LDO1 is a low drop output regulator. It generates 5.0V power. The output current ability is 300mA.

- **♦** LDO2

- LDO2 is a low drop output regulator. It generates 3.3V power. The output current ability is 160mA.

# **♦** LDOAD

LDOAD is a low drop output regulator. It generates 5.0V power. The output current ability is 60mA.

#### **◆ TRACK1**

TRACK1 is a voltage tracker. The output tracks input voltage applied on TREF1. The current ability is 150mA.

### **♦ TRACK2**

TRACK2 is a voltage tracker. The output tracks input voltage applied on TREF2. The current ability is 150mA

## ♦ DCDC1

DCDC1 is a switching regulator. It generates 5.7V power. The output current ability is 1000mA.

## **♦** DCDC2

DCDC2 is a switching regulator. It generates 1.25V power. The output current ability is 700mA.

# ◆ Band gap reference (BGR)

BGRs generate reference voltage for the regulators.

# **♦ VREF**

VREF generates necessary voltage for regulators. To reduce noise of LDO1 and LDOAD, an external capacitor can be added.

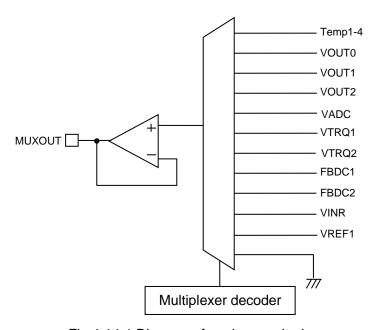

# ◆ Analog multiplexer

An analog multiplexer outputs internal analog voltage of the PMIC.

## **♦** SPI interface

SPI receives requests from microcontroller. Or it also sends register setting.

# ◆ Watch dog timer (WDT)

WDT monitors system operating. WDT can be controlled by WDI pin or via SPI.

# **♦** Sequencer

It controls power up/down of the regulators.

## Operation control

It controls operation of the PMIC and external pins.

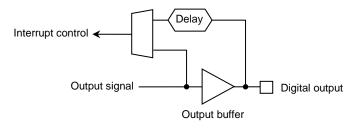

## Interrupt control

It controls interrupt operations.

## ♦ OSC

2.1MHz oscillator for sequencer and DCDC. No external part needed.

#### ◆ Thermal shut-down

It monitors temperature on the die. If the temperature rises higher than designated value, it informs to the sequencer.

# 4 PMIC Function

# 4.1 Abstract of the PMIC

In order to supply power to microcontroller or ASIC, the PMIC contains two current mode DCDC converters (DCDC) and four LDOs. The DCDC1's output is supposed to be used for all LDOs' and DCDC2's power sources. When battery voltage is applied to the PMIC, the regulators rise up automatically in accordance with designated sequence. And after all outputs of the regulators power up successfully, the "INTOUT" signal is released.

The PMIC also has a watchdog timer (WDT). When timer in the WDT expires, a reset signal occurs. The WDT is refreshed by a request via WDI pin or SPI.

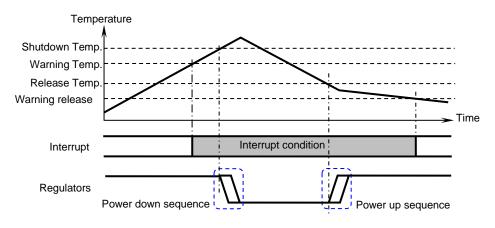

When the junction temperature reaches over Tsd, a reset occurs and all regulators would be forced to power down immediately.

# 4.1.1 PMIC operation

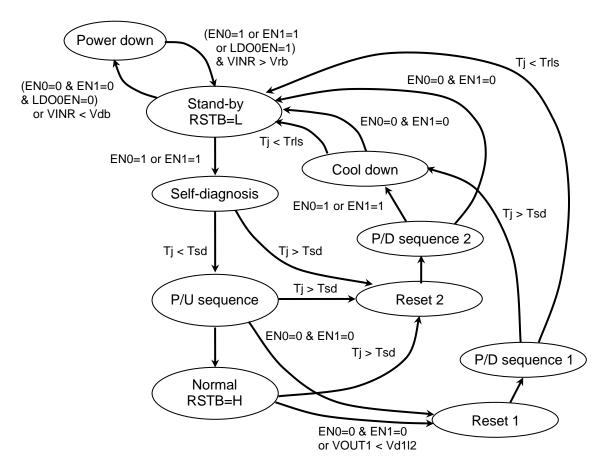

The principal operate transitions and conditions are illustrated in below state diagram.

EN0 or EN1 is enables operation of the PMIC. If EN0 and EN1 are set low, the PMIC enters "Stand-by" state.

Fig.4 State diagram

### ◆ Power down

In this state, no block in the PMIC operates.

#### Stand-by

In this state, the PMIC executes initial reset of internal registers and RSTB pin is asserted low. Only LDO0 operates in this state.

# ♦ Self-diagnosis

If EN0 or EN1 is set 1, self-diagnostic starts. In this state, over/under voltage detector in the regulators and the internal logic circuit are checked. If junction temperature is higher than Tsd, then it enters "Reset2" state.

# ◆ P/U sequence

After executing self-diagnostic, this state is automatically entered. Even if one of regulators doesn't rise up, it stays in this state. After all regulators rise up and it passed 12ms, reset is released. WDENB is detected in this state.

## **♦** Normal

After reset is released, this state is automatically entered. If WDENB is detected as low in this state, system monitor is started with using the WD function. If WDENB is detected as high, the WDT doesn't run. And also the PMIC monitors junction temperature.

#### Reset 1

RSTB asserts low by setting low both EN0 and EN1, or low voltage detection of VOUT1 immediately.

# ♦ P/D sequence 1

This state is automatically entered from "Reset 1" state. All regulators except LDO0 start to fall down in designated order. Junction temperature is checked. If junction temperature is higher than Tsd, then it enters "Cool down" state. If lower than Trls, it enters back "Stand-by" state.

#### Reset 2

When Tj comes over Tsd, RSTB pin asserts low.

## ◆ P/D sequence 2

This state is automatically entered from "Reset 2" state. All regulators except LDO0 start to fall down in designated order.

## **♦** Cool down

The PMIC checks if junction temperature is lower than Trls. If junction temperature is higher than Tsd, the PMIC wait until junction temperature cools down. After junction temperature comes below Trls, it enters "Stand-by" state.

# 4.1.2 Pin setting

The PMIC has several pins to define PMIC operation. For proper operation, these pins should be set to appropriate level. Appropriate setting voltages are described in "6. Electrical Characteristics"

# The PMIC enabling

User can control the PMIC by EN0 or EN1 pin. And it also makes only LD00 power on by LD00EN. These pins can be connected to battery.

Table 4-1 Setting PMIC operation

| EN0 | EN1 | LDO0EN | PMIC operation     |

|-----|-----|--------|--------------------|

| 0   | 0   | 0      | Disenable          |

| 0   | 0   | 1      | Only LDO0 operates |

| 0   | 1   | *      | The PMIC operates  |

| 1   | 0   | *      | The PMIC operates  |

| 1   | 1   | *      | The PMIC operates  |

<sup>\*:</sup> Don't care

Note: If EN0 or EN1 is asserted high after LDO0EN=1, please keep VINR > Vrb. In the condition of VINR < Vrb, the state is shifted to power down.

# ♦ WDT enabling

User can stop WDT operation by setting WDENB pin. When WDENB is set to disenable, the WDT stops operation. Below setting is defined at before start of P/U sequence.

Table 4-2 Setting WDT operation

| WDENB | WDT operation |

|-------|---------------|

| 0     | Enable        |

| 1     | Disenable     |

# 4.1.3 Operating input voltage

The PMIC operates different mode in accordance with its input voltage. The PMIC operation in input voltage range is shown in below table.

Table 4-3 The PMIC operation mode

| Operation mode    | Function                                                                                                    | Input range |

|-------------------|-------------------------------------------------------------------------------------------------------------|-------------|

| Full operation    | All regulators operate normaly.                                                                             | 6.0V ~      |

| Partial operation | DCDC1 stops switching, but all LDOs, DCDC2 and trackers operate normaly. (Not issue low voltage detection.) | 5.4V ~      |

| Lingering mode    | Not issue reset.                                                                                            | 3.9V ~      |

# 4.1.4 Configuration register

In order to configure functional operation of the PMIC, it needs to set in this register. For more setting information, please refer to each described section.

# > Configuration register

This register is a secured register. It is necessary to enter "key" code, before entering this request. (See "4.2.3 Secured request".) Brief explanations of register contents are described in below of the table following;

■ Address (CONF): 10H

| A5 | A4 | A3 | A2 | A1 | A0 |

|----|----|----|----|----|----|

| 0  | 1  | 0  | 0  | 0  | 0  |

Register

| D7 | D6 | D5 | D4     | D3     | D2      | D1    | D0     |

|----|----|----|--------|--------|---------|-------|--------|

| -  | -  | -  | RSTBER | WDTCNT | DL2RSTB | ADVWD | CWRSTB |

Setting contents

| Dogistor no | am o  | Control contents                     | Se     | etting    |

|-------------|-------|--------------------------------------|--------|-----------|

| Register na | arrie | Control contents                     | 1      | 0         |

| RSTBER      | D4    | Reset assertion by ERROR1/2 input    | On     | Off *     |

| WDTCNT      | D3    | Select WDT clear input channel       | SPI    | WDI *     |

| DL2RSTB     | D2    | Reset by DETDC2L or DET2L            | On     | Off *     |

| ADVWD       | D1    | Advanced mode for WD operating       | Enable | Disable * |

| CWRSTB      | D0    | Reset by WD trigger in close window. | On     | Off *     |

<sup>\*</sup> Default setting

Note1: This register is not initialized by RSTB.

Note2: Advanced mode for WD is effective when SPI is selected to refresh WDT.

RSTBER: The register can set to relate with ERROR1/2. After setting "On", RSTB asserts low when ERROR indicates error.

WDTCNT: Select WDT clear input. To clear WDT through SPI, it needs to set this bit.

DL2RSTB: The register can set to make reset when low voltage of DCDC2 or LDO2 is detected.

After setting "On", reset is generated by low voltage of DCDC2 or LDO2.

ADVWD: The register can set to operate WDT in advanced mode. After setting "Enable", WD operates in advanced mode. Please refer to "4.8 Watchdog timer".

CWRSTB: The register can set to make reset when a trigger occurs in close window.

## 4.1.5 Product code

In order to identify the PMIC, product code can be read from the PMIC.

## Product code

In order to identify the PMIC, each product has ID code. It can be read via SPI.

■ Address (CHIPID): 00H

| A5 | A4 | A3 | A2 | A1 | A0 |

|----|----|----|----|----|----|

| 0  | 0  | 0  | 0  | 0  | 0  |

■ Register (Below bits are read only.)

|    | 1     | 1 |    | 1  |    |    |    |

|----|-------|---|----|----|----|----|----|

| D7 | D6 D5 |   | D4 | D3 | D2 | D1 | D0 |

| 1  | 0     | 1 | 1  | 1  | 1  | 1  | 1  |

## 4.1.6 Pin monitor

WDENB and ERROR1/2 are significant pins related to PMIC behavior. These pins are monitored in this register.

# > Pin monitor register

This register is monitoring WDENB and ERROR1/2 pins.

■ Address (PINMON): 02H

| A5 | A4 | A3 | A2 | A1 | A0 |

|----|----|----|----|----|----|

| 0  | 0  | 0  | 0  | 1  | 0  |

■ Register (Below bits are read only.)

| 3 \ |    |    | - , , |    |        |       |       |

|-----|----|----|-------|----|--------|-------|-------|

| D7  | D6 | D5 | D4    | D3 | D2     | D1    | D0    |

| -   | -  | -  | -     | -  | PWDENB | PERR2 | PERR1 |

Setting contents

| Register n | ame | Monitor pin        |

|------------|-----|--------------------|

| PWDENB     | D2  | WDENB pin's level  |

| PERR2      | D1  | ERROR2 pin's level |

| PERR1      | D0  | ERROR1 pin's level |

| Bit | Contents   |

|-----|------------|

| 0   | Low level  |

| 1   | High level |

Note1: Above WDENB is identified at "P/U sequence" state.

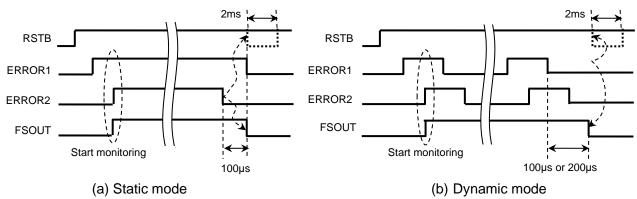

Note2: The PMIC starts to monitor ERROR1/2 after reset is released and sampled every 100µs.

# 4.2 Serial Interface

In order to request to the PMIC, the PMIC includes serial to peripheral interface. (SPI) User can set or request following things. For more detail contents, please refer to each section.

- > WDT operation (If SPI control is selected.)

- > Control the monitor function

- > Interrupt control, read factor, write interrupt clear

- > TRACK1/2 power control

- > Change shutdown or warning temperature

# 4.2.1 Signal format

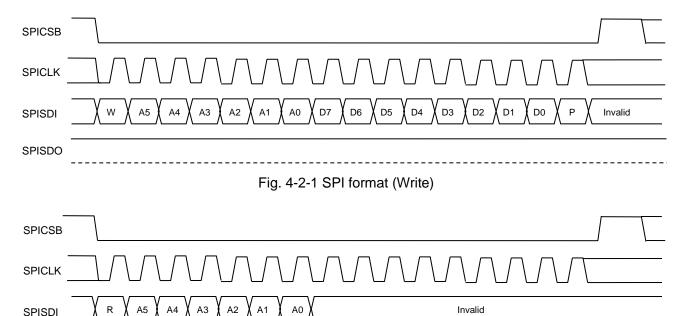

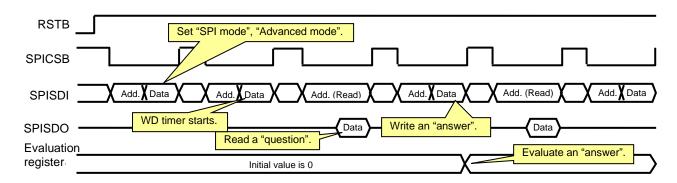

The bit length of the communication is 16bits, and signal format is illustrated in below figures.

The data should be transmitted as MSB first. For this SPI, one SPICSB active is for one request. Therefore, it is necessary to make SPICSB rise up after transmitted data.

Fig. 4-2-2 SPI format (Read)

Do6

Do5

Do7

Do4

Do3

Do2

Do1

Do0

**Caution**: In the PMIC, entered data is latched by rising edge of SPICSB. **Caution**: SPISDO pin should be terminated with pull-up resister to VOUT1.

### ♦ W/R

SPISDO

This bit indicates write or read registers. To write register, bit W/R should be set 0. To read register, bit W/R should be set 1. When user wants to read register, Do7-Do0 bits indicate contents. (D7-D0 bits are ignored in the PMIC.)

# **♦** A5-A0

The PMIC contains several registers. The addresses are described in these bits. Every registers can be read to confirm its content.

# ♦ D7-D0

These bits describe control bits of the PMIC to write into the PMIC.

### ◆ Do7-Do0

These bits describe content bits or flag bits to read from the PMIC.

#### **◆** P

This bit indicates parity bit. It is calculated based on the number of logic contained in bits except parity bit itself

SPISDO terminal stays Hi-Z during transmitting "W/R" bit and address bits, A5-A0. But parity bit of read data is calculated with considering "W/R" bit and all address bits as 1. Therefore, pull-up resister should be placed between SPISDO and VOUT1.

Bit P must be set 0 if the number of 1 is odd.

Bit P must be set 1 if the number of 1 is even.

# 4.2.2 Ensuring communication

To ensure the communication between the PMIC and microcontroller, the PMIC checks the SPI signal of following accesses. The PMIC counts how many times below access happen.

#### Number of SPICLK

The PMIC counts SPICLK clocks while SPICSB is low. If the number of clock is not 16, it is considered as a communication error. The PMIC ignores this command or request.

Not related address

When unrelated address is transmitted, the PMIC ignores this address' contents.

Parity bit

The SPI format includes a parity bit. The PMIC checks the parity bit and if transmitted bits are not based on the parity bit, it is considered as a communication error. The PMIC ignores this command or request.

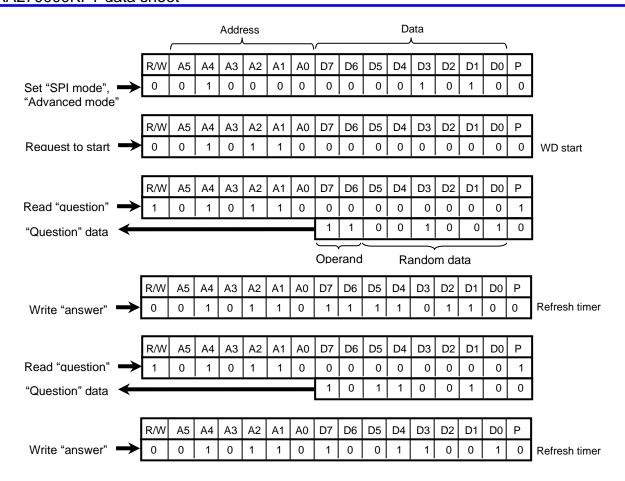

# 4.2.3 Secured request

There are some registers which need to be careful when register's content is changed. When it needs to change following contents, microcontroller needs to request code as a "key" to the PMIC. And write below address with a "key" code at once before changing contents. Without a "key" code, the request would be ignored. To execute software reset, obtained "key" should be combined instead of sending protect code address.

- Configuration register (Address : 10H)

- DCDC protect operation setting (Address : 1BH)

- Power control for TRACK1/2 (Address : 1AH)

- Window time setting for WD timer (Address: 17H)

- ➤ Interrupt mask register (Address : 0CH-0FH)

- > Reset mask register (Address: 14H)

- > Temperature setting for thermal shut down (Address: 1EH)

- Software reset (Address: 1DH)

# 4.2.4 Register

The contents of SPI setting are described in this section.

# > Protect remove code

■ Address (PRTCT): 11H

| A5 | A4 | A3 | A2 | A1 | A0 |

|----|----|----|----|----|----|

| 0  | 1  | 0  | 0  | 0  | 1  |

## Register

Before access secured register, need to obtain below random code by read mode.

| Do7 | Do6             | Do5 | Do4 | Do3 | Do2 | Do1 | Do0 |  |  |  |  |  |  |

|-----|-----------------|-----|-----|-----|-----|-----|-----|--|--|--|--|--|--|

|     | RDMKEY(Do7:Do0) |     |     |     |     |     |     |  |  |  |  |  |  |

|     |                 |     |     |     |     |     |     |  |  |  |  |  |  |

It needs to enter the obtained data before microcontroller enters request.

D7

D6

D5

D4

D3

D2

D1

D0

RDMKEY(D7:D0)

# ■ Setting contents

- RDMKEY(Do7:Do0): Random code from the PMIC

- RDMKEY(D7:D0): Copy RDMO(Do7:Do0)

Note: Read PRTCT register to get key and write it back to PRTCT register before modify those function protect registers, instead of write the key to those function protect registers.

# 4.2.5 Register table

The registers which can be set in the PMIC are summarized in below table with its address and data. Detail contents are described in each section.

| Function                  | Chip ID     | Monitor digital output pins | Interrupt factor | Interrupt request 1 | Interrupt request 2 | Interrupt request 3 | Interrupt request 4 | Interrupt clear 1 | Interrupt clear 2 | Interrupt clear 3 | Interrupt clear 4 | Interrupt mask1 | Interrupt mask2               | Interrupt mask3 | Interrupt mask4 | Configuration register | Protect remove code | Reset factor | Reset factor clear | Reset factor mask | EXCNT and SUSP pin, error monitor setting | WD advanced mode | Windowtime setting | Muxamp control | Accumulated value for WD advanced mode | TRACK1/2 on/off control | Limit control for DCDC | Numver of reset for W D advanced mode | Software reset | Thermal shutdown temperature |

|---------------------------|-------------|-----------------------------|------------------|---------------------|---------------------|---------------------|---------------------|-------------------|-------------------|-------------------|-------------------|-----------------|-------------------------------|-----------------|-----------------|------------------------|---------------------|--------------|--------------------|-------------------|-------------------------------------------|------------------|--------------------|----------------|----------------------------------------|-------------------------|------------------------|---------------------------------------|----------------|------------------------------|

| Reset by                  |             | DET00                       | DET00            | DET00               | DET00               | DET00               | DET00               | RSTB              | RSTB              | RSTB              | RSTB              | RSTB            | RSTB                          | RSTB            | RSTB            | DET00                  | RSTB                | DET00        | RSTB               | RSTB              | RSTB                                      | RSTB             | RSTB               | RSTB           | RSTB                                   | RSTB                    | DET00                  | RSTB                                  | RSTB           | DET00                        |

| Initial Secured Reset by  |             |                             |                  |                     |                     |                     |                     |                   |                   |                   |                   | 0               | 0                             | 0               | 0               | 0                      |                     |              |                    | 0                 |                                           |                  | 0                  |                |                                        | 0                       | 0                      |                                       | 0              | 0                            |

| Initial                   | 0xBF        | *0x0                        | 0x00             | 0x00                | 0x00                | 00x0                | 0x00                |                   | ,                 |                   |                   | 0x00            | 0x00                          | 00x0            | 0x00            | 0x00                   | 0x**                | 00x0         |                    | 0x00              | 0x30                                      | 0xFF             | 0x03               | 00x0           | 0x00                                   | 00x0                    | 0x44                   | 0xff                                  |                | 0x94                         |

| 00                        |             | PERR1                       | INTR1            | DETDC1U             | DETDC1L             | DETDC10C            | PRSTB               | CLDC1U            | CLDC1L            | CLDC10C           | CLPRSTB           | MSKDC1U         | MSKDC1L                       | M SKDC10C       | MSKPRSTB        | CWRSTB                 |                     | LVLD01       | CLLVLD01           |                   | EMODE                                     |                  | WDTIME<1:0>        |                |                                        | VTRQ1CNT                | 1<1:0>                 |                                       |                | -                            |

| М                         |             | PERR2                       | INTR2            | DETDC2U             | DETDC2L             | DETDC20C            | PSUSP               | CLDC2U            | CLDC2L            | CLDC20C           | CLPSUSP           | MSKDC2U         | MSKDC2L                       | MSKDC20C        | MSKPSUSP        | ADVWD                  |                     | LVDC2        | CLLVDC2            | MSKLVDC2          | SELDT                                     |                  | WILDW              | :[<3:0>        |                                        | VTRQ2CNT                | DTIME1<1:0>            |                                       |                | THDET                        |

| D2                        |             | PWDENB                      | INTR3            | DET1U               | DET1L               | DETBAT1             | PEXCNT              | CL1U              | CL1L              | CLBAT1            | CLPEXCNT          | MSK1U           | MSK1L                         | MSKBAT1         | MSKPEXCNT       | DL2RSTB                |                     | WDEXP        | CLWDEXP            | MSKWDEXP          |                                           | <0:5>            | <4:0>              | MUXSEL<3:0>    |                                        | 1                       | 1<1:0>                 |                                       |                | WARDET<1:0>                  |

| D3                        | <7:0>       | ı                           | INTR4            | DET2U               | DET2L               | DETREF              | PFSOUT              | CL2U              | CL2L              | CLREF             | CLPFSOUT          | MSK2U           | MSK2L                         | 1               | MSKPFSOUT       | WDTCNT                 | Y<7:0>              | TSDTMP       | CLTSDTMP           | MSKTSDTMP         |                                           | SUBJ<5:0>        | CWSET<1:0⊳         |                | <0:/>>                                 | 1                       | INTIME1<1:0>           | <0:/>                                 | Y<7:0>         | WARDE                        |

| D4                        | CHIPID<7:0> | ı                           | INTSD            | DETADU              | DETADL              | WRWDT               | SD0SW               | CLADU             | CLADL             | CLWDT             | CLOSW             | MSKADU          | MSKADL                        | MSKWDT          | 1               | RSTBER                 | RDMKEY<7:0>         | LVLD02       | CLLVLD02           | MSKLVLD02         | SETEXCNT                                  |                  | -                  | ı              | ACCVA<7:0>                             | ı                       | 2<1:0>                 | SETVA<7:0>                            | RDMKEY<7:0>    | <1:0>                        |

| D2                        |             | 1                           | INTRSFG          | DETTRQ1U            | DETTRQ1L            | WRTMP1              | SDSTA               | CLTRQ1U           | CLTRQ1L           | CLTMP1            | CLSTA             | MSKTRQ1U        | MSKTRQ1L                      | MSKTMP1         | MSKSTA          | !                      |                     | 1            | -                  | -                 | SETSUSP                                   |                  | -                  | !              |                                        | !                       | DTIME2<1:0>            |                                       |                | THREL<1:0>                   |

| 90                        |             | ı                           | -                | DETTRQ2U            | DETTRQ2L            | WRTMP2              | SDOSC               | CLTRQ2U           | CLTRQ2L           | CLTMP2            | -                 | MSKTRQ2U        | MSKTRQ2L                      | M SKTMP2        | MSKOSC          | ı                      |                     | -            | -                  | -                 | -                                         | <1:0>            | -                  | MUXCNT         |                                        | 1                       | 2<1:0>                 |                                       |                | :L<1:0>                      |

|                           |             | ı                           | -                | ı                   | DETOSWL             | -                   | DUMMY               | -                 | CL0SWL            | ı                 | CLDUMMY           | -               | MSK0SWL                       | 1               | MSKDUMMY        | ı                      |                     | 1            | -                  | -                 | -                                         | OPE<1:0>         | -                  | ı              |                                        | ı                       | INTIME2<1:0>           |                                       |                | WARREL<1:0>                  |

| R/W                       | В           | æ                           | В                | æ                   | R                   | Ж                   | Я                   | W                 | W                 | W                 | W                 | RW              | RW                            | RW              | RW              | RW                     | RIW                 | Ж            | W                  | RW                | RW                                        | RW               | RW                 | RW             | R                                      | RW                      | RW                     | RW                                    | W              | RW                           |

| Address Register Name R/W | CHIPID      | PINMON                      | INTFAC           | INTREQ1             | INTREQ2             | INTREQ3             | INTREQ4             | INTCL1            | INTCL2            | INTCL3            | INTCL4            | INTMSK1         | INTMSK2                       | INTMSK3         | INTMSK4         | CONF                   | PRTCT               | RSTFAC       | RSTFCL             | RSTFMSK           | PINSET                                    | WDTRG            | WDTIME             | MUXCNT         | QAEVA                                  | TROCNI                  | DCLIM                  | RSTVA                                 | SFTRST         | SENTMP                       |

| Address                   | 00x0        | 0x02                        | 0x03             | 0x04                | 90x0                | 90×0                | 0x07                | 80x0              | 60×0              | 0x0a              | 90x0              | 0x0c            | p <sub>0</sub> x <sub>0</sub> | 0x0e            | 0×0f            | 0x10                   | 0x11                | 0x12         | 0x13               | 0x14              | 0x15                                      | 0x16             | 0x17               | 0x18           | 0x19                                   | 0x1A                    | 0x1B                   | 0x1C                                  | 0x1D           | 0x1E                         |

Note: The initial value of PINMON is set with according to level of the pins. The initial value of "PRTCT" register is unknown.

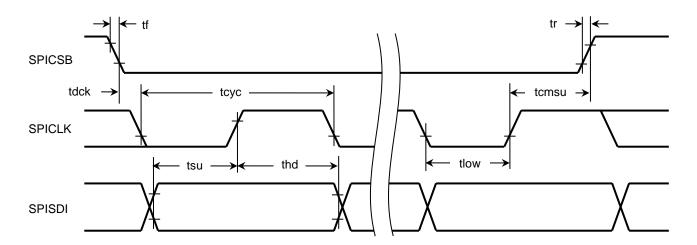

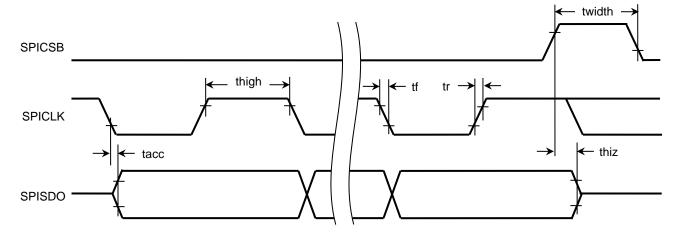

# 4.2.6 Electrical characteristics

| Parameter               | Symbol | Conditions                   | MIN  | TYP | MAX | Unit |

|-------------------------|--------|------------------------------|------|-----|-----|------|

| SPICLK delay            | tdck   | From SPICSB fall             | 400  | -   | -   | ns   |

| SPICLK period           | tcyc   |                              | 800  | -   | -   | ns   |

| High period of SPICLK   | thigh  |                              | 320  | •   | -   | ns   |

| Low period of SPICLK    | tlow   |                              | 320  | -   | -   | ns   |

| Rise time of SPICLK/SDI | tr     |                              | -    | -   | 10  | ns   |

| Fall time of SPICLK/SDI | tf     |                              | -    | •   | 10  | ns   |

| Command set-up          | tcmsu  | From last SPICLK rise        | 400  | 1   | -   | ns   |

| Data set-up             | tsu    | Before SPICLK rise           | 100  | -   | -   | ns   |

| Data hold               | thd    | After SPCLK rise             | 100  | 1   | -   | ns   |

| Data access time        | tacc   | From last address clock fall | -    | 1   | 50  | ns   |

| Read data Hi-Z time     | thiz   |                              | -    | 1   | 50  | ns   |

| High width of SPICSB    | twidth |                              | 2800 | -   | -   | ns   |

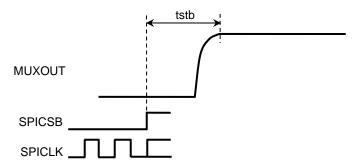

Fig. 4-2-3 SPI write timing

Fig. 4-2-4 SPI read timing

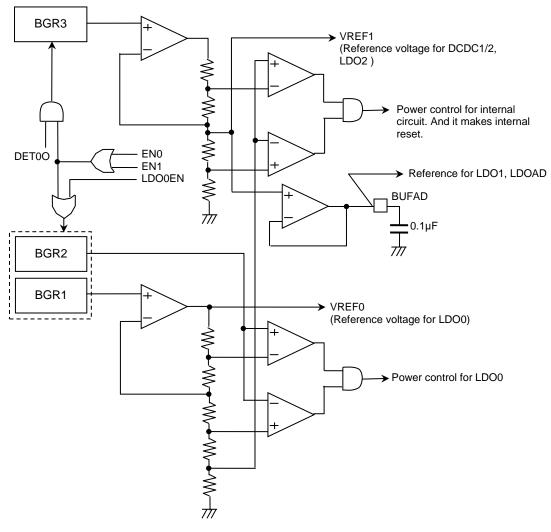

# 4.3 Reference Voltage

Below figure shows simplified reference voltage generator block.

Fig 4-3 REF block diagram

There are three Band Gap Reference (BGR) circuits in the PMIC. In the upper figure, if BGR1 or BGR2 has damage, the PMIC would not power up. And if BGR3 suffers damage, all regulators except LDO0 would not power up.

BUFAD is reference voltage for LDO1 and LDOAD. In order to apply "clear" supply for ADC in microcontroller, 0.1µF capacitor is recommended to connect to ground.

# 4.3.1 Electrical characteristics

Below table shows characteristic of reference output.

$C0=0.1\mu F (ESR=0~0.1\Omega)$

| Parameter      | Symbol | Conditions | MIN   | TYP   | MAX   | Unit |

|----------------|--------|------------|-------|-------|-------|------|

| Output voltage | VBUF   |            | 1.176 | 1.200 | 1.224 | V    |

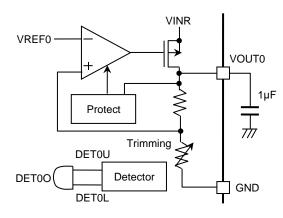

# 4.4 LDO

The PMIC includes four LDOs. Each LDO needs a ceramic capacitor on its output. This allows improvement of output transient response. The gain stage of LDOs except LDO0 is operated with 3.3V generated by LDO0. And each input of power stage is supposed to be connected to DCDC1's output .All LDOs have protection circuit with fold back characteristics.

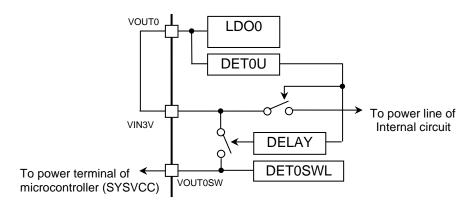

## ♦ LDO0

Typically, the LDO0 output should be used as power supply for internal circuit of the PMIC. The typical output voltage is 3.3V.

It contains output voltage detector.

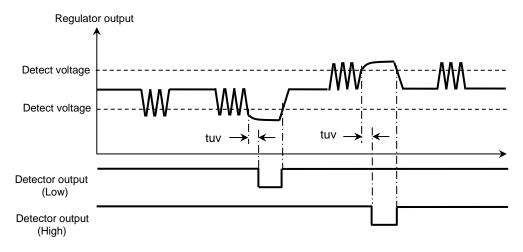

Especially, when over voltage is detected, the power line switch for internal circuit of the PMIC will be cut off supply power. Or when low voltage is detected, it makes reset and initializes internal register. The detect voltages are described in section 4.12.4

Fig. 4-4-1 LDO0 block diagram

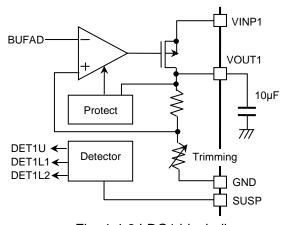

## **♦** LD01

Typically, the LDO1 output should be used as power supply for I/O of microcontroller. The typical output voltage is 5.0V.

It includes output voltage detector. If output voltage comes across unexpected voltage, a flag is set into register and INTOUT asserts low. Especially, when DET1L1 is detected, SUSP is asserted as warning. And when DET1L2 is detected, RSTB is asserted. The detect voltages are described in section 4.12.4.

Fig. 4-4-2 LDO1 block diagram

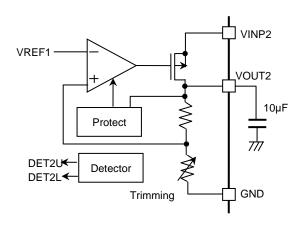

## ♦ LDO2

The LDO2 output is used as power supply for analog part of microcontroller. The typical output voltage is 3.3V.

It includes output voltage detectors. If output voltage comes across unexpected voltage, a flag is set into register and INTOUT asserts low. The detect voltages are described in section 4.12.4.

If over voltage is detected, it forces DCDC1 to enter protect mode. For more detail DCDC1's behavior, please refer to section 4.6.1.

Low voltage detection can be added to reset condition by setting configuration register. When low voltage is detected, reset occurs immediately. Reset asserts low while VOUT2 is below low voltage detection level. After VOUT2 comes up usual output and 12ms passes, the reset is released.

Fig. 4-4-3 LDO2 block diagram

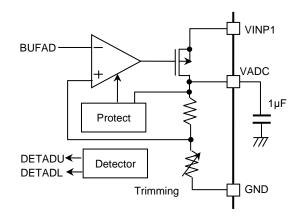

## **♦ LDOAD**

Typically, the LDOAD output is used as power supply for ADC of microcontroller. The typical output voltage is 5.0V.

It includes output voltage detectors. If output voltage comes across unexpected voltage, a flag is set into register and INTOUT asserts low. Actual detect voltage is described in section 4.12.4.

Fig. 4-4-4 LDOAD block diagram

## **♦ VOUT0SW**

VOUT0SW is a pin which applies voltage for retention area of microcontroller. The output voltage comes through internal switch. In order to prevent to apply unusual high voltage of LDO0, the switch is controlled by over voltage detect of LDO0.

If output voltage comes down unexpected low voltage, a flag is set into register and INTOUT asserts low. Actual detect voltage is described in section 4.12.4.

Fig. 4-4-5 Internal switch of VOUT0SW

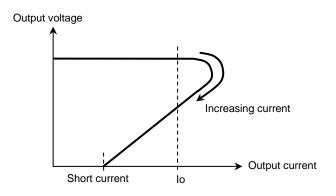

# 4.4.1 Output protect function

When something wrong like solder bridge happens, huge current flows to ground. This may cause heat issue. To prevent flowing over current from the output, all LDOs have a current limit function. Fold-back characteristic is illustrated in below figure.

In this figure, "lo" is a guaranteed current which maintains specified output voltage. For more than "lo" current, the more output current flows, the lower output voltage goes down with decreasing output current.

Fig. 4-4-6 Fold-back characteristic

# 4.4.2 Electrical characteristics

Characteristics noted under conditions GND=0V, unless otherwise noted. The condition is Tj=-40 to 150°C, unless otherwise specified.

# ♦ LDO0

$C0=1\mu F (ESR=0~0.1\Omega)$

| Parameter      | Symbol | Conditions     | MIN   | TYP   | MAX   | Unit |

|----------------|--------|----------------|-------|-------|-------|------|

| Output voltage | Vo0    | Io=0~10mA (DC) | 3.250 | 3.300 | 3.399 | V    |

| Short current  | ls0    | Vo=0V          | -     | -     | 20    | mΑ   |

## **♦** LDO1

C1=10 $\mu$ F (ESR=0 $\sim$ 0.1 $\Omega$ )

| Parameter      | Symbol | Conditions                 | MIN    | TYP  | MAX  | Unit |

|----------------|--------|----------------------------|--------|------|------|------|

|                | Vo11   | lo=0~150mA (DC)            | 4.90   | 5.00 | 5.10 | W    |

| Output voltage | VOII   | lo=150~300mA (DC)          | 4.85 * | -    | 5.10 | V    |

| Output voltage | Vo12   | VINP1=4.95V, Io=150mA (DC) | 4.75   | -    | 4.95 | V    |

|                | Vo13   | VINP1=3.5V, Io=150mA (DC)  | 3.18   | -    | 3.50 | V    |

| Short current  | ls1    | Vo=0V                      | -      | ı    | 80   | mA   |

<sup>\*</sup> Guaranteed by design.

# ♦ LDO2

C2=10 $\mu$ F (ESR=0~0.1 $\Omega$ )

| Parameter      | Symbol | Conditions      | MIN   | TYP   | MAX   | Unit |

|----------------|--------|-----------------|-------|-------|-------|------|

| Output voltage | Vo2    | lo=0~160mA (DC) | 3.234 | 3.300 | 3.366 | V    |

| Short current  | ls2    | Vo=0V           | -     | -     | 80    | mΑ   |

## **♦ LDOAD**

CAD=1 $\mu$ F (ESR=0 $\sim$ 0.1 $\Omega$ )

| 2AD=1pi (LON=0~0.132 | )      |                              |      |      |      |      |

|----------------------|--------|------------------------------|------|------|------|------|

| Parameter            | Symbol | Conditions                   | MIN  | TYP  | MAX  | Unit |

| Output voltage       | VoA1   | 5.0V setting, Io=0~60mA (DC) | 4.95 | 5.00 | 5.05 | V    |

| Short current        | IsA    | Vo=0V                        | -    | -    | 30   | mA   |

# 4.5 Tracker

The PMIC includes two trackers. Each tracker needs a ceramic capacitor on its output. And each input of power stage is supposed to be connected to DCDC1's output.

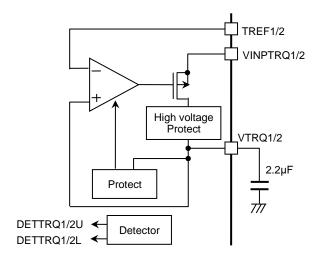

#### ◆ TRACK1/2

TRACK1 and TRACK2 are auxiliary power rails. The output voltage is set by input voltage. Power up control is set via SPI. These trackers have high voltage protect function to prevent reverse current from the output. When outputs touch high voltage like battery, this circuit stops reverse current toward the PMIC.

The trackers have protect function as same as LDO's fold-back characteristic.

Fig. 4-5 Voltage tracker diagram

# 4.5.1 Register

The content of TRACK1/2 setting is only for power control.

# > TRACK1/2 power control

■ Address (TRQCNT): 1AH

| A5 | A4 | A3 | A2 | A1 | A0 |

|----|----|----|----|----|----|

| 0  | 1  | 1  | 0  | 1  | 0  |

■ Register

| D7 | D6 | D5 | D4 | D3 | D2 | D1       | D0       |

|----|----|----|----|----|----|----------|----------|

| -  | -  | •  | 1  | •  | 1  | VTRQ2CNT | VTRQ1CNT |

Setting contents

| Pogistor no   | mo | Control contents | Set | ting  |

|---------------|----|------------------|-----|-------|

| Register name |    | Control contents | 1   | 0     |

| VTRQ2CNT D1   |    | TRACK2 on/off    | On  | Off * |

| VTRQ1CNT D0   |    | TRACK1 on/off    | On  | Off * |

<sup>\*</sup> Default setting

## 4.5.2 Electrical characteristics

Characteristics noted under conditions GND=0V, unless otherwise noted. The condition is Tj=-40 to 150°C, unless otherwise specified.

## **♦ TRACK1**

CTRQ1=2.2 $\mu$ F (ESR=0 $\sim$ 0.1 $\Omega$ )

| Parameter Symbol            |        | ameter Symbol Conditions     |     | TYP  | MAX  | Unit |

|-----------------------------|--------|------------------------------|-----|------|------|------|

| Matching output error dVTR1 |        | 5V input, Io=150mA (DC)      | -10 | -    | 10   | mV   |

| Short current IsTR1         |        | Vo=0V                        | -   | -    | 80   | mΑ   |

| Power on time *             | Trtrq1 | 5V input voltage, 90% output | -   | 1.78 | 2.34 | ms   |

<sup>\*</sup> Guaranteed by design.

# **♦ TRACK2**

CTRQ2=2.2 $\mu$ F (ESR=0~0.1 $\Omega$ )

| Parameter             | Symbol | Conditions                    | MIN | TYP  | MAX  | Unit |

|-----------------------|--------|-------------------------------|-----|------|------|------|

| Matching output error | dVTR2  | dVTR2 5V input, lo=150mA (DC) |     | -    | 10   | mV   |

| Short current         | IsTR2  | Vo=0V                         | -   | -    | 80   | mΑ   |

| Power on time *       | Trtrq2 | 5V input voltage, 90% output  | -   | 1.78 | 2.34 | ms   |

<sup>\*</sup> Guaranteed by design.

# 4.6 DCDC

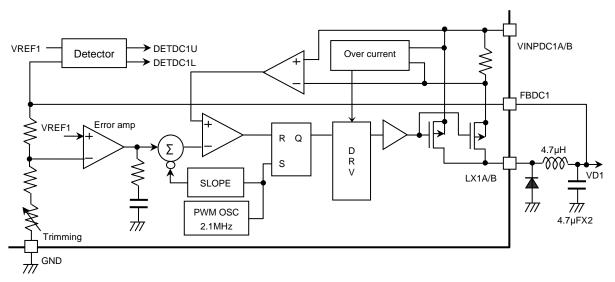

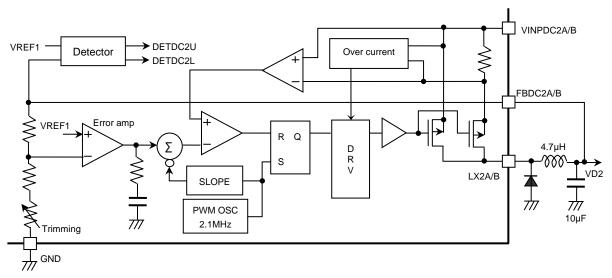

The PMIC includes two DCDCs. Internal high-side PMOS power stages are implemented in each DCDC to reduce the PCB space. Each DCDC needs schottky diode, inductor and ceramic capacitor on its output like the diagram. Analog processing circuit except power PMOS is operated with the 3.3V generated by LDO0. Two DCDCs include output voltage detectors. The detectors monitor over voltage and lower voltage, and have output protect function and over current protection.

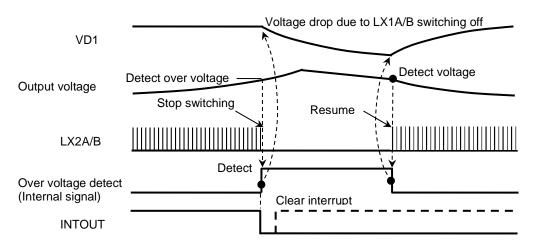

## ◆ DCDC1

The DCDC1 operates with current mode control. And it is supposed to supply power as intermediate power supply. This means all regulators' power input should be connected to DCDC1's output. (Except LDO0) The DCDC1 includes output voltage detector. If output voltage comes across unexpected voltage, the flag is set into register and INTOUT signal occurs. Actual detect voltage is described in section 4.12.4. Hereafter, VD1 refers to as the output of DCDC1.

Fig.4-6-1 DCDC1 block diagram

## **♦** DCDC2

The DCDC2 also operates with current mode. The DCDC2 is supposed to supply power to microcontroller's core circuit. The DCDC2 includes output voltage detector. If output voltage comes across unexpected voltage, the flag is set into register and INTOUT signal occurs as well. Actual detect voltage is described in section 4.12.4.

Hereafter, VD2 refers to as the output of DCDC2.

Fig.4-6-2 DCDC2 block diagram

# 4.6.1 Output protect function

To operate the PMIC safety, interval operation would start in the case of output abnormal conditions. Each DCDC operation is as follows.

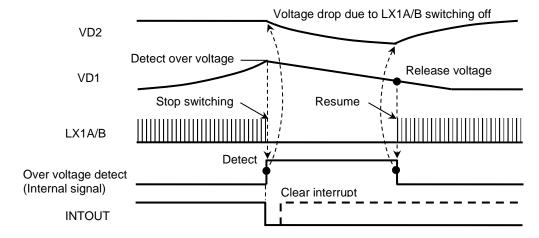

#### ◆ DCDC1

When DCDC1 fall into unusual condition, DCDC1 enters to protect mode.

The protection circuit monitors output current and output voltage. In the case that over voltage is detected on DCDC1, it would force to stop the DCDC1's and DCDC2's switching. When over current or low voltage are detected with taking over detect mask time, then DCDC1 would enter interval operation. The mask time of over current detection can be set via SPI. During protect mode, the DCDC1 tries to resume its operation regularly. The interval time of resuming can be set via SPI as well. When root cause of unusual condition is taken away, the DCDC1 comes to operate normally.

And when over voltage is detected in either DCDC2 or LDO2, DCDC1 would operate in protect mode as well. Before DCDC1's operation comes into protect mode, INTOUT asserts low.

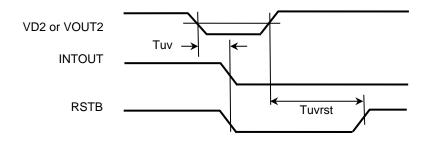

The operation timing is shown in below figure. And detect mask times are described in next table.

Fig.4-6-3 DCDC1 protect function behavior 1

Fig.4-6-4 DCDC1 protect function behavior 2

Table 4-6-1 Detect mask time

| Over current detect | Low voltage detect | DCDC2 detect |

|---------------------|--------------------|--------------|

| Variable            | 92µs               | 92µs         |

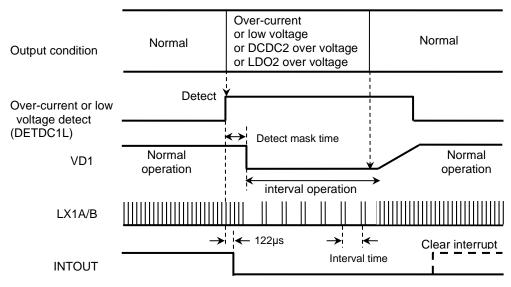

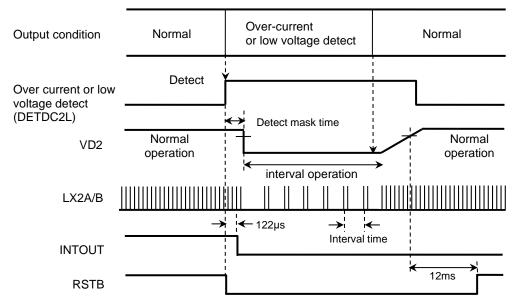

## **♦** DCDC2

DCDC2's protect operation is almost same as DCDC1's.

The protection circuit monitors load current and output voltage. When over current or low voltage is detected with taking over detect mask time, then DCDC2 would enter interval operation. The mask time of over current detection can be set via SPI. During protect mode, the DCDC2 tries to resume its operation regularly. The interval time of resuming can be also set via SPI. In the case of over voltage is detected, it would force to stop switching of both DCDC1 and DCDC2. Before DCDC2's operation comes into protect mode, INTOUT asserts low.

The operation timing is shown in below figure. And detect mask times are described in below table.

Low voltage detection can be added to reset condition by setting configuration register.

When low voltage is detected, reset occurs immediately. Reset asserts low while VD2 is below low voltage detection level. After VD2 comes up usual output and 12ms passes, the reset is released.

Fig.4-6-5 DCDC2 protect function behavior 1 (In case of DL2RSTB bit in CONF register is set "1".)

Fig.4-6-6 DCDC2 protection behavior 2

Table 4-6-2 Protect detect mask time

| Over current detect | Low voltage detect |

|---------------------|--------------------|

| Variable            | 92µs               |

# 4.6.2 Register

The contents of protect function setting are described here.

# > DCDC protection mode setting

■ Address (DCLIM) : 1BH

| A5 | A4 | A3 | A2 | A1 | A0 |

|----|----|----|----|----|----|

| 0  | 1  | 1  | 0  | 1  | 1  |

■ Register

| 1 | 9.0.0. |         |       |        |        |         |       |        |

|---|--------|---------|-------|--------|--------|---------|-------|--------|

|   | D7     | D6      | D5    | D4     | D3     | D2      | D1    | D0     |

|   | INTIM  | E2(1:0) | DTIME | 2(1:0) | INTIME | E1(1:0) | DTIME | 1(1:0) |

# Setting contents

Interval time and over current detect mask time for DCDC2.

| INTIME2(1:0) |    | Interval time |  |  |  |  |

|--------------|----|---------------|--|--|--|--|

| D7           | D6 | Interval time |  |  |  |  |

| 0            | 0  | 15.6ms        |  |  |  |  |

| 0            | 1  | 31.2ms *      |  |  |  |  |

| 1            | 0  | 124.9ms       |  |  |  |  |

| 1            | 1  | 249.9ms       |  |  |  |  |

| DTIME | 2(1:0) | Detect mask time |  |  |  |  |  |

|-------|--------|------------------|--|--|--|--|--|

| D5    | D4     | Detect mask time |  |  |  |  |  |

| 0     | 0      | 122µs *          |  |  |  |  |  |

| 0     | 1      | 122µs            |  |  |  |  |  |

| 1     | 0      | 610µs            |  |  |  |  |  |

| 1     | 1      | 1098µs           |  |  |  |  |  |

<sup>\*</sup> Default setting

Interval time and over current detect mask time for DCDC1.

| INTIME1(1:0) |  | 1(1:0) | Interval time |  |  |  |  |

|--------------|--|--------|---------------|--|--|--|--|

| D3           |  | D2     | interval time |  |  |  |  |

| 0            |  | 0      | 15.6ms        |  |  |  |  |

| 0            |  | 1      | 31.2ms *      |  |  |  |  |

| 1            |  | 0      | 124.9ms       |  |  |  |  |

| 1            |  | 1      | 249.9ms       |  |  |  |  |

| DTIME1(1:0) |    | Detect mask time |  |  |  |  |  |

|-------------|----|------------------|--|--|--|--|--|

| D1          | D0 | Detect mask time |  |  |  |  |  |

| 0           | 0  | 122µs *          |  |  |  |  |  |

| 0           | 1  | 122µs            |  |  |  |  |  |

| 1           | 0  | 610µs            |  |  |  |  |  |

| 1           | 1  | 1098µs           |  |  |  |  |  |

<sup>\*</sup> Default setting

Note1: This register is not initialized by RSTB.

# 4.6.3 Electrical characteristics

Characteristics noted under conditions, GND=0V, unless otherwise noted. The condition is Tj=-40 to 150°C, unless otherwise specified.

## ◆ DCDC1

$Co=4.7\mu Fx2$  (ESR=0.0~0.1 $\Omega$ ), L=3.3/4.7 $\mu$ H

| Parameter      | Symbol | Conditions       | MIN  | TYP  | MAX  | Unit |

|----------------|--------|------------------|------|------|------|------|

| Output voltage | VoDC1  | Io=0~1000mA (DC) | 5.40 | 5.70 | 6.00 | V    |

| OSC frequency  | Fosc1  |                  | 1890 | 2100 | 2310 | kHz  |

## **♦** DCDC2

Co=10 $\mu$ F (ESR= $0.0\sim0.1\Omega$ ), L= $3.3/4.7\mu$ H

| Parameter      | Symbol | Conditions      | MIN   | TYP  | MAX   | Unit |

|----------------|--------|-----------------|-------|------|-------|------|

| Output voltage | VoDC2  | Io=0~700mA (DC) | 1.225 | 1.25 | 1.275 | V    |

| OSC frequency  | Fosc2  |                 | 1890  | 2100 | 2310  | kHz  |

# 4.7 Power Rail Sequence

When battery voltage is applied to the PMIC, the LDO0 rises up first. After the LDO0 rises up, the other regulators are powered up in the sequence automatically. Therefore, user doesn't need to consider power rail sequence at all. After all regulators rise up, reset signal is released.

# 4.7.1 Power up sequence

After the PMIC is applied supply voltage, all regulators rise up automatically. Difference of rise up time between regulators is suitable for RENESAS MCUs.

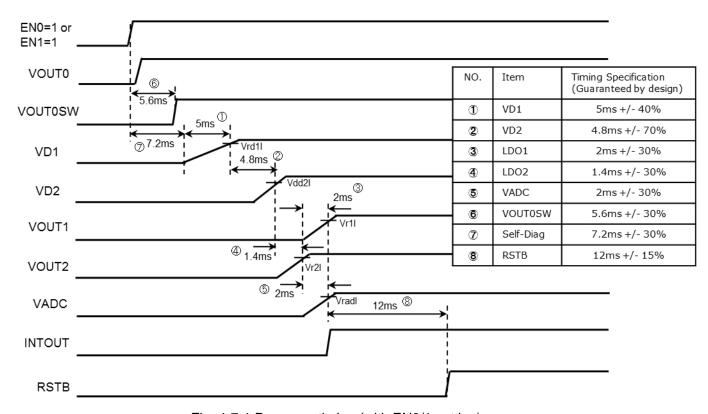

# ◆ Power up with using EN0 or EN1

While supply voltage is applied, the PMIC can be controlled by EN0 or EN1 pin. After EN0 or EN1 is entered, self-diagnosis execution starts first. The order of each regulator's rising is controlled by internal sequencer. After all regulators rise up, interrupt signal is released. Further 12ms passes, reset signal is released as well. Each timing specification is specified in the below table and guaranteed by design.

Fig. 4-7-1 Power up timing (with EN0/1 setting)

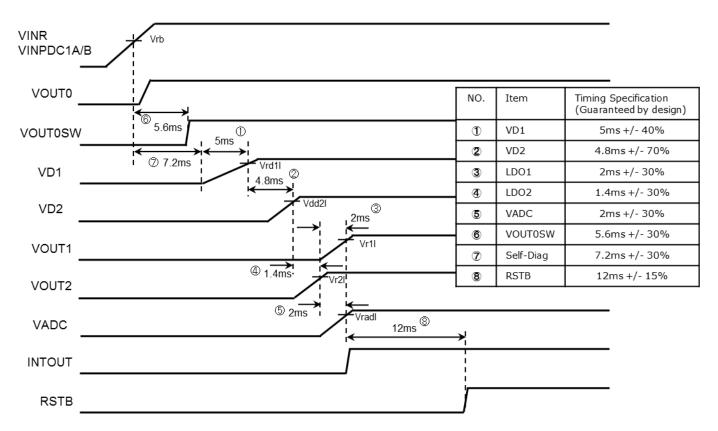

# ◆ Power up without using EN0 or EN1

When EN0 and/or EN1 are connected to supply voltage and supply voltage comes up, power up sequence starts automatically. Power up sequence behavior is same as using EN0 or EN1. Each timing specification is specified in the below table and guaranteed by design.

Fig. 4-7-2 Power up timing (Supply power coming up)

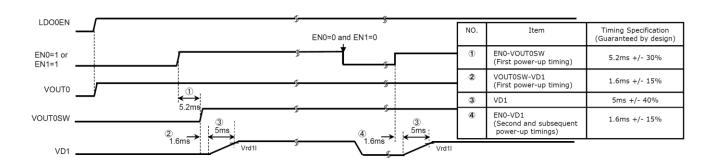

# ◆ Power up after LDO0EN

While supply voltage is applied to the PMIC, only LDO0 can rise up with using LDO0EN control. The PMIC executes self-diagnosis after either EN0 or EN1 rises. After either EN0 or EN1 set up, self-diagnosis of detectors are executed and power-up sequence starts. Each timing specification is specified in the below table and guaranteed by design.

Fig. 4-7-3 Power up timing (Supply power coming up)

Note: Please make EN0 or EN1 high in the condition of VINR > Vrb. Otherwise, the state is shifted to power down.

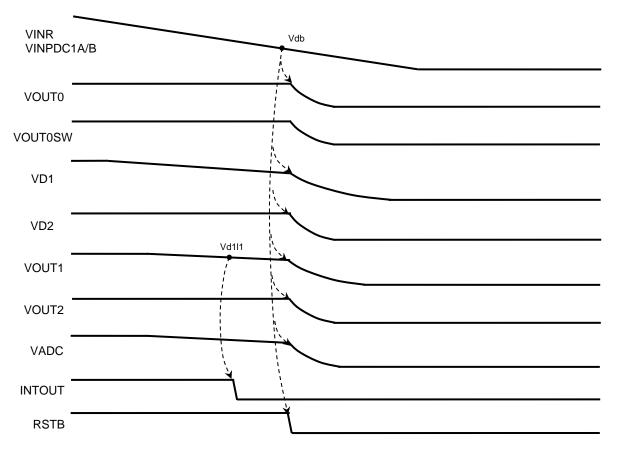

# 4.7.2 Power down sequence

When the PMIC powers down, all regulators fall down automatically. Difference of fall down time between regulators is suitable for RENESAS MCUs.

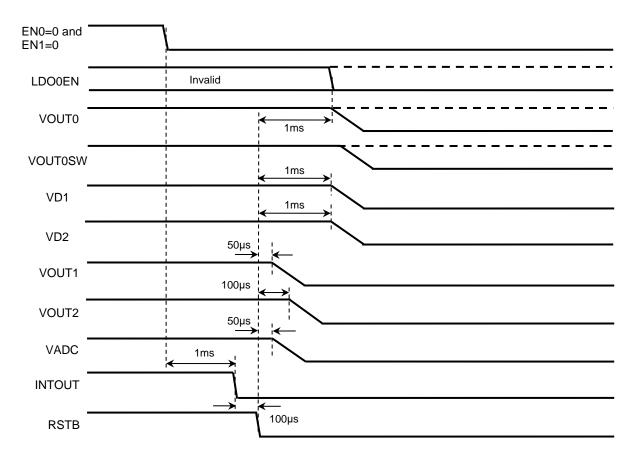

# ◆ Power down with using EN0 or EN1

When the PMIC is stopped operating by EN0 or EN1, interrupt and reset signal would be asserted. After the PMIC sets RSTB to low, power down sequence starts automatically. If the system needs to maintain VOUT0 output, LDO0EN should be set high before LDO0 power down. The time deviation in below figure is +/-10%. That value is guaranteed by design.

Fig. 4-7-4 Power down timing (with EN0/1 setting)

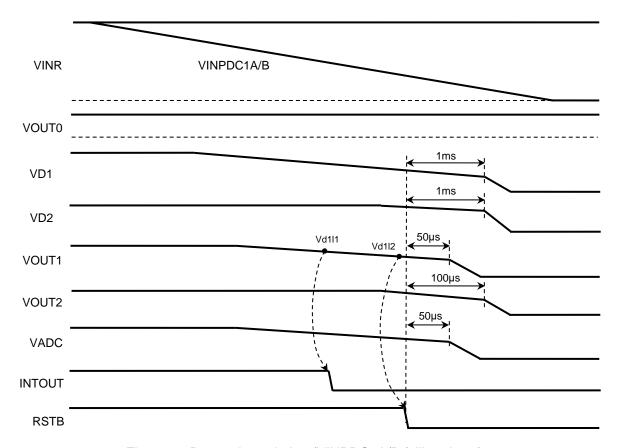

# ◆ Power down without using EN0 or EN1

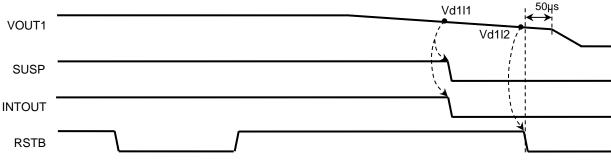

Output behavior in low supply voltage is shown in below figure. Even though the supply voltage of the PMIC goes down lower than the output voltage, regulators can generate output voltage. But output voltage becomes to be almost same as supply voltage.

When supply voltage falls down and LDO1 goes across Vd1I1, the PMIC asserts SUSP signal as a warning. Further the supply voltage falls down across Vdb, the PMIC asserts RSTB and all regulators except LDO0 fall down.

Fig. 4-7-5 Power down timing (Supply voltage falling down)

# ♦ Power down except LDO0

LDO0 and output part of DCDC1 have terminal for supply voltage respectively. Below figure shows the behavior of cutting off supply voltage for DCDC1. Since supply voltage maintains for the LDO0, the output of LDO0 generates its output. On the other hand, supply voltage of DCDC1 is cut off, the outputs of regulators which powered by DCDC1 fall down. Turn-off time of regulators is controlled by the sequencer. The time deviation in below figure is +/-10%. That value is guaranteed by design.

Fig. 4-7-6 Power down timing (VINPDC1A/B falling down)

# 4.8 Watchdog (WD) Timer

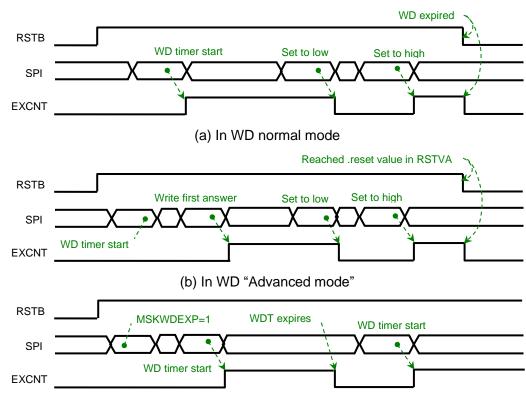

The watchdog (WD) timer can be used for monitoring the system health to prevent a runaway operation. In order to refresh WD timer (WDT), a trigger via SPI or on WDI pin is needed.

Further, to improve functional safety, it can be done with logical operation to monitor microcontroller's operation. And also watchdog time can be set via SPI.

In order to operate WD, WDENB should be set low at "P/U sequence" state. Once WD starts its operation, WDENB setting can't stop WD function. WDENB setting in the PMIC can be set in any state except "Normal" state.

## ♦ WDI pin or SPI control

There are two ways to start WD operating or refresh the timer. One way is to use WDI pin, and the other one is to use SPI. It can select WDI pin or SPI by setting configuration register. To use WDI pin is default setting.

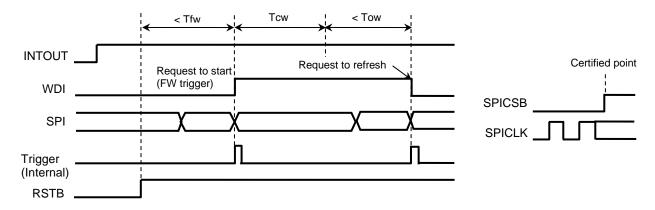

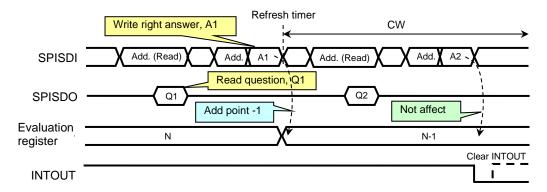

# 4.8.1 Window WDT

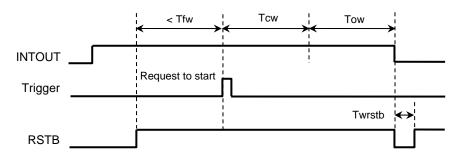

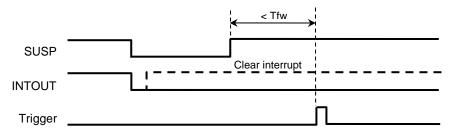

Window WDT is implemented in the PMIC. It needs a trigger to start WD operation during first window (FW) in "Normal" state. If the trigger is not executed, a reset pulse occurs and the PMIC wait for a FW trigger again. After WD starts operating in "System monitor" state, a trigger should not be executed during Close Window (CW). If a trigger is executed, INTOUT would be asserted and enter Open Window (OW). A trigger should be executed to refresh the timer during OW. If the refreshing is not executed within designated time, a reset pulse occurs. While WDT is operating and when SUSP is asserted, WDT would stop its operating. And when SUSP is released, then WDT resumes from "Normal" state.

CW time and OW time are programmed via SPI.

# 4.8.2 WDT operation

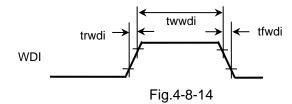

Detail WD operation is described in this section. In order to clear the timer, toggling on WDI or SPI is needed.

## Operation in normal

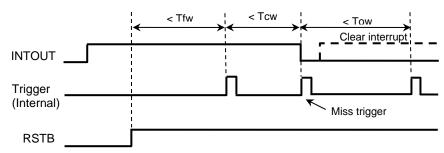

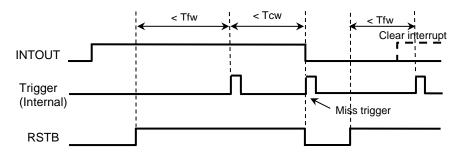

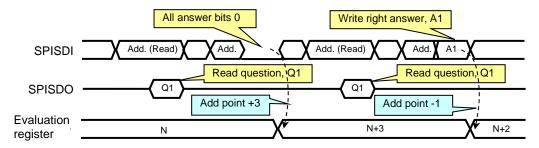

Below figure shows normal operation of WDT when the trigger from WDI pin or SPI is entered within designated time. Certified point as a trigger is the changing point of WDI or rising edge of SPICSB.

Fig.4-8-1 WDT normal operation

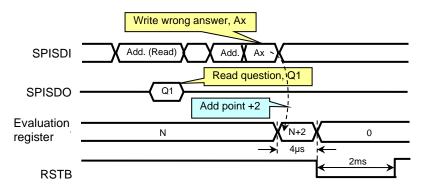

# **♦** Behaviors in unusual operation

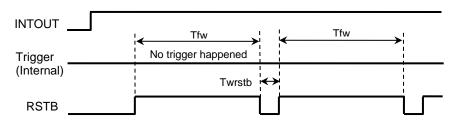

When the trigger is not executed and the timer expires, then a reset occurs.

# (1) No trigger in FW

When the trigger is not entered in FW, reset would occur. After that, if the triggers aren't entered, reset occurs regularly.

Fig.4-8-2 No trigger in FW

# (2) A Trigger in CW

When the trigger is entered in CW, INTOUT would assert low.

Fig.4-8-3 Trigger in CW 1

And when the configuration register is set to make reset, WD behavior is show in below figure.

Fig.4-8-4 Trigger in CW 2

# (3) No trigger in OW

When the trigger is not entered in OW, the timer expires and reset would be asserted. After reset is released, WD starts from FW again and the PMIC maintains asserting low so that microcontroller is able to know that the reset is caused by timer expire.

Fig.4-8-5 No trigger in OW

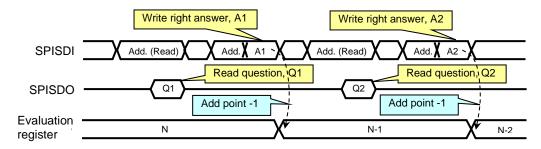

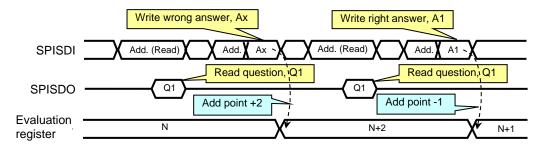

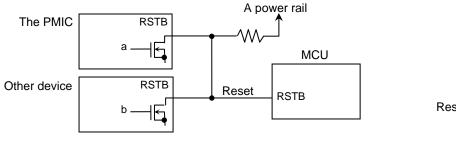

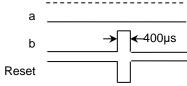

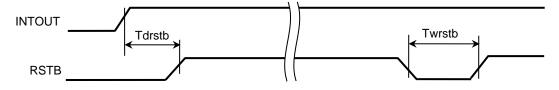

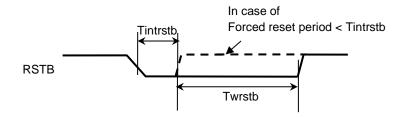

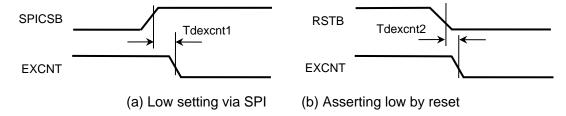

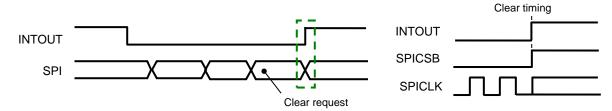

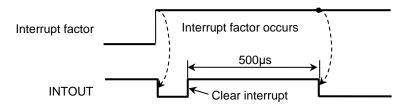

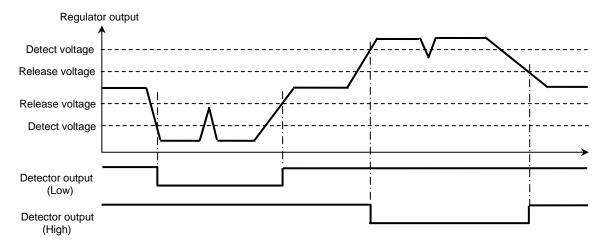

# Suspend WD operating