#### RAA214048

Ultra-Low Dropout, Low VIN, Ultra-Low Noise, High PSRR, 4A LDO

The RAA214048 is an ultra-low noise, high PSRR, low-dropout regulator capable of sourcing up to 4A of load current with only 250mV dropout voltage. It operates from an input voltage of 1.1V for low-voltage applications to 6.5V.

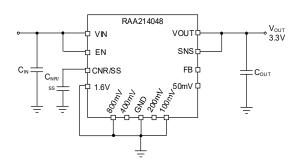

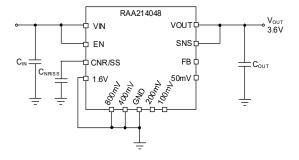

The LDO output voltage can be programmed from 0.8V to 3.95V using voltage setting pins on the IC in 50mV steps, eliminating the need for traditional external feedback resistors and saving PCB space. External feedback resistors can still be used for higher output voltage applications, allowing the output voltage to be programmed anywhere from 0.8V to 5.1V.

The RAA214048 has an ultra-low output noise and high PSRR without a feed-forward capacitor. It only requires a single  $1\mu\text{F}$  noise-reduction capacitor to achieve  $7\mu\text{VRMS}$  output noise, making it great for noise-sensitive and space-constrained applications.

The LDO features a ±1% output voltage accuracy, input voltage, and BIAS voltage UVLO with hysteresis, enable control, internal current limit, over-temperature shutdown protection with hysteresis, power-good indication, voltage BIAS pin, and fast-start up.

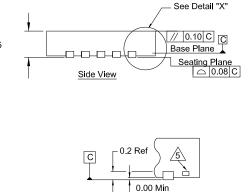

The RAA214048 is stable with a minimum 22µF ceramic output capacitor and is available in a 20-Ld 3.5mm×3.5mm QFN package.

#### **Features**

- Maximum dropout: 250mV at 4A with BIAS

- Output voltage accuracy: ±1%

- Ultra-low output noise: 7µVRMS

- Input voltage range:

- Without BIAS: 1.4V to 6.5V

- With BIAS: 1.1V to 6.5V

- Output voltage range:

- Using PCB layout and voltage set pins: 0.8V to 3 95V

- External FB resistors: 0.8V to 5.1V

- BIAS voltage range: 3V to 6.5V

- Max operating load current: 4A

- High PSRR at V<sub>HEADROOM</sub> = 0.5V

- 100kHZ: 35dB at 4A

- Enable control and power-good indication

- Overcurrent, short-circuit and over-temperature fault protection

- Excellent load transient response

## **Applications**

- Sensor, imaging, and radar

- Test and measurement

- Instrumentation, medical, and audio

- RF power supplies

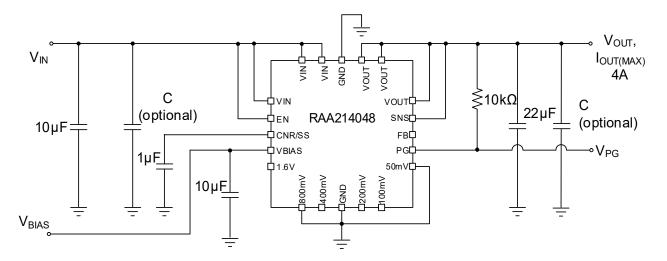

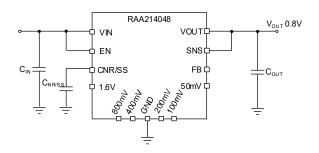

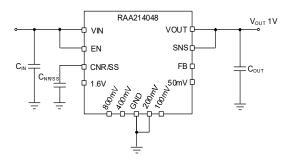

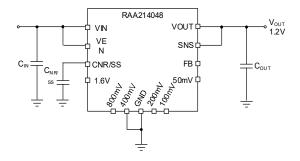

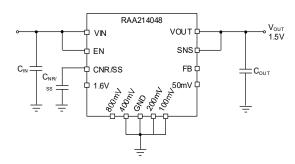

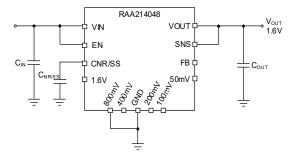

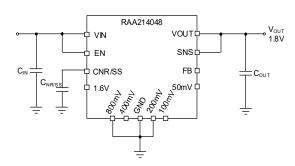

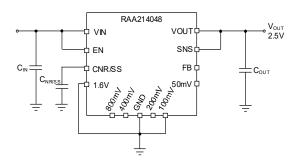

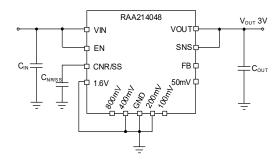

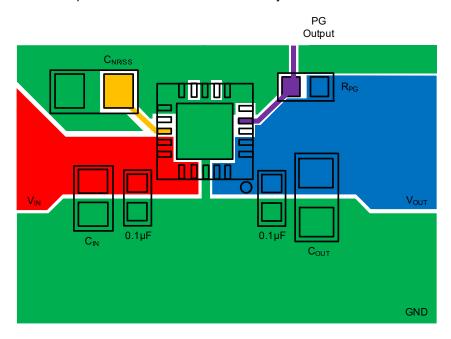

Figure 1. Typical Application Schematic

# **Contents**

| 1.  | Over   | view                                      | . 3 |

|-----|--------|-------------------------------------------|-----|

|     | 1.1    | Block Diagram                             | . 3 |

| 2.  | Pin Ir | nformation                                | . 4 |

|     | 2.1    | Pin Assignments                           | . 4 |

|     | 2.2    | Pin Descriptions                          | . 4 |

| 3.  | Spec   | ifications                                | . 6 |

|     | 3.1    | Absolute Maximum Ratings                  | . 6 |

|     | 3.2    | Recommended Operating Conditions          |     |

|     | 3.3    | Thermal Specifications                    |     |

|     | 3.4    | Electrical Specifications                 | . 7 |

| 4.  | Typic  | eal Performance Curves                    | 11  |

|     | 4.1    | PSRR                                      | 11  |

|     | 4.2    | Output Noise                              |     |

|     | 4.3    | Start-Up                                  | 14  |

|     | 4.4    | Load Transient Response                   | 15  |

|     | 4.5    | Short-Circuit                             | 15  |

|     | 4.6    | Dropout Voltage                           | 16  |

|     | 4.7    | Load and Line Regulation                  |     |

|     | 4.8    | Other Typical Performance Curves          | 19  |

| 5.  | Appli  | ications Information                      | 20  |

|     | 5.1    | Overview                                  | 20  |

|     | 5.2    | Theory of Operation of NMOS LDOs          | 20  |

| 6.  | Func   | tional Description                        | 21  |

|     | 6.1    | Low Output Noise                          | 21  |

|     | 6.2    | High Power-Supply Ripple-Rejection (PSRR) | 21  |

|     | 6.3    | VBIAS, VIN, and VEN Sequencing            | 22  |

|     | 6.4    | UVLO                                      | 22  |

|     | 6.5    | Power-Good (PG) Indication                | 23  |

|     | 6.6    | Enable Control                            | 23  |

|     | 6.7    | Internal Current Limit (ILIM)             |     |

|     | 6.8    | Thermal Protection                        |     |

|     | 6.9    | Output Capacitor Automatic Discharge      |     |

|     | 6.10   | BIAS                                      |     |

|     | 6.11   | Output Accuracy                           |     |

| 7.  | Appli  | ication Requirements                      |     |

|     | 7.1    | Input Voltage                             |     |

|     | 7.2    | Programming the Output Voltage            |     |

|     | 7.3    | Bias Voltage                              |     |

|     | 7.4    | External Bypass Capacitor Selection       |     |

|     | 7.5    | Power Dissipation and Thermals            |     |

| 8.  | Layo   | ut Guidelines                             | 33  |

| 9.  | Pack   | age Outline Drawing                       | 34  |

| 10. | Orde   | ring Information                          | 35  |

| 11. | Revis  | sion History                              | 35  |

|     |        | •                                         |     |

## 1. Overview

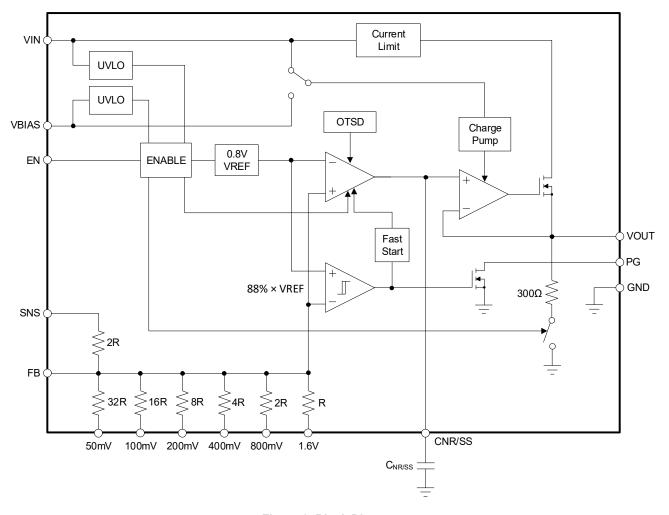

# 1.1 Block Diagram

Figure 2. Block Diagram

# 2. Pin Information

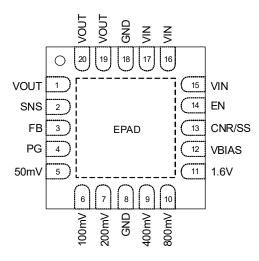

# 2.1 Pin Assignments

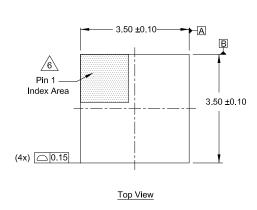

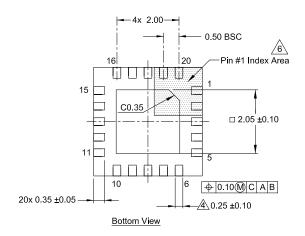

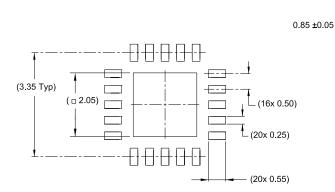

Figure 3. Pin Assignments - Top View

# 2.2 Pin Descriptions

| Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 19, 20  | VOUT     | VOUT are the output pins that supply power to the load. The recommended operating output voltage for these pins is 0.8V to 5.1V. The maximum current that these pins can source is 4A. Renesas recommends tying all three pins to the same output PCB plane. A minimum 22µF ceramic capacitor is required from these pins to GND for stable operation. Place the output capacitor as close as possible to the OUT pins. Add an optional 100nF bypass capacitor parallel with the 22µF to reduce higher-frequency noise and supply higher frequency load currents if required. See Programming the Output Voltage for programming the output voltage and Output Capacitor (COUT) for selecting COUT. |

| 2          | SNS      | SNS is the output voltage sense pin. Connect this pin to the OUT pins (1, 19, 20) if the output voltage set pins (50mV, 100mV, 200mV, 400mV, 800mV, and 1.6V pins) are used to program the output voltage. If external feedback resistors are used to program the output voltage, leave this pin floating.                                                                                                                                                                                                                                                                                                                                                                                          |

| 3          | FB       | FB is the output voltage feedback pin. This pin is internally connected to the error amplifier and is compared with 0.8V of the voltage reference circuitry. The voltage divider formed around this pin with either the internal or external feedback resistors programs the LDO output voltage. See Internal Feedback Resistors and Output Voltage Set Pins for using the internal FB resistors and External Feedback Resistors for using the external FB resistors to program the output voltage.                                                                                                                                                                                                 |

| 4          | PG       | PG is the power good pin. This pin monitors the output voltage and signals other circuit ICs in a system connected to this pin when the output voltage is at or near its programmed value. When the output voltage exceeds -12% of its programmed value, this pin pulls LOW, indicating a fault. When the output voltage is within -12% of its programmed value, the pin is open circuit (high Z) without a pull-up resistor. Therefore, to ensure a proper logic HIGH to devices connected to this pin, Renesas recommends tying a $10k\Omega$ (minimal) pull-up resistor. If this pin is not being used, it can be left floating.                                                                 |

| Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 5          | 50mV     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 6          | 100mV    | These are the output voltage set pins. These pins can either be grounded or left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 7          | 200mV    | Connecting any pin to ground increases the output voltage by the value of the pin name.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 9          | 400mV    | With all the pins left floating, the output voltage equals V <sub>REF</sub> , which is 0.8V. With all the pins grounded, the output voltage is 3.95V. See Internal Feedback Resistors and Output Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 10         | 800mV    | Set Pins for more detail on how to use these pins to program the output voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 11         | 1.6V     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 8, 18      | GND      | GND is the ground pin. Tie this pin to the PCB ground plane and the EPAD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 12         | VBIAS    | VBIAS is the BIAS pin. This pin enables low-input voltage ( $V_{IN} < 1.4V$ ) to reduce power dissipation for low-voltage applications. It also improves DC and AC performance for $V_{IN} \le 1.4V$ . A minimum 1µF capacitor must be connected between this pin and GND. Place this capacitor as close as possible to the BIAS pin. If not using this pin, it can be left floating or tied to GND without impacting performance.                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 13         | CNR/SS   | CNR/SS is the noise-reduction and soft-start pin. A 100nF capacitor is required between this pin and GND for LDO stability and to help reduce low-to-mid frequency noise and increase low-to-mid frequency PSRR. For optimal noise/PSRR performance, Renesas recommends using a 1 $\mu$ F capacitor on this pin. Using a larger capacitor can increase the soft-start time to reduce in-rush current. See Noise-Reduction and Soft-Start Capacitor ( $C_{NR/SS}$ ) for more details about selecting $C_{NR/SS}$ .                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| 14         | EN       | EN is the enable pin. This pin can enable or disable the LDO. If the voltage on this pin is LOW, the LDO is disabled and shuts down. When the voltage is HIGH, the LDO is enabled. <i>Important</i> : This pin must not be left floating. Instead, tie it to the VIN pins for automatic enabling. See Enable Control for more details about the EN function.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 15, 16, 17 | VIN      | VIN are the input voltage pins that supply power to the LDO and the LDO load. The recommended operating input voltage for these pins is 1.4V to 6.5V without BIAS and down to 1.1V with BIAS. Renesas recommends tying all three pins to the same input PCB plane. A minimum 10µF ceramic capacitor is required between these pins to GND to minimize the impedance of the input supply. The input capacitor also helps reduce high-frequency input noise. Place this capacitor as close as possible to the VIN pins. Add an optional 100nF bypass capacitor in parallel with the 10µF to reduce higher-frequency input noise and further reduce input supply impedance supply if required. See Input Capacitor (C <sub>IN</sub> ) for more details about selecting C <sub>IN</sub> . |  |  |  |  |  |  |

| -          | EPAD     | EPAD is the exposed pad on the bottom of the package. Solder the exposed pad to the PCB ground plane and tie it directly to pins 8 and 18 to ensure the best electrical and thermal performance. See Layout Guidelines for more layout guidelines for this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

## 3. Specifications

# 3.1 Absolute Maximum Ratings

**Caution:** Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

| Parameter <sup>[1]</sup>                        | Minimum | Maximum | Unit |

|-------------------------------------------------|---------|---------|------|

| VIN, EN, BIAS                                   | -0.3    | +7.5    | V    |

| VOUT, PG, NR/SS                                 | -0.3    | +6.5    | V    |

| 50mV, 100mV, 200mV, 400mV, 800mV, 1.6V          | -0.3    | +6.5    | V    |

| FB                                              | -0.3    | +3.3    | V    |

| Maximum Junction Temperature                    | -40     | +125    | °C   |

| Maximum Storage Temperature Range               | -65     | +150    | °C   |

| Human Body Model (Tested per JS-001-2023)       | -       | 2       | kV   |

| Charged Device Model (Tested per JS-002-2022)   | -       | 750     | V    |

| Latch-Up (Tested per JESD78E; Class 2, Level A) | -       | 100     | mA   |

<sup>1.</sup> All voltages referenced to GND unless otherwise specified.

## 3.2 Recommended Operating Conditions

| Parameter <sup>[1]</sup>                       | Minimum | Maximum | Unit |

|------------------------------------------------|---------|---------|------|

| Supply Voltage, V <sub>IN</sub>                | 1.1     | 6.5     | V    |

| Bias Voltage, V <sub>BIAS</sub>                | 3       | 6.5     | V    |

| Enable Voltage, V <sub>EN</sub>                | 0       | 6.5     | V    |

| Output Voltage, V <sub>OUT</sub>               | 0.8     | 5.1     | V    |

| Output Current, I <sub>OUT</sub>               | 0       | 4       | А    |

| Output Capacitor, C <sub>OUT</sub>             | 22      | -       | μF   |

| Input Capacitor, C <sub>IN</sub>               | 10      | -       | μF   |

| Bias Capacitor, C <sub>BIAS</sub>              | 1       | -       | μF   |

| Power-Good Pull-Up Resistance, R <sub>PG</sub> | 10      | -       | kΩ   |

| Noise Reduction Capacitor, C <sub>NR/SS</sub>  | 0.1     | -       | μF   |

| Junction Temperature                           | -40     | +125    | °C   |

<sup>1.</sup> All voltages referenced to GND unless otherwise specified.

# 3.3 Thermal Specifications

| Parameter          | Package               | Symbol              | Conditions          | Typical<br>Value | Unit |

|--------------------|-----------------------|---------------------|---------------------|------------------|------|

| Thermal Pesistance | 20-Ld 3.5mm×3.5mm QFN | θ <sub>JA</sub> [1] | Junction to ambient | 42               | °C/W |

| Thermal Resistance | Package               | $\theta_{JC}^{[2]}$ | Junction to case    | 4.5              | °C/W |

<sup>1.</sup>  $\theta_{JA}$  is measured in free air with the component mounted on a high-effective thermal conductivity test board with direct attach features. See TB379 for details.

<sup>2.</sup> For  $\theta_{JC}$ , the case temperature location is the center of the exposed metal pad on the package underside.

# 3.4 Electrical Specifications

Operating conditions unless otherwise noted: T<sub>J</sub> = -40°C to +125°C, V<sub>IN</sub> = V<sub>OUT</sub>+400mV or 1.4V whichever is greater, V<sub>BIAS</sub> = OPEN, V<sub>OUT</sub> = 0.8V, V<sub>EN</sub> = 5V, I<sub>OUT</sub> = 0mA, C<sub>IN</sub> = 47||10||10µF, C<sub>OUT</sub> = 47||10||10µF, C<sub>NR/SS</sub> = 100nF.

| Parameter                                  | Symbol                               | Test Conditions                                                                                          | Min <sup>[1]</sup> | Тур. | Max <sup>[1]</sup> | Unit  |  |  |

|--------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------|------|--------------------|-------|--|--|

| Input                                      |                                      | •                                                                                                        | •                  |      |                    |       |  |  |

| Input Voltage Range                        | $V_{IN}$                             | With V <sub>BIAS</sub> between 3V and 6.5V                                                               | 1.1                | -    | 6.5                | V     |  |  |

|                                            |                                      | Without V <sub>BIAS</sub>                                                                                | 1.4                | -    | 6.5                |       |  |  |

| Input Voltage UVLO without BIAS            | $V_{IN\_UVLO}$                       | -                                                                                                        | -                  | 1.33 | 1.4                | V     |  |  |

| Input Voltage UVLO Hysteresis without BIAS | V <sub>IN_UVLO_HYS</sub>             | -                                                                                                        | -                  | 100  | -                  | mV    |  |  |

| Input Voltage UVLO with BIAS               | V <sub>IN_UVLO(BIAS)</sub>           | V <sub>IN</sub> Rising, V <sub>BIAS</sub> = 3V                                                           | -                  | 1    | 1.1                | V     |  |  |

| Input Voltage UVLO Hysteresis with BIAS    | V <sub>IN_UVLO_HYS(BIAS)</sub>       | V <sub>BIAS</sub> = 3V                                                                                   | -                  | 40   | -                  | mV    |  |  |

| BIAS voltage UVLO                          | $V_{BIAS\_UVLO}$                     | -                                                                                                        | -                  | -    | 3.0                | ٧     |  |  |

| BIAS voltage UVLO Hysteresis               | V <sub>BIAS_UVLO_HYS</sub>           | -                                                                                                        | -                  | 100  | -                  | mV    |  |  |

| V <sub>IN</sub> Quiescent Current          | I <sub>Q(VIN)</sub>                  | $I_{OUT} = 0A$ , $V_{IN} = 1.4V$ , $V_{OUT} = 0.8V$ , PG is floating                                     | -                  | 0.9  | -                  | mA    |  |  |

| V <sub>BIAS</sub> Quiescent Current        | I <sub>Q(VBIAS)</sub>                | $V_{IN}$ = 1.1V, $V_{BIAS}$ = 5V, $V_{OUT}$ = 0.8V, PG is floating                                       | -                  | 1    | -                  | mA    |  |  |

| Shutdown Current                           | I <sub>SHTD</sub>                    | V <sub>IN</sub> = 6.5V, V <sub>EN</sub> = 0V,<br>C <sub>IN</sub> = 100nF                                 | -                  | 9    | 25                 | μΑ    |  |  |

| Output                                     |                                      |                                                                                                          |                    |      |                    |       |  |  |

| Output Voltage Range                       | V <sub>OUT</sub>                     | -                                                                                                        | 8.0                | -    | 5.1                | V     |  |  |

| Output Current                             | I <sub>OUT</sub>                     | -                                                                                                        | 0                  | -    | 4                  | Α     |  |  |

| FB Voltage                                 | $V_{FB}$                             | For configuration using external resistor divider                                                        | -                  | 0.8  | -                  | V     |  |  |

|                                            |                                      | V <sub>OUT</sub> = 0.8V, I <sub>OUT</sub> = 10mA                                                         | -1.25              | -    | 1.25               |       |  |  |

| Output Voltage Accuracy                    | -                                    | V <sub>OUT</sub> = 1.1V to 3.95V,<br>I <sub>OUT</sub> = 10mA                                             | -1                 | -    | 1                  | %     |  |  |

|                                            |                                      | V <sub>IN</sub> = 1.4V to 6.5V, I <sub>OUT</sub> = 5mA                                                   | -                  | 0.1  | -                  |       |  |  |

| Line Regulation                            | $\Delta V_{OUT}/\Delta V_{IN}$       | V <sub>IN</sub> = 1.1V to 4V, I <sub>OUT</sub> = 5mA,<br>V <sub>BIAS</sub> = 5V                          | -                  | 0.1  | -                  | mV/V  |  |  |

| Load Regulation                            | AV /AI                               | V <sub>IN</sub> = 1.4V, V <sub>OUT</sub> = 0.8V,<br>I <sub>OUT</sub> = 1mA to 4A                         | -                  | 1.2  | -                  | m\//A |  |  |

| Load Regulation                            | ΔV <sub>OUT</sub> /ΔΙ <sub>OUT</sub> | V <sub>IN</sub> = 1.1V, V <sub>OUT</sub> = 0.8V,<br>I <sub>OUT</sub> = 1mA to 4A, V <sub>BIAS</sub> = 5V | -                  | 1.2  | -                  | mV/A  |  |  |

|                                            |                                      | $V_{IN}$ = 1.1V, $V_{BIAS}$ = 5V, $V_{FB}$ forced to 97% of $V_{REF}$ , 4A $I_{OUT}$                     | -                  | 100  | 200                |       |  |  |

| Dropout Voltage <sup>[2]</sup>             | $V_{DO}$                             | $V_{IN}$ = 1.4V, $V_{FB}$ forced to 97% of $V_{REF}$ , 4A $I_{OUT}$                                      | -                  | 160  | 270                | 0 mV  |  |  |

|                                            |                                      | $V_{IN}$ = 5.5V, $V_{FB}$ forced to 97% of $V_{REF}$ , 4A $I_{OUT}$                                      | -                  | 100  | 250                |       |  |  |

| Start-Up Time                              | -                                    | V <sub>IN</sub> = 5.5V, V <sub>OUT</sub> = 1.8V,<br>I <sub>OUT</sub> = 10mA, CNR/SS =1μF                 | -                  | -    | 1000               | μs    |  |  |

Operating conditions unless otherwise noted: T<sub>J</sub> = -40°C to +125°C, V<sub>IN</sub> = V<sub>OUT</sub>+400mV or 1.4V whichever is greater, V<sub>BIAS</sub> = OPEN, V<sub>OUT</sub> = 0.8V, V<sub>EN</sub> = 5V, I<sub>OUT</sub> = 0mA, C<sub>IN</sub> = 47||10||10 $\mu$ F, C<sub>OUT</sub> = 47||10||10 $\mu$ F, C<sub>NR/SS</sub> = 100nF. (Cont.)

| Parameter                     | Symbol         | Test Conditions                                                                                                                                                              | Min <sup>[1]</sup> | Тур. | Max <sup>[1]</sup> | Unit     |

|-------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|--------------------|----------|

| Noise Spectral Density        |                |                                                                                                                                                                              |                    |      |                    |          |

|                               |                | $V_{IN}$ = 1.1V, $V_{BIAS}$ = 5V,<br>$V_{OUT}$ = 0.8V, $I_{OUT}$ = 4A,<br>$CNR/SS$ = 1 $\mu$ F, $C_{OUT}$ = 47 $\mu$ F   <br>10 $\mu$ F    10 $\mu$ F, FREQ = 10Hz           | -                  | 600  | -                  |          |

| Noise with BIAS               | V              | $V_{IN} = 1.1V$ , $V_{BIAS} = 5V$ , $V_{OUT} = 0.8V$ , $I_{OUT} = 4A$ , $CNR/SS = 1\mu F$ , $C_{OUT} = 47\mu F$ $\parallel$ $10\mu F$ $\parallel$ $10\mu F$ , $FREQ = 100Hz$ | -                  | 120  | -                  | nV/√Hz   |

| Noise with BIAG               | $V_{n(BIAS)}$  | $V_{IN} = 1.1V, V_{BIAS} = 5V, \ V_{OUT} = 0.8V, I_{OUT} = 4A, \ CNR/SS = 1\mu F, C_{OUT} = 47\mu F    10\mu F    10\mu F, FREQ = 1kHz$                                      | -                  | 40   | -                  | 110/112  |

|                               |                | $V_{IN} = 1.1V, V_{BIAS} = 5V, \ V_{OUT} = 0.8V, I_{OUT} = 4A, \ CNR/SS = 1\mu F, C_{OUT} = 47\mu F    10\mu F    10\mu F, FREQ = 10kHz$                                     | -                  | 20   | -                  |          |

|                               |                | $V_{IN} = 3.8V, V_{OUT} = 3.3V, I_{OUT} = 4A, CNR/SS = 1\mu F, C_{OUT} = 47\mu F    10\mu F    10\mu F, FREQ = 10Hz$                                                         | -                  | 800  | -                  |          |

| Noise without BIAS            | V              | $V_{IN} = 3.8V, V_{OUT} = 3.3V, I_{OUT} = 4A, CNR/SS = 1\mu F, C_{OUT} = 47\mu F    10\mu F    10\mu F, FREQ = 100Hz$                                                        | -                  | 145  | -                  | nV/√Hz   |

| Noise willout BIAS            | V <sub>n</sub> | $V_{IN} = 3.8V, V_{OUT} = 3.3V, I_{OUT} = 4A, CNR/SS = 1\mu F, C_{OUT} = 47\mu F    10\mu F    10\mu F, FREQ = 1kHz$                                                         | -                  | 40   | -                  | IIV/VIIZ |

|                               |                | $V_{IN} = 3.8V, V_{OUT} = 3.3V, I_{OUT} = 4A, CNR/SS = 1\mu F, C_{OUT} = 47\mu F    10\mu F    10\mu F, FREQ = 10kHz$                                                        | -                  | 20   | -                  |          |

| Output RMS Noise with BIAS    | V <sub>n</sub> | $V_{IN}$ = 1.1V, $V_{BIAS}$ = 5V, $V_{OUT}$ = 0.8V, $I_{OUT}$ = 4A, $CNR/SS$ = 1 $\mu$ F, $C_{OUT}$ = 47 $\mu$ F    10 $\mu$ F    10 $\mu$ F, BW = 10Hz to 100kHz            | -                  | 7    | -                  | μVRMS    |

| Output RMS Noise without BIAS | $V_n$          | $V_{IN}$ = 3.8V, $V_{OUT}$ = 3.3V, $I_{OUT}$ = 4A, CNR/SS = 1 $\mu$ F, $C_{OUT}$ = 47 $\mu$ F    10 $\mu$ F    10 $\mu$ F, BW = 10Hz to 100kHz                               | -                  | 7    | -                  | μVRMS    |

Operating conditions unless otherwise noted: T<sub>J</sub> = -40°C to +125°C, V<sub>IN</sub> = V<sub>OUT</sub>+400mV or 1.4V whichever is greater, V<sub>BIAS</sub> = OPEN, V<sub>OUT</sub> = 0.8V, V<sub>EN</sub> = 5V, I<sub>OUT</sub> = 0mA, C<sub>IN</sub> = 47||10||10µF, C<sub>OUT</sub> = 47||10||10µF, C<sub>NR/SS</sub> = 100nF. (Cont.)

| Parameter                   | Symbol              | Test Conditions                                                                                                                                                                                                                                                                                                                                                                                     | Min <sup>[1]</sup> | Тур. | Max <sup>[1]</sup> | Unit |

|-----------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|--------------------|------|

| PSRR                        |                     |                                                                                                                                                                                                                                                                                                                                                                                                     |                    |      |                    |      |

|                             |                     | $V_{IN} = 1.2V, V_{BIAS} = 5V, \ V_{OUT} = 0.8V, I_{OUT} = 4A, \ CNR/SS = 1\mu F, C_{IN} = None, \ COUT = 47\mu F    10\mu F    10\mu F, \ FREQ = 120Hz, \ V_{RIPPLE} = 150mV_{P-P}$                                                                                                                                                                                                                | -                  | 65   | -                  |      |

| PSRR with BIAS              |                     | $V_{IN} = 1.2V, V_{BIAS} = 5V, \ V_{OUT} = 0.8V, I_{OUT} = 4A, \ CNR/SS = 1\mu F, C_{IN} = None, \ C_{OUT} = 47\mu F    10\mu F    10\mu F, \ FREQ = 10kHz, \ V_{RIPPLE} = 150mV_{P-P}$                                                                                                                                                                                                             | -                  | 45   | -                  | dB   |

| T CITIC WILLIAMS            |                     | $\begin{split} &V_{\text{IN}} = 1.2 \text{V, } V_{\text{BIAS}} = 5 \text{V,} \\ &V_{\text{OUT}} = 0.8 \text{V, } I_{\text{OUT}} = 4 \text{A,} \\ &\text{CNR/SS} = 1 \mu \text{F, } C_{\text{IN}} = \text{None,} \\ &C_{\text{OUT}} = 47 \mu \text{F, }    \ 10 \mu \text{F, }    10 \mu \text{F,} \\ &\text{FREQ} = 100 \text{kHz,} \\ &V_{\text{RIPPLE}} = 150 \text{mV}_{\text{P-P}} \end{split}$ | -                  | 30   | -                  | uБ   |

|                             |                     | $\begin{split} &V_{\text{IN}} = 1.2 \text{V, } V_{\text{BIAS}} = 5 \text{V,} \\ &V_{\text{OUT}} = 0.8 \text{V, } I_{\text{OUT}} = 4 \text{A,} \\ &\text{CNR/SS} = 1 \mu \text{F, } C_{\text{IN}} = \text{None,} \\ &C_{\text{OUT}} = 47 \mu \text{F    } 10 \mu \text{F    } 10 \mu \text{F,} \\ &\text{FREQ} = 1 \text{MHz,} \\ &V_{\text{RIPPLE}} = 150 \text{mV}_{\text{P-P}} \end{split}$       | -                  | 25   | -                  |      |

|                             |                     | $V_{IN} = 3.8V, V_{OUT} = 3.3V, I_{OUT} = 4A, CNR/SS = 1\mu F, C_{IN} = None, C_{OUT} = 47\mu F    10\mu F    10\mu F, FREQ= 120Hz, V_{RIPPLE} = 150mV_{P-P}$                                                                                                                                                                                                                                       | -                  | 65   | -                  |      |

| PSRR without BIAS           |                     | $V_{IN} = 3.8V, V_{OUT} = 3.3V, I_{OUT} = 4A, CNR/SS = 1\mu F, C_{IN} = None, C_{OUT} = 47\mu F    10\mu F    10\mu F, FREQ = 10kHz, V_{RIPPLE} = 150mV_{P-P}$                                                                                                                                                                                                                                      | -                  | 50   | -                  | dB   |

| r Sixix without BIAS        | -                   | $V_{IN} = 3.8V, V_{OUT} = 3.3V, I_{OUT} = 4A, CNR/SS = 1\mu F, C_{IN} = None, C_{OUT} = 47\mu F    10\mu F    10\mu F, FREQ = 100kHz, V_{RIPPLE} = 150mV_{P-P}$                                                                                                                                                                                                                                     | -                  | 35   | -                  | uБ   |

|                             |                     | $V_{IN}$ = 3.8V, $V_{OUT}$ = 3.3V, $I_{OUT}$ = 4A, CNR/SS= 1 $\mu$ F, $C_{IN}$ = None, $C_{OUT}$ = 47 $\mu$ F    10 $\mu$ F, FREQ = 1MHz, $V_{RIPPLE}$ = 150mV <sub>P-P</sub>                                                                                                                                                                                                                       | -                  | 30   | -                  |      |

| EN                          |                     |                                                                                                                                                                                                                                                                                                                                                                                                     |                    |      |                    |      |

| EN Voltage Rising Threshold | V <sub>EN</sub>     | V <sub>EN</sub> Rising                                                                                                                                                                                                                                                                                                                                                                              | 0.75               | 1.0  | 1.05               | V    |

| EN Hysteresis               | V <sub>EN_HYS</sub> | -                                                                                                                                                                                                                                                                                                                                                                                                   | -                  | 100  | -                  | mV   |

| EN Leakage                  | I <sub>EN</sub>     | V <sub>EN</sub> = 5.5V                                                                                                                                                                                                                                                                                                                                                                              | -100               | -    | 100                | nA   |

#### RAA214048 Datasheet

Operating conditions unless otherwise noted: T<sub>J</sub> = -40°C to +125°C, V<sub>IN</sub> = V<sub>OUT</sub>+400mV or 1.4V whichever is greater, V<sub>BIAS</sub> = OPEN, V<sub>OUT</sub> = 0.8V, V<sub>EN</sub> = 5V, I<sub>OUT</sub> = 0mA, C<sub>IN</sub> = 47||10||10µF, C<sub>OUT</sub> = 47||10||10µF, C<sub>NR/SS</sub> = 100nF. (Cont.)

| Parameter                   | Symbol                             | Test Conditions                                                                                               | Min <sup>[1]</sup> | Тур. | Max <sup>[1]</sup> | Unit |

|-----------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------|------|--------------------|------|

| PG                          |                                    | <u>'</u>                                                                                                      | •                  |      |                    |      |

| PG Rising Threshold         | PG <sub>TH</sub>                   | w.r.t. VOUT                                                                                                   | -                  | -12  | -                  | %    |

| PG Hysteresis               | PG <sub>HYS</sub>                  | -                                                                                                             | -                  | 1    | -                  | %    |

| PG Voltage during VOUT low  | PG <sub>VOL</sub>                  | I <sub>PG</sub> = 1mA                                                                                         | -                  | 150  | 400                | mV   |

| Protection                  |                                    | '                                                                                                             |                    |      |                    |      |

| Internal Current Limit      | I <sub>LIM</sub>                   | V <sub>IN</sub> = 1.1V, V <sub>BIAS</sub> = 5V, V <sub>OUT</sub> forced to 90% of V <sub>OUT_PROGRAMMED</sub> | -                  | 7    | -                  | А    |

| Thermal Shutdown            | T <sub>OTSD</sub>                  | Temperature Rising                                                                                            | -                  | 165  | -                  | °C   |

| Thermal Shutdown Hysteresis | ysteresis T <sub>OTSD_HYST</sub> - |                                                                                                               | -                  | 15   | -                  | °C   |

- 1. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested. Compliance to limits is assured by characterization and design.

- 2. Dropout Voltage is measured with the LDO in an open-loop configuration where FB is disconnected from VOUT. A V<sub>FB</sub> lower than the reference voltage is applied to the FB pin, which causes the error amplifier to drive the main pass-transistor into saturation to try and bring the output voltage (which is sensed through FB) back up into regulation. Because VOUT is disconnected from FB, the output voltage rails up to a margin below V<sub>IN</sub> and the V<sub>IN</sub>-V<sub>OUT</sub> differential is taken to be the dropout voltage.

# 4. Typical Performance Curves

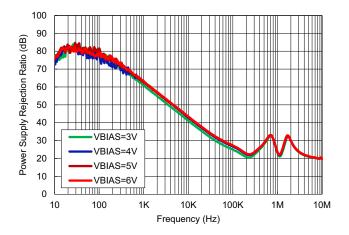

### 4.1 PSRR

Figure 4. PSRR vs Frequency for Various BIAS ( $V_{IN}$  = 1.1V,  $V_{OUT}$  = 0.8V,  $I_{OUT}$  = 4A,  $C_{NR/SS}$  = 1 $\mu$ F)

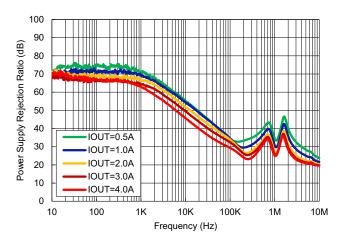

Figure 5. PSRR vs Frequency for Various  $I_{OUT}$  ( $V_{IN}$  = 1.2V,  $V_{OUT}$  = 0.8V,  $V_{BIAS}$  = 5V,  $C_{NR/SS}$  = 1 $\mu$ F)

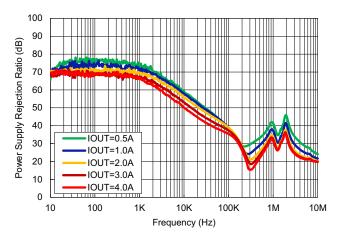

Figure 6. PSRR vs Frequency for Various  $I_{OUT}$ ( $V_{IN} = 3.7V$ ,  $V_{OUT} = 3.3V$ ,  $C_{NR/SS} = 1\mu F$ )

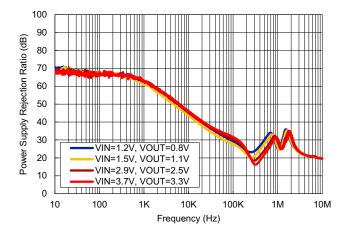

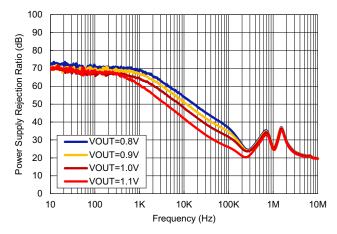

Operating conditions unless otherwise noted:  $T_A$  = 25°C,  $V_{IN}$  =  $V_{OUT}$ +0.4V or 1.4V whichever is greater,  $V_{BIAS}$  = open,  $V_{OUT}$  = 0.8V, VEN tied directly to VIN,  $C_{IN}$  = None,  $C_{OUT}$  = 47||10||10 $\mu$ F,  $C_{NR/SS}$  = 1 $\mu$ F, and PG pulled up to  $V_{OUT}$  with 10k $\Omega$ . (Cont.)

Figure 7. PSRR vs Frequency for Various  $V_{OUT}$  ( $V_{IN}$  =  $V_{OUT}$  + 0.4V,  $V_{BIAS}$  = 5V,  $I_{OUT}$  = 4A,  $C_{NR/SS}$  = 1 $\mu$ F)

Figure 8. PSRR vs Frequency for Various  $V_{OUT}$  ( $V_{IN}$  = 1.4V,  $V_{BIAS}$  = 5V,  $I_{OUT}$  = 4A,  $C_{NR/SS}$  = 1 $\mu$ F)

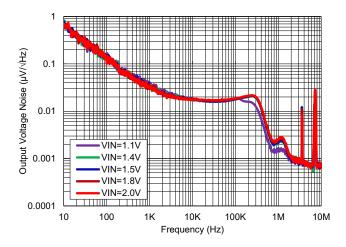

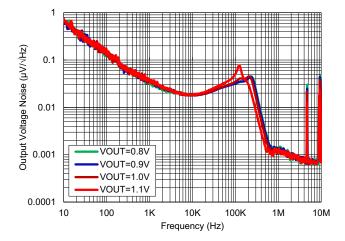

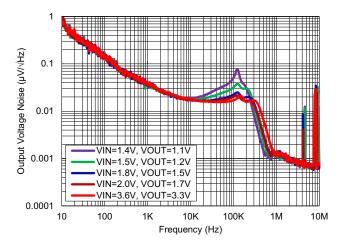

## 4.2 Output Noise

Figure 9. Output Voltage Noise for Various  $V_{IN}$  ( $V_{OUT}$  = 0.8V,  $V_{BIAS}$  = 5V,  $I_{OUT}$  = 4A,  $C_{NR/SS}$  = 1 $\mu$ F)

Figure 10. Output Voltage Noise for Various  $V_{IN}$ ( $V_{OUT}$  = 0.8V,  $I_{OUT}$  = 4A,  $C_{NR/SS}$  = 1 $\mu$ F)

Output Voltage Noise (µV/√Hz) 0.1 0.01 IOUT=0.5A IOUT=1.0A 0.001 IOUT=2.0A IOUT=3.0A IOUY=4.0A 0.0001 100 100K 10 10K 10M Frequency (Hz)

Figure 11. Output Voltage Noise for Various  $V_{OUT}$ ( $V_{OUT}$  = 1.4V,  $I_{OUT}$  = 4A,  $C_{NR/SS}$  = 1 $\mu$ F)

Figure 12. Output Voltage Noise for Various  $I_{OUT}$ ( $V_{IN}$  = 1.4V,  $V_{OUT}$  = 0.8V,  $C_{NR/SS}$  = 1 $\mu$ F)

Figure 13. PSRR vs Frequency for Various  $V_{OUT}$  ( $V_{IN} = V_{OUT} + 0.3V$ ,  $I_{OUT} = 4A$ ,  $C_{NR/SS} = 1\mu F$ )

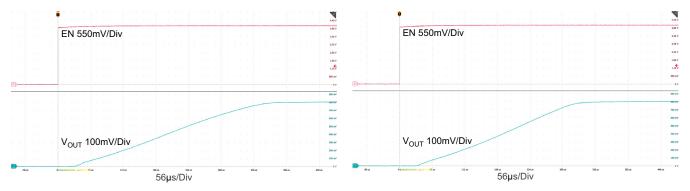

## 4.3 Start-Up

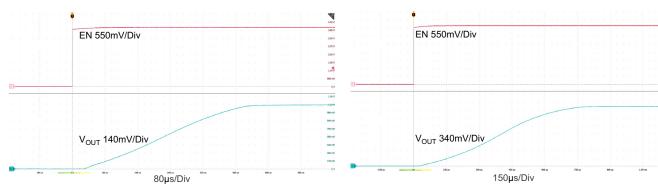

Figure 14. Start-Up ( $V_{IN}$  = 1.1V,  $V_{OUT}$  = 0.8V,  $V_{BIAS}$  = 5V,  $I_{OUT}$  = 4A,  $C_{NR/SS}$  = 1 $\mu$ F)

Figure 15. Start-Up ( $V_{IN}$  = 1.4V,  $V_{OUT}$  = 0.8V,  $I_{OUT}$  = 4A,  $C_{NR/SS}$  = 1 $\mu$ F)

Figure 16. Start-Up ( $V_{IN}$  = 1.5V,  $V_{OUT}$  = 1.1V,  $I_{OUT}$  = 4A,  $C_{NR/SS}$  = 1 $\mu$ F)

Figure 17. Start-Up (V<sub>IN</sub> = 2.9V, V<sub>OUT</sub> = 2.5V, I<sub>OUT</sub> = 4A,  $C_{NR/SS} = 1\mu F$ )

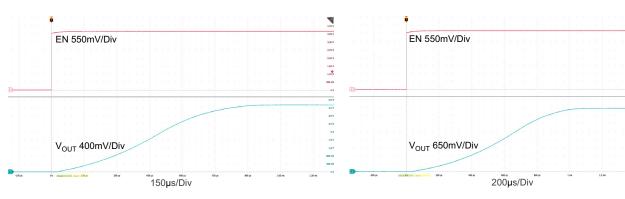

Figure 18. Start-Up ( $V_{IN}$  = 3.7V,  $V_{OUT}$  = 3.3V,  $I_{OUT}$  = 4A,  $C_{NR/SS}$  = 1 $\mu$ F)

Figure 19. Start-Up ( $V_{IN}$  = 5.5V,  $V_{OUT}$  = 5.1V,  $I_{OUT}$  = 4A,  $C_{NR/SS}$  = 1 $\mu$ F)

## 4.4 Load Transient Response

Operating conditions unless otherwise noted:  $T_A$  = 25°C,  $V_{IN}$  =  $V_{OUT}$ +0.4V or 1.4V whichever is greater,  $V_{BIAS}$  = open,  $V_{OUT}$  = 0.8V, VEN tied directly to VIN,  $C_{IN}$  = 47||10||10 $\mu$ F,  $C_{OUT}$  = 47||10||10 $\mu$ F,  $C_{NR/SS}$  = 1 $\mu$ F, and PG pulled up to  $V_{OUT}$  with 10 $\mu$ C.

Figure 20. Load Transient Response (V<sub>IN</sub> = 1.4V, V<sub>OUT</sub> = 1.0V,  $\Delta I_{OUT}$  = 0.2A to 4A at 1A/ $\mu$ s, C<sub>NR/SS</sub> = 1 $\mu$ F)

Figure 21. Load Transient Response ( $V_{IN}$  = 3.7V,  $V_{OUT}$  = 3.3V,  $\Delta I_{OUT}$  = 0.2A to 4A at 1A/µs,  $C_{NR/SS}$  = 1µF)

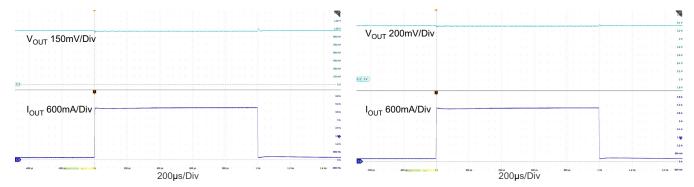

### 4.5 Short-Circuit

Figure 22. Short after Start-Up (V<sub>IN</sub> = 1.4V, V<sub>OUT</sub> = 0.8V,  $C_{NR/SS} = 1 \mu F$ )

Figure 23. Short before Start-Up (V<sub>IN</sub> = 1.4V, V<sub>OUT</sub> = 0.8V,  $C_{NR/SS}$  = 1 $\mu$ F)

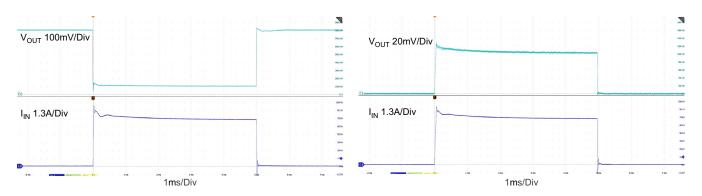

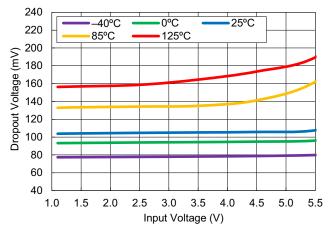

## 4.6 Dropout Voltage

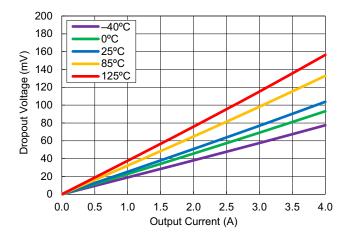

Figure 24. Dropout Voltage vs Output Current (V<sub>IN</sub> = 1.1V, V<sub>BIAS</sub> = 5V)

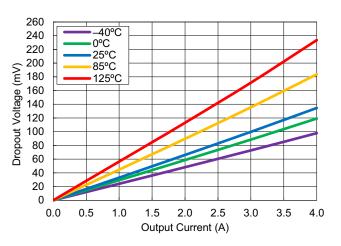

Figure 25. Dropout Voltage vs Output Current (V<sub>IN</sub> = 1.4V, without Bias)

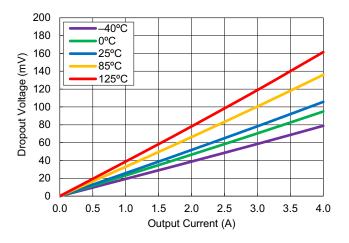

Figure 26. Dropout Voltage vs Output Current  $(V_{IN} = 3.5V \text{ without Bias})$

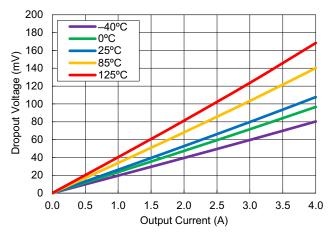

Figure 27. Dropout Voltage vs Output Current (V<sub>IN</sub> = 5.5V without Bias)

Operating conditions unless otherwise noted:  $T_A$  = 25°C,  $V_{IN}$  =  $V_{OUT}$ +0.4V or 1.4V whichever is greater,  $V_{BIAS}$  = open,  $V_{OUT}$  = 0.8V, VEN tied directly to VIN,  $C_{IN}$  = 47||10||10 $\mu$ F,  $C_{OUT}$  = 47||10||10 $\mu$ F,  $C_{NR/SS}$  = 1 $\mu$ F, and PG pulled up to  $V_{OUT}$  with 10 $\mu$ C. (Cont.)

200 -40°C 0°C 25°C 180 85°C 125°C Dropout Voltage (mV) 160 140 120 100 80 60 40 3.0 3.5 5.0 5.5 4.0 4.5 6.0 6.5 Bias Voltage (V)

Figure 28. Dropout Voltage vs Input Voltage (I<sub>OUT</sub> = 4A, V<sub>BIAS</sub> = 6.5V)

Figure 29. Dropout Voltage vs Bias Voltage  $(V_{IN} = 1.4V, I_{OUT} = 4A)$

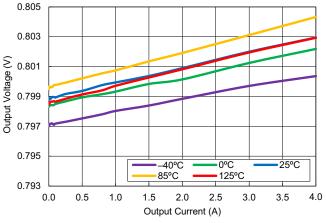

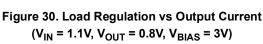

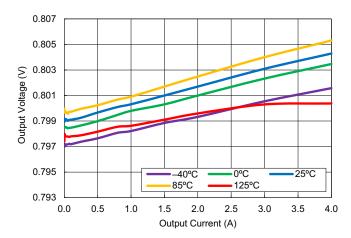

## 4.7 Load and Line Regulation

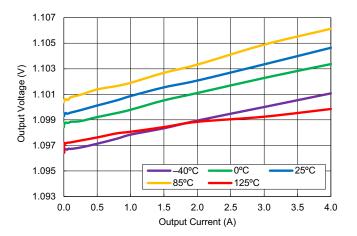

Figure 31. Load Regulation vs Output Current  $(V_{IN} = 1.4V, V_{OUT} = 0.8V)$

Figure 32. Load Regulation vs Output Current  $(V_{IN} = 1.5V, V_{OUT} = 1.1V)$

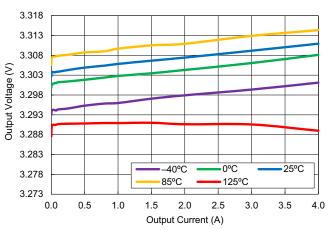

Figure 33. Load Regulation vs Output Current  $(V_{IN} = 3.7V, V_{OUT} = 3.3V)$

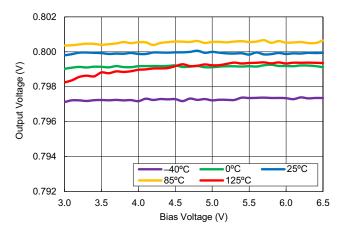

Figure 34. Line Regulation vs Bias Voltage (V<sub>IN</sub> = 1.1V, V<sub>OUT</sub> = 0.8V, I<sub>OUT</sub> = 5mA)

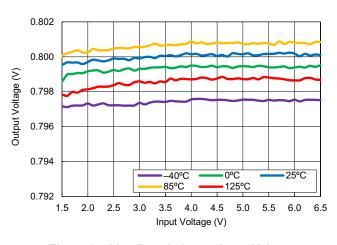

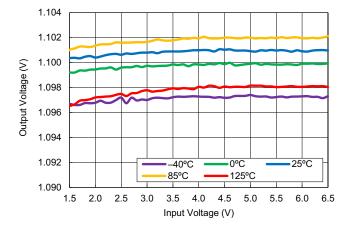

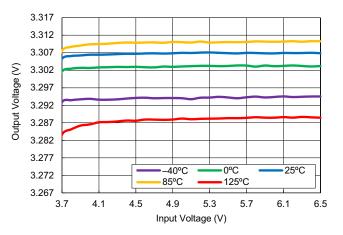

Figure 35. Line Regulation vs Input Voltage  $(V_{OUT} = 0.8V, I_{OUT} = 5mA)$

Figure 36. Line Regulation vs Input Voltage  $(V_{OUT} = 1.1V, I_{OUT} = 5mA)$

Figure 37. Line Regulation vs Input Voltage  $(V_{OUT} = 3.3V, I_{OUT} = 5mA)$

## 4.8 Other Typical Performance Curves

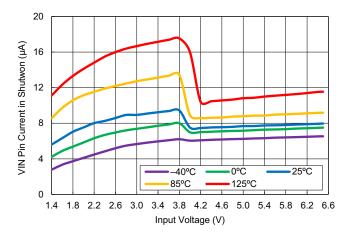

Figure 38. Shutdown Current vs Input Voltage for Various Temperatures

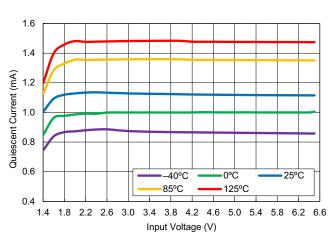

Figure 39. Quiescent Current vs Input Voltage for Various Temperatures

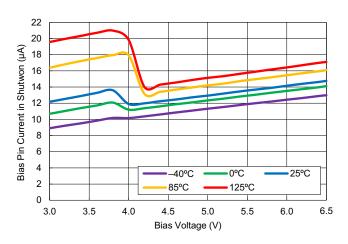

Figure 40. Bias Pin Current in Shutdown vs Bias Voltage for Various Temperatures  $(V_{IN} = 1.1V)$

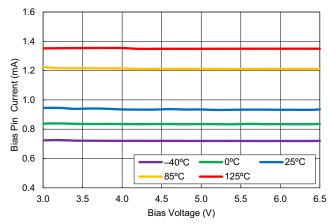

Figure 41. Bias Pin Quiescent Current vs Bias Voltage for Various Temperatures  $(V_{IN} = 1.1V)$

## 5. Applications Information

#### 5.1 Overview

The RAA214048 is a low-noise, high PSRR, low-dropout (LDO) regulator. The LDO can source up to 4A load current with only 250mV dropout voltage. It operates from an input voltage of 1.1V to 6.5V (with a minimum 3V BIAS) for very low input voltage applications with ±1% accuracy over line, load, and temperature. The output voltage can be programmed from 0.8V to 3.95V using output voltage setting pins on the IC in 50mV steps or from 0.8V to 5.1V using external feedback resistors.

The RAA214048 is designed and tested with a  $10\mu\text{F}$  ceramic input capacitor,  $22\mu\text{F}$  ceramic output capacitor, a  $1\mu\text{F}$  noise-reduction, a soft-start capacitor ( $C_{\text{NR/SS}}$ ), and a  $10\mu\text{F}$  BIAS capacitor if VBIAS is being used. The LDO is available in a 20-Ld  $3.5\text{mm}\times3.5\text{mm}$  QFN package.

The RAA214048 integrates the following additional features in this package:

- High output accuracy (±1%)

- Low output noise

- High PSRR

- No sequencing requirement between VBIAS, VIN, and VEN

- Power-good indication

- Convenient output voltage set pins to program the LDO output

- Undervoltage lockout (UVLO)

- Enable control

- Internal current limit protection

- Thermal shutdown protection

- Minimum 22µF ceramic output capacitor for stability

- Output capacitor automatic discharge

- BIAS pin for lower dropout voltage and lower VIN performance

## 5.2 Theory of Operation of NMOS LDOs

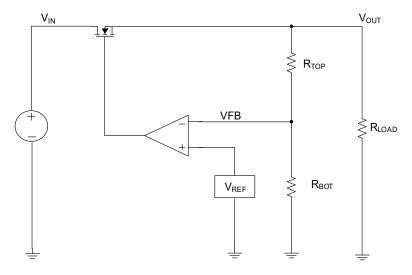

Like the majority of LDOs with an NMOS pass transistor, the RAA214048 output voltage (V<sub>OUT</sub>) regulation can be modeled with a voltage reference (V<sub>REF</sub>), feedback (FB) resistors, error amplifier, and NMOS pass-transistor as shown in Figure 42.

Figure 42. Simple NMOS LDO Regulator Block Diagram

The NMOS pass transistor can be modeled as a variable resistor  $(r_{DS(ON)})$  that is controlled by the error amplifier to maintain a constant DC output voltage for changes in load current  $(I_{OUT})$ . Assume the input voltage  $(V_{IN})$  remains constant and the  $r_{DS(ON)}$  is adjusted for a given  $I_{OUT}$  to set  $V_{OUT}$ .

Equation 1 summarizes this relationship.

(EQ. 1)

$$V_{OUT} = V_{IN} - I_{OUT} \times r_{DS(ON)}$$

V<sub>OUT</sub> is set using the FB resistor divider, which sets V<sub>OUT</sub> to a value that corresponds to Equation 2.

(EQ. 2)

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R_{TOP}}{R_{BOT}}\right)$$

The error amplifier compares  $V_{FB}$  with the fixed  $V_{REF}$  voltage and works to minimize the difference between VFB and VREF by changing the gate voltage of the NMOS pass transistor and, therefore, the  $r_{DS(ON)}$ .

If the  $I_{OUT}$  suddenly increases because of decreased load resistance,  $V_{OUT}$  decreases because the regulator has not responded to the change, and the  $r_{DS(ON)}$  is set too high.  $V_{FB}$  correspondingly decreases and is below the  $V_{REF}$  voltage, therefore increasing the error voltage. The error amplifier senses and minimizes the error by driving the NMOS gate voltage more positively relative to the FET source to decrease the  $R_{DS(ON)}$ , which increases the output voltage, bringing it back into regulation.

By similar logic, a sudden decrease in  $I_{OUT}$  because of increased load resistance causes  $V_{OUT}$  to increase because the  $r_{DS(ON)}$  is set too low.  $V_{FB}$  is then higher than the fixed  $V_{REF}$  voltage, increasing the error. The error amplifier senses and minimizes the error by driving the NMOS gate voltage more negatively relative to the FET source to increase the  $r_{DS(ON)}$ , which decreases the output voltage, bringing it back into regulation.

## 6. Functional Description

### 6.1 Low Output Noise

The LDO output noise is the internally generated noise created largely by the band-gap voltage reference and the error amplifier. The output noise is commonly represented in units of  $nV/\sqrt{Hz}$  for a specific frequency or as an integrated root-mean square (RMS) value in  $\mu V$  over a range of frequencies typically 10Hz to 100kHz or 100Hz to 100kHZ.

The RAA214048 output noise is largely independent of the output voltage and does not require a feed-forward capacitor to achieve very low output noise. On the other hand, it depends on the output current,  $C_{NR/SS}$ , and  $C_{OUT}$  capacitor. The  $C_{NR/SS}$  improves the low-frequency output noise of the LDO. Renesas recommends using a 1 $\mu$ F  $C_{NR/SS}$  capacitor for the best low-output noise. See  $C_{NR/SS}$  capacitor for selecting the correct noise-reduction and soft-start capacitor.  $C_{OUT}$  improves the noise at high-frequencies by reducing the high-frequency output impedance of the LDO. See the Output Capacitor ( $C_{OUT}$ ) section for selecting the correct output capacitor.

## 6.2 High Power-Supply Ripple-Rejection (PSRR)

The PSRR is how much attenuation or rejection the LDO control loop gives to externally generated input voltage noise, such as from a switching regulator. Although PSRR represents a loss in the input noise signal, it is common to see it as a positive decibel (dB) number. Mathematically, PSRR is represented as a logarithmic ratio between an input and output ripple sinusoid signal at a specific frequency as shown in Equation 3.

(EQ. 3)

$$PSRR(dB) = 20 \times log \left( \frac{V_{IN(RIPPLE)}}{V_{OUT(RIPPLE)}} \right)$$

The PSRR for the RAA214048 is largely independent of the output voltage and does not require a feed-forward capacitor. On the other hand, it depends on the output current, headroom voltage ( $V_{IN}$ - $V_{OUT}$ ),  $C_{NR/SS}$  capacitor,  $C_{OUT}$  capacitor, and PCB layout.

The higher the output current, the lower the PSRR is across all frequencies compared to a lower output current. The PSRR at low- and mid-frequencies can be improved by increasing the headroom voltage, but this comes at the cost of increased power dissipation. If the headroom is lowered, it decreases the power dissipation and lowers the PSRR at low- to mid-frequencies.

## 6.3 VBIAS, VIN, and VEN Sequencing

The RAA214048 the VBIAS, VIN, and VEN pins do not need to be powered on in any specific order. Table 1 gives the status of the LDO and various circuits depending on the status of VBIAS, VIN, and VEN.

| VIN Status                                   | VBIAS Status                                         | VEN Status             | LDO<br>Status | Active<br>Discharge | V <sub>PG</sub> Status                                                                |  |

|----------------------------------------------|------------------------------------------------------|------------------------|---------------|---------------------|---------------------------------------------------------------------------------------|--|

| V <sub>IN</sub> ≥                            | V <sub>BIAS</sub> ≥ V <sub>UVLO(BIAS)</sub> (RISING) | V <sub>EN</sub> = HIGH | ON            | OFF                 | V <sub>PG</sub> = HIGH or High-Z when<br>V <sub>OUT</sub> ≥ 0.88×V <sub>OUT_SET</sub> |  |

| V <sub>UVLO(RISING)</sub>                    |                                                      | V <sub>EN</sub> = LOW  |               |                     |                                                                                       |  |

|                                              | V <sub>BIAS</sub> < V <sub>UVLO(BIAS)(RISING)</sub>  | Status does            | OFF           | ON <sup>[1]</sup>   | V <sub>PG</sub> = LOW                                                                 |  |

| V <sub>IN</sub> ≤ V <sub>UVLO(FALLING)</sub> | Status does not matter                               | not matter             |               |                     |                                                                                       |  |

Table 1. VBIAS, VIN, and VEN Functionality

#### **6.4 UVLO**

The RAA214048 integrates an internal UVLO circuit to keep the output voltage safely DISABLED if the input voltage or bias voltage is below the UVLO threshold. When the input voltage is above the UVLO threshold, the part is ENABLED, and the output voltage ramps up into regulation. The UVLO hysteresis prevents input voltage noise from causing the output to oscillate.

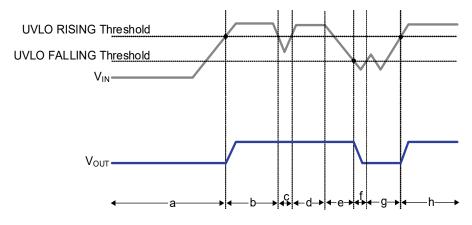

When the input voltage is below the UVLO, an internal  $300\Omega$  discharge resistor connects the LDO output to ground to quickly discharge the output capacitor. The resistor is connected to the output capacitor when the input voltage exceeds 0.9V but less than the UVLO threshold of 1V (typical). Figure 43 illustrates the UVLO operation.

Figure 43. UVLO Operation

<sup>1.</sup> The output discharge circuitry remains enabled if  $V_{IN}$  does not drop below 0.9V (typical) or  $V_{BIAS}$  does not drop below 2.75V (typical).

- a The input voltage has not reached the UVLO Rising threshold (1V), so the LDO remains disabled. The 300Ω internal discharge resistor is connected to the output voltage if the input voltage is above the UVLO riding threshold between 0.9V and 1V.

- b The LDO is enabled, and the output rises to its regulated programmed value when the UVLO RISING threshold is reached by the input voltage (1V). At the same time, the 300Ω discharge resistor is disconnected from VOUT.

- c A brownout occurs, but the LDO remains enabled, and the 300Ω discharge resistor remains disconnected because the input voltage has not reached the UVLO FALLING threshold (0.9V). The output voltage can still fall out of regulation.

- d Output is regulated to its programmed output voltage value.

- e The input voltage is turned OFF but has not yet crossed the UVLO FALLING threshold (0.9V), so the LDO is still enabled, and the 300Ω discharge resistor remains disconnected. The output voltage can fall out of regulation.

- f The input voltage turns OFF, and the output voltage falls because of the load and 300Ω discharge resistor, which remains connected to VOUT if the input voltage is between 0.9V and 1V. The LDO is disabled.

- g The LDO remains disabled because the input voltage has not reached the UVLO RISING threshold (1V).

The 300Ω internal discharge resistor remains connected to the output voltage if the input voltage is between 0.9V and 1V.

- h Output is regulated to its programmed output voltage value.

### 6.5 Power-Good (PG) Indication

The Power-good (PG) pin is an open-drain NMOS-FET. The PG pin circuitry monitors the FB pin voltage to indicate whether the output voltage is 12% below its programmed value (Undervoltage (UV) threshold). When the output voltage is 12% below its programmed value, the PG circuitry drives the NMOS FET ON and indicates LOW on the PG pin. If the output voltage exceeds 88% of its programmed value, the PG circuitry drives the NMOS-FET OFF, and the PG pin becomes HIGH. When the output voltage is below the PG UV thresholds, the fast-start-up circuitry is activated to bring the output voltage above the 88% nominal value.

Renesas recommends using a  $10k\Omega$  or greater pull-up resistor to tie the PG pin to VIN, VOUT, or an external supply to ensure a proper HIGH voltage to any downstream logic device such as an MCU or FPGA. If the PG pin is not used, it can be left floating. The  $10k\Omega$  lower limit results from the maximum pull-down strength of the NMOS-FET. Working outside of this range may result in invalid digital logic level readings.

### 6.6 Enable Control

The RAA214048 uses the EN pin voltage ( $V_{EN}$ ) to enable or disable the LDO. On power-up, if the enable voltage remains lower than the  $V_{EN}$  Rising threshold ( $V_{EN} \le 1V$ ), the LDO remains DISABLED. If  $V_{EN}$  exceeds the  $V_{EN}$  Rising threshold ( $V_{EN} \ge 1V$  typical), the LDO is ENABLED. When  $V_{EN}$  falls below the  $V_{EN}$  falling threshold ( $V_{EN} \le 0.9V$ ), the LDO is DISABLED. The  $V_{EN}$  hysteresis (100mV) prevents the enable voltage noise from causing the output to oscillate. When the LDO is disabled, the shutdown current is typically 9µA.

When the LDO is disabled, and the input voltage is greater than or equal to 0.9V, the same  $300\Omega$  discharge resistor controlled by the UVLO circuitry is connected between the LDO output and GND to discharge the output capacitor quickly.

Connect the EN pin directly to the input voltage for automatic start-up or to a logic controller such as an FPGA MCU. Some logic pins use an open-collector or open-drain transistor to pull LOW and float when HIGH. Make sure to connect a  $10k\Omega$  pull-up resistor to ensure proper logic HIGH. To ensure proper Enable control operation, ensure the  $V_{\text{EN}}$  signal source can swing above and below the threshold values.

### 6.7 Internal Current Limit (ILIM)

The internal current limit (ILIM) circuitry limits the maximum output current the RAA214048 can source to the load during start-up because of in-rush current or during faults such as output short-circuits. ILIM is set above the maximum recommended output current of the RAA214048 (4A).

During in-rush current or fault events, the LDO becomes a constant current source, and as a result, any decrease in load resistance causes a decrease in the output voltage. The LDO returns to regulation when the short or overcurrent condition is removed. Because of the high power dissipation caused by overcurrent faults, the LDO may begin to cycle ON and OFF because of the thermal shutdown circuitry. The thermal shutdown circuitry turns the LDO OFF when the die junction temperature exceeds thermal fault conditions (+165°C) and turns the LDO ON after cooling to +150°C when the LDO output is OFF.

#### 6.8 Thermal Protection

The RAA214048 is protected against thermal overloads caused by excessive power dissipation, such as during overcurrent conditions or high ambient temperatures.

When the die junction temperature exceeds +165°C, the thermal shutdown circuit disables the LDO, shutting off the output and allowing the LDO to cool. A 15°C hysteresis is included to prevent the LDO from uncontrollably heating and cooling.

Prolonged exposure to a junction temperature exceeding  $+125^{\circ}$ C reduces the long-term stability and life of the LDO. Therefore, the design must consider the ambient temperature that the LDO works in, the junction-to-ambient thermal resistance ( $\theta_{JA}$ ), and any fault conditions that can cause the junction to exceed the recommended operating range. In some applications, a heat sink may need to be implemented. See Power Dissipation and Thermals to approximate the maximum junction temperature for an application.

## 6.9 Output Capacitor Automatic Discharge

The RAA214048 features a  $300\Omega$  discharge resistor that rapidly discharges the output capacitor when the LDO is disabled. The UVLO and ENABLE circuitry control the  $300\Omega$  discharge resistor.

The  $300\Omega$  discharge resistor is connected to the LDO output when the LDO is disabled using the ENABLE or UVLO circuitry and when the input voltage or VBIAS voltage is greater than or equal to 1V. If the input voltage collapses faster than the discharge circuitry can discharge the output capacitor, the output voltage may be greater than the input voltage. In this case,  $C_{OUT}$  discharges through the NMOS transistor body diode.

#### 6.10 BIAS

Using a BIAS voltage ≥ 3.3V for V<sub>IN</sub>s less than 3.3V improves the dropout voltage and PSRR.

### 6.11 Output Accuracy

The RAA214048 features an output voltage accuracy of 1% maximum, including the errors introduced by the internal reference, load regulation, line regulation, and operating temperature as specified by the Electrical Characteristics tables. The output voltage accuracy specifies minimum and maximum output voltage error with respect to the nominal output voltage stated as a percent.

## 7. Application Requirements

## 7.1 Input Voltage

The RAA214048 operates with an input voltage of 1.4V to 6.5V on the VIN pin (without BIAS) and from 1.1V to 6.5V on the VIN pin (with a minimum of 3V BIAS). If  $V_{IN} \ge V_{BIAS}$ , it is pointless to use the BIAS pin.

The input supply must be able to supply the required current the LDO needs to supply to the load. For proper regulation, ensure the input voltage is higher than the sum of the output voltage and the maximum dropout voltage expected for a given application as expressed in Equation 4.

(EQ. 4)

$$V_{IN} > V_{OUT} + V_{DROPOUT(max)}$$

## 7.2 Programming the Output Voltage

The output voltage can be programmed using convenient output voltage set pins on the IC or traditional external feedback resistors.

### 7.2.1 Internal Feedback Resistors and Output Voltage Set Pins

The RAA214048 has convenient IC pins that connect an array of internal FB resistors to program the output voltage easily. In this configuration, the output voltage can be programmed from 0.8V to 3.95V in steps of 50mV.

*Important:* To use the internal FB resistors and convenient IC voltage set pins to program the output voltage, the SNS pin must be shorted to the VOUT(s) pins.

The Voltage Set pins are labeled 50mV (Pin 5), 100mV (pin 6), 200mV (Pin 7), 400mV (Pin 9), 800mV (Pin 10) and 1.6V (Pin 11). These pins are either grounded or left floating using the PCB layout. Grounding these pins adds the voltages assigned to each grounded pin to the 0.8V reference voltage as shown in Equation 5.

(EQ. 5)

$$V_{OLIT} = 0.8V + \Sigma (Grounded Output Voltage Set Pins)$$

For example, to program the output voltage to 3.3V, ground the 1.6V, 800mV, and 100mV pins. The sum of these three pins (2.5V) added to the 0.8V reference equals the required 3.3V output. Figure 44 through Figure 53 illustrate how to connect the LDO output voltage set pins to get various common output voltage rails.

Figure 44. Internal FB Resistor Configuration for 0.8V (V<sub>OLT</sub> = 0.8VREF)

Figure 45. Internal FB Resistor Configuration for 1V (V<sub>OLT</sub> = 0.8VREF + 200mV)

Figure 46. Internal FB Resistor Configuration for 1.2V  $(V_{OUT} = 0.8VREF + 400mV)$

Figure 47. Internal FB Resistor Configuration for 1.5V (V<sub>OUT</sub> = 0.8VREF + 400mV + 200mV + 100mV)

Figure 48. Internal FB Resistor Configuration for 1.6V (V<sub>OUT</sub> = 0.8VREF + 800mV)

Figure 49. Internal FB Resistor Configuration for 1.8V (V<sub>OUT</sub> = 0.8VREF + 800mV + 200mV)

Figure 50. Internal FB Resistor Configuration for 2.5V (V<sub>OUT</sub> = 0.8VREF + 1.6V + 100mV)

Figure 51. Internal FB Resistor Configuration for 3V (V<sub>OUT</sub> = 0.8VREF + 1.6V + 400mV + 200mV)

Figure 52. Internal FB Resistor Configuration for 3.3V (V<sub>OUT</sub> = 0.8VREF + 1.6V + 800mV + 100mV)

Figure 53. Internal FB Resistor Configuration for 3.6V (V<sub>OUT</sub> = 0.8VREF + 1.6V + 800mV + 400mV)

Table 2 shows all possible output voltages and the corresponding Voltage Set pins to short to GND or leave floating.

Table 2. Output Voltage Set Pin Configuration and corresponding Output Voltages ( $V_{REF} = 0.8V$ )

| V <sub>OUT</sub> (V) | 50mV | 100mV | 200mV | 400mV | 800mV | 1.6V | V <sub>OUT</sub> (V) | 50mV | 100mV | 200mV | 400mV | 800mV | 1.6V |

|----------------------|------|-------|-------|-------|-------|------|----------------------|------|-------|-------|-------|-------|------|

| 0.80                 | Open | Open  | Open  | Open  | Open  | Open | 2.40                 | Open | Open  | Open  | Open  | Open  | GND  |

| 0.85                 | GND  | Open  | Open  | Open  | Open  | Open | 2.45                 | GND  | Open  | Open  | Open  | Open  | GND  |

| 0.90                 | Open | GND   | Open  | Open  | Open  | Open | 2.50                 | Open | GND   | Open  | Open  | Open  | GND  |

| 0.95                 | GND  | GND   | Open  | Open  | Open  | Open | 2.55                 | GND  | GND   | Open  | Open  | Open  | GND  |

| 1.00                 | Open | Open  | GND   | Open  | Open  | Open | 2.60                 | Open | Open  | GND   | Open  | Open  | GND  |

| 1.05                 | GND  | Open  | GND   | Open  | Open  | Open | 2.65                 | GND  | Open  | GND   | Open  | Open  | GND  |

| 1.10                 | Open | GND   | GND   | Open  | Open  | Open | 2.70                 | Open | GND   | GND   | Open  | Open  | GND  |

| 1.15                 | GND  | GND   | GND   | Open  | Open  | Open | 2.75                 | GND  | GND   | GND   | Open  | Open  | GND  |

| 1.20                 | Open | Open  | Open  | GND   | Open  | Open | 2.80                 | Open | Open  | Open  | GND   | Open  | GND  |

| 1.25                 | GND  | Open  | Open  | GND   | Open  | Open | 2.85                 | GND  | Open  | Open  | GND   | Open  | GND  |

| 1.30                 | Open | GND   | Open  | GND   | Open  | Open | 2.90                 | Open | GND   | Open  | GND   | Open  | GND  |

| 1.35                 | GND  | GND   | Open  | GND   | Open  | Open | 2.95                 | GND  | GND   | Open  | GND   | Open  | GND  |

| 1.40                 | Open | Open  | GND   | GND   | Open  | Open | 3.00                 | Open | Open  | GND   | GND   | Open  | GND  |

| 1.45                 | GND  | Open  | GND   | GND   | Open  | Open | 3.05                 | GND  | Open  | GND   | GND   | Open  | GND  |

| 1.50                 | Open | GND   | GND   | GND   | Open  | Open | 3.10                 | Open | GND   | GND   | GND   | Open  | GND  |

| 1.55                 | GND  | GND   | GND   | GND   | Open  | Open | 3.15                 | GND  | GND   | GND   | GND   | Open  | GND  |

| 1.60                 | Open | Open  | Open  | Open  | GND   | Open | 3.20                 | Open | Open  | Open  | Open  | GND   | GND  |

| 1.65                 | GND  | Open  | Open  | Open  | GND   | Open | 3.25                 | GND  | Open  | Open  | Open  | GND   | GND  |

| 1.70                 | Open | GND   | Open  | Open  | GND   | Open | 3.30                 | Open | GND   | Open  | Open  | GND   | GND  |

| 1.75                 | GND  | GND   | Open  | Open  | GND   | Open | 3.35                 | GND  | GND   | Open  | Open  | GND   | GND  |

| 1.80                 | Open | Open  | GND   | Open  | GND   | Open | 3.40                 | Open | Open  | GND   | Open  | GND   | GND  |

| 1.85                 | GND  | Open  | GND   | Open  | GND   | Open | 3.45                 | GND  | Open  | GND   | Open  | GND   | GND  |

| 1.90                 | Open | GND   | GND   | Open  | GND   | Open | 3.50                 | Open | GND   | GND   | Open  | GND   | GND  |

| 1.95                 | GND  | GND   | GND   | Open  | GND   | Open | 3.55                 | GND  | GND   | GND   | Open  | GND   | GND  |

| 2.00                 | Open | Open  | Open  | GND   | GND   | Open | 3.60                 | Open | Open  | Open  | GND   | GND   | GND  |

| 2.05                 | GND  | Open  | Open  | GND   | GND   | Open | 3.65                 | GND  | Open  | Open  | GND   | GND   | GND  |

| 2.10                 | Open | GND   | Open  | GND   | GND   | Open | 3.70                 | Open | GND   | Open  | GND   | GND   | GND  |

| 2.15                 | GND  | GND   | Open  | GND   | GND   | Open | 3.75                 | GND  | GND   | Open  | GND   | GND   | GND  |

| 2.20                 | Open | Open  | GND   | GND   | GND   | Open | 3.80                 | Open | Open  | GND   | GND   | GND   | GND  |

Table 2. Output Voltage Set Pin Configuration and corresponding Output Voltages (V<sub>REF</sub> = 0.8V) (Cont.)

| V <sub>OUT</sub> (V) | 50mV | 100mV | 200mV | 400mV | 800mV | 1.6V |

|----------------------|------|-------|-------|-------|-------|------|

| 2.25                 | GND  | Open  | GND   | GND   | GND   | Open |

| 2.30                 | Open | GND   | GND   | GND   | GND   | Open |

| 2.35                 | GND  | GND   | GND   | GND   | GND   | Open |

| V <sub>OUT</sub><br>(V) | 50mV | 100mV | 200mV | 400mV | 800mV | 1.6V |

|-------------------------|------|-------|-------|-------|-------|------|

| 3.85                    | GND  | Open  | GND   | GND   | GND   | GND  |

| 3.90                    | Open | GND   | GND   | GND   | GND   | GND  |

| 3.95                    | GND  | GND   | GND   | GND   | GND   | GND  |

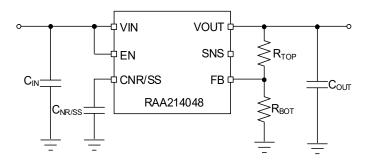

#### 7.2.2 External Feedback Resistors

The RAA214048 output voltage can be programmed down to 0.8V and up to 5.1V using external FB resistors ( $R_{TOP}$  and  $R_{ROT}$ ) as shown in Figure 54.

Important: The SNS pin must be left floating to use the external FB resistors to program the output voltage.

Figure 54. Simplified External FB Resistor Schematic

Use Equation 6 to calculate V<sub>OUT</sub>.

**(EQ. 6)**

$$V_{OUT} = 0.8V \times \left(1 + \frac{R_{TOP}}{R_{BOT}}\right)$$

Calculate the R<sub>BOT</sub> resistor for any target output voltage by rearranging Equation 6 to get Equation 7.

(EQ. 7)

$$R_{BOT} = R_{TOP} \times \left( \frac{0.8V}{V_{OUT} - 0.8V} \right)$$

Similarly, use Equation 8 to calculate the R<sub>TOP</sub> resistor.

(EQ. 8)

$$R_{TOP} = R_{BOT} \times \left( \frac{V_{OUT}}{0.8V} - 1 \right)$$

Table 3 lists recommended FB resistor values to obtain some standard output voltages for the RAA214048. The FB resistors are commercially available in 1% tolerances. This list is non-exhaustive.

Table 3. Recommended FB Resistor Values for Common Output Voltages ( $V_{REF} = 0.8V$ )