**Product Discontinuance Notice – Last Time Buy Expires on (12/3/2013)**

**DATASHEET**

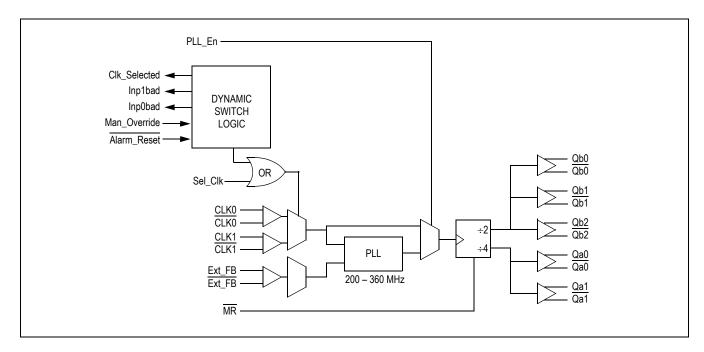

The MPC99J93 is a PLL clock driver designed specifically for redundant clock tree designs. The device receives two differential LVPECL clock signals from which it generates five new differential LVPECL clock outputs. Two of the output pairs regenerate the input signals frequency and phase while the other three pairs generate 2x, phase aligned clock outputs.

#### **Features**

- Fully Integrated PLL

- · Intelligent Dynamic Clock Switch

- · LVPECL Clock Outputs

- LVCMOS Control I/O

- 3.3-V Operation

- 32-Lead LQFP Packaging, Pb-Free

### **Functional Description**

The MPC99J93 Intelligent Dynamic Clock Switch (IDCS) circuit continuously monitors both input CLK signals. Upon detection of a failure (CLK stuck HIGH or LOW for at least 1 period), the INP\_BAD for that CLK will be latched (H). If that CLK is the primary clock, the IDCS will switch to the good secondary clock and phase/frequency alignment will occur with minimal output phase disturbance. The typical phase bump caused by a failed clock is eliminated. (See Applications Information section).

## **MPC99J93**

INTELLIGENT DYNAMIC CLOCK SWITCH PLL CLOCK DRIVER

AC SUFFIX 32-LEAD LQFP PACKAGE Pb-FREE PACKAGE CASE 873A-03

Figure 1. Block Diagram

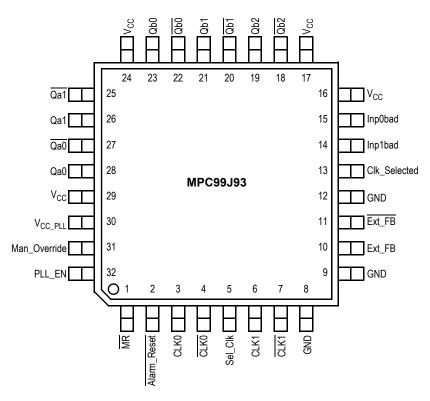

Figure 2. 32-Lead Pinout (Top View)

**Table 1. Pin Descriptions**

| Pin Name                 | I/O                          | Pin Definition                                                                                                                                                             |

|--------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK0, CLK0<br>CLK1, CLK1 | LVPECL Input<br>LVPECL Input | Differential PLL clock reference (CLK0 pulldown, CLK0 pullup) Differential PLL clock reference (CLK1 pulldown, CLK1 pullup)                                                |

| Ext_FB, Ext_FB           | LVPECL Input                 | Differential PLL feedback clock (Ext_FB pulldown, Ext_FB pullup)                                                                                                           |

| Qa0:1, Qa0:1             | LVPECL Output                | Differential 1x output pairs. Connect one QAx pair to Ext_FB.                                                                                                              |

| Qb0:2, Qb0:2             | LVPECL Output                | Differential 2x output pairs                                                                                                                                               |

| Inp0bad                  | LVCMOS Output                | Indicates detection of a bad input reference clock 0 with respect to the feedback signal. The output is active HIGH and will remain HIGH until the alarm reset is asserted |

| Inp1bad                  | LVCMOS Output                | Indicates detection of a bad input reference clock 1 with respect to the feedback signal. The output is active HIGH and will remain HIGH until the alarm reset is asserted |

| Clk_Selected             | LVCMOS Output                | '0' if clock 0 is selected, '1' if clock 1 is selected                                                                                                                     |

| Alarm_Reset              | LVCMOS Input                 | '0' will reset the input bad flags and align Clk_Selected with Sel_Clk. The input is "one-shotted" (50kΩ pullup)                                                           |

| Sel_Clk                  | LVCMOS Input                 | '0' selects CLK0, '1' selects CLK1 (50kΩ pulldown)                                                                                                                         |

| Manual_Override          | LVCMOS Input                 | '1' disables internal clock switch circuitry (50kΩ pulldown)                                                                                                               |

| PLL_En                   | LVCMOS Input                 | '0' bypasses selected input reference around the phase-locked loop (50k $\Omega$ pullup)                                                                                   |

| MR                       | LVCMOS Input                 | '0' resets the internal dividers forcing Q outputs LOW. Asynchronous to the clock (50kΩ pullup)                                                                            |

| V <sub>CCA</sub>         | Power Supply                 | PLL power supply                                                                                                                                                           |

| V <sub>CC</sub>          | Power Supply                 | Digital power supply                                                                                                                                                       |

| GNDA                     | Power Supply                 | PLL ground                                                                                                                                                                 |

| GND                      | Power Supply                 | Digital ground                                                                                                                                                             |

Table 2. Absolute Maximum Ratings<sup>(1)</sup>

| Symbol           | Characteristics     | Min  | Max                  | Unit |

|------------------|---------------------|------|----------------------|------|

| V <sub>CC</sub>  | Supply Voltage      | -0.3 | 3.9                  | V    |

| V <sub>IN</sub>  | DC Input Voltage    | -0.3 | V <sub>CC</sub> +0.3 | V    |

| V <sub>OUT</sub> | DC Output Voltage   | -0.3 | V <sub>CC</sub> +0.3 | V    |

| I <sub>IN</sub>  | DC Input Current    |      | ±20                  | mA   |

| I <sub>OUT</sub> | DC Output Current   |      | ±50                  | mA   |

| T <sub>S</sub>   | Storage Temperature | -65  | 125                  | °C   |

<sup>1.</sup> Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated conditions is not implied.

**Table 3. General Specifications**

| Symbol            | Characteristics                                                                                                  | Min  | Тур                                                                          | Max                                                                          | Unit                                    | Condition                                                                                                                                                |

|-------------------|------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>TT</sub>   | Output Termination Voltage                                                                                       |      | V <sub>CC</sub> – 2                                                          |                                                                              | V                                       |                                                                                                                                                          |

| MM                | ESD Protection (Machine model)                                                                                   | 175  |                                                                              |                                                                              | ٧                                       |                                                                                                                                                          |

| НВМ               | ESD Protection (Human body model)                                                                                | 1500 |                                                                              |                                                                              | V                                       |                                                                                                                                                          |

| CDM               | ESD Protection (Charged device model)                                                                            | 1000 |                                                                              |                                                                              | V                                       |                                                                                                                                                          |

| LU                | Latch-Up Immunity                                                                                                | 100  |                                                                              |                                                                              | mA                                      |                                                                                                                                                          |

| C <sub>IN</sub>   | Input Capacitance                                                                                                |      | 4.0                                                                          |                                                                              | pF                                      | Inputs                                                                                                                                                   |

| θЈΑ               | Thermal Resistance Junction to Ambient JESD 51-3, single layer test board  JESD 51-6, 2S2P multilayer test board |      | 83.1<br>73.3<br>68.9<br>63.8<br>57.4<br>59.0<br>54.4<br>52.5<br>50.4<br>47.8 | 86.0<br>75.4<br>70.9<br>65.3<br>59.6<br>60.6<br>55.7<br>53.8<br>51.5<br>48.8 | °C/W °C/W °C/W °C/W °C/W °C/W °C/W °C/W | Natural convection<br>100 ft/min<br>200 ft/min<br>400 ft/min<br>800 ft/min<br>Natural convection<br>100 ft/min<br>200 ft/min<br>400 ft/min<br>800 ft/min |

| $\theta_{\sf JC}$ | Thermal Resistance Junction to Case                                                                              |      | 23.0                                                                         | 26.3                                                                         | °C/W                                    | MIL-SPEC 883E<br>Method 1012.1                                                                                                                           |

| TJ                | Operating Junction Temperature <sup>(1)</sup> (continuous operation) MTBF = 9.1 years                            |      |                                                                              | 110                                                                          | °C                                      |                                                                                                                                                          |

<sup>1.</sup> Operating junction temperature impacts device life time. Maximum continuous operating junction temperature should be selected according to the application life time requirements (See application note AN1545 for more information). The device AC and DC parameters are specified up to 110°C junction temperature allowing the MPC99J93 to be used in applications requiring industrial temperature range. It is recommended that users of the MPC99J93 employ thermal modeling analysis to assist in applying the junction temperature specifications to their particular application.

Table 4. DC Characteristics (V $_{CC}$  = 3.3 V ± 5%, T $_{A}$  = -40° to +85°C)

| Symbol              | Characteristics                                 | Min                   | Тур                   | Max                   | Unit | Condition                                |

|---------------------|-------------------------------------------------|-----------------------|-----------------------|-----------------------|------|------------------------------------------|

| LVCMOS C            | ontrol Inputs (MR, PLL_En, Sel_Clk, Mai         | n_Override, Alarm     | n_Reset)              |                       | 1    |                                          |

| V <sub>IH</sub>     | Input High Voltage                              | 2.0                   |                       | V <sub>CC</sub> + 0.3 | V    |                                          |

| V <sub>IL</sub>     | Input Low Voltage                               |                       |                       | 0.8                   | V    |                                          |

| I <sub>IN</sub>     | Input Current <sup>(1)</sup>                    |                       |                       | ±100                  | μА   | V <sub>IN</sub> = V <sub>CC</sub> or GND |

| LVCMOS C            | ontrol Outputs (Clk_selected, Inp0bad, Ir       | np1bad)               |                       |                       | 1    |                                          |

| V <sub>OH</sub>     | Output High Voltage                             | 2.0                   |                       |                       | V    | I <sub>OH</sub> = -24 mA                 |

| V <sub>OL</sub>     | Output Low Voltage                              |                       |                       | 0.55                  | V    | I <sub>OL</sub> = 24 mA                  |

| LVPECL CIO          | ock Inputs (CLK0, CLK1, Ext_FB) <sup>(2)</sup>  | 1                     |                       |                       | I.   |                                          |

| $V_{PP}$            | DC Differential Input Voltage <sup>(3)</sup>    | 0.1                   |                       | 1.3                   | V    | Differential operation                   |

| $V_{CMR}$           | Differential Cross Point Voltage <sup>(4)</sup> | V <sub>CC</sub> -1.8  |                       | V <sub>CC</sub> -0.3  | V    | Differential operation                   |

| I <sub>IN</sub>     | Input Current <sup>(1)</sup>                    |                       |                       | ±100                  | μА   | V <sub>IN</sub> = V <sub>CC</sub> or GND |

| LVPECL CIO          | ock Outputs (QA[1:0], QB[2:0])                  |                       |                       |                       | 1    |                                          |

| V <sub>OH</sub>     | Output High Voltage                             | V <sub>CC</sub> -1.20 | V <sub>CC</sub> -0.95 | V <sub>CC</sub> -0.70 | V    | Termination 50 $\Omega$ to $V_{TT}$      |

| V <sub>OL</sub>     | Output Low Voltage                              | V <sub>CC</sub> -1.90 | V <sub>CC</sub> -1.75 | V <sub>CC</sub> -1.45 | V    | Termination 50 $\Omega$ to $V_{TT}$      |

| Supply Curr         | ent                                             | •                     | <u>'</u>              | •                     | •    |                                          |

| I <sub>GND</sub>    | Maximum Power Supply Current                    |                       |                       | 180                   | mA   | GND pins                                 |

| I <sub>CC_PLL</sub> | Maximum PLL Supply Current                      |                       |                       | 15                    | mA   | V <sub>CC_PLL</sub> pin                  |

<sup>1.</sup> Inputs have internal pull-up/pull-down resistors affecting the input current.

<sup>2.</sup> Clock inputs driven by differential LVPECL compatible signals.

V<sub>PP</sub> is the minimum differential input voltage swing required to maintain AC characteristics.

V<sub>CMR</sub> (DC) is the crosspoint of the differential input signal. Functional operation is obtained when the crosspoint is within the V<sub>CMR</sub> (DC) range and the input swing lies within the V<sub>PP</sub> (DC) specification.

Table 5. AC Characteristics (V<sub>CC</sub> = 3.3 V  $\pm$  5%, T<sub>A</sub> =  $-40^{\circ}$ C to  $+85^{\circ}$ C)<sup>(1)</sup>

| Symbol                          | Characteristics                                                                                                      | Min                  | Тур                    | Max                    | Unit                 | Condition                |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------|------------------------|------------------------|----------------------|--------------------------|

| f <sub>ref</sub>                | Input Reference Frequency ÷4 feedback                                                                                | 50                   |                        | 90                     | MHz                  | PLL locked               |

| f <sub>VCO</sub>                | VCO Frequency Range <sup>(2)</sup> ÷4 feedback                                                                       | 200                  |                        | 360                    | MHz                  |                          |

| f <sub>MAX</sub>                | Output Frequency QA[1:0] QB[2:0]                                                                                     | 50<br>100            |                        | 90<br>180              | MHz<br>MHz           | PLL locked               |

| f <sub>refDC</sub>              | Reference Input Duty Cycle                                                                                           | 25                   |                        | 75                     | %                    |                          |

| t <sub>(∅)</sub>                | Propagation Delay SPO, static phase offset <sup>(3)</sup> CLK0, CLK1 to any Q                                        | -0.15<br>0.9         |                        | +0.17<br>1.8           | ns<br>ns             | PLL_EN = 1<br>PLL_EN = 0 |

| V <sub>PP</sub>                 | Differential Input Voltage <sup>(4)</sup> (peak-to-peak)                                                             | 0.25                 |                        | 1.3                    | V                    |                          |

| V <sub>CMR</sub>                | Differential Input Crosspoint Voltage <sup>(5)</sup>                                                                 | V <sub>CC</sub> -1.7 |                        | V <sub>CC</sub> -0.3   | V                    |                          |

| t <sub>sk(O)</sub>              | Output-to-Output Skew within QA[2:0] or QB[1:0] within device                                                        |                      |                        | 50<br>80               | ps<br>ps             |                          |

| $\Delta_{	extsf{per/cycle}}$    | Rate of Change of Period QA[1:0] <sup>(6)</sup> QB[2:0] <sup>(6)</sup> QA[1:0] <sup>(7)</sup> QB[2:0] <sup>(7)</sup> |                      | 20<br>10<br>200<br>100 | 50<br>25<br>400<br>200 | ps<br>ps<br>ps<br>ps |                          |

| DC                              | Output Duty Cycle                                                                                                    | 45                   | 50                     | 55                     | %                    |                          |

| t <sub>JIT(CC)</sub>            | Cycle-to-Cycle Jitter RMS (1 $\sigma$ )                                                                              |                      | 25                     |                        | ps                   |                          |

| t <sub>LOCK</sub>               | Maximum PLL Lock Time                                                                                                |                      |                        | 10                     | ms                   |                          |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall Time                                                                                                | 0.05                 |                        | 0.70                   | ns                   | 20% to 80%               |

- 1. AC characteristics apply for parallel output termination of 50  $\Omega$  to  $V_{CC}$  2 V.

- 2. The input reference frequency must match the VCO lock range divided by the feedback divider ratio (FB):  $f_{ref} = f_{VCO} \div FB$ .

- 3. CLK0, CLK1 to Ext\_FB.

- 4. V<sub>PP</sub> is the minimum differential input voltage swing required to maintain AC characteristics including SPO and device-to-device skew. Applicable to CLK0, CLK1 and Ext\_FB.

- V<sub>CMR</sub> (AC) is the crosspoint of the differential input signal. Normal AC operation is obtained when the crosspoint is within the V<sub>CMR</sub> (AC) range and the input swing lies within the V<sub>PP</sub> (AC) specification. Violation of V<sub>CMR</sub> (AC) or V<sub>PP</sub> (AC) impacts the SPO, device and part-to-part skew. Applicable to CLK0, CLK1 and Ext FB.

- 6. Specification holds for a clock switch between two input signals (CLK0, CLK1) no greater than 400 ps out of phase. Delta period change per cycle is averaged over the clock switch excursion.

- 7. Specification holds for a clock switch between two input signals (CLK0, CLK1) at any phase difference (±180°). Delta period change per cycle is averaged over the clock switch excursion.

#### APPLICATIONS INFORMATION

The MPC99J93 is a dual clock PLL with on-chip Intelligent Dynamic Clock Switch (IDCS) circuitry.

#### **Definitions**

**primary clock:** The input CLK selected by Sel\_Clk. **secondary clock:** The input CLK NOT selected by Sel\_Clk.

**PLL reference signal:** The CLK selected as the PLL reference signal by Sel\_Clk or IDCS. (IDCS can override Sel\_Clk).

#### **Status Functions**

**Clk\_Selected:** Clk\_Selected (L) indicates CLK0 is selected as the PLL reference signal. Clk\_Selected (H) indicates CLK1 is selected as the PLL reference signal.

**INP\_BAD:** Latched (H) when it's CLK is stuck (H) or (L) for at least one Ext\_FB period (Pos to Pos or Neg to Neg). Cleared (L) on assertion of Alarm\_Reset.

#### **Control Functions**

**Sel\_Clk**: Sel\_Clk (L) selects CLK0 as the primary clock. Sel\_Clk (H) selects CLK1 as the primary clock.

**Alarm\_Reset:** Asserted by a negative edge. Generates a one-shot reset pulse that clears INPUT\_BAD latches and Clk Selected latch.

**PLL\_En:** While (L), the PLL reference signal is substituted for the VCO output.

**MR:** While (L), internal dividers are held in reset which holds all Q outputs LOW.

#### Man Override (H)

(IDCS is disabled, PLL functions normally). PLL reference signal (as indicated by Clk\_Selected) will always be the CLK selected by Sel\_Clk. The status function INP\_BAD is active in Man Override (H) and (L).

#### Man Override (L)

(IDCS is enabled, PLL functions enhanced). The first CLK to fail will latch it's INP\_BAD (H) status flag and select the other input as the Clk\_Selected for the PLL reference clock. Once latched, the Clk\_Selected and INP\_BAD remain latched until assertion of Alarm\_Reset which clears all latches (INP\_BADs are cleared and Clk\_Selected = Sel\_Clk). NOTE: If both CLKs are bad when Alarm\_Reset is asserted,

both INP\_BADs will be latched (H) after one Ext\_FB period and Clk\_Selected will be latched (L) indicating CLK0 is the PLL reference signal. While neither INP\_BAD is latched (H), the Clk\_Selected can be freely changed with Sel\_Clk. Whenever a CLK switch occurs, (manually or by IDCS), following the next negative edge of the newly selected PLL reference signal, the next positive edge pair of Ext\_FB and the newly selected PLL reference signal will slew to alignment.

To calculate the overall uncertainty between the input CLKs and the outputs from multiple MPC99J93's, the following procedure should be used. Assuming that the input CLKs to all MPC9993's are exactly in phase, the total uncertainty will be the sum of the static phase offset, max I/O jitter, and output to output skew.

During a dynamic switch, the output phase between two devices may be increased for a short period of time. If the two input CLKs are 400ps out of phase, a dynamic switch of an MPC99J93 will result in an instantaneous phase change of 400ps to the PLL reference signal without a corresponding change in the output phase (due to the limited response of the PLL). As a result, the I/O phase of a device, undergoing this switch, will initially be 400ps and diminish as the PLL slews to its new phase alignment. This transient timing issue should be considered when analyzing the overall skew budget of a system.

#### Hot insertion and withdrawal

In PECL applications, a powered up driver will experience a low impedance path through an MPC99J93 input to its powered down  $V_{CC}$  pins. In this case, a 100 ohm series resistance should be used in front of the input pins to limit the driver current. The resistor will have minimal impact on the rise and fall times of the input signals.

#### **Acquiring Frequency Lock**

- While the MPC99J93 is receiving a valid CLK signal, assert Man Override HIGH.

- The PLL will phase and frequency lock within the specified lock time.

- Apply a HIGH to LOW transition to Alarm\_Reset to reset Input Bad flags.

- De-assert Man\_Override LOW to enable Intelligent Dynamic Clock Switch mode.

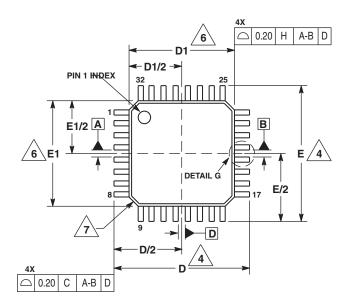

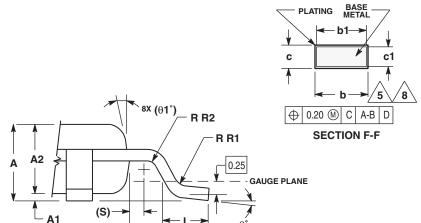

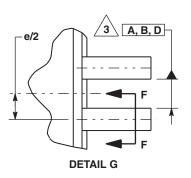

#### **PACKAGE DIMENSIONS**

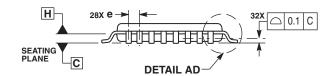

**DETAIL AD**

**CASE 873A-03 ISSUE B** 32-LEAD LQFP PACKAGE

- NOTES:

1. DIMENSIONS ARE IN MILLIMETERS.

2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994.

3. DATUMS A, B, AND D TO BE DETERMINED AT DATUM PLANE H.

4. DIMENSIONS D AND E TO BE DETERMINED AT SEATING PLANE C.

5. DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION. AND ADMORE THAN 0.08-mm. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE POOT. MINIMUM SPACE BETWEEN PROTRUSION AND DAJACENT LEAD OR PROTRUSION: 0.07-mm.

6. DIMENSIONS DI AND E1 DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25-mm PER SIDE. DI AND E1 AD NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25-mm PER SIDE. DI AND E1 AD NOT INCLUDING MOLD MISMATCH.

2. EXACT SHAPE OF EACH CORNER IS OPTIONAL.

8. THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.1-mm AND 0.25-mm FROM THE LEAD TIP.

|     | MILLIMETERS |      |  |  |  |

|-----|-------------|------|--|--|--|

| DIM | MIN         | MAX  |  |  |  |

| Α   | 1.40        | 1.60 |  |  |  |

| A1  | 0.05        | 0.15 |  |  |  |

| A2  | 1.35        | 1.45 |  |  |  |

| b   | 0.30        | 0.45 |  |  |  |

| b1  | 0.30        | 0.40 |  |  |  |

| С   | 0.09        | 0.20 |  |  |  |

| c1  | 0.09 0.16   |      |  |  |  |

| D   | 9.00 BSC    |      |  |  |  |

| D1  | 7.00 BSC    |      |  |  |  |

| е   | 0.80 BSC    |      |  |  |  |

| Е   | 9.00        | BSC  |  |  |  |

| E1  | 7.00        | BSC  |  |  |  |

| L   | 0.50        | 0.70 |  |  |  |

| L1  | 1.00        | REF  |  |  |  |

| q   | 0° 7°       |      |  |  |  |

| q1  | 12 REF      |      |  |  |  |

| R1  | 0.08        | 0.20 |  |  |  |

| R2  | 0.08        |      |  |  |  |

| S   | 0.20 REF    |      |  |  |  |

# **Revision History Sheet**

| Rev | Table | Page | Description of Change                                                | Date     |

|-----|-------|------|----------------------------------------------------------------------|----------|

| 4   |       | 1    | Product Discontinuance Notice – Last Time Buy Expires on (12/3/2013) | 2/6/2013 |

|     |       |      |                                                                      |          |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.