# Low EMI, Spread Modulating, Clock Generator

#### Features:

- ICS91718 is a Spread Spectrum Clock targeted for Mobile PC and LCD panel applications.

Generates an EMI optimized clock signal (EMI peak reduction of 7-14 dB on 3rd-19th harmonics) through use of Spread Spectrum techniques.

- ICS91718 operates with input frequencies at 14.318 - 80 MHz.

- Spread modulation frequency range is 20kHz to 40kHz.

- Spread percentage/type programming through I<sup>2</sup>C.

## **Specifications:**

- Supply Voltages: V<sub>DD</sub> = 3.3V ±0.3V

- Cyc to Cyc jitter: <150ps</li>

- Output duty cycle 45/55%

- Guarantees +85°C operational condition

- 8-pin SOIC (150 mil) package

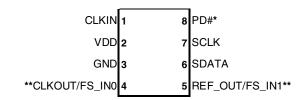

### **Pin Configuration**

### 8-pin SOIC & TSSOP

Notes:

- \* Internal pull-up resistor

- \*\* Internal pull-down resistor

## **Input Select Functionality**

| FS_IN1 | FS_IN0 | MHz          | SPREAD %              |

|--------|--------|--------------|-----------------------|

| 0      | 0      | 14.318 in    | -1.0% down sprd       |

| U      | U      | 48.00 out    | -1.0% down spru       |

| 0      | 1      | 14.318 in    | -1.0% down sprd       |

| U      | I      | 66.66 out    | -1.0% down spru       |

| 4      | 0      | 48.00 in/out | -1.0% down sprd       |

| 1      | U      | 66.66 in/out | -1.0% down spru       |

| -1     | 1      | 48.00 in/out | +/-1.0% center sprd   |

| '      | '      | 66.66 in/out | +/-1.0 % certier spru |

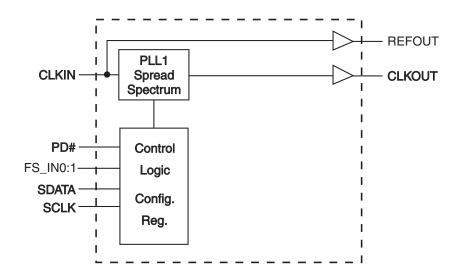

### **Block Diagram**

# **Pin Descriptions**

| PIN# | PIN NAME         | PIN TYPE          | DESCRIPTION                                                                                                                                                                                                                     |  |  |

|------|------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1    | CLKIN            | INPUT Input clock |                                                                                                                                                                                                                                 |  |  |

| 2    | VDD              | POWER             | Power supply, nominal 3.3V                                                                                                                                                                                                      |  |  |

| 3    | GND              | POWER             | Ground pin.                                                                                                                                                                                                                     |  |  |

| 4    |                  |                   | CLKOUT modulated clock output FS_IN0 latched input, selects modulation percentage/type                                                                                                                                          |  |  |

| 5    | REF_OUT/FS_IN1** | I/O               | REF_OUT, unmodulated reference clock output FS_IN1 latched input, selects modulation percentage/type                                                                                                                            |  |  |

| 6    | SDATA            | I/O               | Data pin for I2C circuitry 5V tolerant                                                                                                                                                                                          |  |  |

| 7    | SCLK             | INPUT             | Clock pin of I2C circuitry 5V tolerant                                                                                                                                                                                          |  |  |

| 8    | PD#*             | INPUT             | Asynchronous active low input pin used to power down the device into a low power state. The internal clocks are disabled and the VCO and the crystal are stopped. The latency of the power down will not be greater than 1.8ms. |  |  |

<sup>\*</sup> Internal Pull-Up Resistor

<sup>\*\*</sup> Internal Pull-Down Resistor

Table 1: Frequency Configuration Table (See I2C Byte 0)

|            | FS4 | FS3 | FS2 | FS1 | FS0 | Sprd Type        | Sprd % |

|------------|-----|-----|-----|-----|-----|------------------|--------|

|            | 0   | 0   | 0   | 0   | 0   |                  | 0.80   |

|            | 0   | 0   | 0   | 0   | 1   |                  | 1.00   |

|            | 0   | 0   | 0   | 1   | 0   | DOWN             | 1.25   |

|            | 0   | 0   | 0   | 1   | 1   | SPREAD           | 1.50   |

|            | 0   | 0   | 1   | 0   | 0   | (-)              | 1.75   |

| 14in/48out | 0   | 0   | 1   | 0   | 1   |                  | 2.00   |

|            | 0   | 0   | 1   | 1   | 0   |                  | 2.50   |

|            | 0   | 0   | 1   | 1   | 1   |                  | 0.60   |

|            | 0   | 1   | 0   | 0   | 0   | CENTER           | 1.00   |

|            | 0   | 1   | 0   | 0   | 1   | SPREAD           | 1.25   |

|            | 0   | 1   | 0   | 1   | 0   | (+/-)            | 1.50   |

|            | 0   | 1   | 0   | 1   | 1   |                  | 2.00   |

|            | 0   | 1   | 1   | 0   | 0   | DOWN             | 1.25   |

| 14in/66out | 0   | 1   | 1   | 0   | 1   | SPREAD           | 1.00   |

|            | 0   | 1   | 1   | 1   | 0   |                  | 1.50   |

|            | 0   | 1   | 1   | 1   | 1   | (-)              | 2.00   |

|            | 1   | 0   | 0   | 0   | 0   |                  | 0.80   |

|            | 1   | 0   | 0   | 0   | 1   |                  | 1.00   |

|            | 1   | 0   | 0   | 1   | 0   | DOWN             | 1.25   |

|            | 1   | 0   | 0   | 1   | 1   | SPREAD           | 1.50   |

|            | 1   | 0   | 1   | 0   | 0   |                  | 1.75   |

|            | 1   | 0   | 1   | 0   | 1   | (-)              | 2.00   |

|            | 1   | 0   | 1   | 1   | 0   |                  | 2.50   |

| 48in/48out | 1   | 0   | 1   | 1   | 1   |                  | 3.00   |

| 66in/66out | 1   | 1   | 0   | 0   | 0   |                  | 0.30   |

|            | 1   | 1   | 0   | 0   | 1   |                  | 0.40   |

|            | 1   | 1   | 0   | 1   | 0   | CENTER           | 0.50   |

|            | 1   | 1   | 0   | 1   | 1   | CENTER<br>SPREAD | 0.60   |

|            | 1   | 1   | 1   | 0   | 0   |                  | 0.80   |

|            | 1   | 1   | 1   | 0   | 1   | (+/-)            | 1.00   |

|            | 1   | 1   | 1   | 1   | 0   |                  | 1.25   |

|            | 1   | 1   | 1   | 1   | 1   |                  | 1.50   |

For 14.318 in 48.008 out default is...00001 For 14.318 in 66.66 out default is...01101 For 48/48 and 66/66 default is....10001

## General I<sup>2</sup>C serial interface information

The information in this section assumes familiarity with  $I^2C$  programming. For more information, contact ICS for an  $I^2C$  programming application note.

### **How to Write:**

- · Controller (host) sends a start bit.

- Controller (host) sends the write address D4 (41)

- ICS clock will acknowledge

- · Controller (host) sends a dummy command code

- ICS clock will acknowledge

- · Controller (host) sends a dummy byte count

- ICS clock will acknowledge

- Controller (host) starts sending first byte (Byte 0) through byte 6

- ICS clock will acknowledge each byte one at a time.

- · Controller (host) sends a Stop bit

| How to Write:      |                      |  |  |  |  |  |  |

|--------------------|----------------------|--|--|--|--|--|--|

| Controller (Host)  | ICS (Slave/Receiver) |  |  |  |  |  |  |

| Start Bit          |                      |  |  |  |  |  |  |

| Address            |                      |  |  |  |  |  |  |

| D4 <sub>(H)</sub>  |                      |  |  |  |  |  |  |

|                    | ACK                  |  |  |  |  |  |  |

| Dummy Command Code |                      |  |  |  |  |  |  |

|                    | ACK                  |  |  |  |  |  |  |

| Dummy Byte Count   |                      |  |  |  |  |  |  |

|                    | ACK                  |  |  |  |  |  |  |

| Byte 0             |                      |  |  |  |  |  |  |

|                    | ACK                  |  |  |  |  |  |  |

| Byte 1             |                      |  |  |  |  |  |  |

|                    | ACK                  |  |  |  |  |  |  |

| Byte 2             | 401/                 |  |  |  |  |  |  |

| D. t. O            | ACK                  |  |  |  |  |  |  |

| Byte 3             | ACK                  |  |  |  |  |  |  |

| Puto 4             | ACK                  |  |  |  |  |  |  |

| Byte 4             | ACK                  |  |  |  |  |  |  |

| Byte 5             | ACA                  |  |  |  |  |  |  |

| Бую о              | ACK                  |  |  |  |  |  |  |

| Byte 6             | 7.57                 |  |  |  |  |  |  |

| 2,100              | ACK                  |  |  |  |  |  |  |

| Byte 7             |                      |  |  |  |  |  |  |

| ,                  | ACK                  |  |  |  |  |  |  |

| Stop Bit           |                      |  |  |  |  |  |  |

### How to Read:

- · Controller (host) will send start bit.

- Controller (host) sends the read address D5 (H)

- ICS clock will acknowledge

- ICS clock will send the byte count

- Controller (host) acknowledges

- ICS clock sends first byte (Byte 0) through byte 7

- Controller (host) will need to acknowledge each byte

- · Controller (host) will send a stop bit

| How to            | Read:                |

|-------------------|----------------------|

| Controller (Host) | ICS (Slave/Receiver) |

| Start Bit         |                      |

| Address           |                      |

| D5 <sub>(H)</sub> |                      |

|                   | ACK                  |

|                   | Byte Count           |

| ACK               |                      |

|                   | Byte 0               |

| ACK               |                      |

|                   | Byte 1               |

| ACK               |                      |

|                   | Byte 2               |

| ACK               |                      |

|                   | Byte 3               |

| ACK               |                      |

|                   | Byte 4               |

| ACK               |                      |

|                   | Byte 5               |

| ACK               |                      |

|                   | Byte 6               |

| ACK               |                      |

|                   | Byte 7               |

| Stop Bit          |                      |

### **Notes:**

- 1. The ICS clock generator is a slave/receiver, I<sup>2</sup>C component. It can read back the data stored in the latches for verification. **Read-Back will support Intel PIIX4 "Block-Read" protocol**.

- 2. The data transfer rate supported by this clock generator is 100K bits/sec or less (standard mode)

- 3. The input is operating at 3.3V logic levels.

- 4. The data byte format is 8 bit bytes.

- 5. To simplify the clock generator I<sup>2</sup>C interface, the protocol is set to use only "Block-Writes" from the controller. The bytes must be accessed in sequential order from lowest to highest byte with the ability to stop after any complete byte has been transferred. The Command code and Byte count shown above must be sent, but the data is ignored for those two bytes. The data is loaded until a Stop sequence is issued.

- 6. At power-on, all registers are set to a default condition, as shown.

| BYTE  |       | Affected Pin  |                                                           | ш   | Bit Control |                |     |

|-------|-------|---------------|-----------------------------------------------------------|-----|-------------|----------------|-----|

| 0     | Pin # | Name          | Control Function                                          | ΤYΡ | 0           | 1              | PWD |

| Bit 7 | -     | N/A           | FS0                                                       | RW  |             |                | 1   |

| Bit 6 | -     | N/A           | FS1                                                       | RW  |             |                | 0   |

| Bit 5 |       | N/A           | FS2                                                       | RW  | See RON     | <b>M</b> TABLE | 0   |

| Bit 4 |       | N/A           | FS3                                                       | RW  |             |                | 0   |

| Bit 3 |       | N/A           | FS4                                                       | RW  |             |                | 0   |

| Bit 2 |       | N/A           | PD# Tri_Sate                                              | RW  | Hi-Z        | LOW            | 1   |

| Bit 1 |       | N/A           | Spread Enable                                             | RW  | OFF         | ON             | 1   |

| Bit 0 |       | HW/SW Control | Spread Spectrum Control<br>FS 2:4 Hard/Software<br>Select | RW  | HW          | SW             | 0   |

| BYTE  |       | Affected Pin    |                   | ш   | Bit Co  | ontrol |     |

|-------|-------|-----------------|-------------------|-----|---------|--------|-----|

| 1     | Pin # | Name            | Control Function  | ΤΥΡ | 0       | 1      | PWD |

| Bit 7 | 5     | REF_OUT         | REF_OUT ENABLE    | RW  | Disable | Enable | 1   |

| Bit 6 | 5     | REF_OUT         | Slew Rate REF-OUT | RW  | Nominal | Fast   | 1   |

| Bit 5 |       | FS_IN1 Readback | FS_IN1 Readback   | RW  | -       | -      | 1   |

| Bit 4 |       | FS_IN0 Readback | FS_IN0 Readback   | RW  | -       | -      | 1   |

| Bit 3 | 4     | CLK_OUT         | Slew Rate CLK-OUT | RW  | Nominal | Fast   | 1   |

| Bit 2 | 4     | CLK_OUT         | CLK_OUT_Enable    | RW  | Disable | Enable | 1   |

| Bit 1 |       | Reserved        | Reserved          | R   | -       | -      | 1   |

| Bit 0 |       | Reserved        | Reserved          | R   | -       | -      | 1   |

| BYTE  |      | Affected Pin |                         | ñ   | Bit Control |        |     |

|-------|------|--------------|-------------------------|-----|-------------|--------|-----|

| 2     | Pin# | Name         | <b>Control Function</b> | ΤΥP | 0           | 1      | PWD |

| Bit 7 | Х    | -            | RESERVED                | -   | -           | -      | 1   |

| Bit 6 | Х    | RESERVED     | RESERVED                | RW  | Disable     | Enable | 1   |

| Bit 5 | Х    | RESERVED     | RESERVED                | RW  | Disable     | Enable | 1   |

| Bit 4 | Х    | RESERVED     | RESERVED                | RW  | Disable     | Enable | 1   |

| Bit 3 | Х    | RESERVED     | RESERVED                | RW  | Disable     | Enable | 1   |

| Bit 2 | Х    | RESERVED     | RESERVED                | RW  | Disable     | Enable | 1   |

| Bit 1 | Х    | RESERVED     | RESERVED                | RW  | Disable     | Enable | 1   |

| Bit 0 | Х    | RESERVED     | RESERVED                | RW  | Disable     | Enable | 1   |

| BYTE  |       | Affected Pin |                  | Й    | Bit Co  | ontrol         |     |

|-------|-------|--------------|------------------|------|---------|----------------|-----|

| 3     | Pin # | Name         | Control Function | TYPE | 0       | 1              | PWD |

| Bit 7 | Χ     | RESERVED     | RESERVED         | RW   | Disable | Enable         | 1   |

| Bit 6 | Χ     | RESERVED     | RESERVED         | RW   | Disable | Enable         | 1   |

| Bit 5 | Х     | RESERVED     | RESERVED         | RW   | Freerun | Not<br>Freerun | 1   |

| Bit 4 | Χ     | RESERVED     | RESERVED         | RW   | Freerun | Not<br>Freerun | 1   |

| Bit 3 | Х     | RESERVED     | RESERVED         | RW   | Freerun | Not<br>Freerun | 1   |

| Bit 2 | Χ     | RESERVED     | RESERVED         | RW   | Disable | Enable         | 1   |

| Bit 1 | Χ     | RESERVED     | RESERVED         | RW   | Disable | Enable         | 1   |

| Bit 0 | Χ     | RESERVED     | RESERVED         | RW   | Disable | Enable         | 1   |

| BYTE  | Affected Pin |          |                         | ш  | Bit Co  | ontrol |     |

|-------|--------------|----------|-------------------------|----|---------|--------|-----|

| 4     | Pin #        | Name     | <b>Control Function</b> | ₹  | 0       | 1      | PWD |

| Bit 7 | Χ            | RESERVED | RESERVED                | RW | Disable | Enable | 1   |

| Bit 6 | Χ            | RESERVED | RESERVED                | RW | Disable | Enable | 1   |

| Bit 5 | Χ            | RESERVED | RESERVED                | RW | Disable | Enable | 1   |

| Bit 4 | Χ            | RESERVED | RESERVED                | RW | Disable | Enable | 1   |

| Bit 3 | Χ            | RESERVED | RESERVED                | RW | Disable | Enable | 1   |

| Bit 2 | Χ            | RESERVED | RESERVED                | RW | Disable | Enable | 1   |

| Bit 1 | Χ            | RESERVED | RESERVED                | RW | Disable | Enable | 1   |

| Bit 0 | Χ            | RESERVED | RESERVED                | RW | Disable | Enable | 1   |

| BYTE  |       | Affected Pin |                  | Й   | Bit Co  | ontrol |     |

|-------|-------|--------------|------------------|-----|---------|--------|-----|

| 5     | Pin # | Name         | Control Function | ΤΥΡ | 0       | 1      | PWD |

| Bit 7 | Χ     | RESERVED     | RESERVED         | -   | -       | -      | 1   |

| Bit 6 | Χ     | RESERVED     | RESERVED         | -   | -       | -      | 1   |

| Bit 5 | Χ     | RESERVED     | RESERVED         | -   | -       | -      | 1   |

| Bit 4 | Χ     | RESERVED     | RESERVED         | -   | -       | -      | 1   |

| Bit 3 | Χ     | RESERVED     | RESERVED         | RW  | Disable | Enable | 1   |

| Bit 2 | Χ     | RESERVED     | RESERVED         | RW  | Disable | Enable | 1   |

| Bit 1 | Χ     | RESERVED     | RESERVED         | RW  | Disable | Enable | 1   |

| Bit 0 | Χ     | RESERVED     | RESERVED         | RW  | Disable | Enable | 1   |

| BYTE  |      | Affected Pin      |                  | ш   | Bit Co | ontrol |     |

|-------|------|-------------------|------------------|-----|--------|--------|-----|

| 6     | Pin# | Name              | Control Function | ТҮР | 0      | 1      | PWD |

| Bit 7 | Χ    | Revision ID Bit 3 | (Reserved)       | R   | -      | -      | 1   |

| Bit 6 | Χ    | Revision ID Bit 2 | (Reserved)       | R   | 1      | 1      | 1   |

| Bit 5 | Χ    | Revision ID Bit 1 | (Reserved)       | R   | -      | -      | 1   |

| Bit 4 | Χ    | Revision ID Bit 0 | (Reserved)       | R   | •      | -      | 1   |

| Bit 3 | Χ    | Vendor ID Bit 3   | (Reserved)       | R   | 1      | ı      | 1   |

| Bit 2 | Χ    | Vendor ID Bit 2   | (Reserved)       | R   | -      | -      | 1   |

| Bit 1 | Χ    | Vendor ID Bit 1   | (Reserved)       | R   | •      | -      | 1   |

| Bit 0 | Χ    | Vendor ID Bit 0   | (Reserved)       | R   | -      | -      | 1   |

| BYTE  |       | Affected Pin |                         | Ä   | Bit Control |   |     |

|-------|-------|--------------|-------------------------|-----|-------------|---|-----|

| 7     | Pin # | Name         | <b>Control Function</b> | ТҮР | 0           | 1 | PWD |

| Bit 7 | Χ     | DEVICE ID7   | (Reserved)              | R   | -           | - | 0   |

| Bit 6 | Χ     | DEVICE ID6   | (Reserved)              | R   | 1           | - | 0   |

| Bit 5 | Χ     | DEVICE ID5   | (Reserved)              | R   | ı           | - | 0   |

| Bit 4 | Χ     | DEVICE ID4   | (Reserved)              | R   | ı           | - | 0   |

| Bit 3 | Χ     | DEVICE ID3   | (Reserved)              | R   | •           | - | 0   |

| Bit 2 | Χ     | DEVICE ID2   | (Reserved)              | R   | •           | - | 0   |

| Bit 1 | Χ     | DEVICE ID1   | (Reserved)              | R   | -           | - | 0   |

| Bit 0 | Χ     | DEVICE ID0   | (Reserved)              | R   | -           | - | 1   |

| BYTE  |       | Affected Pin |                  | ய Bit Control |   |   |     |

|-------|-------|--------------|------------------|---------------|---|---|-----|

| 8     | Pin # | Name         | Control Function | TYP           | 0 | 1 | PWD |

| Bit 7 | Х     | Byte Count7  | (Reserved)       | R             | - | - | 0   |

| Bit 6 | Χ     | Byte Count6  | (Reserved)       | R             | - | - | 0   |

| Bit 5 | Χ     | Byte Count5  | (Reserved)       | R             | - | - | 0   |

| Bit 4 | Χ     | Byte Count4  | (Reserved)       | R             | - | - | 0   |

| Bit 3 | Χ     | Byte Count3  | (Reserved)       | R             | - | - | 0   |

| Bit 2 | Χ     | Byte Count2  | (Reserved)       | R             | - | - | 1   |

| Bit 1 | Χ     | Byte Count1  | (Reserved)       | R             | - | - | 1   |

| Bit 0 | Χ     | Byte Count0  | (Reserved)       | R             | - | - | 1   |

## **Absolute Maximum Ratings**

Supply Voltage..... 3.7 V

Power Dissipation . . . . . . . . . . . . 0.5 W

Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

## Electrical Characteristics - Input/Supply/Common Output Parameters

$T_A = 0 - 85$ °C; Supply Voltage  $V_{DD} = 3.3 \text{ V +/-5}\%$

| PARAMETER                      | SYMBOL               | CONDITIONS                                              | MIN                   | TYP | MAX            | UNITS |

|--------------------------------|----------------------|---------------------------------------------------------|-----------------------|-----|----------------|-------|

| Input High Voltage             | $V_{IH}$             |                                                         | 2                     |     | $V_{DD} + 0.3$ | V     |

| Input Low Voltage              | $V_{IL}$             |                                                         | V <sub>SS</sub> - 0.3 |     | 0.8            | V     |

| Input High Current             | I <sub>IH</sub>      | $V_{IN} = V_{DD}$                                       | -5                    |     | 5              | ∠A    |

| Input Low Current              | I <sub>IL1</sub>     | V <sub>IN</sub> = 0 V; Inputs with no pull-up resistors | -5                    |     |                | ∠A    |

| Supply Current                 |                      | $f_{IN} = 14.318MHz$                                    |                       | 27  | 35             | mA    |

| Supply Culletti                | l <sub>DD</sub>      | $f_{IN} = 66.66MHz$                                     |                       | 42  | 50             | mA    |

| Powerdown Current              | I <sub>DD3.3PD</sub> |                                                         |                       | 3   | 5              | mA    |

| Pin Inductance                 | $L_{pin}$            |                                                         |                       |     | 7              | nΗ    |

| Din Canasitanas                | $C_{IN}$             | Logic Inputs                                            |                       |     | 5              | рF    |

| Pin Capacitance <sup>1</sup>   | C <sub>OUT</sub>     | Output pin capacitance                                  |                       |     | 6              | рF    |

| Transition time <sup>1</sup>   | T <sub>trans</sub>   | To 1st crossing of target frequency                     |                       |     | 3              | ms    |

| Settling time <sup>1</sup>     | T <sub>s</sub>       | From 1st crossing to 1% target frequency                |                       |     | 3              | ms    |

| Clk Stabilization <sup>1</sup> | T <sub>STAB</sub>    | From V <sub>DD</sub> = 3.3 V to 1% target frequency     |                       | 1   | 3              | ms    |

| Delay <sup>1</sup>             | $t_{PZH}, t_{PZL}$   | Output enable delay (all outputs)                       | 1                     |     | 10             | ns    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

### **AC Electrical Characteristics**

$T_A = 0 - 70$ °C; Supply Voltage  $V_{DD} = 3.3 \text{ V} \pm 0.3 \text{V}$

| PARAMETER         | DESCRIPTION            | TEST CONDITION          | MIN    | TYP | MAX | UNITS |

|-------------------|------------------------|-------------------------|--------|-----|-----|-------|

| F <sub>IN</sub>   | Input Frequency        | Input Clock             | 14.318 |     | 80  | MHz   |

| f <sub>OUT</sub>  | Output Frequency       | Spread Off              | 14.318 |     | 80  | MHz   |

| t <sub>R</sub>    | Output Rise Time       | 15 pF load, 0.8V - 2.4V | 0.5    |     | 1   | ns    |

| t <sub>F</sub>    | Output Fall Time       | 15 pF load, 2.4 - 0.8V  | 0.5    |     | 1   | ns    |

| I <sub>OD</sub>   | Output Duty Cycle      | 15 pf load              | 45     |     | 55  | %     |

| t <sub>ID</sub>   | Input Duty Cycle       |                         | 45     |     | 55  | %     |

| t <sub>JCYC</sub> | Jitter, Cycle-to-Cycle |                         |        |     | 250 | ps    |

## **Electrical Characteristics - CLOCK\_OUT**

$T_A = 0 - 85$ °C;  $V_{DD} = 3.3V + /-5\%$ ;  $C_L = 10-20 \ pF$  (unless otherwise specified)

| PARAMETER              | SYMBOL                  | CONDITIONS                       | MIN  | TYP | MAX | UNITS |

|------------------------|-------------------------|----------------------------------|------|-----|-----|-------|

| Current Source         |                         |                                  |      |     |     |       |

| Output Impedance       | Zo <sup>1</sup>         | $V_O = V_x$                      | 3000 |     |     | (     |

| Output High Voltage    | $V_{OH3}$               | $I_{OH} = -1 \text{ mA}$         | 2.4  |     |     | V     |

| Output Low Voltage     | $V_{OL3}$               | $I_{OL} = 1 \text{ mA}$          |      |     | 0.4 |       |

| Rise Time              | t <sub>r3</sub>         | $V_{OL} = 0.41V, V_{OH} = 0.86V$ | 0.5  |     | 1   | ns    |

| Fall Time              | t <sub>f3</sub>         | $V_{OH} = 0.86V V_{OL} = 0.41V$  | 0.5  |     | 1   | ns    |

| Duty Cycle             | d <sub>t3</sub>         | V <sub>T</sub> = 50%             | 45   | 51  | 55  | %     |

| Jitter, Cycle to cycle | t <sub>jcyc-cyc</sub> 1 | $V_T = 50\%$                     |      |     | 250 | ps    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

## **Electrical Characteristics - REF**

$T_A = 0 - 85$ °C; VDD=3.3V +/-5%;  $C_L = 10$ -20 pF (unless otherwise specified)

| PARAMETER           | SYMBOL                  | CONDITIONS                                                  | MIN | TYP | MAX | UNITS |

|---------------------|-------------------------|-------------------------------------------------------------|-----|-----|-----|-------|

| Output Frequency    | F <sub>O1</sub>         |                                                             |     |     |     | MHz   |

| Output Impedance    | $R_{DSP1}^{1}$          | $V_{O} = V_{DD}^{*}(0.5)$                                   | 20  |     | 60  |       |

| Output High Voltage | $V_{OH}^{-1}$           | I <sub>OH</sub> = -1 mA                                     | 2.4 |     |     | V     |

| Output Low Voltage  | $V_{OL}^{1}$            | I <sub>OL</sub> = 1 mA                                      |     |     | 0.4 | V     |

| Output High Current | $I_{OH}^{-1}$           | V <sub>OH@MIN</sub> = 1.0 V, V <sub>OH@MAX</sub> = 3.135 V  | -29 |     | -23 | mA    |

| Output Low Current  | $I_{OL}^{1}$            | $V_{OL @MIN} = 1.95 \text{ V}, V_{OL @MAX} = 0.4 \text{ V}$ | 29  |     | 27  | mA    |

| Rise Time           | $t_{r1}^{-1}$           | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$            | 0.5 |     | 1   | ns    |

| Fall Time           | $t_{f1}^1$              | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$            | 0.5 |     | 1   | ns    |

| Duty Cycle          | $d_{t1}^{1}$            | $V_T = 1.5 \text{ V}$                                       | 45  |     | 55  | %     |

| Accumulated Jitter  | t <sub>jlongterm</sub>  | $V_T = 1.5 \text{ V } 10 \text{us}.$                        |     |     | 2   | ns    |

| Jitter              | t <sub>jcyc-cyc</sub> 1 | $V_T = 1.5 \text{ V}$                                       |     |     | 500 | ps    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> I<sub>OWT</sub> can be varied and is selectable thru the MULTSEL pin.

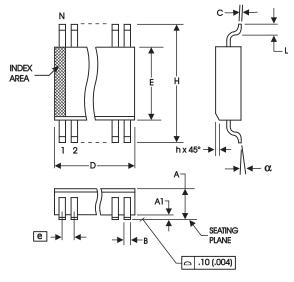

150mil Body, .50mil pitch

| 150 mil (Narrow Body) SC | ЭIC | ) |

|--------------------------|-----|---|

|--------------------------|-----|---|

| 100 mm (marrow Body) colo |                |           |                   |          |  |  |  |

|---------------------------|----------------|-----------|-------------------|----------|--|--|--|

|                           | In Millimeters |           | In Inches         |          |  |  |  |

| SYMBOL                    | COMMON D       | IMENSIONS | COMMON DIMENSION: |          |  |  |  |

|                           | MIN            | MAX       | MIN               | MAX      |  |  |  |

| Α                         | 1.35           | 1.75      | .0532             | .0688    |  |  |  |

| A1                        | 0.10           | 0.25      | .0040             | .0098    |  |  |  |

| В                         | 0.33           | 0.51      | .013              | .020     |  |  |  |

| С                         | 0.19           | 0.25      | .0075             | .0098    |  |  |  |

| D                         | SEE VAF        | RIATIONS  | SEE VARIATIONS    |          |  |  |  |

| E                         | 3.80           | 4.00      | .1497             | .1574    |  |  |  |

| е                         | 1.27 E         | BASIC     | 0.050             | BASIC    |  |  |  |

| Н                         | 5.80           | 6.20      | .2284             | .2440    |  |  |  |

| h                         | 0.25           | 0.50      | .010              | .020     |  |  |  |

| L                         | 0.40           | 1.27      | .016              | .050     |  |  |  |

| N                         | SEE VAF        | RIATIONS  | SEE VAI           | RIATIONS |  |  |  |

| а                         | 0°             | 8°        | 0°                | 8°       |  |  |  |

### **VARIATIONS**

| N | D mm. |      | D (inch) |       |  |

|---|-------|------|----------|-------|--|

|   | MIN   | MAX  | MIN      | MAX   |  |

| 8 | 4.80  | 5.00 | .1890    | .1968 |  |

Reference Doc.: JEDEC Publication 95, MS-012

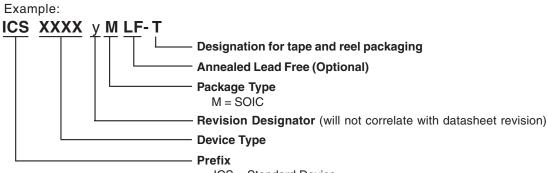

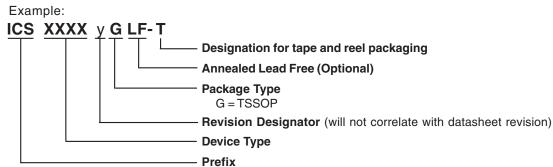

# **Ordering Information**

ICS91718yMLF-T

ICS = Standard Device

0500D--07/15/04

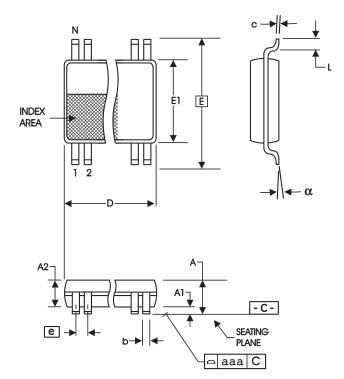

4.40 mm. Body, 0.65 mm. Pitch TSSOP (173 mil) (25.6 mil)

|        | (************************************** | (====,    |                   |       |  |

|--------|-----------------------------------------|-----------|-------------------|-------|--|

|        | In Milli                                | meters    | In Inches         |       |  |

| SYMBOL | COMMON D                                | IMENSIONS | COMMON DIMENSIONS |       |  |

|        | MIN                                     | MAX       | MIN               | MAX   |  |

| Α      |                                         | 1.20      |                   | .047  |  |

| A1     | 0.05                                    | 0.15      | .002              | .006  |  |

| A2     | 0.80                                    | 1.05      | .032              | .041  |  |

| b      | 0.19                                    | 0.30      | .007              | .012  |  |

| С      | 0.09                                    | 0.20      | .0035             | .008  |  |

| D      | SEE VAF                                 | RIATIONS  | SEE VARIATIONS    |       |  |

| E      | 6.40 BASIC                              |           | 0.252             | BASIC |  |

| E1     | 4.30                                    | 4.50      | .169              | .177  |  |

| е      | 0.65 E                                  | BASIC     | 0.0256            | BASIC |  |

| L      | 0.45                                    | 0.75      | .018              | .030  |  |

| N      | SEE VARIATIONS                          |           | SEE VARIATIONS    |       |  |

| а      | 0°                                      | 8°        | 0°                | 8°    |  |

| aaa    |                                         | 0.10      |                   | .004  |  |

#### **VARIATIONS**

|  | N | Dr   | nm.  | D (inch) |      |  |

|--|---|------|------|----------|------|--|

|  |   | MIN  | MAX  | MIN      | MAX  |  |

|  | 8 | 2.90 | 3.10 | .114     | .122 |  |

Reference Doc.: JEDEC Publication 95, MO-153

10-0035

# **Ordering Information**

ICS91718yGLF-T

ICS = Standard Device

0500D—07/15/04

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.