# SYNCHRONOUS ETHERNET PLL

## 8V89307 DATASHEET

Revision 8

April 12, 2016

---

#### DISCLAIMER

Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

#### LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.

1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2. A critical component is any components of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

# Table of Contents

## Datasheet

|                                                               |           |

|---------------------------------------------------------------|-----------|

| <b>FEATURES .....</b>                                         | <b>7</b>  |

| HIGHLIGHTS.....                                               | 7         |

| MAIN FEATURES .....                                           | 7         |

| OTHER FEATURES.....                                           | 7         |

| <b>APPLICATIONS.....</b>                                      | <b>7</b>  |

| <b>DESCRIPTION.....</b>                                       | <b>8</b>  |

| <b>1 PIN ASSIGNMENT .....</b>                                 | <b>9</b>  |

| <b>2 PIN DESCRIPTION .....</b>                                | <b>10</b> |

| <b>3 FUNCTIONAL DESCRIPTION .....</b>                         | <b>14</b> |

| 3.1 RESET .....                                               | 14        |

| 3.2 MASTER CLOCK .....                                        | 14        |

| 3.3 INPUT CLOCKS .....                                        | 15        |

| 3.4 INPUT CLOCK PRE-DIVIDER .....                             | 15        |

| 3.5 INPUT CLOCK QUALITY MONITORING .....                      | 17        |

| 3.5.1 Activity Monitoring .....                               | 17        |

| 3.5.2 Frequency Monitoring .....                              | 18        |

| 3.6 DPLL INPUT CLOCK SELECTION .....                          | 20        |

| 3.6.1 Forced Selection .....                                  | 20        |

| 3.6.2 Automatic Selection .....                               | 20        |

| 3.7 SELECTED INPUT CLOCK MONITORING .....                     | 21        |

| 3.7.1 DPLL Locking Detection .....                            | 21        |

| 3.7.1.1 Fast Loss .....                                       | 21        |

| 3.7.1.2 Coarse Phase Loss .....                               | 21        |

| 3.7.1.3 Fine Phase Loss .....                                 | 21        |

| 3.7.1.4 Hard Limit Exceeding .....                            | 21        |

| 3.7.2 Locking Status .....                                    | 21        |

| 3.7.3 Phase Lock Alarm .....                                  | 21        |

| 3.8 INPUT CLOCK SELECTION .....                               | 23        |

| 3.8.1 Input Clock Validity .....                              | 23        |

| 3.8.2 Input Clock Selection .....                             | 23        |

| 3.8.2.1 Revertive Switching .....                             | 23        |

| 3.8.2.2 Non-Revertive Switching .....                         | 23        |

| 3.8.3 Selected / Qualified Input Clocks Indication .....      | 23        |

| 3.9 SELECTED INPUT CLOCK STATUS VS. DPLL OPERATING MODE ..... | 25        |

| 3.9.1 Selected Input Clock vs. DPLL Operating Mode .....      | 25        |

| 3.10 DPLL OPERATING MODE .....                                | 27        |

| 3.10.1 DPLL Operating Mode .....                              | 27        |

| 3.10.1.1 Free-Run Mode .....                                  | 27        |

| 3.10.1.2 Pre-Locked Mode .....                                | 27        |

| 3.10.1.3 Locked Mode .....                                    | 27        |

| 3.10.1.4 Temp-Holdover Mode .....                             | 27        |

| 3.10.1.5 Lost-Phase Mode .....                                | 27        |

| 3.10.1.6 Holdover Mode .....                                  | 27        |

| 3.10.1.6.1 Automatic Instantaneous .....                      | 28        |

| 3.10.1.6.2 Automatic Slow Averaged .....                      | 28        |

| 3.10.1.6.3 Automatic Fast Averaged .....                      | 28        |

| 3.10.1.6.4 Manual .....                                       | 28        |

| 3.10.1.6.5 Holdover Frequency Offset Read .....               | 28        |

| 3.10.1.7 Pre-Locked2 Mode .....                               | 28        |

|          |                                                                       |     |

|----------|-----------------------------------------------------------------------|-----|

| 3.11     | DPLL OUTPUT .....                                                     | 30  |

| 3.11.1   | PFD Output Limit .....                                                | 30  |

| 3.11.2   | Frequency Offset Limit .....                                          | 30  |

| 3.11.3   | Hitless REference Switching (HS) .....                                | 30  |

| 3.11.4   | Phase Offset Selection .....                                          | 30  |

| 3.11.5   | Phase Slope Limiting .....                                            | 30  |

| 3.11.6   | Five Paths of the DPLL Outputs .....                                  | 30  |

| 3.11.6.1 | DPLL Path .....                                                       | 30  |

| 3.12     | APLL .....                                                            | 32  |

| 3.12.1   | EXTERNAL FILTER .....                                                 | 32  |

| 3.13     | OUTPUT CLOCKS .....                                                   | 32  |

| 3.13.1   | 1 Pulse per Second .....                                              | 33  |

| 3.14     | INTERRUPT SUMMARY .....                                               | 34  |

| 3.15     | POWER SUPPLY FILTERING TECHNIQUES .....                               | 35  |

| 4        | MICROPROCESSOR INTERFACE .....                                        | 37  |

| 4.1      | SERIAL MODE .....                                                     | 38  |

| 4.2      | I2C MODE .....                                                        | 40  |

| 4.2.1    | I2C Device Address .....                                              | 40  |

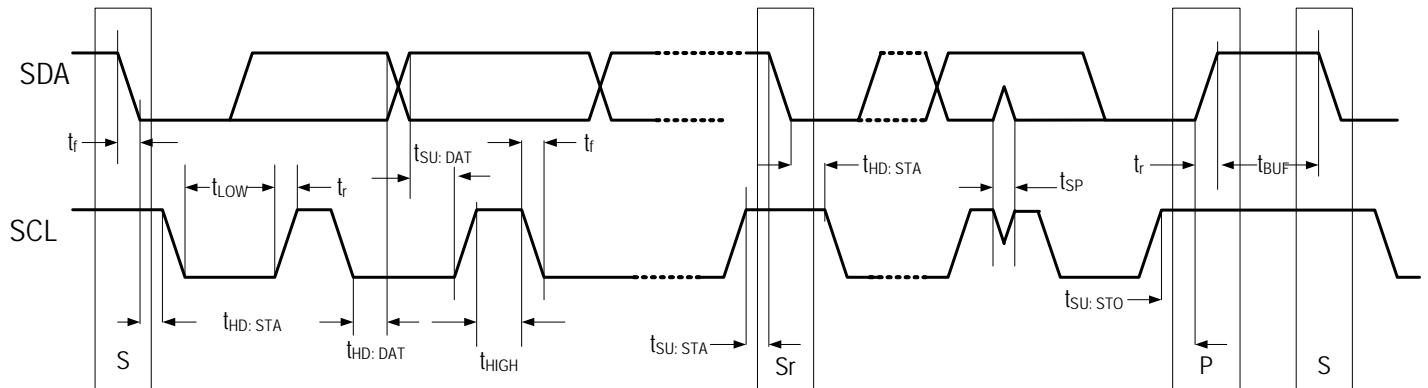

| 4.2.2    | I2C Bus Timing .....                                                  | 40  |

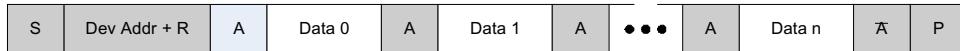

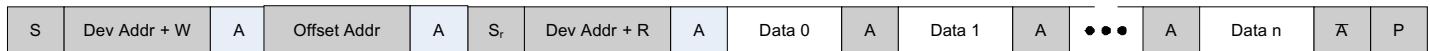

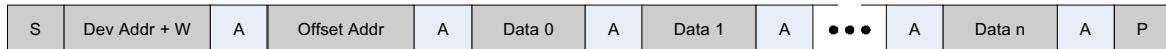

| 4.2.3    | Supported Transactions .....                                          | 42  |

| 5        | JTAG .....                                                            | 43  |

| 6        | PROGRAMMING INFORMATION .....                                         | 44  |

| 6.1      | REGISTER MAP .....                                                    | 44  |

| 6.2      | REGISTER DESCRIPTION .....                                            | 50  |

| 6.2.1    | Global Control Registers .....                                        | 50  |

| 6.2.2    | Interrupt Registers .....                                             | 56  |

| 6.2.3    | Input Clock Frequency & Priority Configuration Registers .....        | 59  |

| 6.2.4    | Input Clock Quality Monitoring Configuration & Status Registers ..... | 66  |

| 6.2.5    | IDPLL Input Clock Selection Registers .....                           | 76  |

| 6.2.6    | DPLL State Machine Control Registers .....                            | 79  |

| 6.2.7    | DPLL & APLL Configuration Registers .....                             | 80  |

| 6.2.8    | Output Configuration Registers .....                                  | 92  |

| 6.2.9    | Phase Offset Control Registers .....                                  | 96  |

| 6.3      | PAGE 1 REGISTERS DESCRIPTION .....                                    | 97  |

| 7        | ELECTRICAL SPECIFICATIONS .....                                       | 100 |

| 7.1      | ABSOLUTE MAXIMUM RATING .....                                         | 100 |

| 7.2      | RECOMMENDED OPERATION CONDITIONS .....                                | 100 |

| 7.3      | I/O SPECIFICATIONS .....                                              | 101 |

| 7.3.1    | CMOS Input / Output Port .....                                        | 101 |

| 7.3.2    | PECL / LVDS Input / Output Port .....                                 | 102 |

| 7.3.2.1  | PECL Input / Output Port .....                                        | 102 |

| 7.3.2.2  | LVDS Input / Output Port .....                                        | 104 |

| 7.3.2.3  | Single-Ended Input for Differential Input .....                       | 105 |

| 7.4      | JITTER PERFORMANCE .....                                              | 106 |

| 7.5      | OUTPUT WANDER GENERATION .....                                        | 110 |

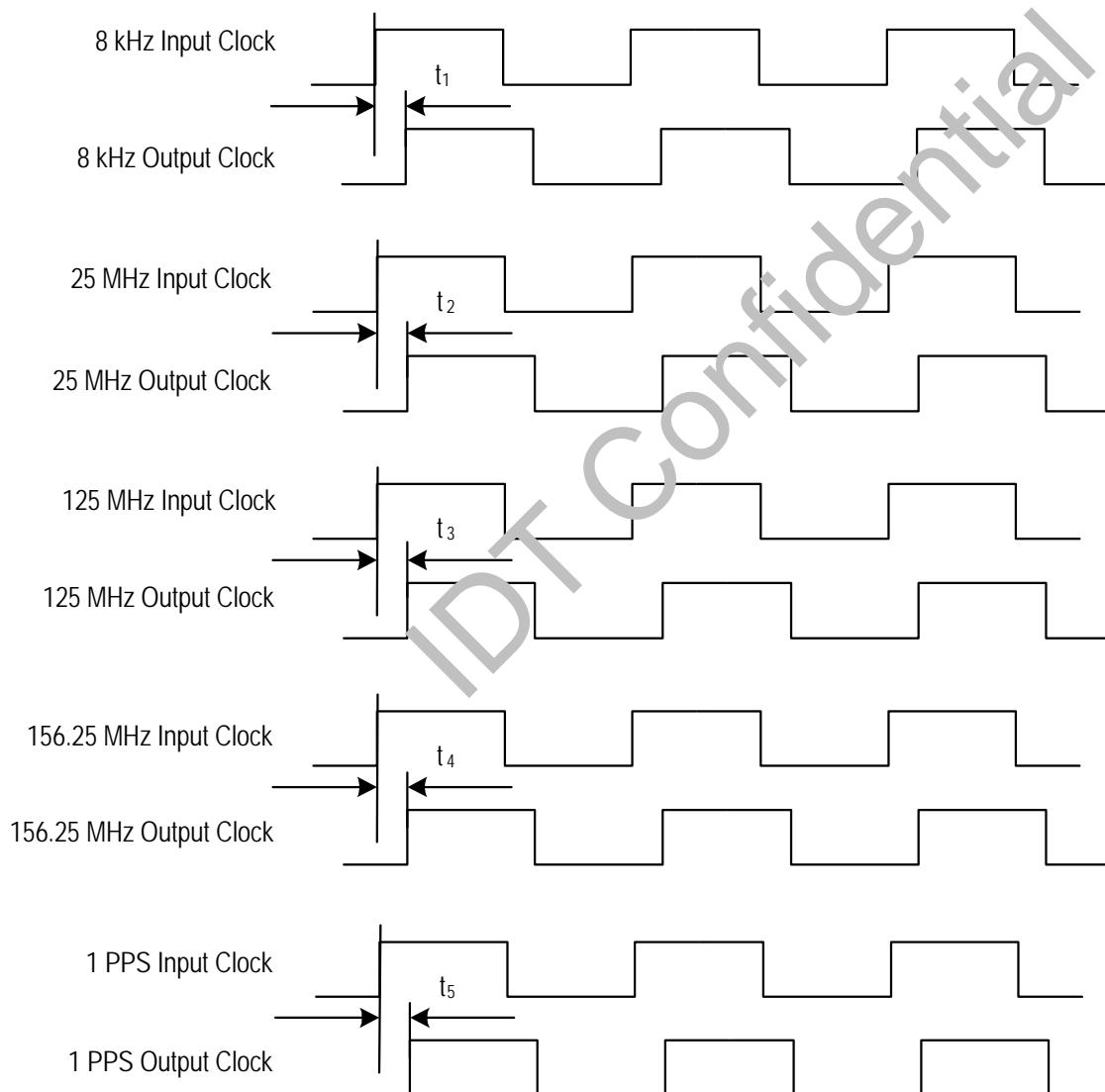

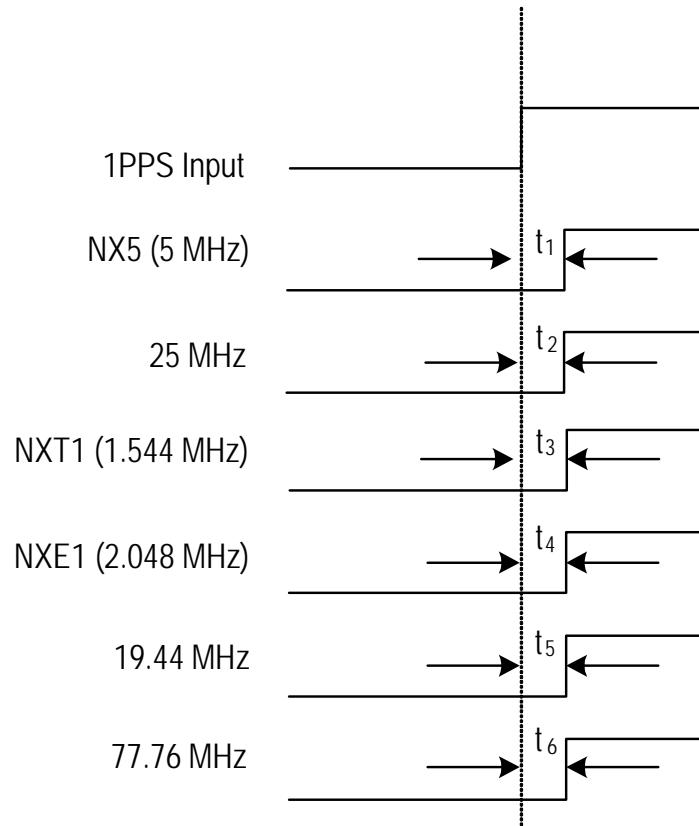

| 7.6      | INPUT / OUTPUT CLOCK TIMING .....                                     | 111 |

| 7.7      | 1PPS INPUT AND OUTPUT CLOCK TIMING .....                              | 112 |

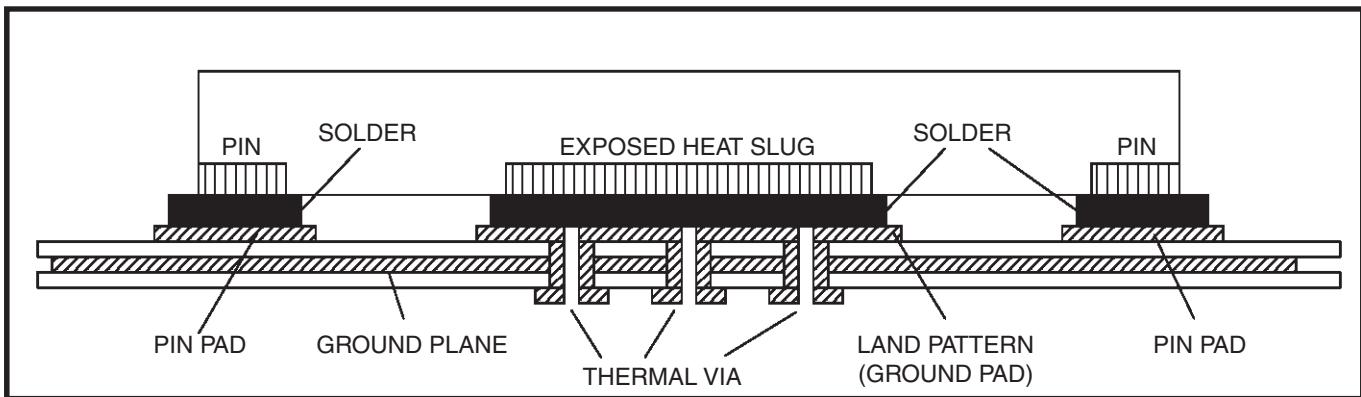

| 8        | THERMAL MANAGEMENT .....                                              | 114 |

| 8.1      | JUNCTION TEMPERATURE .....                                            | 114 |

| 8.2      | VQFN EPAD THERMAL RELEASE PATH .....                                  | 115 |

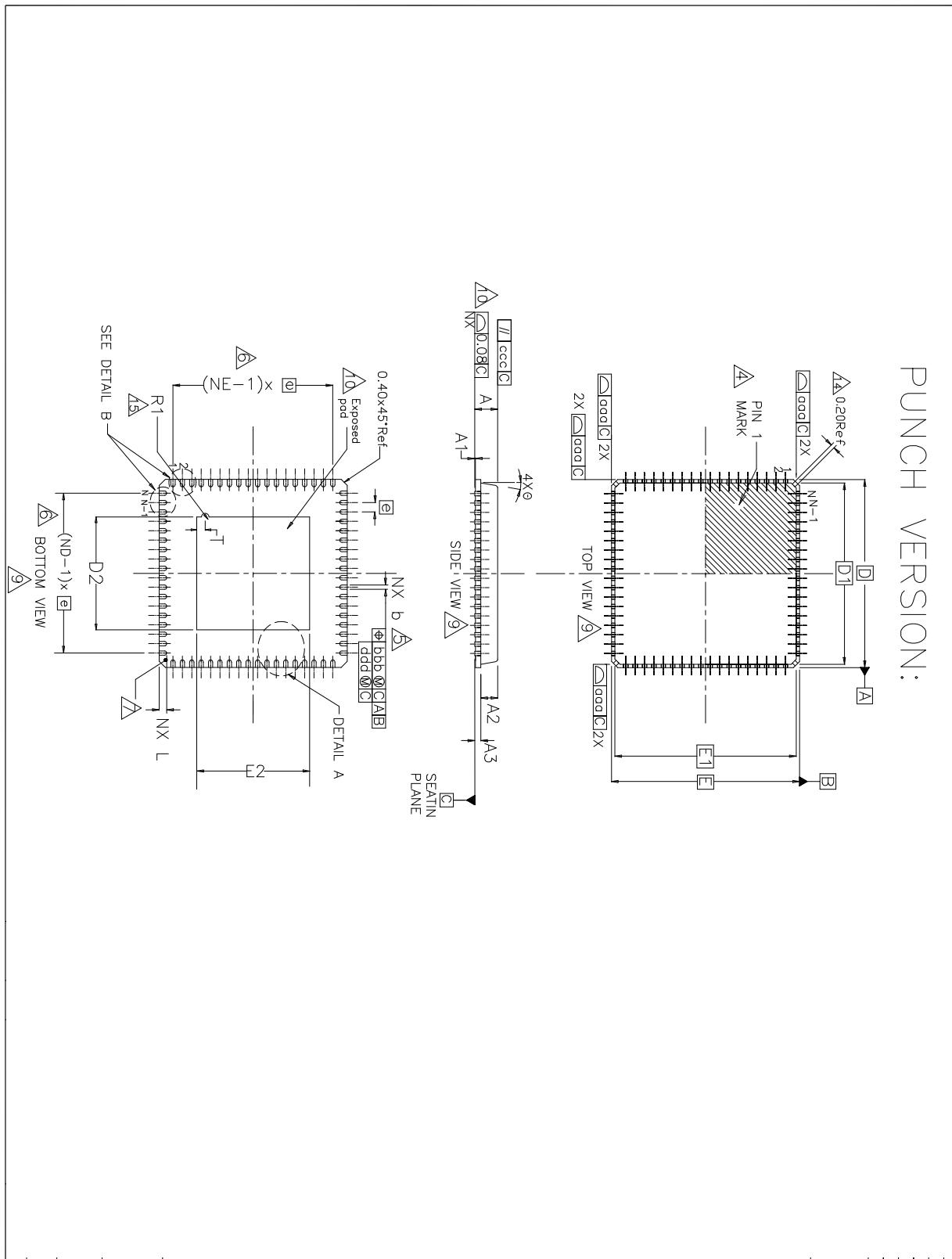

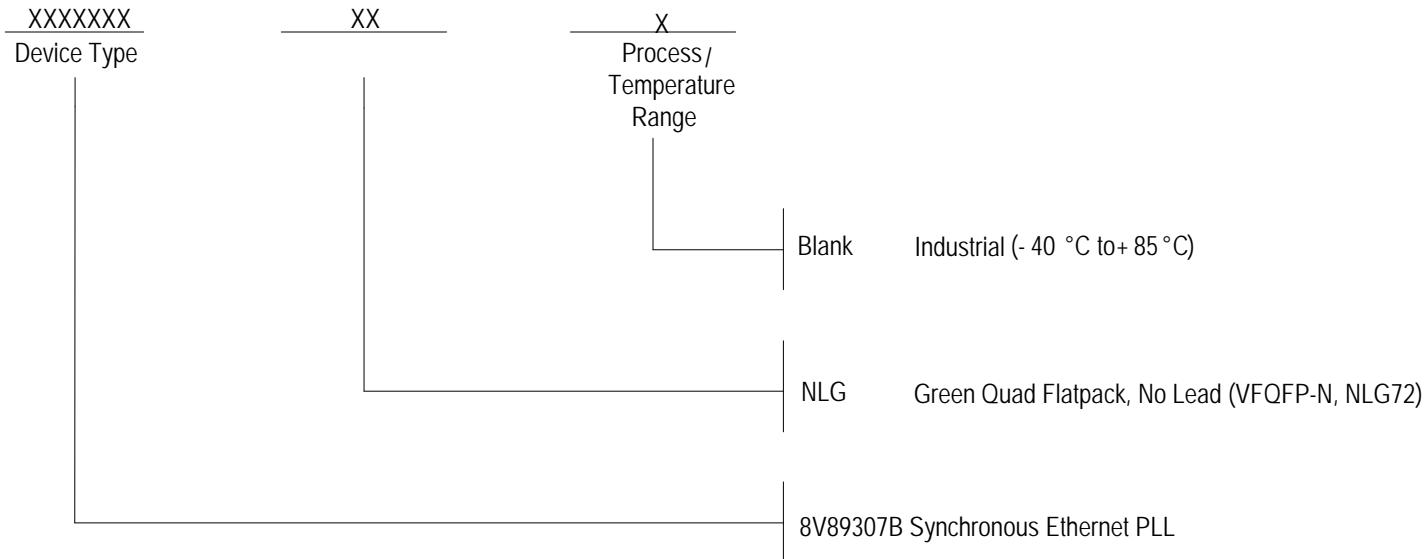

|          | PACKAGE DIMENSIONS .....                                              | 119 |

|          | ORDERING INFORMATION .....                                            | 123 |

|          | REVISION HISTORY .....                                                | 123 |

# List of Tables

## Datasheet

|                                                                                                               |     |

|---------------------------------------------------------------------------------------------------------------|-----|

| Table 1: Pin Description .....                                                                                | 10  |

| Table 2: Related Bit / Register in Chapter 3.2 .....                                                          | 14  |

| Table 3: Pre-Divider Function .....                                                                           | 16  |

| Table 4: Related Bit / Register in Chapter 3.5 .....                                                          | 19  |

| Table 5: Input Clock Selection for the DPLL .....                                                             | 20  |

| Table 6: Related Bit / Register in Chapter 3.6 .....                                                          | 20  |

| Table 7: Coarse Phase Limit Programming (the selected input clock of 2 kHz, 4 kHz or 8 kHz) .....             | 21  |

| Table 8: Coarse Phase Limit Programming (the selected input clock of other than 2 kHz, 4 kHz and 8 kHz) ..... | 21  |

| Table 9: Related Bit / Register in Chapter 3.7 .....                                                          | 22  |

| Table 10: Related Bit / Register in Chapter 3.8 .....                                                         | 24  |

| Table 11: DPLL Operating Mode Control .....                                                                   | 25  |

| Table 12: Related Bit / Register in Chapter 3.9 .....                                                         | 26  |

| Table 13: Frequency Offset Control in Temp-Holdover Mode .....                                                | 27  |

| Table 14: Frequency Offset Control in Holdover Mode .....                                                     | 28  |

| Table 15: Holdover Frequency Offset Read .....                                                                | 28  |

| Table 16: Related Bit / Register in Chapter 3.10 .....                                                        | 29  |

| Table 17: Related Bit / Register in Chapter 3.11 .....                                                        | 31  |

| Table 18: Related Bit / Register in Chapter 3.12 .....                                                        | 32  |

| Table 19: APLL Approximate Loop Bandwidth Selection .....                                                     | 32  |

| Table 20: Outputs on OUT1 ~ OUT3 if Derived from DPLL Outputs .....                                           | 32  |

| Table 21: Outputs on OUT1 ~ OUT3 if Derived from APLL1 .....                                                  | 33  |

| Table 22: Related Bit / Register in Chapter 3.13 .....                                                        | 33  |

| Table 23: Related Bit / Register in Chapter 3.14 .....                                                        | 34  |

| Table 24: Microprocessor Interface .....                                                                      | 37  |

| Table 25: Microprocessor Interface Pins .....                                                                 | 37  |

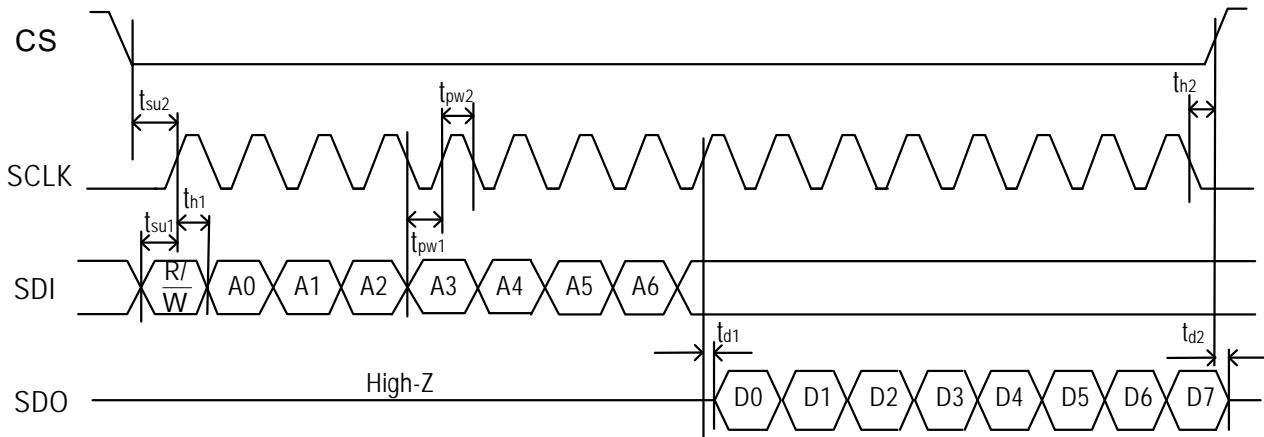

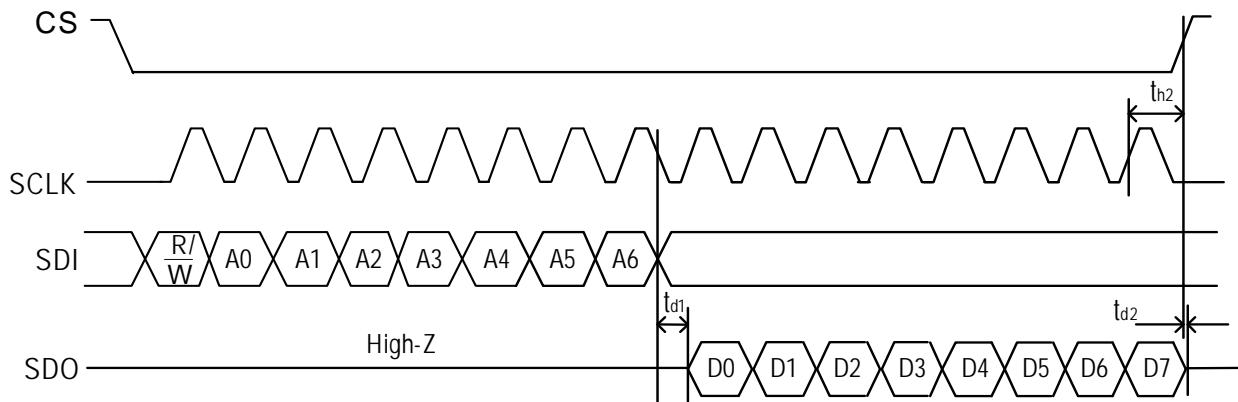

| Table 26: Read Timing Characteristics in Serial Mode .....                                                    | 39  |

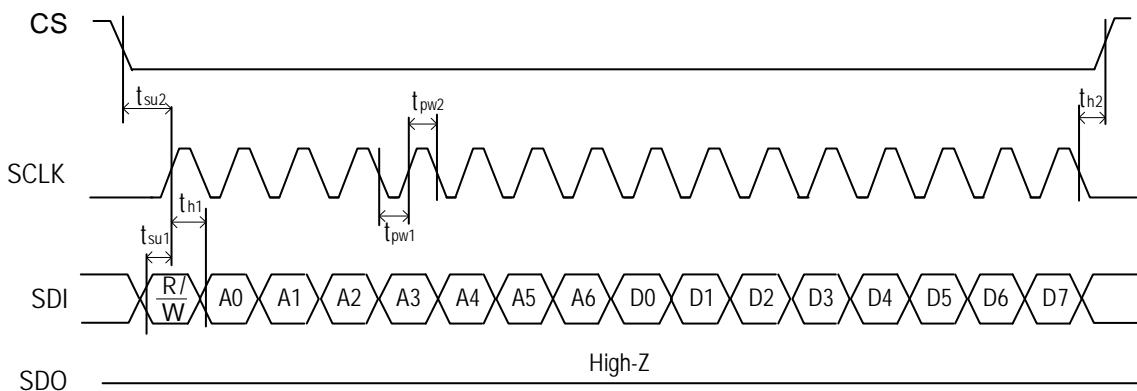

| Table 27: Write Timing Characteristics in Serial Mode .....                                                   | 39  |

| Table 28: Timing Definition for Standard Mode and Fast Mode(1) .....                                          | 41  |

| Table 29: Description of I2C Slave Interface Supported Transactions .....                                     | 42  |

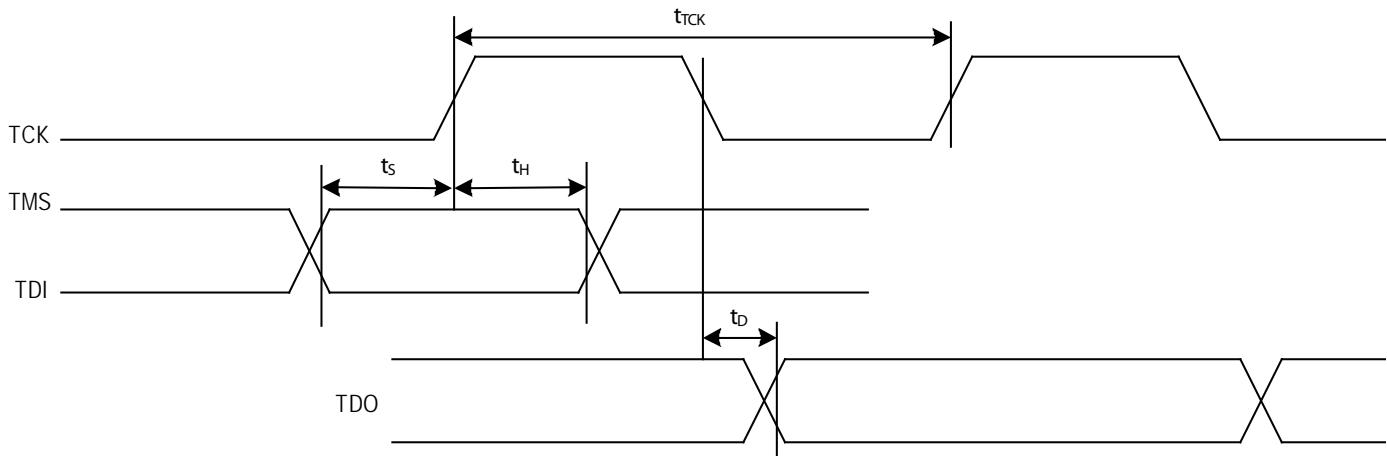

| Table 30: JTAG Timing Characteristics .....                                                                   | 43  |

| Table 31: Register List and Mapping .....                                                                     | 44  |

| Table 32: Page 1 Register List and Mapping .....                                                              | 49  |

| Table 33: Absolute Maximum Rating .....                                                                       | 100 |

| Table 34: Recommended Operation Conditions .....                                                              | 100 |

| Table 35: CMOS Input Port Electrical Characteristics .....                                                    | 101 |

| Table 36: CMOS Input Port with Internal Pull-Up Resistor Electrical Characteristics .....                     | 101 |

| Table 37: CMOS Input Port with Internal Pull-Down Resistor Electrical Characteristics .....                   | 101 |

| Table 38: CMOS Output Port Electrical Characteristics .....                                                   | 101 |

| Table 39: PECL Input / Output Port Electrical Characteristics .....                                           | 103 |

| Table 40: LVDS Input / Output Port Electrical Characteristics .....                                           | 104 |

| Table 41: Output Clock Jitter Generation .....                                                                | 106 |

| Table 42: Output Clock Jitter Generation .....                                                                | 107 |

| Table 43: Output Clock Jitter Generation .....                                                                | 108 |

| Table 44: Output Clock Jitter Generation .....                                                                | 109 |

| Table 45: Input/Output Clock Timing .....                                                                     | 112 |

| Table 46: Output Clock Timing .....                                                                           | 113 |

| Table 47: Thermal Data .....                                                                                  | 114 |

# List of Figures

## Datasheet

|                                                                             |     |

|-----------------------------------------------------------------------------|-----|

| Figure 1. Functional Block Diagram .....                                    | 7   |

| Figure 1. Pin Assignment (Top View) .....                                   | 9   |

| Figure 2. Pre-Divider for An Input Clock .....                              | 16  |

| Figure 3. Input Clock Activity Monitoring .....                             | 17  |

| Figure 4. Hysteresis Frequency Monitoring .....                             | 18  |

| Figure 5. Qualified Input Clocks for Automatic Selection .....              | 20  |

| Figure 6. DPLL Selected Input Clock vs. DPLL Automatic Operating Mode ..... | 25  |

| Figure 7. APLL External Filter Components .....                             | 32  |

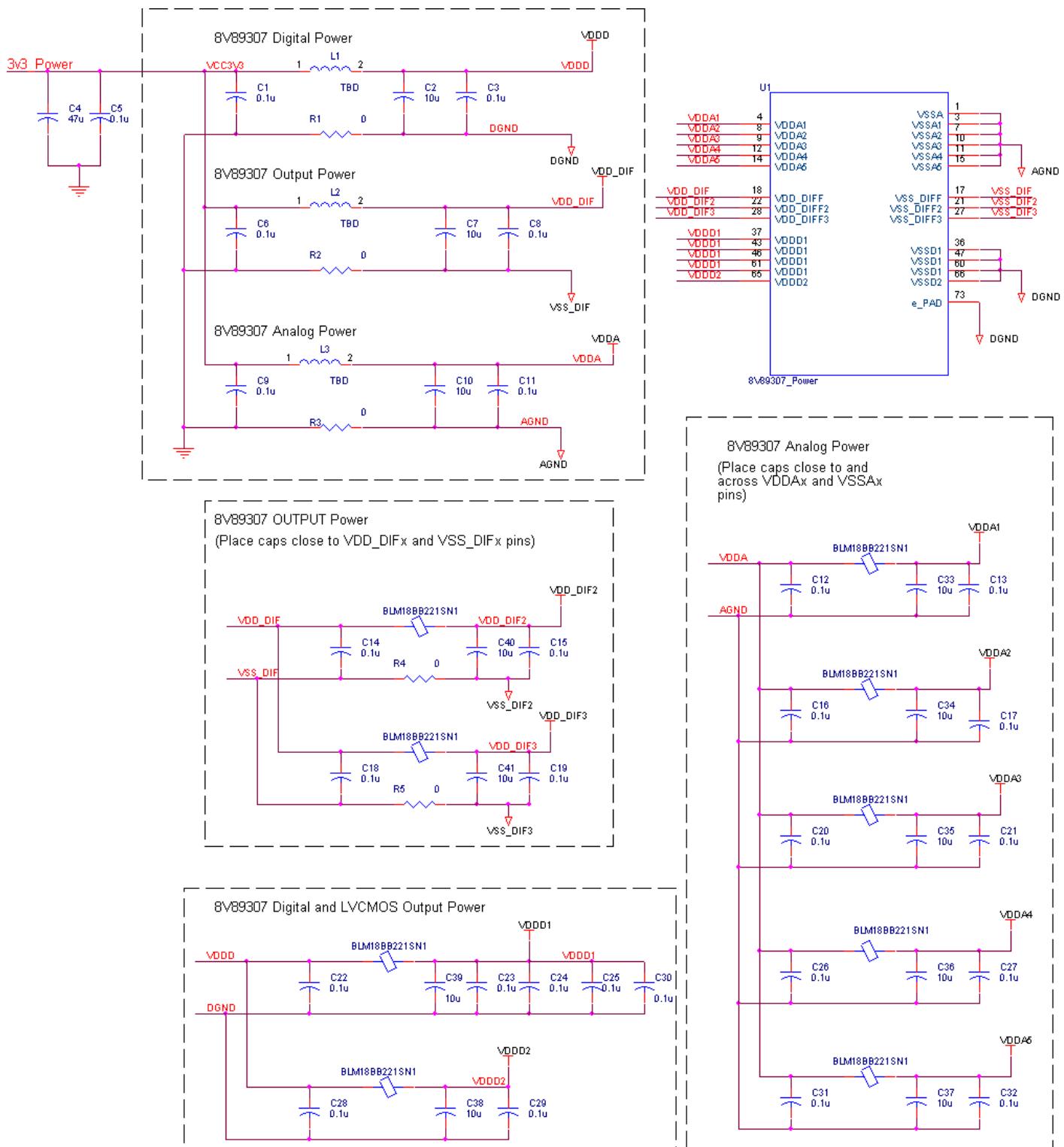

| Figure 8. 8V89307 Power Decoupling Scheme .....                             | 36  |

| Figure 9. Serial Read Timing Diagram (CLKE Asserted Low) .....              | 38  |

| Figure 10. Serial Read Timing Diagram (CLKE Asserted High) .....            | 38  |

| Figure 11. Serial Write Timing Diagram .....                                | 39  |

| Figure 12. Definition of I2C Bus Timing .....                               | 40  |

| Figure 13. I2C Slave Interface Supported Transactions .....                 | 42  |

| Figure 14. JTAG Interface Timing Diagram .....                              | 43  |

| Figure 15. Recommended PECL Input Port Line Termination .....               | 102 |

| Figure 16. Recommended PECL Output Port Line Termination .....              | 102 |

| Figure 17. Recommended LVDS Input Port Line Termination .....               | 104 |

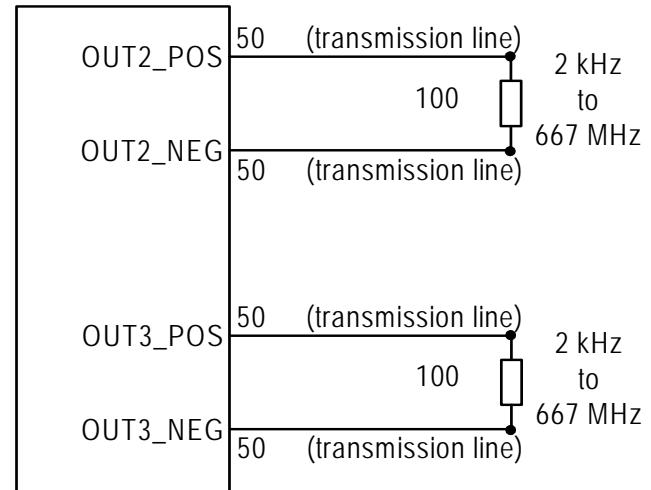

| Figure 18. Recommended LVDS Output Port Line Termination .....              | 104 |

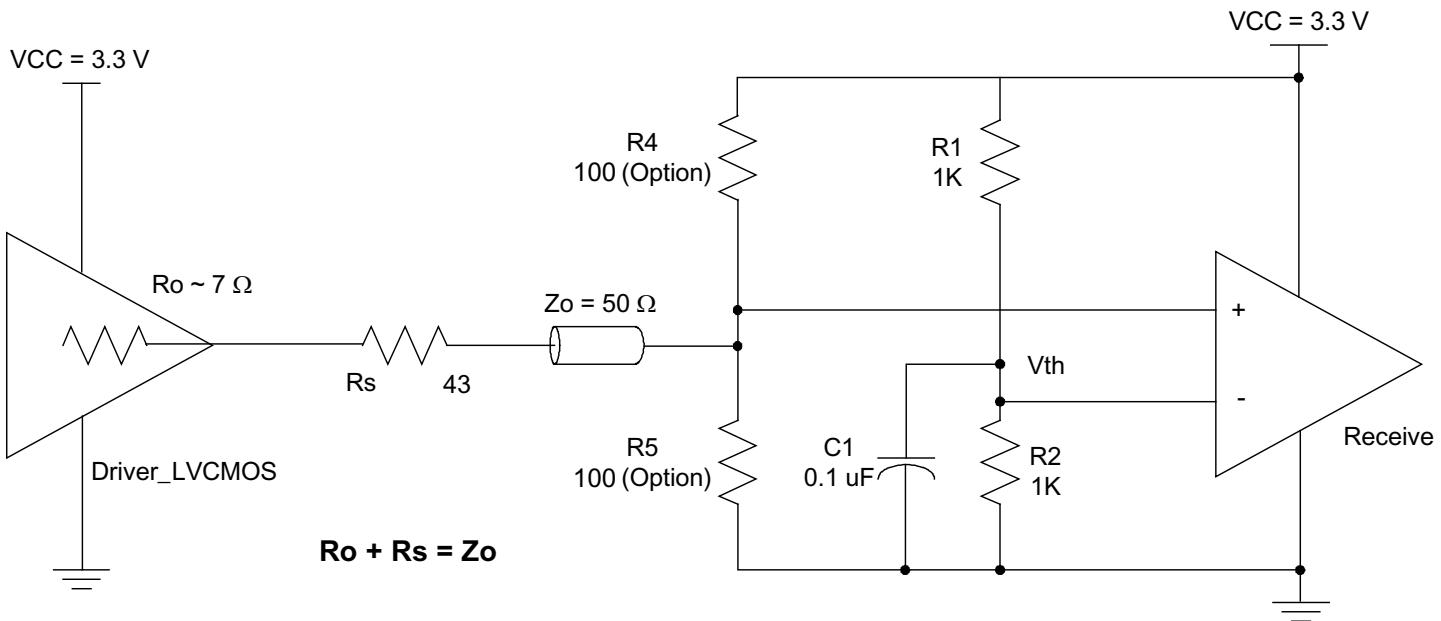

| Figure 19. Example of Single-Ended Signal to Drive Differential Input ..... | 105 |

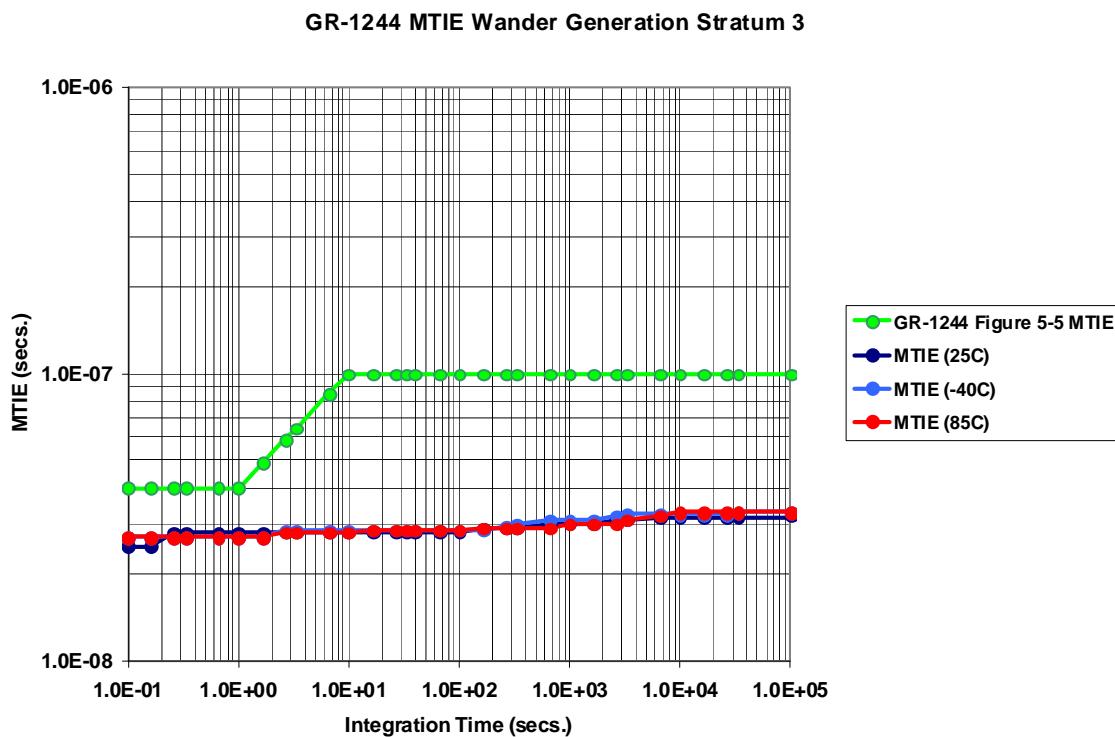

| Figure 20. MTIE Output Wander Generation .....                              | 110 |

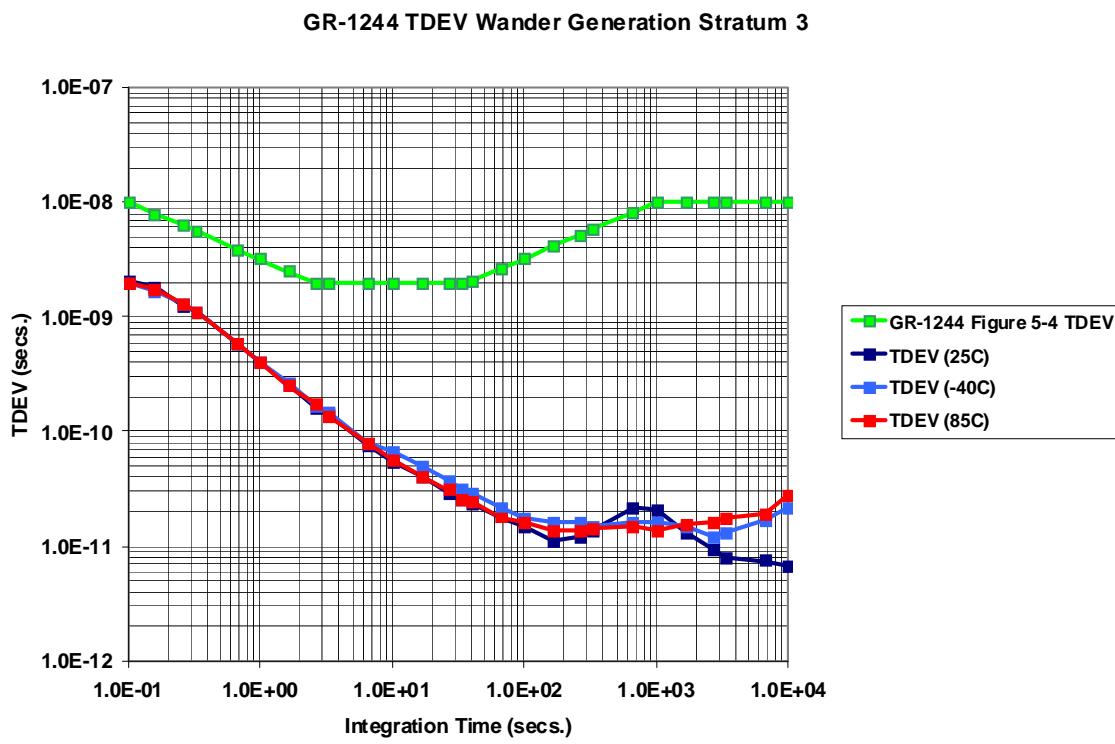

| Figure 21. TDEV Output Wander Generation .....                              | 110 |

| Figure 22. Input / Output Clock Timing .....                                | 111 |

| Figure 23. 1PPS Input and Output Clock Timing .....                         | 112 |

| Figure 24. assembly for Expose Pad thermal Release Path (Side View) .....   | 115 |

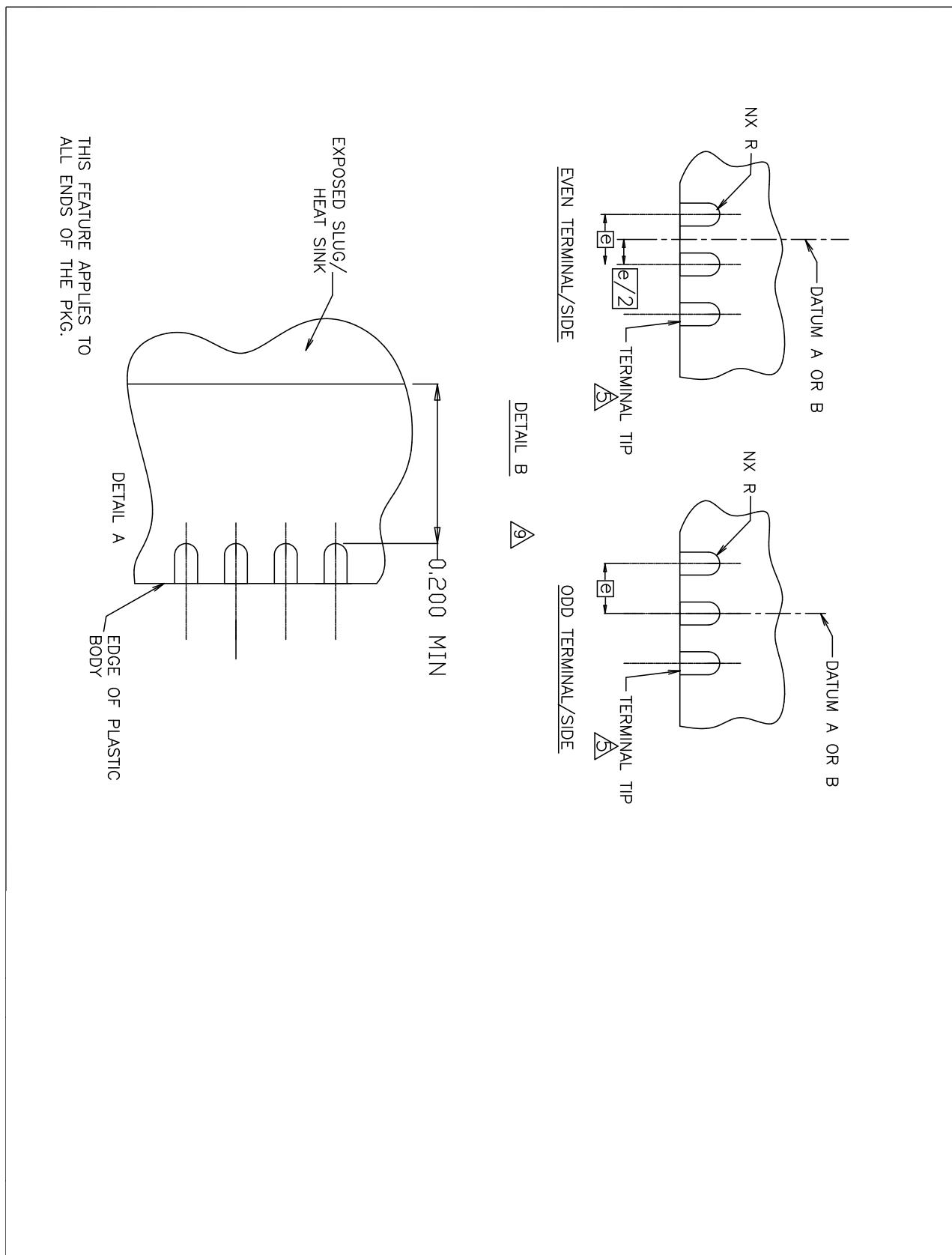

| Figure 25. 72-Pin QFN Package Dimensions (a) (in Millimeters) .....         | 119 |

| Figure 26. 72-Pin QFN Package Dimensions (b) (in Millimeters) .....         | 120 |

| Figure 27. 72-Pin QFN Dimensions .....                                      | 121 |

| Figure 28. Package Notes .....                                              | 122 |

## FEATURES

### HIGHLIGHTS

- Features 15 mHz to 560 Hz bandwidth

- Provides node clock for ITU-T G.8261/G.8262 Synchronous Ethernet (SyncE)

- Supports GR-253-CORE (OC-192) and ITU-T G.813 (STM-64) jitter generation requirements

- Provides clocks for 1 Gigabit and 10 Gigabit Ethernet applications

### MAIN FEATURES

- Provides an integrated single-chip solution for Synchronous Equipment Timing Source, including Stratum 3, 4E, 4, SMC, EEC-Option 1 and EEC-Option 2 Clocks

- Supports 1PPS input and output

- Employs PLL architecture to feature excellent jitter performance and minimize the number of external components

- Supports programmable DPLL bandwidth (15 mHz to 560 Hz) and damping factor (1.2 to 20 in 5 steps)

- Supports  $1.1 \times 10^{-5}$  ppm absolute holdover accuracy and  $4.4 \times 10^{-8}$  ppm instantaneous holdover accuracy

- Provides 2 differential output clocks whose frequencies cover from 1Hz (1PPS) to 644.53125 MHz

- Includes 25 MHz, 125 MHz and 156.25 MHz for CMOS outputs

- Includes 25.78125 MHz, 128.90625 MHz and 161.1328125 MHz for CMOS outputs

- Includes 25 MHz, 125 MHz, 156.25 MHz, 312.5 MHz and 625 MHz for differential outputs

- Includes 25.78125 MHz, 128.90625 MHz, 161.1328125 MHz, 322.265625 MHz and 644.53125 MHz for differential outputs

- Provides 1 single ended output clock whose frequencies cover from 1 Hz (1PPS) to 156.25 MHz

- Provides 2 differential input clocks whose frequency cover from 1 Hz (1PPS) to 625 MHz

- Includes 25 MHz, 125 MHz and 156.25 MHz for CMOS inputs

- Includes 25 MHz, 125 MHz, 156.25 MHz, 312.5 MHz and 625 MHz for differential inputs

- Provides 1 single ended input clock whose frequencies cover from 1 Hz (1PPS) to 156.25 MHz

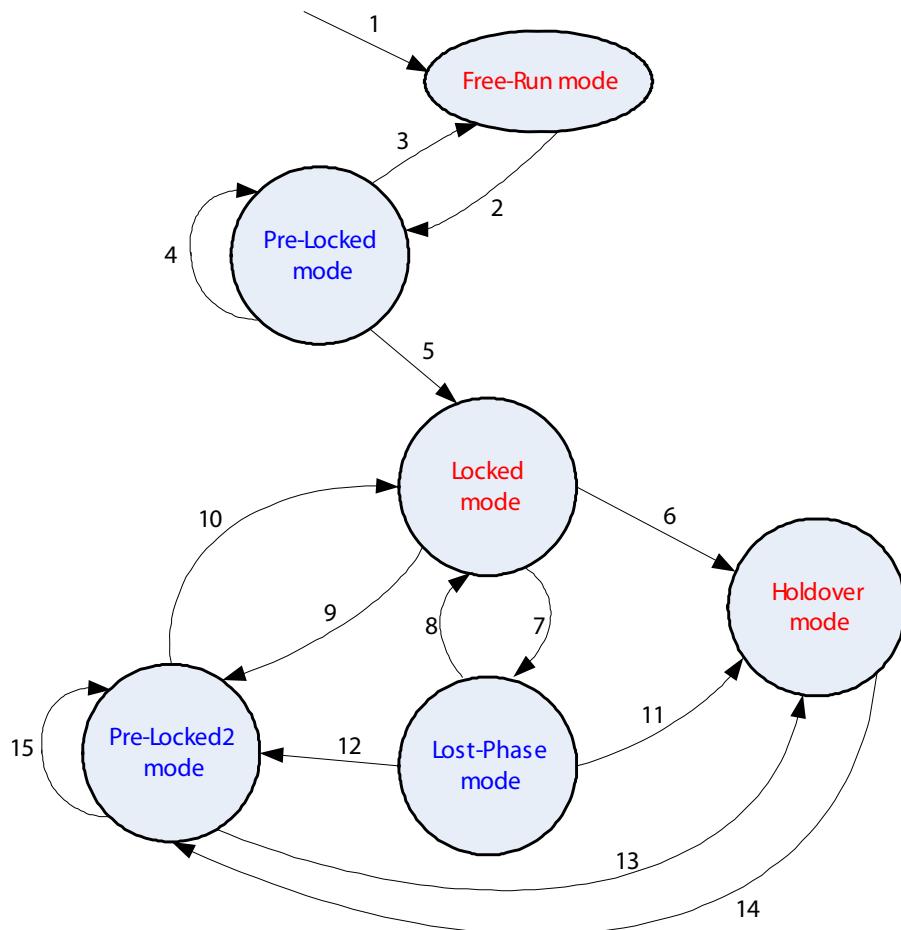

- Supports Forced or Automatic operating mode switch controlled by an internal state machine

- Automatic state machine supports Free- Run, Locked and Holdover

- Supports manual and automatic selected input clock switch

- Supports automatic hitless selected input clock switch on clock failure

- Supports Telcordia GR-1244-CORE, Telcordia GR-253-CORE, ITU-T G.812, ITU-T G.8262, ITU-T G.813 and ITU-T G.783 recommendations

### OTHER FEATURES

- Microprocessor interface modes: I2C and Serial

- IEEE 1149.1 JTAG Boundary Scan

- Single 3.3 V operation with 5 V tolerant CMOS I/Os

- 72-pin QFN package, green package options available

### APPLICATIONS

- 1 Gigabit Ethernet and 10 Gigabit Ethernet

- Synchronous Ethernet equipment

- Core and access IP switches / routers

- Gigabit and terabit IP switches / routers

- IP and ATM core switches and access equipment

- Broadband and multi-service access equipment

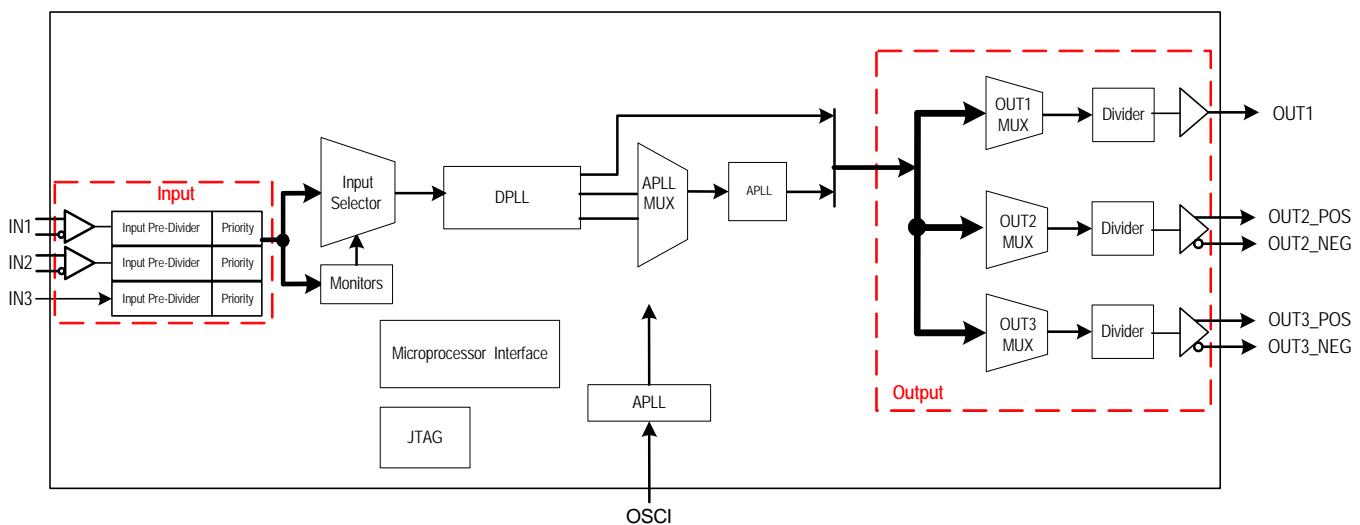

Figure 1. Functional Block Diagram

## DESCRIPTION

The 8V89307 is an integrated solution for the Synchronous Equipment Timing Source supporting EEC-Option1, EEC-Option2 clocks in Synchronous Ethernet equipment.

The device has a high quality DPLL to provide system clocks for node timing synchronization within a Synchronous Ethernet network. It also integrates an APLL for better jitter performance.

An input clock is automatically or manually selected. It supports three primary operating modes: Free-Run, Locked and Holdover. In Free-Run mode, the DPLL refers to the master clock. In Locked mode, the DPLL locks to the selected input clock. In Holdover mode, the DPLL resorts to the frequency data acquired in Locked mode. Whatever the operating

mode is, the DPLL gives a stable performance without being affected by operating conditions or silicon process variations.

The device provides programmable DPLL bandwidths: 15 mHz to 560 Hz and damping factors: 1.2 to 20 in 5 steps. Different settings cover all clock synchronization requirements.

A stable oscillator is required for the master clock in different applications. The master clock is used as a reference clock for all the internal circuits in the device. It can be calibrated within  $\pm 741$  ppm.

All the read/write registers are accessed through a microprocessor interface. The device supports Serial and I2C interfaces.

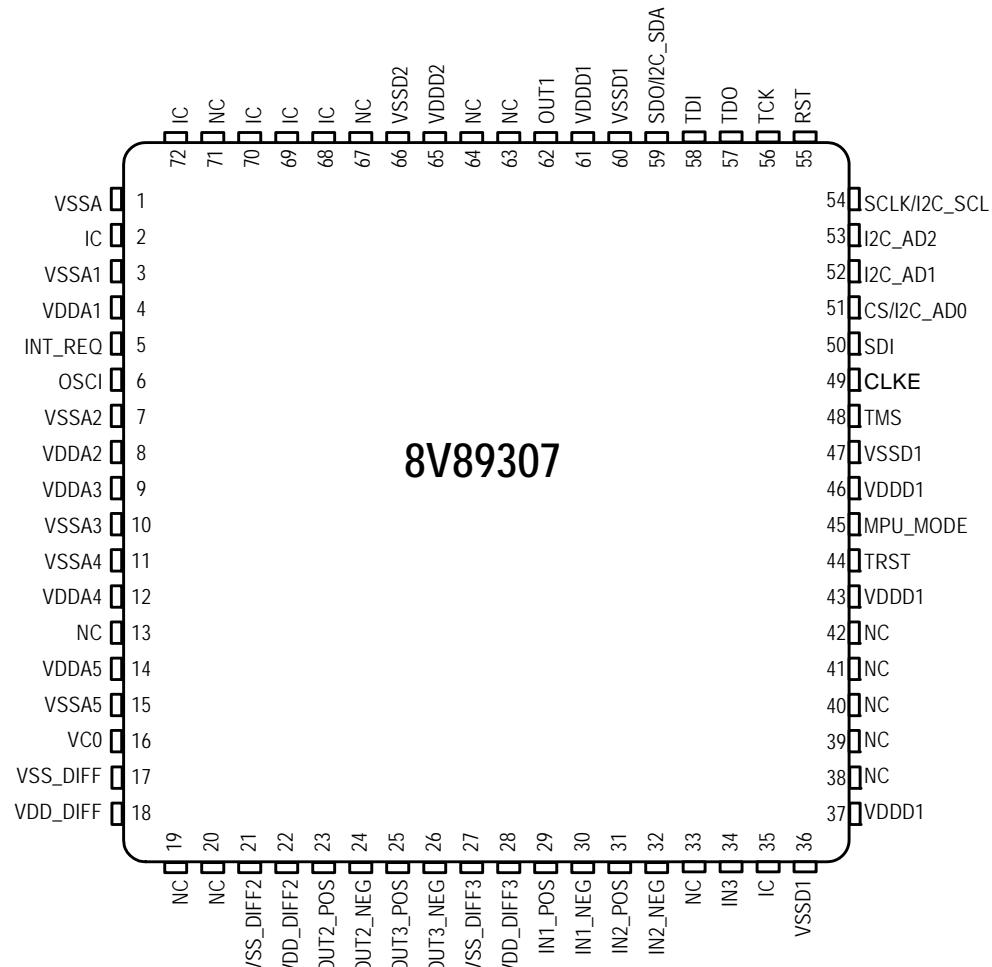

## 1 PIN ASSIGNMENT

**Figure 1. Pin Assignment (Top View)**

## 2 PIN DESCRIPTION

Table 1: Pin Description

| Name                  | Pin No. | I/O            | Type      | Description <sup>1, 2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------|---------|----------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Global Control Signal |         |                |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| OSCI                  | 6       | I              | CMOS      | <b>OSCI: Crystal Oscillator Master Clock</b><br>A nominal 12.8000 MHz clock provided by a crystal oscillator is input on this pin. It is the master clock for the device.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RST                   | 55      | I<br>pull-up   | CMOS      | <b>RST: Reset</b><br>A low pulse of at least 50 $\mu$ s on this pin resets the device. After this pin is high, the device will still be held in reset state for 500 ms (typical).                                                                                                                                                                                                                                                                                                                                                                                                               |

| Input Clock           |         |                |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

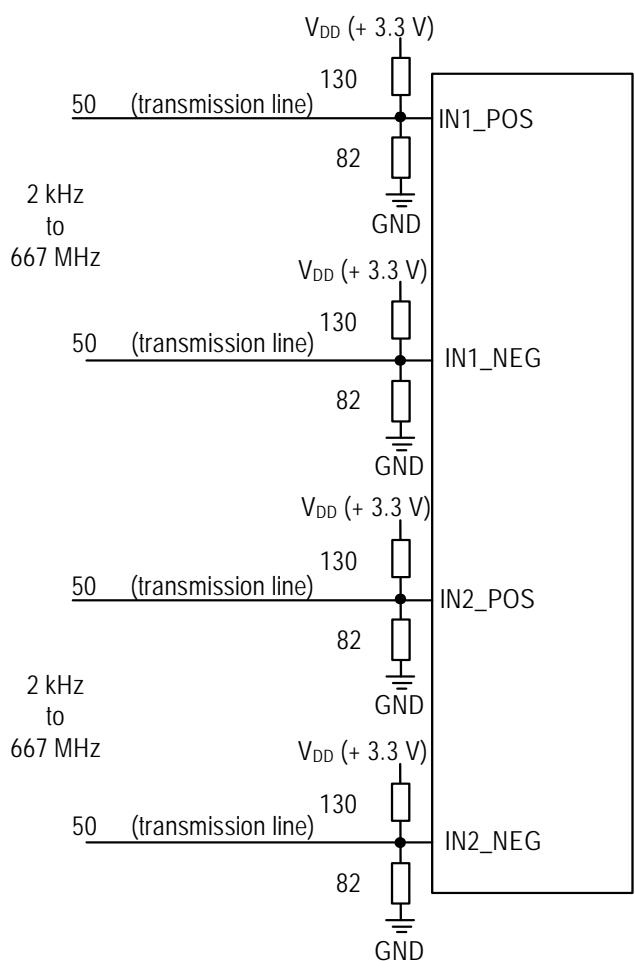

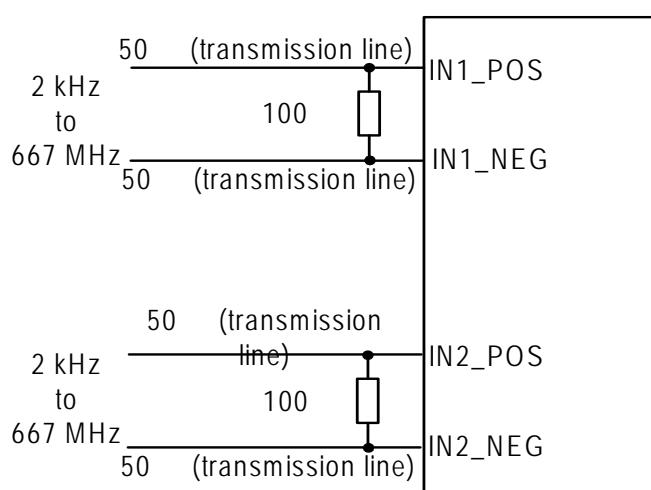

| IN1_POS               | 29      | I              | PECL/LVDS | <b>IN1_POS / IN1_NEG: Positive / Negative Input Clock 1</b><br>A 1PPS, 2 kHz, 4 kHz, N x 8 kHz <sup>3</sup> , 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.25 MHz, 6.48 MHz, 10 MHz, 19.44 MHz, 25 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 155.52 MHz, 156.25 MHz, 311.04 MHz, 312.5 MHz, 622.08 MHz or 625 MHz clock is differentially input on this pair of pins. Whether the clock signal is PECL or LVDS is automatically detected.<br>Single-ended input for differential input is also supported. Refer to <a href="#">Chapter 7.3.2.3 Single-Ended Input for Differential Input</a> . |

| IN1_NEG               | 30      | I              |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| IN2_POS               | 31      | I              | PECL/LVDS | <b>IN2_POS / IN2_NEG: Positive / Negative Input Clock 2</b><br>A 1PPS, 2 kHz, 4 kHz, N x 8 kHz <sup>3</sup> , 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.25 MHz, 6.48 MHz, 10 MHz, 19.44 MHz, 25 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 155.52 MHz, 156.25 MHz, 311.04 MHz, 312.5 MHz, 622.08 MHz or 625 MHz clock is differentially input on this pair of pins. Whether the clock signal is PECL or LVDS is automatically detected.<br>Single-ended input for differential input is also supported. Refer to <a href="#">Chapter 7.3.2.3 Single-Ended Input for Differential Input</a> . |

| IN2_NEG               | 32      | I              |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| IN3                   | 34      | I<br>pull-down | CMOS      | <b>IN3: Input Clock 3</b><br>A 1PPS, 2 kHz, 4 kHz, N x 8 kHz <sup>3</sup> , 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.25 MHz, 6.48 MHz, 10 MHz, 19.44 MHz, 25 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 155.52 MHz or 156.25 MHz clock is input on this pin.                                                                                                                                                                                                                                                                                                                                |

| Output Clock          |         |                |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| OUT1                  | 62      | O              | CMOS      | <b>OUT1: Output Clock 1</b><br>A 1PPS, 400 Hz, 2 kHz, 8 kHz, 64 kHz, N x E1 <sup>4</sup> , N x T1 <sup>5</sup> , N x 13.0 MHz <sup>6</sup> , N x 3.84 MHz <sup>7</sup> , 5 MHz, 10 MHz, 20 MHz, E3, T3, 6.48 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 25MHz, 25.78125 MHz, 125 MHz, 128.90625 MHz, 155.52 MHz or 156.25 MHz or 161.1328125 MHz clock is output on these pins.                                                                                                                                                                                                |

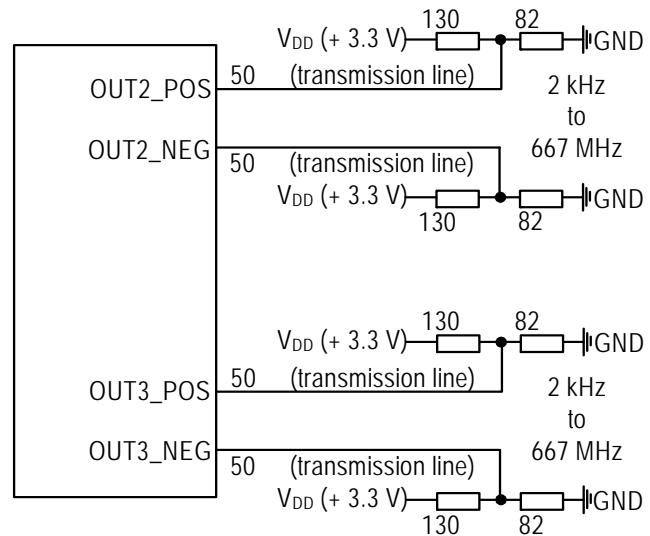

| OUT2_POS              | 23      | O              | PECL/LVDS | <b>OUT2_POS / OUT2_NEG: Positive / Negative Output Clock 2</b><br>A 1PPS, 400 Hz, 2 kHz, 8 kHz, 64 kHz, N x E1 <sup>4</sup> , N x T1 <sup>5</sup> , N x 13.0 MHz <sup>6</sup> , N x 3.84 MHz <sup>7</sup> , 5 MHz, 10 MHz, 20 MHz, 25 MHz, E3, T3, 6.48 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 125 MHz, 128.90625 MHz, 155.52 MHz, 156.25 MHz, 161.1328125MHz, 311.04 MHz, 312.5 MHz, 322.265625 MHz, 622.08 MHz, 625 MHz or 644.53125 MHz clock is differentially output on this pin pair.                                                                                |

| OUT2_NEG              | 24      | O              |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| OUT3_POS              | 25      | O              | PECL/LVDS | <b>OUT3_POS / OUT3_NEG: Positive / Negative Output Clock 3</b><br>A 1PPS, 400 Hz, 2 kHz, 8 kHz, 64 kHz, N x E1 <sup>4</sup> , N x T1 <sup>5</sup> , N x 13.0 MHz <sup>6</sup> , N x 3.84 MHz <sup>7</sup> , 5 MHz, 10 MHz, 20 MHz, 25 MHz, E3, T3, 6.48 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 125 MHz, 128.90625 MHz, 155.52 MHz, 156.25 MHz, 161.1328125 MHz, 311.04 MHz, 312.5 MHz, 322.265625 MHz, 622.08 MHz, 625 MHz or 644.53125 MHz clock is differentially output on this pin pair.                                                                               |

| OUT3_NEG              | 26      | O              |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

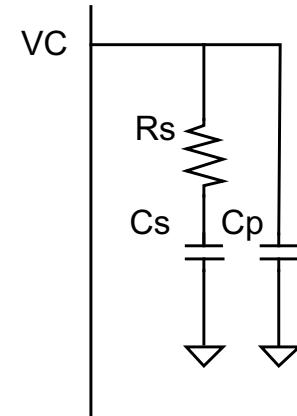

| VC0                   | 16      | O              | Analog    | <b>VC0: APLL VC Output</b><br>External RC filter<br>See <a href="#">"APLL" on page 32</a> for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Table 1: Pin Description (Continued)

| Name                     | Pin No. | I/O              | Type | Description <sup>1, 2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------|---------|------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Microprocessor Interface |         |                  |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CS / I2C_ADO             | 51      | I/O<br>pull-up   | CMOS | <p><b>CS: Chip Selection</b><br/>In Serial mode, this pin is an input. A transition from high to low must occur on this pin for each read or write operation and this pin should remain low until the operation is over.</p> <p><b>I2C_ADO: Device Address Bit 0</b><br/>In I2C mode, I2C_AD[2:0] pins are the address bus of the microprocessor interface.</p>                                                                                                                                                                                                                                           |

| INT_REQ                  | 5       | 0                | CMOS | <p><b>INT_REQ: Interrupt Request</b><br/>This pin is used as an interrupt request. The output characteristics are determined by the HZ_EN bit (b1, 0CH) and the INT_POL bit (b0, 0CH).</p>                                                                                                                                                                                                                                                                                                                                                                                                                |

| MPU_MODE                 | 45      | I<br>pull-down   | CMOS | <p><b>MPU_MODE: Microprocessor Interface Mode Selection</b><br/>The device supports 2 microprocessor interface modes: I2C and Serial.<br/>During reset, these pins determine the default value of the MPU_SEL_CNFG[0] bit(b0, 7FH) as follows:<br/>0: I2C mode<br/>1: Serial mode<br/>After reset, these pins are general purpose inputs. The microprocessor interface mode is selected by the MPU_SEL_CNFG[0] bits (b0, 7FH).<br/>After reset de-assertion, wait 10 <math>\mu</math>s for the mode to be active.<br/>The value of this pin is always reflected by the MPU_PIN_STS[0] bits (b0, 02H).</p> |

| CLKE                     | 49      | I/O<br>pull-down | CMOS | <p><b>CLKE: SCLK Active Edge Selection</b><br/>In Serial mode, this pin is an input, it selects the active edge of SCLK to update the SDO:<br/>High - The falling edge;<br/>Low - The rising edge.</p> <p>See <a href="#">Table 25</a> for details.</p>                                                                                                                                                                                                                                                                                                                                                   |

| SDI                      | 50      | I/O<br>pull-down | CMOS | <p><b>SDI: Serial Data Input</b><br/>In Serial mode, this pin is used as the serial data input. Address and data on this pin are serially clocked into the device on the rising edge of SCLK.</p> <p>See <a href="#">Table 25</a> for details.</p>                                                                                                                                                                                                                                                                                                                                                        |

| SDO / I2C_SDA            | 59      | I/O<br>pull-down | CMOS | <p><b>SDO: Serial Data Output</b><br/>In Serial mode, this pin is used as the serial data output. Data on this pin is serially clocked out of the device on the active edge of SCLK.</p> <p><b>I2C_SDA: Serial Data Input/Output</b><br/>In I2C mode, this pin is used as the input/output for the serial data.</p>                                                                                                                                                                                                                                                                                       |

| I2C_AD1                  | 52      | I<br>pull-up     | CMOS | <p><b>I2C_AD1: Device Address Bit 1</b><br/>In I2C mode, I2C_AD[2:0] pins are the address bus of the microprocessor interface.<br/>In Serial mode, this pin should be connected to ground.</p>                                                                                                                                                                                                                                                                                                                                                                                                            |

| I2C_AD2                  | 53      | I<br>pull-up     | CMOS | <p><b>I2C_AD2: Device Address Bit 2</b><br/>In I2C mode, I2C_AD[2:0] pins are the address bus of the microprocessor interface.<br/>In Serial mode, this pin should be connected to ground.</p>                                                                                                                                                                                                                                                                                                                                                                                                            |

| SCLK / I2C_SCL           | 54      | I<br>pull-down   | CMOS | <p><b>SCLK: Shift Clock</b><br/>In Serial mode, a shift clock is input on this pin.<br/>Data on SDI is sampled by the device on the rising edge of SCLK. Data on SDO is updated on the active edge of SCLK. The active edge is determined by the CLKE.</p> <p><b>I2C_SCL: Serial Clock Line</b><br/>In I2C mode, the serial clock is input on this pin.</p>                                                                                                                                                                                                                                               |

Table 1: Pin Description (Continued)

| Name                   | Pin No.        | I/O            | Type | Description <sup>1, 2</sup>                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------|----------------|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG (per IEEE 1149.1) |                |                |      |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TRST                   | 44             | I<br>pull-down | CMOS | TRST: JTAG Test Reset (Active Low)<br>A low signal on this pin resets the JTAG test port.<br>This pin should be connected to ground when JTAG is not used.                                                                                                                                                                                                                                                                       |

| TMS                    | 48             | I<br>pull-up   | CMOS | TMS: JTAG Test Mode Select<br>The signal on this pin controls the JTAG test performance and is sampled on the rising edge of TCK.                                                                                                                                                                                                                                                                                                |

| TCK                    | 56             | I<br>pull-down | CMOS | TCK: JTAG Test Clock<br>The clock for the JTAG test is input on this pin. TDI and TMS are sampled on the rising edge of TCK and TDO is updated on the falling edge of TCK.<br>If TCK is idle at a low level, all stored-state devices contained in the test logic will indefinitely retain their state.                                                                                                                          |

| TDI                    | 58             | I<br>pull-up   | CMOS | TDI: JTAG Test Data Input<br>The test data are input on this pin. They are clocked into the device on the rising edge of TCK.                                                                                                                                                                                                                                                                                                    |

| TDO                    | 57             | O              | CMOS | TDO: JTAG Test Data Output<br>The test data are output on this pin. They are clocked out of the device on the falling edge of TCK.<br>TDO pin outputs a high impedance signal except during the process of data scanning.<br>This pin can indicate the interrupt of DPLL selected input clock fail, as determined by the LOS_FLAG_ON_TDO bit (b6, 0BH). Refer to <a href="#">Chapter 3.8.1 Input Clock Validity</a> for details. |

| Power & Ground         |                |                |      |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VDDD1                  | 37, 43, 46, 61 | Power          | -    | VDDD1: Digital Core Power.                                                                                                                                                                                                                                                                                                                                                                                                       |

| VDDD2                  | 65             | Power          | -    | VDDD2: CMOS CLK Output Power                                                                                                                                                                                                                                                                                                                                                                                                     |

| VDD_DIFF               | 18             | Power          | -    | VDD_DIFF: Differential I/O Power Supply                                                                                                                                                                                                                                                                                                                                                                                          |

| VDD_DIFF3              | 28             | Power          | -    | VDD_DIFF3: Differential I/O Power Supply                                                                                                                                                                                                                                                                                                                                                                                         |

| VDD_DIFF2              | 22             | Power          | -    | VDD_DIFF2: Differential I/O Power Supply                                                                                                                                                                                                                                                                                                                                                                                         |

| VSSD1                  | 36, 47, 60     | Ground         | -    | VSSD1: Digital Core Ground                                                                                                                                                                                                                                                                                                                                                                                                       |

| VSSD2                  | 66             | Ground         | -    | VSSD2: CMOS CLK Output Ground                                                                                                                                                                                                                                                                                                                                                                                                    |

| VSS_DIFF               | 17             | Ground         | -    | VSS_DIFF: Differential I/O Ground                                                                                                                                                                                                                                                                                                                                                                                                |

| VSS_DIFF3              | 27             | Ground         | -    | VSS_DIFF3: Differential I/O Ground                                                                                                                                                                                                                                                                                                                                                                                               |

| VSS_DIFF2              | 21             | Ground         | -    | VSS_DIFF2: Differential I/O Ground                                                                                                                                                                                                                                                                                                                                                                                               |

| VSSA                   | 1              | Ground         | -    | VSSA: Common Ground                                                                                                                                                                                                                                                                                                                                                                                                              |

| VSSA1                  | 3              |                |      | VSSAn: APLL Ground                                                                                                                                                                                                                                                                                                                                                                                                               |

| VSSA2                  | 7              |                |      |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VSSA3                  | 10             | Ground         | -    |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VSSA4                  | 11             |                |      |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VSSA5                  | 15             |                |      |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VDDA1                  | 4              |                |      | VDDAn: APLL Power                                                                                                                                                                                                                                                                                                                                                                                                                |

| VDDA2                  | 8              |                |      |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VDDA3                  | 9              | Power          | -    |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VDDA4                  | 12             |                |      |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VDDA5                  | 14             |                |      |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Table 1: Pin Description (Continued)

| Name   | Pin No.                                               | I/O | Type | Description <sup>1, 2</sup>                                                                                   |

|--------|-------------------------------------------------------|-----|------|---------------------------------------------------------------------------------------------------------------|

| Others |                                                       |     |      |                                                                                                               |

| IC     | 72                                                    | -   | -    | <b>IC: Internal Connected</b><br>Internal Use. These pins should be connected to ground for normal operation. |

| IC     | 2, 35, 68, 69, 70                                     | -   | -    | <b>IC: Internal Connected</b><br>Internal Use. These pins should be left open for normal operation.           |

| NC     | 13, 19, 20, 33, 38, 39,<br>40, 41, 42, 63, 64, 67, 71 | -   | -    | <b>NC: Not Connected</b><br>These pins are not connected                                                      |

**Note:**

1. All the unused input pins should be connected to ground; the output of all the unused output pins are don't-care.

2. The contents in the brackets indicate the position of the register bit/bits.

3. N x 8 kHz:  $1 \leq N \leq 19440$ .

4. N x E1: N = 1, 2, 3, 4, 6, 8, 12, 16

5. N x T1: N = 1, 2, 3, 4, 6, 8, 12, 16, 24

6. N x 13.0 MHz: N = 1, 2

7. N x 3.84 MHz: N = 1, 2, 4, 8

## 3 FUNCTIONAL DESCRIPTION

### 3.1 RESET

The reset operation resets all registers and state machines to their default value or status.

After power on, the device must be reset for normal operation.

For a complete reset, the RST pin must be asserted low for at least 50  $\mu$ s. After the RST pin is pulled high, the device will still be in reset state for 250 ms (typical). If the RST pin is held low continuously, the device remains in reset state.

### 3.2 MASTER CLOCK

A nominal 12.8000 MHz clock, provided by a crystal oscillator, is input on the OSC1 pin. This clock is provided for the device as a master clock. The master clock is used as a reference clock for all the internal circuits. A better active edge of the master clock is selected by the OSC\_EDGE bit to improve jitter and wander performance.

In fact, an offset from the nominal frequency may be input on the OSC1 pin. This offset can be compensated by setting the NOMINAL\_FREQ\_VALUE[23:0] bits. The calibration range is within  $\pm 741$  ppm.

The crystal oscillator should be chosen accordingly to meet GR-1244-CORE, GR-253-CORE, ITU-T G.8262, ITU-T G.812 and ITU-T G.813.

Table 2: Related Bit / Register in [Chapter 3.2](#)

| Bit                      | Register                                                                  | Address (Hex) |

|--------------------------|---------------------------------------------------------------------------|---------------|

| NOMINAL_FREQ_VALUE[23:0] | NOMINAL_FREQ[23:16]_CNFG, NOMINAL_FREQ[15:8]_CNFG, NOMINAL_FREQ[7:0]_CNFG | 06, 05, 04    |

| OSC_EDGE                 | DIFFERENTIAL_IN_OUT_OSCI_CNFG                                             | 0A            |

### 3.3 INPUT CLOCKS

The device provide 3 input clock ports and supports the following types of input:

- PECL/LVDS

- CMOS

The 8V89307 supports Telecom and Ethernet frequencies from 1PPS up to 625 MHz. It supports 1PPS, 2 kHz, 4 kHz, N x 8 kHz, 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.25 MHz, 6.48 MHz, 10 MHz, 19.44 MHz, 25 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 125 MHz, 155.52 MHz, 156.25 MHz, 311.04 MHz, 312.5 MHz, 622.08 MHz and 625 MHz frequencies.

IN3 supports CMOS input signal only.

IN1 and IN2 support PECL/LVDS input signal and automatically detect whether the signal is PECL or LVDS.

To lock to 10 MHz then first set 12E1\_GPS\_E3\_T3\_SEL[1:0] to GPS mode in DPLL & APLL Path Configuration Register, address 55H. 8V89307 supports single-ended input for differential input.

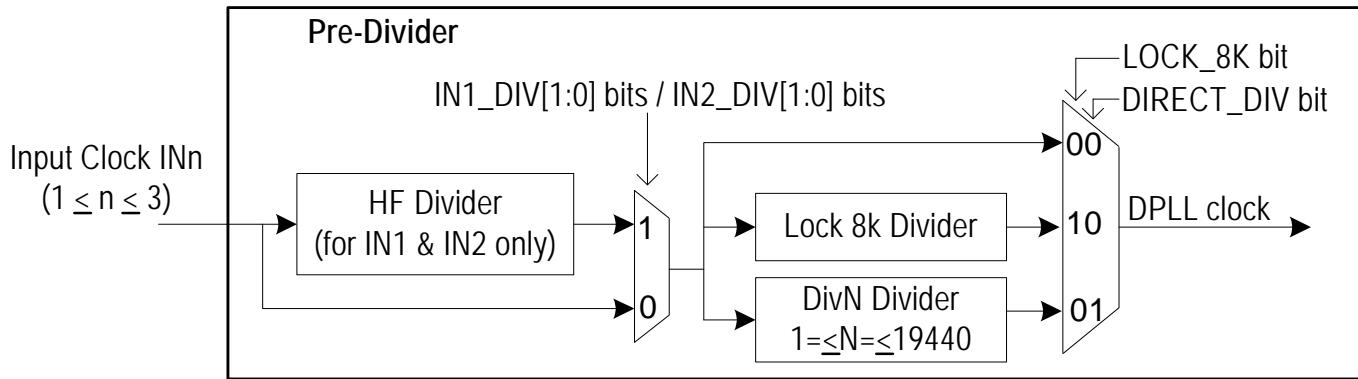

### 3.4 INPUT CLOCK PRE-DIVIDER

Each input clock is assigned an internal Pre-Divider. The Pre-Divider is used to divide the clock frequency down to the internal DPLL's required input frequency, which is no more than 38.88 MHz.

For IN1 ~ IN3, the DPLL required frequency is set by the corresponding IN\_FREQ[3:0] bits.

Each Pre-Divider consists of a DivN Divider and a Lock 8k Divider. IN1 and IN2 also include a HF (High Frequency) Divider. [Figure 2](#) shows a block diagram of the pre-dividers for an input clock and [Table 3](#) shows the Pre-Divider Functions.

When the Lock 8k Divider is used, the input clock is divided down to 8 kHz internally; the PRE\_DIVN\_VALUE [14:0] bits are not required. Lock 8k Divider can be used for 1.544 MHz, 2.048 MHz, 6.48 MHz, 19.44 MHz, 25.92 MHz or 38.88 MHz input clock frequency and the corresponding IN\_FREQ[3:0] bits should be set to match the input frequency.

For 2 kHz, 4 kHz or 8 kHz input clock frequency only, the Pre-Divider should be bypassed by setting IN1\_DIV[1:0] bits / IN2\_DIV[1:0] bits = 0, DIRECT\_DIV bit = 0, and LOCK\_8K bit = 0. The corresponding IN\_-

FREQ[3:0] bits should be set to match the input frequency. The input clock can be inverted, as determined by the IN\_2K\_4K\_8K\_INV bit.

The HF Divider, which is only available for IN1 and IN2, should be used when the input clock is higher than ( $>$ ) 155.52 MHz. The input clock can be divided by 4, 5 or can bypass the HF Divider, as determined by the IN1\_DIV[1:0]/IN2\_DIV[1:0] bits correspondingly.

Either the DivN Divider or the Lock 8k Divider can be used or both can be bypassed, as determined by the DIRECT\_DIV bit and the LOCK\_8K bit.

When the DivN Divider is used for INn ( $1 \leq n \leq 3$ ), the division factor setting should observe the following order:

1. Select an input clock by the PRE\_DIV\_CH\_VALUE[3:0] bits;

2. Write the lower eight bits of the division factor to the PRE\_DIVN\_VALUE[7:0] bits;

3. Write the higher eight bits of the division factor to the PRE\_DIVN\_VALUE[14:8] bits.

Once the division factor is set for the input clock selected by the PRE\_DIV\_CH\_VALUE[3:0] bits, it is valid until a different division factor is set for the same input clock. The division factor is calculated as follows:

$$\text{Division Factor} = (\text{the frequency of the clock input to the DivN Divider} \div \text{the frequency of the DPLL required clock set by the IN-FREQ[3:0] bits}) - 1$$

The DivN Divider can only divide the input clock whose frequency is less than or equal to ( $\leq$ ) 155.52 MHz.

The Pre-Divider configuration and the division factor setting depend on the input clock on one of the IN1 ~ IN3 pins and the DPLL required clock. Here is an example:

The input clock on the IN2 pin is 622.08 MHz; the DPLL required clock is 6.48 MHz by programming the IN\_FREQ[3:0] bits of register IN2 to '0010'. Do the following step by step to divide the input clock:

1. Use the HF Divider to divide the clock down to 155.52 MHz:

$622.08 \div 155.52 = 4$ , so set the IN2\_DIV[1:0] bits to '01';

2. Use the DivN Divider to divide the clock down to 6.48 MHz:

Set the PRE\_DIV\_CH\_VALUE[3:0] bits to '0110';

Set the DIRECT\_DIV bit in Register IN2\_CNFG to '1' and the LOCK\_8K bit in Register IN2\_CNFG to '0';

$155.52 \div 6.48 = 24$ ;  $24 - 1 = 23$ , so set the PRE\_DIVN\_VALUE[14:0] bits to '10111'.

Figure 2. Pre-Divider for An Input Clock

Table 3: Pre-Divider Function

| Pre-Divider              | Input Clock INn Frequency                                                                                   | Control Register                                                                                                                                                                                                                                                                                                                                    | Register/ Address <sup>1</sup>                                                                                    |

|--------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| HF- Divider <sup>2</sup> | >155.52 MHz                                                                                                 | IN1_DIV[1:0]<br>IN2_DIV[1:0]                                                                                                                                                                                                                                                                                                                        | IN1_IN2_HF_DIV_CNF (18)                                                                                           |

| Divider Bypassed         | 1 Hz, 2kHz, 4kHz, 8kHz, 1.544 MHz, 2.048 MHz, 6.25 MHz, 6.48 MHz, 10 MHz, 19.44 MHz, 25.92 MHz or 38.88 MHz | IN_FREQ[3:0] – set to match input Clock INn frequency.<br>LOCK_8K= 0'b; DIRECT_DIV= 0'b (Bypass Dividers)                                                                                                                                                                                                                                           | IN1_CNF ~ IN3_CNF (16, 19, 1A)                                                                                    |

| Lock 8K Divider          | 1.544 MHz, 2.048 MHz, 6.48 MHz, 19.44 MHz, 25.92 MHz or 38.88 MHz                                           | IN_FREQ[3:0] – set to match input Clock INn frequency.<br>LOCK_8K= 1'b; DIRECT_DIV= 0'b (select Lock 8k Divider)                                                                                                                                                                                                                                    | IN1_CNF ~ IN3_CNF (16, 19, 1A)                                                                                    |

| DivN                     | Nx8kHz<br>(1 ≤ N ≤ 19440)<br><br>Example:<br>25 MHz = 3125 x 8 kHz                                          | LOCK_8K= 0'b; DIRECT_DIV= 1'b (select DivN Divider)<br><br>IN_FREQ[3:0] – set to the DPLL required frequency.<br>('0000': 8 kHz (default))<br><br>PRE_DIV_CH_VALUE[3:0]<br>PRE_DIVN_VALUE[14:0]<br><br>Example:<br>25 MHz = 3125 x 8 kHz<br>Division Factor = 3125 -1= 3124 Dec (or 0C34h)<br>PRE_DIVN_VALUE[7:0]= 34h<br>PRE_DIVN_VALUE[14:8]= 0Ch | IN1_CNF ~ IN3_CNF (16, 19, 1A)<br><br>PRE_DIV_CH_CNF (23)<br>PRE_DIVN[14:8]_CNFG (25),<br>PRE_DIVN[7:0]_CNFG (24) |

Note 1: Please see register description for details.

Note 2: For 156.25 MHz, 312.5 MHz and 625 MHz differential input clock frequency, the divider mode should be DivN with IN\_FREQ[3:0] = '1100': 6.25 MHz.

### 3.5 INPUT CLOCK QUALITY MONITORING

The qualities of all the input clocks are always monitored in the following aspects:

- Activity

- Frequency

Activity and frequency monitoring are conducted on all the input clocks.

The qualified clocks are available for DPLL selection. The selected input clocks monitored further. Refer to [Chapter 3.7 Selected Input Clock Monitoring](#) for details.

#### 3.5.1 ACTIVITY MONITORING

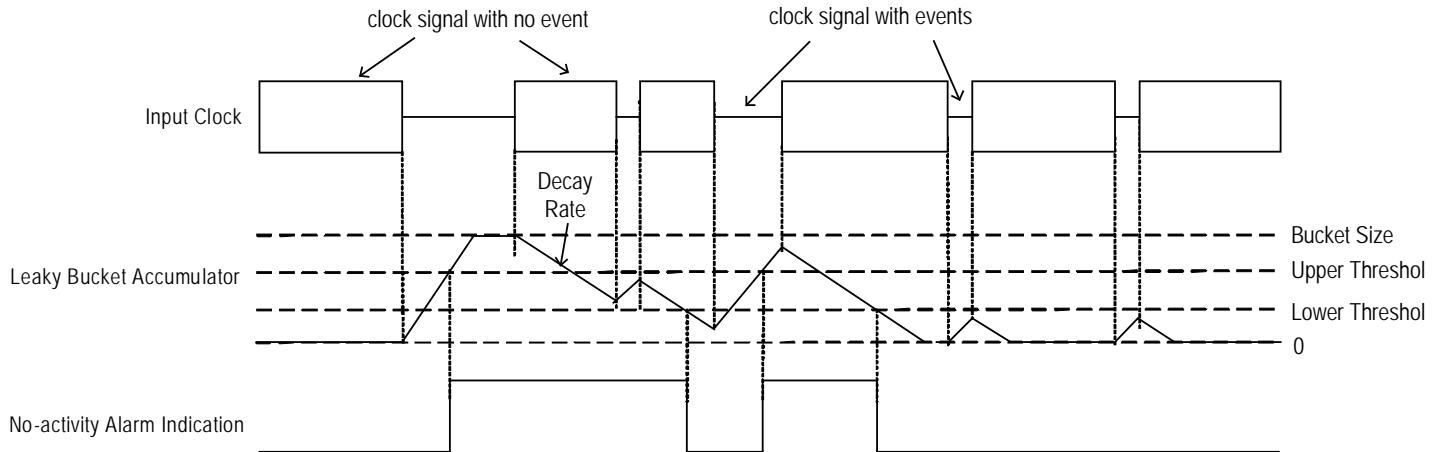

Activity is monitored by using an internal leaky bucket accumulator, as shown in [Figure 3](#).

Each input clock is assigned an internal leaky bucket accumulator. The input clock is monitored for each period of 128 ms, the internal leaky bucket accumulator is increased by 1 when an event is detected; and it is decreased by 1 when no event is detected within the period set by the decay rate. The event is that an input clock drifts outside ( $>$ )  $\pm 500$  ppm with respect to the master clock within a 128 ms period.

There are four configurations (0 - 3) for a leaky bucket accumulator. The leaky bucket configuration for an input clock is selected by the corresponding BUCKET\_SEL[1:0] bits. Each leaky bucket configuration consists of four elements: upper threshold, lower threshold, bucket size and decay rate.

The bucket size is the capability of the accumulator. If the number of the accumulated events reach the bucket size, the accumulator will stop increasing even if further events are detected. The upper threshold is a point above which a no-activity alarm is raised. The lower threshold is a point below which the no-activity alarm is cleared. The decay rate is a certain period during which the accumulator decreases by 1 if no event is detected.

The leaky bucket configuration is programmed by one of four groups of register bits: the BUCKET\_SIZE\_n\_DATA[7:0] bits, the UPPER\_THRESHOLD\_n\_DATA[7:0] bits, the LOWER\_THRESHOLD\_n\_DATA[7:0] bits and the DECAY\_RATE\_n\_DATA[1:0] bits respectively; 'n' is 0 ~ 3.

The no-activity alarm status of the input clock is indicated by the INn\_NO\_ACTIVITY\_ALARM bit ( $3 \geq n \geq 1$ ).

The input clock with a no-activity alarm is disqualified for clock selection for the DPLL.

**Figure 3. Input Clock Activity Monitoring**

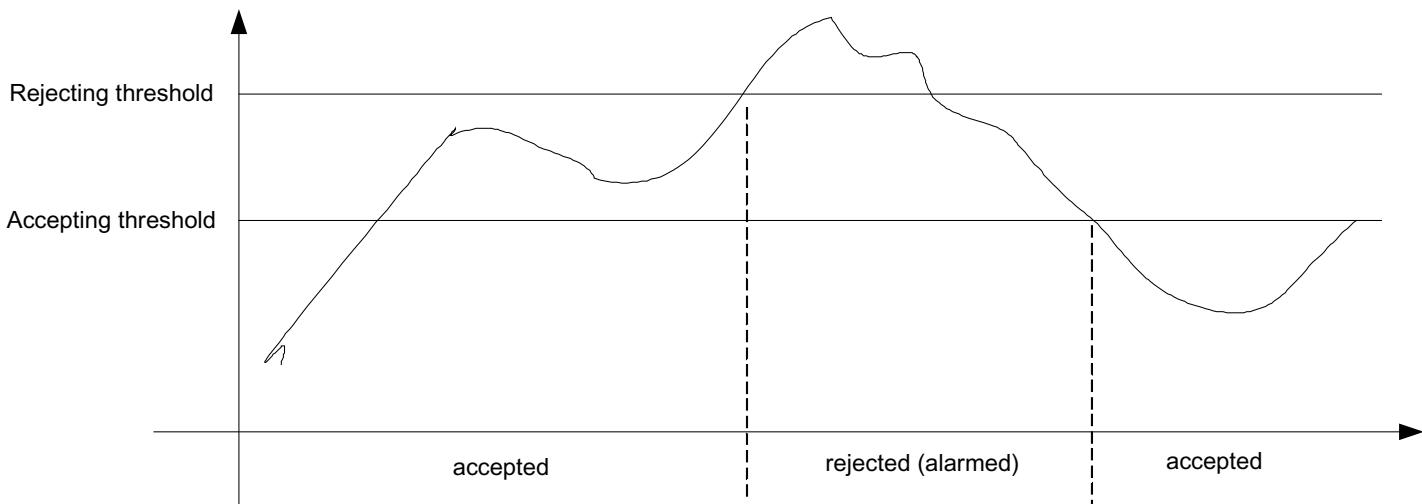

### 3.5.2 FREQUENCY MONITORING

Frequency is monitored by comparing the input clock with a reference clock. The reference clock can be derived from the master clock or the output of the DPLL, as determined by the FREQ\_MON\_CLK bit.

Each reference clock has a hard frequency monitor and a soft frequency monitor. Both monitors have two thresholds, rejecting threshold and accepting threshold, which are set in HARD\_FREQ\_MON\_THRESHOLD[7:0] and SOFT\_FREQ\_MON\_THRESHOLD[7:0]. So four frequency alarm thresholds are set for frequency monitoring: Hard Alarm Accepting Threshold, Hard Alarm Rejecting Threshold, Soft Alarm Accepting Threshold and Soft Alarm Rejecting Threshold.

The frequency hard alarm accepting threshold can be calculated as follows:

$$\text{Frequency Hard Alarm Accepting Threshold (ppm)} = (\text{HARD_FREQ_MON_THRESHOLD}[7:4] + 1) \times \text{FREQ_MON_FACTOR}[3:0] \text{ (b3-0, 2EH)}$$

The frequency hard alarm rejecting threshold can be calculated as follows:

$$\text{Frequency Hard Alarm Rejecting Threshold (ppm)} = (\text{HARD_FREQ_MON_THRESHOLD}[3:0] + 1) \times \text{FREQ_MON_FACTOR}[3:0] \text{ (b3-0, 2EH)}$$

When the input clock frequency raises to above the hard alarm rejecting threshold, the INn\_FREQ\_HARD\_ALARM bit ( $3 \geq n \geq 1$ ) will alarm and indicate '1'. The alarm will remain until the frequency is down to below the hard alarm accepting threshold, then the INn\_FREQ\_HARD\_ALARM bit will back to '0'. There is a hysteresis between frequency monitoring, refer to [Figure 4. Hysteresis Frequency Monitoring](#)

The soft alarm is indicated by the INn\_FREQ\_SOFT\_ALARM bit ( $3 \geq n \geq 1$ ) in the same way as hard alarm.

If the FREQ\_MON\_HARD\_EN bit is '1', the frequency alarm status of the input clock is indicated by the INn\_FREQ\_HARD\_ALARM bit ( $3 \geq n \geq 1$ ). When the FREQ\_MON\_HARD\_EN bit is '0', no frequency hard alarm is raised even if the input clock is above the frequency alarm threshold.

The input clock with a frequency hard alarm is disqualified for clock selection for the DPLL, but the soft alarm don't affect the clock selection for the DPLL.

In addition, if the input clock is 2 kHz, 4 kHz or 8 kHz, its clock edges with respect to the reference clock are monitored. If any edge drifts outside  $\pm 5\%$ , the input clock is disqualified for clock selection for the DPLL. The input clock is qualified if any edge drifts inside  $\pm 5\%$ . This function is supported only when the IN\_NOISE\_WINDOW bit is '1'.

The frequency of each input clock with respect to the reference clock can be read by doing the following step by step:

1. Select an input clock by setting the IN\_FREQ\_READ\_CH[3:0] bits;

2. Read the value in the IN\_FREQ\_VALUE[7:0] bits and calculate as follows:

$$\text{Input Clock Frequency (ppm)} = \text{IN_FREQ_VALUE}[7:0] \times \text{FREQ_MON_FACTOR}[3:0]$$

Note that the value set by the FREQ\_MON\_FACTOR[3:0] bits depends on the application.

**Figure 4. Hysteresis Frequency Monitoring**

Table 4: Related Bit / Register in Chapter 3.5

| Bit                                               | Register                                        | Address (Hex)  |

|---------------------------------------------------|-------------------------------------------------|----------------|

| BUCKET_SIZE_n_DATA[7:0] (3 $\geq$ n $\geq$ 0)     | BUCKET_SIZE_0_CNFG ~ BUCKET_SIZE_3_CNFG         | 33, 37, 3B, 3F |

| UPPER_THRESHOLD_n_DATA[7:0] (3 $\geq$ n $\geq$ 0) | UPPER_THRESHOLD_0_CNFG ~ UPPER_THRESHOLD_3_CNFG | 31, 35, 39, 3D |

| LOWER_THRESHOLD_n_DATA[7:0] (3 $\geq$ n $\geq$ 0) | LOWER_THRESHOLD_0_CNFG ~ LOWER_THRESHOLD_3_CNFG | 32, 36, 3A, 3E |

| DECAY_RATE_n_DATA[1:0] (3 $\geq$ n $\geq$ 0)      | DECAY_RATE_0_CNFG ~ DECAY_RATE_3_CNFG           | 34, 38, 3C, 40 |

| BUCKET_SEL[1:0]                                   | IN1_CNFG ~ IN3_CNFG                             | 16, 19, 1A     |

| INn_NO_ACTIVITY_ALARM (3 $\geq$ n $\geq$ 1)       | IN1_IN2_STS ~ IN3_STS                           | 44 ~ 45        |

| INn_FREQ_HARD_ALARM (3 $\geq$ n $\geq$ 1)         |                                                 |                |

| INn_FREQ_SOFT_ALARM (3 $\geq$ n $\geq$ 1)         |                                                 |                |

| FREQ_MON_CLK                                      | MON_SW_HS_CNFG                                  | 0B             |

| FREQ_MON_HARD_EN                                  |                                                 |                |

| HARD_FREQ_MON_THRESHOLD[7:0]                      | HARD_FREQ_MON_THRESHOLD_CNFG                    | 2F             |

| SOFT_FREQ_MON_THRESHOLD[7:0]                      | SOFT_FREQ_MON_THRESHOLD_CNFG                    | 30             |

| FREQ_MON_FACTOR[3:0]                              | FREQ_MON_FACTOR_CNFG                            | 2E             |

| IN_NOISE_WINDOW                                   | PHASE_MON_CNFG                                  | 78             |

| IN_FREQ_READ_CH[3:0]                              | IN_FREQ_READ_CH_CNFG                            | 41             |

| IN_FREQ_VALUE[7:0]                                | IN_FREQ_READ_STS                                | 42             |

### 3.6 DPLL INPUT CLOCK SELECTION

The DPLL\_INPUT\_SEL[3:0] bits determine the input clock selection, as shown in [Table 5](#):

**Table 5: Input Clock Selection for the DPLL**

| Control Bit         | Input Clock Selection |

|---------------------|-----------------------|

| DPLL_INPUT_SEL[3:0] |                       |

| other than 0000     | Forced selection      |

| 0000                | Automatic selection   |

Forced selection is done by setting the related registers.

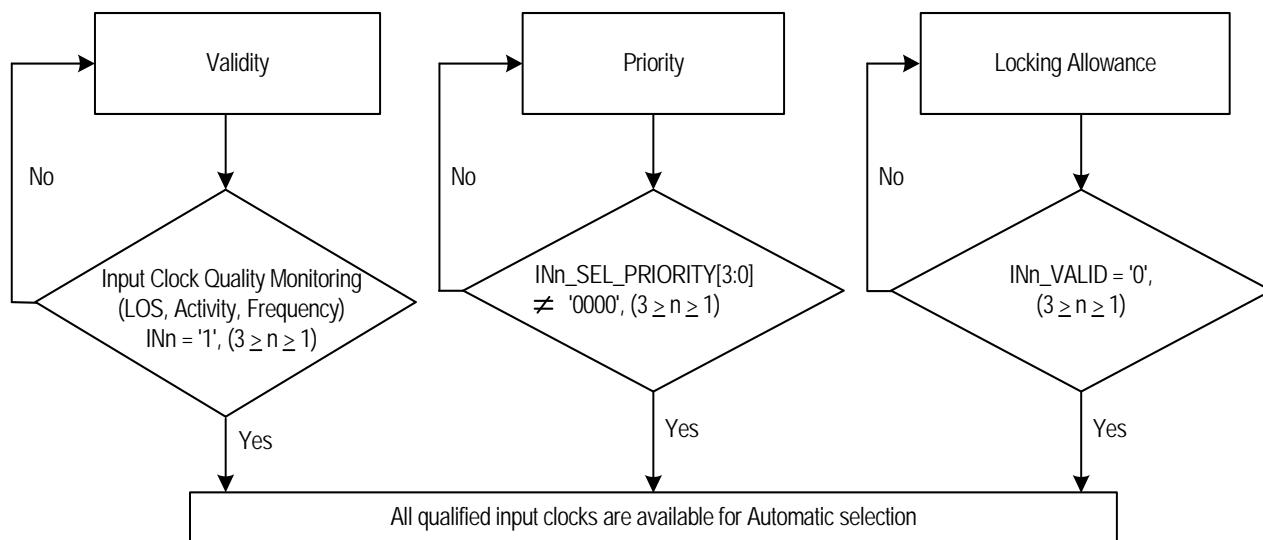

Automatic selection is done based on the results of input clocks quality monitoring and the related registers configuration.

#### 3.6.1 FORCED SELECTION

In Forced selection, the selected input clock is set by the INPUT\_SEL[3:0] bits. The results of input clocks quality monitoring (refer to [Chapter 3.5 Input Clock Quality Monitoring](#)) do not affect the input clock selection if Forced selection is used.

#### 3.6.2 AUTOMATIC SELECTION