## Description

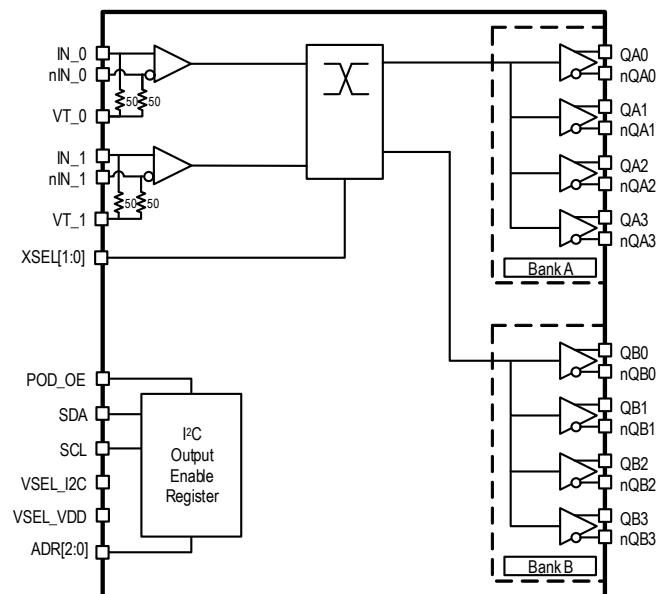

The 8T79S308 is a fully integrated signal fanout buffer for high-performance, low additive phase noise applications. The main function of the device is the distribution and fanout of high-frequency clocks or low-frequency synchronization signals.

The 8T79S308 is optimized to deliver very low phase noise clocks and precise, low-skew outputs, low device-to-device skew characteristics and fast output rise/fall times help the system design to achieve deterministic clock phase relationship across devices.

The device distributes the input signals (IN\_0, IN\_1) to two fanout banks. A input select logic allows the device to operate as 1:8 buffer, dual 1:4 buffers, and to cross the input signals.

The propagation delay in both outputs banks is designed for equal delay to support fixed phase relationships between both banks. All outputs are very flexible in LVPECL/LVDS output style configuration, output signal termination, and allow both DC and AC coupling. Outputs can be individually disabled through a serial interface.

The device is packaged in a lead-free (RoHS 6) 40-VFQFPN package. The extended temperature range supports wireless infrastructure, telecommunication, and networking end equipment requirements. The 8T79S308 is a member of the high-performance clock family from IDT.

## Block Diagram

## Features

- High-performance, flexible clock/data/1PPS fanout buffer

- Low phase noise floor: -160dBc/Hz (156.25MHz clock)

- Integrated phase noise of < 65fs RMS typical (12kHz–20MHz)

- Flexible input selection

- 1:8 Fanout modes

- Dual 1:4 Buffer fanout modes

- Eight differential outputs, organized in two banks of four outputs

- Low-power LVPECL/LVDS outputs support DC and AC coupling and LVPECL, LVDS line terminations techniques

- Individually configured outputs through an I<sup>2</sup>C interface

- LVPECL/LVDS output style, HCSL compatible (AC-coupled)

- Output amplitude

- Output enable

- Supported clock frequency range: 0 to 3GHz

- Core and output supply voltage modes:

- 3.3V core, 3.3V, 2.5V, and 1.8V output supply

- 2.5V core, 2.5V, and 1.8V output supply

- Selectable I<sup>2</sup>C I/O interface voltage: 1.8V and VDD

- Integrated low dropout regulators (LDOs) for excellent power supply noise rejection

- Package: 6 × 6 mm 40-VFQFPN

- Temperature range: -40°C to +105°C

## Typical Applications

- Wireless infrastructure applications: GSM, WCDMA, LTE, LTE-A

- Ideal clock driver for jitter-sensitive ADC and DAC circuits

- Low phase noise clock generation

- Ethernet line cards

- Radar and imaging

- Instrumentation and medical

## Contents

|                                                                          |    |

|--------------------------------------------------------------------------|----|

| Description .....                                                        | 1  |

| Block Diagram .....                                                      | 1  |

| Features .....                                                           | 1  |

| Typical Applications .....                                               | 1  |

| Pin Assignments .....                                                    | 3  |

| Pin Descriptions .....                                                   | 3  |

| Principles of Operation .....                                            | 5  |

| Overview .....                                                           | 5  |

| Voltage Supply .....                                                     | 5  |

| Pin Controlled Settings .....                                            | 6  |

| Input Signal Selection .....                                             | 6  |

| Configuration Registers .....                                            | 7  |

| Device Information Registers .....                                       | 8  |

| Device Configuration Registers .....                                     | 9  |

| Serial Interface .....                                                   | 10 |

| I2C Interface .....                                                      | 10 |

| Absolute Maximum Ratings .....                                           | 12 |

| Pin Characteristics .....                                                | 12 |

| DC Characteristics .....                                                 | 13 |

| AC Characteristics .....                                                 | 17 |

| Phase Noise Plots .....                                                  | 19 |

| Application Information .....                                            | 21 |

| Termination for Q, nQ LVDS Outputs .....                                 | 22 |

| AC Termination for Q, nQ Outputs .....                                   | 22 |

| Termination for Q, nQ LVPECL Outputs .....                               | 23 |

| Termination for Q, nQ LVPECL Outputs AC-Coupled into HCSL-Receiver ..... | 23 |

| Input Interface Circuits .....                                           | 24 |

| Thermal Characteristics .....                                            | 26 |

| Temperature Considerations .....                                         | 26 |

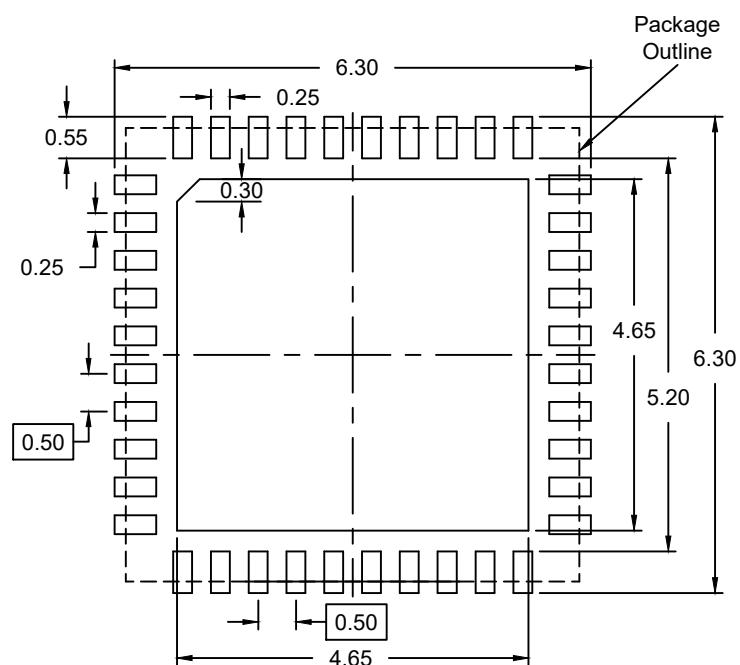

| Package Outline Drawings .....                                           | 28 |

| Marking Diagram .....                                                    | 28 |

| Ordering Information .....                                               | 28 |

| Glossary .....                                                           | 29 |

| Revision History .....                                                   | 29 |

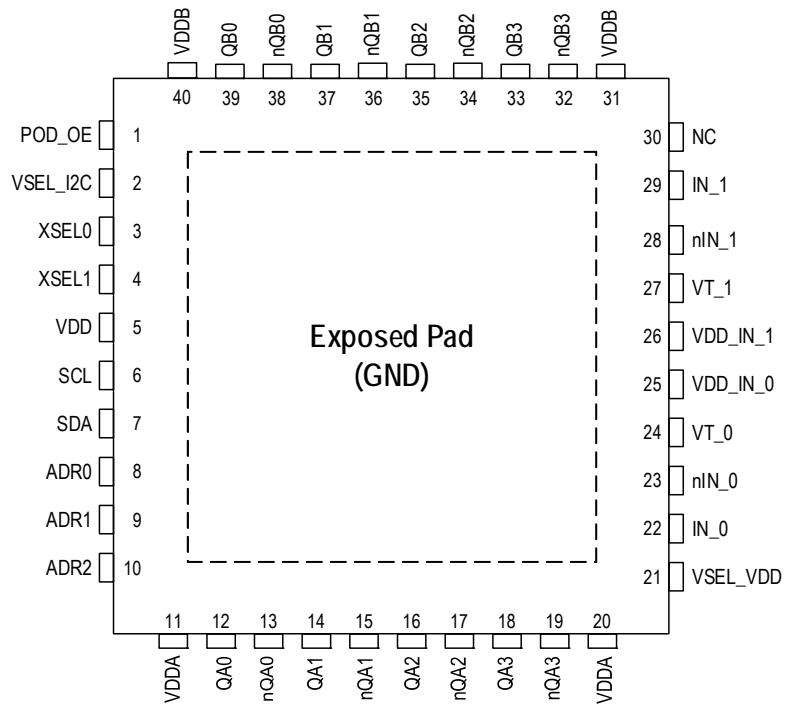

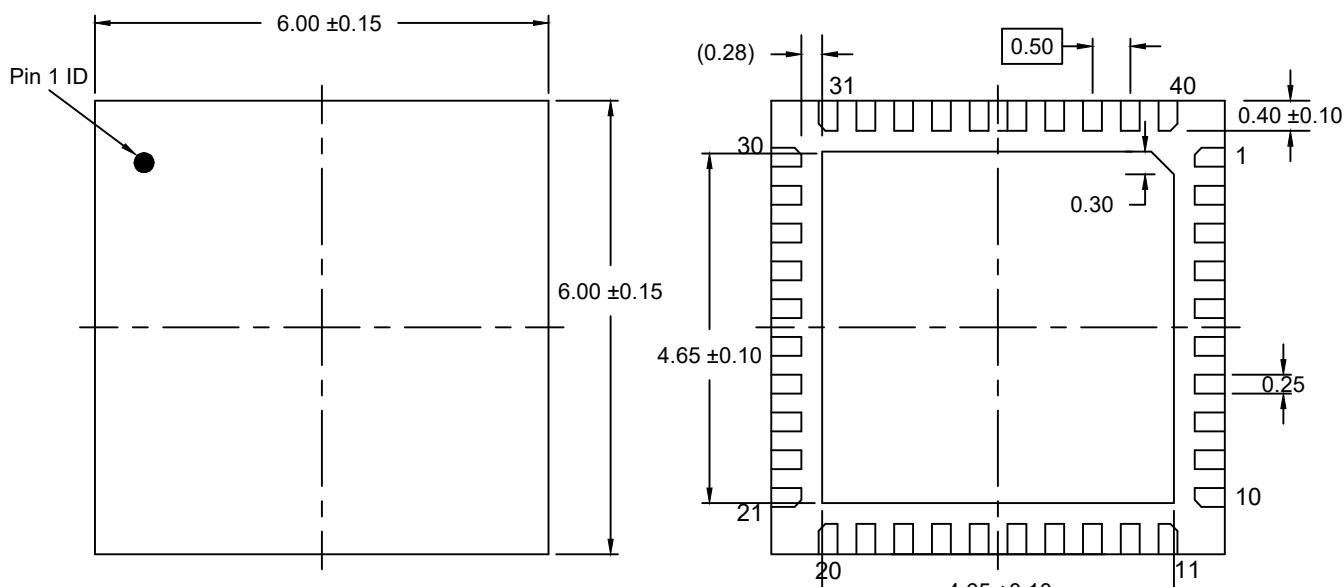

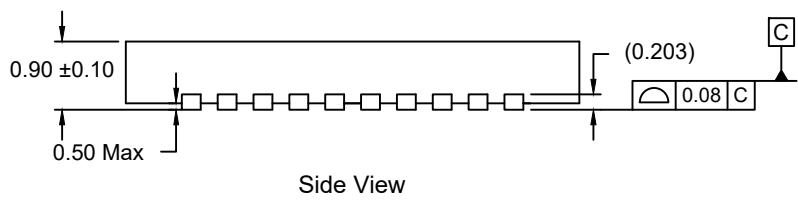

## Pin Assignments

Figure 1. Pin Assignments (Top View)

## Pin Descriptions

Table 1. Pin Descriptions<sup>[a]</sup>

| Pin                | Name      | Type <sup>[b]</sup> | Description |                                                                                                                                               |

|--------------------|-----------|---------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Input Pins  |           |                     |             |                                                                                                                                               |

| 22                 | IN_0      | Input               |             | Device clock 0 inverting and non-inverting differential clock input. Internally terminated 50Ω to VT_0. Compatible with LVPECL, LVDS signals. |

| 23                 | nIN_0     |                     |             |                                                                                                                                               |

| 24                 | VT_0      | Termination         |             | Input for termination. Both IN_0 and nIN_0 inputs are internally terminated 50Ω to this pin.                                                  |

| 29                 | IN_1      | Input               |             | Device clock 1 inverting and non-inverting differential clock input. Internally terminated 50Ω to VT_1. Compatible with LVPECL, LVDS signals. |

| 28                 | nIN_1     |                     |             |                                                                                                                                               |

| 27                 | VT_1      | Termination         |             | Input for termination. Both IN_1 and nIN_1 inputs are internally terminated 50Ω to this pin.                                                  |

| Signal Output Pins |           |                     |             |                                                                                                                                               |

| 12, 13             | QA0, nQA0 | Output              |             | Differential clock output A0 (Bank A). Configurable LVPECL/LVDS style.                                                                        |

| 14, 15             | QA1, nQA1 | Output              |             | Differential clock output A1 (Bank A). Configurable LVPECL/LVDS style.                                                                        |

| 16, 17             | QA2, nQA2 | Output              |             | Differential clock output A2 (Bank A). Configurable LVPECL/LVDS style.                                                                        |

Table 1. Pin Descriptions<sup>[a]</sup> (Cont.)

| Pin                                          | Name         | Type <sup>[b]</sup> |    | Description                                                                                                                                                                                                                                       |

|----------------------------------------------|--------------|---------------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18,<br>19                                    | QA3,<br>nQA3 | Output              |    | Differential clock output A3 (Bank A). Configurable LVPECL/LVDS style.                                                                                                                                                                            |

| 39,<br>38                                    | QB0,<br>nQB0 | Output              |    | Differential clock output B0 (Bank B). Configurable LVPECL/LVDS style.                                                                                                                                                                            |

| 37,<br>36                                    | QB1,<br>nQB1 | Output              |    | Differential clock output B1 (Bank B). Configurable LVPECL/LVDS style.                                                                                                                                                                            |

| 35,<br>34                                    | QB2,<br>nQB2 | Output              |    | Differential clock output B2 (Bank B). Configurable LVPECL/LVDS style.                                                                                                                                                                            |

| 33,<br>32                                    | QB3,<br>nQB3 | Output              |    | Differential clock output B3 (Bank B). Configurable LVPECL/LVDS style.                                                                                                                                                                            |

| <b>I<sup>2</sup>C Serial Interface Pins</b>  |              |                     |    |                                                                                                                                                                                                                                                   |

| 6                                            | SCL          | Input               |    | Serial Control Port I <sup>2</sup> C Clock Input. Interface voltage is selected by the VSEL_I2C pin. Input has hysteresis. Use an external pull-up resistor to the serial interface supply voltage.                                               |

| 7                                            | SDA          | Input/<br>Output    |    | Serial Control Port I <sup>2</sup> C data I/O. Interface voltage is selected by the VSEL_I2C pin. Input has hysteresis (when input). For output: open collector, use an external pull-up resistor to the selected serial interface supply voltage |

| <b>LVCMOS Control Function Pins</b>          |              |                     |    |                                                                                                                                                                                                                                                   |

| 8                                            | ADR0         | Input               | PD | Serial Control Port/I <sup>2</sup> C Address Bit 0, 1 and 2. LVCMOS interface levels are determined by $V_{DD\_V}$ voltage.                                                                                                                       |

| 9                                            | ADR1         | Input               | PD |                                                                                                                                                                                                                                                   |

| 10                                           | ADR2         | Input               | PD |                                                                                                                                                                                                                                                   |

| 3                                            | XSEL_0       | Input               | PD | Signal distribution select pins 0 and 1. LVCMOS interface levels are determined by $V_{DD\_V}$ voltage.                                                                                                                                           |

| 4                                            | XSEL_1       | Input               | PD |                                                                                                                                                                                                                                                   |

| 2                                            | VSEL_I2C     | Input               | PD | Interface voltage select for the I <sup>2</sup> C interface pins. LVCMOS interface levels are determined by $V_{DD\_V}$ voltage.                                                                                                                  |

| 21                                           | VSEL_VDD     | Input               | PD | Core supply voltage select. Set this pin to 0 or 1 according to the applied core voltage (2.5V or 3.3V) of the device. LVCMOS interface levels.                                                                                                   |

| 30                                           | NC           | -                   |    | No connect.                                                                                                                                                                                                                                       |

| 1                                            | POD_OE       | Input               | PD | Power-on default output-enable state. LVCMOS interface levels are determined by $V_{DD\_V}$ voltage.                                                                                                                                              |

| <b>Power Pins and Exposed Pad Connection</b> |              |                     |    |                                                                                                                                                                                                                                                   |

| 25                                           | VDD_IN_0     | Power               |    | Positive supply voltage (3.3V, 2.5V) for the IN_0/nIN_0 input.                                                                                                                                                                                    |

| 26                                           | VDD_IN_1     | Power               |    | Positive supply voltage (3.3V, 2.5V) for the IN_1/nIN_1 input.                                                                                                                                                                                    |

| 11, 20                                       | VDDA         | Power               |    | Positive supply voltage (3.3V, 2.5V, 1.8V) for the QA[3:0] outputs.                                                                                                                                                                               |

| 31, 40                                       | VDDB         | Power               |    | Positive supply voltage (3.3V, 2.5V, 1.8V) for the QB[3:0] outputs.                                                                                                                                                                               |

| 5                                            | VDD          | Power               |    | Positive supply voltage (3.3V, 2.5V) for the device core functions.                                                                                                                                                                               |

| —                                            | GND          | Power               |    | Exposed pad: Ground supply voltage (GND) and ground return path. Connect to board GND (0V).                                                                                                                                                       |

[a] For essential information on power supply filtering, see [Application Information](#).

[b] PU (pull-up) and PD (pull-down) indicate internal input resistors (for values, see [Figure 13](#)).

# Principles of Operation

## Overview

The 8T79S308 is designed for low phase noise and skew critical differential clock distribution systems and supports clock frequencies from 1PPS up to 3GHz. An input-to-output cross-connect, individually configurable LVPECL/LVDS outputs, amplitude settings and output enable make this device very flexible. The power-up default output enable state can be set by an dedicated control input. An I<sup>2</sup>C interface is available for individual output configurations. The signal voltage level of the I<sup>2</sup>C interface pins is configurable to 1.8V and 2.5V/3.3V voltage supply. The configurable I<sup>2</sup>C slave address pins are available to allow up to eight devices on the same I<sup>2</sup>C bus.

**Signal flow:** The device can be configured as single 1:8 or dual 1:4 buffer with selectable IN\_0 and IN\_1 inputs as signal source, controlled by the XSEL[1:0] configuration input.

The output style state of each individual differential output Q, nQ can be set by the content the I<sup>2</sup>C register 0x10 (see [Table 10](#)). A logic zero to an I<sup>2</sup>C bit in register 0x10 sets corresponding differential output to LVPECL, while a logic one sets the differential output to LVDS (see [Table 11](#)). Register 0x10 resets to logic 0 (all outputs: LVPECL) at each power-up. Setting and changing the output style through the I<sup>2</sup>C interface is asynchronous to the input reference clock.

The output amplitude of each individual differential output Q, nQ can be set by the content of the I<sup>2</sup>C registers 0x11–0x12 (see [Table 11](#)). For LVPECL outputs, the device supports amplitude settings of 500mV and 750mV; for LVDS outputs, 350mV and 500mV are supported. Register 0x11-0x12 reset to logic 0 (LVPECL standard amplitude) at each power-up. Setting and changing the output style through the I<sup>2</sup>C interface is asynchronous to the input reference clock. For LVPECL, the output termination has to be adjusted for the selected amplitude.

The output enable/disable state of each individual differential output Q, nQ can be set by the content of I<sup>2</sup>C register 0x13 (see [Table 11](#)). A logic zero to an I<sup>2</sup>C bit in register 0x02 disables the corresponding differential output in high-impedance state, while a logic one enables the differential output (see [Table 11](#)). After each power cycle, the device copies the state of the POD\_OE input into all eight bits (D7-0) of register 0x13 to: If pin POD\_OE = 0 or open, the device powers up with all outputs disabled in high-impedance state, if pin POD\_OE=1, the device powers up with all outputs enabled. After the first valid I<sup>2</sup>C write, the output enable state is controlled by the I<sup>2</sup>C register 0x13. Setting and changing the output enable state through the I<sup>2</sup>C interface is asynchronous to the input reference clock.

## Voltage Supply

Table 2. Supported Voltage Supply Operations

| Core Supply $V_{DD\_V}$ <sup>[a][b]</sup> | Output Supply $V_{DD\_O}$ <sup>[c][d]</sup> |

|-------------------------------------------|---------------------------------------------|

| 3.3V                                      | 3.3V, 2.5V, 1.8V                            |

| 2.5V                                      | 2.5V, 1.8V                                  |

[a]  $V_{DD\_V}$  denotes  $V_{DD}$ ,  $V_{DD\_IN\_1}$ ,  $V_{DD\_IN\_0}$ . I<sup>2</sup>C interface levels are configured by the VSEL\_I2C pin.

[b]  $V_{DD\_V}$  core supply voltages must be equal:  $V_{DD} = V_{DD\_IN\_0} = V_{DD\_IN\_1}$ .

[c]  $V_{DD\_O}$  denotes  $V_{DDA}$  and  $V_{DDB}$ .  $V_{DD\_V} \geq V_{DD\_O}$ .

[d]  $V_{DDA} = V_{DDB}$  and  $V_{DDA} \neq V_{DDB}$  are both supported voltage operations.

## Pin Controlled Settings

Table 3. Output State Power-On Default Setting

| POD_OE      | Operation                                                                                                              |

|-------------|------------------------------------------------------------------------------------------------------------------------|

| 0 (default) | After power-up and before the first I <sup>2</sup> C access, the outputs Qn, nQn are disabled in high impedance state. |

| 1           | After power-up and before the first I <sup>2</sup> C access, the outputs Qn, nQn are enabled.                          |

Table 4. I<sup>2</sup>C Interface Voltage Select

| VSEL_I2C    | Operation                                                                                                                                                                  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 (default) | I <sup>2</sup> C Interface voltage (SDA, SCL) is 1.8V. The 1.8V voltage supply is regulated internally and is independent on the <a href="#">V<sub>DD_V</sub></a> voltage. |

| 1           | I <sup>2</sup> C Interface voltage (SDA, SCL) is equal to the voltage supplied to <a href="#">V<sub>DD_V</sub></a> (2.5V or 3.3V).                                         |

Table 5. Core Voltage Supply Select

| VSEL_VDD    | Operation                                              |

|-------------|--------------------------------------------------------|

| 0 (default) | <a href="#">V<sub>DD_V</sub></a> core voltage is 2.5V. |

| 1           | <a href="#">V<sub>DD_V</sub></a> core voltage is 3.3V. |

## Input Signal Selection

Table 6. Input Signal and Buffer Signal Flow Selection

| XSEL_1      | XSEL_0      | Signal Flow                  | Description                      |

|-------------|-------------|------------------------------|----------------------------------|

| 0 (default) | 0 (default) | IN_0 → QA0-3 and QB0-3       | 1:8 Buffer                       |

| 0           | 1           | IN_0 → QA0-3<br>IN_1 → QB0-3 | Dual 1:4 Buffer                  |

| 1           | 0           | IN_0 → QB0-3<br>IN_1 → QA0-3 | Dual 1:4 Buffer, crossed signals |

| 1           | 1           | IN_1 → QA0-3 and QB0-3       | 1:8 Buffer (from IN_1)           |

## Configuration Registers

Table 7. Configuration Registers

| Register Address | Register Description     |

|------------------|--------------------------|

| 0x00-0x02        | Reserved                 |

| 0x03             | Device Type              |

| 0x04             | Device ID                |

| 0x05             | Device ID                |

| 0x06             | Device Version           |

| 0x07-0x0B        | Reserved                 |

| 0x0C             | Vendor ID                |

| 0x0D             | Vendor ID                |

| 0x0E             | I <sup>2</sup> C Address |

| 0x0F             | Reserved                 |

| 0x10             | Output Style             |

| 0x11             | Output Amplitude         |

| 0x12             | Output Amplitude         |

| 0x13             | Output Enable            |

| 0x14-0x1F        | Reserved                 |

## Device Information Registers

Table 8. Device Information Bit Field Locations

| Bit Field Location |          |    |    |    |                 |    |    |    |

|--------------------|----------|----|----|----|-----------------|----|----|----|

| Register Address   | D7       | D6 | D5 | D4 | D3              | D2 | D1 | D0 |

| 0x03               |          |    |    |    | DEV_TYPE[7:0]   |    |    |    |

| 0x04               |          |    |    |    | DEV_ID[7:0]     |    |    |    |

| 0x05               |          |    |    |    | DEV_ID[15:8]    |    |    |    |

| 0x06               |          |    |    |    | DEV_VER[7:0]    |    |    |    |

| 0x0C               |          |    |    |    | VENDOR_ID[7:0]  |    |    |    |

| 0x0D               |          |    |    |    | VENDOR_ID[15:8] |    |    |    |

| 0x0E               | Reserved |    |    |    | I2C_ADR         |    |    |    |

Table 9. Device Information Register Descriptions

| Register Description |            |                                                           |                                                                                                                                       |

|----------------------|------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Bit Field Name       | Field Type | Default (Binary)                                          | Description                                                                                                                           |

| DEV_TYPE[7:0]        | R only     | 0x07                                                      | Device (Chip) Type<br>Reads 0x07 (RF-Buffer) after power-up and reset.                                                                |

| DEV_ID[15:0]         | R only     | 0x04:<br>0100 0011<br>0x05:<br>0000 0000<br>Value: 0x0043 | Device ID<br>Device is composed of registers 0x05 (high byte) and register 0x04 (low byte).<br>Reads 0x0043 after power-up and reset. |

| DEV_VER[7:0]         | R only     | 0x00<br>Value: 0x00                                       | Device Version<br>0x00. Reads 0x00 (First silicon revision) after power-up and reset.                                                 |

| VENDOR_ID            | R only     | 0x0C:<br>0010 0110<br>0x0D:<br>0000 0100<br>Value: 0x0426 | Vendor ID<br>0x0426 (Integrated Device Technology, IDT). Reads 0x0426 (IDT) after power-up and reset.                                 |

Table 9. Device Information Register Descriptions

| Register Description |            |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------|------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit Field Name       | Field Type | Default (Binary)                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                     |

| I2C_ADR[6:0]         | R          | 1101<br>[ADR2]<br>[ADR1]<br>[ADR0] | <p><math>\text{I}^2\text{C}</math> Device address</p> <p>This read-only register stores the binary <math>\text{I}^2\text{C}</math> device address: 1101[ADR2][ADR1][ADR0].</p> <p>Bit D2 is equal to the logic state of the ADR2 pin</p> <p>Bit D1 is equal to the logic state of the ADR1 pin</p> <p>Bit D0 is equal to the logic state of the ADR0 pin.</p> <p>This register cannot be used to change the device address.</p> |

## Device Configuration Registers

Table 10. Device Configuration Bit Field Locations

| Bit Field Location |           |           |           |           |           |           |           |           |

|--------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Register Address   | D7        | D6        | D5        | D4        | D3        | D2        | D1        | D0        |

| 0x10               | STYLE_QB3 | STYLE_QB2 | STYLE_QB1 | STYLE_QB0 | STYLE_QA3 | STYLE_QA2 | STYLE_QA1 | STYLE_QA0 |

| 0x11               | A_QB3     |           | A_QB2     |           | A_QB1     |           | A_QB0     |           |

| 0x12               | A_QA3     |           | A_QA2     |           | A_QA1     |           | A_QA0     |           |

| 0x13               | OE_QB3    | OE_QB2    | OE_QB1    | OE_QB0    | OE_QA3    | OE_QA2    | OE_QA1    | OE_QA0    |

Table 11. Device Configuration Register Descriptions

| Register Description |            |                  |                                              |

|----------------------|------------|------------------|----------------------------------------------|

| Bit Field Name       | Field Type | Default (Binary) | Description                                  |

| STYLE_Qn             | R/W        | 0                | 0 = Output is LVPECL.<br>1 = Output is LVDS. |

Table 11. Device Configuration Register Descriptions

| Register Description                                                                                  |            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------|------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit Field Name                                                                                        | Field Type | Default (Binary) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A_Qn                                                                                                  | R/W        | 00               | Output Amplitude                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                       |            |                  | A_Qn[1:0] Amplitude if Output is LVPECL Amplitude if Output is LVDS                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                       |            |                  | 00 750mV (standard LVPECL)<br>Output termination: see <a href="#">Figure</a> 500mV amplitude (high-amplitude LVDS)<br>Output termination: 100Ω between Q, nQ; see <a href="#">Figure 7</a> , <a href="#">Figure 8</a> , <a href="#">Figure 9</a> .                                                                                                                                                                                                                                                            |

|                                                                                                       |            |                  | 01 500mV (low-amplitude LVPECL)<br>Output termination: see <a href="#">Figure</a> 350mV amplitude (standard LVDS)<br>Output termination: 100Ω between Q, nQ; see <a href="#">Figure 7</a> , <a href="#">Figure 8</a> , <a href="#">Figure 9</a> .                                                                                                                                                                                                                                                             |

|                                                                                                       |            |                  | 10 Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                       |            |                  | 11 Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>DD_O</sub> = 1.8V: output amplitudes of 350mV and 500mV are available, 750mV is not available. |            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OE_Qn                                                                                                 | R/W        | POD_OE pin state | Output Enable<br>0 = Output Qn, nQn is disabled in the high-impedance state.<br>1 = Output Qn, nQn is enabled.<br>After each power cycle, the device copies the state of the POD_OE input to all eight bits (D7-0) of this register. If pin POD_OE = 1 or open, the device powers up with all outputs enabled, if pin POD_OE=0, the device powers up with all outputs disabled in high-impedance state. After the first valid I <sup>2</sup> C write, the output enable state is controlled by this register. |

## Serial Interface

The 8T79S308 supports an I<sup>2</sup>C configuration interface.

### I<sup>2</sup>C Interface

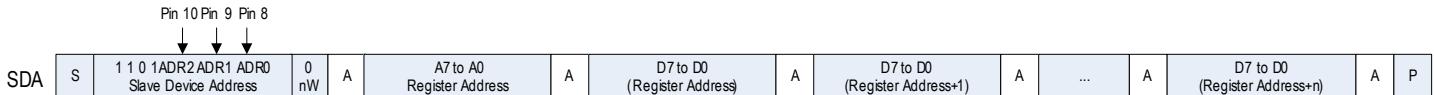

The device will respond as a slave in an I<sup>2</sup>C compatible configuration at a base address of 1101[ADR2, ADR1, ADR0]b, to allow access to any of the internal registers for device programming or examination of internal status. The ADR[2:0] bits of the I<sup>2</sup>C interface address are set by the logic state of the ADR2 (pin 10), ADR1 (pin 9) and ADR0 (pin 8) inputs. If more than one 8T79S308 device is connected to the same I<sup>2</sup>C bus, set ADR[2:0] to different states on each device to avoid address conflicts.

The I<sup>2</sup>C interface is designed to fully support v1.2 of the I<sup>2</sup>C Specification for Normal and Fast mode operation. The device acts as a slave device on the I<sup>2</sup>C bus at 100kHz or 400kHz using a fixed base address of 1101[ADR2, ADR1, ADR0]b. The interface accepts byte-oriented block write and block read operations. One address byte specifies the register address of the byte position of the first register to write or read. Data bytes (registers) are accessed in sequential order from the lowest to the highest byte (most significant bit first). Read and write block transfers can be stopped after any complete byte transfer. During a write operation, data is moved into the registers byte by byte and before a STOP bit is received.

The device implements registers in the address range 0x00 to 0x1F. Write access to the address range 0x20-0xFF has no effect, read access to this range will return 0x00.

For full electrical I<sup>2</sup>C compliance, it is recommended to use external pull-up resistors for SDA and SCL. The internal pull-up resistors have a size of 51kΩ typical.

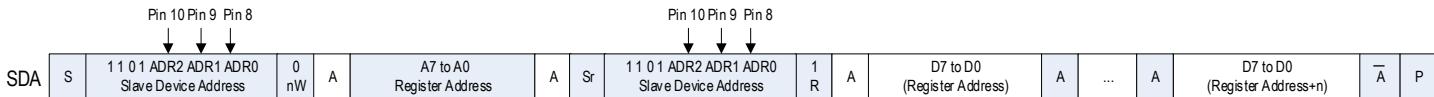

Figure 2. I<sup>2</sup>C Write Data (Master Transmit, Slave Receive) from any Register Address

Write to slave to the specified register address A [7:0]. The slave auto-increments the register address and data is written sequentially .

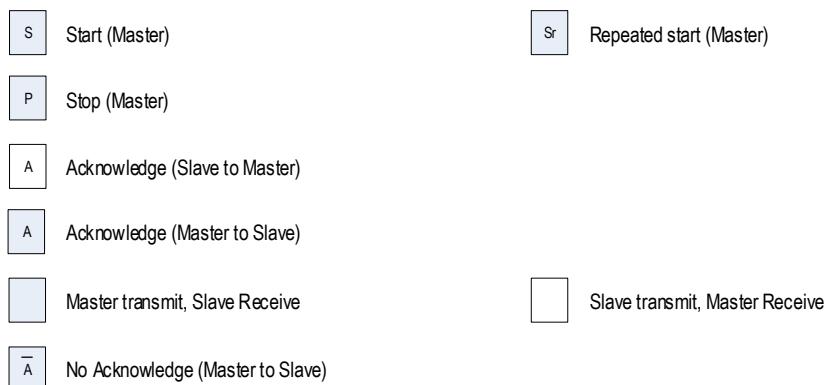

Figure 3. I<sup>2</sup>C Read Data (Slave Transmit, Master Receive) from any Register Address

Read from slave from the specified register address A[7:0]. Data is transmitted to the master after a change of the transfer direction with a repeated start. The slave auto-increments the register address and transmits register data to the master sequentially.

## Absolute Maximum Ratings

The absolute maximum ratings are stress ratings only. Stresses greater than those listed below can cause permanent damage to the device. Functional operation of the 8T79S308 at absolute maximum ratings is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

Table 12. Absolute Maximum Ratings

| Item                                                           | Rating                      |

|----------------------------------------------------------------|-----------------------------|

| Supply Voltage, $V_{DD\_V}$ , $V_{DD\_O}$                      | 3.6V                        |

| Inputs                                                         | -0.5V to $V_{DD\_V}$ + 0.5V |

| Outputs, $V_O$ (SDA)                                           | -0.5V to $V_{DD\_O}$ + 0.5V |

| Outputs, $I_O$ (LVPECL)<br>Continuous Current<br>Surge Current | 50mA<br>100mA               |

| Outputs, $I_O$ (LVDS)<br>Continuous Current<br>Surge Current   | 50mA<br>100mA               |

| Input termination current, $I_{VT}$                            | $\pm 35$ mA                 |

| Operating Junction Temperature, $T_J$                          | 125°C                       |

| Storage Temperature, $T_{STG}$                                 | -65°C to 150°C              |

| ESD - Human Body Model <sup>[a]</sup>                          | 2000V                       |

| ESD - Charged Device Model <sup>[a]</sup>                      | 500V                        |

[a] According to JEDEC JS-001-2012/JESD22-C101

## Pin Characteristics

Table 13. Pin Characteristics,  $V_{DD\_V} = (3.3V \text{ or } 2.5V) \pm 5\%$ ,  $V_{DD\_O} = (3.3V \text{ or } 2.5V \text{ or } 1.8V) \pm 5\%$ ,  $T_A = -40^\circ\text{C}$  to  $+105^\circ\text{C}$  (Case)

| Symbol                  | Parameter                   | Test Conditions                                              | Minimum | Typical  | Maximum | Units |

|-------------------------|-----------------------------|--------------------------------------------------------------|---------|----------|---------|-------|

| $C_{IN}$ <sup>[a]</sup> | Input Capacitance           | $IN\_0, nIN\_0, IN\_1, nIN\_1$ .                             |         | 2        | 4       | pF    |

|                         |                             | Other inputs.                                                |         | 2        | 4       | pF    |

| $R_{PD}$                | Input Pull-Down Resistor    |                                                              |         | 51       |         | kΩ    |

| $R_T$                   | Input Termination Impedance | $IN\_0, nIN\_0$ to $VT\_0$ .<br>$IN\_1, nIN\_1$ to $VT\_1$ . |         | 50<br>50 |         | Ω     |

[a] Guaranteed by design.

## DC Characteristics

Table 14. Power Supply DC Characteristics,  $V_{DD\_V} = (3.3V \text{ or } 2.5V) \pm 5\%$ ,  $V_{DD\_O} = (3.3V \text{ or } 2.5V \text{ or } 1.8V) \pm 5\%$ ,  $T_A = -40^\circ\text{C}$  to  $+105^\circ\text{C}$  (Case)<sup>[a][b]</sup>

| Symbol                       | Parameter                  | Test Conditions                           | Minimum                          | Typical           | Maximum                          | Units |

|------------------------------|----------------------------|-------------------------------------------|----------------------------------|-------------------|----------------------------------|-------|

| $V_{DD\_V}$                  | Core Supply Voltage        |                                           | 2.5 - 5%<br>3.3 - 5%             | 2.5<br>3.3        | 2.5 + 5%<br>3.3 + 5%             | V     |

| $V_{DD\_O}$                  | Output Supply Voltage      |                                           | 2.5 - 5%<br>3.3 - 5%<br>1.8 - 5% | 2.5<br>3.3<br>1.8 | 2.5 + 5%<br>3.3 + 5%<br>1.8 + 5% | V     |

| $I_{DD\_V +}$<br>$I_{DD\_O}$ | Total Power Supply Current | $V_{DD\_V} = V_{DD\_O} = 2.5V$ .          |                                  | 395               | 457                              | mA    |

|                              |                            | $V_{DD\_V} = V_{DD\_O} = 3.3V$ .          |                                  | 406               | 467                              |       |

|                              |                            | $V_{DD\_V} = 2.5V$ , $V_{DD\_O} = 1.8V$ . |                                  | 345               | 395                              |       |

[a] Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specifications after thermal equilibrium has been reached under these conditions.

[b]  $V_{DD\_V} \geq V_{DD\_O}$

Table 15. Typical Power Supply DC Current Characteristics,  $V_{DD\_V} = 3.3V$ ,  $V_{DD\_O} = 3.3V$ ,  $T_A = 25^\circ\text{C}$ <sup>[a][b]</sup>

| Symbol                | Supply Pin Current                            | Test Case |        |      |      | Unit |

|-----------------------|-----------------------------------------------|-----------|--------|------|------|------|

|                       |                                               | 1         | 2      | 3    | 4    |      |

| Qn                    | Style                                         | LVPECL    | LVPECL | LVDS | LVDS |      |

|                       |                                               | On        | On     | On   | On   |      |

|                       |                                               | 500       | 750    | 350  | 500  |      |

| $I_{DD\_CA}$          | Current through VDD pin                       | 4         | 4      | 4    | 4    | mA   |

| $I_{DD\_CB}$          | Current through VDDA pin                      | 135       | 160    | 108  | 112  | mA   |

| $I_{DD\_CC}$          | Current through VDDB pin                      | 135       | 160    | 108  | 112  | mA   |

| $I_{DD\_CD}$          | Current through VDD_IN_0 pin                  | 41        | 41     | 40   | 40   | mA   |

| $I_{DD\_CE}$          | Current through VDD_IN_1 pin                  | 41        | 41     | 40   | 40   | mA   |

| $P_{TOT}$             | Total Device Power Consumption                | 0.709     | 0.805  | 0.99 | 1.02 | W    |

| $P_{TOT, \text{SYS}}$ | Total System Power Consumption <sup>[c]</sup> | 1.18      | 1.34   | 0.99 | 1.02 | W    |

[a] Configuration:  $f_{CLK}$  (input) = 245.76MHz, Qn outputs terminated according to amplitude settings.

[b] Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specifications after thermal equilibrium has been reached under these conditions.

[c] Includes total device power consumption and the power dissipated in external output termination components.

Table 16. Typical Power Supply DC Current Characteristics,  $V_{DD\_V} = 2.5V$ ,  $V_{DD\_O} = 2.5V$ ,  $T_A = 25^\circ C$ <sup>[a][b]</sup>

| Symbol         | Supply Pin Current                            | Test Case |        |      |      | Unit |

|----------------|-----------------------------------------------|-----------|--------|------|------|------|

|                |                                               | 1         | 2      | 3    | 4    |      |

| Qn             | Style                                         | LVPECL    | LVPECL | LVDS | LVDS |      |

|                |                                               | On        | On     | On   | On   |      |

|                |                                               | 500       | 750    | 350  | 500  | mV   |

| $I_{DD\_CA}$   | Current through VDD pin                       | 4         | 4      | 4    | 4    | mA   |

| $I_{DD\_CB}$   | Current through VDDA pin                      | 131       | 156    | 107  | 111  | mA   |

| $I_{DD\_CC}$   | Current through VDDB pin                      | 131       | 156    | 107  | 111  | mA   |

| $I_{DD\_CD}$   | Current through VDD_IN_0 pin                  | 40        | 40     | 39   | 39   | mA   |

| $I_{DD\_CE}$   | Current through VDD_IN_1 pin                  | 40        | 40     | 39   | 39   | mA   |

| $P_{TOT}$      | Total Device Power Consumption                | 0.587     | 0.672  | 0.98 | 1.00 | W    |

| $P_{TOT, SYS}$ | Total System Power Consumption <sup>[c]</sup> | 1.15      | 1.31   | 0.98 | 1.00 | W    |

[a] Configuration:  $f_{CLK}$  (input) = 245.76MHz, Qn outputs terminated according to amplitude settings.

[b] Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500lfp. The device will meet specifications after thermal equilibrium has been reached under these conditions.

[c] Includes total device power consumption and the power dissipated in external output termination components.

Table 17. LVCMOS Input DC Characteristics,  $V_{DD\_V} = (3.3V \text{ or } 2.5V) \pm 5\%$ ,  $V_{DD\_O} = (3.3V \text{ or } 2.5V \text{ or } 1.8V) \pm 5\%$ ,  $T_A = -40^\circ C$  to  $+105^\circ C$  (Case)<sup>[a][b]</sup>

| Symbol   | Parameter          |                               | Test Conditions                                               | Minimum | Typical | Maximum     | Units   |

|----------|--------------------|-------------------------------|---------------------------------------------------------------|---------|---------|-------------|---------|

| $V_{IH}$ | Input High Voltage |                               | $V_{DD\_V} = 2.5V$ .                                          | 1.7     |         | $V_{DD\_V}$ | V       |

|          |                    |                               | $V_{DD\_V} = 3.3V$ .                                          | 2       |         | $V_{DD\_V}$ | V       |

| $V_{IL}$ | Input Low Voltage  |                               |                                                               | -0.3    |         | 0.5         | V       |

| $I_{IH}$ | Input High Current | Input with pull-down resistor | $V_{DD\_V} = 2.5V \text{ or } 3.3V$ .<br>$V_{IN} = V_{DD\_V}$ |         |         | 150         | $\mu A$ |

| $I_{IL}$ | Input Low Current  |                               | $V_{DD\_V} = 2.5V \text{ or } 3.3V$ .<br>$V_{IN} = 0V$ .      | -5      |         |             | $\mu A$ |

[a] Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfp. The device will meet specifications after thermal equilibrium has been reached under these conditions.

[b] LVCMOS inputs: ADR[2:0], XSEL[1:0], VSEL\_VDD, VSEL\_I2C, and POD\_OE.

Table 18. I<sup>2</sup>C Input/Output DC Characteristics,  $V_{DD\_V} = (3.3V \text{ or } 2.5V) \pm 5\%$ ,  $V_{DD\_O} = (3.3V \text{ or } 2.5V \text{ or } 1.8V) \pm 5\%$ ,  $T_A = -40^\circ\text{C}$  to  $+105^\circ\text{C}$  (Case)<sup>[a][b]</sup>

| Symbol   | Parameter                              | Test Conditions                                                                           | Minimum                                                                                   | Typical                      | Maximum                     | Units         |   |

|----------|----------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------|-----------------------------|---------------|---|

| $V_I$    | Input Voltage                          |                                                                                           | -0.3                                                                                      |                              | 3.3V                        | V             |   |

| $V_{T+}$ | Positive-going input threshold voltage | VSEL_I2C = 0.<br>VSEL_I2C = 1, $V_{DD\_V} = 2.5V$ .<br>VSEL_I2C = 1, $V_{DD\_V} = 3.3V$ . | 0.660                                                                                     | 1.10–1.40<br>1.45–1.75       | 1.365                       | V             |   |

| $V_{T-}$ | Negative-going input threshold voltage | VSEL_I2C = 0.<br>VSEL_I2C = 1, $V_{DD\_V} = 2.5V$ .<br>VSEL_I2C = 1, $V_{DD\_V} = 3.3V$ . | 0.495                                                                                     | 0.91<br>0.65–0.95<br>0.8–1.1 | 1.170                       | V             |   |

| $V_H$    | Hysteresis Voltage                     | $V_{T+} - V_{T-}$                                                                         | VSEL_I2C = 0.<br>VSEL_I2C = 1, $V_{DD\_V} = 2.5V$ .<br>VSEL_I2C = 1, $V_{DD\_V} = 3.3V$ . | 0.165                        | 0.6<br>0.15–0.45<br>0.5–0.8 | 0.780         | V |

| $I_{IH}$ | Input High Current                     |                                                                                           | $V_{DD\_V} = 2.5V \text{ or } 3.3V$ .<br>$V_{IN} = V_{DD\_V}$                             |                              | 150                         | $\mu\text{A}$ |   |

| $I_{IL}$ | Input Low Current                      |                                                                                           | $V_{DD\_V} = 2.5V \text{ or } 3.3V$ .<br>$V_{IN} = 0V$ .                                  | -5                           |                             | $\mu\text{A}$ |   |

| $V_{OL}$ | Output Low Voltage                     |                                                                                           | VSEL_I2C = 0, $I_{OL} = 4mA$ .<br>VSEL_I2C = 1, $I_{OL} = 4mA$ .                          |                              | 0.292<br>0.292              | 0.55          | V |

[a] Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specifications after thermal equilibrium has been reached under these conditions.

[b] Valid for inputs/outputs: SCL and SDA. Inputs have hysteresis and tolerate any voltage up to 3.3V.

Table 19. Differential Input DC Characteristics,  $V_{DD\_V} = (3.3V \text{ or } 2.5V) \pm 5\%$ ,  $V_{DD\_O} = (3.3V \text{ or } 2.5V \text{ or } 1.8V) \pm 5\%$ ,  $T_A = -40^\circ\text{C} \text{ to } +105^\circ\text{C}$  (Case)<sup>[a]</sup>

| Symbol         | Parameter                                |            | Test Conditions                              | Minimum | Typical | Maximum                  | Units    |  |

|----------------|------------------------------------------|------------|----------------------------------------------|---------|---------|--------------------------|----------|--|

| $V_{IN}$       | Input Voltage Swing                      | IN_0, IN_1 |                                              | 0.15    |         | 1.2                      | V        |  |

| $V_{DIFF\_IN}$ | Differential Input Voltage Swing         |            |                                              | 0.3     |         | 2.4                      | V        |  |

| $V_{CMR}$      | Common Mode Input Voltage                |            |                                              | 1       |         | $V_{DD\_V} - (V_{IN}/2)$ | V        |  |

| $R_T$          | Input Termination Impedance              |            | IN_0, nIN_0 to VT_0,<br>IN_1, nIN_1 to VT_1. | 40      | 50      | 60                       | $\Omega$ |  |

| $R_{T\_DIFF}$  | Differential Input Termination Impedance |            | IN_0 to nIN_0.<br>IN_0 to nIN_1.             | 80      | 100     | 120                      | $\Omega$ |  |

[a] Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfm. The device will meet specifications after thermal equilibrium has been reached under these conditions.

Table 20. LVPECL DC Characteristics (QAn, QBn),  $V_{DD\_V} = (3.3V \text{ or } 2.5V) \pm 5\%$ ,  $V_{DD\_O} = (3.3V \text{ or } 2.5V \text{ or } 1.8V) \pm 5\%$ ,  $T_A = -40^\circ\text{C} \text{ to } +105^\circ\text{C}$  (Case)

| Symbol   | Parameter           |  | Test Conditions                           | Minimum                                  | Typical                                  | Maximum                                  | Units |

|----------|---------------------|--|-------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|-------|

| $V_{OH}$ | Output High Voltage |  | Amplitude = 750mV.<br>Amplitude = 500 mV. | $V_{DD\_O} - 1.04$<br>$V_{DD\_O} - 0.99$ | $V_{DD\_O} - 0.9$<br>$V_{DD\_O} - 0.89$  | $V_{DD\_O} - 0.83$<br>$V_{DD\_O} - 0.82$ | V     |

| $V_{OL}$ | Output Low Voltage  |  | Amplitude = 750mV.<br>Amplitude = 500 mV. | $V_{DD\_O} - 1.73$<br>$V_{DD\_O} - 1.48$ | $V_{DD\_O} - 1.62$<br>$V_{DD\_O} - 1.38$ | $V_{DD\_O} - 1.56$<br>$V_{DD\_O} - 1.33$ | V     |

Table 21. LVDS DC Characteristics (QAn, QBn),  $V_{DD\_V} = (3.3V \text{ or } 2.5V) \pm 5\%$ ,  $V_{DD\_O} = (3.3V \text{ or } 2.5V \text{ or } 1.8V) \pm 5\%$ ,  $T_A = -40^\circ\text{C} \text{ to } +105^\circ\text{C}$  (Case)<sup>[a]</sup>

| Symbol          | Parameter                     |                    | Test Conditions                      | Minimum      | Typical      | Maximum      | Units |

|-----------------|-------------------------------|--------------------|--------------------------------------|--------------|--------------|--------------|-------|

| $V_{OS}$        | Offset Voltage <sup>[b]</sup> | $V_{DD\_O} = 3.3V$ | 500mV Amplitude.<br>350mV Amplitude. | 1.8<br>1.9   | 2.3<br>2.3   | 2.8<br>2.9   | V     |

| $V_{OS}$        | Offset Voltage <sup>[c]</sup> | $V_{DD\_O} = 2.5V$ | 500mV Amplitude.<br>350mV Amplitude. | 1.05<br>1.10 | 1.42<br>1.42 | 1.75<br>1.80 | V     |

| $V_{OS}$        | Offset Voltage <sup>[d]</sup> | $V_{DD\_O} = 1.8V$ | 500mV Amplitude.<br>350mV Amplitude. | 0.40<br>0.45 | 0.70<br>0.78 | 1.0<br>1.1   | V     |

| $\Delta V_{OS}$ | $V_{OS}$ Magnitude Change     |                    |                                      |              | 10           | 50           | mV    |

[a] Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfm. The device will meet specifications after thermal equilibrium has been reached under these conditions.

[b]  $V_{OS}$  changes with  $V_{DD\_O}$ .

[c]  $V_{OS}$  changes with  $V_{DD\_O}$ .

[d]  $V_{OS}$  changes with  $V_{DD\_O}$ .

## AC Characteristics

Table 22. AC Characteristics,  $V_{DD\_V} = (3.3V \text{ or } 2.5V) \pm 5\%$ ,  $V_{DD\_O} = (3.3V \text{ or } 2.5V \text{ or } 1.8V) \pm 5\%$ ,  $T_A = -40^\circ\text{C}$  to  $+105^\circ\text{C}$  (Case)<sup>[a]</sup>

| Symbol         | Parameter                                                          |                         | Test Conditions                                                                            | Minimum | Typical | Maximum                  | Units         |

|----------------|--------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------|---------|---------|--------------------------|---------------|

| $f_{IN}$       | Signal Input and Output Frequency                                  |                         |                                                                                            | 0       |         | 3000                     | MHz           |

| $f_{SCL}$      | $I^2C$ Clock Frequency                                             |                         |                                                                                            |         |         | 400                      | kHz           |

| $V_{IN}$       | Input Voltage Amplitude <sup>[b]</sup>                             | IN_n                    |                                                                                            | 0.15    |         | 1.2                      | V             |

| $V_{DIFF\_IN}$ | Differential Input Voltage Amplitude <sup>[b][c]</sup>             | IN_n                    |                                                                                            | 0.3     |         | 2.4                      | V             |

| $V_{CMR}$      | Common Mode Input Voltage                                          |                         |                                                                                            | 1.0     |         | $V_{DD\_V} - (V_{IN/2})$ | V             |

| odc            | Output Duty Cycle                                                  |                         | QAn, QBn (Clock)                                                                           | 45      | 50      | 55                       | %             |

|                |                                                                    |                         | QAn, QBn (Clock) > 2.5GHz                                                                  | 40      | 50      | 60                       |               |

| $t_R / t_F$    | Output Rise/Fall Time, Differential                                |                         | QAn, QBn (Clock), 20% to 80%.                                                              |         | 100     | 200                      | ps            |

|                |                                                                    |                         | QAn, QBn, 20% to 80%.                                                                      |         | 100     | 200                      | ps            |

| $V_{O(PP)}$    | LVPECL Output Voltage Swing, Peak-to-peak                          | 750mV                   | 1GHz.                                                                                      | 630     | 730     | 830                      | mV            |

|                |                                                                    | 750mV                   | 2GHz.                                                                                      | 640     | 744     | 850                      | mV            |

|                | LVPECL Differential Output Voltage Swing, Peak-to-peak             | 750mV                   | 1GHz.                                                                                      | 1260    | 1460    | 1660                     | mV            |

|                |                                                                    | 750mV                   | 2GHz.                                                                                      | 1280    | 1488    | 1700                     | mV            |

| $V_{OD}$       | LVDS Output Voltage Swing, Peak-to-peak                            | 350mV                   | 1GHz.                                                                                      | 280     | 360     | 420                      | mV            |

|                |                                                                    | 350mV                   | 2GHz.                                                                                      | 230     | 360     | 470                      | mV            |

| $V_{OD}$       | LVDS Differential Output Voltage Swing, Peak-to-peak               | 350mV                   | 1GHz.                                                                                      | 560     | 720     | 840                      | mV            |

|                |                                                                    | 350mV                   | 2GHz.                                                                                      | 460     | 720     | 940                      | mV            |

| $t_{PD}$       | Propagation delay between any signal input and any QAn, QBn output |                         |                                                                                            |         |         | 750                      | ps            |

| $t_{PDZ}$      | Output enable and disable time                                     |                         | From active state to disable <sup>[d]</sup><br>From disable to active state <sup>[e]</sup> |         | 1<br>30 | 3<br>50                  | $\mu\text{s}$ |

| $t_{sk(o)}$    | Output Skew <sup>[f][g]</sup>                                      | Within one output bank. |                                                                                            |         | 10      | 25                       | ps            |

|                |                                                                    | Any output.             |                                                                                            |         | 16      | 35                       | ps            |

| $t_{sk(pp)}$   | Part-to-part Skew <sup>[f][g]</sup>                                |                         |                                                                                            |         |         | 200                      | ps            |

| $t_{sk(p)}$    | Output Pulse Skew <sup>[g]</sup>                                   |                         | Any output.                                                                                |         | 21      | 50                       | ps            |

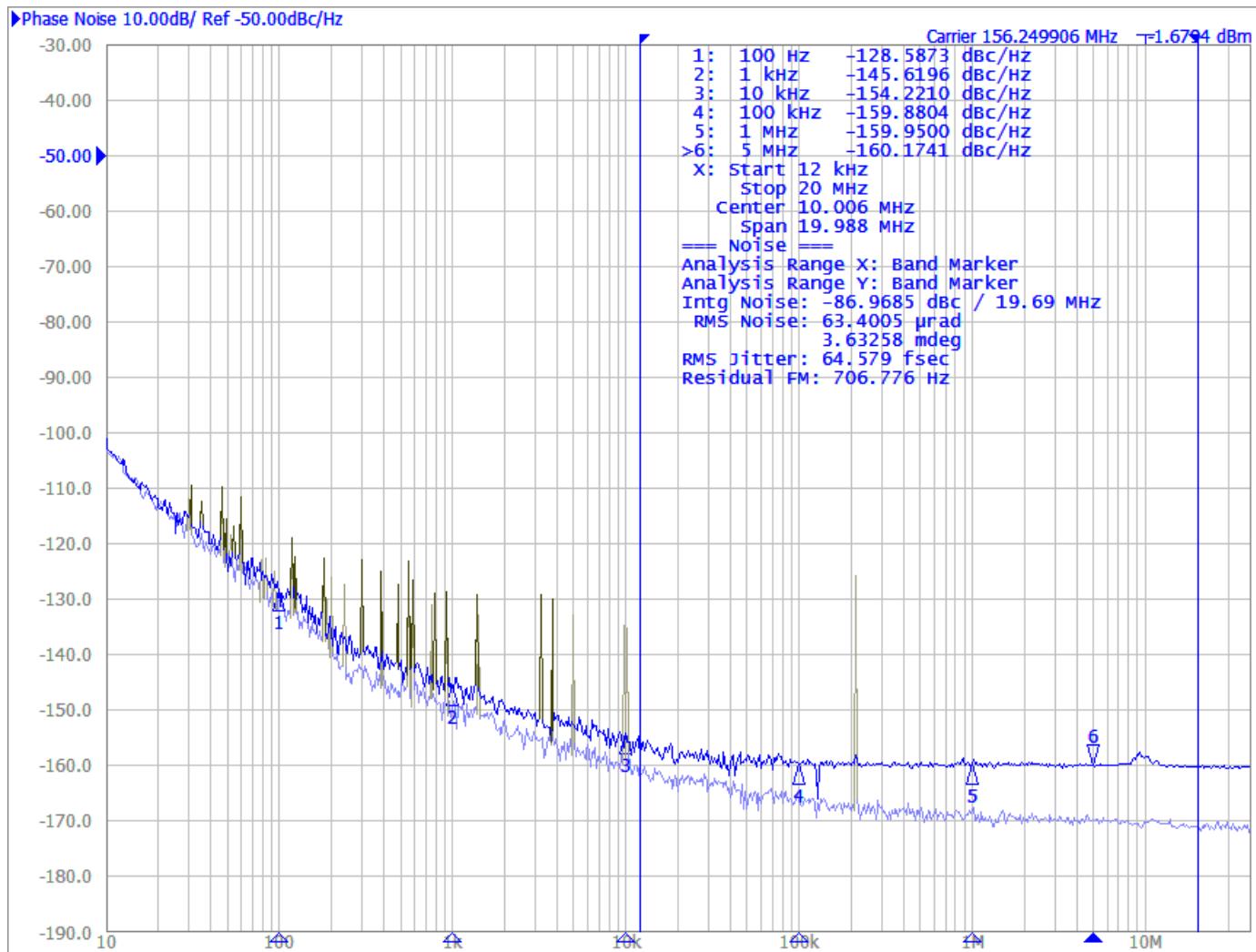

| $L(\infty)$    | Output Noise Floor                                                 |                         | QAn, QBn, 156.25MHz. LVDS Outputs                                                          |         | -160    | -155                     | dBc           |

|                |                                                                    |                         | QAn, QBn, 156.25MHz. LVPECL Outputs                                                        |         | -160    | -157                     |               |

Table 22. AC Characteristics,  $V_{DD\_V} = (3.3V \text{ or } 2.5V) \pm 5\%$ ,  $V_{DD\_O} = (3.3V \text{ or } 2.5V \text{ or } 1.8V) \pm 5\%$ ,  $T_A = -40^\circ\text{C}$  to  $+105^\circ\text{C}$  (Case)<sup>[a]</sup> (Cont.)

| Symbol     | Parameter                                             | Test Conditions                      | Minimum | Typical | Maximum | Units |

|------------|-------------------------------------------------------|--------------------------------------|---------|---------|---------|-------|

| L          | Additive Phase Noise, RMS                             | QAn, QBn, 156.25MHz (12kHz–20MHz).   |         | 60      | 100     | fs    |

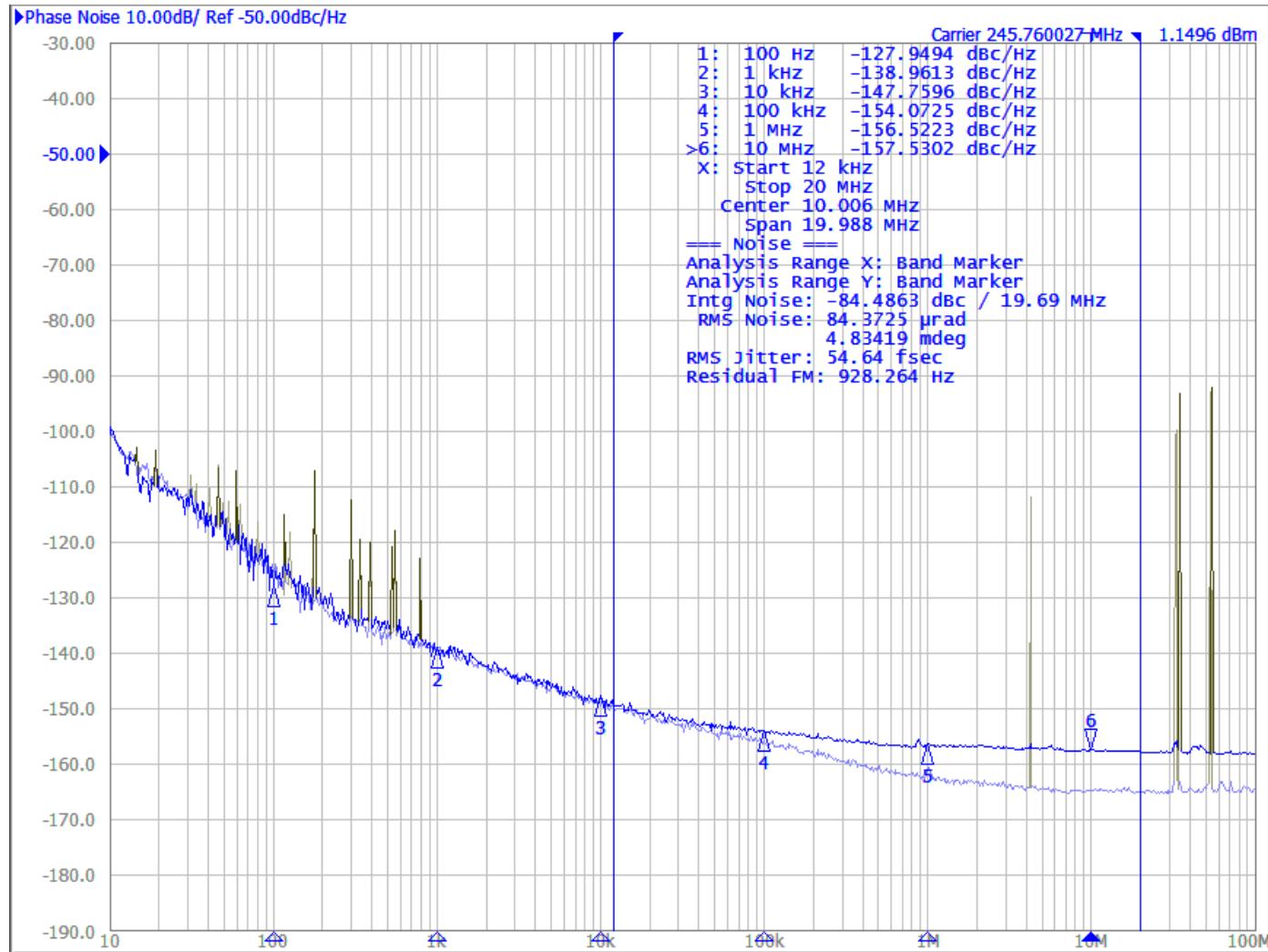

|            |                                                       | QAn, QBn, 245.76MHz (12kHz–20MHz).   |         | 50      | 80      | fs    |

|            |                                                       | QAn, QBn, 245.76MHz (1kHz–61.44MHz). |         | 95      | 110     | fs    |

| $\Delta F$ | Output isolation between any neighboring clock output | $f_{OUT} = 125\text{MHz}$ .          |         | 80      | 75      | dB    |

|            |                                                       | $f_{OUT} = 245.76\text{MHz}$ .       |         | 75      | 70      | dB    |

| $\Delta F$ | Input isolation between any signal input              | $f_{IN} = 125\text{MHz}$ .           |         | 80      | 75      | dB    |

|            |                                                       | $f_{IN} = 245.76\text{MHz}$ .        |         | 75      | 70      | dB    |

| CMNR       | Common mode noise rejection <sup>[h]</sup>            | $f_{IN} = 156.25\text{MHz}$ .        |         | -90     |         | dBc   |

[a] Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specifications after thermal equilibrium has been reached under these conditions.

[b]  $V_{IL}$  should not be less than -0.3V and  $V_{IH}$  should not be greater than  $V_{DD\_V}$ .

[c] Common Mode Input Voltage is defined as the cross-point voltage.

[d] Measured from I<sup>2</sup>C slave acknowledge bit to output in high-impedance state. Verified by simulation.

[e] Measured from I<sup>2</sup>C slave acknowledge bit to output in active low/high state. Verified by simulation.

[f] This parameter is defined in accordance with JEDEC standard 65.

[g] Defined as skew between outputs at the same supply voltage and with equal load conditions. Measured at the differential cross points.

[h] Measured at a differential output using a balun. DC/DC voltage supply as aggressor, ~490kHz switching frequency. Device power supply bypass as shown in example schematics.

Table 23. Typical Qn Output Amplitude,  $T_A = 25^\circ\text{C}$ <sup>[a]</sup>

| Symbol            | Parameter                                 | Test Conditions                         |                  | Qn Output Frequency in MHz |        |        |         |         | Units |

|-------------------|-------------------------------------------|-----------------------------------------|------------------|----------------------------|--------|--------|---------|---------|-------|

|                   |                                           | Supply voltage                          | Output Amplitude | 245.76                     | 491.52 | 983.04 | 1966.08 | 2949.12 |       |

| $V_{O(PP)}^{[b]}$ | LVPECL Output Voltage Swing, Peak-to-peak | $V_{DD\_V} = V_{DD\_O} = 3.3V$          | 500mV            | 540                        | 490    | 499    | 499     | 351     | mV    |

|                   |                                           |                                         | 750mV            | 783                        | 710    | 722    | 720     | 506     | mV    |

|                   |                                           | $V_{DD\_V} = V_{DD\_O} = 2.5V$          | 500mV            | 538                        | 494    | 499    | 518     | 376     | mV    |

|                   |                                           |                                         | 750mV            | 773                        | 705    | 717    | 732     | 530     | mV    |

|                   |                                           | $V_{DD\_V} = 2.5$<br>$V_{DD\_O} = 1.8V$ | 500mV            | 523                        | 481    | 489    | 505     | 373     | mV    |

|                   |                                           |                                         |                  |                            |        |        |         |         |       |

[a] Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specifications after thermal equilibrium has been reached under these conditions.

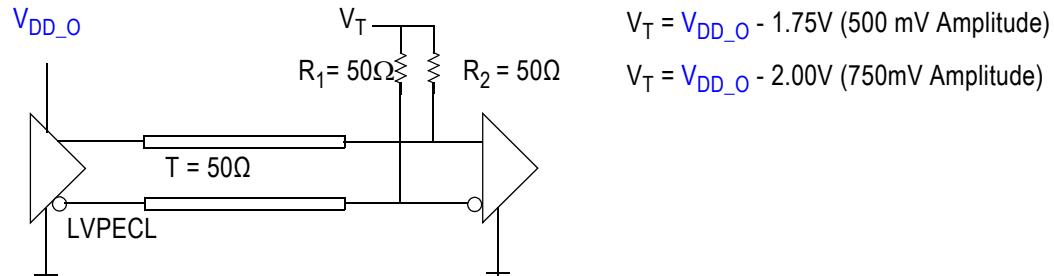

[b] LVPECL outputs terminated with 50Ω to  $V_{DD\_V} - 1.75V$  (500mV amplitude setting),  $V_{DD\_V} - 2.0V$  (750mV amplitude setting).

## Phase Noise Plots

Figure 4. Typical Phase Noise at 156.25MHz

\* Thick line: 8T79S308 output

Thin line: Wenzel oscillator drives 8T79S308 input

Figure 5. Typical Phase Noise at 245.76MHz

## Application Information

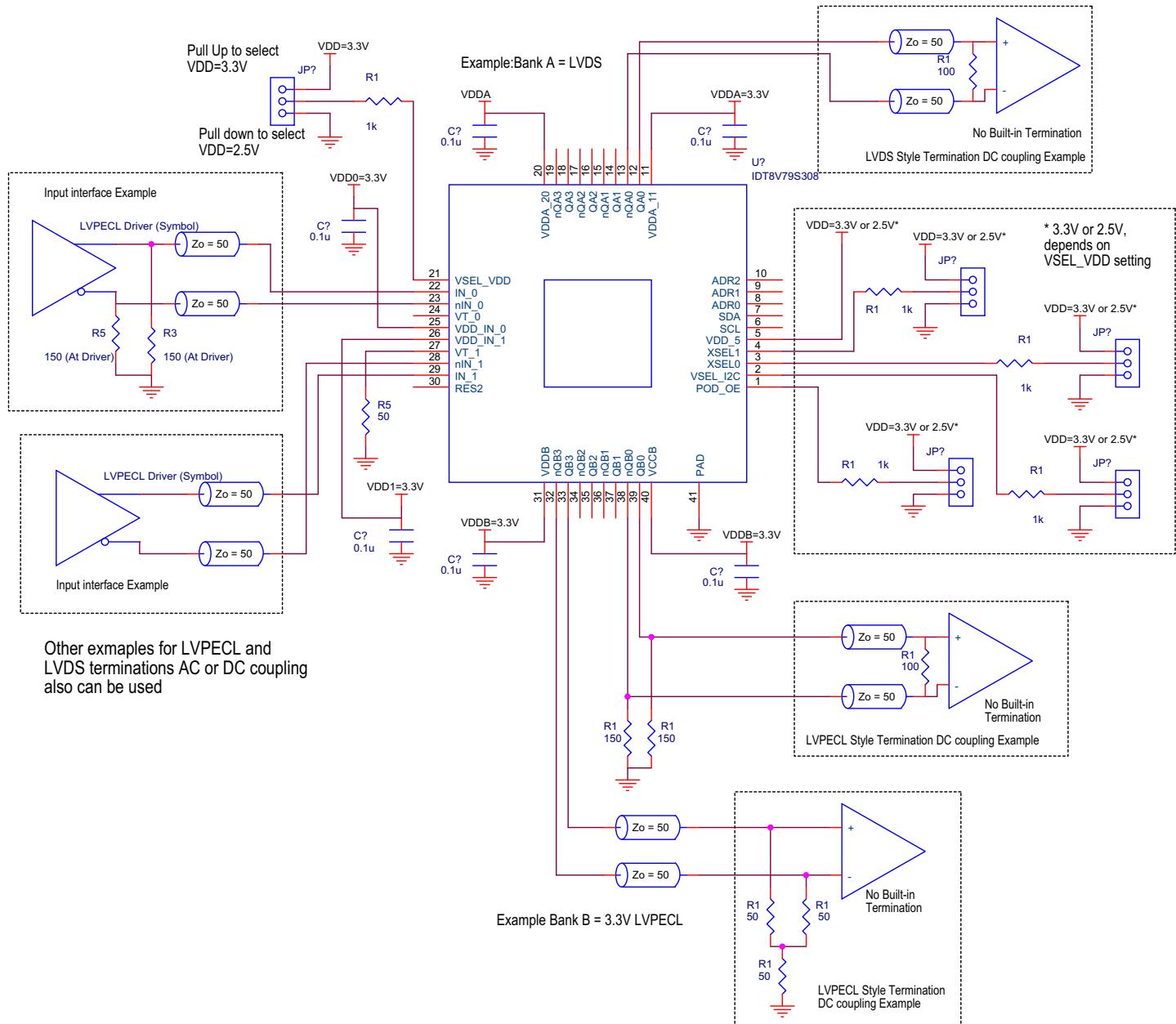

The figure below shows an example schematics. Due to the excellent common-mode noise rejection characteristics, this device uses standard power supply bypass techniques and does not require dedicated, active power supply circuitry for noise rejection purpose.

Figure 6. Application Information

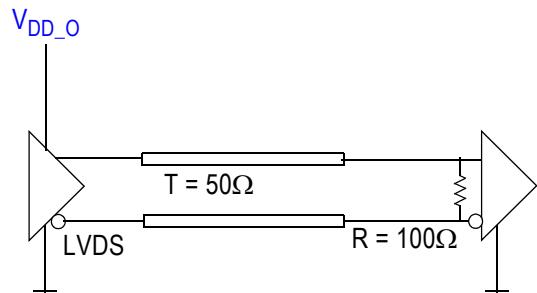

## Termination for Q, nQ LVDS Outputs

Figure 7 shows an example termination for the Q, nQ LVDS outputs. In this example, the characteristic transmission line impedance is  $50\Omega$ . The termination resistor  $R$  ( $100\Omega$ ) is matched to the line impedance. The termination resistor must be placed at the line end. No external termination resistor is required if  $R$  is an internal part of the receiver circuit. The LVDS termination in Figure 7 is applicable for any output amplitude setting specified in Table 9.

Figure 7. LVDS Output Termination

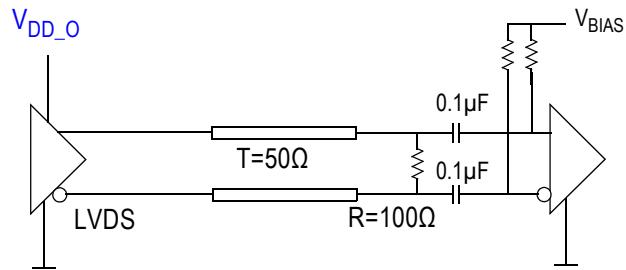

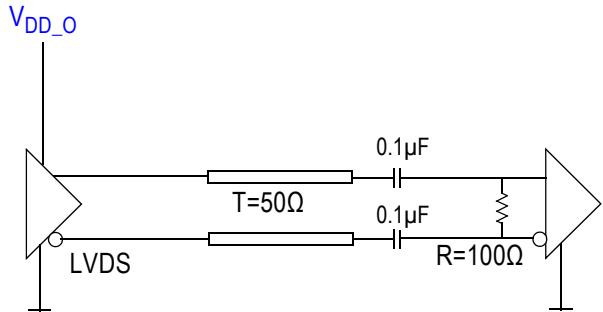

## AC Termination for Q, nQ Outputs

Figure 8 and Figure 9 show example AC terminations for the Q, nQ LVDS outputs. In the examples, the characteristic transmission line impedance is  $50\Omega$ . In Figure 8, the termination resistor  $R$  ( $100\Omega$ ) is placed at the line end. No external termination resistor is required if  $R$  is an internal part of the receiver circuit, which is shown in Figure 9. The LVDS terminations in both Figure 8 and Figure 9 are applicable for any output amplitude setting specified in Table 9. The receiver input should be re-biased according to its common mode range specifications.

Figure 8. LVDS (STYLE = 0) AC Output Termination

Figure 9. LVDS (STYLE = 0) AC Coupling

## Termination for Q, nQ LVPECL Outputs

Figure shows an example termination for the Q, nQ LVPECL outputs. In this example, the characteristic transmission line impedance is  $50\Omega$ . The  $R_1$  ( $50\Omega$ ) and  $R_2$  ( $50\Omega$ ) resistors are matched load terminations. The output is terminated to the termination voltage  $V_T$ .  $V_T$  must be set according to the output amplitude setting defined in Table 9. The termination resistors must be placed close at the line end.

Figure 10. Output Termination

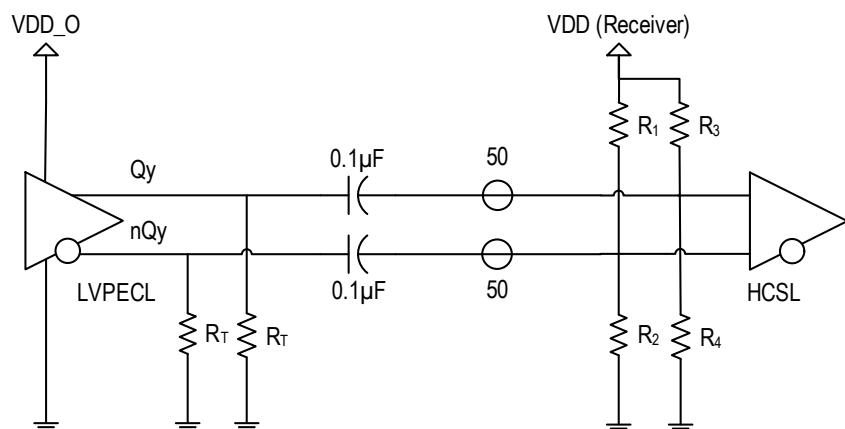

## Termination for Q, nQ LVPECL Outputs AC-Coupled into HCSL-Receiver

Figure 11. LVPECL Output AC-Coupled into HCSL Receiver

Table 24. Termination Resistors

|       | $V_{DD\_O} = 2.5V$ | $V_{DD\_O} = 3.3V$ |

|-------|--------------------|--------------------|

| $R_T$ | $100\Omega$        | $180\Omega$        |

Table 25. HCSL Receiver Voltage Bias

|            | $V_{DD} = 2.5V$ | $V_{DD} = 3.3V$ |

|------------|-----------------|-----------------|

| $R_1, R_3$ | $357\Omega$     | $470\Omega$     |

| $R_2, R_4$ | $58\Omega$      | $56\Omega$      |

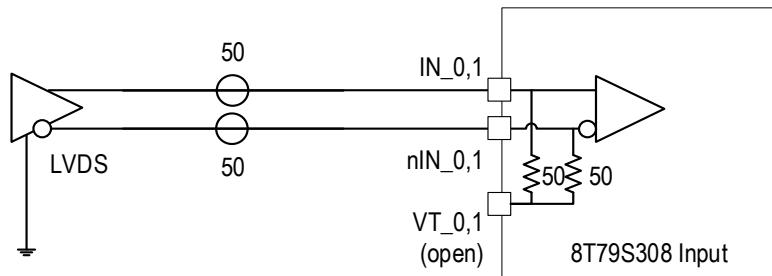

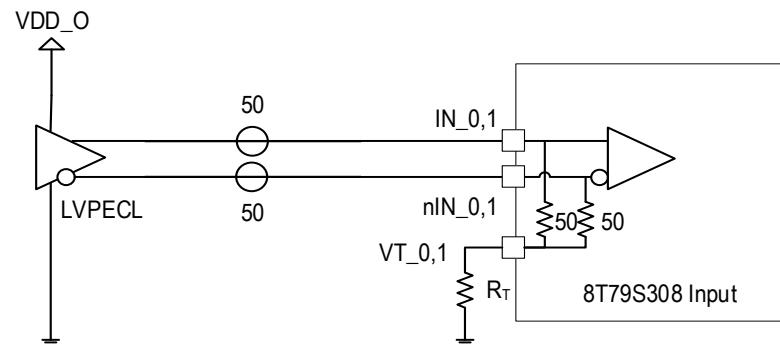

## Input Interface Circuits

Figure 12. LVDS Output Drives 8T79S308 Input (DC-Coupled)

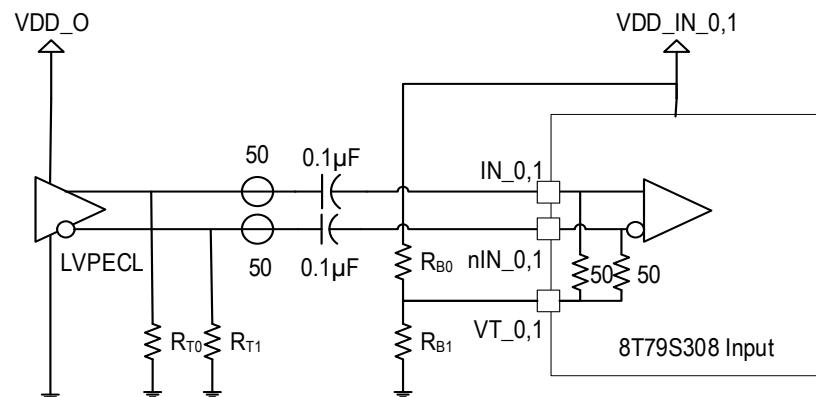

Figure 13. LVPECL Output Drives 8T79S308 Input (DC-Coupled)

|       | $V_{DD_O} = 2.5V$ | $V_{DD_O} = 3.3V$ |

|-------|-------------------|-------------------|

| $R_T$ | 18Ω               | 50Ω               |

Figure 14. LVPECL Output Drives 8T79S308 Input (AC-Coupled)

|            | $V_{DD_O} = 2.5V$ | $V_{DD_O} = 3.3V$ |

|------------|-------------------|-------------------|

| $R_{T0,1}$ | 56Ω               | 120–240Ω          |

|          | $V_{DD_{IN0,1}} = 2.5V$ | $V_{DD_{IN0,1}} = 3.3V$ |

|----------|-------------------------|-------------------------|

| $R_{B0}$ | 5.1kΩ                   | 5.1kΩ                   |

| $R_{B1}$ | 10kΩ                    | 10kΩ                    |

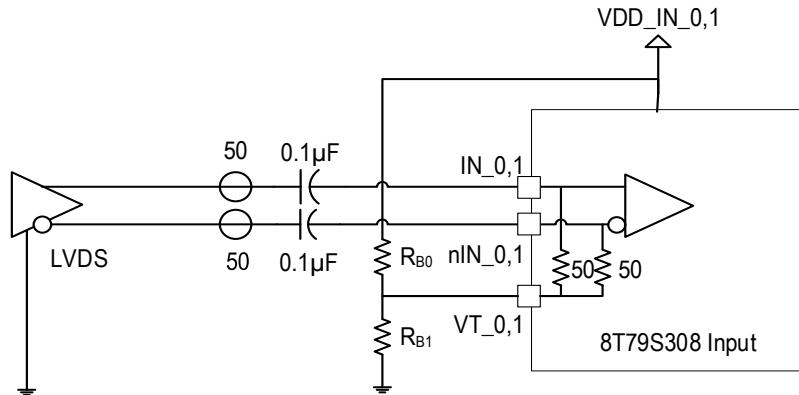

Figure 15. LVDS Output Drives 8T79S308 Input (AC-Coupled)

|          | $V_{DD\_IN0,1} = 2.5V$ | $V_{DD\_IN0,1} = 3.3V$ |

|----------|------------------------|------------------------|

| $R_{B0}$ | 5.1kΩ                  | 5.1kΩ                  |

| $R_{B1}$ | 10kΩ                   | 10kΩ                   |

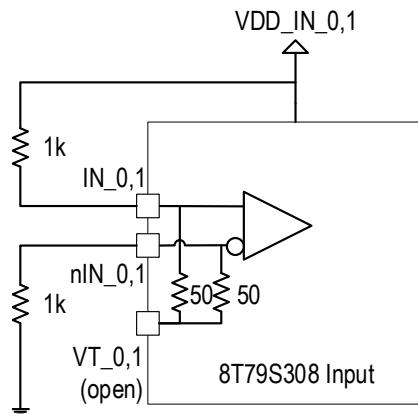

Figure 16. Unused Input

## Thermal Characteristics

Table 26. Thermal Characteristics<sup>[a]</sup>

| Multi-Layer PCB, JEDEC Standard Test Board |                                  |                |       |      |

|--------------------------------------------|----------------------------------|----------------|-------|------|

| Symbol                                     | Thermal Parameter                | Condition      | Value | Unit |

| $\Theta_{JA}$                              | Junction to ambient              | 0 m/s air flow | 24.6  | °C/W |

|                                            |                                  | 1 m/s air flow | 21.2  |      |

|                                            |                                  | 2 m/s air flow | 19.6  |      |

|                                            |                                  | 3 m/s air flow | 18.8  |      |

|                                            |                                  | 4 m/s air flow | 18.2  |      |

|                                            |                                  | 5 m/s air flow | 17.6  |      |

| $\Theta_{JC}$                              | Junction to case                 | —              | 21.6  |      |