### Features:

- True Dual-Port memory cells which allow simultaneous access of the same memory location

- High-speed data access

- Commercial: 3.6ns (166MHz)/4.2ns (133MHz)(max.)

- Industrial: 4.2ns (133MHz) (max.)

- Selectable Pipelined or Flow-Through output mode

- Counter enable and repeat features

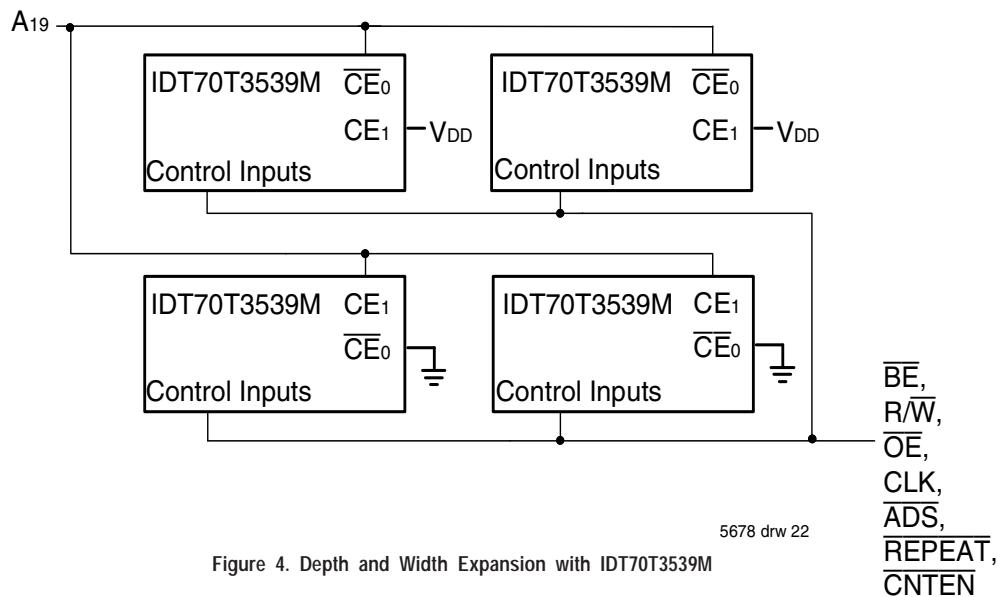

- Dual chip enables allow for depth expansion without additional logic

- Interrupt and Collision Detection Flags

- Full synchronous operation on both ports

- 6ns cycle time, 166MHz operation (12Gbps bandwidth)

- Fast 3.6ns clock to data out

- 1.5ns setup to clock and 0.5ns hold on all control, data, and address inputs @ 166MHz

- Data input, address, byte enable and control registers

- Self-timed write allows fast cycle time

- Separate byte controls for multiplexed bus and bus matching compatibility

- Dual Cycle Deselect (DCD) for Pipelined Output Mode

- 2.5V ( $\pm 100$ mV) power supply for core

- LVTTL compatible, selectable 3.3V ( $\pm 150$ mV) or 2.5V ( $\pm 100$ mV) power supply for I/Os and control signals on each port

- Includes JTAG functionality

- Industrial temperature range (-40°C to +85°C) is available at 133MHz

- Available in a 256-pin Ball Grid Array (BGA)

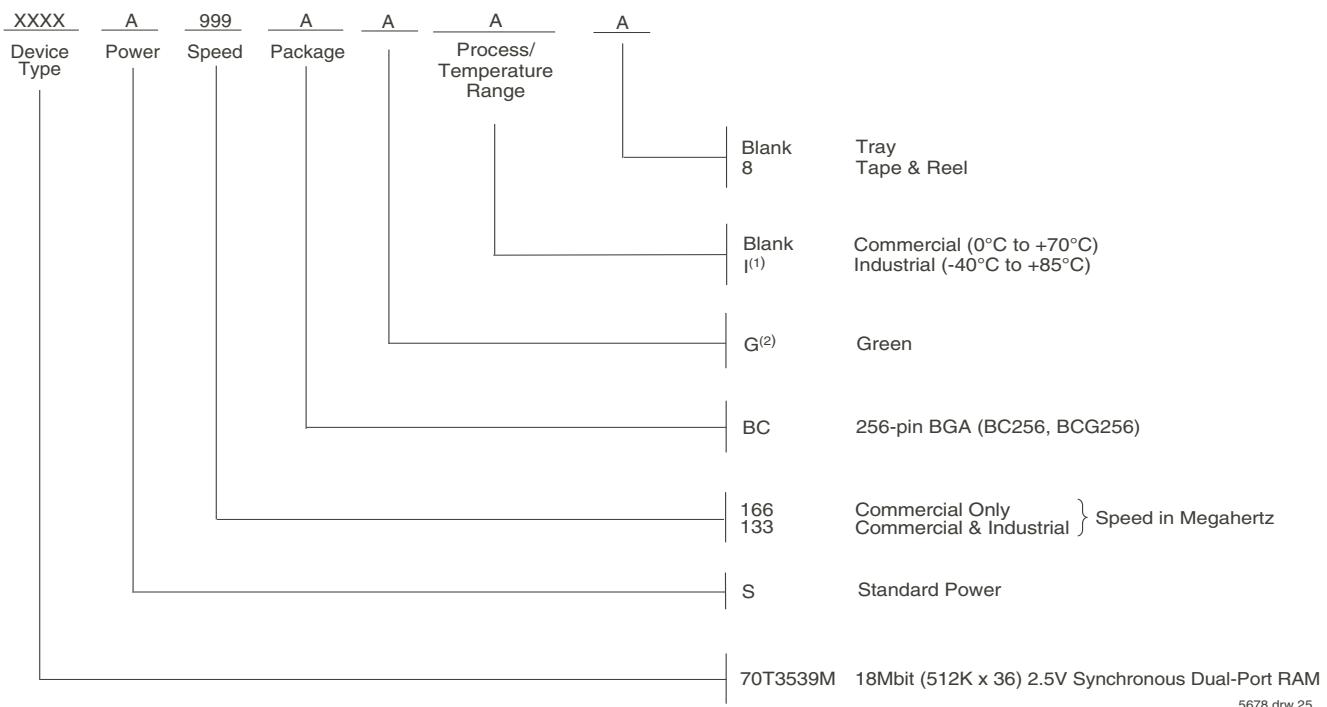

- Green parts available, see ordering information

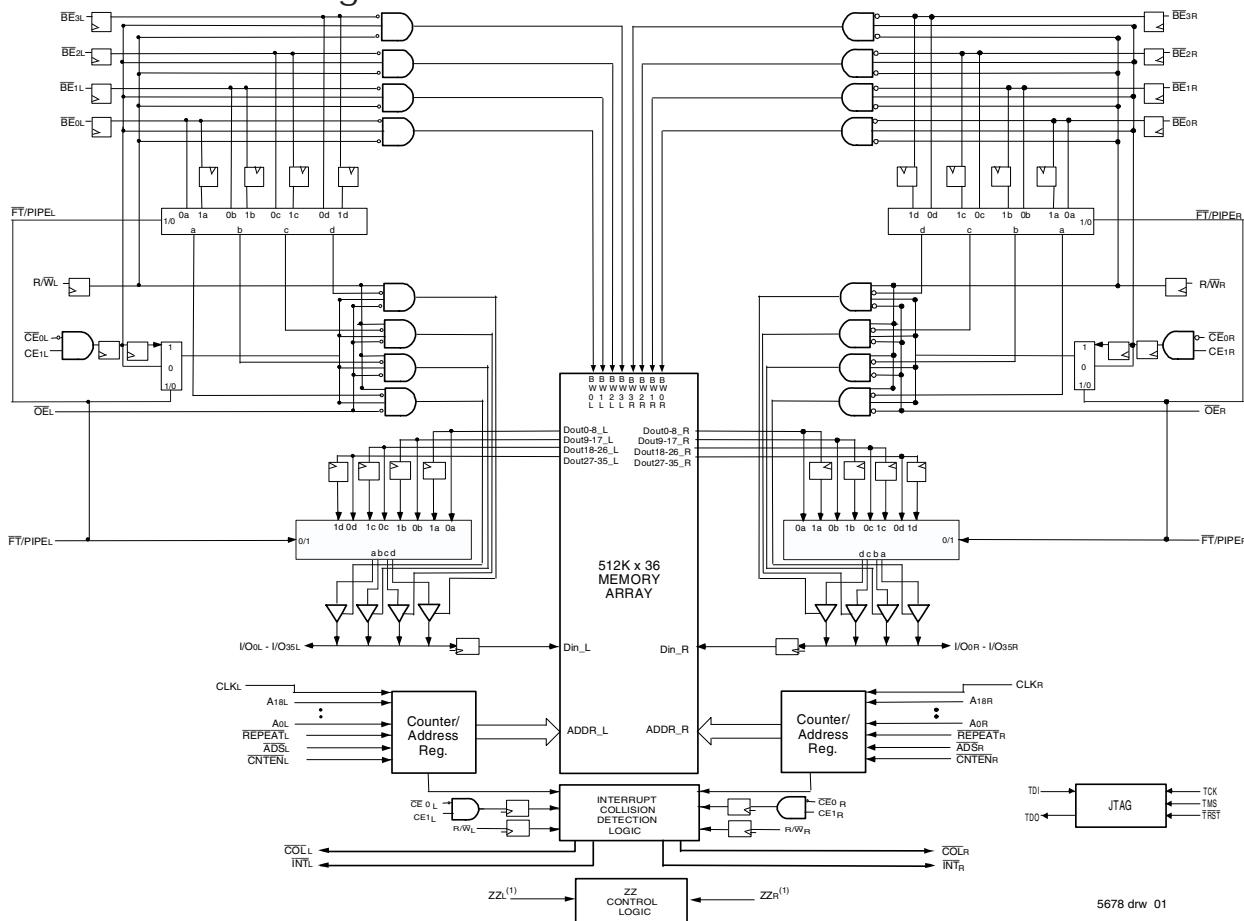

### Functional Block Diagram

#### NOTE:

- The sleep mode pin shuts off all dynamic inputs, except JTAG inputs, when asserted. All static inputs, i.e., PL/FTx and OPTx and the sleep mode pins themselves (ZZx) are not affected during sleep mode.

JUNE 2019

## Description:

The IDT70T3539M is a high-speed 512K x 36 bit synchronous Dual-Port RAM. The memory array utilizes Dual-Port memory cells to allow simultaneous access of any address from both ports. Registers on control, data, and address inputs provide minimal setup and hold times. The timing latitude provided by this approach allows systems to be designed with very short cycle times. With an input data register, the IDT70T3539M has been optimized for applications having unidirectional or bidirectional data flow

in bursts. An automatic power down feature, controlled by  $\overline{CE}_0$  and  $CE_1$ , permits the on-chip circuitry of each port to enter a very low standby power mode.

The 70T3539M can support an operating voltage of either 3.3V or 2.5V on one or both ports, controllable by the OPT pins. The power supply for the core of the device ( $V_{DD}$ ) is at 2.5V.

Pin Configuration <sup>(1,2,3,4)</sup>70T3539M

BC256<sup>(5)</sup>

BCG256<sup>(5)</sup>256-Pin BGA

Top View<sup>(6)</sup>

10/07/03

| A1<br>NC     | A2<br>TDI    | A3<br>NC     | A4<br>A17L      | A5<br>A14L  | A6<br>A11L  | A7<br>A8L   | A8<br>B̄E2L | A9<br>CE1L  | A10<br>OĒL  | A11<br>CNTENL  | A12<br>A5L   | A13<br>A2L   | A14<br>A0L    | A15<br>NC     | A16<br>NC     |

|--------------|--------------|--------------|-----------------|-------------|-------------|-------------|-------------|-------------|--------------|----------------|--------------|--------------|---------------|---------------|---------------|

| B1<br>I/O18L | B2<br>NC     | B3<br>TDO    | B4<br>A18L      | B5<br>A15L  | B6<br>A12L  | B7<br>A9L   | B8<br>B̄E3L | B9<br>CĒ0L | B10<br>R/WL  | B11<br>REPEATL | B12<br>A4L   | B13<br>A1L   | B14<br>VDD    | B15<br>I/O17L | B16<br>NC     |

| C1<br>I/O18R | C2<br>I/O19L | C3<br>VSS    | C4<br>A16L      | C5<br>A13L  | C6<br>A10L  | C7<br>A7L   | C8<br>B̄E1L | C9<br>B̄E0L | C10<br>CLKL  | C11<br>ADS̄L   | C12<br>A6L   | C13<br>A3L   | C14<br>OPTL   | C15<br>I/O17R | C16<br>I/O16L |

| D1<br>I/O20R | D2<br>I/O19R | D3<br>I/O20L | D4<br>PIPE/F̄TL | D5<br>VDDQL | D6<br>VDDQL | D7<br>VDDQR | D8<br>VDDQR | D9<br>VDDQL | D10<br>VDDQL | D11<br>VDDQR   | D12<br>VDDQR | D13<br>VDD   | D14<br>I/O15R | D15<br>I/O15L | D16<br>I/O16R |

| E1<br>I/O21R | E2<br>I/O21L | E3<br>I/O22L | E4<br>VDDQL     | E5<br>VDD   | E6<br>VDD   | E7<br>INTL  | E8<br>VSS   | E9<br>VSS   | E10<br>VSS   | E11<br>VDD     | E12<br>VDD   | E13<br>VDDQR | E14<br>I/O13L | E15<br>I/O14L | E16<br>I/O14R |

| F1<br>I/O23L | F2<br>I/O22R | F3<br>I/O23R | F4<br>VDDQL     | F5<br>VDD   | F6<br>NC    | F7<br>COLL  | F8<br>VSS   | F9<br>VSS   | F10<br>VSS   | F11<br>VSS     | F12<br>VDD   | F13<br>VDDQR | F14<br>I/O12R | F15<br>I/O13R | F16<br>I/O12L |

| G1<br>I/O24R | G2<br>I/O24L | G3<br>I/O25L | G4<br>VDDQR     | G5<br>VSS   | G6<br>VSS   | G7<br>VSS   | G8<br>VSS   | G9<br>VSS   | G10<br>VSS   | G11<br>VSS     | G12<br>VSS   | G13<br>VDDQL | G14<br>I/O10L | G15<br>I/O11L | G16<br>I/O11R |

| H1<br>I/O26L | H2<br>I/O25R | H3<br>I/O26R | H4<br>VDDQR     | H5<br>VSS   | H6<br>VSS   | H7<br>VSS   | H8<br>VSS   | H9<br>VSS   | H10<br>VSS   | H11<br>VSS     | H12<br>VSS   | H13<br>VDDQL | H14<br>I/O9R  | H15<br>IO9L   | H16<br>I/O10R |

| J1<br>I/O27L | J2<br>I/O28R | J3<br>I/O27R | J4<br>VDDQL     | J5<br>ZZR   | J6<br>VSS   | J7<br>VSS   | J8<br>VSS   | J9<br>VSS   | J10<br>VSS   | J11<br>VSS     | J12<br>ZZL   | J13<br>VDDQR | J14<br>I/O8R  | J15<br>I/O7R  | J16<br>I/O8L  |

| K1<br>I/O29R | K2<br>I/O29L | K3<br>I/O28L | K4<br>VDDQL     | K5<br>VSS   | K6<br>VSS   | K7<br>VSS   | K8<br>VSS   | K9<br>VSS   | K10<br>VSS   | K11<br>VSS     | K12<br>VSS   | K13<br>VDDQR | K14<br>I/O6R  | K15<br>I/O6L  | K16<br>I/O7L  |

| L1<br>I/O30L | L2<br>I/O31R | L3<br>I/O30R | L4<br>VDDQR     | L5<br>VDD   | L6<br>NC    | L7<br>COLR  | L8<br>VSS   | L9<br>VSS   | L10<br>VSS   | L11<br>VSS     | L12<br>VDD   | L13<br>VDDQL | L14<br>I/O5L  | L15<br>I/O4R  | L16<br>I/O5R  |

| M1<br>I/O32R | M2<br>I/O32L | M3<br>I/O31L | M4<br>VDDQR     | M5<br>VDD   | M6<br>VDD   | M7<br>INTR  | M8<br>VSS   | M9<br>VSS   | M10<br>VSS   | M11<br>VDD     | M12<br>VDD   | M13<br>VDDQL | M14<br>I/O3R  | M15<br>I/O3L  | M16<br>I/O4L  |

| N1<br>I/O33L | N2<br>I/O34R | N3<br>I/O33R | N4<br>PIPE/F̄T  | N5<br>VDDQR | N6<br>VDDQR | N7<br>VDDQL | N8<br>VDDQL | N9<br>VDDQR | N10<br>VDDQR | N11<br>VDDQL   | N12<br>VDDQL | N13<br>VDD   | N14<br>I/O2L  | N15<br>I/O1R  | N16<br>I/O2R  |

| P1<br>I/O35R | P2<br>I/O34L | P3<br>TMS    | P4<br>A16R      | P5<br>A13R  | P6<br>A10R  | P7<br>A7R   | P8<br>B̄E1R | P9<br>B̄E0R | P10<br>CLKR  | P11<br>ADS̄R   | P12<br>A6R   | P13<br>A3R   | P14<br>I/O0L  | P15<br>I/O0R  | P16<br>I/O1L  |

| R1<br>I/O35L | R2<br>NC     | R3<br>TRST   | R4<br>A18R      | R5<br>A15R  | R6<br>A12R  | R7<br>A9R   | R8<br>B̄E3R | R9<br>CĒ0R | R10<br>R/WR  | R11<br>REPEATR | R12<br>A4R   | R13<br>A1R   | R14<br>OPTR   | R15<br>NC     | R16<br>NC     |

| T1<br>NC     | T2<br>TCK    | T3<br>NC     | T4<br>A17R      | T5<br>A14R  | T6<br>A11R  | T7<br>A8R   | T8<br>B̄E2R | T9<br>CE1R  | T10<br>OĒR  | T11<br>CNTENR  | T12<br>A5R   | T13<br>A2R   | T14<br>A0R    | T15<br>NC     | T16<br>NC     |

## NOTES:

- All VDD pins must be connected to 2.5V power supply.

- All VDDQ pins must be connected to appropriate power supply: 3.3V if OPT pin for that port is set to VDD (2.5V), and 2.5V if OPT pin for that port is set to VSS (0V).

- All VSS pins must be connected to ground supply.

- Package body is approximately 17mm x 17mm x 1.4mm, with 1.0mm ball-pitch.

- This package code is used to reference the package diagram.

- This text does not indicate orientation of the actual part-marking.

5678 drw 02d

## Pin Names

| Left Port                                   | Right Port                                  | Names                                                    |

|---------------------------------------------|---------------------------------------------|----------------------------------------------------------|

| $\overline{CE}_{0L}$ , $CE_{1L}$            | $\overline{CE}_{0R}$ , $CE_{1R}$            | Chip Enables (Input) <sup>(5)</sup>                      |

| $R/W_L$                                     | $R/W_R$                                     | Read/Write Enable (Input)                                |

| $\overline{OE}_L$                           | $\overline{OE}_R$                           | Output Enable (Input)                                    |

| $A_{0L}$ - $A_{18L}$                        | $A_{0R}$ - $A_{18R}$                        | Address (Input)                                          |

| $I/O_{0L}$ - $I/O_{35L}$                    | $I/O_{0R}$ - $I/O_{35R}$                    | Data Input/Output                                        |

| $CLK_L$                                     | $CLK_R$                                     | Clock (Input)                                            |

| $PL/\overline{FT}_L$                        | $PL/\overline{FT}_R$                        | Pipeline/Flow-Through (Input)                            |

| $\overline{ADS}_L$                          | $\overline{ADS}_R$                          | Address Strobe Enable (Input)                            |

| $CNTEN_L$                                   | $CNTEN_R$                                   | Counter Enable (Input)                                   |

| $\overline{REPEAT}_L$                       | $\overline{REPEAT}_R$                       | Counter Repeat <sup>(3)</sup>                            |

| $\overline{BE}_{0L}$ - $\overline{BE}_{3L}$ | $\overline{BE}_{0R}$ - $\overline{BE}_{3R}$ | Byte Enables (9-bit bytes) (Input) <sup>(5)</sup>        |

| $V_{DDQ_L}$                                 | $V_{DDR}$                                   | Power (I/O Bus) (3.3V or 2.5V) <sup>(1)</sup> (Input)    |

| $OPT_L$                                     | $OPT_R$                                     | Option for selecting $V_{DDQX}$ <sup>(1,2)</sup> (Input) |

| $ZZ_L$                                      | $ZZ_R$                                      | Sleep Mode pin <sup>(4)</sup> (Input)                    |

| $V_{DD}$                                    |                                             | Power (2.5V) <sup>(1)</sup> (Input)                      |

| $V_{SS}$                                    |                                             | Ground (0V) (Input)                                      |

| $TDI$                                       |                                             | Test Data Input                                          |

| $TDO$                                       |                                             | Test Data Output                                         |

| $TCK$                                       |                                             | Test Logic Clock (10MHz) (Input)                         |

| $TMS$                                       |                                             | Test Mode Select (Input)                                 |

| $\overline{TRST}$                           |                                             | Reset (Initialize TAP Controller) (Input)                |

| $\overline{INT}_L$                          | $\overline{INT}_R$                          | Interrupt Flag (Output)                                  |

| $\overline{COL}_L$                          | $\overline{COL}_R$                          | Collision Alert (Output)                                 |

5678tbl01

## NOTES:

1.  $V_{DD}$ ,  $OPT_x$ , and  $V_{DDQX}$  must be set to appropriate operating levels prior to applying inputs on the I/Os and controls for that port.

2.  $OPT_x$  selects the operating voltage levels for the I/Os and controls on that port. If  $OPT_x$  is set to  $V_{DD}$  (2.5V), then that port's I/Os and controls will operate at 3.3V levels and  $V_{DDQX}$  must be supplied at 3.3V. If  $OPT_x$  is set to  $V_{SS}$  (0V), then that port's I/Os and address controls will operate at 2.5V levels and  $V_{DDQX}$  must be supplied at 2.5V. The  $OPT$  pins are independent of one another—both ports can operate at 3.3V levels, both can operate at 2.5V levels, or either can operate at 3.3V with the other at 2.5V.

3. When  $\overline{REPEAT}_x$  is asserted, the counter will reset to the last valid address loaded via  $\overline{ADS}_x$ .

4. The sleep mode pin shuts off all dynamic inputs, except JTAG inputs, when asserted. All static inputs, i.e.,  $PL/\overline{FT}_x$  and  $OPT_x$  and the sleep mode pins themselves ( $ZZ_x$ ) are not affected during sleep mode. It is recommended that boundary scan not be operated during sleep mode.

5. Chip Enables and Byte Enables are double buffered when  $PL/\overline{FT} = V_{IH}$ , i.e., the signals take two cycles to deselect.

Truth Table I—Read/Write and Enable Control <sup>(1,2,3,4)</sup>

| <u>OE</u> | CLK | <u>CE<sub>0</sub></u> | CE <sub>1</sub> | <u>BE<sub>3</sub></u> | <u>BE<sub>2</sub></u> | <u>BE<sub>1</sub></u> | <u>BE<sub>0</sub></u> | R/W | ZZ | Byte 3<br>I/O <sub>27-35</sub> | Byte 2<br>I/O <sub>18-26</sub> | Byte 1<br>I/O <sub>9-17</sub> | Byte 0<br>I/O <sub>0-8</sub> | MODE                        |

|-----------|-----|-----------------------|-----------------|-----------------------|-----------------------|-----------------------|-----------------------|-----|----|--------------------------------|--------------------------------|-------------------------------|------------------------------|-----------------------------|

| X         | ↑   | H                     | X               | X                     | X                     | X                     | X                     | X   | L  | High-Z                         | High-Z                         | High-Z                        | High-Z                       | Deselected—Power Down       |

| X         | ↑   | X                     | L               | X                     | X                     | X                     | X                     | X   | L  | High-Z                         | High-Z                         | High-Z                        | High-Z                       | Deselected—Power Down       |

| X         | ↑   | L                     | H               | H                     | H                     | H                     | H                     | X   | L  | High-Z                         | High-Z                         | High-Z                        | High-Z                       | All Bytes Deselected        |

| X         | ↑   | L                     | H               | H                     | H                     | H                     | L                     | L   | L  | High-Z                         | High-Z                         | High-Z                        | DIN                          | Write to Byte 0 Only        |

| X         | ↑   | L                     | H               | H                     | H                     | L                     | H                     | L   | L  | High-Z                         | High-Z                         | DIN                           | High-Z                       | Write to Byte 1 Only        |

| X         | ↑   | L                     | H               | H                     | L                     | H                     | H                     | L   | L  | High-Z                         | DIN                            | High-Z                        | High-Z                       | Write to Byte 2 Only        |

| X         | ↑   | L                     | H               | L                     | H                     | H                     | H                     | L   | L  | DIN                            | High-Z                         | High-Z                        | High-Z                       | Write to Byte 3 Only        |

| X         | ↑   | L                     | H               | H                     | L                     | L                     | L                     | L   | L  | High-Z                         | High-Z                         | DIN                           | DIN                          | Write to Lower 2 Bytes Only |

| X         | ↑   | L                     | H               | L                     | L                     | H                     | H                     | L   | L  | DIN                            | DIN                            | High-Z                        | High-Z                       | Write to Upper 2 bytes Only |

| X         | ↑   | L                     | H               | L                     | L                     | L                     | L                     | L   | L  | DIN                            | DIN                            | DIN                           | DIN                          | Write to All Bytes          |

| L         | ↑   | L                     | H               | H                     | H                     | H                     | L                     | H   | L  | High-Z                         | High-Z                         | High-Z                        | DOUT                         | Read Byte 0 Only            |

| L         | ↑   | L                     | H               | H                     | H                     | L                     | H                     | H   | L  | High-Z                         | High-Z                         | DOUT                          | High-Z                       | Read Byte 1 Only            |

| L         | ↑   | L                     | H               | H                     | L                     | H                     | H                     | H   | L  | High-Z                         | DOUT                           | High-Z                        | High-Z                       | Read Byte 2 Only            |

| L         | ↑   | L                     | H               | L                     | H                     | H                     | H                     | H   | L  | DOUT                           | High-Z                         | High-Z                        | High-Z                       | Read Byte 3 Only            |

| L         | ↑   | L                     | H               | H                     | H                     | L                     | L                     | H   | L  | High-Z                         | High-Z                         | DOUT                          | DOUT                         | Read Lower 2 Bytes Only     |

| L         | ↑   | L                     | H               | L                     | L                     | H                     | H                     | H   | L  | DOUT                           | DOUT                           | High-Z                        | High-Z                       | Read Upper 2 Bytes Only     |

| L         | ↑   | L                     | H               | L                     | L                     | L                     | L                     | H   | L  | DOUT                           | DOUT                           | DOUT                          | DOUT                         | Read All Bytes              |

| H         | ↑   | X                     | X               | X                     | X                     | X                     | X                     | X   | L  | High-Z                         | High-Z                         | High-Z                        | High-Z                       | Outputs Disabled            |

| X         | X   | X                     | X               | X                     | X                     | X                     | X                     | X   | H  | High-Z                         | High-Z                         | High-Z                        | High-Z                       | Sleep Mode                  |

5678 tbl 02

## NOTES:

1. "H" = V<sub>IH</sub>, "L" = V<sub>IL</sub>, "X" = Don't Care.

2. ADS, CNTEN, REPEAT = X.

3. OE and ZZ are asynchronous input signals.

4. It is possible to read or write any combination of bytes during a given access. A few representative samples have been illustrated here.

Truth Table II—Address Counter Control <sup>(1,2)</sup>

| Address | Previous Internal Address | Internal Address Used | CLK | <u>ADS</u>       | <u>CNTEN</u>     | <u>REPEAT</u> <sup>(6)</sup> | I/O <sup>(3)</sup> | MODE                                                      |

|---------|---------------------------|-----------------------|-----|------------------|------------------|------------------------------|--------------------|-----------------------------------------------------------|

| An      | X                         | An                    | ↑   | L <sup>(4)</sup> | X                | H                            | D/Io (n)           | External Address Used                                     |

| X       | An                        | An + 1                | ↑   | H                | L <sup>(5)</sup> | H                            | D/Io(n+1)          | Counter Enabled—Internal Address generation               |

| X       | An + 1                    | An + 1                | ↑   | H                | H                | H                            | D/Io(n+1)          | External Address Blocked—Counter disabled (An + 1 reused) |

| X       | X                         | An                    | ↑   | X                | X                | L <sup>(4)</sup>             | D/Io(n)            | Counter Set to last valid <u>ADS</u> load                 |

5678tbl 03

## NOTES:

1. "H" = V<sub>IH</sub>, "L" = V<sub>IL</sub>, "X" = Don't Care.

2. Read and write operations are controlled by the appropriate setting of R/W, CE<sub>0</sub>, CE<sub>1</sub>, BE<sub>n</sub> and OE.

3. Outputs configured in flow-through output mode: if outputs are in pipelined mode the data out will be delayed by one cycle.

4. ADS and REPEAT are independent of all other memory control signals including CE<sub>0</sub>, CE<sub>1</sub> and BE<sub>n</sub>.

5. The address counter advances if CNTEN = V<sub>IL</sub> on the rising edge of CLK, regardless of all other memory control signals including CE<sub>0</sub>, CE<sub>1</sub>, BE<sub>n</sub>.

6. When REPEAT is asserted, the counter will reset to the last valid address loaded via ADS. This value is not set at power-up: a known location should be loaded via ADS during initialization if desired. Any subsequent ADS access during operations will update the REPEAT address location.

Recommended Operating

Temperature and Supply Voltage <sup>(1)</sup>

| Grade      | Ambient Temperature | GND | V <sub>DD</sub>  |

|------------|---------------------|-----|------------------|

| Commercial | 0°C to +70°C        | 0V  | 2.5V $\pm$ 100mV |

| Industrial | -40°C to +85°C      | 0V  | 2.5V $\pm$ 100mV |

5678 tbl 04

## NOTES:

1. This is the parameter TA. This is the "instant on" case temperature.

Recommended DC Operating

Conditions with V<sub>DDO</sub> at 2.5V

| Symbol           | Parameter                                                                 | Min.                   | Typ. | Max.                                    | Unit |

|------------------|---------------------------------------------------------------------------|------------------------|------|-----------------------------------------|------|

| V <sub>DD</sub>  | Core Supply Voltage                                                       | 2.4                    | 2.5  | 2.6                                     | V    |

| V <sub>DDO</sub> | I/O Supply Voltage <sup>(3)</sup>                                         | 2.4                    | 2.5  | 2.6                                     | V    |

| V <sub>SS</sub>  | Ground                                                                    | 0                      | 0    | 0                                       | V    |

| V <sub>IH</sub>  | Input High Voltage<br>(Address, Control & Data I/O Inputs) <sup>(3)</sup> | 1.7                    | —    | V <sub>DDO</sub> + 100mV <sup>(2)</sup> | V    |

| V <sub>IH</sub>  | Input High Voltage - JTAG                                                 | 1.7                    | —    | V <sub>DD</sub> + 100mV <sup>(2)</sup>  | V    |

| V <sub>IH</sub>  | Input High Voltage - ZZ, OPT, PIPE/FT                                     | V <sub>DD</sub> - 0.2V | —    | V <sub>DD</sub> + 100mV <sup>(2)</sup>  | V    |

| V <sub>IL</sub>  | Input Low Voltage                                                         | -0.3 <sup>(1)</sup>    | —    | 0.7                                     | V    |

| V <sub>IL</sub>  | Input Low Voltage - ZZ, OPT, PIPE/FT                                      | -0.3 <sup>(1)</sup>    | —    | 0.2                                     | V    |

5678 tbl 05a

## NOTES:

1. V<sub>IL</sub> (min.) = -1.0V for pulse width less than tcyc/2 or 5ns, whichever is less.

2. V<sub>IH</sub> (max.) = V<sub>DD</sub> + 1.0V for pulse width less than tcyc/2 or 5ns, whichever is less.

3. To select operation at 2.5V levels on the I/Os and controls of a given port, the OPT pin for that port must be set to V<sub>SS</sub>(0V), and V<sub>DDOx</sub> for that port must be supplied as indicated above.

Recommended DC Operating

Conditions with V<sub>DDO</sub> at 3.3V

| Symbol           | Parameter                                                                 | Min.                   | Typ. | Max.                                    | Unit |

|------------------|---------------------------------------------------------------------------|------------------------|------|-----------------------------------------|------|

| V <sub>DD</sub>  | Core Supply Voltage                                                       | 2.4                    | 2.5  | 2.6                                     | V    |

| V <sub>DDO</sub> | I/O Supply Voltage <sup>(3)</sup>                                         | 3.15                   | 3.3  | 3.45                                    | V    |

| V <sub>SS</sub>  | Ground                                                                    | 0                      | 0    | 0                                       | V    |

| V <sub>IH</sub>  | Input High Voltage<br>(Address, Control & Data I/O Inputs) <sup>(3)</sup> | 2.0                    | —    | V <sub>DDO</sub> + 150mV <sup>(2)</sup> | V    |

| V <sub>IH</sub>  | Input High Voltage - JTAG                                                 | 1.7                    | —    | V <sub>DD</sub> + 100mV <sup>(2)</sup>  | V    |

| V <sub>IH</sub>  | Input High Voltage - ZZ, OPT, PIPE/FT                                     | V <sub>DD</sub> - 0.2V | —    | V <sub>DD</sub> + 100mV <sup>(2)</sup>  | V    |

| V <sub>IL</sub>  | Input Low Voltage                                                         | -0.3 <sup>(1)</sup>    | —    | 0.8                                     | V    |

| V <sub>IL</sub>  | Input Low Voltage - ZZ, OPT, PIPE/FT                                      | -0.3 <sup>(1)</sup>    | —    | 0.2                                     | V    |

5678 tbl 05b

## NOTES:

1. V<sub>IL</sub> (min.) = -1.0V for pulse width less than tcyc/2, or 5ns, whichever is less.

2. V<sub>IH</sub> (max.) = V<sub>DDO</sub> + 1.0V for pulse width less than tcyc/2 or 5ns, whichever is less.

3. To select operation at 3.3V levels on the I/Os and controls of a given port, the OPT pin for that port must be set to V<sub>DD</sub> (2.5V), and V<sub>DDOx</sub> for that port must be supplied as indicated above.

Absolute Maximum Ratings<sup>(1)</sup>

| Symbol                              | Rating                                             | Commercial & Industrial | Unit |

|-------------------------------------|----------------------------------------------------|-------------------------|------|

| $V_{TERM}$ ( $V_{DD}$ )             | $V_{DD}$ Terminal Voltage with Respect to GND      | -0.5 to 3.6             | V    |

| $V_{TERM}^{(2)}$ ( $V_{DDQ}$ )      | $V_{DDQ}$ Terminal Voltage with Respect to GND     | -0.3 to $V_{DDQ} + 0.3$ | V    |

| $V_{TERM}^{(2)}$ (INPUTS and I/O's) | Input and I/O Terminal Voltage with Respect to GND | -0.3 to $V_{DDQ} + 0.3$ | V    |

| $T_{BIAS}^{(3)}$                    | Temperature Under Bias                             | -55 to +125             | °C   |

| $T_{STG}$                           | Storage Temperature                                | -65 to +150             | °C   |

| $T_{JN}$                            | Junction Temperature                               | +150                    | °C   |

| $I_{OUT}$ (For $V_{DDQ} = 3.3V$ )   | DC Output Current                                  | 50                      | mA   |

| $I_{OUT}$ (For $V_{DDQ} = 2.5V$ )   | DC Output Current                                  | 40                      | mA   |

5678 tbl 06

## NOTES:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. This is a steady-state DC parameter that applies after the power supply has reached its nominal operating value. Power sequencing is not necessary; however, the voltage on any Input or I/O pin cannot exceed  $V_{DD}$  during power supply ramp up.

3. Ambient Temperature under DC Bias. No AC Conditions. Chip Deselected.

Capacitance<sup>(1)</sup>

(TA = +25°C, F = 1.0MHz) BGA ONLY

| Symbol          | Parameter          | Conditions <sup>(2)</sup> | Max. | Unit |

|-----------------|--------------------|---------------------------|------|------|

| $C_{IN}$        | Input Capacitance  | $V_{IN} = 0V$             | 15   | pF   |

| $C_{OUT}^{(3)}$ | Output Capacitance | $V_{OUT} = 0V$            | 10.5 | pF   |

5678tbl 07

## NOTES:

1. These parameters are determined by device characterization, but are not production tested.

2.  $C_{OUT}$  also references  $C_{IO}$ .

## DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range (VDD = 2.5V ± 100mV)

| Symbol          | Parameter                                        | Test Conditions                                                             | 70T3539MS |      | Unit |

|-----------------|--------------------------------------------------|-----------------------------------------------------------------------------|-----------|------|------|

|                 |                                                  |                                                                             | Min.      | Max. |      |

| $ I_{UL} $      | Input Leakage Current <sup>(1)</sup>             | $V_{DDQ} = \text{Max.}$ , $V_{IN} = 0V$ to $V_{DDQ}$                        | —         | 10   | µA   |

| $ I_{UL} $      | JTAG & ZZ Input Leakage Current <sup>(1,2)</sup> | $V_{DD} = \text{Max.}$ , $V_{IN} = 0V$ to $V_{DD}$                          | —         | ±30  | µA   |

| $ I_{OL} $      | Output Leakage Current <sup>(1,3)</sup>          | $\overline{CE}_0 = V_{IH}$ or $CE_1 = V_{IL}$ , $V_{OUT} = 0V$ to $V_{DDQ}$ | —         | 10   | µA   |

| $V_{OL}$ (3.3V) | Output Low Voltage <sup>(1)</sup>                | $I_{OL} = +4mA$ , $V_{DDQ} = \text{Min.}$                                   | —         | 0.4  | V    |

| $V_{OH}$ (3.3V) | Output High Voltage <sup>(1)</sup>               | $I_{OH} = -4mA$ , $V_{DDQ} = \text{Min.}$                                   | 2.4       | —    | V    |

| $V_{OL}$ (2.5V) | Output Low Voltage <sup>(1)</sup>                | $I_{OL} = +2mA$ , $V_{DDQ} = \text{Min.}$                                   | —         | 0.4  | V    |

| $V_{OH}$ (2.5V) | Output High Voltage <sup>(1)</sup>               | $I_{OH} = -2mA$ , $V_{DDQ} = \text{Min.}$                                   | 2.0       | —    | V    |

5678tbl 08

## NOTES:

1.  $V_{DDQ}$  is selectable (3.3V/2.5V) via OPT pins. Refer to p.5 for details.

2. Applicable only for TMS, TDI and TRST inputs.

3. Outputs tested in tri-state mode.

DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range <sup>(3)</sup> ( $V_{DD} = 2.5V \pm 100mV$ )

| Symbol                          | Parameter                                             | Test Condition                                                                                                                                                                                | Version | 70T3539MS166<br>Com'l Only |      | 70T3539MS133<br>Com'l & Ind |      | Unit |    |

|---------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------|------|-----------------------------|------|------|----|

|                                 |                                                       |                                                                                                                                                                                               |         | Typ. <sup>(4)</sup>        | Max. | Typ. <sup>(4)</sup>         | Max. |      |    |

| I <sub>DD</sub>                 | Dynamic Operating Current (Both Ports Active)         | $\overline{CE}_L = \overline{CE}_R = V_{IL}$ , Outputs Disabled, $f = f_{MAX}^{(1)}$                                                                                                          | COM'L   | S                          | 640  | 900                         | 520  | 740  | mA |

|                                 |                                                       |                                                                                                                                                                                               | IND     | S                          | —    | —                           | 520  | 900  |    |

| I <sub>SB1</sub> <sup>(6)</sup> | Standby Current (Both Ports - TTL Level Inputs)       | $\overline{CE}_L = \overline{CE}_R = V_{IH}$ , $f = f_{MAX}^{(1)}$                                                                                                                            | COM'L   | S                          | 350  | 460                         | 280  | 380  | mA |

|                                 |                                                       |                                                                                                                                                                                               | IND     | S                          | —    | —                           | 280  | 470  |    |

| I <sub>SB2</sub> <sup>(6)</sup> | Standby Current (One Port - TTL Level Inputs)         | $\overline{CE}^{(A)} = V_{IL}$ and $\overline{CE}^{(B)} = V_{IH}^{(5)}$ , Active Port Outputs Disabled, $f=f_{MAX}^{(1)}$                                                                     | COM'L   | S                          | 500  | 650                         | 400  | 500  | mA |

|                                 |                                                       |                                                                                                                                                                                               | IND     | S                          | —    | —                           | 400  | 620  |    |

| I <sub>SB3</sub>                | Full Standby Current (Both Ports - CMOS Level Inputs) | Both Ports $\overline{CE}_L$ and $\overline{CE}_R \geq V_{DDQ} - 0.2V$ , $V_{IN} \geq V_{DDQ} - 0.2V$ or $V_{IN} \leq 0.2V$ , $f = 0^{(2)}$                                                   | COM'L   | S                          | 12   | 20                          | 12   | 20   | mA |

|                                 |                                                       |                                                                                                                                                                                               | IND     | S                          | —    | —                           | 12   | 25   |    |

| I <sub>SB4</sub> <sup>(6)</sup> | Full Standby Current (One Port - CMOS Level Inputs)   | $\overline{CE}^{(A)} \leq 0.2V$ and $\overline{CE}^{(B)} \geq V_{DDQ} - 0.2V^{(5)}$ , $V_{IN} \geq V_{DDQ} - 0.2V$ or $V_{IN} \leq 0.2V$ , Active Port, Outputs Disabled, $f = f_{MAX}^{(1)}$ | COM'L   | S                          | 500  | 650                         | 400  | 500  | mA |

|                                 |                                                       |                                                                                                                                                                                               | IND     | S                          | —    | —                           | 400  | 620  |    |

| I <sub>zz</sub>                 | Sleep Mode Current (Both Ports - TTL Level Inputs)    | $Z_{ZL} = Z_{ZR} = V_{IH}$ , $f=f_{MAX}^{(1)}$                                                                                                                                                | COM'L   | S                          | 12   | 20                          | 12   | 20   | mA |

|                                 |                                                       |                                                                                                                                                                                               | IND     | S                          | —    | —                           | 12   | 25   |    |

5678 Ibl 09

## NOTES:

- At  $f = f_{MAX}$ , address and control lines (except Output Enable) are cycling at the maximum frequency clock cycle of  $1/t_{cyc}$ , using "AC TEST CONDITIONS".

- $f = 0$  means no address, clock, or control lines change. Applies only to input at CMOS level standby.

- Port "A" may be either left or right port. Port "B" is the opposite from port "A".

- $V_{DD} = 2.5V$ ,  $T_A = 25^\circ C$  for Typ, and are not production tested.  $I_{DD DC}(f=0) = 30mA$  (Typ).

- $\overline{CE}_X = V_{IL}$  means  $\overline{CE}_{0X} = V_{IL}$  and  $CE_{1X} = V_{IH}$

$\overline{CE}_X = V_{IH}$  means  $\overline{CE}_{0X} = V_{IH}$  or  $CE_{1X} = V_{IL}$

$\overline{CE}_X \leq 0.2V$  means  $\overline{CE}_{0X} \leq 0.2V$  and  $CE_{1X} \geq V_{DDQ} - 0.2V$

$CE_X \geq V_{DDQ} - 0.2V$  means  $\overline{CE}_{0X} \geq V_{DDQ} - 0.2V$  or  $CE_{1X} \leq 0.2V$

"X" represents "L" for left port or "R" for right port.

- I<sub>SB1</sub>, I<sub>SB2</sub> and I<sub>SB4</sub> will all reach full standby levels (I<sub>SB3</sub>) on the appropriate port(s) if  $Z_{ZL}$  and/or  $Z_{ZR} = V_{IH}$ .

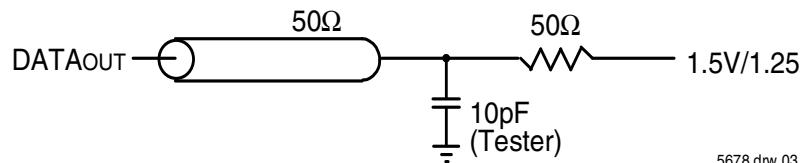

AC Test Conditions (V<sub>DDO</sub> - 3.3V/2.5V)

|                                         |                         |

|-----------------------------------------|-------------------------|

| Input Pulse Levels (Address & Controls) | GND to 3.0V/GND to 2.4V |

| Input Pulse Levels (I/Os)               | GND to 3.0V/GND to 2.4V |

| Input Rise/Fall Times                   | 2ns                     |

| Input Timing Reference Levels           | 1.5V/1.25V              |

| Output Reference Levels                 | 1.5V/1.25V              |

| Output Load                             | Figure 1                |

5678 tbl 10

5678 drw 03

Figure 1. AC Output Test load.

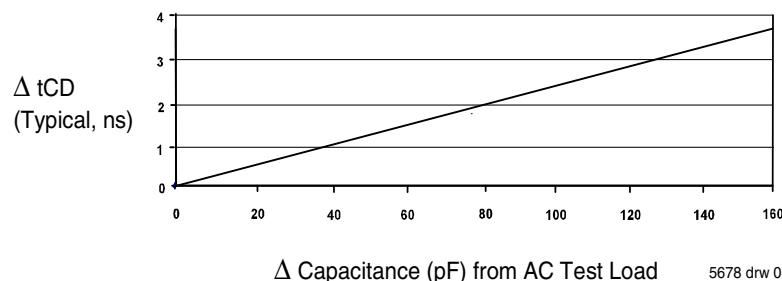

Δ Capacitance (pF) from AC Test Load

5678 drw 04

AC Electrical Characteristics Over the Operating Temperature Range

(Read and Write Cycle Timing)<sup>(2,3)</sup> (VDD = 2.5V ± 100mV, TA = 0°C to +70°C)

| Symbol                    | Parameter                                         | 70T3539MS166<br>Com'l Only                                  |      | 70T3539MS133<br>Com'l & Ind |      | Unit   |

|---------------------------|---------------------------------------------------|-------------------------------------------------------------|------|-----------------------------|------|--------|

|                           |                                                   | Min.                                                        | Max. | Min.                        | Max. |        |

| tCYC1                     | Clock Cycle Time (Flow-Through) <sup>(1)</sup>    | 20                                                          | —    | 25                          | —    | ns     |

| tCYC2                     | Clock Cycle Time (Pipelined) <sup>(1)</sup>       | 6                                                           | —    | 7.5                         | —    | ns     |

| tCH1                      | Clock High Time (Flow-Through) <sup>(1)</sup>     | 8                                                           | —    | 10                          | —    | ns     |

| tCL1                      | Clock Low Time (Flow-Through) <sup>(1)</sup>      | 8                                                           | —    | 10                          | —    | ns     |

| tCH2                      | Clock High Time (Pipelined) <sup>(2)</sup>        | 2.4                                                         | —    | 3                           | —    | ns     |

| tCL2                      | Clock Low Time (Pipelined) <sup>(1)</sup>         | 2.4                                                         | —    | 3                           | —    | ns     |

| tSA                       | Address Setup Time                                | 1.7                                                         | —    | 1.8                         | —    | ns     |

| tHA                       | Address Hold Time                                 | 0.5                                                         | —    | 0.5                         | —    | ns     |

| tSC                       | Chip Enable Setup Time                            | 1.7                                                         | —    | 1.8                         | —    | ns     |

| tHC                       | Chip Enable Hold Time                             | 0.5                                                         | —    | 0.5                         | —    | ns     |

| tSB                       | Byte Enable Setup Time                            | 1.7                                                         | —    | 1.8                         | —    | ns     |

| tHB                       | Byte Enable Hold Time                             | 0.5                                                         | —    | 0.5                         | —    | ns     |

| tSW                       | R/W Setup Time                                    | 1.7                                                         | —    | 1.8                         | —    | ns     |

| tHW                       | R/W Hold Time                                     | 0.5                                                         | —    | 0.5                         | —    | ns     |

| tSD                       | Input Data Setup Time                             | 1.7                                                         | —    | 1.8                         | —    | ns     |

| tHD                       | Input Data Hold Time                              | 0.5                                                         | —    | 0.5                         | —    | ns     |

| tSAD                      | ADS Setup Time                                    | 1.7                                                         | —    | 1.8                         | —    | ns     |

| tHAD                      | ADS Hold Time                                     | 0.5                                                         | —    | 0.5                         | —    | ns     |

| tSCN                      | CNTEN Setup Time                                  | 1.7                                                         | —    | 1.8                         | —    | ns     |

| tHCN                      | CNTEN Hold Time                                   | 0.5                                                         | —    | 0.5                         | —    | ns     |

| tSRPT                     | REPEAT Setup Time                                 | 1.7                                                         | —    | 1.8                         | —    | ns     |

| tHRPT                     | REPEAT Hold Time                                  | 0.5                                                         | —    | 0.5                         | —    | ns     |

| toE                       | Output Enable to Data Valid                       | —                                                           | 4.4  | —                           | 4.6  | ns     |

| tOLZ <sup>(6)</sup>       | Output Enable to Output Low-Z                     | 1                                                           | —    | 1                           | —    | ns     |

| tOHZ <sup>(6)</sup>       | Output Enable to Output High-Z                    | 1                                                           | 3.6  | 1                           | 4.2  | ns     |

| tCD1                      | Clock to Data Valid (Flow-Through) <sup>(1)</sup> | —                                                           | 12   | —                           | 15   | ns     |

| tCD2                      | Clock to Data Valid (Pipelined) <sup>(1)</sup>    | —                                                           | 3.6  | —                           | 4.2  | ns     |

| tDC                       | Data Output Hold After Clock High                 | 1                                                           | —    | 1                           | —    | ns     |

| tCKHZ <sup>(6)</sup>      | Clock High to Output High-Z                       | 1                                                           | 3.6  | 1                           | 4.2  | ns     |

| tCKLZ <sup>(6)</sup>      | Clock High to Output Low-Z                        | 1                                                           | —    | 1                           | —    | ns     |

| tINS                      | Interrupt Flag Set Time                           | —                                                           | 7    | —                           | 7    | ns     |

| tINR                      | Interrupt Flag Reset Time                         | —                                                           | 7    | —                           | 7    | ns     |

| tCOLS                     | Collision Flag Set Time                           | —                                                           | 3.6  | —                           | 4.2  | ns     |

| tCOLR                     | Collision Flag Reset Time                         | —                                                           | 3.6  | —                           | 4.2  | ns     |

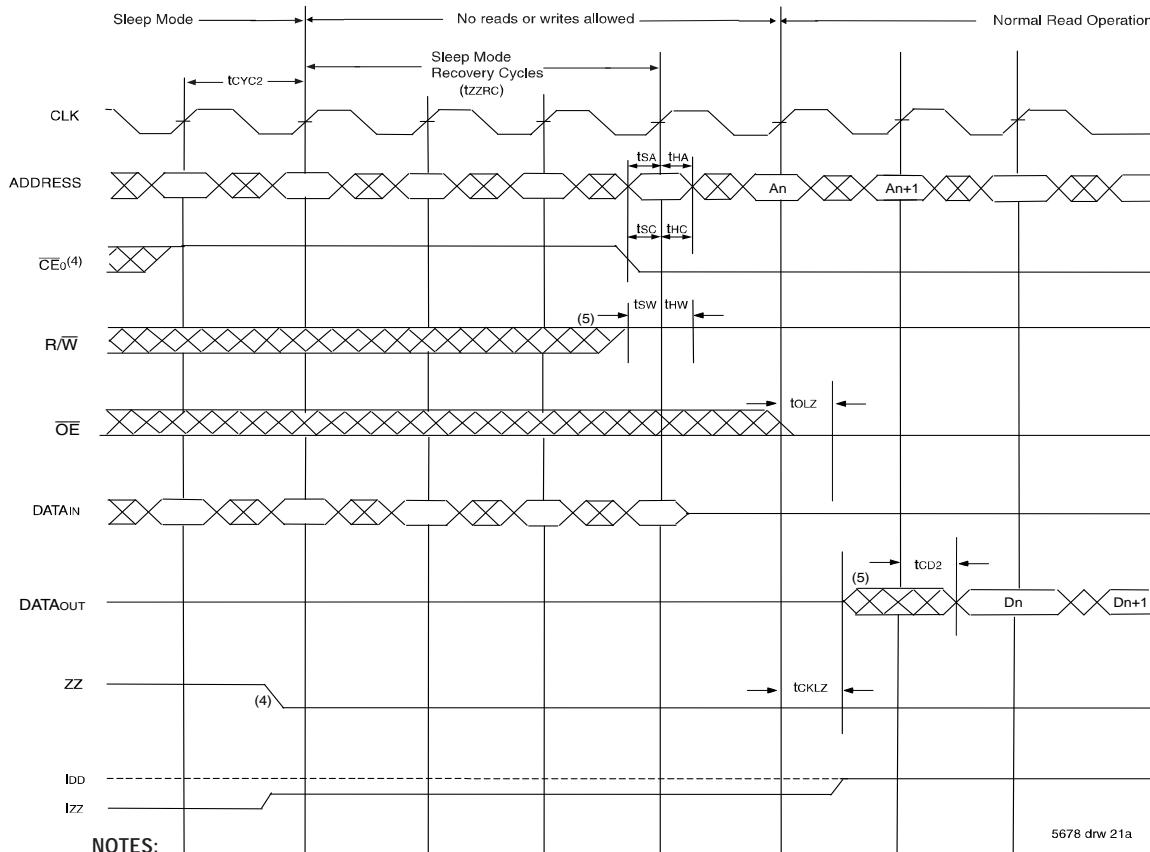

| tZSC                      | Sleep Mode Set Cycles                             | 2                                                           | —    | 2                           | —    | cycles |

| tZRC                      | Sleep Mode Recovery Cycles                        | 3                                                           | —    | 3                           | —    | cycles |

| <b>Port-to-Port Delay</b> |                                                   |                                                             |      |                             |      |        |

| tCO                       | Clock-to-Clock Offset                             | 5                                                           | —    | 6                           | —    | ns     |

| tOFS                      | Clock-to-Clock Offset for Collision Detection     | Please refer to Collision Detection Timing Table on Page 19 |      |                             |      |        |

## NOTES:

- The Pipelined output parameters (tCYC2, tCD2) apply to either or both left and right ports when  $\overline{FT}/PIPE_{Ex} = VDD$  (2.5V). Flow-through parameters (tCYC1, tCD1) apply when  $\overline{FT}/PIPE = VSS$  (0V) for that port.

- All input signals are synchronous with respect to the clock except for the asynchronous Output Enable ( $\overline{OE}$ ),  $\overline{FT}/PIPE$  and OPT.  $\overline{FT}/PIPE$  and OPT should be treated as DC signals, i.e. steady state during operation.

- These values are valid for either level of VDD (3.3V/2.5V). See page 6 for details on selecting the desired operating voltage levels for each port.

- Guaranteed by design (not production tested).

5678tbl1

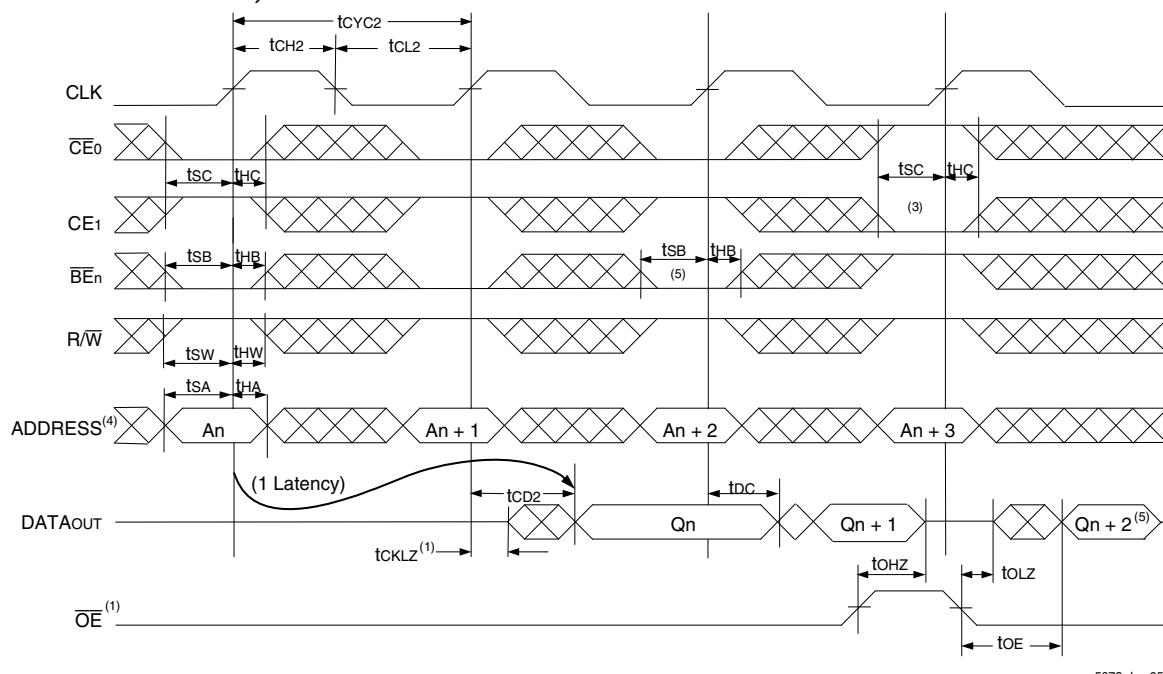

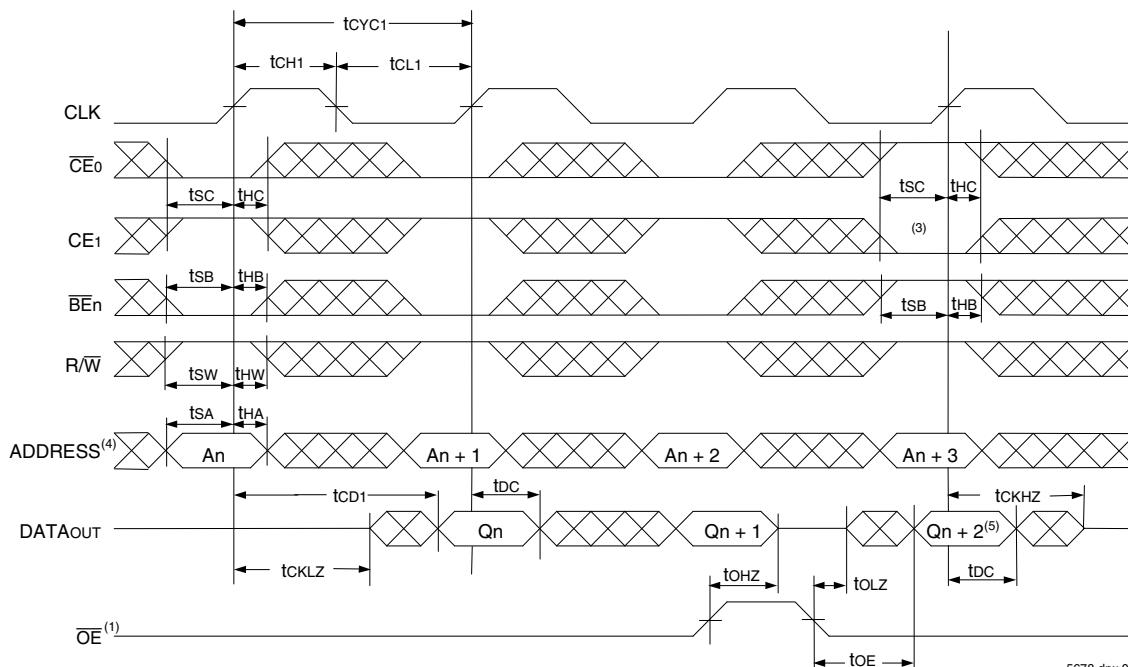

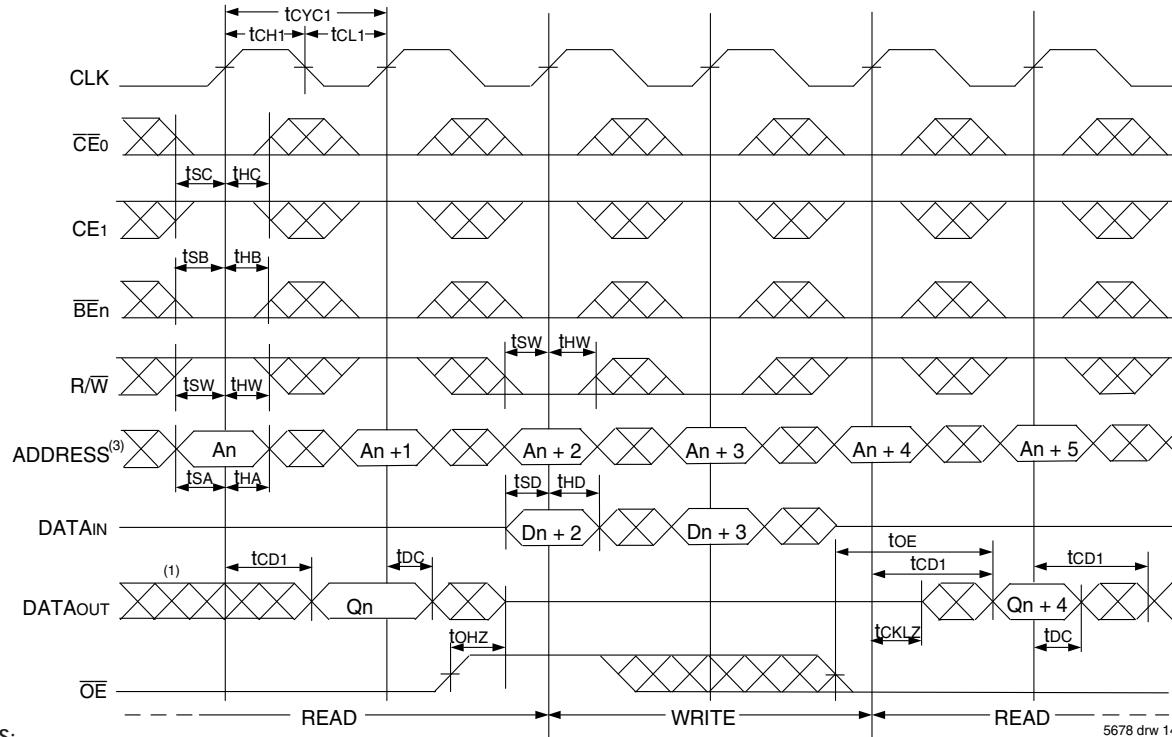

Timing Waveform of Read Cycle for Pipelined Operation

( $\overline{FT}/PIPE'x' = V_{IH}$ )<sup>(1,2)</sup>

5678 drw 05

Timing Waveform of Read Cycle for Flow-through Output

( $\overline{FT}/PIPE''x'' = V_{IL}$ )<sup>(1,2,6)</sup>

5678 drw 06

## NOTES:

1.  $\overline{OE}$  is asynchronously controlled; all other inputs depicted in the above waveforms are synchronous to the rising clock edge.

2.  $\overline{ADS} = V_{IL}$ ,  $\overline{CNTEN}$  and  $\overline{REPEAT} = V_{IH}$ .

3. The output is disabled (High-Impedance state) by  $\overline{CE}_0 = V_{IH}$ ,  $CE1 = V_{IL}$ ,  $\overline{BE}_n = V_{IH}$  following the next rising edge of the clock. Refer to Truth Table 1.

4. Addresses do not have to be accessed sequentially since  $\overline{ADS} = V_{IL}$  constantly loads the address on the rising edge of the CLK; numbers are for reference use only.

5. If  $\overline{BE}_n$  was HIGH, then the appropriate Byte of DATAOUT for  $Q_n + 2$  would be disabled (High-Impedance state).

6. "x" denotes Left or Right port. The diagram is with respect to that port.

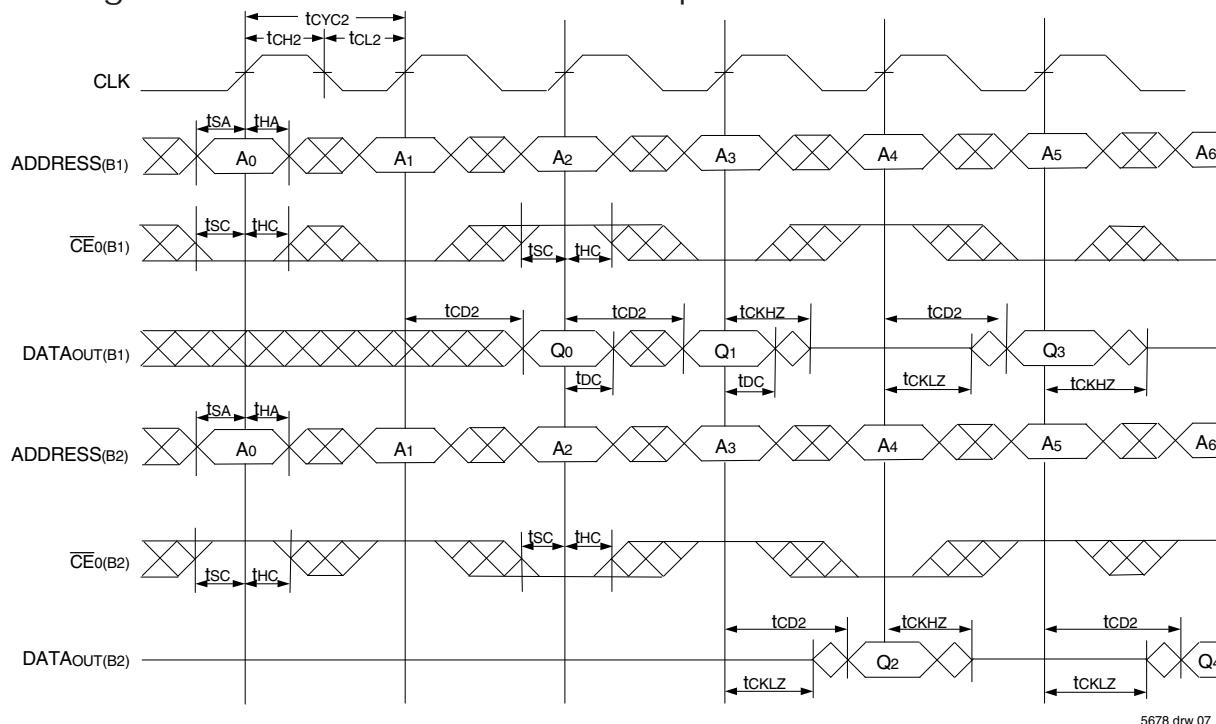

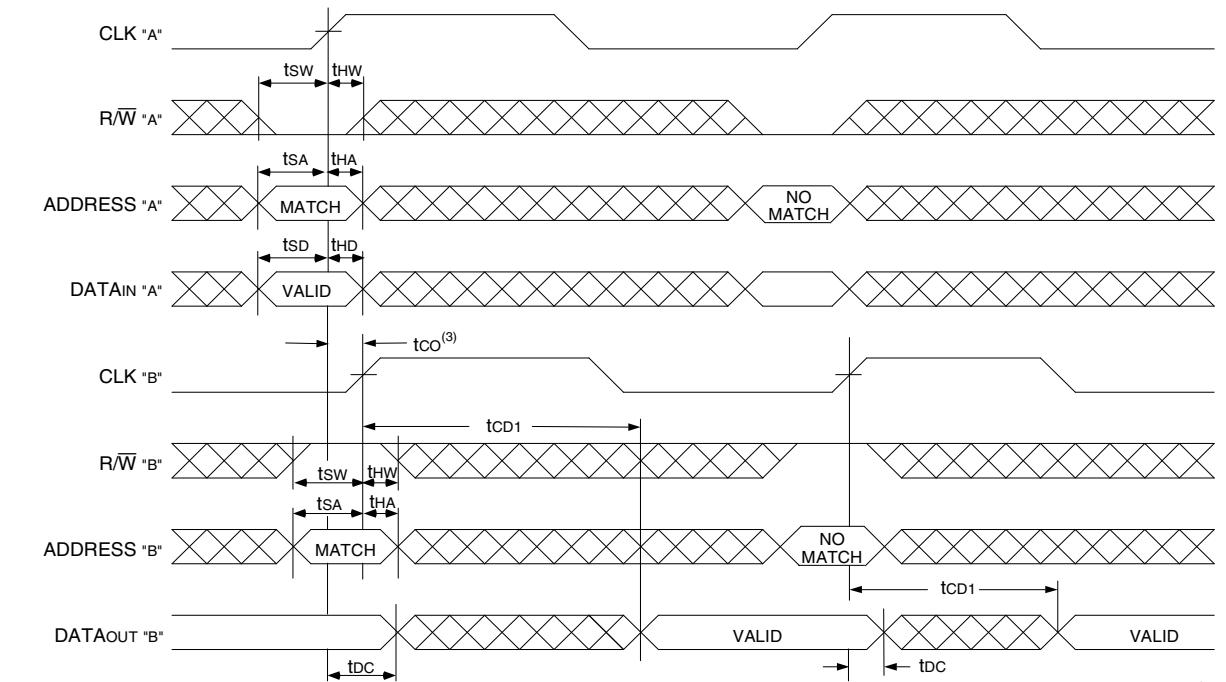

Timing Waveform of a Multi-Device Pipelined Read<sup>(1,2)</sup>Timing Waveform of a Multi-Device Flow-Through Read<sup>(1,2)</sup>

## NOTES:

1. B1 Represents Device #1; B2 Represents Device #2. Each Device consists of one IDT70T3539M for this waveform, and are setup for depth expansion in this situation. ADDRESS<sub>(B1)</sub> = ADDRESS<sub>(B2)</sub> in this situation.

2. BE<sub>n</sub>, OE, and ADS = V<sub>IL</sub>; CE1<sub>(B1)</sub>, CE1<sub>(B2)</sub>, R/W, CNTE<sub>N</sub>, and REPEAT = V<sub>IH</sub>.

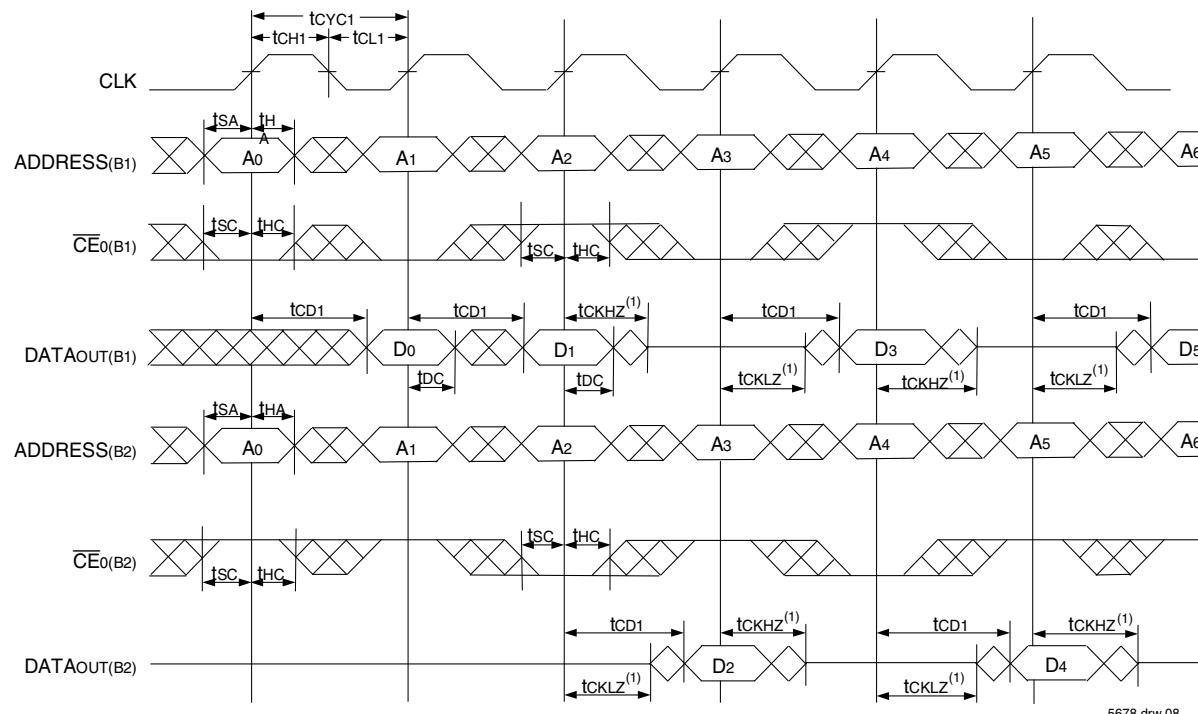

Timing Waveform of Left Port Write to Pipelined Right Port Read<sup>(1,2,4)</sup>

## NOTES:

- $\overline{CE}_0$ ,  $\overline{BE}_n$ , and  $\overline{ADS} = V_{IL}$ ;  $CE_1$ ,  $CNTEN$ , and  $\overline{REPEAT} = V_{IH}$ .

- $\overline{OE} = V_{IL}$  for Port "B", which is being read from.  $\overline{OE} = V_{IH}$  for Port "A", which is being written to.

- If  $t_{CO} \leq$  minimum specified, then data from Port "B" read is not valid until following Port "B" clock cycle (i.e., time from write to valid read on opposite port will be  $t_{CO} + 2 \cdot t_{CYC2} + t_{CD2}$ ). If  $t_{CO} >$  minimum, then data from Port "B" read is available on first Port "B" clock cycle (i.e., time from write to valid read on opposite port will be  $t_{CO} + t_{CYC2} + t_{CD2}$ ).

- All timing is the same for Left and Right ports. Port "A" may be either Left or Right port. Port "B" is the opposite of Port "A".

Timing Waveform with Port-to-Port Flow-Through Read<sup>(1,2,4)</sup>

## NOTES:

- $\overline{CE}_0$ ,  $\overline{BE}_n$ , and  $\overline{ADS} = V_{IL}$ ;  $CE_1$ ,  $CNTEN$ , and  $\overline{REPEAT} = V_{IH}$ .

- $\overline{OE} = V_{IL}$  for the Right Port, which is being read from.  $\overline{OE} = V_{IH}$  for the Left Port, which is being written to.

- If  $t_{CO} \leq$  minimum specified, then data from Port "B" read is not valid until following Port "B" clock cycle (i.e., time from write to valid read on opposite port will be  $t_{CO} + t_{CYC} + t_{CD1}$ ). If  $t_{CO} >$  minimum, then data from Port "B" read is available on first Port "B" clock cycle (i.e., time from write to valid read on opposite port will be  $t_{CO} + t_{CD1}$ ).

- All timing is the same for both left and right ports. Port "A" may be either left or right port. Port "B" is the opposite of Port "A".

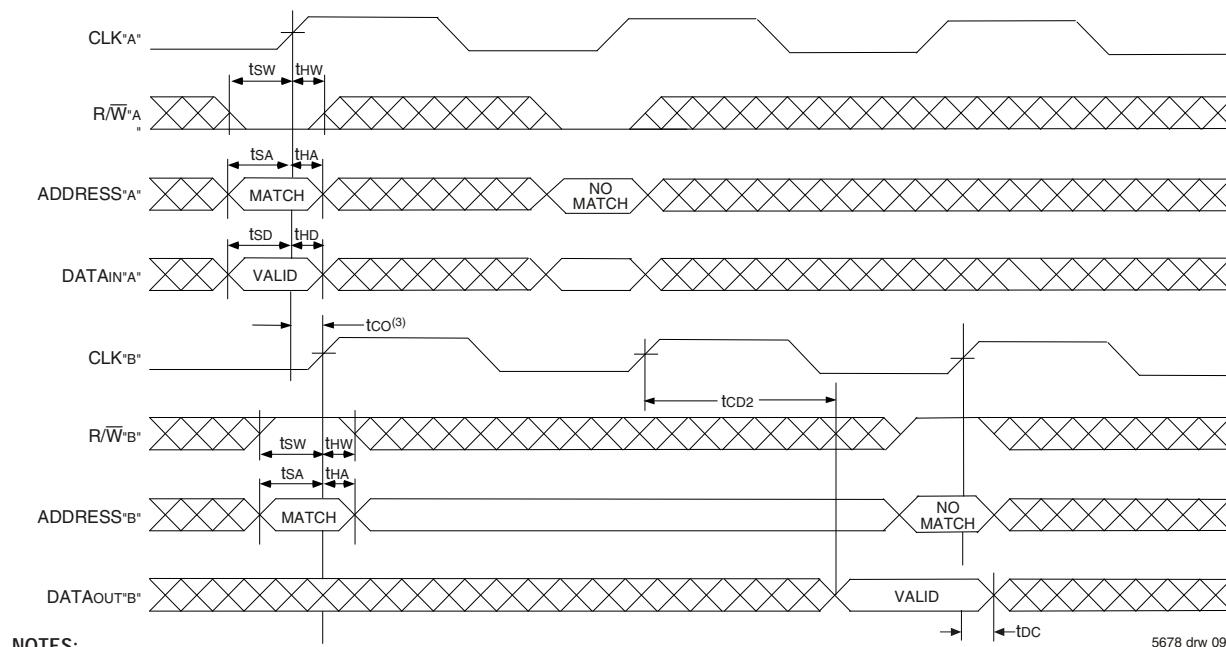

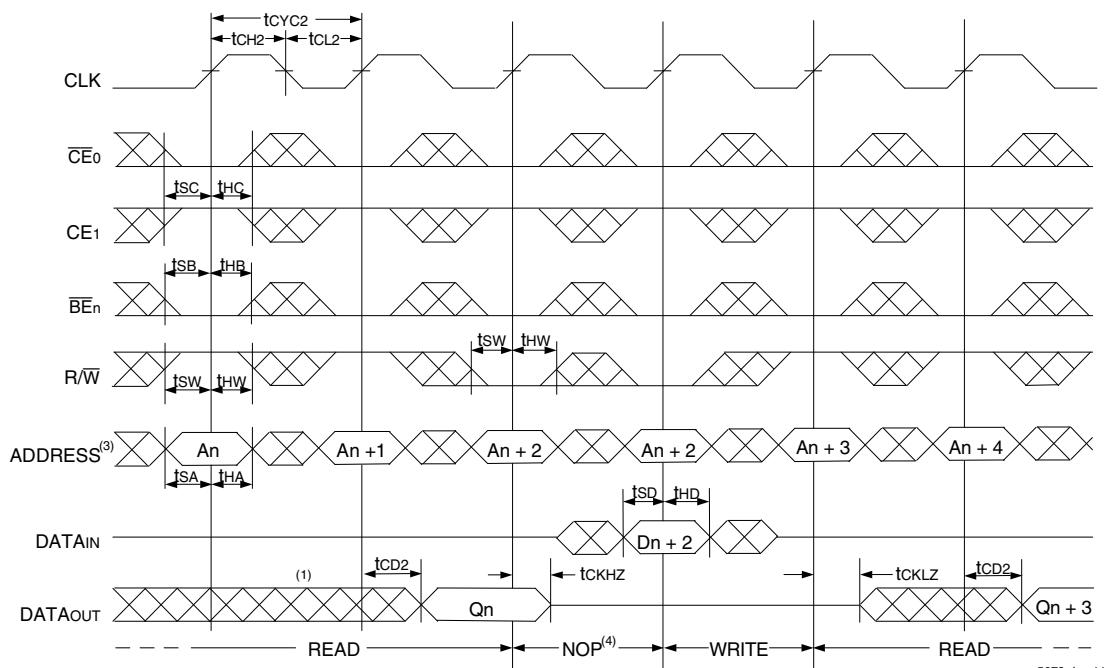

Timing Waveform of Pipelined Read-to-Write-to-Read ( $\overline{OE} = V_{IL}$ )<sup>(2)</sup>

## NOTES:

1. Output state (High, Low, or High-impedance) is determined by the previous cycle control signals.

2.  $\overline{CE}_0$ ,  $\overline{BE}_n$ , and  $\overline{ADS} = V_{IL}$ ;  $CE_1$ ,  $\overline{CNTEN}$ , and  $\overline{REPEAT} = V_{IH}$ . "NOP" is "No Operation".

3. Addresses do not have to be accessed sequentially since  $\overline{ADS} = V_{IL}$  constantly loads the address on the rising edge of the CLK; numbers are for reference use only.

4. "NOP" is "No Operation." Data in memory at the selected address may be corrupted and should be re-written to guarantee data integrity.

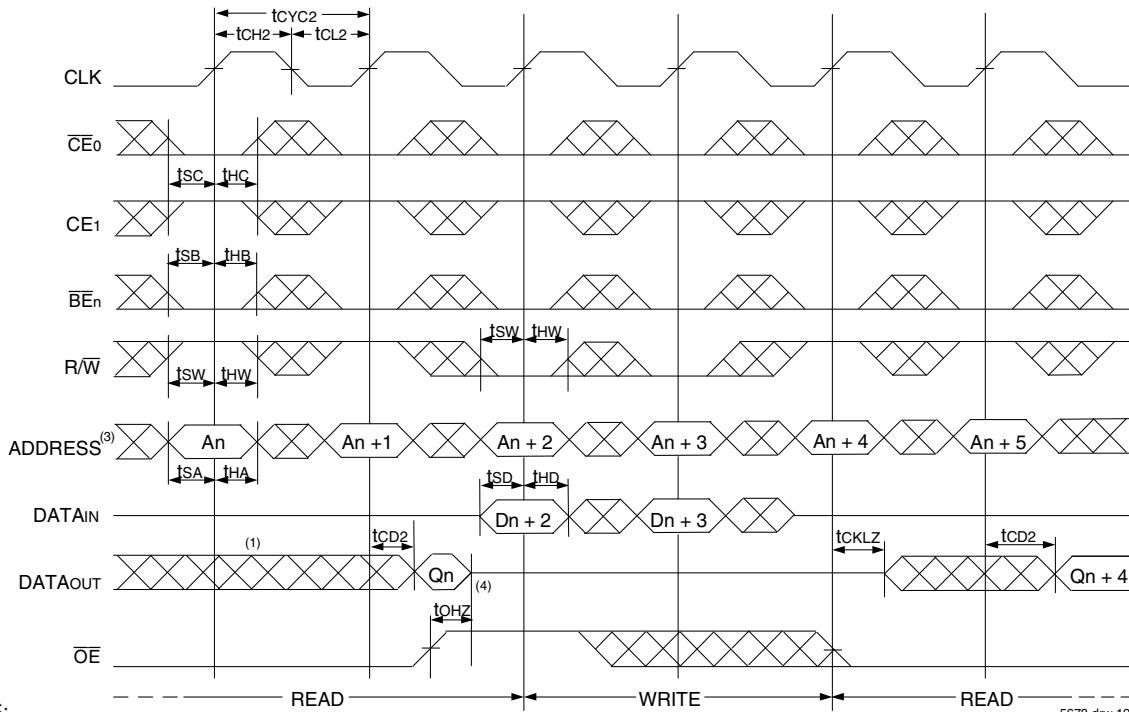

Timing Waveform of Pipelined Read-to-Write-to-Read ( $\overline{OE}$  Controlled)<sup>(2)</sup>

## NOTES:

1. Output state (High, Low, or High-impedance) is determined by the previous cycle control signals.

2.  $\overline{CE}_0$ ,  $\overline{BE}_n$ , and  $\overline{ADS} = V_{IL}$ ;  $CE_1$ ,  $\overline{CNTEN}$ , and  $\overline{REPEAT} = V_{IH}$ .

3. Addresses do not have to be accessed sequentially since  $\overline{ADS} = V_{IL}$  constantly loads the address on the rising edge of the CLK; numbers are for reference use only.

4. This timing does not meet requirements for fastest speed grade. This waveform indicates how logically it could be done if timing so allows.

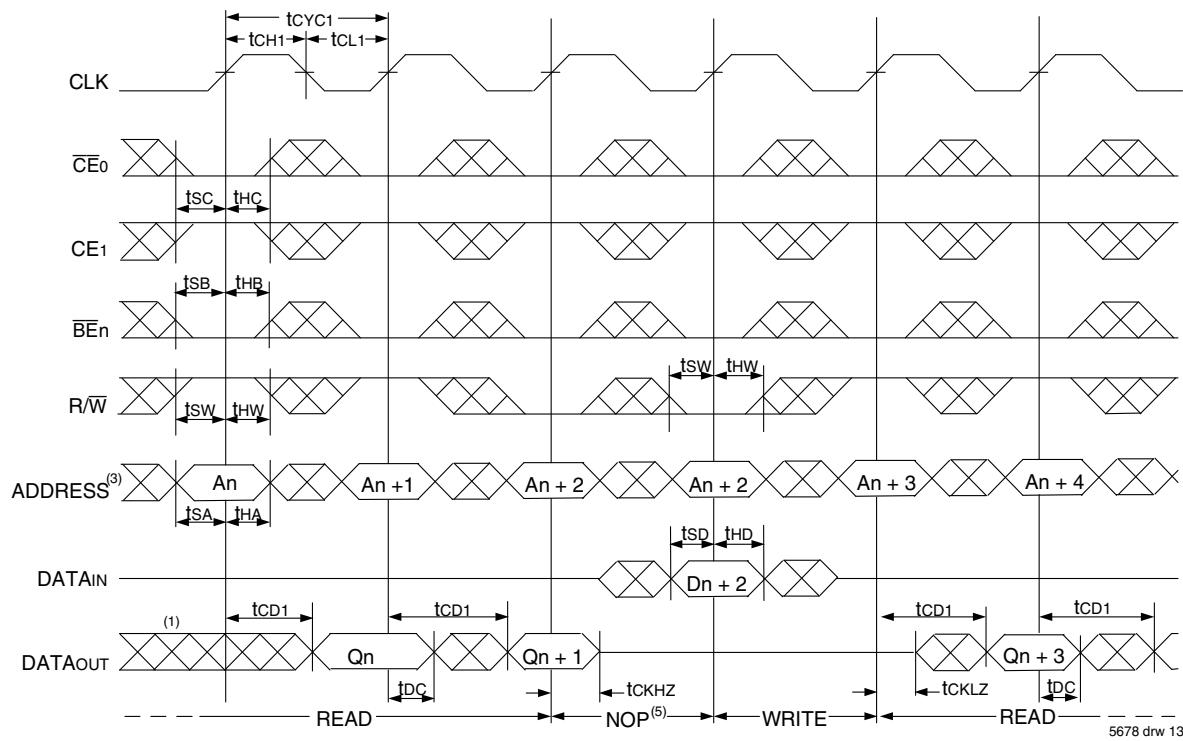

## Timing Waveform of Flow-Through Read-to-Write-to-Read ( $\overline{\text{OE}} = V_{IL}$ )<sup>(2)</sup>

## Timing Waveform of Flow-Through Read-to-Write-to-Read (**OE** Controlled)<sup>(2)</sup>

## NOTES:

1. Output state (High, Low, or High-impedance) is determined by the previous cycle control signals.

2.  $\overline{CE_0}$ ,  $\overline{BE_n}$ , and  $\overline{ADS} = V_{IL}$ ;  $CE_1$ ,  $\overline{CNTEN}$ , and  $\overline{REPEAT} = V_{IH}$ .

3. Addresses do not have to be accessed sequentially since  $\overline{ADS} = V_{IL}$  constantly loads the address on the rising edge of the CLK; numbers are for reference use only.

4. "NOP" is "No Operation." Data in memory at the selected address may be corrupted and should be re-written to guarantee data integrity.

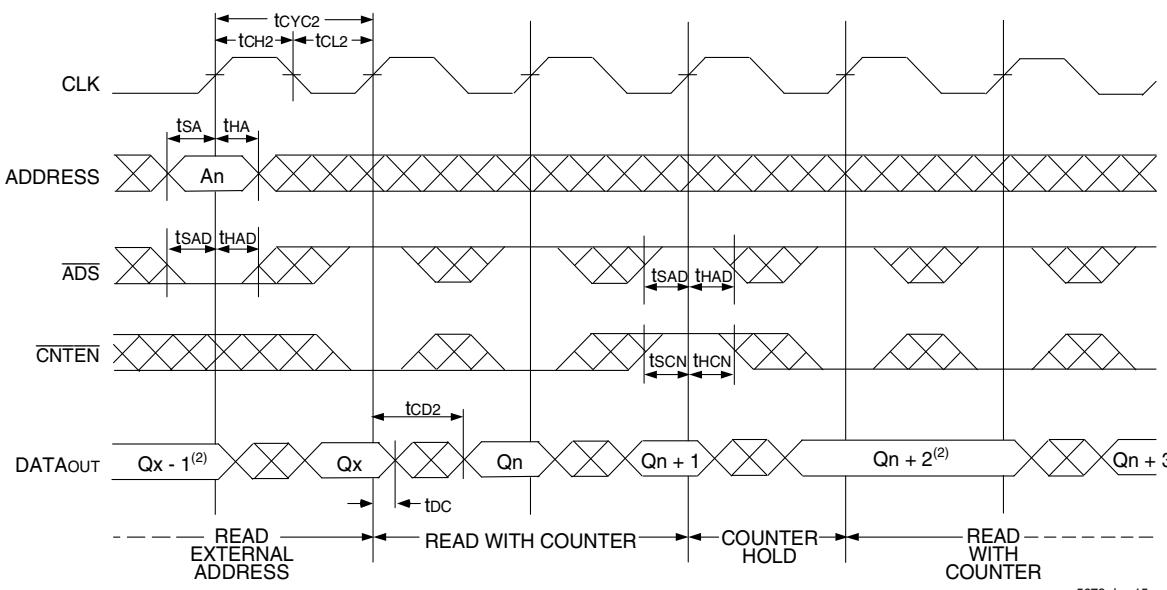

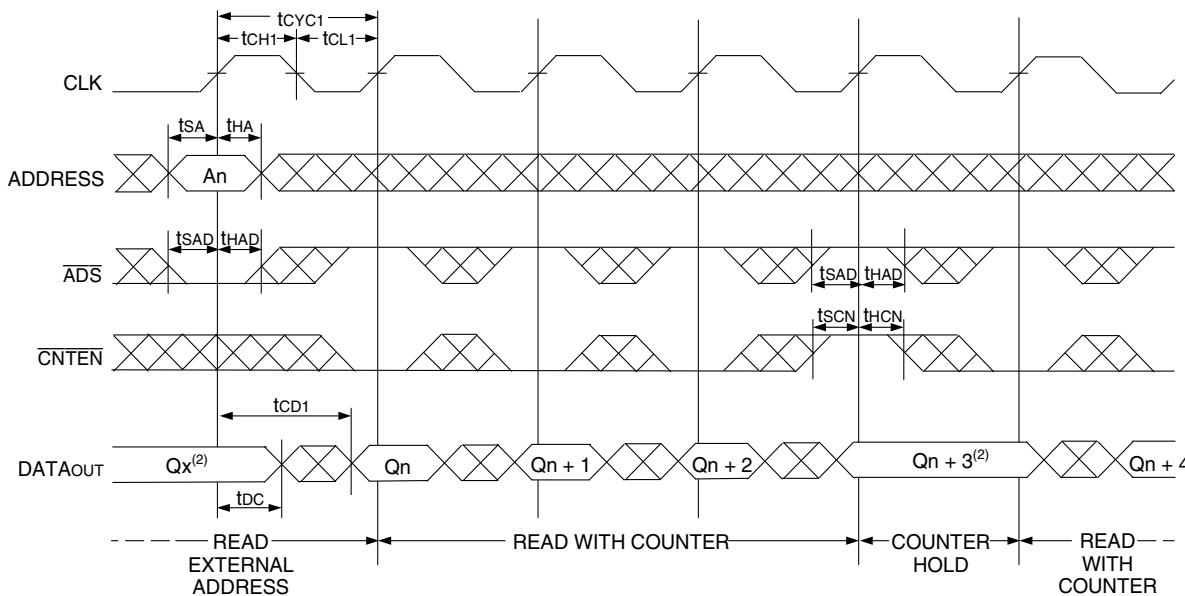

Timing Waveform of Pipelined Read with Address Counter Advance<sup>(1)</sup>Timing Waveform of Flow-Through Read with Address Counter Advance<sup>(1)</sup>

## NOTES:

1.  $\overline{CE}_0$ ,  $\overline{OE}$ ,  $\overline{BE}_n$  =  $V_{IL}$ ;  $CE_1$ ,  $R/\overline{W}$ , and  $\overline{REPEAT}$  =  $V_{IH}$ .

2. If there is no address change via  $\overline{ADS} = V_{IL}$  (loading a new address) or  $\overline{CNTEN} = V_{IL}$  (advancing the address), i.e.  $\overline{ADS} = V_{IH}$  and  $\overline{CNTEN} = V_{IH}$ , then the data output remains constant for subsequent clocks.

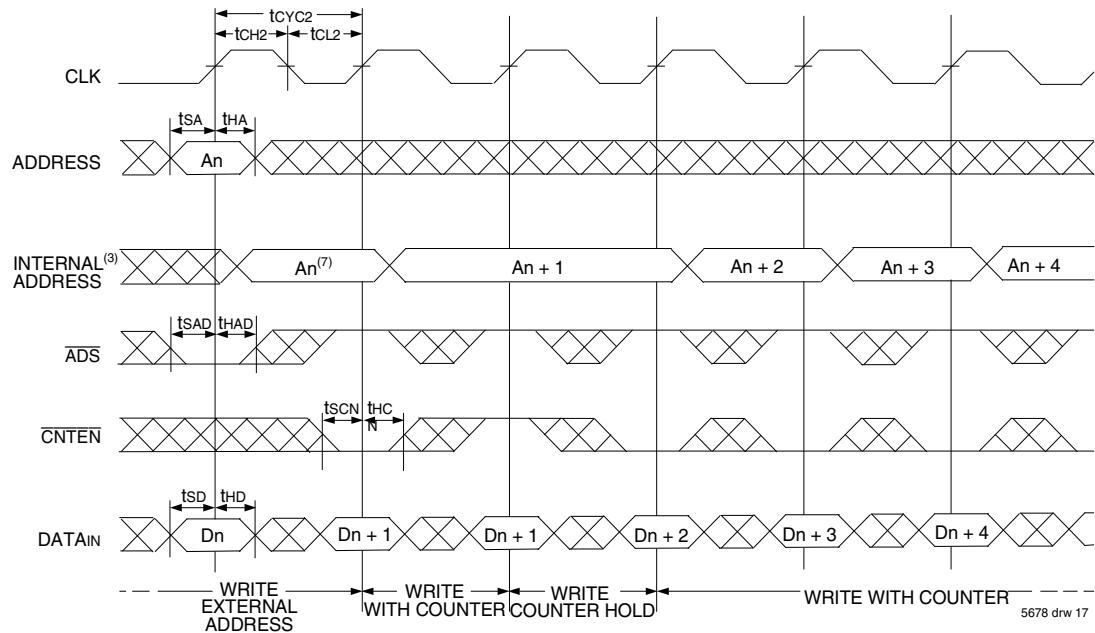

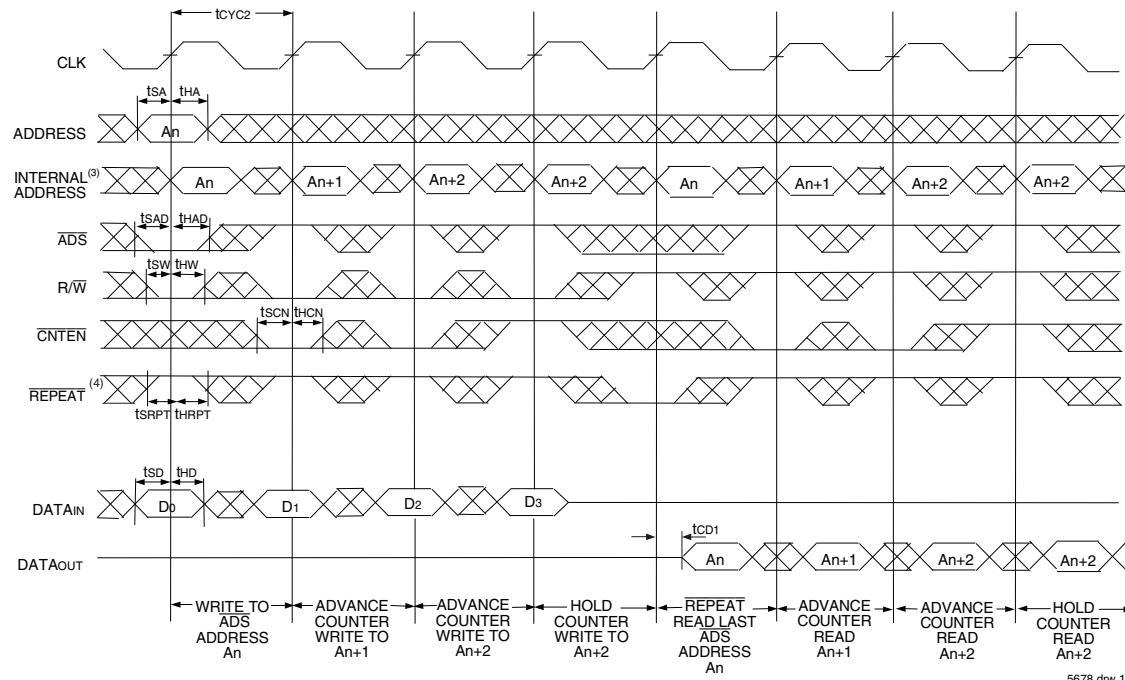

Timing Waveform of Write with Address Counter Advance

(Flow-through or Pipelined Inputs)<sup>(1)</sup>Timing Waveform of Counter Repeat<sup>(2,6)</sup>

## NOTES:

1.  $\overline{CE}_0$ ,  $\overline{BE}_n$ , and  $\overline{R/W} = V_{IL}$ ;  $CE_1$  and  $\overline{REPEAT} = V_{IH}$ .

2.  $\overline{CE}_0$ ,  $\overline{BE}_n = V_{IL}$ ;  $CE_1 = V_{IH}$ .

3. The "Internal Address" is equal to the "External Address" when  $\overline{ADS} = V_{IL}$  and equals the counter output when  $\overline{ADS} = V_{IH}$ .

4. No dead cycle exists during  $\overline{REPEAT}$  operation. A READ or WRITE cycle may be coincidental with the counter  $\overline{REPEAT}$  cycle: Address loaded by last valid ADS load will be accessed. For more information on  $\overline{REPEAT}$  function refer to Truth Table II.

5.  $CNTEN = V_{IL}$  advances Internal Address from 'An' to 'An +1'. The transition shown indicates the time required for the counter to advance. The 'An +1'Address is written to during this cycle.

6. For Pipelined Mode user should add 1 cycle latency for outputs as per timing waveform of read cycle for pipelined operations.

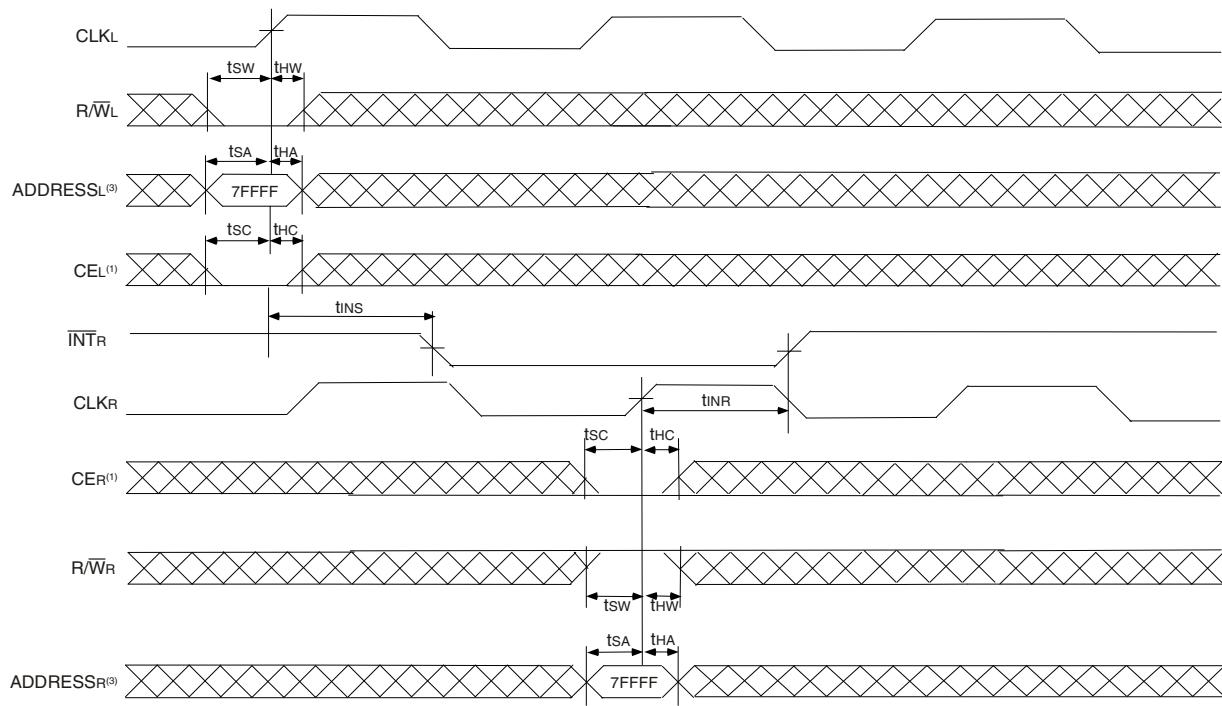

Waveform of Interrupt Timing<sup>(2)</sup>

5678 drw 19

## NOTES:

1.  $\overline{CE}_0 = V_{IL}$  and  $CE_1 = V_{IH}$

2. All timing is the same for Left and Right ports.

3. Address is for internal register, not the external bus, i.e., address needs to be qualified by one of the Address counter control signals.

Truth Table III — Interrupt Flag<sup>(1)</sup>

| Left Port |                          |              |          |      | Right Port |                          |              |          |      | Function                          |

|-----------|--------------------------|--------------|----------|------|------------|--------------------------|--------------|----------|------|-----------------------------------|

| CLKL      | $\overline{R/W}_L^{(2)}$ | $CE_1^{(2)}$ | A18L-A0L | INTL | CLKR       | $\overline{R/W}_R^{(2)}$ | $CE_1^{(2)}$ | A18R-A0R | INTR |                                   |

| ↑         | L                        | L            | 7FFFF    | X    | ↑          | X                        | X            | X        | L    | Set Right INT <sub>R</sub> Flag   |

| ↑         | X                        | X            | X        | X    | ↑          | H                        | L            | 7FFF     | H    | Reset Right INT <sub>R</sub> Flag |

| ↑         | X                        | X            | X        | L    | ↑          | L                        | L            | 7FFE     | X    | Set Left INT <sub>L</sub> Flag    |

| ↑         | H                        | L            | 7FFE     | H    | ↑          | X                        | X            | X        | X    | Reset Left INT <sub>L</sub> Flag  |

## NOTES:

1. INTL and INT<sub>R</sub> must be initialized at power-up by Resetting the flags.

2.  $\overline{CE}_0 = V_{IL}$  and  $CE_1 = V_{IH}$ . R/W and CE are synchronous with respect to the clock and need valid set-up and hold times.

3. Address is for internal register, not the external bus, i.e., address needs to be qualified by one of the Address counter control signals.

5678tbl12

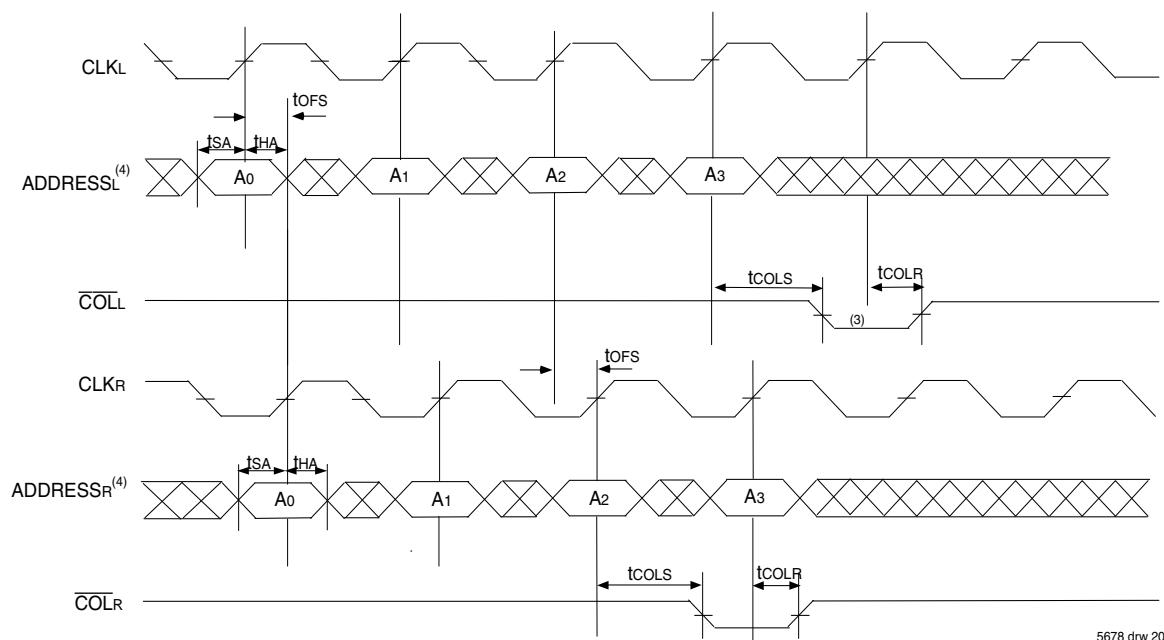

Waveform of Collision Timing<sup>(1,2)</sup>

## NOTES:

1.  $\overline{CE}_0 = V_{IL}$ ,  $CE_1 = V_{IH}$ .

2. For reading port,  $\overline{OE}$  is a Don't care on the Collision Detection Logic. Please refer to Truth Table IV for specific cases.

3. Leading Port Output flag might output  $3t_{CYC2} + t_{COLS}$  after Address match.

4. Address is for internal register, not the external bus, i.e., address needs to be qualified by one of the Address counter control signals.

Collision Detection Timing<sup>(3,4)</sup>

| Cycle Time | tOFS (ns)                    |                              |

|------------|------------------------------|------------------------------|

|            | Region 1 (ns) <sup>(1)</sup> | Region 2 (ns) <sup>(2)</sup> |

| 5ns        | 0 - 2.8                      | 2.81 - 4.6                   |

| 6ns        | 0 - 3.8                      | 3.81 - 5.6                   |

| 7.5ns      | 0 - 5.3                      | 5.31 - 7.1                   |

## NOTES:

1. Region 1

Both ports show collision after 2nd cycle for Addresses 0, 2, 4 etc.

2. Region 2

Leading port shows collision after 3rd cycle for addresses 0, 3, 6, etc.

while trailing port shows collision after 2nd cycle for addresses 0, 2, 4 etc.

3. All the production units are tested to midpoint of each region.

4. These ranges are based on characterization of a typical device.

5678 tbl 13

## Truth Table IV — Collision Detection Flag

| Left Port |                                 |                                |                                                  |      | Right Port |                                 |                                |                                                  |      | Function                                                                              |

|-----------|---------------------------------|--------------------------------|--------------------------------------------------|------|------------|---------------------------------|--------------------------------|--------------------------------------------------|------|---------------------------------------------------------------------------------------|

| CLKL      | R/W <sub>L</sub> <sup>(1)</sup> | CE <sub>L</sub> <sup>(1)</sup> | A <sub>18L</sub> -A <sub>0L</sub> <sup>(2)</sup> | COLL | CLKR       | R/W <sub>R</sub> <sup>(1)</sup> | CE <sub>R</sub> <sup>(1)</sup> | A <sub>18R</sub> -A <sub>0R</sub> <sup>(2)</sup> | COLR |                                                                                       |

| ↑         | H                               | L                              | MATCH                                            | H    | ↑          | H                               | L                              | MATCH                                            | H    | Both ports reading. Not a valid collision.<br>No flag output on either port.          |

| ↑         | H                               | L                              | MATCH                                            | L    | ↑          | L                               | L                              | MATCH                                            | H    | Left port reading, Right port writing.<br>Valid collision, flag output on Left port.  |

| ↑         | L                               | L                              | MATCH                                            | H    | ↑          | H                               | L                              | MATCH                                            | L    | Right port reading, Left port writing.<br>Valid collision, flag output on Right port. |

| ↑         | L                               | L                              | MATCH                                            | L    | ↑          | L                               | L                              | MATCH                                            | L    | Both ports writing. Valid collision. Flag output on both ports.                       |

5678 tbl 14

## NOTES:

1.  $\overline{CE}_0 = V_{IL}$  and  $CE_1 = V_{IH}$ . R/W and CE are synchronous with respect to the clock and need valid set-up and hold times.

2. Address is for internal register, not the external bus, i.e., address needs to be qualified by one of the Address counter control signals.

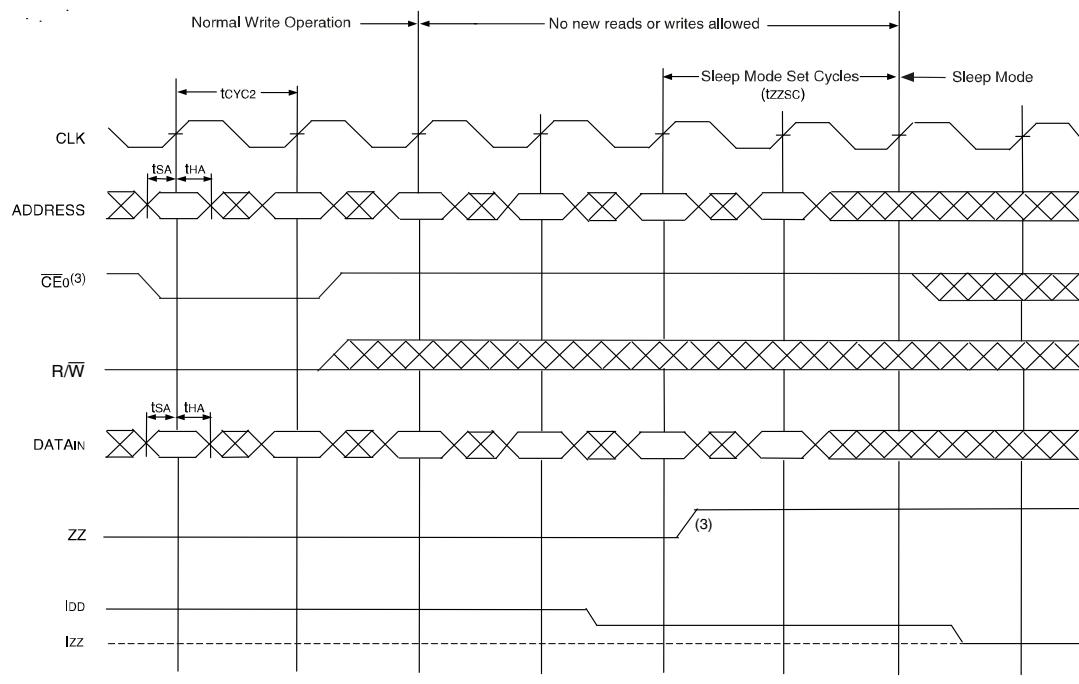

Timing Waveform - Entering Sleep Mode <sup>(1,2)</sup>Timing Waveform - Exiting Sleep Mode <sup>(1,2)</sup>

## NOTES:

1. CE1 = V<sub>IH</sub>.

2. All timing is same for Left and Right ports.

3. CE0 has to be deactivated (CE0 = V<sub>IH</sub>) three cycles prior to asserting ZZ (ZZx = V<sub>IH</sub>) and held for two cycles after asserting ZZ (ZZx = V<sub>IH</sub>).

4. CE0 has to be deactivated (CE0 = V<sub>IH</sub>) one cycle prior to de-asserting ZZ (ZZx = V<sub>IL</sub>) and held for three cycles after de-asserting ZZ (ZZx = V<sub>IL</sub>).

5. The device must be in Read Mode (R/W High) when exiting sleep mode. Outputs are active but data is not valid until the following cycle.

## Functional Description

The IDT70T3539M provides a true synchronous Dual-Port Static RAM interface. Registered inputs provide minimal set-up and hold times on address, data, and all critical control inputs. All internal registers are clocked on the rising edge of the clock signal, however, the self-timed internal write pulse width is independent of the cycle time.

An asynchronous output enable is provided to ease asynchronous bus interfacing. Counter enable inputs are also provided to stall the operation of the address counters for fast interleaved memory applications.

A HIGH on  $\overline{CE}_0$  or a LOW on  $CE_1$  for one clock cycle will power down the internal circuitry to reduce static power consumption. Multiple chip enables allow easier banking of multiple IDT70T3539Ms for depth expansion configurations. Two cycles are required with  $\overline{CE}_0$  LOW and  $CE_1$  HIGH to re-activate the outputs.

## Interrupts

If the user chooses the interrupt function, a memory location (mail box or message center) is assigned to each port. The left port interrupt flag ( $\overline{INT}_L$ ) is asserted when the right port writes to memory location 7FFF (HEX), where a write is defined as  $\overline{CE}_R = R/\overline{W}_R = V_{IL}$  per the Truth Table. The left port clears the interrupt through access of address location 7FFF when  $\overline{CE}_L = V_{IL}$  and  $R/\overline{W}_L = V_{IH}$ . Likewise, the right port interrupt flag ( $\overline{INT}_R$ ) is asserted when the left port writes to memory location 7FFF (HEX) and to clear the interrupt flag ( $\overline{INT}_R$ ), the right port must read the memory location 7FFF. The message (36 bits) at 7FFF or 7FFF is user-defined since it is an addressable SRAM location. If the interrupt function is not used, address locations 7FFF and 7FFF are not used as mail boxes, but as part of the random access memory. Refer to Truth Table III for the interrupt operation.

## Collision Detection

Collision is defined as an overlap in access between the two ports resulting in the potential for either reading or writing incorrect data to a specific address. For the specific cases: (a) Both ports reading - no data is corrupted, lost, or incorrectly output, so no collision flag is output on either port. (b) One port writing, the other port reading - the end result of the write will still be valid. However, the reading port might capture data that is in a state of transition and hence the reading port's collision flag is output. (c) Both ports writing - there is a risk that the two ports will interfere with each other, and the data stored in memory will not be a valid write from either port (it may essentially be a random combination of the two). Therefore, the collision flag is output on both ports. Please refer to Truth Table IV for all of the above cases.

The alert flag ( $\overline{COL}_x$ ) is asserted on the 2nd or 3rd rising clock edge of the affected port following the collision, and remains low for one cycle. Please refer to Collision Detection Timing Table on Page 19. During that next cycle, the internal arbitration is engaged in resetting the alert flag (this avoids a specific requirement on the part of the user to reset the alert flag). If two collisions occur on subsequent clock cycles, the second collision may not generate the appropriate alert flag. A third collision will generate the alert flag as appropriate. In the event that a user initiates a burst access on both ports with the

same starting address on both ports and one or both ports writing during each access (i.e., imposes a long string of collisions on contiguous clock cycles), the alert flag will be asserted and cleared every other cycle. Please refer to the Collision Detection timing waveform on Page 19.

Collision detection on the IDT70T3539M represents a significant advance in functionality over current sync multi-ports, which have no such capability. In addition to this functionality the IDT70T3539M sustains the key features of bandwidth and flexibility. The collision detection function is very useful in the case of bursting data, or a string of accesses made to sequential addresses, in that it indicates a problem within the burst, giving the user the option of either repeating the burst or continuing to watch the alert flag to see whether the number of collisions increases above an acceptable threshold value. Offering this function on chip also allows users to reduce their need for arbitration circuits, typically done in CPLD's or FPGA's. This reduces board space and design complexity, and gives the user more flexibility in developing a solution.

## Sleep Mode

The IDT70T3539M is equipped with an optional sleep or low power mode on both ports. The sleep mode pin on both ports is asynchronous and active high. During normal operation, the ZZ pin is pulled low. When ZZ is pulled high, the port will enter sleep mode where it will meet lowest possible power conditions. The sleep mode timing diagram shows the modes of operation: Normal Operation, No Read/Write Allowed and Sleep Mode.

For normal operation all inputs must meet setup and hold times prior to sleep and after recovering from sleep. Clocks must also meet cycle high and low times during these periods. Three cycles prior to asserting ZZ ( $ZZ_x = V_{IH}$ ) and three cycles after de-asserting ZZ ( $ZZ_x = V_{IL}$ ), the device must be disabled via the chip enable pins. If a write or read operation occurs during these periods, the memory array may be corrupted. Validity of data out from the RAM cannot be guaranteed immediately after ZZ is asserted (prior to being in sleep). When exiting sleep mode, the device must be in Read mode ( $R/\overline{W}_x = V_{IH}$ ) when chip enable is asserted, and the chip enable must be valid for one full cycle before a read will result in the output of valid data.

During sleep mode the RAM automatically deselects itself. The RAM disconnects its internal clock buffer. The external clock may continue to run without impacting the RAM's sleep current ( $I_{zz}$ ). All outputs will remain in high-Z state while in sleep mode. All inputs are allowed to toggle. The RAM will not be selected and will not perform any reads or writes.

## Depth and Width Expansion

The IDT70T3539M features dual chip enables (refer to Truth Table I) in order to facilitate rapid and simple depth expansion with no requirements for external logic. Figure 4 illustrates how to control the various chip enables in order to expand two devices in depth.

The IDT70T3539M can also be used in applications requiring expanded width, as indicated in Figure 4. Through combining the control signals, the devices can be grouped as necessary to accommodate applications needing 72-bits or wider.

Figure 4. Depth and Width Expansion with IDT70T3539M

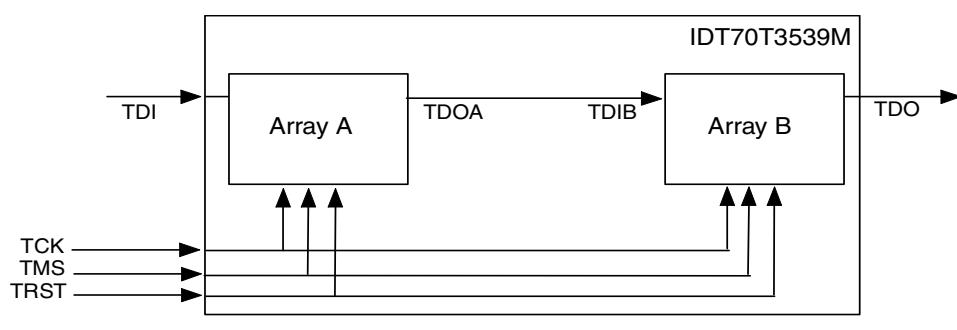

## JTAG Functionality and Configuration

The IDT70T3539M is composed of two independent memory arrays, and thus cannot be treated as a single JTAG device in the scan chain. The two arrays (A and B) each have identical characteristics and commands but must be treated as separate entities in JTAG operations. Please refer to Figure 5.

JTAG signaling must be provided serially to each array and utilize the information provided in the Identification Register Definitions, Scan

Register Sizes, and System Interface Parameter tables. Specifically, commands for Array B must precede those for Array A in any JTAG operations sent to the IDT70T3539M. Please reference Application Note AN-411, "JTAG Testing of Multichip Modules" for specific instructions on performing JTAG testing on the IDT70T3539M. AN-411 is available at [www.idt.com](http://www.idt.com).

Figure 5. I<sup>T</sup>AG Configuration for IDT70T3539M

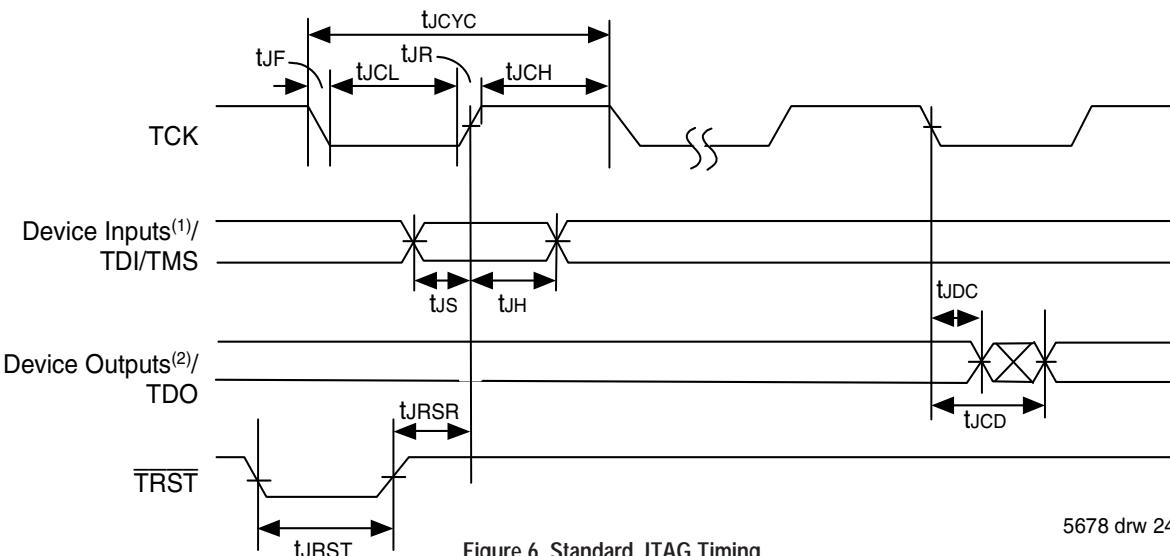

## JTAG Timing Specifications

5678 drw 24

Figure 6. Standard JTAG Timing

## NOTES:

1. Device inputs = All device inputs except TDI, TMS, and TRST.

2. Device outputs = All device outputs except TDO.

JTAG AC Electrical Characteristics<sup>(1,2,3,4)</sup>

| Symbol | Parameter               | 70T3539M |                  |       |

|--------|-------------------------|----------|------------------|-------|

|        |                         | Min.     | Max.             | Units |

| tJCYC  | JTAG Clock Input Period | 100      | —                | ns    |

| tJCH   | JTAG Clock HIGH         | 40       | —                | ns    |

| tJCL   | JTAG Clock Low          | 40       | —                | ns    |

| tJR    | JTAG Clock Rise Time    | —        | 3 <sup>(1)</sup> | ns    |

| tJF    | JTAG Clock Fall Time    | —        | 3 <sup>(1)</sup> | ns    |

| tJRST  | JTAG Reset              | 50       | —                | ns    |

| tJRSR  | JTAG Reset Recovery     | 50       | —                | ns    |

| tJCD   | JTAG Data Output        | —        | 25               | ns    |

| tJDC   | JTAG Data Output Hold   | 0        | —                | ns    |

| tJS    | JTAG Setup              | 15       | —                | ns    |

| tJH    | JTAG Hold               | 15       | —                | ns    |

5678 tbl 15

## NOTES:

1. Guaranteed by design.

2. 30pF loading on external output signals.

3. Refer to AC Electrical Test Conditions stated earlier in this document.

4. JTAG operations occur at one speed (10MHz). The base device may run at any speed specified in this datasheet.

## Identification Register Definitions

| Instruction Field Array B         | Value Array B | Instruction Field Array A          | Value Array A | Description                                          |

|-----------------------------------|---------------|------------------------------------|---------------|------------------------------------------------------|

| Revision Number (31:28)           | 0x0           | Revision Number (63:60)            | 0x0           | Reserved for Version number                          |

| IDT Device ID (27:12)             | 0x333         | IDT Device ID (59:44)              | 0x333         | Defines IDT Part number                              |

| IDT JEDEC ID (11:1)               | 0x33          | IDT JEDEC ID (43:33)               | 0x33          | Allows unique identification of device vendor as IDT |

| ID Register Indicator Bit (Bit 0) | 1             | ID Register Indicator Bit (Bit 32) | 1             | Indicates the presence of an ID Register             |

5678tbl 16

## Scan Register Sizes

| Register Name        | Bit Size Array A | Bit Size Array B | Bit Size 70T3539M |

|----------------------|------------------|------------------|-------------------|

| Instruction (IR)     | 4                | 4                | 8                 |

| Bypass (BYR)         | 1                | 1                | 2                 |

| Identification (IDR) | 32               | 32               | 64                |

| Boundary Scan (BSR)  | Note (3)         | Note (3)         | Note (3)          |

5678tbl 17

## System Interface Parameters

| Instruction    | Code                                                                 | Description                                                                                                                                                                                                                                                                      |

|----------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTEST         | 0000000                                                              | Forces contents of the boundary scan cells onto the device outputs <sup>(1)</sup> . Places the boundary scan register (BSR) between TDI and TDO.                                                                                                                                 |

| BYPASS         | 1111111                                                              | Places the bypass register (BYR) between TDI and TDO.                                                                                                                                                                                                                            |

| IDCODE         | 00100010                                                             | Loads the ID register (IDR) with the vendor ID code and places the register between TDI and TDO.                                                                                                                                                                                 |

| HIGHZ          | 01000100                                                             | Places the bypass register (BYR) between TDI and TDO. Forces all device output drivers except INT <sub>x</sub> and COL <sub>x</sub> to a High-Z state.                                                                                                                           |

| CLAMP          | 00110011                                                             | Uses BYR. Forces contents of the boundary scan cells onto the device outputs. Places the bypass register (BYR) between TDI and TDO.                                                                                                                                              |

| SAMPLE/PRELOAD | 00010001                                                             | Places the boundary scan register (BSR) between TDI and TDO. SAMPLE allows data from device inputs <sup>(2)</sup> to be captured in the boundary scan cells and shifted serially through TDO. PRELOAD allows data to be input serially into the boundary scan cells via the TDI. |

| RESERVED       | 01010101, 01110111, 10001000, 10011001, 10101010, 10111011, 11001100 | Several combinations are reserved. Do not use codes other than those identified above.                                                                                                                                                                                           |