# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# H8SX Family

Using the DMAC to Drive Continuous SCI Transmission in Clock Synchronous Mode

### Introduction

Clock synchronous transfer is used to transmit 128 bytes of data. Using the DMAC to handle the transfer (transmission) of data enables continuous transmission with no CPU intervention.

### **Target Device**

H8SX/1653

### Contents

| 1. | Specification                  | . 2 |

|----|--------------------------------|-----|

| 2. | Applicable Conditions          | . 2 |

| 3. | Description of Modules Used    | . 3 |

| 4. | Principles of Operation        | . 7 |

| 5. | Description of Software        | 11  |

| 6. | Documents for Reference (Note) | 25  |

### 1. Specification

Clock synchronous transfer is used to transmit 128 bytes of data. Using the DMAC to handle the transfer (transmission) of data enables continuous transmission with no CPU intervention.

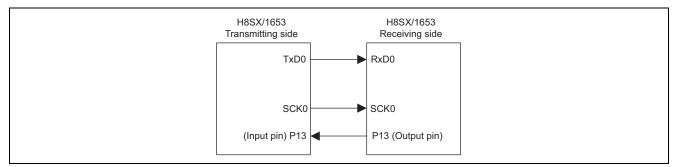

- An example of connection for this sample task is shown in figure 1.

- Table 1 shows the communications format.

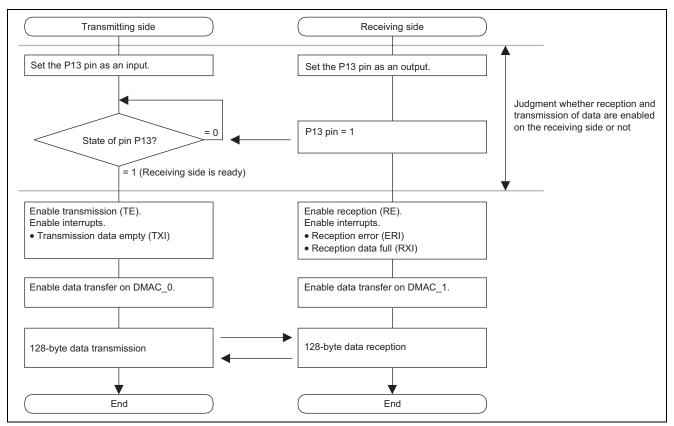

- After a power-on reset of the transmitting side, the SCI and DMAC modules are set up and the state of pin P13 is polled. When the P13 pin is a high level, the transmitting side judges the transfer is enabled at the receiving side, after which operations for the clock synchronous transmission of 128 bytes of data proceed.

- After a power-on reset of the receiving side, the SCI and DMAC functions are set up. The same side outputs a highlevel signal on pin P13, after which operations for the clock synchronous reception of 128 bytes of data proceed in synchronization with the transmitting-side clock input on pin SCK.

In this sample task, the DMAC modules on each side are interrupt-activated to handle consecutive transmission of the 128 bytes of data.

Figure 1 Clock Synchronous Serial Transmission

#### Table 1 Format for Clock Synchronous Serial Transmission

| Format                            | Setting           |

|-----------------------------------|-------------------|

| Ρφ                                | 32 MHz            |

| Serial communications mode        | Clock synchronous |

| Clock source                      | Internal clock    |

| Transfer rate                     | 250 kbps          |

| Data length                       | 8 bits            |

| Serial/parallel conversion format | LSB first         |

### 2. Applicable Conditions

#### Table 2 Applicable Conditions

| Item                                                | Description              |                                            |

|-----------------------------------------------------|--------------------------|--------------------------------------------|

| Operating frequency                                 | Input clock              | :16 MHz                                    |

|                                                     | System clock (I          | :32 MHz (input clock frequency $\times$ 2) |

|                                                     | Peripheral mode clock (P | :32 MHz (input clock frequency $	imes$ 2)  |

|                                                     | External bus clock (Bø)  | :32 MHz (input clock frequency $\times$ 2) |

| Mode of operation Mode 6 (MD2 = 1, MD1 = 1, MD0 = 0 |                          | $MD0 = 0, MD_CLK = 0)$                     |

### 3. Description of Modules Used

### 3.1 Description in Outline

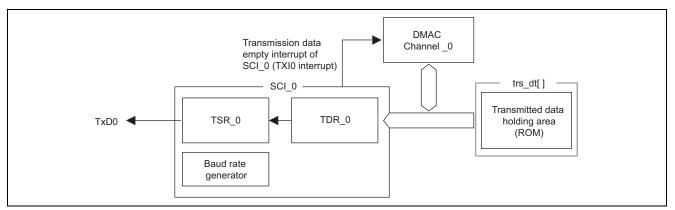

Peripheral modules of the H8SX/1653 which are used in this sample task are shown in Figure 2.

Figure 2 Functions of the H8SX/1653

The description which concerns the blocks shown in figure 2 is stated below.

1. SCI\_0

Transmits data with timing provided by the clock synchronous communications.

- When TSR\_0 is not full, data for transmission are written to TDR\_0, transferred to TSR\_0, and then output on the TxD0 pin.

- When the data are transferred from TDR\_0 to TSR\_0, a transmission data empty interrupt (TXI0 interrupt) from SCI\_0 is generated.

- 2. DMAC channel 0

- Channel 0 is activated by the transmission data empty interrupt (TXI0 interrupt) from SCI\_0 and transfers data from the area where data for transmission are stored to the TDR\_0 register.

### 3.2 Description of SCI\_0

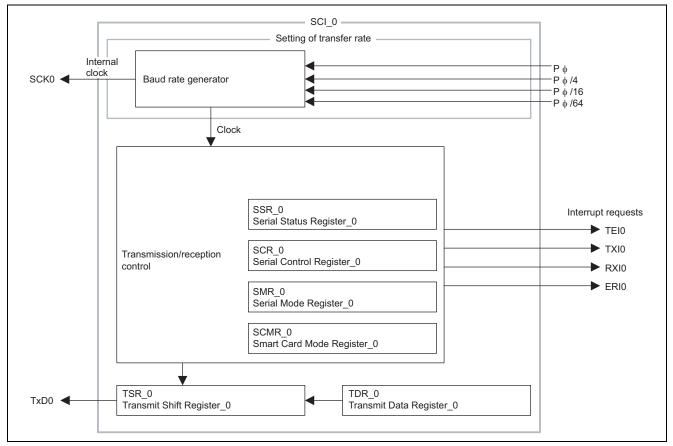

In this sample task, SCI\_0 is used for clock synchronous serial data transmission. Figure 3 is a block diagram of SCI\_0.

Figure 3 Block Diagram of SCI\_0

The description which concerns the blocks shown in figure 3 is stated below.

- On-chip peripheral clock P¢ This is the base clock for the operation of on-chip peripheral functions and is generated by a clock oscillator.

- Transmit shift register\_0 (TSR\_0) TSR\_0 is used to transmit serial data. In transmission, data are transferred from the transmit data register (TDR\_0) to TSR\_0, and then output on the TxD0 pin. TSR\_0 is not directly accessible from the CPU.

- Transmit data register\_0 (TDR\_0) TDR\_0 is an 8-bit register and used to store data for transmission. When SCI\_0 detects that TSR\_0 is empty, data that have been written to TDR\_0 are automatically transferred to TSR\_0. Since TDR\_0 and TSR\_0 function as a double buffer, if the next data for transmission has already been written to TDR\_0 when one frame of data is transmitted, the written data are transferred to TSR\_0. This allows continual transmission. Although TDR\_0 can be read from or written to by the CPU at all times, only write data for transmission data after having confirmed setting of the TDRE bit in the serial status register (SSR\_0) to 1.

- Serial mode register\_0 (SMR\_0) SMR\_0 is an 8-bit register and used to select the format of serial data communications and the clock source for the on-chip baud-rate generator.

- Serial control register\_0 (SCR\_0) SCR\_0 is used to control transmission, reception, and interrupts, and to select the clock source for transmission and reception.

- Serial status register\_0 (SSR\_0) SSR\_0 consists of status flags for SCI\_0 and multiprocessor bits for transmission and reception. TDRE, RDRF, ORER, PER, and FER can only be cleared.

- Smart card mode register\_0 (SCMR\_0) SCMR\_0 is used to select the smart-card or normal interface mode for SCMR\_0, and to set up the format for the smart-card mode. For this task, the setting in SCMR\_0 selects the normal asynchronous or clock synchronous mode.

- Bit rate register\_0 (BRR\_0) BRR\_0 is an 8-bit register that is used to adjust the bit rate.

### 3.3 Channel 0 of the DMAC

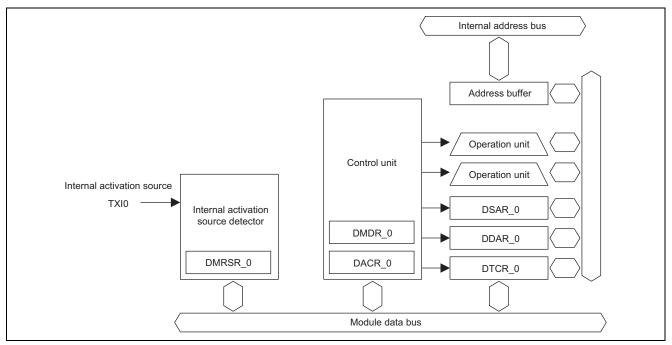

In this sample task, DMAC channel 0 is activated by the TXI0 interrupt of SCI\_0. A block diagram of the DMAC is given in figure 4.

Figure 4 Block Diagram of the DMAC

The description with reference to figure 4 is stated below.

• DMA source address register \_0 (DSAR\_0)

DSAR\_0 is a 32-bit readable/writable register and specifies the source address for the transfer. The register is equipped with an address-updating function, so the source address is updated to that for the next transfer each time a transfer operation takes place.

• DMA destination address register \_0 (DDAR\_0)

DDAR\_0 is a 32-bit readable/writable register and specifies the destination address for the transfer. This register is equipped with an address-updating function, so the destination address is updated to that for the next transfer each time a transfer operation takes place.

• DMA transfer count register \_0 (DTCR\_0)

DTCR\_0 is a 32-bit readable/writable register and specifies the amount of data to be transferred (total size for transfer). After data transfer operation, the value is reduced by the amount that corresponds to the transferred amount of data. In this sample task, the register is set for 128 bytes of data, and the byte is selected as the unit of data access. One is subtracted from the value on DMAC operation, to indicate the amount still to be transferred.

- DMA mode control register \_0 (DMDR\_0) DMDR\_0 controls DMAC operation.

- DMA address control register\_0 (DACR\_0) DACR\_0 sets the operating mode and transfer method.

- DMA module request select register\_0 (DMRSR\_0) DMRSR\_0 sets the activation source.

### 4. Principles of Operation

### 4.1 Outline

An outline of operation for this sample task is given in figure 5. 128-byte blocks of data are simultaneously transferred in both directions between the transmitting and receiving sides.

Figure 5 Outline of Operation

### 4.2 Transmission

#### 4.2.1 Transmission Start

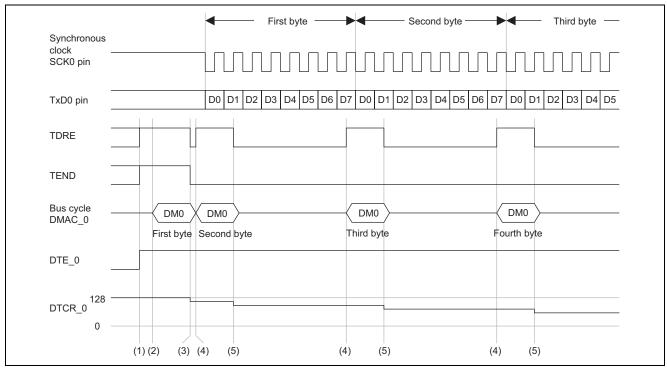

The timing of transmission start operations is illustrated in figure 6. Table 3 is a list of the hardware and software processing at the numbered points in figure 6.

Figure 6 Timing of Transmission Start

#### Table 3 Processing

|     | Hardv                                                                                                                             | vare Processing                                                                                                        | Software Processing |

|-----|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------|

| (1) | Powe                                                                                                                              | r-on reset                                                                                                             | Initial settings*   |

| (2) | <ul> <li>Activate DMAC_0, and transfers data for<br/>transmission from the transmitted data<br/>holding area to TDR_0.</li> </ul> |                                                                                                                        | No processing       |

| (3) | a.                                                                                                                                | Clear TDRE to 0.                                                                                                       | No processing       |

|     | b.                                                                                                                                | DTCR_0 counts down.                                                                                                    |                     |

|     | с.                                                                                                                                | Transfer the contents of TDR_0 to TSR_0.                                                                               |                     |

| (4) | a.                                                                                                                                | Set TDRE to 1.                                                                                                         | No processing       |

|     | b.                                                                                                                                | Activate DMAC_0 by TXI interrupt, and transfers data for transmission from the transmitted data holding area to TDR_0. |                     |

|     | C.                                                                                                                                | Output the contents of data of TSR_0 on pin TxD0.                                                                      |                     |

| (5) | a.                                                                                                                                | Clear TDRE to 0.                                                                                                       | No processing       |

|     | b.                                                                                                                                | DTCR_0 counts down.                                                                                                    |                     |

|     | C.                                                                                                                                | Transfer the contents of TDR_0 to TSR_0.                                                                               |                     |

#### Notes: \*Initial settings

DMAC\_0 settings

a. Source for activation: TXI0 interrupt. The flag (TDRE) fro the TXI0 interrupt source is cleared on completion of the DMA transfer.

- b. Source address: First address of the area where the data for transmission are stored. Incrementation is selected as the address incrementation or decrementation setting.

- c. Destination address: Address of TDR\_0. Fixed address is selected as the address incrementation or decrementation setting.

- d. Total amount of transfer: 128 bytes

- e. DMA data transfer is enabled ( $DTE_0 = 1$ ).

### SCR\_0 settings

- a. Clock synchronous mode. When  $P\phi = 32$  MHz, set the transfer rate to 250 kbps.

- b. TXI0 interrupt requests are enabled.

- c. Set SCI\_0 to enable transmit operations.

### 4.2.2 Transmission End

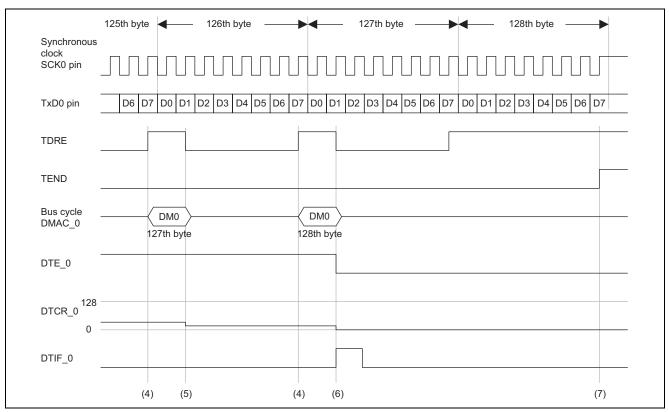

The timing of end of transmission operations is illustrated in figure 7. Table 4 is a list of the hardware and software processing at the numbered points in figure 7.

Figure 7 Timing of Transmission End

#### Table 4 Processing

|     | Hardy                 | ware Processing                           | Software Processing                                       |

|-----|-----------------------|-------------------------------------------|-----------------------------------------------------------|

| (4) | (4) a. Set TDRE to 1. |                                           | No processing                                             |

|     | b.                    | Activate DMAC_0 by TXI0 interrupt, and    |                                                           |

|     |                       | transfers data for transmission from the  |                                                           |

|     |                       | transmitted data holding area to TDR_0.   |                                                           |

|     | с.                    | Output the contents of TSR_0 on pin TxD0. |                                                           |

| (5) | a.                    | Clear TDRE to 0.                          | No processing                                             |

|     | b.                    | DTCR_0 counts down.                       |                                                           |

|     | с.                    | Transfer the contents of TDR_0 to TSR_0.  |                                                           |

| (6) | a.                    | Clear TDRE to 0.                          | DMAC_0 transfer end interrupt                             |

|     | b.                    | $DTCR_0$ ( $DTCR_0 = 0$ ) counts down.    | a. Disable interrupt request.                             |

|     | с.                    | Transfer the contents of TDR_0 to TSR_0.  | b. Disable DMAC_0 transfer end interrupt                  |

|     |                       |                                           | requests.                                                 |

| (7) | a.                    | Set TEND to 1.                            | TEI0 Interrupt                                            |

|     |                       |                                           | <ul> <li>a. Stop SCI_0 transmission operations</li> </ul> |

|     |                       |                                           | (TE = 0).                                                 |

|     |                       |                                           | b. Disable TEI0 interrupt requests.                       |

### 5. Description of Software

### 5.1 **Operating Environment**

### Table 5 Operating Environment

| Item                                                                                 | Details                                        |

|--------------------------------------------------------------------------------------|------------------------------------------------|

| Development tool High-performance Embedded Workshop Ver.4.01.01                      |                                                |

| C/C++ compiler H8S, H8/300 Series C/C++ Compiler Ver.6.01.02                         |                                                |

|                                                                                      | (manufactured by Renesas Technology)           |

| Compiler options -cpu = h8sxa:24:md, -code = machinecode, -optimize = 1, -regparam = |                                                |

|                                                                                      | -speed = (register, shift, struct, expression) |

#### Table 6 Section Setting

| Address  | Section Name | Description                          |

|----------|--------------|--------------------------------------|

| H'001000 | Р            | Program area                         |

|          | С            | Constant area                        |

| H'FF2000 | В            | Non-initialized data area (RAM area) |

#### Table 7 Vector Table for Interrupt Exception Handling

| Exception Handling Source |         | Vector No. | Vector Address | Function to Interrupt Destination |

|---------------------------|---------|------------|----------------|-----------------------------------|

| Reset                     |         | 0          | H'000000       | init                              |

| DMAC_0                    | DMTEND0 | 128        | H'000200       | dmtend0_int                       |

| SCI_0                     | TEI0    | 147        | H'00024C       | tei0_int                          |

### 5.2 List of Functions

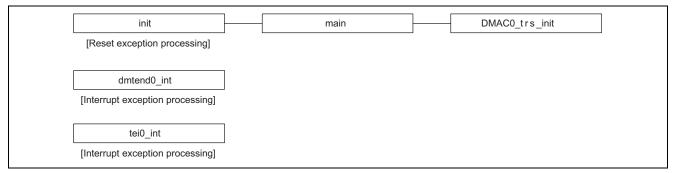

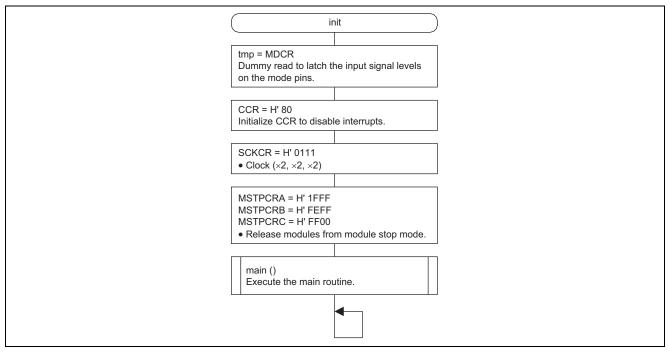

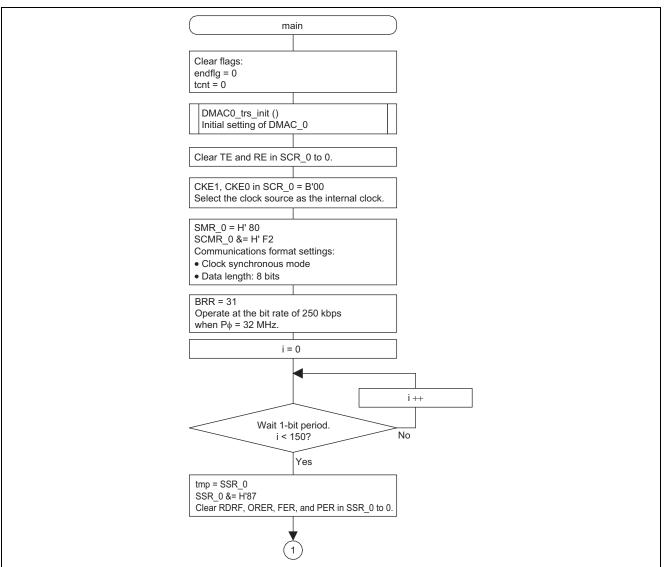

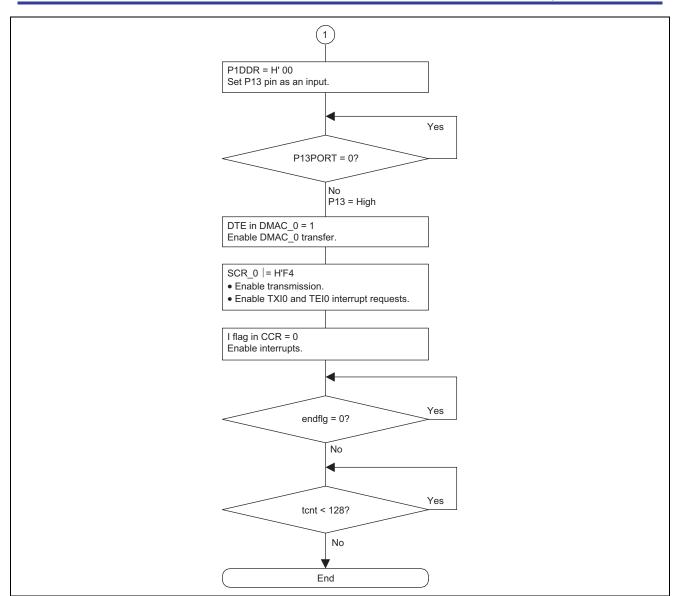

Table 8 lists the functions used in this sample task. Figure 8 shows the structure of hierarchy.

#### Table 8 List of Functions

| Function Name  | Description                                                                          |

|----------------|--------------------------------------------------------------------------------------|

| init           | Initialization routine:                                                              |

|                | Takes the chip out of module stop mode, performs clock settings, and calls the main  |

|                | function.                                                                            |

| main           | Main routine                                                                         |

|                | Selects clock synchronous SCI. Calls the DMAC0_trs_init function. Judges input of    |

|                | high-level signal on pin P13. Makes settings for transmission of 128 bytes of data.  |

| DMAC0_trs_init | DMAC_0 initialization                                                                |

|                | Selects TXI0-interrupt-triggered processing of transfer from the area where data for |

|                | transmission are stored to TDR_0.                                                    |

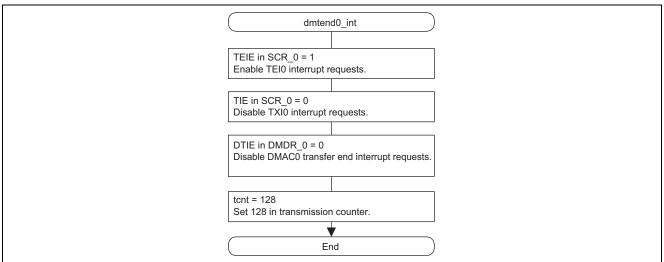

| dmtend0_int    | DMAC_0 transfer end interrupt                                                        |

|                | Sets TEI0 interrupt request enabled, TXI0 interrupt and DMAC_0 transfer end          |

|                | interrupt requests disabled.                                                         |

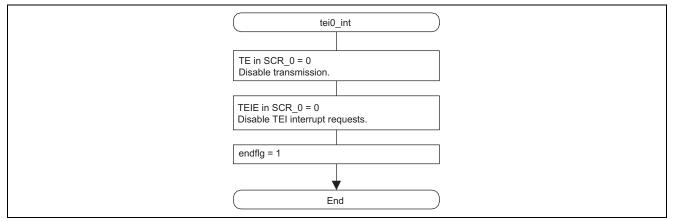

| tei0_int       | Transmission end interrupt                                                           |

|                | Sets SCI_0 transmission and TEI0 interrupt requests disabled.                        |

#### Figure 8 Hierarchy of Calls in the User Program

### 5.3 RAM Usage

#### Table 9 RAM Usage

| Туре          | Variable Name | Description                 | Used in           |

|---------------|---------------|-----------------------------|-------------------|

| unsigned char | endflg        | Transmission end flag       | main, tei0_int    |

|               |               | 0: Transmission in progress |                   |

|               |               | 1: Transmission ended       |                   |

| unsigned char | tcnt          | Transmission counter        | main, dmtend0_int |

### 5.4 Constant

### Table 10 Constants

| Туре          | Variable Name | Setting                           | Description                         | Used in                 |

|---------------|---------------|-----------------------------------|-------------------------------------|-------------------------|

| unsigned char | trs_dt[128]   | H'00, H'01, H'02, …<br>H'7E, H'7F | Transmitted data holding area (ROM) | main,<br>DMAC0_trs_init |

### 5.5 Symbolic Constants

Table 11

Symbolic Constants

| Constant Name | Setting | Description                               |

|---------------|---------|-------------------------------------------|

| NUM           | 128     | Sets the number of data for transmission. |

### 5.6 Description of Functions

#### 5.6.1 init Function

- Functional overview

Initialization routine which releases the required modules from module stop mode, makes clock settings, and calls the main function.

- 2. Argument None

- 3. Return value None

- 4. Description of internal registers used

The internal registers used in this sample task are described below. The settings shown in these tables are the values used in this sample task and differ from the initial values.

• Mode control register (MDCR) Number of bits: 16 Address: H'FFFDC0

| Bit | Bit Name | Setting    | R/W | Description                                                   |

|-----|----------|------------|-----|---------------------------------------------------------------|

| 15  | MDS7     | Undefined* | R   | Indicates the value set by a mode pin (MD3).                  |

|     |          |            |     | When MDCR is read, the input level on the MD3 pin is          |

|     |          |            |     | latched. This latching is released by a reset.                |

| 11  | MDS3     | Undefined* | R   | Mode Select 3 to 0                                            |

| 10  | MDS2     | Undefined* | R   | These bits indicate the operating mode selected by the        |

| 9   | MDS1     | Undefined* | R   | mode pins (MD2 to MD0) (see table 12). When MDCR is           |

| 8   | MDS0     | Undefined* | R   | read, the signal levels input on pins MD2 to MD0 are          |

|     |          |            |     | latched into these bits. The latches are released by a reset. |

Note: \* Determined by the settings on pins MD3 to MD0.

#### Table 12 Settings of Bits MDS3 to MDS0

| MCU            | Mode Pi | ns  |     | MDCR | MDCR |      |      |  |

|----------------|---------|-----|-----|------|------|------|------|--|

| Operating Mode | MD2     | MD1 | MD0 | MDS3 | MDS2 | MDS1 | MDS0 |  |

| 2              | 0       | 1   | 0   | 1    | 1    | 0    | 0    |  |

| 4              | 1       | 0   | 0   | 0    | 0    | 1    | 0    |  |

| 5              | 1       | 0   | 1   | 0    | 0    | 0    | 1    |  |

| 6              | 1       | 1   | 0   | 0    | 1    | 0    | 1    |  |

| 7              | 1       | 1   | 1   | 0    | 1    | 0    | 0    |  |

| Bit | Bit Name | Setting | R/W | Description                                                 |

|-----|----------|---------|-----|-------------------------------------------------------------|

| 10  | ICK2     | 0       | R/W | System Clock (I                                             |

| 9   | ICK1     | 0       | R/W | These bits select the frequency of the system clock signal, |

| 8   | ICK0     | 1       | R/W | which is provided to the CPU, DMAC, and DTC.                |

|     |          |         |     | 001: Input clock $\times$ 2                                 |

| 6   | PCK2     | 0       | R/W | Peripheral Module Clock (P                                  |

| 5   | PCK1     | 0       | R/W | These bits select the frequency of the peripheral module    |

| 4   | PCK0     | 1       | R/W | clock.                                                      |

|     |          |         |     | 001: Input clock $\times$ 2                                 |

| 2   | BCK2     | 0       | R/W | External Bus Clock (B                                       |

| 1   | BCK1     | 0       | R/W | These bits select the frequency of the external bus clock.  |

| 0   | BCK0     | 1       | R/W | 001: Input clock × 2                                        |

• MSTPCRA, MSTPCRB, and MSTPCRC control module stop mode. Setting a bit to 1 places the corresponding module in module stop mode, while clearing the bit to 0 releases the module from module stop mode.

| • Mo | dule stop contro | l register A (MS | STPCRA) | Number of bits: 16 Address: H'FFFDC8                                                                                                                                                                                                                                                                       |

|------|------------------|------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit  | Bit Name         | Setting          | R/W     | Description                                                                                                                                                                                                                                                                                                |

| 15   | ACSE             | 0                | R/W     | All-Module-Clock-Stop Mode Enable                                                                                                                                                                                                                                                                          |

|      |                  |                  |         | This bit enables/disables all-module-clock-stop mode for<br>reducing current consumption by stopping the bus<br>controller and I/O port operation when the CPU executes<br>the SLEEP instruction after module stop mode has been<br>set for all of the on-chip peripheral modules controlled by<br>MSTPCR. |

|      |                  |                  |         | 0: All-module-clock-stop mode disabled                                                                                                                                                                                                                                                                     |

|      |                  |                  |         | 1: All-module-clock-stop mode enabled                                                                                                                                                                                                                                                                      |

| 13   | MSTPA13          | 0                | R/W     | DMA controller (DMAC)                                                                                                                                                                                                                                                                                      |

| 12   | MSTPA12          | 1                | R/W     | Data transfer controller (DTC)                                                                                                                                                                                                                                                                             |

| 9    | MSTPA9           | 1                | R/W     | 8-bit timer unit (TMR_3, TMR_2)                                                                                                                                                                                                                                                                            |

| 8    | MSTPA8           | 1                | R/W     | 8-bit timer unit (TMR_1, TMR_0)                                                                                                                                                                                                                                                                            |

| 5    | MSTPA5           | 1                | R/W     | D/A converter (channels 1 and 0)                                                                                                                                                                                                                                                                           |

| 3    | MSTPA3           | 1                | R/W     | A/D converter (unit 0)                                                                                                                                                                                                                                                                                     |

| 0    | MSTPA0           | 1                | R/W     | 16-bit timer pulse unit (TPU channels 5 to 0)                                                                                                                                                                                                                                                              |

• Module stop control register B (MSTPCRB) Number of bits: 16 Address: H'FFFDCA

| Bit | Bit Name | Setting | R/W | Description                               |  |

|-----|----------|---------|-----|-------------------------------------------|--|

| 15  | MSTPB15  | 1       | R/W | Programmable pulse generator (PPG)        |  |

| 12  | MSTPB12  | 1       | R/W | Serial communications interface_4 (SCI_4) |  |

| 10  | MSTPB10  | 1       | R/W | Serial communications interface_2 (SCI_2) |  |

| 9   | MSTPB9   | 1       | R/W | Serial communications interface_1 (SCI_1) |  |

| 8   | MSTPB8   | 0       | R/W | Serial communications interface_0 (SCI_0) |  |

| 7   | MSTPB7   | 1       | R/W | I <sup>2</sup> C bus interface_1 (IIC_1)  |  |

| 6   | MSTPB6   | 1       | R/W | I <sup>2</sup> C bus interface_0 (IIC_0)  |  |

|     |          |         |     |                                           |  |

| • M | • Module stop control register C (MSTPCRC) |            |   | Number of bits: 16 Address: H'FFFDCC              |

|-----|--------------------------------------------|------------|---|---------------------------------------------------|

| Bit | Bit Name                                   | Setting R/ | W | Description                                       |

| 15  | MSTPC15                                    | 1 R/       | W | Serial communications interface_5 (SCI_5), (IrDA) |

| 14  | MSTPC14                                    | 1 R/       | W | Serial communications interface_6 (SCI_6)         |

| 13  | MSTPC13                                    | 1 R/       | W | 8-bit timer unit (TMR_4, TMR_5)                   |

| 12  | MSTPC12                                    | 1 R/       | W | 8-bit timer unit (TMR_6, TMR_7)                   |

| 11  | MSTPC11                                    | 1 R/       | W | Universal serial bus interface (USB)              |

| 10  | MSTPC10                                    | 1 R/       | W | Cyclic redundancy check module                    |

| 4   | MSTPC4                                     | 0 R/       | W | On-chip RAM_4 (H'FF2000 to H'FF3FFF)              |

| 3   | MSTPC3                                     | 0 R/       | W | On-chip RAM_3 (H'FF4000 to H'FF5FFF)              |

| 2   | MSTPC2                                     | 0 R/       | W | On-chip RAM_2 (H'FF6000 to H'FF7FFF)              |

| 1   | MSTPC1                                     | 0 R/       | W | On-chip RAM_1 (H'FF8000 to H'FF9FFF)              |

| 0   | MSTPC0                                     | 0 R/       | W | On-chip RAM_0 (H'FFA000 to H'FFBFFF)              |

#### 5.6.2 main Function

#### 1. Functional overview

Main routine: Sets the clock synchronous SCI, calls the DMAC0\_trs\_init function, judges input of high-level signal on pin P13, and sets transmission of 128 byte-data.

- 2. Argument None

- 3. Return value None

- 4. Description of internal registers used

The internal registers used in this sample task are described below. The settings shown in these tables are the values used in this sample task and differ from the initial values.

| Bit               | Bit Name                                     | Setting                                       | R/W                           | Description                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------|----------------------------------------------|-----------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3                 | P13DDR                                       | 0                                             | W                             | 0: Sets pin P13 as an input.                                                                                                                                                                                                                                                                                                                                                                          |

| 5                 | TISEDIK                                      | 0                                             | vv                            | 1: Sets pin P13 as an output.                                                                                                                                                                                                                                                                                                                                                                         |

|                   |                                              |                                               |                               |                                                                                                                                                                                                                                                                                                                                                                                                       |

| • DN              | IA mode control                              | l register_0 (DM                              | DR 0) N                       | Jumber of bits: 32 Address: H'FFFC14                                                                                                                                                                                                                                                                                                                                                                  |

| Bit               | Bit Name                                     | Setting                                       | R/W                           | Description                                                                                                                                                                                                                                                                                                                                                                                           |

| 31                | DTE                                          | 1                                             | R/W                           | Data Transfer Enable                                                                                                                                                                                                                                                                                                                                                                                  |

|                   |                                              |                                               |                               | 0: Disables data transfer.                                                                                                                                                                                                                                                                                                                                                                            |

|                   |                                              |                                               |                               | 1: Enables data transfer.                                                                                                                                                                                                                                                                                                                                                                             |

|                   |                                              |                                               |                               |                                                                                                                                                                                                                                                                                                                                                                                                       |

| • Por             | rt 1 register (POI                           | RT1) Number                                   | of bits: 8                    | Address: H'FFFF40                                                                                                                                                                                                                                                                                                                                                                                     |

| Bit               | Bit Name                                     | Setting                                       | R/W                           | Description                                                                                                                                                                                                                                                                                                                                                                                           |

|                   |                                              |                                               |                               |                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3                 | P13PORT                                      | Undefined                                     | R                             | 0: Pin P13 is set to a high level.                                                                                                                                                                                                                                                                                                                                                                    |

| 3                 | P13PORT                                      | Undefined                                     | R                             | 0: Pin P13 is set to a high level.<br>1: Pin P13 is set to a low level.                                                                                                                                                                                                                                                                                                                               |

| 3                 | P13PORT                                      | Undefined                                     | R                             | 5                                                                                                                                                                                                                                                                                                                                                                                                     |

| -                 |                                              |                                               |                               | 5                                                                                                                                                                                                                                                                                                                                                                                                     |

| • Sei             |                                              | Undefined<br>I register_0 (SMI<br>Setting     |                               | 1: Pin P13 is set to a low level.                                                                                                                                                                                                                                                                                                                                                                     |

| • Sei<br>Bit      | rial mode control                            | l register_0 (SMI                             | R_0) Nur                      | 1: Pin P13 is set to a low level.<br>nber of bits: 8 Address: H'FFFF80                                                                                                                                                                                                                                                                                                                                |

| • Sei<br>Bit      | rial mode control<br>Bit Name                | l register_0 (SMF<br>Setting                  | R_0) Nur<br><b>R/W</b>        | 1: Pin P13 is set to a low level.<br>nber of bits: 8 Address: H'FFFF80<br>Description<br>Communication Mode                                                                                                                                                                                                                                                                                           |

| • Sei<br>Bit      | rial mode control<br>Bit Name                | l register_0 (SMF<br>Setting                  | R_0) Nur<br><b>R/W</b>        | 1: Pin P13 is set to a low level.<br>mber of bits: 8 Address: H'FFFF80<br>Description<br>Communication Mode<br>0: Asynchronous                                                                                                                                                                                                                                                                        |

| • Ser<br>Bit<br>7 | rial mode control<br>Bit Name<br>C/A         | l register_0 (SMI<br><b>Setting</b><br>1      | R_0) Nur<br><b>R/W</b><br>R/W | 1: Pin P13 is set to a low level.<br>mber of bits: 8 Address: H'FFFF80<br>Description<br>Communication Mode<br>0: Asynchronous<br>1: Clock synchronous                                                                                                                                                                                                                                                |

| • Ser<br>Bit<br>7 | rial mode control<br>Bit Name<br>C/A<br>CKS1 | l register_0 (SMF<br><b>Setting</b><br>1<br>0 | R_0) Nur<br><b>R/W</b><br>R/W | 1: Pin P13 is set to a low level.<br>mber of bits: 8 Address: H'FFFF80<br>Description<br>Communication Mode<br>0: Asynchronous<br>1: Clock synchronous<br>Clock Select 1, 0                                                                                                                                                                                                                           |

| • Ser<br>Bit<br>7 | rial mode control<br>Bit Name<br>C/A         | l register_0 (SMI<br><b>Setting</b><br>1      | R_0) Nur<br><b>R/W</b><br>R/W | 1: Pin P13 is set to a low level.<br>mber of bits: 8 Address: H'FFFF80<br>Description<br>Communication Mode<br>0: Asynchronous<br>1: Clock synchronous<br>Clock Select 1, 0<br>These bits select the clock source for the baud rate                                                                                                                                                                   |

| -                 | rial mode control<br>Bit Name<br>C/A<br>CKS1 | l register_0 (SMF<br><b>Setting</b><br>1<br>0 | R_0) Nur<br><b>R/W</b><br>R/W | 1: Pin P13 is set to a low level.<br>mber of bits: 8 Address: H'FFFF80<br>Description<br>Communication Mode<br>0: Asynchronous<br>1: Clock synchronous<br>Clock Select 1, 0<br>These bits select the clock source for the baud rate<br>generator.                                                                                                                                                     |

| • Ser<br>Bit<br>7 | rial mode control<br>Bit Name<br>C/A<br>CKS1 | l register_0 (SMF<br><b>Setting</b><br>1<br>0 | R_0) Nur<br><b>R/W</b><br>R/W | 1: Pin P13 is set to a low level.<br>mber of bits: 8 Address: H'FFFF80<br>Description<br>Communication Mode<br>0: Asynchronous<br>1: Clock synchronous<br>Clock Select 1, 0<br>These bits select the clock source for the baud rate<br>generator.<br>00: P\u00f6 clock (n = 0)                                                                                                                        |

| • Ser<br>Bit<br>7 | rial mode control<br>Bit Name<br>C/A<br>CKS1 | l register_0 (SMF<br><b>Setting</b><br>1<br>0 | R_0) Nur<br><b>R/W</b><br>R/W | 1: Pin P13 is set to a low level.<br>mber of bits: 8 Address: H'FFFF80<br>Description<br>Communication Mode<br>0: Asynchronous<br>1: Clock synchronous<br>Clock Select 1, 0<br>These bits select the clock source for the baud rate<br>generator.<br>00: Pφ clock (n = 0)<br>For the relation between the settings of these bits and the                                                              |

| • Ser<br>Bit<br>7 | rial mode control<br>Bit Name<br>C/A<br>CKS1 | l register_0 (SMF<br><b>Setting</b><br>1<br>0 | R_0) Nur<br><b>R/W</b><br>R/W | 1: Pin P13 is set to a low level.<br>mber of bits: 8 Address: H'FFFF80<br>Description<br>Communication Mode<br>0: Asynchronous<br>1: Clock synchronous<br>Clock Select 1, 0<br>These bits select the clock source for the baud rate<br>generator.<br>00: Pφ clock (n = 0)<br>For the relation between the settings of these bits and the<br>baud rate, see section 14.3.9, Bit Rate Register (BRR) in |

| • Ser<br>Bit<br>7 | rial mode control<br>Bit Name<br>C/A<br>CKS1 | l register_0 (SMF<br><b>Setting</b><br>1<br>0 | R_0) Nur<br><b>R/W</b><br>R/W | 1: Pin P13 is set to a low level.<br>mber of bits: 8 Address: H'FFFF80<br>Description<br>Communication Mode<br>0: Asynchronous<br>1: Clock synchronous<br>Clock Select 1, 0<br>These bits select the clock source for the baud rate<br>generator.<br>00: Pφ clock (n = 0)<br>For the relation between the settings of these bits and the                                                              |

• Bit rate register\_0 (BRR\_0) Number of bits: 8 Address: H'FFFF81

Function: BRR\_0 is used to adjust the bit rate. When  $P\phi = 32$  MHz, CKS1 and CKS2 in SMR\_0 = B'00, and BRR\_0 = 31 will set the bit rate to 250 kbps.

Setting: 31

| Bit | Bit Name | Setting | R/W | Description                                               |

|-----|----------|---------|-----|-----------------------------------------------------------|

| 7   | TIE      | 0/1     | R/W |                                                           |

| 1   | IIE      | 0/1     | R/W | Transmit Interrupt Enable                                 |

|     |          |         |     | 0: Disables TXI interrupt requests.                       |

|     |          |         |     | 1: Enables TXI interrupt requests.                        |

| 6   | RIE      | 0       | R/W | Receive Interrupt Enable                                  |

|     |          |         |     | 0: Disables RXI and ERI interrupt requests.               |

|     |          |         |     | 1: Enables RXI and ERI interrupt requests.                |

| 5   | TE       | 0/1     | R/W | Transmit Enable                                           |

|     |          |         |     | 0: Disables transmission.                                 |

|     |          |         |     | 1: Enables transmission.                                  |

| 4   | RE       | 0       | R/W | Receive Enable                                            |

|     |          |         |     | 0: Disables reception.                                    |

|     |          |         |     | 1: Enables reception.                                     |

| 2   | TEIE     | 0/1     | R/W | Transmit End Interrupt Enable                             |

|     |          |         |     | 0: Disables TEI interrupt requests.                       |

|     |          |         |     | 1: Enables TEI interrupt requests.                        |

| 1   | CKE1     | 0       | R/W | Clock Enable 1 and 0                                      |

| 0   | CKE0     | 0       |     | Selects the clock source.                                 |

|     |          |         |     | When in clock synchronous mode;                           |

|     |          |         |     | 0X: Internal clock. SCK pin is set as a clock output pin. |

|     |          |         |     | 1X: External clock. SCK pin is set as a clock input pin.  |

Note X: Don't care.

• Serial status register\_0 (SSR\_0) Number of bits: 8 Address: H'FFFF84

| Bit | Bit Name | Setting   | R/W    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|----------|-----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TDRE     | Undefined | R/(W)* | <ul> <li>Transmit Data Register Empty</li> <li>Indicates whether TDR contains data for transmission.</li> <li>[Setting conditions]</li> <li>Clearing of the TE bit in SCR to 0</li> <li>Transfer of data from TDR to TSR</li> <li>[Clearing conditions]</li> <li>Writing of 0 to TDRE after having read TDRE = 1<br/>(when using an interrupt and having the CPU clear it, be sure to read the flag after having written 0 to it).</li> <li>Generation of a TXI interrupt request allowing DMAC to write transmit data to TDR</li> </ul> |

| 2   | TEND     | Undefined | R      | <ul> <li>Transmit End</li> <li>[Setting conditions]</li> <li>Clearing of the TE bit in SCR to 0</li> <li>TDRE = 1 on transmission of the last bit of a character</li> <li>[Clearing conditions]</li> <li>Writing of 0 to TDRE after having read TDRE = 1</li> <li>Generation of a TXI interrupt request allowing its value DMAC to write data to TDR</li> </ul>                                                                                                                                                                          |

Note: \* Only 0 can be written here, to clear the flag.

| • Sm | <ul> <li>Smart card mode register_0 (SCMR_0) Number of bits: 8 Address: H'FFFF86</li> </ul> |         |     |                                                                                            |  |  |  |  |

|------|---------------------------------------------------------------------------------------------|---------|-----|--------------------------------------------------------------------------------------------|--|--|--|--|

| Bit  | Bit Name                                                                                    | Setting | R/W | Description                                                                                |  |  |  |  |

| 0    | SMIF                                                                                        | 0       | R/W | Smart Card Interface Mode Select                                                           |  |  |  |  |

|      |                                                                                             |         |     | <ol> <li>Operation is in the normal asynchronous or clock<br/>synchronous mode.</li> </ol> |  |  |  |  |

|      |                                                                                             |         |     | 1: Operation is in smart card interface mode.                                              |  |  |  |  |

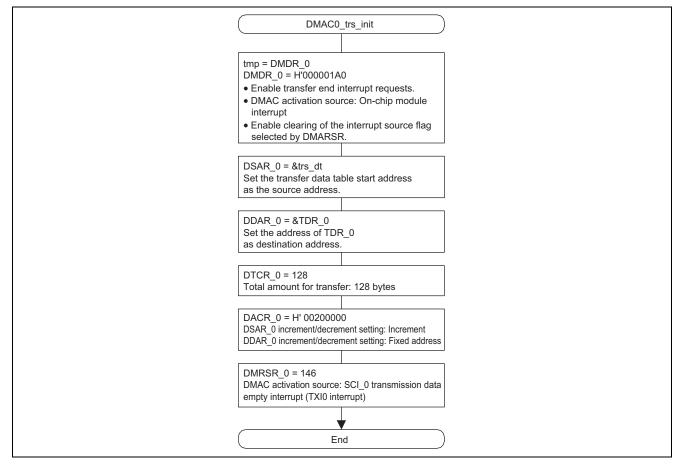

### 5.6.3 DMAC0\_trs\_init Function

1. Functional overview

DMAC\_0 initialization. Sets the transfer processing by TXI0 interrupts to TDR\_0 from transmitted data holding area.

- 2. Argument None

- 3. Return value None

4. Description of internal registers used The internal registers used in this sample task are described below. The settings shown in these tables are the values used in this sample task and differ from the initial values.

- DMA source address register\_0 (DSAR\_0) Number of bits: 32 Address: H'FFFC00 Function: DSAR\_0 specifies the source address for the transfer. Setting: &trs\_dt

- DMA destination address register\_0 (DDAR\_0) Number of bits: 32 Address: H'FFFC04 Function: DDAR\_0 specifies the destination address for the transfer. Setting: &TDR\_0

- DMA transfer count register\_0 (DTCR\_0) Number of bits: 32 Address: H'FFFC0C Function: DTCR\_0 sets the amount of data to be transferred (total amount for transfer). Setting: 128

| • DN | MA mode control | l register_0 (DM | DR_0) Nu | mber of bits: 32 Address: H'FFFC14                                                                           |

|------|-----------------|------------------|----------|--------------------------------------------------------------------------------------------------------------|

| Bit  | Bit Name        | Setting          | R/W      | Description                                                                                                  |

| 31   | DTE             | 0                | R/W      | Data Transfer Enable                                                                                         |

|      |                 |                  |          | 0: Disables data transfer.                                                                                   |

|      |                 |                  |          | 1: Enables data transfer.                                                                                    |

| 26   | NRD             | 0                | R/W      | Next Request Delay                                                                                           |

|      |                 |                  |          | <ol> <li>Starts accepting the next transfer request after<br/>completion of the current transfer.</li> </ol> |

|      |                 |                  |          | 1: Starts accepting the next transfer request one cycle after completion of the current round of transfer.   |

| 17   | ESIF            | 0                | R/(W)*   | Transfer Escape Interrupt Flag                                                                               |

|      |                 |                  |          | 0: A transfer escape end interrupt request has not been issued.                                              |

|      |                 |                  |          | 1: A transfer escape end interrupt request has been issued.                                                  |

| 16   | DTIF            | 0                | R/(W)*   | Data Transfer Interrupt Flag                                                                                 |

|      |                 |                  |          | 0: A transfer end interrupt request by the transfer counter has not been issued.                             |

|      |                 |                  |          | 1: A transfer end interrupt request by the transfer counter has been issued.                                 |

| 15   | DTSZ1           | 0                | R/W      | Data Access Size 1 and 0                                                                                     |

| 14   | DTSZ0           |                  | R/W      | 00: Data access size for transfer is in bytes (8 bits).                                                      |

| 13   | MDS1            | 0                | R/W      | Transfer Mode Select 1 and 0                                                                                 |

| 12   | MDS0            |                  | R/W      | 00: Sets the normal transfer mode.                                                                           |

| Bit | Bit Name | Setting | R/W | Description                                                                                                                                                                                      |

|-----|----------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9   | ESIE     | 0       | R/W | Transfer Escape interrupt Enable                                                                                                                                                                 |

|     |          |         |     | 0: Disables transfer escape interrupt requests.                                                                                                                                                  |

|     |          |         |     | 1: Enables transfer escape interrupt requests.                                                                                                                                                   |

| 8   | DTIE     | 1       | R/W | Data Transfer End Interrupt Enable                                                                                                                                                               |

|     |          |         |     | 0: Disables transfer end interrupt requests.                                                                                                                                                     |

|     |          |         |     | 1: Enables transfer end interrupt requests.                                                                                                                                                      |

| 7   | DTF1     | 1       | R/W | Data Transfer Factor 1 and 0                                                                                                                                                                     |

| 6   | DTF0     | 0       | R/W | 10: DMAC activation source is an on-chip module interrupt.                                                                                                                                       |

| 5   | DTA      | 1       | R/W | Data Transfer Acknowledge                                                                                                                                                                        |

|     |          |         |     | When DTF 1 and DTF $0 = H'10$ , which selects execution of DMA transfer in response to an internal module interrupt, this bit enables or disables clearing of the source flag selected by DMRSR. |

|     |          |         |     | <ol> <li>Source flag for the internal module interrupt is not<br/>cleared.</li> </ol>                                                                                                            |

|     |          |         |     | 1: Source flag for the internal module interrupt is cleared.                                                                                                                                     |

Note: \* Only 0 can be written here, to clear the flag.

| ٠ | DMA address control register_0 (DACR_0) | Number of bits: 32 | Address: H'FFFC18 |

|---|-----------------------------------------|--------------------|-------------------|

|---|-----------------------------------------|--------------------|-------------------|

| 21  |          |         |     |                                         |  |

|-----|----------|---------|-----|-----------------------------------------|--|

| Bit | Bit Name | Setting | R/W | Description                             |  |

| 31  | AMS      | 0       | R/W | Address Mode Select                     |  |

|     |          |         |     | 0: Dual address mode                    |  |

|     |          |         |     | 1: Single address mode                  |  |

| 21  | SAT1     | 1       | R/W | Source Address Update Mode 1 and 0      |  |

| 20  | SAT0     | 0       | R/W | 10: Increment the source address.       |  |

| 17  | DAT1     | 0       | R/W | Destination Address Update Mode 1 and 0 |  |

| 16  | DAT0     | 0       | R/W | 00: Destination address is fixed.       |  |

|     |          |         |     |                                         |  |

• DMA module request select register\_0 (DMRSR\_0) Number of bits: 8 Address: H'FFFD20 Function: DMRSR\_0 specifies the source of on-chip module interrupts. The setting 146 corresponds

Function: DMRSR\_0 specifies the source of on-chip module interrupts. The setting 146 corresponds to DMAC activation by SCI\_0 transmission data empty interrupts (TXI0 interrupts).

Setting: 146

#### 5.6.4 dmtend0\_int Function

1. Functional overview

Handler for the DMAC\_0 transfer end interrupt. Sets TEI0 interrupt requests enabled, TXI0 interrupt requests disabled, and DMAC\_0 transfer end interrupt requests disabled.

- 2. Argument None

- 3. Return value None

- 4. Description of internal registers used

The internal registers used in this sample task are described below. The settings shown in these tables are the values used in this sample task and differ from the initial values.

| 7 | TIE  | 0 | R/W | Transmit Interrupt Enable           |  |

|---|------|---|-----|-------------------------------------|--|

|   |      |   |     | 0: Disables TXI interrupt requests. |  |

|   |      |   |     | 1: Enables TXI interrupt requests.  |  |

| 2 | TEIE | 1 | R/W | Transmit End Interrupt Enable       |  |

|   |      |   |     | 0: Disables TEI interrupt requests. |  |

|   |      |   |     | 1: Enables TEI interrupt requests.  |  |

|   |      |   |     | 1. Enables TET interrupt requests.  |  |

| • DM | [A mode control | l register_0 (E | MDR_0) Nu | mber of bits: 32 Address: H'FFFC14           |

|------|-----------------|-----------------|-----------|----------------------------------------------|

| Bit  | Bit Name        | Setting         | R/W       | Description                                  |

| 8    | DTIE            | 0               | R/W       | Data Transfer End Interrupt Enable           |

|      |                 |                 |           | 0: Disables transfer end interrupt requests. |

|      |                 |                 |           | 1: Enables transfer end interrupt requests.  |

#### 5.6.5 tei0\_int Function

## 1. Functional overview

Handler for SCI\_0 transmission end interrupts (TEI0 interrupt). Sets to SCI\_0 transmission and TEI0 interrupt requests disabled.

- 2. Argument None

- 3. Return value None

- 4. Description of internal registers used

The internal registers used in this sample task are described below. The settings shown in these tables are the values used in this sample task and differ from the initial values.

| ٠ | Serial control register_0 (SCR_0) | Number of bits: 8 | Address: H'FFFF82 |

|---|-----------------------------------|-------------------|-------------------|

|---|-----------------------------------|-------------------|-------------------|

| Bit | Bit Name | Setting | R/W | Description                         |

|-----|----------|---------|-----|-------------------------------------|

| 5   | TE       | 0       | R/W | Transmit Enable                     |

|     |          |         |     | 0: Disables transmission.           |

|     |          |         |     | 1: Enables transmission.            |

| 2   | TEIE     | 0       | R/W | Transmit End Interrupt Enable       |

|     |          |         |     | 0: Disables TEI interrupt requests. |

|     |          |         |     | 1: Enables TEI interrupt requests.  |

### 6. Documents for Reference (Note)

- Hardware Manual H8SX/1653 Group Hardware Manual The most up-to-date version of this document is available on the Renesas Technology Website.

- Technical News/Technical Update The most up-to-date information is available on the Renesas Technology Website.

### Website and Support

Renesas Technology Website <u>http://www.renesas.com/</u>

Inquiries

http://www.renesas.com/inquiry csc@renesas.com

### **Revision Record**

|      |           | Descript |                      |  |

|------|-----------|----------|----------------------|--|

| Rev. | Date      | Page     | Summary              |  |

| 1.00 | Aug.23.07 |          | First edition issued |  |

|      |           |          |                      |  |

|      |           |          |                      |  |

|      |           |          |                      |  |

|      |           |          |                      |  |

### Notes regarding these materials

- 1. This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- 2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.