# **Thermal FET**

# Usage guide

#### Introduction

This application note explains the characteristics and basic usage of thermal FETs.

#### **Contents**

| 1.  | Overview of Thermal FET                                                                      | 2  |

|-----|----------------------------------------------------------------------------------------------|----|

| 1.1 | Development background                                                                       | 2  |

| 1.2 | Features                                                                                     | 2  |

| 1.3 | Advantages of Thermal FET                                                                    | 2  |

| 1.4 | Main function                                                                                | 3  |

| 1.5 | Precautions for use                                                                          | 3  |

| 2.  | Thermal FET Configuration and Operation Overview                                             | 4  |

| 2.1 | Internal Equivalent circuit                                                                  | 4  |

| 2.2 | Mechanism of Overheat shutdown operation (Thermal Shutdown Function)                         | 5  |

| 3.  | Thermal FET Datasheet Explanation                                                            | 8  |

| 3.1 | Typical operating characteristics (RJF0618JPE)                                               | 8  |

| 3.2 | Electrical characteristics (RJF0618JPE)                                                      | 9  |

| 3.3 | How to View the Safe Operating Area of a Thermal FET                                         | 10 |

| 3.4 | Relationship between overheat shutdown operation and gate/drain input voltage in Thermal FET | 11 |

| 4.  | Important Notes About Thermal FET Control                                                    | 12 |

| 4.1 | Gate drive method                                                                            | 12 |

| 4.2 | Concept of external gate resistor                                                            | 13 |

| 4.3 | Precautions for inductance load control                                                      | 14 |

| 4.4 | Precautions for reverse battery connection and use of built-in diode                         | 16 |

| 4.5 | Precautions for repeated use of overheat shutdown operation                                  | 16 |

| 4.6 | Precautions when exceeding Tch=150°C or higher                                               | 17 |

| 5.  | Application                                                                                  | 18 |

| Rev | vision History                                                                               | 19 |

#### 1. Overview of Thermal FET

#### 1.1 Development background

In recent years, high power switches for automobiles have changed from mechanical relays to semiconductors to ensure high functionality and high reliability of the system. Computerization is accelerating to the used switch. Power MOSFETs are commonly used as semiconductor switches, but further to achieve high reliability, protection functions such as "over-temperature protection", "over-current protection", and "over-voltage protection" are required for power devices alone. The need for embedded intelligent power devices is increasing. However, intelligent power devices that make full use of IC technology are often customized for automotive applications. As a result of less versatility, it is often more expensive. Therefore, Renesas has developed a power MOSFET "Thermal FET" with a built-in "overheat cut-off circuit" which is the minimum necessary function for the purpose of device and system protection.

This product will be an intelligent power device with high versatility and low cost. The thermal MOSFET is explained below.

#### 1.2 Features

- 1. Built-in over temperature shut-down circuit.

- 2. It has the same basic structure as a power MOS FET and provides low on-resistance.

- It consists of three pins, which are most commonly use in power MOSFETs, and the packages use is also apply common technology.

- 4. Reliability in an automotive operating environment is at the same level as a power MOSFET.

#### 1.3 Advantages of Thermal FET

- Ensures high fracture resistance

It has sufficient ability to withstand load short circuits, load dumps, and electrostatic surges that are unique to automobiles. Especially it has a load short-circuit resistance that can be used up to 24V vehicles (excluding some products).

- 2. Supports low current consumption

- With the computerization and high functionality of systems, it has become essential to reduce the burden on batteries. Especially, it is essential to reduce dark current (current that flows regardless of whether it is on or off), and thermal FETs achieve low current consumption. (Items are listed in IDSS, etc., but may not be listed in other companies' catalogs.) For LED (Light Emitting Diode), if it is not  $10uA \downarrow$ , it will light up slightly when it is not lit, which will be a problem in use. The thermal FET has a power consumption of 1uA and low current consumption, so it can be used for loads that require low current.

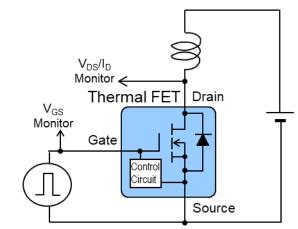

- 3. How to check overheat cutoff operation of thermal FET Generally, there is a detection method that uses the A/D detection function of the microcomputer. However, the A/D detection method requires an external shunt resistor, and there is a limit to the number of A/D pins required on the MCU side. (Because it is used as a judgment of another function that is originally necessary) Therefore, when dealing with the same method, our company uses the I/O port of the microcomputer with a margin, monitors the gate voltage of the thermal FET and the voltage between the drain and the source and confirms the synchronous state. This is recommended because it is possible to check whether or not the overheat cutoff operation is performed.

#### 1.4 Main function

It detects the rise of the channel temperature in the chip and shuts off the power MOSFET by itself. ⇒

"Built-in over-temperature cut-off circuit" With this operation, the Power MOSFET is protected from

thermal damage due to overpower such as load short circuit.

- 2. Two specifications are available for returning to the normal state after the operation of the over-temperature cut-off circuit.

- Latch Type

Holds the state of the overheat cutoff operation. (when applying gate voltage continuously). By setting

the gate voltage to 0V, the holding state of the overheat cutoff circuit is reset (cancelled), and

operation becomes possible by applying the normal bias thereafter.

- 2) Temperature Hysteresis Type

After the overheat shutdown operation, when the channel temperature in the chip drops below a

certain temperature, the holding state of the overheat shutdown circuit is reset (released), and normal

bias application enables operation. Temperature for overheat shutdown operation (Thermal

Shutdown Function). When the channel temperature inside the chip reaches 175°C (typ.), the

overheat shutdown operation occurs and turns off the power MOSFET.

#### 1.5 Precautions for use

- 1. Please treat the overheat cutoff circuit as a "protection function" against thermal destruction in abnormal power conditions, and do not design a system that actively uses it in expectation of its function.

- 2. The operating area of the thermal shutdown circuit is limited for each product. Please be sure to check the "safety assurance operation diagram" described in the data sheet and confirm compatibility with the operating conditions in the system. (Especially when the voltage applied to the drain of a battery, etc., exceeds 16V, it is necessary to thoroughly check the usable range.)

- 3. For normal condition usage, please use the product within the guaranteed range for the "maximum rating", "operating power supply range", "mounting conditions", and others. This product is intended to replace mechanical relays, and its switching time is designed to be slow. Therefore, please note that it is not suitable for controlling loads that require high-speed switching operation. The customer is responsible for verifying the operation speed, so please give us a sufficient evaluation.

#### Thermal FET Configuration and Operation Overview

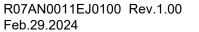

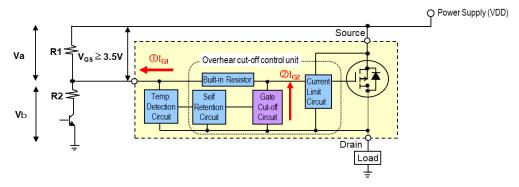

#### 2.1 Internal Equivalent circuit

Fig. 2-1 Internal equivalent circuit description of components

- 1. Temperature detection(sensing) circuit Constructed with diode element and circuitry to detect channel temperature inside the chip. This circuit is placed next to the source electrode and in the center of the chip to accurately detect the channel temperature.

- 2. Self-retention (Latch) circuit A circuit to keep the overheat cutoff state.

- 3. Gate cut-off circuit By turning on the overheat cut-off MOSFET, the impedance between the gate and source is lowered, the main MOSFET is turned off, and the drain current is cut.

- 4. Current limitation circuit It operates when the drain current exceeds the rated current.

- 5. Built in resistance (gate resistance Rg)

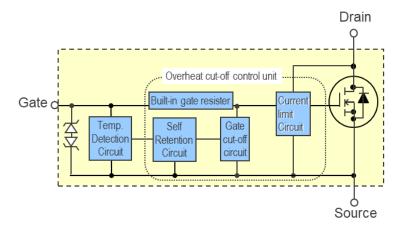

Fig. 2-2 Chip appearance photo (example)

#### 2.2 Mechanism of Overheat shutdown operation (Thermal Shutdown Function)

This section explains on process logic operation of thermal FET overheat shutdown until it recovered by using operation waveform and equivalent circuit.

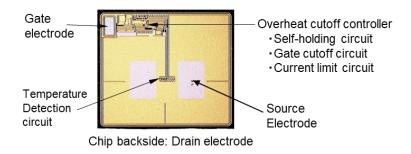

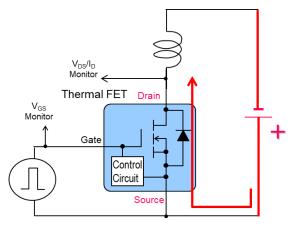

Fig. 2-3 Thermal FET use circuitry example

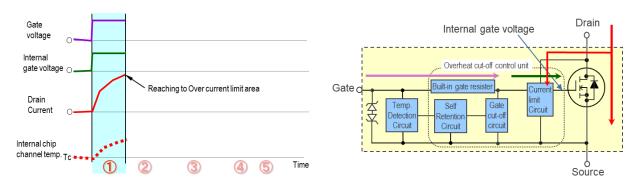

Operation Mode (1): Normal Operation (Operation waveform area ①) A gate voltage is applied and a drain current flows.

Fig. 2-4 Operation mode (1)

Operation Mode (2): Current Limit Operation (Operation waveform area ②)

When over current and current limit circuit is judged, internal gate voltage is limited and drain current is lowered.

Fig. 2-5 Operation mode (2)

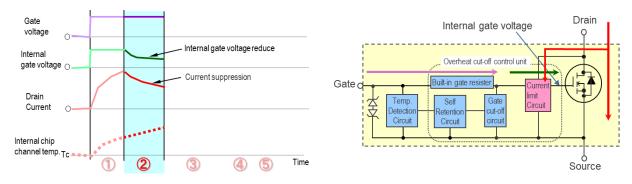

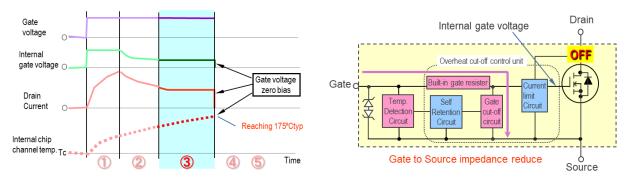

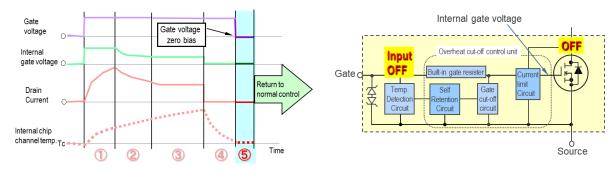

Operation Mode (3): Overheat Shutdown Operation (Operation waveform area ③)

Even there is a current is limiter, when chip internal channel temperature rises and reaches the cut-off temperature, gate cut-off circuit will function to cuts off.

Fig. 2-6 Operation mode (3)

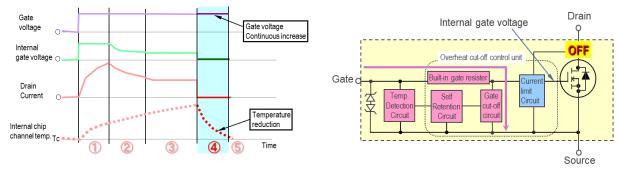

Operation Mode (4): Self-retention Operation (Operation waveform area ④)

If the gate voltage is continuously applied form the outside after the overheat is cut-off, the Thermal FET will self-hold the OFF state.

Fig. 2-7 Operation mode (4)

Operation Mode (5-1): Release of Self-retention Operation(latch release) (Operating waveform area ⑤)

After overheat shutting down, the gate voltage is set to zero bias from the outside, and the system returns to normal control state.

Fig. 2-8 Operation mode (5-1)

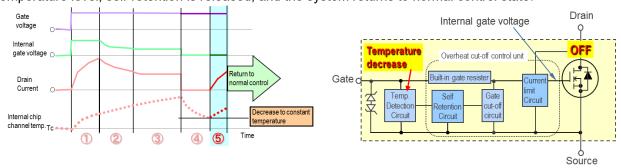

Operation Mode (5-2): Release of Self-retention Operation(latch release) (Operating waveform area ⑤) After overheat shutting down, the chip internal channel temperature drops to a certain constant temperature level, self-retention is released, and the system returns to normal control state.

Fig. 2-9 Operation mode (5-2)

#### 3. Thermal FET Datasheet Explanation

As mentioned above, the thermal FET is a power MOSFET with a built-in protection function. For this reason, there are "unique" expressions in the datasheets provided for each product. In addition, for the ratings and characteristics items which are not "unique" expressions, it is conformed to be the same content as power MOSFET datasheet.

#### 3.1 Typical operating characteristics (RJF0618JPE)

Table 3-1 Typical operating characteristics (RJF0618FJPE)

(Ta = 25°C)

| item                          | Symbol               | Specification |      | unit | Measurement  | t Commentary                |                                                                                                                   |  |

|-------------------------------|----------------------|---------------|------|------|--------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------|--|

|                               |                      | Min.          | Тур  | Max. |              | condition                   |                                                                                                                   |  |

| Input voltage                 | ViH                  | 3.5           | -    | -    | V            |                             | Minimum voltage to operate the breaking circuit                                                                   |  |

| Input voltage                 | V <sub>IL</sub>      | -             | -    | 1.2  | V            |                             | Maximum voltage for release self-retention operation                                                              |  |

| Input current                 | I <sub>IH1</sub>     | -             | -    | 100  | μA           | V <sub>i</sub> = 8V,        | When the gate bias is                                                                                             |  |

| (When gate is not cut<br>off) |                      |               |      |      |              | $V_{DS} = 0$                | applied, maximum dark<br>current consumed at the<br>cutoff control circuit (Same                                  |  |

| Input current                 | I <sub>IH2</sub>     | -             | -    | 50   | μA           | V <sub>i</sub> = 8V,        | meaning as IGSS)                                                                                                  |  |

| (When gate is not cut<br>off) |                      |               |      |      |              | $V_{DS} = 0$                |                                                                                                                   |  |

| Input current                 | IιL                  | -             | -    | 1    | μA           | V <sub>i</sub> = 8V,        |                                                                                                                   |  |

| (When gate is not cut off)    |                      |               |      |      |              | $V_{DS} = 0$                |                                                                                                                   |  |

| Input current                 | I <sub>IH(sd)1</sub> | -             | 0.8  | -    | mA           | V <sub>i</sub> = 8V,        | Gate current consumed during cutoff circuit operation.                                                            |  |

| (When gate is cut off)        |                      |               |      |      |              | $V_{DS} = 0$                |                                                                                                                   |  |

|                               |                      |               |      |      |              |                             | Gate current during normal                                                                                        |  |

| Input current                 | I <sub>IH(sd)2</sub> | -             | 0.35 | -    | mA           | V <sub>i</sub> = 8V,        | operation is 100uA Vi=8V,                                                                                         |  |

| (When gate is cut off)        |                      |               |      |      |              | V <sub>DS</sub> = 0         | Since the current increases to 0.8mA for the breaking operation. Please secure the capacity of the drive circuit. |  |

| Cut-off temperature           | Tsd                  | -             | 175  | -    | $^{\circ}$ C | Channel<br>Temperature      | Cut-off operating temperature                                                                                     |  |

| Gate operation voltage        | Vop                  | 3.5           | -    | 12   | V            |                             | Cut-off circuit operating voltage <sup>Note1</sup>                                                                |  |

| Drain current (Current        | I <sub>D limit</sub> | 40            | -    | -    | Α            | $V_{GS} = 5V$ ,             | Current limit value                                                                                               |  |

| limit value)                  |                      |               |      |      |              | V <sub>DS</sub> = 10V Note2 |                                                                                                                   |  |

Note1: Cut-off operation cannot be expected at 12V or higher.

Note2: pulse measurement

# 3.2 Electrical characteristics (RJF0618JPE)

Table 3-2 Electrical characteristics (RJF0618FJPE)

| Item                                      | Symbol                | Specification |      | unit Measurement |    | item                                             |                                                                                                                                                                                                 |

|-------------------------------------------|-----------------------|---------------|------|------------------|----|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                           |                       | Min.          | Тур  | Max.             | -  |                                                  |                                                                                                                                                                                                 |

| Drain current                             | I <sub>D1</sub>       | -             | -    | 67               | A  | $V_{GS} = 3.5V$ , $V_{DS} = 10V$ Notes1          | At the minimum gate voltage that activates the cut-off circuit maximum drain current                                                                                                            |

|                                           | I <sub>D2</sub>       | •             | -    | 1.2              | mA | V <sub>GS</sub> = 1.2V,<br>V <sub>DS</sub> = 10V | Maximum drain current at shutdown circuit off voltage                                                                                                                                           |

|                                           | I <sub>D3</sub>       | 40            | -    | -                | A  | $V_{GS} = 5V$ , $V_{DS} = 10V^{Notes1}$          | Current limit value                                                                                                                                                                             |

| Gate-source<br>breakdown voltage          | V <sub>(BR)</sub> GSS | 16            | -    | -                | V  | $I_G = 800 \mu A,$ $V_{DS} = 0$                  | For considering direct drive of the automobile power supply, positive voltage side can be input up to 16V. For negative voltage side is -2.5V due to the restrictions of the protection circuit |

|                                           |                       | -2.5          | -    | -                |    | $I_{G} = -100 \mu \text{ A},$ $V_{DS} = 0$       |                                                                                                                                                                                                 |

| turn-on delay time                        | t <sub>d(on)</sub>    | ı             | 0.8  | -                | μs | V <sub>GS</sub> = 10V<br>I <sub>D</sub> = 20A    | Switching speed is limited by built-in gate series resistor                                                                                                                                     |

| Rise time                                 | tr                    | -             | 0.35 | -                |    | $R_L = 1.5 \Omega$                               | Tesisioi                                                                                                                                                                                        |

| turn-off delay time                       | t <sub>d(off)</sub>   | -             | 175  | -                |    |                                                  |                                                                                                                                                                                                 |

| Fall time                                 | t <sub>f</sub>        | -             | 12.5 | 12               |    |                                                  |                                                                                                                                                                                                 |

| Load short-circuit Cut off operation time | tos                   | -             | 0.48 | -                | ms | $V_{GS} = 5V$ , $VDD = 16V$ $V_{GS} = 5V$ ,      | Time for completion form load short circuit occurs until overheat cut-off operation completion.                                                                                                 |

| Notes 4, mule                             |                       |               |      |                  |    | VDD = 24V                                        | The load short-circuit breaking operation time varies depending on the usage environment, usage conditions, etc.                                                                                |

Notes 1: pulse measurement.

Notes 2: The parasitic capacitance  $(C_{iss}//C_{rss})$  of thermal FET cannot be quantified and expressed individually due to the built-in control circuit between the gate and source.

#### 3.3 How to View the Safe Operating Area of a Thermal FET

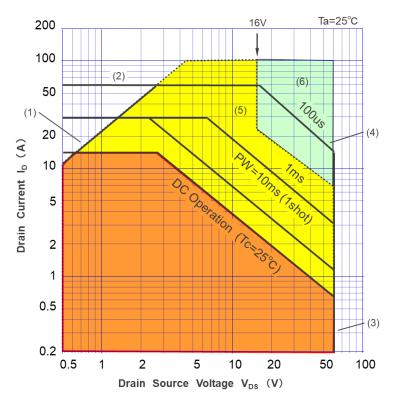

Fig. 3-1 Safe operating area with Thermal FET (SOA diagram)

- (1) Area is limited by ON resistance.

- (2) Area is limited by drain current rating "I<sub>D</sub>".

- (3) Area is limited by drain voltage rating "V<sub>DSS</sub>".

- (4) Area is the area limited by the safe operating area of the body MOSFET. For product design under normal conditions, please use within the limits of (1) to (4) region.

- (5) If this range is exceeded, an overheat shutdown operation will occur. (Yellow color area) Therefore, regarding the heat shutdown area, the yellow and orange areas are areas where overheat shutdown protection is possible.(In addition, the overheat cutoff mode that occurs in the orange area can be considered that when the channel temperature in the chip reaches 150°C or more due to factors such as "increase in ambient temperature" or "improper heat dissipation.")

- (6) The green area (6) is a high voltage and high current area. When a load short circuit occurs, the power becomes high. Because of this, control circuit response from temperature detection until shutdown operation of Thermal FET not able to match and the internal power MOSFET will lead to power (thermal) destruction. Please be careful when using this product in a system with a battery voltage of 16V or higher.

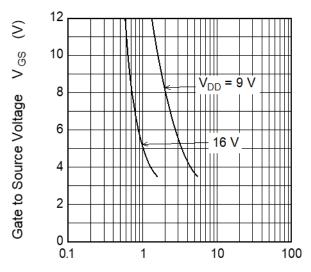

# 3.4 Relationship between overheat shutdown operation and gate/drain input voltage in Thermal FET

Fig. 3-2 Shutdown Time of Load-Short Test

1) Change in overheat shutdown operation time

The overheat cutoff operation of the thermal FET has the characteristic that the cutoff time changes depending on the applied gate voltage and drain voltage. Since the characteristics are determined individually according to the specifications of each product, please confirm it characteristic as describe in right side diagram in each product datasheet. Please take this into consideration when designing your system. The reason for such a change in the overheat cutoff time is When a load short circuit occurs, the amount of drain current that flows in depends on the characteristics of the thermal FET itself, the gate voltage, and the drain voltage. Therefore, the time it takes for the channel temperature in the chip to reach the temperature at which the cutoff operation occurs It is for change.

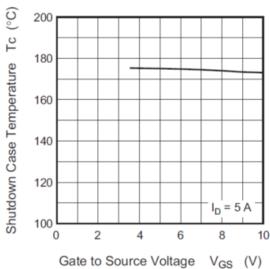

2) Change in overheat shutdown temperature (typ. value) The overheat cutoff temperature (typ. value) of the thermal FET does not vary greatly with the gate voltage being driven and it has almost constant characteristics.

Shutdown Case Temperature vs. Gate to Source Voltage

Fig. 3-3 Shutdown case temperature dependence

#### 4. Important Notes About Thermal FET Control

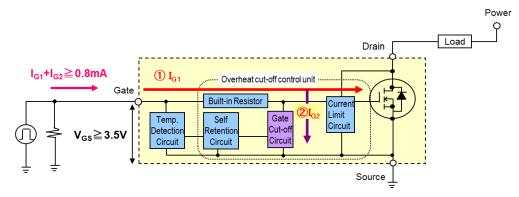

#### 4.1 Gate drive method

The guideline for the internal current consumption of the thermal FET is as below:

- ①Gate current consumed during normal operation (gate charge current and gate leakage current to MOSFET)

- I<sub>G1</sub>≥100uA (V<sub>GS</sub>=3.5V, full temperature range)

- ②Gate current consumed during overheat shutdown operation

- I<sub>G2</sub>≥0.7mA (The main current is determined by the internal resistance Rg, full temperature range at 3.5V)

Therefore, ①+② ( $I_{G1}+I_{G2} \ge 0.8mA$ ) is consumed during the cut-off operation. Considering this current consumption, at the gate voltage please design a drive that can secure  $V_{GS} \ge 3.5V$ , which is the minimum operating voltage for the cut-off circuit. In addition, when the gate sink current becomes less than the specified current, the overheat cut-off operation cannot be maintained since the internal gate voltage is divided by the influence of the internal resistance and the self-retention mode (latch situation) is reset (released). It will return to normal operation, please be careful.

Fig. 4-1 Internal equivalent circuit diagram

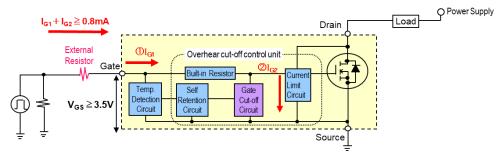

#### 4.2 Concept of external gate resistor

#### 1. Nch Type

As shown in section 4.1, the gate current required for overheat cutoff operation is  $I_{G1} + I_{G2} \ge 0.8$ mA. When inserting an external resistor, please consider this gate current and design an external resistor that can secure the cut-off operating voltage  $V_{GS} \ge 3.5$ V.

Fig. 4-2 Internal equivalent circuit diagram (Nch type)

#### 2. Pch Type

When inserting an external resistor as voltage divider,

- ① Cut-off operating voltage V<sub>GS</sub>≥3.5V is required.

- ② A gate current of  $I_{G1} + I_{G2} \ge 0.8$ mA) is required for overheat cut-off operation.

- ③ Therefore, from VDD=Va+Vb, please set the resistance value considering the required gate current ( $I_{G1}+I_{G2} \ge 0.8mA$ ).

Fig. 4-3 Internal equivalent circuit diagram (Pch type)

#### 4.3 Precautions for inductance load control

Notes (1)

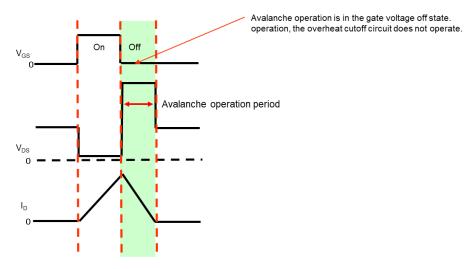

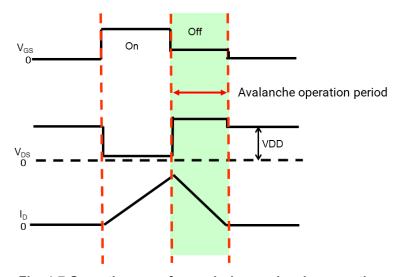

The thermal FET has resistance to avalanche operation like the power MOSFET. However, the avalanche operation originally occurs when the gate is turn off. It is an operation that absorbs (extinguishes) the back electromotive force of the inductance load using the drain withstand voltage of the product. The device that absorbs this avalanche energy causes a temperature rise in the chip, but overheating shutdown operation cannot be performed against this temperature rise. As mentioned above, the overheat cutoff operation of the thermal FET is based on assumption that the gate voltage is supplied within the specified range. There is no protection against events that occur in the gate voltage off state.

Fig. 4-4 Basic circuit example for inductance load control

Fig. 4-5 Waveform during avalanche operation with inductive load

Notes (2)

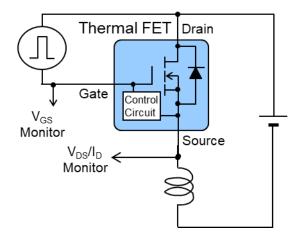

When using Nch Thermal FET as high side switch for inductance load control, same as power MOSFET the gate is turned on at an extremely low voltage. Back electromotive force is absorbed (extinguished) by using the operation in the non-saturation operation area of the power MOSFET. However, for the temperature rise inside the chip that occurs due to back electromotive force absorption, the gate voltage has not reached the specified range, so the overheat shutdown operation cannot be performed. The principle that the Thermal FET uses the non-saturation operating region in this operation is that when the Nch Thermal FET turns off, the potential of the source terminal drops, and a voltage difference occurs between the gate and source. The potential difference is a very low voltage, but when it exceeds the  $V_{GS(off)}$  voltage, the Nch Thermal FET turns on and starts absorbing back electromotive force. (Since the absorption starts, the gate voltage remains low and stabilizes.) Therefore, only a low gate voltage that slightly exceeds the  $V_{GS(off)}$  voltage is generated at the gate, so overheat shutdown operation is not possible. This Drain to Source Voltage ( $V_{DS}$ ) ON time is becoming VDD +voltage difference of gate to source.

Fig. 4-6 Example of inductance load control circuit in high-side configuration

Fig. 4-7 Operating waveforms during avalanche operation

#### 4.4 Precautions for reverse battery connection and use of built-in diode

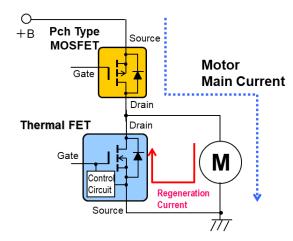

A thermal FET has a similar built-in parasitic diode between the drain and source to a power MOSFET. Therefore, if the power supply such as a battery is connected in reverse, the thermal FET will generate heat because the current will flow from the source to the drain via the parasitic diode. However, this diode current can flow regardless of the gate control method, so even if the channel temperature in the chip reaches the cutoff start temperature and the overheat cutoff operation occurs, the current cannot be cut off. Also, even if the customer expects the characteristics of the built-in parasitic diode to be used in a way that is not an abnormal mode (regenerative current arc extinguishing, etc.), the current that flows in the forward direction of the diode due to the original thermal FET cut-off operation for the above reason. cannot be blocked.

Fig. 4-8 Reverse battery connection.

Fig. 4-9 Example of using regenerative current with a motor load.

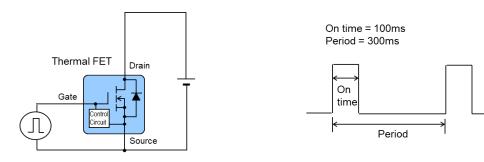

#### 4.5 Precautions for repeated use of overheat shutdown operation.

In the overheat shutdown operation caused by the load short circuit, the channel temperature in the chip becomes  $150^{\circ}$ C or more, so if the operation leading to that state is repeated, the initial structure cannot be maintained because the chip is exposed to high temperature for a long time. It may disappear and destroy. Therefore, please consider not to design a system that expected to have active usage of cut-off operation due to load short circuit.

### 4.6 Precautions when exceeding Tch=150℃ or higher

In the event of system failure such as load short circuit, it has been set that the permissible limit number of load short circuits for each product. Please set the fail-safe function within this allowable number of times for safety design of the system.

Table 4-1 Load short circuit allowable limit number of times Note.

| Product    | Test condition                                                         | Allowable number of load short circuits |

|------------|------------------------------------------------------------------------|-----------------------------------------|

| RJF0618JPE | VDD=16V, V <sub>GS</sub> =5V, R <sub>L</sub> =0, T <sub>a</sub> =25°C, | 10k times                               |

|            | Independently implement                                                |                                         |

Note: For inquiries about individual products, please contact our sales representatives.

図 4-10 Load short-circuit test condition

# 5. Application

Table 5-1 Application example

| Field                   | Use                                               | Usage purpose                             | Usage example           | Product Adoption         |

|-------------------------|---------------------------------------------------|-------------------------------------------|-------------------------|--------------------------|

| Vending<br>Machine      | Motor Drive                                       | Preventing<br>damage due to<br>motor lock | M<br>Low Side           | HAF2026RJ                |

| Farming<br>Machine      | Motor drive, Buzzer, Body control, Engine control | Short circuit protection                  | H bridge                | RJE0620JPD<br>RJF0618JSP |

| Industrial<br>Equipment | Power supply distribution switch, PLC,            | Short circuit protection                  | Load Load Load Low Side | RJF0622JSP<br>RJF0604JPD |

| Printer                 | Drawer Drive                                      | Short circuit protection                  | Load  Low Side          | RJF0610JSP               |

| Amusement               | Motor Drive                                       | Short circuit protection                  | Load  Low Side          | RJF0622JSP               |

# **Revision History**

|          |             | Description |               |  |

|----------|-------------|-------------|---------------|--|

| Rev.     | Date        | Page        | Summary       |  |

| Rev.1.00 | Feb-29.2024 | -           | First edition |  |

#### **Notice**

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.5.0-1 October 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners

#### **Contact information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <a href="https://www.renesas.com/contact/">www.renesas.com/contact/</a>.