Renesas Synergy<sup>™</sup> Platform

# **SPI Framework Module Guide**

## Introduction

This module guide will enable you to effectively use a module in your own design. Upon completion of this guide, you will be able to add this module to your own design, configure it correctly for the target application and write code, using the included application project code as a reference and efficient starting point. References to more detailed API descriptions and suggestions of other application projects that illustrate more advanced uses of the module are available on the Renesas Synergy Knowledge Base (as described in the References section at the end of this document), and should be valuable resources for creating more complex designs.

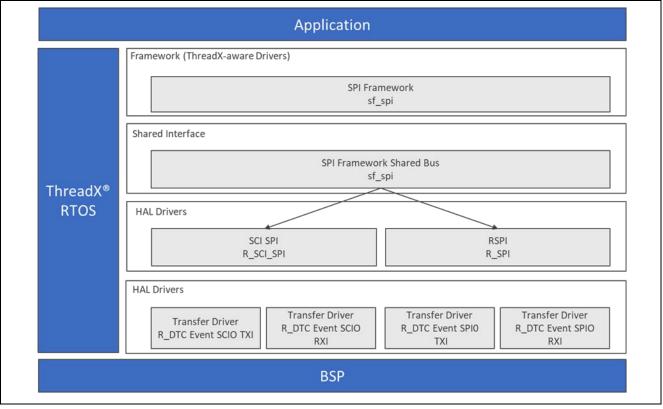

The SPI Framework module provides a ThreadX-aware framework API and handles the integration and synchronization of multiple SPI peripherals on an SPI bus (including chip-select handling and its level activation). With the SPI Framework, one or more SPI buses can be created and multiple SPI peripherals can be connected to the SPI bus. The SPI Framework module uses a single interface to access both SCI SPI and RSPI drivers. The SPI Framework module uses the SCI and RSPI peripherals on the Synergy MCU.

## Contents

| 1.    | SPI Framework Module Features                                    | 3  |

|-------|------------------------------------------------------------------|----|

| 2.    | SPI Framework Module APIs Overview                               | 3  |

| 3.    | SPI Framework Module Operational Overview                        | 5  |

| 3.1   | Multiple Slave Devices on the Same Bus                           | 5  |

| 3.2   | Bus Locking                                                      | 5  |

| 3.3   | SPI Framework Module Important Operational Notes and Limitations | 5  |

| 3.3.1 | 1 SPI Framework Module Operational Notes                         | 5  |

| 3.3.2 | 2 SPI Framework Module Limitations                               | 5  |

| 4.    | Including the SPI Framework Module in an Application             | 5  |

| 5.    | Configuring the SPI Framework Module                             | 6  |

| 5.1   | Configuration the SPI Framework Lower-Level Modules              | 7  |

| 5.2   | SPI Framework Module Clock Configuration                         |    |

| 5.3   | SPI Framework Module Pin Configuration                           |    |

| 5.4   | SPI Framework Module Additional Settings                         |    |

| 6.    | Using the SPI Framework Module in an Application                 | 13 |

| 6.1   | Implementation Steps for Two Slave Devices on Two Shared Busses  |    |

| 6.2   | Adding Another Shared Bus                                        |    |

| 7.    | SPI Framework Module Application Project                         | 20 |

| 8.    | Customizing the SPI Framework Module for a Target Application    | 23 |

| 9.    | Running the SPI Framework Module Application Project             | 24 |

| 10.  | SPI Framework Module Conclusion            | .25 |

|------|--------------------------------------------|-----|

| 11.  | SPI Framework Module Next Steps            | .25 |

| 12.  | SPI Framework Module Reference Information | .25 |

| Revi | sion History                               | .27 |

#### 1. SPI Framework Module Features

The SPI Framework module uses either the SCI in SPI mode (together with the SCI common lower-level modules) or the RSPI lower-level driver module to communicate with the SPI peripherals on the Synergy microcontroller.

- Supports multiple devices on a bus

- Provides high-level APIs for initialization, transfers, and closing the module

- Supports synchronized transfers

- Supports chip-select operations

- Supports bus-locking

Figure 1. SPI Framework Module Block Diagram

## 2. SPI Framework Module APIs Overview

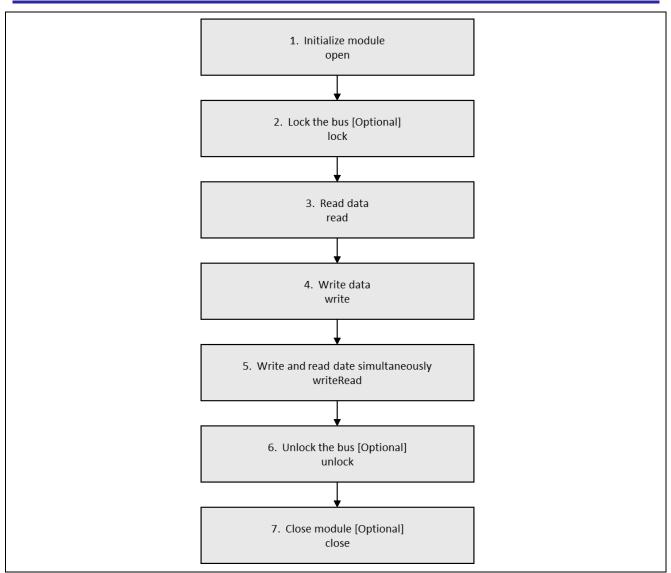

The SPI Framework module defines APIs for opening, closing, reading, writing and other useful functions. A complete list of the available APIs, an example API call and a short description of each can be found in the following table. A table of status return values follows the API summary table.

| Table 1. | SPI Framework Module API Summary |

|----------|----------------------------------|

|----------|----------------------------------|

| Function Name | Example API Call and Description                                           |  |

|---------------|----------------------------------------------------------------------------|--|

| .open         | g_sf_spi_device0.p_api->open(g_sf_spi_device0.p_cntl,                      |  |

|               | g_sf_spi_device0.p_cfg);                                                   |  |

|               | Open a designated SPI device on a bus.                                     |  |

| .read         | <pre>g_sf_spi_device0.p_api-&gt;read(g_sf_spi_device0.p_cntl, dst8,</pre>  |  |

|               | <pre>length, SPI_BIT_WIDTH_8_BITS, TX_WAIT_FOREVER);</pre>                 |  |

|               | Receive data from SPI device.                                              |  |

| .write        | <pre>g_sf_spi_device0.p_api-&gt;write(g_sf_spi_device0.p_cntl, src8,</pre> |  |

|               | <pre>length, SPI_BIT_WIDTH_8_BITS, TX_WAIT_FOREVER);</pre>                 |  |

|               | Transmit data to SPI device.                                               |  |

| Function Name | Example API Call and Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| .writeRead    | <pre>g_sf_spi_device0.p_api-&gt;writeRead (g_sf_spi_device0.p_cntl,<br/>&amp;source, &amp;destination, length, SPI_BIT_WIDTH_8_BITS,<br/>TX_WAIT_FOREVER);<br/>Simultaneously transmits data to an SPI device while receiving data from an SPI<br/>device (full duplex). The writeread API gets a mutex object, handles the SPI data<br/>transmission at SPI HAL layer, and receives data from the SPI HAL layer. The API<br/>uses the event flag wait to synchronize to completion of data transfer.</pre> |  |

| .close        | g_sf_spi_device0.p_api->close(g_sf_spi_device0.p_cntl);<br>Disable the SPI device designated by the control handle and close the RTOS<br>services used by the bus, if no devices are connected to the bus. This function<br>removes power to the SPI channel designated by the handle and disables the<br>associated interrupts.                                                                                                                                                                            |  |

| .lock         | <pre>g_sf_spi_device0.p_api-&gt;lock(g_sf_spi_device0.p_cntl);<br/>Lock the bus for a device. The locking allows devices to reserve a bus to<br/>themselves for a given period of time (such as between lock and unlock). This<br/>allows devices to complete several reads and writes on the bus without an interrupt.</pre>                                                                                                                                                                               |  |

| .unlock       | g_sf_spi_device0.p_api->unlock(g_sf_spi_device0.p_cntl);<br>Unlock the bus for a particular device and make the bus usable for other devices.                                                                                                                                                                                                                                                                                                                                                               |  |

| .versionGet   | g_sf_spi_device0.p_api->versionGet(&version);<br>Retrieve the API version with the version pointer.                                                                                                                                                                                                                                                                                                                                                                                                         |  |

Note: Details on operation and definitions for the function data structures, typedefs, defines, API data, API structures and function variables, review the *SSP User's Manual* API References for the associated module.

Table 2.

Status Return Values

| Name                      | Description                     |

|---------------------------|---------------------------------|

| SSP_SUCCESS               | Function completed successfully |

| SSP_ERR_INVALID_MODE      | Invalid mode                    |

| SSP_ERR_INVALID_CHANNEL   | Invalid channel                 |

| SSP_ERR_IN_USE            | In-use error                    |

| SSP_ERR_INVALID_ARGUMENT  | Invalid argument                |

| SSP_ERR_QUEUE_UNAVAILABLE | Queue unavailable               |

| SSP_ERR_INVALID_POINTER   | Invalid pointer                 |

| SSP_ERR_INTERNAL          | Internal error                  |

| SSP_ERR_TRANSFER_ABORTED  | Transfer aborted                |

| SSP_ERR_MODE_FAULT        | Mode fault                      |

| SSP_ERR_READ_OVF          | Read overflow                   |

| SSP_ERR_PARITY            | Parity error                    |

| SSP_ERR_OVERRUN           | Overrun error                   |

| SSP_ERR_UNDEF             | Unknown error                   |

| SSP_ERR_TIMEOUT           | Timeout error                   |

| SSP_ERR_NOT_OPEN          | Device not opened               |

Note: Lower-level drivers may return common error codes. Refer to the SSP User's Manual API References for the associated module for a definition of all relevant status return values.

## 3. SPI Framework Module Operational Overview

The SPI Framework module complies with the layered-driver architecture of the SSP. It uses either the SCI on SPI module or the RSPI module to communicate with the SPI peripherals on the Synergy microcontroller.

## 3.1 Multiple Slave Devices on the Same Bus

The SPI framework module uses a "bus" and "device on bus" architecture. Only one device is configured to the lower level driver at a time, and the other devices are reconfigured upon a read or write operation as required. The lower level driver can only be reconfigured when the bus is not locked. Every slave device is linked to the bus to which it will be connected and shares the bus with all other slave devices.

The user must configure the SPI framework shared-bus and the lower-level SPI HAL layer for each SPI framework module connecting to the bus. The user can add the existing framework shared-bus module when configuring multiple devices on the same bus. Each SPI framework module must be configured with a unique name in the ISDE configurator.

A common start and stop procedure is used for all SPI data-transfer operations (spi\_api\_t::read, spi\_api\_t::write, and spi\_api\_t::writeRead). During the start process, the SPI framework module checks whether reconfiguration is required. Chip select is asserted during the transfer-start process and de-asserted during the transfer-end process if the bus is not locked. The user must configure the chip-select IO pin and the chip-select active level.

## 3.2 Bus Locking

The SPI Framework module supports bus-locking functionality, meaning that the bus can be locked for a given slave peripheral. The locking allows slave devices to reserve a bus to themselves for the period between the lock and unlock commands. This allows devices to complete several reads and writes on the bus without interruption (which can be required in some situations). The chip select becomes active during lock and becomes inactive when unlocked. Writes and reads in between the lock and unlock do not alter the chip-select line.

## 3.3 SPI Framework Module Important Operational Notes and Limitations

#### 3.3.1 SPI Framework Module Operational Notes

- Multiple SPI devices can be configured to share a common bus. Once the SPI Framework bus module is configured, different SPI peripherals (devices) can be connected to that bus.

- For each SPI device connected to the bus, one SPI HAL module and one SPI Framework device module must be added.

- User-defined callback is not required as the framework takes care of internally.

- Setting the interrupts to different priority levels could result in improper operation.

#### 3.3.2 SPI Framework Module Limitations

- Refer to the MCU specification manual for identifying SPI bus compatibility. Device compatibility with the SPI bus is not checked in the framework hence incompatible SPI device may result in improper operation.

- Refer to the most recent SSP Release Notes for any additional operational limitations for this module.

# 4. Including the SPI Framework Module in an Application

This section describes how to include the SPI Framework module in an application using the SSP configurator.

Note: It is assumed you are familiar with creating a project, adding threads, adding a stack to a thread, and configuring a block within the stack. If you are unfamiliar with any of these items, refer to the first few chapters of the *SSP User's Manual* to learn how to manage each of these important steps in creating SSP-based applications.

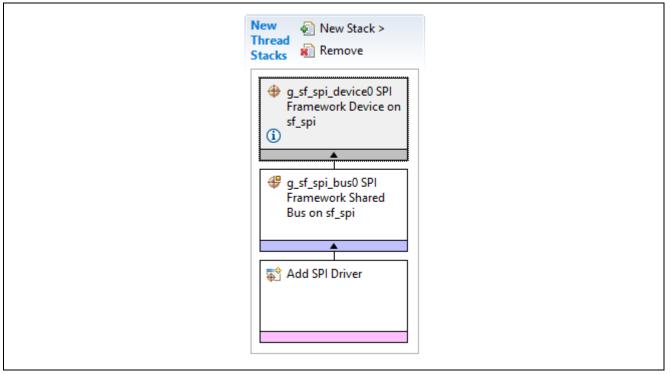

To add the SPI Framework module to an application, simply add it to a thread using the stacks selection sequence given in the following table. (The default name for the SPI Framework is g\_sf\_spi\_device0. This name can be changed in the associated **Properties** window.)

#### Table 3. SPI Framework Module Selection Sequence

| Resource                   | ISDE Tab | Stacks Selection Sequence               |  |

|----------------------------|----------|-----------------------------------------|--|

| g_sf_spi_device0 on sf_spi | Threads  | New Stack> Framework> Connectivity> SPI |  |

|                            |          | Framework Device on sf_spi              |  |

When the SPI Framework module on sf\_spi is added to the thread stack as shown in the following figure, the configurator automatically adds any needed lower-level modules. Any drivers that need additional configuration information will have the box text highlighted in Red. Modules with a Gray band are individual modules that stand alone. Modules with a Blue band are shared or common and need only be added once and can be used by multiple stacks. Modules with a Pink band can require the selection of lower level drivers; these are either optional or recommended (this is indicated in the block with the inclusion of this text.) If the addition of lower-level drivers is required, the module description will include Add in the text. Clicking on any Pink banded modules brings up the New icon and displays possible choices.

Figure 2. SPI Framework Module Stack

## 5. Configuring the SPI Framework Module

The SPI Framework module must be configured by the user for the desired operation. The SSP configuration window will automatically identify (by highlighting the block in red) any required configuration selections, such as interrupts or operating modes, which must be configured for lower-level modules to ensure successful operation. Furthermore, only those properties that can be changed without causing conflicts are available for modification. Other properties are 'locked' and are not available for changes, and are identified with a lock icon for the 'locked' property in the Properties window in the ISDE. This approach simplifies the configuration process and makes it much less error-prone than previous 'manual' approaches to configuration. The available configuration settings and defaults for all the user-accessible properties are given in the Properties tab within the SSP configurator, and are shown in the following tables for easy reference.

Note: You may want to open your ISDE, create the module and explore the property settings in parallel with looking over the configuration table settings in the following table. This helps to orient you, and can be a useful hands-on approach to learning the ins and outs of developing with SSP.

| Parameter                | Value                                                                                                                                                                                              | Description                                                            |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Parameter Checking       | BSP, Enabled, Disabled<br>Default: BSP                                                                                                                                                             | Selects if code for parameter checking is to be included in the build. |

|                          |                                                                                                                                                                                                    |                                                                        |

| Name                     | g_sf_spi_device0                                                                                                                                                                                   | Module name.                                                           |

| Clock Phase              | Data sampling on odd edge,<br>data variation on even<br>edge/Data sampling on even<br>edge, data variation on odd<br>edge<br>Default: Data sampling on odd<br>edge, data variation on even<br>edge | Select the clock phase.                                                |

| Clock Polarity           | Low when idle, High when idle Default: Low when idle                                                                                                                                               | Select the clock polarity.                                             |

| Chip Select Pin          | 00 thru 15                                                                                                                                                                                         | Select GPIO pin used for the chip select.                              |

|                          | Default: 00                                                                                                                                                                                        |                                                                        |

| Chip Select Pin          | 00 thru 15                                                                                                                                                                                         | Select GPIO pin used for the chip select.                              |

| -                        | (Default: 00)                                                                                                                                                                                      |                                                                        |

| Chip Select Active Level | Low, High                                                                                                                                                                                          | Polarity of the Chip Select signal, active High                        |

|                          | Default: Low                                                                                                                                                                                       | or Low                                                                 |

#### Table 4. Configuration Settings for the SPI Framework Module on sf\_spi

Note: The example values and defaults are for a project using the Synergy S7G2 MCU Group. Other MCUs may have different default values and available configuration settings.

In some cases, settings other than the defaults can be desirable. For example, it might be useful to select different chip-select GPIOs or levels. The configurable properties for the lower-level stack modules are given in the following sections for completeness and as a reference.

## 5.1 Configuration the SPI Framework Lower-Level Modules

Typically, only a small number of settings must be modified from the default for lower-level drivers as indicated via the red text in the thread stack block. Notice that some of the configuration properties must be set to a certain value for proper framework operation and will be locked to prevent user modification. The following table identifies all the settings within the properties section for the lower-level modules:

| Table 5. | Configuration | Settings for the | SPI Framework S | hard Bus on sf_spi |

|----------|---------------|------------------|-----------------|--------------------|

|----------|---------------|------------------|-----------------|--------------------|

| ISDE Property | Value         | Description |

|---------------|---------------|-------------|

| Name          | g_sf_spi_bus0 | Module name |

|               |               |             |

| Table 6. | . Configuration Settings for the RS | SPI HAL Driver on r_rspi |

|----------|-------------------------------------|--------------------------|

|----------|-------------------------------------|--------------------------|

| ISDE Property       | Value                           | Description                            |

|---------------------|---------------------------------|----------------------------------------|

| Parameter Checking  | BSP, Enabled, Disabled          | If selected code for parameter         |

| r aramotor encoking | Default: BSP                    | checking is included in the build.     |

| Name                | g_spi0                          | Module name.                           |

| Channel             | 0                               | SCI or SPI Channel number to which     |

| Charmer             | 0                               | the device has been connected.         |

|                     | Master, Slave                   | Configure as a Master or Slave device. |

| Operating Mode      | -                               | Note: Current version of SSP supports  |

|                     | Default: Master                 | only SPI Master mode.                  |

| Clock Phase         | Data sampling on odd edge, data | Data sampling on odd or even clock     |

| CIOCK FILASE        | variation on even edge          | edge.                                  |

Note: Most of the property settings for modules are fairly intuitive and usually can be determined by inspection of the associated Properties window from the SSP configurator.

| ISDE Property                      | Value                                                                                           | Description                                                   |

|------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| Clock Polarity                     | Low when idle                                                                                   | Clock level when idle.                                        |

| Mode Fault Error                   | Enable, Disable                                                                                 | Indicates Mode fault error                                    |

|                                    | Default: Disable                                                                                | (master/slave conflict) flag.                                 |

| Bit Order                          | MSB First, LSB First (Default: MSB First)                                                       | Select transmit order MSB/LSB first.                          |

| Bitrate                            | 500000                                                                                          | Transmission or reception rate. Bits per second.              |

| Callback                           | NULL                                                                                            | Optional Callback function pointer.                           |

| SPI Mode                           | SPI Operation, Clock synchronous<br>operation<br>Default: SPI Operation                         | Select spi or clock syn mode operation.                       |

| Slave Select<br>Polarity(SSL1)     | Active Low, Active High<br>Default: Active Low                                                  | Select SSL1 signal polarity.                                  |

| Slave Select<br>Polarity(SSL2)     | Active Low, Active High<br>Default: Active Low                                                  | Select SSL2 signal polarity.                                  |

| Slave Select<br>Polarity(SSL3)     | Active Low, Active High<br>Default: Active Low                                                  | Select SSL3 signal polarity.                                  |

| Select Loopback1                   | Normal, Inverted<br>Default: Normal                                                             | Select the data mode for loopback 1.                          |

| Select Loopback2                   | Normal, Inverted<br>Default: Normal                                                             | Select the data mode for loopback 2.                          |

| Enable MOSI Idle                   | Enable, Disable<br>Default: Disable                                                             | Select MOSI idle fixed value and selection                    |

| MOSI Idle State                    | MOSI Low, MOSI High<br>Default: MOSI Low                                                        | Select MOSI idle fixed value and selection                    |

| Enable Parity                      | Enable, Disable<br>Default: Disable                                                             | Enable/disable parity                                         |

| Parity Mode                        | Parity Odd, Parity Even<br>Default: Parity Odd                                                  | Select parity                                                 |

| Select SSL(Slave Select)           | SSL0, SSL1, SSL2, SSL3<br>Default: SSL0                                                         | Select which slave to use; 0-SSL0; 1-<br>SSL1; 2-SSL2; 3-SSL3 |

| Select SSL Level After<br>Transfer | SSL Level Keep, SSL Level Do<br>Not Keep<br>Default: SSL Level Do Not Keep                      | Select SSL level after transfer completion; 0-negate; 1-keep  |

| Clock Delay Enable                 | Clock Delay Enable, Clock Delay<br>Disable<br>Default: Clock Delay Disable                      | Clock delay enable selection                                  |

| Clock Delay Count                  | Clock Delay 1 thru 8 RSPCK<br>Default: Clock Delay 1 RSPCK                                      | Clock delay count selection                                   |

| SSL Negation Delay<br>Enable       | Negation Delay Enable, Negation<br>Delay Disable<br>Default: Negation Delay Disable             | SSL negation delay enable selection                           |

| Negation Delay Count               | Negation Delay 1 thru 8 RSPCK<br>Default: Negation Delay 1 RSPCK                                | Negation delay count selection                                |

| Next Access Delay Enable           | Next Access Delay Enable, Next<br>Access Delay Disable<br>Default: Next Access Delay<br>Disable | Next access delay enable selection                            |

| Next Access Delay Count            | Next Access Delay 1 thru 8<br>RSPCK<br>Default: Next Access Delay 1<br>RSPCK                    | Next access delay count selection                             |

| ISDE Property                      | Value                                                                                                               | Description                           |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Receive Interrupt Priority         | Priority 0 (highest), Priority 1:14<br>Priority 15 (lowest - not valid if<br>using ThreadX)<br>Default: Priority 12 | Receive interrupt priority selection  |

| Transmit Interrupt Priority        | Priority 0 (highest), Priority 1:14<br>Priority 15 (lowest - not valid if<br>using ThreadX)<br>Default: Priority 12 | Transmit interrupt priority selection |

| Transmit End Interrupt<br>Priority | Priority 0 (highest), Priority 1:14<br>Priority 15 (lowest - not valid if<br>using ThreadX)<br>Default: Priority 12 | Transmit interrupt priority selection |

| Error Interrupt Priority           | Priority 0 (highest), Priority 1:14<br>Priority 15 (lowest - not valid if<br>using ThreadX)<br>Default: Priority 12 | Error interrupt priority selection    |

| ISDE Property                               | Value                                                                                                                      | Description                                                           |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Parameter Checking                          | BSP, Enabled, Disabled<br>Default: BSP                                                                                     | Selects if code for parameter checking is to be included in the build |

| Software Start                              | Enabled, Disabled<br>Default: Disabled                                                                                     | Software start selection                                              |

| Linker section to keep<br>DTC vector table  | .ssp_dtc_vector_table                                                                                                      | Linker section to keep DTC vector table selection                     |

| Name                                        | g_transfer0                                                                                                                | Module name                                                           |

| Mode                                        | Normal                                                                                                                     | Mode selection                                                        |

| Transfer Size                               | 2 Bytes                                                                                                                    | Transfer size selection                                               |

| Destination Address Mode                    | Fixed                                                                                                                      | Destination address mode selection                                    |

| Source Address Mode                         | Incremented                                                                                                                | Source address mode selection                                         |

| Repeat Area (Unused in<br>Normal Mode       | Source                                                                                                                     | Repeat area selection                                                 |

| Interrupt Frequency                         | After all transfers have completed                                                                                         | Interrupt frequency selection                                         |

| Destination Pointer                         | NULL                                                                                                                       | Destination pointer selection                                         |

| Source Pointer                              | NULL                                                                                                                       | Source pointer selection                                              |

| Number of Transfers                         | 0                                                                                                                          | Number of transfers selection                                         |

| Number of Blocks (Valid only in Block Mode) | 0                                                                                                                          | Number of blocks selection                                            |

| Activation Source (Must enable IRQ)         | Event SPI0 TXI                                                                                                             | Activation source selection                                           |

| Auto Enable                                 | False                                                                                                                      | Auto enable selection                                                 |

| Callback (Only valid with Software start)   | NULL                                                                                                                       | Callback selection                                                    |

| ELC Software Event<br>Interrupt Priority    | Priority 0 (highest), Priority 1:14<br>Priority 15 (lowest - not valid if<br>using ThreadX), Disabled<br>Default: Disabled | ELC Software Event interrupt priority selection.                      |

| ISDE Property                               | Value                                                                                                                      | Description                                      |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Deremeter Checking                          | BSP, Enabled, Disabled                                                                                                     | Selects if code for parameter checking           |

| Parameter Checking                          | Default: BSP                                                                                                               | is to be included in the build                   |

| Software Start                              | Enabled, Disabled<br>Default: Disabled                                                                                     | Software start selection                         |

| Link section to keep DTC vector table       | .ssp_dtc_vector_table                                                                                                      | Link section to keep DTC vector table selection  |

| Name                                        | g_transfer1                                                                                                                | Module name                                      |

| Mode                                        | Normal                                                                                                                     | Mode selection                                   |

| Transfer Size                               | 2 Bytes                                                                                                                    | Transfer size selection                          |

| Destination Address Mode                    | Incremented                                                                                                                | Destination address mode selection               |

| Source Address Mode                         | Fixed                                                                                                                      | Source address mode selection                    |

| Repeat Area (Unused in Normal Mode          | Destination                                                                                                                | Repeat area selection                            |

| Interrupt Frequency                         | After all transfers have completed                                                                                         | Interrupt frequency selection                    |

| Destination Pointer                         | NULL                                                                                                                       | Destination pointer selection                    |

| Source Pointer                              | NULL                                                                                                                       | Source pointer selection                         |

| Number of Transfers                         | 0                                                                                                                          | Number of transfers selection                    |

| Number of Blocks (Valid only in Block Mode) | 0                                                                                                                          | Number of blocks selection                       |

| Activation Source (Must enable IRQ)         | Event SPI0 RXI                                                                                                             | Activation source selection                      |

| Auto Enable                                 | False                                                                                                                      | Auto enable selection                            |

| Callback (Only valid with Software start)   | NULL                                                                                                                       | Callback selection                               |

| ELC Software Event<br>Interrupt Priority    | Priority 0 (highest), Priority 1:14<br>Priority 15 (lowest - not valid if<br>using ThreadX), Disabled<br>Default: Disabled | ELC Software Event interrupt priority selection. |

| Table 8. | Configuration Settings for the Transfer Driver on r_dtc Event SPI0 RXI |

|----------|------------------------------------------------------------------------|

|----------|------------------------------------------------------------------------|

| Table 9. Configuration Settings for the SPI Driver on r_sci_s | spi |

|---------------------------------------------------------------|-----|

|---------------------------------------------------------------|-----|

| ISDE Property      | Value                                                  | Description                                                                                                 |

|--------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Parameter Checking | BSP, Enabled, Disabled<br>Default: BSP                 | Enable or disable the parameter error checking.                                                             |

| Name               | g_spi0                                                 | Module name                                                                                                 |

| Channel            | 0                                                      | SCI or SPI Channel number to which the device has been connected.                                           |

| Operating Mode     | Master, Slave<br>Default: Master                       | Configure as a Master or Slave<br>device.<br>Note: Current version of SSP supports<br>only SPI Master mode. |

| Clock Phase        | Data sampling on odd edge, data variation on even edge | Data sampling on odd or even clock edge.                                                                    |

| Clock Polarity     | Low when idle                                          | Clock level when idle.                                                                                      |

| Mode Fault Error   | Enable, Disable<br>Default: Disable                    | Indicates Mode fault error<br>(master/slave conflict) flag.                                                 |

| Bit Order          | MSB First, LSB First<br>Default: MSB First             | Select transmit order MSB/LSB first                                                                         |

| Bitrate            | 100000                                                 | Transmission or reception rate. Bits per second.                                                            |

| ISDE Property               | Value                               | Description                               |

|-----------------------------|-------------------------------------|-------------------------------------------|

| Bit Rate Modulation Enable  | Enable, Disable                     | Bitrate Modulation Function enable or     |

|                             | Default: Enable                     | disable                                   |

| Callback                    | NULL                                | Optional Call back function pointer.      |

|                             | Priority 0 (highest), Priority 1:14 | Bitrate Modulation Function enable or     |

| Receive Interrupt Priority  | Priority 15 (lowest - not valid if  | disable.                                  |

| Receive interrupt Fridity   | using ThreadX)                      | Note: This is applicable only for SCI     |

|                             | Default: Priority 12                | SPI.                                      |

|                             | Priority 0 (highest), Priority 1:14 |                                           |

| Transmit Interrupt Priority | Priority 15 (lowest - not valid if  | Transmit interrupt priority selection.    |

|                             | using ThreadX)                      | Transmit interrupt priority selection.    |

|                             | Default: Priority 12                |                                           |

|                             | Priority 0 (highest), Priority 1:14 |                                           |

| Transmit End Interrupt      | Priority 15 (lowest - not valid if  | Transmit end interrupt priority selection |

| Priority                    | using ThreadX)                      | Transmit end interrupt priority selection |

|                             | Default: Priority 12                |                                           |

| Error Interrupt Drigrity    | Priority 0 (highest), Priority 1:14 |                                           |

|                             | Priority 15 (lowest - not valid if  | Error interrupt priority selection        |

| Error Interrupt Priority    | using ThreadX)                      |                                           |

|                             | Default: Priority 12                |                                           |

| ISDE Property                               | Value                                                                                                                      | Description                                                           |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Parameter Checking                          | BSP, Enabled, Disabled<br>Default: BSP                                                                                     | Selects if code for parameter checking is to be included in the build |

| Software Start                              | Enabled, Disabled<br>Default: Disabled                                                                                     | Software start selection                                              |

| Linker section to keep DTC vector table     | .ssp_dtc_vector_table                                                                                                      | Linker section to keep DTC vector table selection                     |

| Name                                        | g_transfer0                                                                                                                | Module name                                                           |

| Mode                                        | Normal                                                                                                                     | Mode selection                                                        |

| Transfer Size                               | 1 Byte                                                                                                                     | Transfer size selection                                               |

| Destination Address Mode                    | Fixed                                                                                                                      | Destination address mode selection                                    |

| Source Address Mode                         | Incremented                                                                                                                | Source address mode selection                                         |

| Repeat Area (Unused in<br>Normal Mode       | Source                                                                                                                     | Repeat area selection                                                 |

| Interrupt Frequency                         | After all transfers have completed                                                                                         | Interrupt frequency selection                                         |

| Destination Pointer                         | NULL                                                                                                                       | Destination pointer selection                                         |

| Source Pointer                              | NULL                                                                                                                       | Source pointer selection                                              |

| Number of Transfers                         | 0                                                                                                                          | Number of transfers selection                                         |

| Number of Blocks (Valid only in Block Mode) | 0                                                                                                                          | Number of blocks selection                                            |

| Activation Source (Must enable IRQ)         | Event SCI0 TXI                                                                                                             | Activation source selection                                           |

| Auto Enable                                 | False                                                                                                                      | Auto enable selection                                                 |

| Callback (Only valid with Software start)   | NULL                                                                                                                       | Callback selection                                                    |

| ELC Software Event<br>Interrupt Priority    | Priority 0 (highest), Priority 1:14<br>Priority 15 (lowest - not valid if<br>using ThreadX), Disabled<br>Default: Disabled | ELC Software Event interrupt priority selection.                      |

| ISDE Property                               | Value                                                                                                                      | Description                                                                 |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Parameter Checking                          | BSP, Enabled, Disabled<br>Default: BSP                                                                                     | Selects if code for parameter<br>checking is to be included in the<br>build |

| Software Start                              | Enabled, Disabled<br>Default: Disabled                                                                                     | Software start selection                                                    |

| Linker section to keep DTC vector table     | .ssp_dtc_vector_table                                                                                                      | Linker section to keep DTC vector table selection                           |

| Name                                        | g_transfer1                                                                                                                | Module name                                                                 |

| Mode                                        | Normal                                                                                                                     | Mode selection                                                              |

| Transfer Size                               | 1 Byte                                                                                                                     | Transfer size selection                                                     |

| Destination Address Mode                    | Incremented                                                                                                                | Destination address mode selection                                          |

| Source Address Mode                         | Fixed                                                                                                                      | Source address mode selection                                               |

| Repeat Area (Unused in<br>Normal Mode       | Destination                                                                                                                | Repeat area selection                                                       |

| Interrupt Frequency                         | After all transfers have<br>completed                                                                                      | Interrupt frequency selection                                               |

| Destination Pointer                         | NULL                                                                                                                       | Destination pointer selection                                               |

| Source Pointer                              | NULL                                                                                                                       | Source pointer selection                                                    |

| Number of Transfers                         | 0                                                                                                                          | Number of transfers selection                                               |

| Number of Blocks (Valid only in Block Mode) | 0                                                                                                                          | Number of blocks selection                                                  |

| Activation Source (Must enable IRQ)         | Event SCI0 RXI                                                                                                             | Activation source selection                                                 |

| Auto Enable                                 | False                                                                                                                      | Auto enable selection                                                       |

| Callback (Only valid with Software start)   | NULL                                                                                                                       | Callback selection                                                          |

| ELC Software Event Interrupt<br>Priority    | Priority 0 (highest), Priority 1:14<br>Priority 15 (lowest - not valid if<br>using ThreadX), Disabled<br>Default: Disabled | ELC Software Event interrupt priority selection.                            |

| Table 11. Configuration Settings for the Transfe | er Driver on r_dtc Event SCI0 RXI |

|--------------------------------------------------|-----------------------------------|

|--------------------------------------------------|-----------------------------------|

Note: The example values and defaults are for a project using the Synergy S7G2. Other MCUs may have different default values and available configuration settings.

# 5.2 SPI Framework Module Clock Configuration

The SPI peripheral module uses PCLKB as its clock source. The PCLKB frequency is set by using the SSP configurator clock tab prior to a build, or by using the CGC Interface at run-time.

## 5.3 SPI Framework Module Pin Configuration

The SPI peripheral module uses pins on the MCU to communicate to external devices. I/O pins must be selected and configured as required by the external device. The following table illustrates the method for selecting the pins within the SSP configuration window and the subsequent table illustrates an example selection for the SPI pins.

Note: For some peripherals, the operation mode selection determines what peripheral signals are available and thus what MCU pins are required.

| Resource | ISDE Tab | Pin selection Sequence                        |

|----------|----------|-----------------------------------------------|

| SCI      | Pins     | Select Peripherals > Connectivity: SCI> SCI1  |

| RSPI     | Pins     | Select Peripherals > Connectivity: SPI > SPI0 |

Note: The top selection sequence assumes SCI1 and SPI0 are the desired hardware targets for the driver and the bottom selection sequence assumes SPI0 is the desired target.

Table 13. Pin Configuration Settings for the SPI Framework Module

| Property        | Settings                                 | Description              |

|-----------------|------------------------------------------|--------------------------|

| Operation Mode  | Disabled, Asynchronous UART, Synchronous | Select Simple SPI as the |

|                 | UART, Simple I2C, Simple SPI, SmartCard  | Operation Mode for SPI   |

|                 | Default: Disabled                        | on SCI                   |

| CTS0_RTS0_SS0   | None, P103, P413                         | SS0 Pin selection        |

|                 | Default: None                            |                          |

| RXD0_SCL0_MISO0 | None, P100, P410                         | MISO0 Pin selection      |

|                 | Default: None                            |                          |

| SCK0            | None, P102, P412                         | SCK0 Pin selection       |

|                 | Default: None                            |                          |

| TXD1_SDA1_MOSI0 | None, P100, P410                         | MOSI0 Pin selection      |

|                 | Default: None                            |                          |

Note: The example values and defaults are for a project using the Synergy S7G2. Other MCUs may have different default values and available configuration settings.

## 5.4 SPI Framework Module Additional Settings

If external chip selects are being used, configure the chip select pins as GPIO outputs.

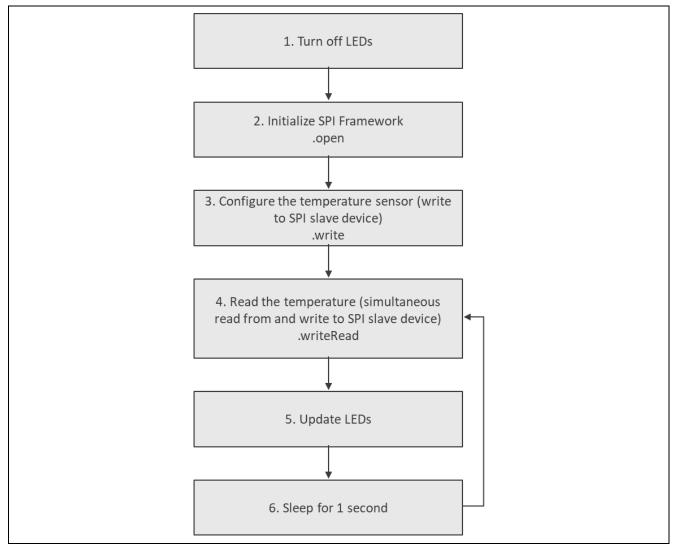

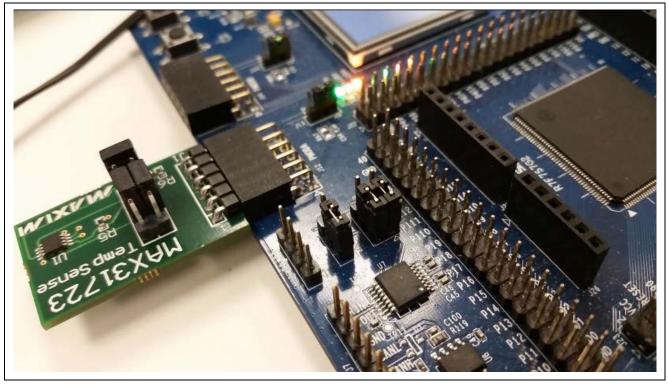

## 6. Using the SPI Framework Module in an Application

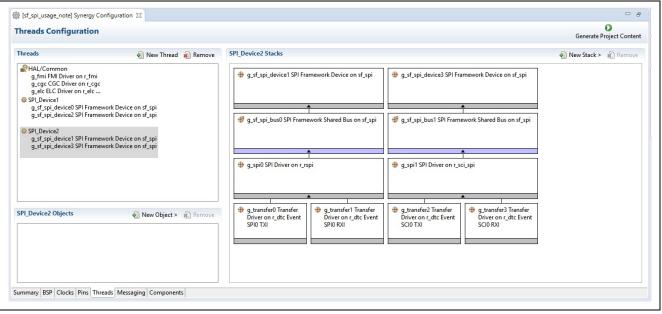

A common application for the SPI framework module requires multiple slave devices on a single bus. The implementation for this common application is described below. A second implementation shows two busses each with two slave devices attached.

#### Implementation Steps for Two Slave Devices on a Single Shared Bus

When using the SPI framework module to create a single bus with multiple slave devices, create two thread stacks each with an I2C framework instance. These instances will use the same shared bus instance. Follow the steps below to see how this is done within the SSP Configurator.

Note: The following steps assume some familiarity with the use of the SSP development environment. If any of the following steps are confusing, read over the first few chapters of the SSP User's Manual to become familiar with the SSP development environment.

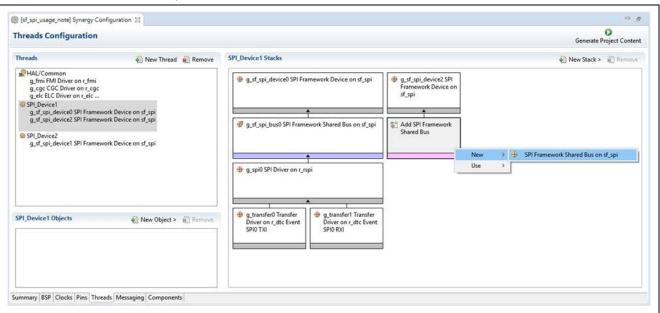

**Step 1**: Add the first SPI framework device module to a new or existing thread. This creates the SPI master stack. A shared bus on sf\_spi is added along with the I2C driver. The SPI driver can be selected for implementation on r\_rspi or r\_sci\_spi. The DTC transfer driver is also added by default. This can be removed if the CPU transfer mode is needed instead.

The resulting module stack is shown in the following figure. Example configuration settings are given in the tables that follow the figure.

| Threads                                                                                     | <ol> <li>New Thread Remove</li> </ol> | SPI_Device1 Stacks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 🕢 New Stack > 🔬 Remove |

|---------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| HAL/Common<br>g_fmi FMI Driver on r_f<br>g_cgc CGC Driver on r_e<br>g_elc ELC Driver on r_e | mi<br>cgc                             | g_sf_spi_device0 SPI Framework Device on sf_spi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                        |

| SPI_Device1                                                                                 | amework Device on sf_spi              | g_st_spi_bus0 SPI Framework Shared Bus on st_spi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                        |

|                                                                                             |                                       | € g_spi0 SPI Driver on r_sci_spi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                        |

|                                                                                             |                                       | grav ar one on the one of th |                        |

| SPL_Device1 Objects                                                                         | 🔊 New Object > 🦓 Remove               | g_transfer0 Transfer Driver on r_dtc Event SCI0 TXI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                        |

|                                                                                             |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                        |

Figure 3. Resulting Module Stack

Example configuration settings for the key first thread stack modules for Slave Device #1 are as follows:

| Table 14. Configuration Settings for the SPI Framework Module on sf_ | spi |

|----------------------------------------------------------------------|-----|

|                                                                      | ~~  |

| Property                    | Settings                  | Description                                                                                                                   |

|-----------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Parameter Checking          | Disabled                  | Enable or Disable Parameter Checking.                                                                                         |

| Name                        | g_sf_spi_device1          | Give a name to identify the SPI Framework<br>device. API, Config and Control instances<br>will be created based on this name. |

| Clock Phase                 | Data sampling on odd edge | Specify the clock phase for data variation and data sampling                                                                  |

| Clock Polarity              | Low when idle             | Select the clock polarity when clock is idle.                                                                                 |

| Clock Select Port           | 01                        | Select GPIO port used for the chip select.                                                                                    |

| Chip Select Pin             | 04                        | Select GPIO pin used for the chip select.                                                                                     |

| Chip Select Active<br>Level | Low                       | Select Polarity of the chip select signal.                                                                                    |

#### Table 15. Configuration Settings for the SPI Framework Shared Bus on sf\_spi

| Property | Settings      | Description                                                                                                                  |

|----------|---------------|------------------------------------------------------------------------------------------------------------------------------|

| Name     | g_sf_spi_bus0 | Give a name to identify the SPI Framework<br>shared bus. This shared bus will be shared<br>by multiple SPI Framework Devices |

#### Table 16. Configuration Settings for the SPI Driver on r\_rspi

| Property                           | Settings             | Description                                    |