# SH7262/SH7264 Group

Hardware Design Guide

REJ06B0999-0100 Rev. 1.00 Jun. 30, 2010

### Summary

This application note contains tips on designing a system using the SH7264. As a technical reference it will help the designer avoid common mistakes and get their product up and running when doing their first SH2A design.

### **Target Device**

SH7262/SH7264 MCU (In this document, SH7262/SH7264 are described as "SH7264".)

### Contents

| 1.  | Power Supplies          |

|-----|-------------------------|

| 2.  | Reset7                  |

| 3.  | Oscillator Circuit      |

| 4.  | Operating Mode Control  |

| 5.  | External ROM17          |

| 6.  | Handling of Pins        |

| 7.  | On-chip Resource Access |

| 8.  | Endianness              |

| 9.  | Power-down Modes        |

| 10. | References              |

### **Related Application Notes**

For more information, refer to the following application notes:

- SH7262/SH7264 Group Guidelines for Hi-Speed USB 2.0 Board Design

- SH7262/SH7264 Group Using Deep Standby Mode in Power-down Mode

- SH7262/SH7264 Group Connecting the NOR Flash Memory

- SH7262/SH7264 Group Interfacing Serial Flash Memory Using the Renesas Serial Peripheral Interface

### About Active-low Pins (Signals)

The symbol "#" suffixed to the pin (or signal) names indicates that the pins (or signals) are active-low.

### 1. Power Supplies

### **1.1 Power Supplies**

CPU core voltage is between 1.1 V and 1.3 V, and I/O power supply voltage is between 3.0 V and 3.6 V. This LSI (SH7264) uses both digital and analog power supplies. Place the digital circuit and analog circuit as far as possible on the board.

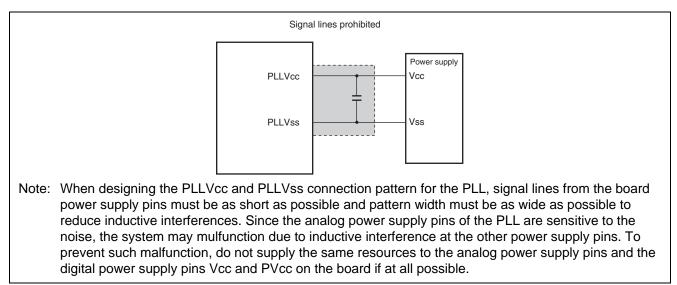

Table 1 lists the digital power supplies. Table 2 lists the analog power supplies. Figure 1 describes the note on using the PLL oscillator circuit.

| Symbol                  | Name                                                          | Voltage Range | Description                                                                                                                                         |

|-------------------------|---------------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc                     | Power Supply                                                  | 1.1 to 1.3 V  | Power supply pin<br>Connect all Vcc pins to the system power<br>supply. The system does not work when any<br>of those pins are open.                |

| Vss                     | Ground                                                        | 0 V           | Ground pin<br>Connect all Vss pins to the system power<br>supply (0 V). The system does not work<br>when any of those pins are open.                |

| PVcc                    | I/O circuit power supply                                      | 3.0 to 3.6 V  | Power supply pin for I/O pins. Connect all<br>PVcc pins to the system power supply. The<br>system does not work when any of those<br>pins are open. |

| USBDPVcc <sup>(2)</sup> | Transceiver digital pin<br>power supply                       | 3.0 to 3.6 V  | Power supply for USB pins                                                                                                                           |

| USBDPVss <sup>(3)</sup> | Transceiver digital pin ground                                | 0 V           | Ground for USB pins                                                                                                                                 |

| USBDVcc <sup>(1)</sup>  | Transceiver digital core power supply                         | 1.1 to 1.3 V  | Power supply for USB core                                                                                                                           |

| USBDVss <sup>(3)</sup>  | Transceiver digital core ground                               | 0 V           | Ground for USB core                                                                                                                                 |

| USBUVcc <sup>(1)</sup>  | Power supply for 480-<br>MHz USB 2.0<br>host/function modules | 1.1 to 1.3 V  | Power supply for 480-MHz modules                                                                                                                    |

| USBUVss <sup>(3)</sup>  | Ground for 480-MHz<br>USB 2.0 host/function<br>modules        | 0 V           | Ground for 480-MHz modules                                                                                                                          |

#### **Table 1 Digital Power Supplies**

Notes: 1. USBAVcc, USBDVcc, and USBUVcc must be at the same electric potential as the Vcc.

2. USBAPVcc and USBDPVcc must be at the same electric potential as the PVcc.

3. USBAVss, USBDVss, USBUVss, USBAPVss, and USBDPVss must be at the same potential as the Vss.

| Symbol                     | Name                                    | Voltage Range | Description                              |

|----------------------------|-----------------------------------------|---------------|------------------------------------------|

| PLLVcc                     | PLL power supply                        | 1.1 to 1.3 V  | Power supply for internal PLL oscillator |

| PLLVss                     | PLL ground                              | 0 V           | Ground pin for internal PLL oscillator   |

| USBAPVcc <sup>(2)(4)</sup> | Transceiver analog pin<br>power supply  | 3.0 to 3.6 V  | Power supply for USB pins                |

| USBAPVss <sup>(3)(4)</sup> | Transceiver analog pin ground           | 0 V           | Ground for USB pins                      |

| USBAVcc <sup>(1)(4)</sup>  | Transceiver analog core<br>power supply | 1.1 to 1.3 V  | Power supply for USB pins                |

| USBAVss <sup>(3)(4)</sup>  | Transceiver analog core ground          | 0 V           | Ground for USB core                      |

| AVcc (5) (7)               | Analog power supply                     | 3.0 to 3.6 V  | A/D Converter power supply pin           |

| AVss (5) (7)               | Analog ground                           | 0 V           | A/D Converter ground pin                 |

| AVref <sup>(6)(7)</sup>    | Analog reference voltage                | 3.0 to 3.6 V  | A/D Converter reference voltage pin      |

#### **Table 2 Analog Power Supplies**

Notes: 1. USBAVcc, USBDVcc, and USBUVcc must be at the same electric potential as the Vcc.

2. USBAPVcc and USBDPVcc must be at the same electric potential as the PVcc.

- 3. USBAVss, USBDVss, USBUVss, USBAPVss, and USBDPVss must be at the same electric potential as the Vss.

- 4. Isolate analog power supplies (USBAVcc, USBAVss, USBAPVcc, and USBAPVss) from the digital power supplies.

- 5. AVcc must be set as PVcc −0.3 V ≤ AVcc ≤ PVcc. AVss must be at the same electric potential as the Vss.

Do not open pins AVcc and AVss when not using the A/D Converter, or in software standby mode. When not using the A/D Converter, connect AVcc to PVcc, and AVss to Vss, respectively.

- 6. Set the reference voltage range of the AVref pin as  $3.0 \text{ V} \leq \text{AVref} \leq \text{AVcc}$ .

- 7. Isolate AVref and AVcc (also A/D Converter analog input pin) from the digital circuit with the AVss. AVss must be connected on a stable digital ground (Vss) on board.

Figure 1 Note on Using PLL Oscillation Circuit

# 1.2 Bypass Capacitor

A multilayer ceramic capacitor must be installed as a bypass capacitor for each pair of power supply pins. Install the bypass capacitor as close as possible to the LSI power supply pins. Connect the bypass capacitor with capacitance between 0.1 and  $0.33 \,\mu\text{F}$  (recommended value).

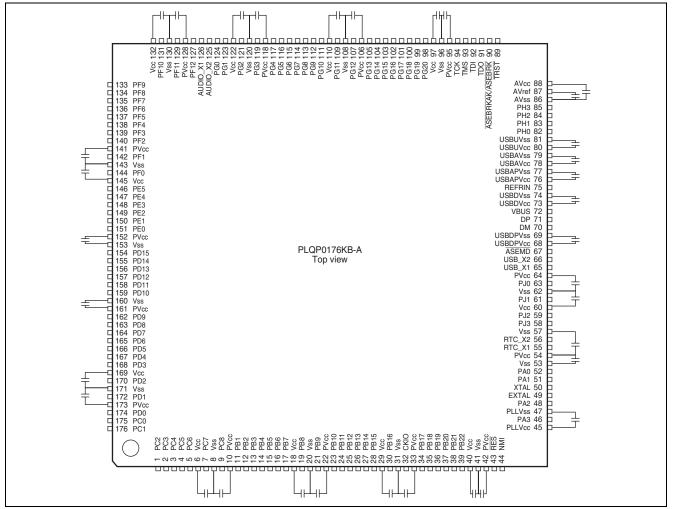

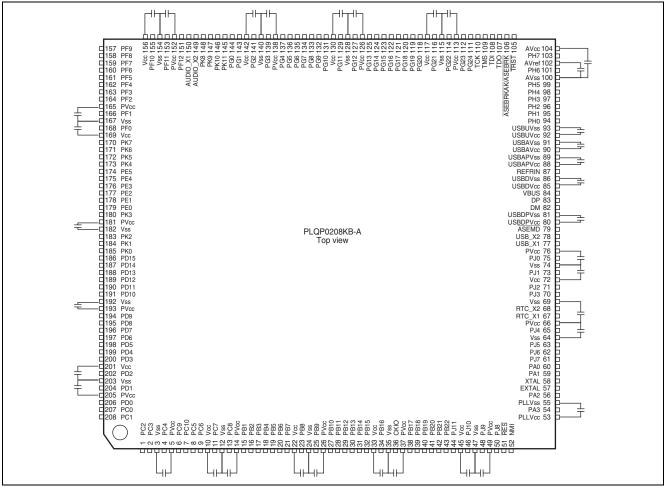

Figure 2 shows an example of installing an external capacitor with the SH7262. Figure 3 shows an example of installing an external capacitor with the SH7264.

Figure 2 Installing an External Capacitor with the SH7262

### SH7262/SH7264 Group

Figure 3 Installing an External Capacitor with the SH7264

### 2. Reset

### 2.1 Power-on/Power-off Sequence

Either the 1.2 V power supplies (Vcc, PLVcc, USBAVcc, USBDVcc, and USBUVcc) or 3.3 V power supplies (PVcc, AVcc, USBAPVcc, and USBDPVcc) can be turned ON or OFF first.

When turning ON the SH7264, make sure to fix pins TRST# and RES# to low level. If not, output pins and I/O pins (output) may be in undefined state to cause malfunction in the entire system.

To avoid such malfunction described above, make sure to fix pins TRST# and RES# to low level when turning OFF the SH7264.

### 2.2 Oscillation Settling Time

When the RES# pin is driven low, the SH7264 enters the power-on reset state. To make sure to reset the SH7264, the RES# pin must be kept at the low level during the oscillation settling time at power-on, or when exiting from software standby mode and deep standby mode. Keep the RES# pin at low level for at least 20  $t_{cyc}$  when setting the RES# pin to low level while the clock is running.

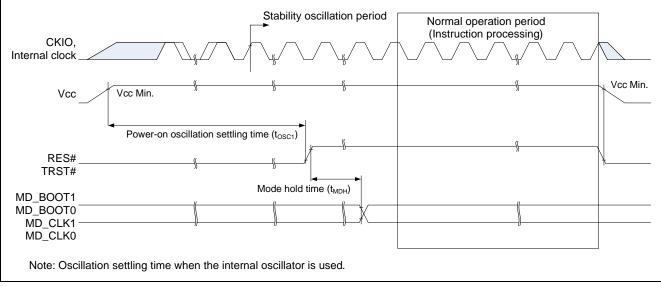

The power-on oscillation settling time  $(t_{osc1})$  is 10 ms, which is specified from when the Vcc exceeds the minimum operating voltage until the RES# pin exceeds the V<sub>IL</sub> voltage. Figure 4 shows the relation between power-on/off and clock, reset signals. This timing is easily accommodated by many "supervisor" ICs available on the market such as Renesas Electronics RNA51957BFP.

Figure 4 Relations between Power-on/off and Clock, Reset Signals

### 2.3 Power-on Reset

The SH7264 has two reset options; power-on reset and manual reset. This section describes sources for the power-on reset exception handling.

#### 2.3.1 Power-on Reset by the RES# Pin

When the RES# pin is driven low, the SH7264 enters power-on reset state to initialize the CPU's internal state and all on-chip peripheral registers <sup>(note)</sup>. In power-on reset state, power-on reset exception handling starts when the RES# pin is first driven low for a fixed period and then returns to high. For more information on the "fixed period" to drive the RES# pin low, refer to 2.2 Oscillation Settling Time.

### 2.3.2 Power-on Reset by the User Debug Interface (H-UDI) Reset Assert Command

When the H-UDI reset assert command is set, the SH7264 enters the power-on reset state to initialize the CPU's internal state and all on-chip peripheral registers <sup>(note)</sup>, like the power-on reset by the RES# pin. Power-on reset exception handling starts in power-on reset state. The period required between the H-UDI reset assert command and the H-UDI reset negate command is the same as the period to drive the RES# pin low to start the power-on reset.

### 2.3.3 **Power-on Reset by the Watchdog Timer (WDT)**

When setting the WDT as watchdog timer mode, and specifying the power-on reset when the WDT watchdog timer counter (WTCNT) overflows, the SH7264 enters power-on reset state and the WDT starts power-on reset exception handling, however, the Watchdog reset control/status register (WRCSR) of the WDT and the Frequency control register (FRQCR) of the Clock Pulse Generator (CPG) are not initialized <sup>(note)</sup>.

Note: For more information on register status, refer to 36.3 Register States in Each Operating Mode in the SH7262 Group, SH7264 Group Hardware Manual.

### 2.4 Manual Reset

This section describes sources for the manual reset exception handling.

#### 2.4.1 Manual Reset by the Watchdog Timer (WDT)

When setting the WDT as watchdog timer mode, and specifying the manual reset when the WTCNT of the WDT overflows, the SH7264 enters manual reset state and the WDT starts manual reset exception handling.

When the SH7264 enters manual reset state while the CPU is leaving the bus or the Direct Memory Access Controller (DMAC) transfers data in burst mode, the manual reset exception handling is deferred until the CPU retrieves the bus.

In manual reset state, the SH7264 initializes CPU and the BN bit in the Bank number register (IBNR) of the Interrupt controller (INTC), but FPU and other modules are not included <sup>(note)</sup>.

Note: For more information on register status, refer to 36.3 Register States in Each Operating Mode in the SH7262 Group, SH7264 Group Hardware Manual.

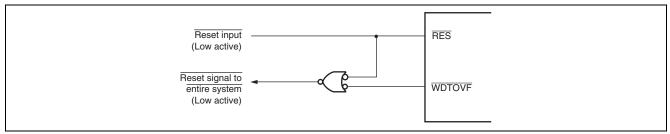

### 2.5 System Reset by the Watchdog Timer (WDT)

Sometimes it is desirable to have the WDT reset the entire system during an overflow condition using the WDTOVF# signal from the WDT. In this case the WDTOVF# should be not be connected directly to the RES# of the MCU as this would cause problems. A "tiny" gate can be used to OR the "power-on" reset signal and the WDTOVF# as shown in Figure 5: System Reset using WDTOVF#.

# 3. Oscillator Circuit

### 3.1 Clock Pins

Pins listed in the following table can be connected to crystal resonators or input clocks.

#### Table 3 Clock pins

| Xin Pin<br>(Crystal resonator can be<br>connected, or used as<br>external clock input pin) | Xout Pin<br>(Crystal resonator can be<br>connected) | Remarks                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTAL                                                                                      | XTAL                                                | 10 MHz to 18 MHz                                                                                                                                                                                                                                                                                                    |

| USB_X1                                                                                     | USB_X2                                              | <ul> <li>When the USB controller is in high-speed:<br/>48 MHz ± 100 ppm</li> <li>When the USB controller is NOT in high-speed and<br/>operating as the USB host:<br/>48 MHz ± 500 ppm</li> <li>When the USB controller is NOT in high-speed and<br/>operating as the USB function:<br/>48 MHz ± 2500 ppm</li> </ul> |

| AUDIO_X1                                                                                   | AUDIO_X2                                            | <ul> <li>When connecting a crystal resonator<br/>10 MHz to 25 MHz</li> <li>When inputting an external clock<br/>1 MHz to 25 MHz</li> </ul>                                                                                                                                                                          |

| RTC_X1                                                                                     | RTC_X2                                              | 32.768 kHz                                                                                                                                                                                                                                                                                                          |

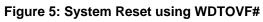

### 3.2 Connecting an External Clock

Figure 6 shows an example of connecting an external clock to the SH7264. When leaving the Xout pin as open, the parasitic capacitance must be less than 10 pF.

Figure 6 Connecting an External Clock

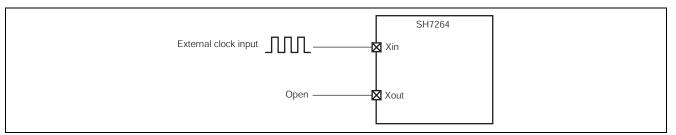

### 3.3 Connecting a Crystal resonator

Figure 7 shows an example of connecting a crystal resonator to the SH7264.

Place the crystal resonator and capacitors (CL1 and CL2) as close to pins Xin and Xout as possible. To avoid inductance and to allow the crystal resonator to oscillate accurately, use the points when the capacitors area connected to the crystal resonator in common and do not place wiring patters close to these components.

Since all the characteristics of the crystal resonator affect the board design, refer to the example shown in Figure 7 and evaluate the entire system before using. As the circuit ratings of the crystal resonator vary with the resonator and the floating capacitance, it is recommended to consult the crystal resonator manufacturer on the constants. Make sure that the applied voltage to the clock pin does not exceed the maximum rating.

The SH7264 includes the feedback resistor, however, an external feedback resistor may be required, according to the characteristics of the crystal resonator. Evaluate the resistor and capacitor thoroughly to set the parameters.

When not using pins Xin and Xout, fix the level on the Xin pin such as pull-up, pull-down, connect to the power supply or ground, and leave the Xout pin as open.

Figure 7 Connecting a Crystal Resonator

### 4. Operating Mode Control

The SH7264 has four boot modes and four clock operating modes. These modes can be set by pins MD\_BOOT1, MD\_BOOT0, MD\_CLK1, and MD\_CLK0.

### 4.1 Boot Modes

#### 4.1.1 Setting the External Pins to Specify Boot Mode

When the RES# pin is driven low, the SH7264 specifies boot mode by external pins. Table 4 lists the relationship between external pins and boot modes.

| MD_BOOT1 | MD_BOOT0 | Boot Mode                                                                                                                         |

|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------|

| 0        | 0        | Boots the MCU from the memory connected to CS0 space (Boot mode 0)                                                                |

| 0        | 1        | Boots the MCU from serial flash memory connected to the Renesas Serial Peripheral Interface channel 0 at high speed (Boot mode 1) |

| 1        | 0        | Boots the MCU from NAND flash memory connected to the NAND flash memory controller (Boot mode 2)                                  |

| 1        | 1        | Boots the MCU from serial flash memory connected to the Renesas Serial Peripheral Interface channel 0 at low speed (Boot mode 3)  |

| Table 4 Relationship between External Pins and Boot Modes |

|-----------------------------------------------------------|

|-----------------------------------------------------------|

#### 4.1.2 Boot Mode 0

Boot mode 0 allows the engineer to boot the SH7264 from memory which is connected to CS0 space. This section describes the steps initiated by the MCU in boot mode 0  $^{(note)}$ .

(1) Retrieve the execution start address from the exception handling vector table

After waking up from power-on reset, CPU retrieves the initial values of the program counter (PC) and stack pointer (SP) from the exception handling vector table which is allocated to the CS0 space-connected memory.

(2) Start executing the program

CPU starts executing the program from the PC address retrieved.

NOTE: There is often misunderstanding between booting and execution. Boot Mode 0 actually allows the execution "in place" (i.e. directly from NOR FLASH). The engineer is not required to move code into RAM when in Boot mode 0, nor does it preclude the user from copying and executing the code from RAM (the common notion of booting). NAND and SPI mode are true "boot modes" where the code must be moved from the non-volatile (FLASH) to RAM (internal or external) to be executed.

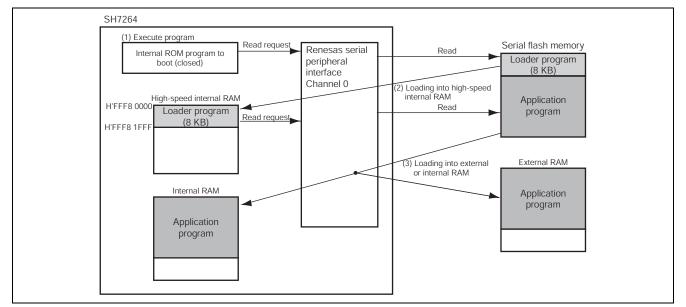

#### 4.1.3 Boot Modes 1 and 3

Boot modes 1 and 3 allow the engineer to boot the SH7264 from serial flash memory which is connected to channel 0 of the Renesas Serial Peripheral Interface (RSPI). This section describes boot modes 1 and 3. Steps 1 and 2 are initiated by the MCU in SPI boot mode, step 3 (optional) is a function of the "loader" that is being executed <sup>(note)</sup>.

NOTE: This step is listed as optional because the "loader" may not actually perform an application load for various reasons (bad image in FLASH, waiting on Hardware response, waiting on "security" key, etc).

(1) Execute the Internal ROM program to boot

After waking up from power-on reset, CPU executes the program stored in the Internal ROM program to boot (closed).

(2) Transfer the loader program

CPU transfers an 8-KB loader program from the start address of the serial flash memory connected to RSPI channel 0 to the start address of high-speed internal RAM.

In boot mode 1, the communication speed is at the 1/2 of the bus clock  $(B\phi)$ . In boot mode 3, the communication speed is at the 1/4 of the bus clock  $(B\phi)$ . Set the boot mode according to the specifications of the serial flash memory used.

After transferring the loader program is completed, CPU jumps to high-speed internal RAM to start executing the transferred loader program.

#### (3) Transfer the application program (optional)

Use the RSPI within the loader program to load data from serial flash memory to internal RAM or external RAM.

Figure 8 shows the schematic view of boot modes 1 and 3.

Figure 8 Boot Modes 1 and 3 Schematic View

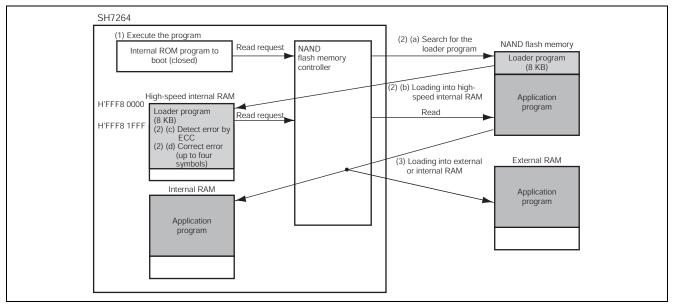

#### 4.1.4 Boot Mode 2

Boot mode 2 allows the engineer to boot the SH7264 from NAND flash memory which is connected to the SH7264 NAND flash memory controller. The SH7264 supports the large-block (2048 bytes + 64 bytes) NAND flash memory with 5-byte address cycles (bigger than 2 Gb density). Number of ECC errors corrected is up to 4. This section describes the steps to initiate boot mode 2. This section describes the steps in boot mode 2. Steps 1 and 2 are initiated by the MCU in NAND boot mode, step 3 (optional) is a function of the "loader" that is being executed <sup>(note)</sup>.

NOTE: This step is listed as optional because the "loader" may not actually perform an application load for various reasons (bad image in FLASH, waiting on Hardware response, waiting on "security" key, etc).

(1) Execute the Internal ROM program to boot

After waking up from power-on reset, CPU executes the program stored in the Internal ROM program to boot (closed).

(2) Transfer the loader program

CPU transfers an 8-KB loader program from the NAND flash memory connected to the NAND flash memory controller to the start address of high-speed internal RAM, as the following steps.

It searches the loader program in NAND flash memory, transfers the loader program to the high-speed internal RAM, and jumps to the entry function of the loader program.

(a) Searches for loader program store blocks (block address 0 to 1023, maximum)

- (b) Reads the 8-KB loader program (16 sectors), transfers the loader program to the high-speed internal RAM

- (c) Detects errors by ECC

- (d) Corrects errors (up to four symbols)

After transferring the loader program is completed, CPU jumps to high-speed internal RAM to start executing the transferred loader program.

(3) Transfer the application program (optional)

Use the NAND flash memory controller within the loader program to load data from NAND flash memory to internal RAM or external RAM.

Figure 9 shows the schematic view of boot mode 2.

Figure 9 Boot Mode 2 Schematic View

### 4.2 Clock Operating Modes

### 4.2.1 External Pins Setting to Decide Clock Operating Modes

When the RES# pin is driven low, the SH7264 uses external pins to decide clock operating modes.

Table 5 lists the relationship between external pins and clock operating modes.

| Mode | Pin Combination |         | Clock I/O      |        | Divider | PLL      | CKIO Frequency         |

|------|-----------------|---------|----------------|--------|---------|----------|------------------------|

|      | MD_CLK1         | MD_CLK0 | Source         | Output | 1       | Circuit  |                        |

| 0    | 0               | 0       | EXTAL/crystal  | CKIO   | 1       | ON (×12) | (EXTAL/crystal) × 4    |

| 1    | 0               | 1       | USB_X1/crystal | CKIO   | 1/4     | ON (×12) | (USB_X1/crystal)       |

| 2    | 1               | 0       | EXTAL/crystal  | CKIO   | 1       | ON (×8)  | (EXTAL/crystal) × 4    |

| 3    | 1               | 1       | USB_X1/crystal | CKIO   | 1/3     | ON (×8)  | (USB_X1/crystal) × 4/3 |

#### Table 5 Relationships between External Pins and Clock Operating Modes

#### 4.2.2 Mode 0

Mode 0 provides the clock from the EXTAL pin or a crystal resonator. PLL circuit shapes the waveform and multiplies the frequency to supply the clock to the SH7264. EXTAL pin input clock and crystal resonator within the range of 10 MHz and 12 MHz can be used in mode 0. The CKIO frequency range is 40 MHz to 48 MHz. When the USB 2.0 host or function module is not used, fix the EXTAL pin (connect to pull-up or pull-down resistors, connect to the power supply or ground) and leave the USB\_X2 pin open to reduce the power consumption.

### 4.2.3 Mode 1

Mode 1 provides the clock from the USB\_X1 pin or a crystal resonator. PLL circuit shapes the waveform, sets the Frequency control register (FRQCR) to multiply the frequency, and supplies the clock to the SH7264. The CKIO frequency range is (USB\_X1/crystal) (48 MHz). To reduce the power consumption, fix the EXTAL pin (connect to pull-up or pull-down resistors, connect to the power supply or ground) and leave the XTAL pin open when using the SH7264 in mode 1.

#### 4.2.4 Mode 2

Mode 2 provides the clock from EXTAL pin or a crystal resonator. PLL circuit shapes the waveform and multiplies the frequency to supply the clock to the SH7264. EXTAL pin input clock and crystal resonator within the range between 10 MHz and 18 MHz can be used in mode 2. The CKIO frequency range is 40 MHz to 72 MHz. When the USB 2.0 host or function module is not used, fix the USB\_X1 pin (connect to pull-up or pull-down resistors, connect to the power supply or ground), and leave the USB\_X2 pin open to reduce the power consumption.

#### 4.2.5 Mode 3

Mode 3 provides the clock from the USB\_X1 pin or a crystal resonator. PLL circuit shapes the waveform, sets the FRQCR to multiply the frequency, and supplies the clock to the SH7264. The CKIO frequency range is  $(USB_X1/crystal resonator) \times 4/3$  (64 MHz). To reduce the power consumption, fix the EXTAL pin (connect to pull-up or pull-down resistors, connect to the power supply or ground), and leave the XTAL pin open when using the SH7264 in mode 3.

### 4.2.6 Available Clock Frequency Range

Table 6 lists clock operating modes and available clock frequency range; do not set these pins other than the combinations shown in the table below.

| Clock<br>Operating | FRQCR<br>Setting | PLL<br>Multiplier | Ratio of<br>Internal                           | Available                     | Clock Freque                  | ency Range (I          | MHz)              |                          |

|--------------------|------------------|-------------------|------------------------------------------------|-------------------------------|-------------------------------|------------------------|-------------------|--------------------------|

| Mode               | (1)              | PLL<br>Circuit    | Clock<br>Frequencies<br>(I:B:P) <sup>(2)</sup> | Input<br>Clock <sup>(3)</sup> | Output<br>Clock<br>(CKIO pin) | Internal<br>Clock (Ιφ) | Bus Clock<br>(Βφ) | Peripheral<br>Clock (Ρφ) |

| 0                  | H'x104           | ON (×12)          | 12:4:2                                         | 10 to 12                      | 40 to 48                      | 120 to 144             | 40 to 48          | 20 to 24                 |

|                    | H'x106           | ON (×12)          | 12:4:1                                         | 10 to 12                      | 40 to 48                      | 120 to 144             | 40 to 48          | 10 to 12                 |

|                    | H'x124           | ON (×12)          | 4:4:2                                          | 10 to 12                      | 40 to 48                      | 40 to 48               | 40 to 48          | 20 to 24                 |

|                    | H'x126           | ON (×12)          | 4:4:1                                          | 10 to 12                      | 40 to 48                      | 40 to 48               | 40 to 48          | 10 to 12                 |

| 1                  | H'x104           | ON (×12)          | 3:1:1/2                                        | 48                            | 48                            | 144                    | 48                | 24                       |

|                    | H'x106           | ON (×12)          | 3:1:1/4                                        | 48                            | 48                            | 144                    | 48                | 12                       |

|                    | H'x124           | ON (×12)          | 1:1:1/2                                        | 48                            | 48                            | 48                     | 48                | 24                       |

|                    | H'x126           | ON (×12)          | 1:1:1/4                                        | 48                            | 48                            | 48                     | 48                | 12                       |

| 2                  | H'x003           | ON (×8)           | 8:4:2                                          | 10 to 18                      | 40 to 72                      | 80 to 144              | 40 to 72          | 20 to 36                 |

|                    | H'x004           | ON (×8)           | 8:4:4/3                                        | 10 to 18                      | 40 to 72                      | 80 to 144              | 40 to 72          | 13.3 to 24               |

|                    | H'x005           | ON (×8)           | 8:4:1                                          | 10 to 18                      | 40 to 72                      | 80 to 144              | 40 to 72          | 10 to 18                 |

|                    | H'x006           | ON (×8)           | 8:4:2/3                                        | 10 to 18                      | 40 to 72                      | 80 to 144              | 40 to 72          | 6.7 to 12                |

|                    | H'x013           | ON (×8)           | 4:4:2                                          | 10 to 18                      | 40 to 72                      | 40 to 72               | 40 to 72          | 20 to 36                 |

|                    | H'x014           | ON (×8)           | 4:4:4/3                                        | 10 to 18                      | 40 to 72                      | 40 to 72               | 40 to 72          | 13.3 to 24               |

|                    | H'x015           | ON (×8)           | 4:4:1                                          | 10 to 18                      | 40 to 72                      | 40 to 72               | 40 to 72          | 10 to 18                 |

|                    | H'x016           | ON (×8)           | 4:4:2/3                                        | 10 to 18                      | 40 to 72                      | 40 to 72               | 40 to 72          | 6.7 to 12                |

| 3                  | H'x003           | ON (×8)           | 8/3:4/3:2/3                                    | 48                            | 64                            | 128                    | 64                | 32                       |

|                    | H'x004           | ON (×8)           | 8/3:4/3:4/9                                    | 48                            | 64                            | 128                    | 64                | 21.3                     |

|                    | H'x005           | ON (×8)           | 8/3:4/3:1/3                                    | 48                            | 64                            | 128                    | 64                | 16                       |

|                    | H'x006           | ON (×8)           | 8/3:4/3:2/9                                    | 48                            | 64                            | 128                    | 64                | 10.7                     |

|                    | H'x013           | ON (×8)           | 4/3:4/3:2/3                                    | 48                            | 64                            | 64                     | 64                | 32                       |

|                    | H'x014           | ON (×8)           | 4/3:4/3:4/9                                    | 48                            | 64                            | 64                     | 64                | 21.3                     |

|                    | H'x015           | ON (×8)           | 4/3:4/3:1/3                                    | 48                            | 64                            | 64                     | 64                | 16                       |

|                    | H'x016           | ON (×8)           | 4/3:4/3:2/9                                    | 48                            | 64                            | 64                     | 64                | 10.7                     |

#### Table 6 Relationship between Clock Operating Mode and Clock Frequency Range

Notes: 1. "x" in the FRQCR setting depends on the setting in bits 12, 13, and 15.

2. The ratio of clock frequencies, where the input clock frequency is assumed to be 1.

3. These values are the clock frequencies of the EXTAL pin input or a crystal resonator in modes 0 and 2.

In modes 1 and 3, these values are the clock frequencies of the USB\_X1 pin input or a crystal resonator.

### 5. External ROM

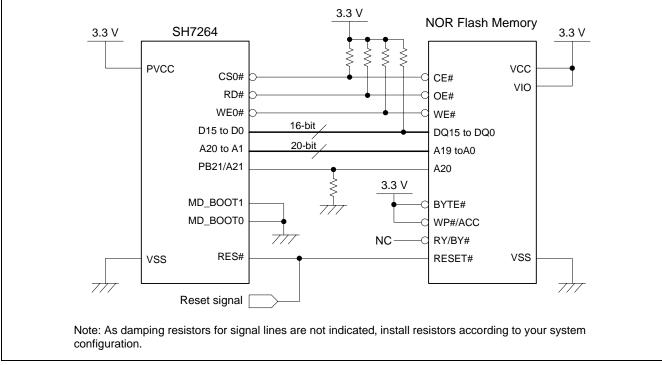

### 5.1 NOR Flash Memory

Figure 10 shows an example of NOR flash memory circuit.

For more information, refer to the application note "SH7262/SH7264 Group Connecting the NOR Flash Memory".

#### Figure 10 Typical NOR Flash Memory Circuit

#### 5.1.1 Data Bus Width

On the SH7264 device, CS0 space (area 0) is fixed to 16-bit bus width. The NOR flash memory on CS0 must be connected to operate as 16-bit memory. The NOR flash memory shown in Figure 10 is fixed to 16 bit operation by setting the BYTE# pin to high level.

To boot the SH7264 from NOR flash memory, fix the SH7264 MD\_BOOT0 and MD\_BOOT1 pins to low level (boot mode 0).

### 5.1.2 NOR Boot Mode BSC Initial State

In Boot Mode 0 (NOR Boot), the Bus State Controller must be programmed to operate with NOR FLASH. To provide maximum flexibility in the engineers design, the minimal configuration is performed as follows, A1-A20 active, D0-D15 as data bus, RD# and CS0# active. Engineers implementing large NOR FLASH using address lines above A20, must pull these down using resistors to logic 0 to allow code to be fetched from address 0 in the NOR FLASH. An example of this is shown in Figure 10 on A21. Once the user's code is running they can program the BSC to support the higher address lines as required by their design.

### 5.1.3 Control signals

The WE0# is configured as I/O port as default, and will be input by default on power up (Hi-Z) until the BSC is programmed, so a pull-up is recommend to avoid improper operation of the NOR FLASH as shown in Figure 10 <sup>(note)</sup>.

NOTE: In general control signals will be undefined during the RESET period before the BSC is initialized, so to get more stable memory operation, pull up pins CS0#, RD#, and WE0# to high level using external resistors. Pull-ups are also recommended on any other CS# and WE# signals used in your design.

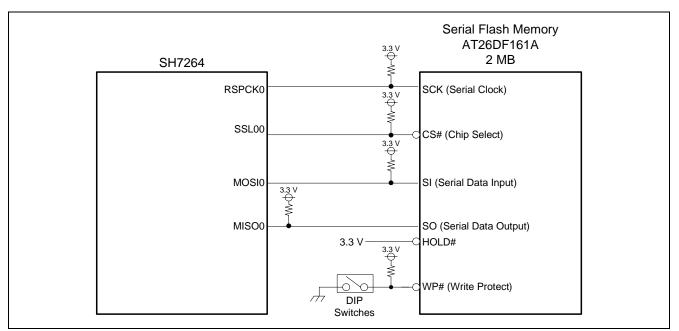

### 5.2 Serial Flash Memory

Connect the serial flash memory to the SH7264 internal Renesas Peripheral Interface (RSPI). Figure 11 shows an example of serial flash memory circuit. Set the SH7264 pin functions as shown in Table 7.

For more information, refer to the application note "SH7262/SH7264 Group Interfacing Serial Flash Memory Using the Renesas Serial Peripheral Interface".

#### Figure 11 Typical Serial Flash Memory Circuit

Note: Pull up or pull down the control signal pins using external resistors.

Pull up or pull down the control signal pins, so the external device does not malfunction when the MCU pins are in the high impedance state. SSL00 pin is pulled up by the external resistor to high level. Pull up or down the RSPCK0 and MOSI0 pins. As the MISO0 pin is an input pin, pull up or down it to avoid floating to an invalid logic level..

| Peripheral | Pin Name | SH7264 Port Control Register |                     | – SH7264                                |  |

|------------|----------|------------------------------|---------------------|-----------------------------------------|--|

| Functions  |          | Register<br>Name             | MD Bit Setting      | Multiplexed Pin Name                    |  |

| RSPI       | MISO0    | PFCR3                        | PF12MD[2:0] = B'011 | PF12/BS#/MISO0/TIOC3D/SPDIF_OUT         |  |

|            | MOSI0    | PFCR2                        | PF11MD[2:0] = B'011 | PF11/A25/SSIDATA3/MOSI0/TIOC3C/SPDIF_IN |  |

|            | SSL00    | PFCR2                        | PF10MD[2:0] = B'011 | PF10/A24/SSIWS3/SSL00/TIOC3B/FCE#       |  |

|            | RSPCK0   | PFCR2                        | PF9MD[2:0] = B'011  | PF9/A23/SSISCK3/RSPCK0/TIOC3A/FRB       |  |

#### **Table 7 Multiplexed Pins**

Note: SH7264 Multiplexed Pins

MISO0, MOSI0, SSL00, and RSPCK0 pins are multiplexed, and set to general-purpose I/O ports as default. Before accessing serial flash memory, use the general-purpose I/O port control register to set the multiplexed pins to RSPI pins. In SPI Boot mode, these pins are programmed by the loader on power up (refer to SPI boot mode operation).

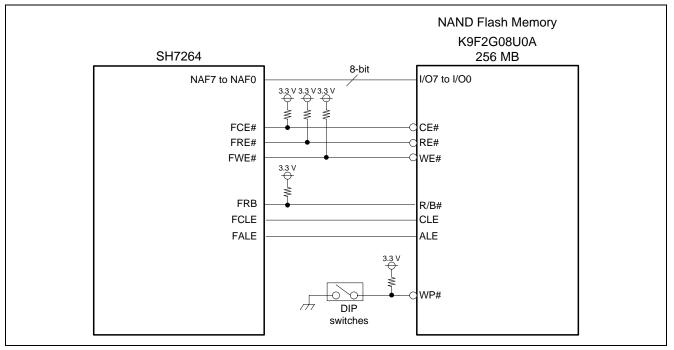

### 5.3 NAND Flash Memory

Figure 12 shows an example of NAND flash memory circuit. Set the SH7264 pin functions as shown in Table 8.

#### Figure 12 Typical NAND Flash Memory Circuit

Note: Pull up or pull down the control signal pins using external resistors.

Pull up or pull down the control signal pins, so the external device does not malfunction when the MCU pins are in the high impedance state. FCE#, FRE#, and FWE# pins are pulled up by the external resistor to high level. FRB pin is also pulled up by an external resistor to high level, as the pin cannot issue commands at low level.

| Devinhevel             |                             | SH7264 Pc                                            | ort Control Register                    |                                   |  |

|------------------------|-----------------------------|------------------------------------------------------|-----------------------------------------|-----------------------------------|--|

| Peripheral<br>Function | Pin Name                    | Register<br>Name                                     | MD Bit Setting                          | SH7264 Multiplexed Pin Name       |  |

| NAND Flash             | NAF4 to NAF7 <sup>(1)</sup> | PDCR3                                                | PD15MD[1:0] = B'01                      | PD15/D15/NAF7/PWM2H               |  |

| Memory                 |                             |                                                      | PD14MD[1:0] = B'01                      | PD14/D14/NAF6/PWM2G               |  |

| Controller             |                             |                                                      | PD13MD[1:0] = B'01                      | PD13/D13/NAF5/PWM2F               |  |

|                        |                             | PD12MD[1:0] = B'01                                   |                                         | PD12/D12/NAF4/PWM2E               |  |

|                        | NAF0 to NAF3 <sup>(1)</sup> | NAF0 to NAF3 <sup>(1)</sup> PDCR2 PD11MD[1:0] = B'01 |                                         | PD11/D11/NAF3/PWM2D               |  |

|                        |                             |                                                      | PD10MD[1:0] = B'01<br>PD9MD[1:0] = B'01 | PD10/D10/NAF2/PWM2C               |  |

|                        |                             |                                                      |                                         | PD9/D9/NAF1/PWM2B                 |  |

|                        |                             |                                                      | PD8MD[1:0] = B'01                       | PD8/D8/NAF0/PWM2A                 |  |

|                        | FWE# <sup>(1)</sup>         | PDCR1                                                | PD7MD[1:0] = B'01                       | PD7/D7/FWE#/PWM1H                 |  |

|                        | FALE <sup>(1)</sup>         | PDCR1                                                | PD6MD[1:0] = B'01                       | PD6/D6/FALE/PWM1G                 |  |

|                        | FCLE <sup>(1)</sup>         | PDCR1                                                | PD5MD[1:0] = B'01                       | PD5/D5/FCLE/PWM1F                 |  |

|                        | FRE# <sup>(1)</sup>         | PDCR1                                                | PD4MD[1:0] = B'01                       | PD4/D4/FRE#/PWM1E                 |  |

|                        | FCE#                        | PFCR2                                                | PF10MD[2:0] = B'101                     | PF10/A24/SSIWS3/SSL00/TIOC3B/FCE# |  |

|                        | FRB                         | PFCR2                                                | PF9MD[2:0] = B'101                      | PF9/A23/SSISCK3/RSPCK0/TIOC3A/FRB |  |

#### Table 8 Multiplexed Pins

Note 1: Bus State Controller pin functions (D4 to D15) and NAND Flash Memory Controller pin functions (NAF0 to NAF7, FWE#, FALE, FCLE, and FRE#) are automatically switched. When using the SH7264 in boot mode 0, D0/NAF0 to D7/NAF7 pin functions are selected as default. When using the SH7264 in boot modes 1 to 3, I/O ports pin functions are selected as default.

### 6. Handling of Pins

### 6.1 ASEMD0# Pin

The ASEMD0# pin selects the H-UDI related functions for use by the emulator.

If the input signal to the ASEMD0# pin is low during the RES# assertion the SH7264 will enter ASE mode. If the input signal is high during the RES# assertion, the MCU will enter product-chip mode (normal operation). Keep the input signal level of the ASEMD0# pin for at least 1 cycle after the RES# pin is negated.

ASEMD0# should have a pull-up resistor so chip enters the correct mode when not being used with the emulator <sup>(note)</sup>.

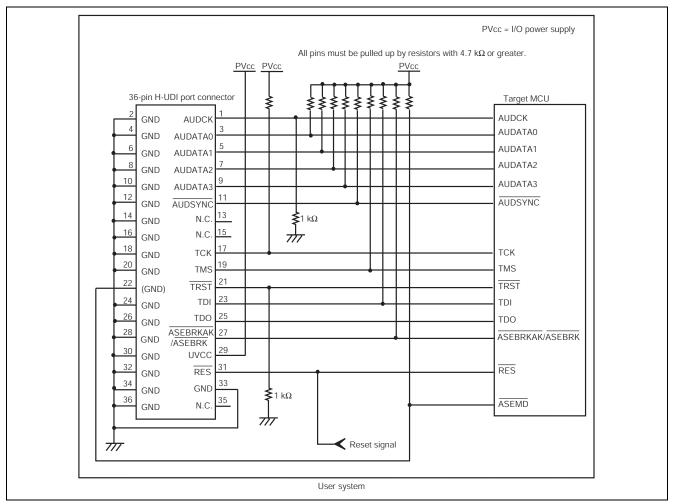

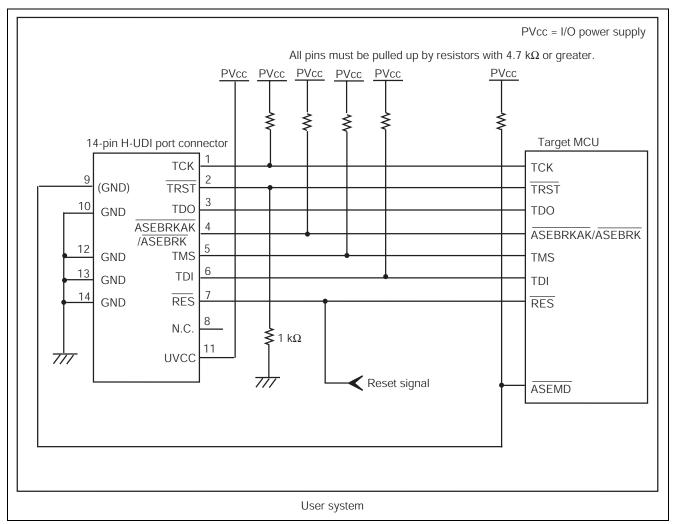

Note: The ASEMD0# pin will be pulled low when using the emulator if the recommended connections as shown in Figure 13 and Figure 14 are used.

### 6.2 TRST# Pin

The TRST# pin is an initialization signal input pin in user debugging interface (H-UDI). It accepts inputs from the H-UDI serial data I/O clock pin (TCK) asynchronously to reset the H-UDI at low level. The TRST# should have a 1K pull-down as shown in Figure 13 and Figure 14 for correct operation whether using or not using the emulator. The emulator will control the TRST# timing when it is being used; in normal mode the engineer does not need to worry about TRST# beyond having the pull-down resistor.

# 6.3 Signal Wiring to the E10A-USB Connector

Figure 13 and Figure 14 show recommended circuits to wire the H-UDI signal when using the E10A-USB emulator. For more information, refer to the "SuperH<sup>TM</sup> Family E10A-USB Emulator Additional Document for User's Manual (Supplementary Information on Using the SH7264 SH7262 SH7266 and SH7267)".

Figure 13 Recommended Circuit between the 36-pin H-UDI Port Connector and MCU (with E10A-USB)

Figure 14 Recommended Circuit between the 14-pin H-UDI Port Connector and MCU (with E10A-USB)

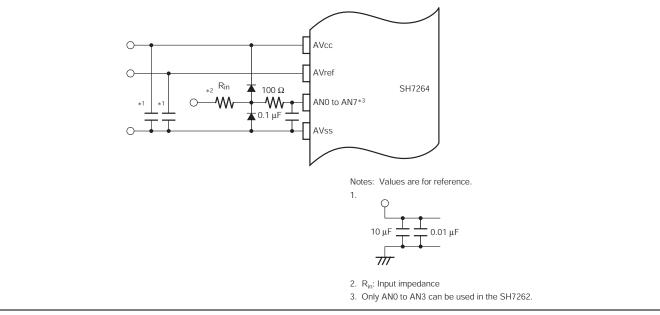

### 6.4 Analog Pins

### 6.4.1 Notes on Designing Board

Analog pins AN0 to AN7 are input-only, applicable when using as multiplexed PH0 to PH7 ports.

Place the digital circuit and analog circuit as far apart as possible on the board (i.e. maintain some isolation between the high-speed digital and analog signals). Analog circuits signals must be wired prior to digital circuit signals, and avoid intersecting with or being close to the digital circuit signals to avoid coupling. Failure to do so may result in the malfunction of analog circuit and adversely affecting the A/D conversion values.

Isolate analog input signals (AN0 to AN7), analog reference voltage (AVref), analog power supply (AVcc), and analog ground (AVss) from the digital circuit. AVss must be connected on a stable digital ground (Vss) on board.

Note: Only analog input pins 0 to 3 (AN0 to AN3) can be used on the SH7262.

### 6.4.2 Analog Pin Protection Circuit

As shown in Figure 15, connect the protection circuit between AVcc and AVss to prevent damage due to an abnormal voltage, such as an excessive surge at analog input pins (AN0 to AN7) and analog reference voltage (AVREF). The circuit also is used as the RC filter to minimize the noise. Note that the circuit shown in the figure below is an example. Consider the circuit constants as appropriate before deciding.

Note: Only analog input pins 0 to 3 (AN0 to AN3) can be used on the SH7262.

Figure 15 Analog Input Pin Protection Circuit Example

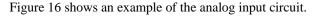

#### 6.4.3 Permissible Signal Source Impedance

The SH7264 analog input is designed to guarantee the conversion accuracy for the input signal when its source impedance is equal to or less than 5 k $\Omega$ . This specification is to charge the input capacitance of the A/D Converter (ADC) sample-and-hold circuit within the sampling time. When the sensor output impedance exceeds 5 k $\Omega$ , charging may be insufficient and it may not be possible to guarantee A/D conversion accuracy. If a large capacitance is provided externally when converting analog to digital in single mode, the input load essentially comprise only the 3k $\Omega$  internal input resistance, and the signal source impedance is not required. However, the SH7264 ADC includes a low-pass filter, it may not be able to handle the analog signal with a large differential coefficient (e.g., 5 mV/µs or greater). Install a low-impedance buffer when converting a high-speed analog signal or converting signals in scan mode.

Figure 16 Analog Input Circuit Example

### 6.5 USB Pins

For details on handling pins to use the USB 2.0 host or function module (USB module), refer to the application note "SH7262/SH7264 Group Guidelines for Hi-Speed USB 2.0 Board Design".

### 6.6 Terminating Pins

#### 6.6.1 Unused Pins

Table 9 lists the handling of unused pins.

#### **Table 9 Unused Pins Handling**

| Pin Name                                                                                                              | Handling                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| NMI                                                                                                                   | Fix at high level (pull up or connect to the power supply)                                     |

| DP, DM, VBUS                                                                                                          | Connect to the USBDPVss                                                                        |

| REFRIN                                                                                                                | Connect to the USBAPVcc via 5.6 k $\Omega \pm 20\%$ resistor                                   |

| USB power supply (USBAPVcc, USBAPVss,<br>USBDPVcc, USBDPVss, USBAVcc, USBAVss,<br>USBDVcc, USBDVss, USBUVcc, USBUVss) | Connect to the power supply, ground                                                            |

| AVref                                                                                                                 | Connect to the AVcc                                                                            |

| ADC power supply (AVcc, AVss)                                                                                         | Connect to the power supply, ground                                                            |

| Other input-only pins                                                                                                 | Fix the level (pull up, pull down, connect to the power supply or ground)                      |

| Other I/O-only pins                                                                                                   | Set to input pin and fix the level (pull up or pull down)<br>Or set to the output pin and open |

| Output-only pins                                                                                                      | Leave open                                                                                     |

| ASEMD#                                                                                                                | Fix to high level (pull up or connect to the power supply)                                     |

| TRST#                                                                                                                 | Fix to low level (pull down or connect to ground)                                              |

| TCK, TMS, TDI                                                                                                         | Fix the level (pull up, pull down, connect to the power supply or ground)                      |

| TDO, ASEBRKAK#/ASEBRK#                                                                                                | Leave open                                                                                     |

|                                                                                                                       |                                                                                                |

Note: We recommend using pull-up or pull-down resistors between 4.7 k $\Omega$  to 100 k $\Omega$ .

### 6.6.2 Used Pins

The engineer may still need to terminate "used" pins in his design with either pull-up or pull-down resistors. During the RESET cycle GPIO pins will revert to high impedance inputs and remain that way until the hardware setup code is executed, which could be considerable depending on the boot time. The engineer will need to evaluate his design and determine if pull-up or pull-down resistors are required in his design. A prime example would be power circuits, where the engineer will want to passively pull them to the "inactive" state to avoid hardware damage or malfunction.

### 7. On-chip Resource Access

The SH7264 includes the high-speed internal RAM, large-capacity internal RAM, and on-chip peripheral modules as the on-chip resources. The number of cycles to access the high-speed internal RAM varies according to the bus used. For details on buses connected to on-chip resources, refer to Figure 1.3 Block Diagram in the SH7262 Group, SH7264 Group Hardware Manual.

Table 10 lists the number of cycles for access to the on-chip resources.

#### Table 10 Number of Cycles for Access to the On-chip Resources

| Read/<br>Write | CPU                                 |                                       | Internal DMA         | A bus (ID bus)                   | - Large-capacity              | Internal<br>peripheral<br>register |

|----------------|-------------------------------------|---------------------------------------|----------------------|----------------------------------|-------------------------------|------------------------------------|

|                | instruction<br>fetch bus<br>(F bus) | CPU memory -<br>access bus<br>(M bus) | lφ:Bφ<br>clock ratio | Number of<br>cycles to<br>access | ₋ internal RAM <sup>(1)</sup> |                                    |

| Read           | 1 Ιφ                                | 1 Ιφ                                  | 1:1                  | 3 Βφ                             | 1 Βφ                          | 2 or more Pq                       |

|                |                                     |                                       | 2:1                  | 2 Βφ                             | -                             |                                    |

|                |                                     |                                       | 3:1                  | 2 Βφ                             |                               |                                    |

|                |                                     |                                       | 4:1                  | 2 Βφ                             |                               |                                    |

|                |                                     |                                       | 6:1                  | 1 Βφ                             |                               |                                    |

|                |                                     | -                                     | 8:1                  | 1 Βφ                             | _                             |                                    |

| Write          | 1 Ιφ                                | 1 Ιφ                                  | 1:1                  | 2 Βφ                             | 1 Βφ                          | 2 or more Pq                       |

|                |                                     | -                                     | 2:1                  | 2 Βφ                             | _                             |                                    |

|                |                                     | -                                     | 3:1                  | 2 Βφ                             | _                             |                                    |

|                |                                     | -                                     | 4:1                  | 2 Βφ                             | _                             |                                    |

|                |                                     | -                                     | 6:1                  | 1 Βφ                             | _                             |                                    |

|                |                                     | -                                     | 8:1                  | 1 Bφ                             | _                             |                                    |

#### High-speed internal RAM (1)

Note: The High-speed internal RAM and large-capacity internal RAM are composed of several pages, and each page has a port for reading/writing. Periherals may access various RAM pages simultaneously, conflict only occurs when accessing the same page from several buses at the same time, causing some degradation in the RAM performance. This is easily avoided in software by partitioning RAM usage and buffers to avoid that situation (i.e. peripherals accessing the RAM access different pages). A very simple example might be don't put the stack (high usage memory) in the same memory page where you are capturing video or in a high usage Ethernet buffer and thus avoid "collisions".

### 8. Endianness

The SH7264 supports big-endian order to store the most significant byte (MSB) at the lowest address 0, and littleendian order to store the least significant byte (LSB) at the lowest address 0. The default endianness is big-endian after power-on reset on all areas. The CSn space bus control register (CSnBCR) specifies endian when the target area is not accessed.

Typical memory, SRAM interface with byte selection can be connected in 8- or 16-bit wide, and SDRAM is connected in 16-bit wide (fixed). PCMCIA interface can be connected in 8- or 16-bit wide, and MPX-I/O interface can be connected in 8- or 16-bit wide (fixed), or 8- or 16-bit wide variable, depending on the address to access.

The endianness and data bus width have restrictions per boot mode. NOTE: Since the SH2A is native "big endian", most common uses of "little-endian" is in data space to connect to "little-endian" devices such as other processors through dual-port memory or "little-endian" memory mapped I/O.

Table 11 lists the boot modes and default state by area.

Note that data position and strobe signals corresponding to addresses depend on the byte order, big-endian or littleendian. WE1 indicates address 0 in big-endian, but WE0 indicates address 0 in little-endian.

IMPORTANT: Since the instruction fetch is mixed with the 32- and 16-bit access, code cannot be allocated to the littleendian area. Always execute instructions from the big-endian areas, internal or external.

NOTE: Since the SH2A is native "big endian", most common uses of "little-endian" is in data space to connect to "little-endian" devices such as other processors through dual-port memory or "little-endian" memory mapped I/O.

| Boot Mode | ltem             | Area 0                                                                     | Areas 1 to 6                                                         |

|-----------|------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------|

| 0         | Data bus width   | Fixed to 16-bit wide, which cannot be modified                             | Set to 16-bit by default, which<br>can be modified by program        |

|           | Endianness       | Fixed to big-endian order, which cannot be modified                        | Set to big-endian order by default, which can be modified by program |

|           | BSC pins setting | Minimal pins to read ROM, such as RD# are set automatically. Other pi      |                                                                      |

| 1, 2, 3   | Data bus width   | Set to 16-bit by default, which can b                                      | be modified by program                                               |

|           | Endianness       | Set to big-endian order by default, v                                      | which can be modified by program                                     |

|           | BSC pins setting | Set to general-purpose port function bus, all required pins must be set by |                                                                      |

#### Table 11 Boot Mode and Default State by Area

### 9. Power-down Modes

The SH7264 has the following power-down modes and function.

(1) Sleep mode

(2) Software standby mode

(3) Deep standby mode

(4) Module standby function

As power-down modes stop CPU, clock, internal memory, and some peripherals or turns off the power supply, it will reduce power consumption. The SH7264 wakes up from these modes by reset or interrupt.

Table 12 lists transition conditions, module states, and how to wake up the MCU. For more information on the register states, refer to 36.3 Register State in Each Operating Mode in the Sh7262 Group, SH7264 Group Hardware Manual.

| Power-        | Transition Conditions | State (1) |                   |                 |                       |                        |           |                 |     |                          | How to Wake Up the                                                    |

|---------------|-----------------------|-----------|-------------------|-----------------|-----------------------|------------------------|-----------|-----------------|-----|--------------------------|-----------------------------------------------------------------------|

| Down<br>Modes |                       | CPG       | CPU               | CPU<br>Register | High-<br>speed        | Large-<br>capacity RAM | OPM       | RTC             | PS  | External<br>Memory       | МСИ                                                                   |

|               |                       |           |                   |                 | RAM                   | (Data-                 |           |                 |     |                          |                                                                       |

|               |                       |           |                   |                 | Cache                 | retention RAM          |           |                 |     |                          |                                                                       |

|               |                       |           |                   |                 | Memory                | included)              |           |                 |     |                          |                                                                       |

| Sleep         | Execute SLEEP         | ON        | OFF               | States held     | ON                    | ON                     | ON        | ON (2)          | ON  | Auto-refresh             | •                                                                     |

| mode          | instruction when the  |           |                   |                 |                       |                        |           |                 |     |                          | Manual reset                                                          |

|               | STBY bit in the       |           |                   |                 |                       |                        |           |                 |     |                          | <ul><li>Power-on reset</li><li>DMA address error</li></ul>            |

|               | STBCR1 is 0           |           |                   |                 |                       |                        |           |                 |     |                          | · DIVIA address entor                                                 |

| Software      | e Execute SLEEP       | OFF       | OFF               | States held     | OFF (Data is          | OFF (Data is           | OFF       | ON (2)          | ON  | Self-refresh             | NMI interrupt                                                         |

| standby       | instruction when the  |           |                   |                 | retained) $^{(5)(6)}$ | retained) $(5)(7)$     |           |                 |     |                          | <ul> <li>IRQ interrupt</li> </ul>                                     |

| mode          | STBY bit in the       |           |                   |                 |                       |                        |           |                 |     |                          | Power-on reset                                                        |

|               | STBCR1 is 1 and       |           |                   |                 |                       |                        |           |                 |     |                          |                                                                       |

|               | DEEP bit in the       |           |                   |                 |                       |                        |           |                 |     |                          |                                                                       |

|               | STBCR1 is 0           |           |                   |                 |                       |                        |           |                 |     |                          |                                                                       |

| Deep          | Execute SLEEP         | OFF       | OFF               | OFF             | OFF (Data is          | OFF (Data in the       | OFF       | ON (2)          | OFF | Self-refresh             | NMI interrupt (4)                                                     |

| standby       | instruction when bits |           |                   |                 | not retained)         | Data-retention         |           |                 |     |                          | Power-on reset (4)                                                    |

| mode          | STBY and DEEP in      |           |                   |                 |                       | RAM                    |           |                 |     |                          | Realtime Clock alarm                                                  |

|               | the STBCR1 are 1      |           |                   |                 |                       | is retained) $^{(3)}$  |           |                 |     |                          | interrupt <sup>(4)</sup>                                              |

|               |                       |           |                   |                 |                       |                        |           |                 |     |                          | <ul> <li>Change pins to wake up the<br/>MCU <sup>(4)</sup></li> </ul> |

| Module        | Set the MSTP bits in  | ON        | ON ON States held | ON States held  | ON                    | ON                     | Specified | OFF             | ON  | Auto-refresh             | Clear the MSTP bit to 0                                               |

| standby       | the STBCR2,           |           |                   |                 |                       | module                 |           |                 |     | Power-on reset (Only for |                                                                       |

| mode          | STBCR3, STBCR4,       |           |                   | is OFF          |                       |                        |           | H-UDI and DMAC) |     |                          |                                                                       |

|               | STBCR5, STBCR6,       |           |                   |                 |                       |                        |           |                 |     |                          |                                                                       |

|               | STBCR7, STBCR8        |           |                   |                 |                       |                        |           |                 |     |                          |                                                                       |

**Table 12 State of Power-Down Modes**

Notes 1. Pin state is either "states held" or "high impedance".

2. The Realtime Clock is ON when the START bit in the RCR2 register is 1. When waking up the MCU from deep standby mode by power-on reset, the operating state cannot be retained. Configure the Realtime Clock again.

3. Set bits RRAMKP3 to RRAMKP0 in the RRAMKP register to 1, and the data stored in the data-retention RAM target area can be retained when the MCU transitions to deep standby mode. Note that the data is initialized when waking up the MCU from deep standby mode by power-on reset. Bits RRAMKP3 and RRAMKP2 can be used only on the MCU with 640-KB RAM.

4. The MCU is woke up from deep standby mode by interrupts (NMI, or real-time clock alarm interrupt), reset (power-on reset), or change pins to wake up the MCU (PC8 to PC5, PG11, PG10, PJ3, and PJ1). When waking up the MCU from deep standby mode not by the reset, the power-on reset exception handling is executed instead of interrupt exception handling. Pins PG11 and PG10 can be used to wake up the MCU only on the MCU with 640-KB RAM.

5. When waking up the MCU from software standby mode by power-on reset, the retained data is initialized.

Disable the RAME bit in the SYSCR1 register or RAMWE bit in the SYSCR2 register to retain the data in the high-speed internal RAM when waking up the MCU from software standby mode by power-on reset.

7. Disable the VRAME bit in the SYSCR3 register or VRAMWE bit in the SYSCR4 register to retain the data in the large-capacity internal RAM (data-retention RAM included) when waking up the MCU from software standby mode by power-on reset.

### 9.1 Sleep Mode

In sleep mode, only CPU stops its operation.

When executing the SLEEP instruction while the STBY bit in the Standby control register 1 (STBCR1) is 0, the SH7264 transitions from the program execution state to sleep mode. The CPU stops its operation immediately after executing the SLEEP instruction; however internal register values remain unchanged, and on-chip peripherals continue to operate in sleep mode. The CKIO pin continues to output clock pulses.

### 9.2 Software Standby Mode

The SH7264 stops its operation completely in software standby mode.

When executing the SLEEP instruction while the STBY bit in the STBCR1 is 1, and DEEP bit is 0, the SH7264 transitions from the program execution state to software standby mode. Not only the CPU, but the clock and on-chip peripherals stop operation in software standby mode. In addition, the CKIO pin stops outputting clock pulses.

CPU and Cache register values are retained in software standby mode. Some on-chip registers are initialized.

The CPU writes data in STBCR1 in a cycle and executes the next instruction. However, it takes one or more cycles to actually write data in the register. Therefore, execute the SLEEP instruction after reading STBCR1 to reflect the write value from CPU to STBCR1 in the SLEEP instruction.

### 9.3 Deep Standby Mode

Deep standby mode stops the SH7264 completely and turns OFF the SH7264.

When executing the SLEEP instruction while the bits STBY and DEEP in STBCR1 is 1, the SH7264 transitions from the program execution state to deep standby mode. Not only the CPU, clock, and on-chip peripheral modules stop operation, but all modules are off, other than the data-retention internal RAM which is set by bits RRAMKP3 to RRAMKP0 in the On-chip data-retention RAM area setting register (RRAMKP) to reduce the power consumption substantially. Therefore, CPU and cache register values, and on-chip peripheral module register values are not retained. Pin states are retained just before transition to deep standby mode.

The CPU writes data in Deep standby cancel source flag register (DSFR) in a cycle and executes the next instruction. However, it takes one or more cycles to actually write data in the register. Therefore, execute the SLEEP instruction after reading the DSFR to reflect the write value from CPU to the DSFR in the SLEEP instruction.

For more information about deep standby mode, refer to the application note "SH7262 Group, SH7264 Group Using Deep Standby Mode in Power-down Mode".

### 9.4 Module Standby Function

The module standby function stops on-chip peripherals separately.

Set the MSTP bits in the Standby control registers of each module to 1 to stop supplying clock to the corresponding onchip peripherals. The power consumption is reduced in power execution state and sleep mode by this function. Make sure to disable a module before setting it in module standby mode. Do not access the registers of a module in module standby mode.

### 9.5 Pin States in Power-down Modes

#### 9.5.1 Pin States in Sleep Mode

As the peripheral modules operate in sleep mode, the pin state varies according to the operation of peripheral modules.

### 9.5.2 Pin States in Module Standby Mode

When using module standby function for the module specified as general-purpose I/O port, the pins of the module whose registers to be initialized at the module standby function is configured to default state. The pin of the module whose registers not to be initialized at the module standby function retains the state immediately before entering module standby mode.

#### 9.5.3 Pin States in Software Standby Mode and Deep Standby Mode

The pin states in software standby mode and deep standby mode depend on the pin function or its setting. Table 13 to Table 15 list pin states in software standby mode and deep standby mode.

#### Table 13 Pin States in Software Standby Mode and Deep Standby Mode (1/3)

| Pin Name |                             | Descriptio  | n                      |                   |  |

|----------|-----------------------------|-------------|------------------------|-------------------|--|

| External | CKIO                        | Specified b | y CKOEN [1:0] bits (FF | RQCR register)    |  |

| bus pins |                             | Setting     | Software standby       | Deep standby      |  |

|          |                             |             | mode                   | mode              |  |

|          |                             | B'00        | Hi-Z                   | Low or high level |  |

|          |                             | B'01        | Low level              | Low or high level |  |

|          |                             | B'10        | Unstable clock         | Low or high level |  |

|          |                             |             | output                 |                   |  |

|          |                             | B'11        | Hi-Z                   | Hi-Z              |  |

|          | A25 to A0, CS6# to CS0#,    | Specified b | y the HIZMEM bit (CMI  | NCR register)     |  |

|          | CE1A#, CE1B#, CE2A#, CE2B#, | 1: Outpu    | ut state               |                   |  |

|          | RD#, RD/WR#, BS#,           | 0: High i   | mpedance state         |                   |  |

|          | ICIOWR#/AH#, ICIORD#,       |             |                        |                   |  |

|          | WE1#/DQMLU/WE#,             |             |                        |                   |  |

|          | WE0#/DQMLL                  |             |                        |                   |  |

|          | RAS#, CAS#, CKE             | Specified b | y the HIZCNT bit (CMN  | ICR register)     |  |

|          |                             | 1: Outpu    | ut state               |                   |  |

|          |                             | 0: High i   | mpedance state         |                   |  |

|          | D15 to D0, WAIT#, IOIS16#   | High imped  | ance state             |                   |  |

| Pin Name                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|