## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# RENESAS

## SH7147

## Resolver Built-in DC Brushless Motor Control

## 1. Abstract

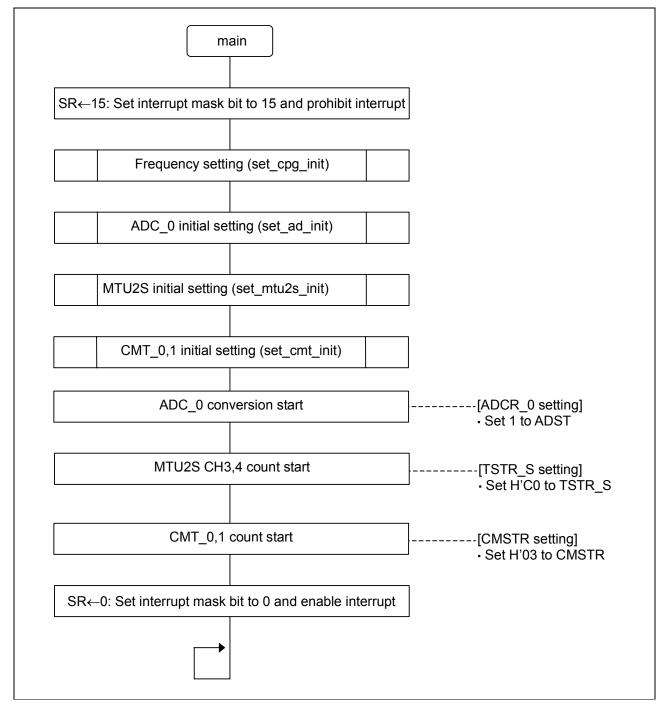

This application note is organized based on sample of resolver built-in DC brushless motor control, which uses SH7147 embedded ADC\_0, MTU2S\_3,4, and CMT\_0,1, and is aimed to provide information users may need during software and hardware design.

Although the operation of each program in this application note has been checked, make sure that you conduct your own operation checks before actually using.

## 2. Introduction

## 2.1 Specification

(1) System Architecture Specification

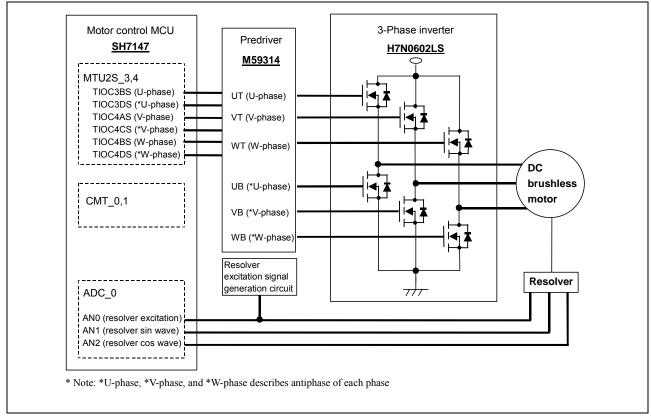

Figure1 describes system architecture of this control.

- SH7147 is used as motor control MCU.

- M59314 is used as step-up predriver for inverter driver

- Six H7N0602LS (power MOS FET) is used as 3-phase inverter

#### (2) Motor Control Specification

Resolver built-in DC brushless motor is controlled in 120-degree energization drive system.

- Resolver output signal is converted to digital at ADC\_0 and motor position is detected at every 30 degree.

- Motor drive wave most suitable to motor position will be outputted from MTU2S (level output on positive phase side, PWM output on antiphase side)

- Motor revolving direction reverses at every 4[sec].

Figure1 Overview of Resolver Built-in DC Brushless Motor Control System

## 2.2 Functions Used

- Multi-function Timer pulse Unit 2S channel 3,4 (MTU2S\_3,4)

- A/D converter 0 (ADC\_0)

- Compare Match Timer channel 0,1 (CMT\_0,1)

## 2.3 Applicable Conditions

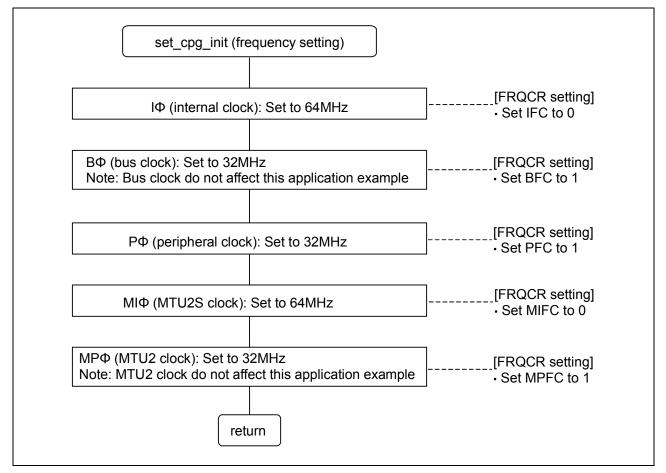

- MCU : SH7147(R5F71474AK64FPV)

- Operation Frequency : Internal Clock 64MHz

Bus Clock 32MHz

Peripheral Clock 64MHz

MTU2S Clock 64MHz

MTU2 Clock 32MHz

C Compiler : Renesas Technology product SuperH RISC engine Family C/C++ compiler package

- Ver.9.00

Compile Option : Default setting by HEW

## 2.4 Related Application Note

• Power MOS FET Application Note

#### 3. Description of Control Sample

This control sample determines motor position by A/D converting output signal of resolver, which is built in DC brushless motor. A motor drive wave, most suitable to the determined mortar position, will be output from MTU2S and controls DC brushless motor.

## 3.1 Overview of Entire Operation

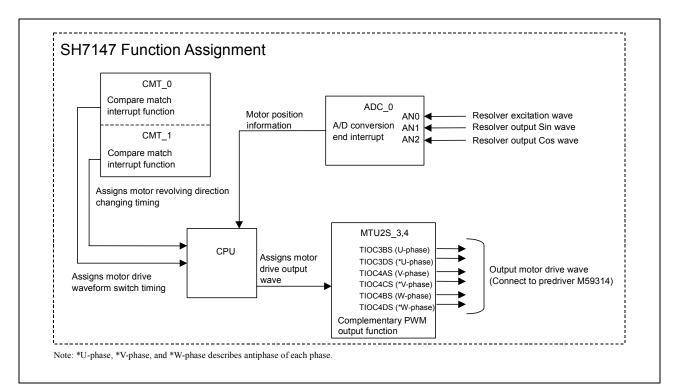

Following describes functions used by SH7147 for controlling resolver built-in DC brushless motor (Figure 2.)

Figure 2 SH7147 Control Block Diagram

Following describes each function.

- A/D Conversion End Interrupt: After conversing resolver input excitation signal, resolver output Sin wave signal, and resolver output Cos wave signal into digital, it requests CPU for interrupt. A/D conversion result is stored to RAM by interrupt procedure.

- Compare Match Interrupt Function (CMT\_0): Request CPU for interrupt at every 50µ[sec]. Interrupt procedure determines motor position and outputs motor drive wave.

- Compare Match Interrupt Function (CMT\_1): Request CPU for interrupts at every 0.8[sec] Interrupt procedure counts number of interrupting times and reverses motor revolving direction at every 5 interrupts process. (reverse motor revolving direction at every 0.8[sec] x 5 = 4[sec])

- Complementary PWM Output Function: Level output on positive phase side and chopping wave output on antiphase side.

## 3.2 Description of Functions Used

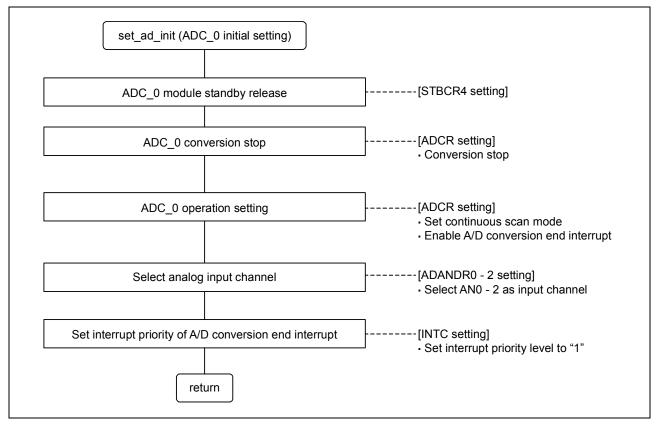

[1] A/D Converter

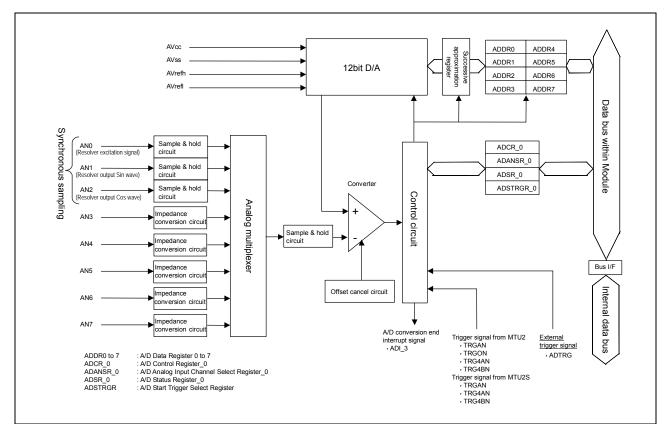

(a) Overview of A/D converter (ADC) operation

Resolver input excitation signal, resolver output Sin wave signal, and resolver output Cos wave signal are input from analog input pin 0,1,2 (AN0, AN1, and AN2) respectively. Input voltage of AN0 to 2 are sampled at a same timing at sample & hold circuit (the step before analog multiplexer) and A/D converted sequentially. The operation mode is continuous scan mode.

Figure 3 describes ADC\_0 block diagram.

Figure 3 ADC\_0 Block Diagram

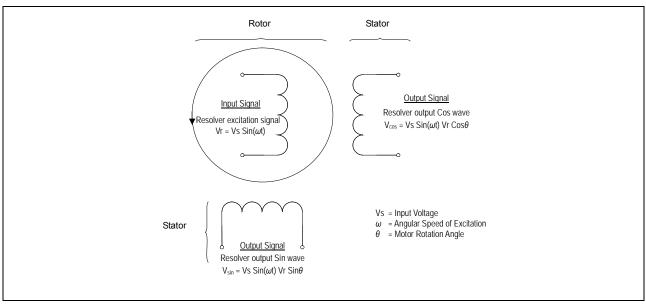

#### (b) Overview of Resolver

Following describes resolver in motor position detection sensor, implemented in this system (Figure 4.) A coil is fixed on the rotor, and two coils are fixed 90 degree of each other on the stator. When resolver input excitation signal (Vr) is inputted, resolver output Sin wave ( $V_{sin}$ ) and resolver output Cos wave ( $V_{cos}$ ), which has 90 degree phase difference, are outputted from two coils on the stator.

Figure 4 Diagram of Resolver Principle

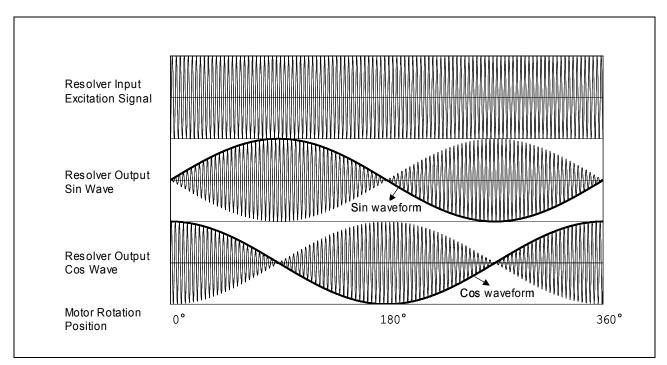

(c) Resolver Input/Output Signal and Motor Rotation Position

Figure 5 describes resolver input excitation signal, resolver output Sin wave, and resolver output Cos wave per revolution of the motor. One motor revolution is equivalent to one cycle of Sin waveform and Cos waveform obtained from resolver output Sin wave and resolver output Cos wave.

Figure 5 Resolver Input/Output Signal and Sin wave/ Cos wave (per motor revolution)

(d) Obtaining Sin waveform/ Cos waveform from each Resolver Output wave

Resolver output Sin wave/ Cos wave can be described in following formula, as been shown in Figure 4 Diagram of Resolver Principle.

Resolver Output Sin Wave Signal:  $V_{sin} = VsSin(\omega t)VrSin\theta$

Resolver Output Cos Wave Signal:  $V_{cos} = VsSin(\omega t)VrCos\theta$

If resolver input excitation signal (VsSin( $\omega$ t)) is regarded as constant,

Resolver Output Sin Wave Signal:  $V_{sin} = ASin\theta$ Resolver Output Cos Wave Signal:  $V_{cos} = ACos\theta$

A : VsVrSin( $\omega$ t)

Sin/Cos waveform can be obtained from above.

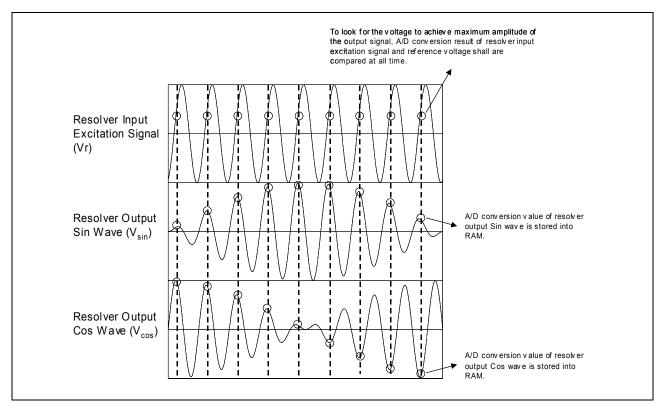

Following describes how to obtain  $\sin\theta$  and  $\cos\theta$  from resolver output Sin wave signal and resolver output Cos wave signal with regarding resolver input excitation signal as constant.

- (i) In this control sample, voltage of resolver input excitation signal (VsSin( $\omega$ t)) is kept constant to have above "A" to be constant. "A" can be regarded as amplitude of resolver output signal. For this amplitude to have the maximum value, the voltage of resolver input signal for achieving the maximum amplitude of resolver output signal shall be obtained in beforehand by examining resolver input/output signal waveform and shall be defined as the reference value.

- (ii) Voltage of resolver input excitation signal, resolver output Sin wave signal, and resolver output Cos wave signal are sampled at a same time and are A/D converted in continuous conversion mode.

- (iii)When A/D conversion result of resolver input excitation signal and the reference voltage defined at (i) matches, in other words, when amplitude of resolver output signal becomes maximum, A/D conversion result of two output signals,  $ASin\theta$  and  $ACos\theta$ , are stored to RAM.

In this control sample, resolver input excitation signal cycle is set 900µ[sec] and motor rotation speed is set 300[rpm] (200m[sec]/revolution).

There are about 222 resolver input excitation signal cycles per motor revolution. As shown in Figure 6,  $\sin\theta$  and  $\cos\theta$  can be achieved once in one resolver input excitation signal cycle. Therefore,  $\sin\theta$  and  $\cos\theta$  can be achieved 222 times per one motor revolution and motor position can be detected per approximately 1.6 degree (360 degree/222) (A/D conversion error not regarded). As for this control sample requires motor position information per 30 degree, 1.6 degree motor positioning meets the requirement.

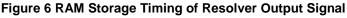

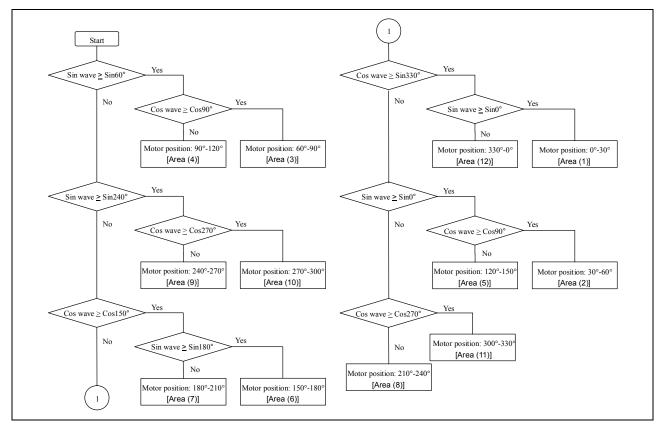

#### (e) Motor Position Determination

Following describes how to calculate an angle from Sin waveform/ Cos waveform achieved from resolver input/output signal. As for this sample controls motor in 120-degree energization method, it captures motor position information for each 30 degree. Figure 7 describes relation between motor position and Sin waveform/ Cos waveform.

Figure 7 Motor Position and Sin Waveform/ Cos Waveform

Motor position can be determined from Sin waveform/Cos waveform with defining following provision.

| Area (1): $\cos\theta > \cos 30^{\circ}$              | & | Sin <i>θ</i> > 0 | Area (7): $\cos\theta > \cos 150^\circ$ &    | Sinθ < 0         |

|-------------------------------------------------------|---|------------------|----------------------------------------------|------------------|

| Area (2): $Sin60^{\circ} > Sin\theta > Sin30^{\circ}$ | & | $\cos\theta > 0$ | Area (8): Sin210° > Sin $\theta$ > Sin240° & | $\cos\theta < 0$ |

| Area (3): $\sin\theta$ > $\sin60^{\circ}$             | & | $\cos\theta > 0$ | Area (9): $\sin\theta > \sin 240^{\circ}$ &  | $\cos\theta < 0$ |

| Area (4): $\sin\theta$ > $\sin60^{\circ}$             | & | $\cos\theta < 0$ | Area (10):Sin $\theta$ > Sin240° &           | $\cos\theta > 0$ |

| Area (5): Sin60° > Sin $\theta$ > Sin30°              | & | $\cos\theta < 0$ | Area (11):Sin210° > Sin $\theta$ > Sin240°&  | $\cos\theta > 0$ |

| Area (6): $\cos\theta > \cos 150^{\circ}$             | & | $\sin\theta > 0$ | Area (12): $\cos\theta > \cos 330^{\circ}$ & | $\sin\theta < 0$ |

Following describes data comparing Sin waveform/Cos waveform.

Analog input voltage of this control sample is maximum of 1.7[V], minimum of 0.3[V], and intermediate of 1.0[V]. Avref is set to 5.0[V].

As for motor is positioned by 30 degrees, voltage for comparing Sin/Cos waveform and constant to be compared is defined as Table 1.

#### Table 1 Voltage of Sin/Cos waveform and Comparison Value

|                   | Sin270°, Cos180°                 | Sin240°, Sin300°, Cos150°, Cos210° | Sin210°, Sin330°, Cos120°, Cos240° |

|-------------------|----------------------------------|------------------------------------|------------------------------------|

| Voltage [V]       | 0.3                              | 0.395                              | 0.65                               |

| Compared constant | H'0F5                            | H'142                              | H'213                              |

|                   | Sin60°, Sin120°, Cos30°, Cos330° | Sin30°, Sin150°, Cos60°, Cos300°   | Sin0°, Cos90°, Sin180°, Cos270°    |

| Voltage [V]       | 1.0                              | 1.35                               | 1.605                              |

| Compared constant | H'332                            | H'451                              | H'522                              |

|                   | Sin90°, Cos0°                    |                                    |                                    |

| Voltage [V]       | 1.7                              |                                    |                                    |

| Compared constant | H'570                            |                                    |                                    |

Flowchart for actually determining motor position by this controller is described in Figure 8.

Figure 8 Motor Position Determining Flow

# RENESAS

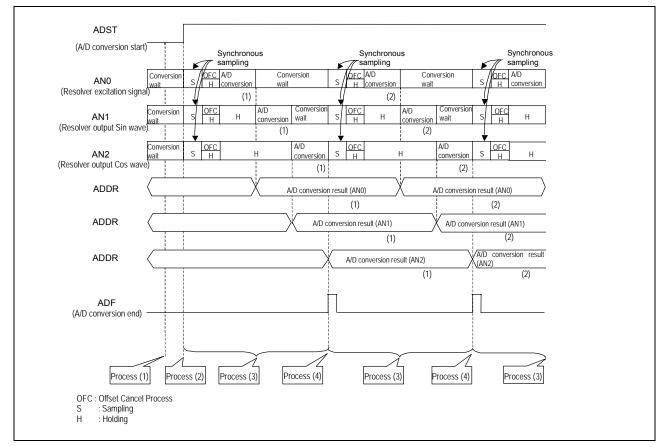

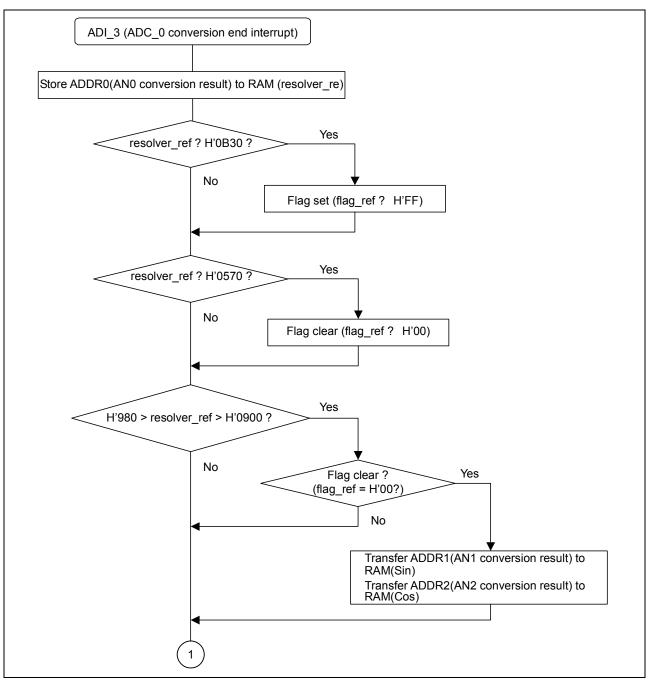

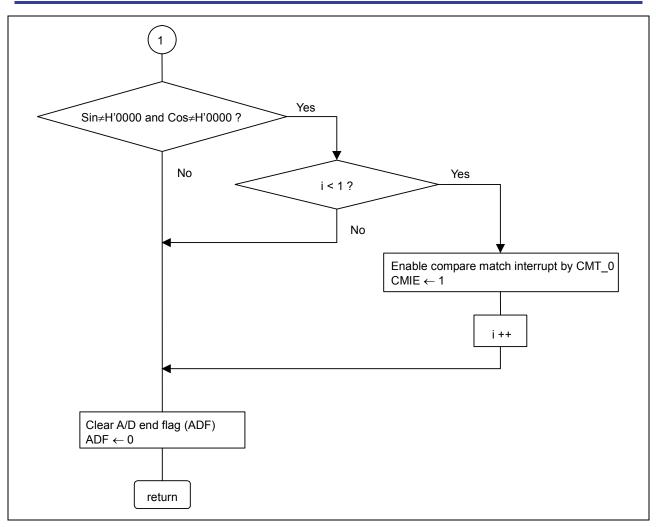

(f) Principle of A/D Converting Operation

Figure 9 describes principle of A/D converting operation. Table 2 shows details of software and hardware processing.

ADST bit is set to "1" by software and executes A/D conversion in continuous scan mode.

Following are processed by A/D conversion end interrupt.

- When A/D conversion result of resolver input excitation signal meets the condition described in Figure 6, A/D conversion result of resolver output Sin/Cos wave signal will be stored to RAM.

- When Figure 6 condition meets (when Sinθ and Cosθ are defined) for the first time, compare match interrupt by compare match timer\_0 is enabled.

(Compare match timer\_0 (CMT\_0) interrupt processing (output motor drive wave) is executed after motor position is defined.)

Figure 9 A/D Conversion Operation in Continuous Scan Mode

#### Table 2 Details of Software/Hardware process for A/D Conversion

|             | Software Process                                                                                                                                                                                                                                                                                                                                                                                                                        | Hardware Process                                                                                                                       |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Process (1) | After releasing AD_0 module stop, followings are set                                                                                                                                                                                                                                                                                                                                                                                    | None                                                                                                                                   |

|             | <ul> <li>Set continuous scan mode by setting ADCS bit to "1"</li> </ul>                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                        |

|             | • Select AN0 to 2 as input channel by setting ANS0-2 to "1"                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                        |

|             | <ul> <li>Enable A/D conversion end interrupt (ADI_3) by setting<br/>ADIE bit to "1"</li> </ul>                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                        |

| Process (2) | <ul> <li>Set A/D conversion start by setting ADST bit to "1"</li> </ul>                                                                                                                                                                                                                                                                                                                                                                 | Start A/D conversion                                                                                                                   |

| Process (3) | None                                                                                                                                                                                                                                                                                                                                                                                                                                    | <ul> <li>Sample AN0-2 synchronously and execute A/D conversion</li> <li>Store A/D conversion result sequentially to ADDR0-2</li> </ul> |

| Process (4) | <ul> <li>Transfer A/D conversion result of AN0 (resolver input excitation signal) to RAM</li> <li>If A/D conversion result of AN0 meets the condition (please refer figure 6), following are executed.</li> <li>(1) Store A/D conversion result of AN1 (resolver output Sin wave) and AN2 (resolver output Cos wave) to RAM.</li> <li>(2) When condition meets for the first time, CMT_0 compare match interrupt is enabled.</li> </ul> | <ul> <li>Set ADF to "1".</li> <li>A/D conversion end interrupt been generated (ADI_3).</li> </ul>                                      |

|             | Clear ADF to "0".                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                        |

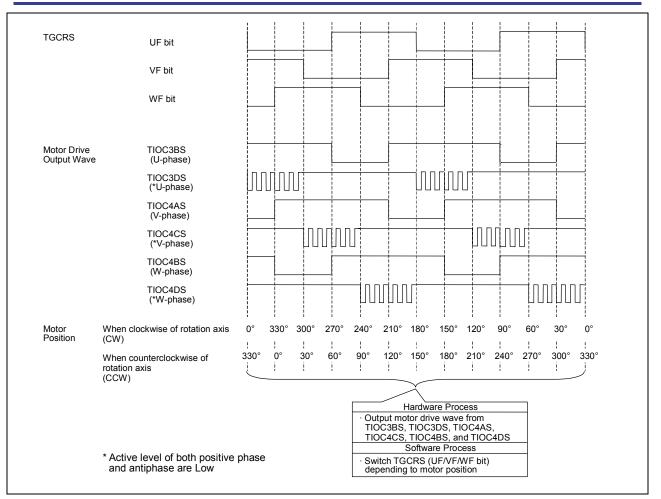

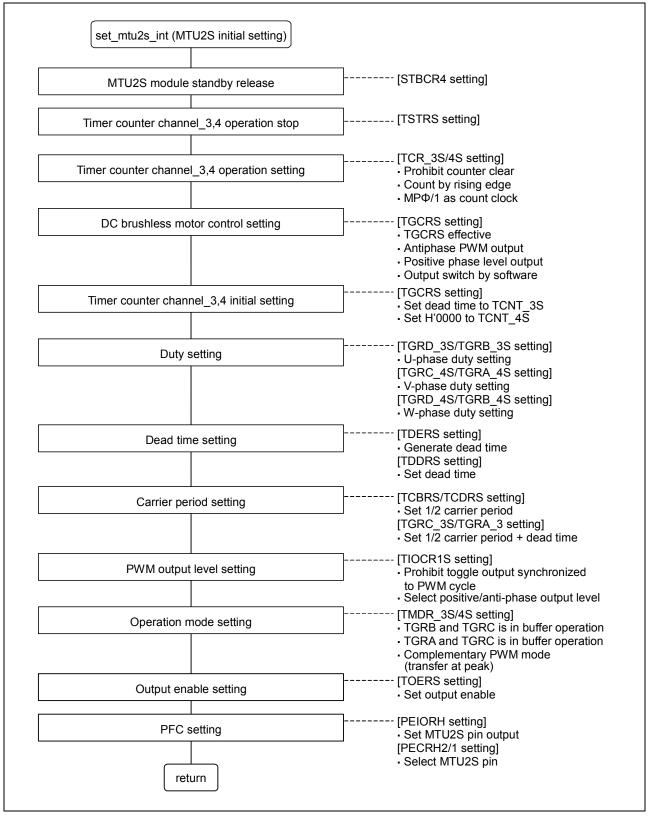

[2] MTU2S

(g) Overview of MTU2S Operation

Complementary PWM wave of three positive phase and three antiphase are outputted by using channel 3 and channel 4 of MTU2S. Operation mode is complementary PWM mode.

Correlation between UF bit, VF bit, and WF bit of timer gate control register S (TGCRS) and output level is shown in Table 3. (active level is set Low in this sample)

UF bit, VF bit, and WF bit are switched by software depending on motor revolving direction and motor position, and then motor drive wave is outputted (Figure 10).

| Bit 2 | Bit 1 | Bit 0 |         | Function |         |          |          |          |  |  |

|-------|-------|-------|---------|----------|---------|----------|----------|----------|--|--|

| WF    | VF    | UF    | TIOC3BS | TIOC4AS  | TIOC4BS | TIOC3DS  | TIOC4CS  | TIOC4D   |  |  |

|       |       |       | U-phase | V-phase  | W-phase | *U-phase | *V-phase | *W-phase |  |  |

| 0     | 0     | 0     | OFF     | OFF      | OFF     | OFF      | OFF      | OFF      |  |  |

| 0     | 0     | 1     | ON      | OFF      | OFF     | OFF      | OFF      | ON       |  |  |

| 0     | 1     | 0     | OFF     | ON       | OFF     | ON       | OFF      | OFF      |  |  |

| 0     | 1     | 1     | OFF     | ON       | OFF     | OFF      | OFF      | ON       |  |  |

| 1     | 0     | 0     | OFF     | OFF      | ON      | OFF      | ON       | OFF      |  |  |

| 1     | 0     | 1     | ON      | OFF      | OFF     | OFF      | ON       | OFF      |  |  |

| 1     | 1     | 0     | OFF     | OFF      | ON      | ON       | OFF      | OFF      |  |  |

| 1     | 1     | 1     | OFF     | OFF      | OFF     | OFF      | OFF      | OFF      |  |  |

#### Table 3 TGCRS (UF, VF, WF bit) and Output Level

Figure 10 Motor Drive Wave by TGCRS (UF, VF, WF bit) Switch

# RENESAS

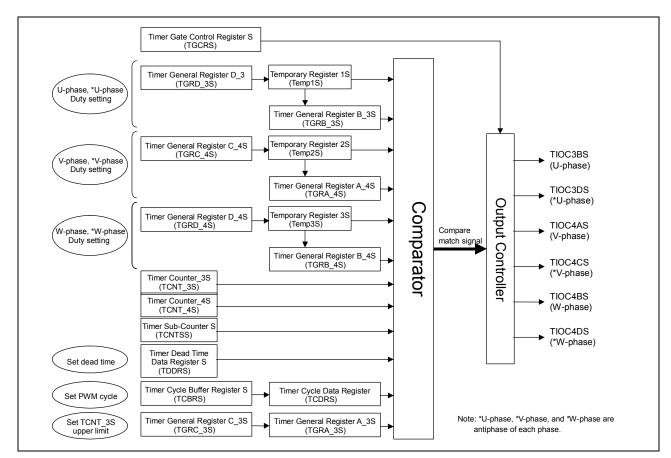

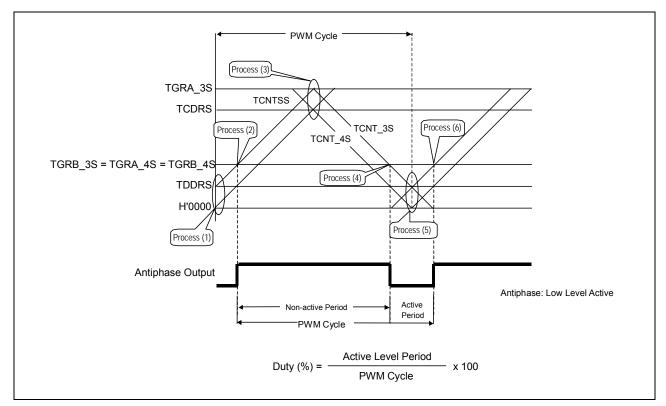

#### (h) Duty Setting

Figure 11 describes MTU2S (ch3, ch4) in complementary PWM mode and duty setting is explained after it.

Figure 11 Block Diagram when in Complementary PWM Mode (Channel 3/4)

[Notes] • CPU cannot directly access Temporary Register (Temp1S, 2S, 3S)

- Write into TGRB\_3S, TGRA\_4S, TGRB\_4S, TGRA\_3S, and TCDRS are prohibited during timer operation.

- When write into above listed register during timer operation is necessary, please write into their buffer register TGRD\_3S, TGRC\_4S, TGRD\_4S, TGRC\_3S, and TCBRS.

Following describes duty setting. This control sample outputs PWM only for antiphase. Level output is made for positive phase. Duty is determined by setting values of TGRB\_3S, TGRA\_4S, and TGRB\_4S. Motor drive current changes by changing duty setting, and it allows changing motor torque and speed. Figure 12 describes operation principle and Table 4 shows details of software/hardware process.

Figure 12 Counter Operation and Duty/PWM Cycle

#### Table 4 Details of Software/Hardware Processing for Duty Setting

|             | Software Process                                                                                                             | Hardware Process                                                                                                                                                                 |

|-------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Process (1) | Configure followings after releasing AD_0 module stop and<br>setting PFC<br>• Timer count start<br>• Output L level from pin | <ul> <li>TCNT_3S and TCNT_4S start up-count</li> </ul>                                                                                                                           |

| Process (2) | None                                                                                                                         | Output H level from pin by compare match between TCNT_3S and TGRB_3S, TGRA_4S, and TGRB_4S                                                                                       |

| Process (3) | • None                                                                                                                       | <ul> <li>TCNT_3S starts down-count by compare match<br/>between TCNT_3S and TGRA_3S</li> <li>TCNT_4S starts down-count by compare match<br/>between TCNT_4S and TCDRS</li> </ul> |

| Process (4) | None                                                                                                                         | <ul> <li>Output L level from pin by compare match between<br/>TCNT_3S and TGRB_3S, TGRA_4S, and TGRB_4S</li> </ul>                                                               |

| Process (5) | • None                                                                                                                       | <ul> <li>TCNT_3S starts up-count by compare match between<br/>TCNT_3S and TGRA_3S</li> <li>TCNT_4S starts up-count by compare match between<br/>TCNT_4S and TCDRS</li> </ul>     |

| Process (6) | • None                                                                                                                       | <ul> <li>Output L level from pin by compare match between<br/>TCNT_3S and TGRB_3S, TGRA_4S, and TGRB_4S</li> </ul>                                                               |

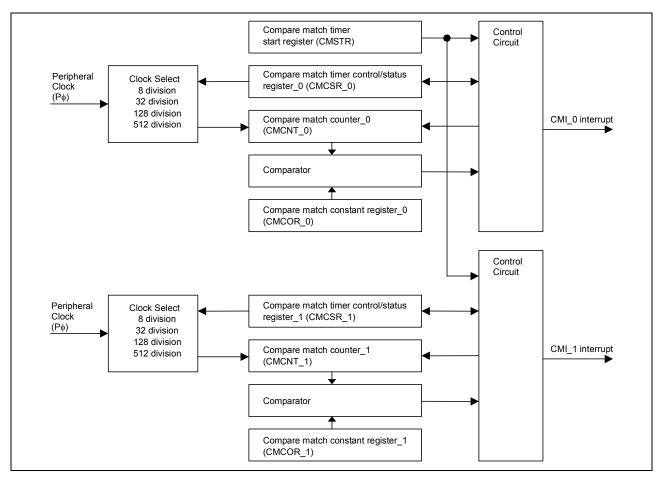

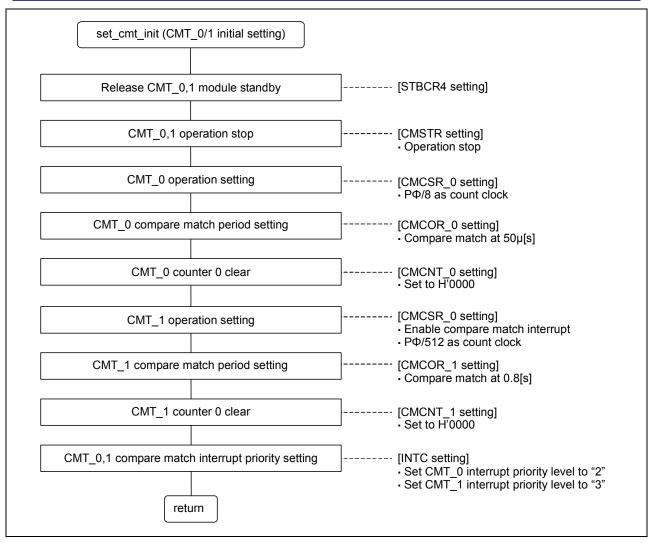

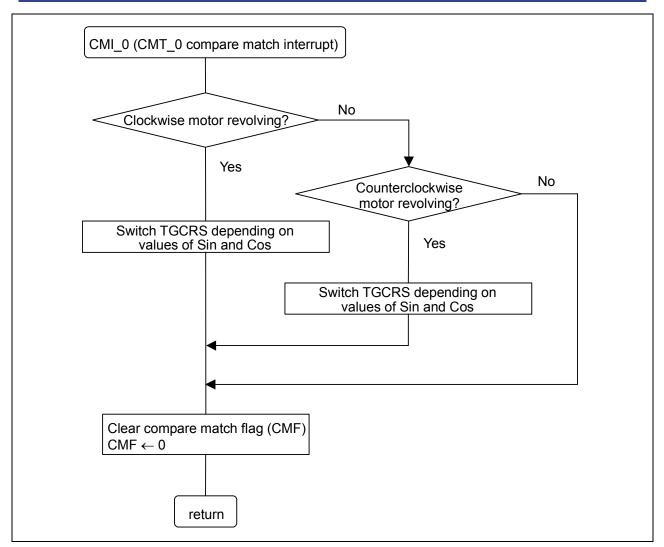

#### [3]CMT

#### (i) Overview of CMT Operation

Interrupt process is executed at every  $50\mu$  [sec] by using compare match timer channel 0 (CMT\_0). Interrupt process switches timer gate control register S (TGCRS) of MTU2S for outputting a PWM wave, which is most suitable to motor position.

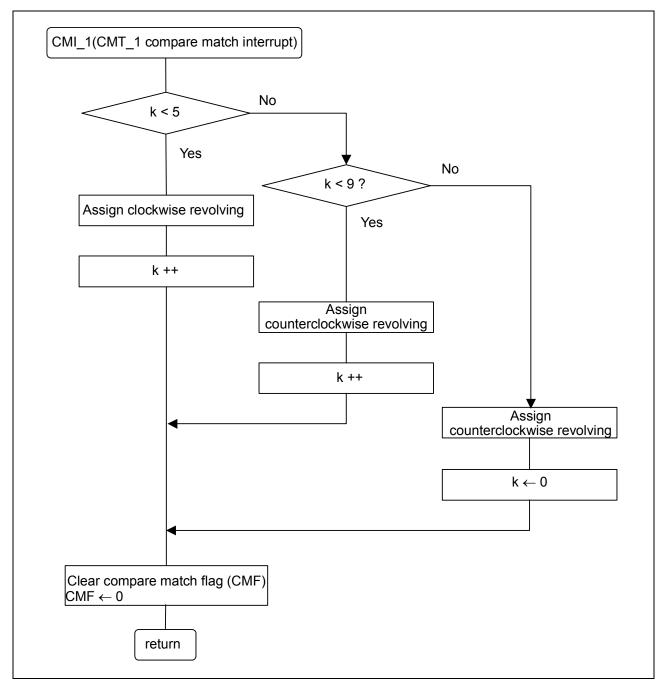

Also, interrupt process is executed at every 0.8 [sec] by using compare match timer channel 1 (CMT\_1). This interrupt process counts number of interrupt process and reverses motor revolving direction (clockwise  $\leftrightarrow$  counterclockwise) at every 5 interrupt process (every 4 [sec]). Figure 13 describes CMT block diagram.

Figure 13 CMT Block Diagram

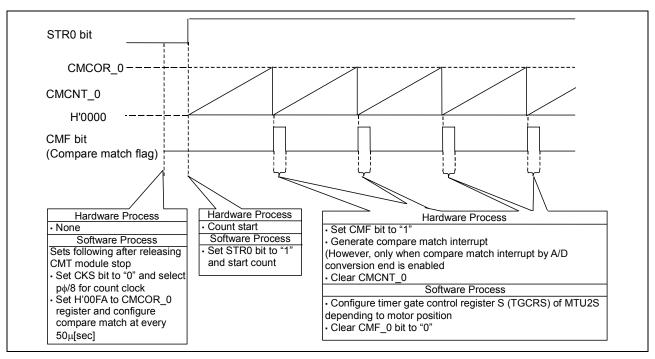

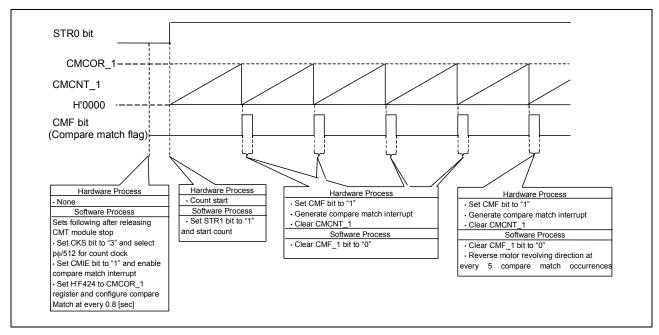

#### (j) Principle of CMT Operation

Figure 14 and Figure 15 describes principles of CMT\_0 and CMT\_1 operation.

Figure 14 Principle of CMT\_0 Operation (Assign TGCRS setting timing)

Figure 15 Principle of CMT\_1 Operation (Assign motor revolving direction reversing timing)

## 3.3 Sample program Procedure

Following describes each register setting.

#### Table 5 ADC\_0 Setting

| Register Name               | Bit Name  | Bit   | Function                                                                  | Set Value |

|-----------------------------|-----------|-------|---------------------------------------------------------------------------|-----------|

| A/D Control Register        | ADST      | 7     | 0: A/D conversion start                                                   | 0         |

| (ADCR_0)                    |           |       | 1: A/D conversion stop                                                    | 1         |

|                             | ADSC      | 6     | 0: 1 cycle scan                                                           | 1         |

|                             |           |       | 1: Continuous scan                                                        |           |

|                             | ACE       | 5     | 0: Prohibit automatic clear, after ADDR read                              | 0         |

|                             |           |       | 1: Enable automatic clear, after ADDR read                                |           |

|                             | ADIE      | 4     | 0: Prohibit A/D conversion end interrupt                                  | 1         |

|                             |           |       | 1: Enable A/D conversion end interrupt                                    |           |

|                             | Reserve   | 3-2   | —                                                                         | 0         |

|                             | TRGE      | 1     | 0: Prohibit A/D conversion triggered by exterior or MTU2/2S               | 0         |

|                             |           |       | 1: Enable A/D conversion triggered by exterior or MTU2/2S                 |           |

|                             | EXTRG     | 0     | 0: Select MTU2/MTU2S as A/D conversion start trigger                      | 0         |

|                             |           |       | 1: Select external pin (ADTRG) as A/D conversion start trigger            |           |

| A/D Status Register_0       | Reserve   | 7-1   | _                                                                         | 0         |

| (ADSR_0)                    | ADF       | 0     | A status flag indicating A/D conversion end                               | 0         |

|                             |           |       | 1 Set: A/D conversion of all the selected channels have ended.            | Note1     |

|                             |           |       | (Settable only by hardware process)                                       |           |

|                             |           |       | 0 Clear: • After read "1", write "0"                                      |           |

|                             |           |       | <ul> <li>Activate DTC by A/D conversion end interrupt and read</li> </ul> |           |

|                             |           |       | ADDR                                                                      | -         |

| A/D Analog Input Channel    | ANS7      | 7     | 0: Unselect AN7 as input channel                                          | 0         |

| Select Register_0           |           |       | 1: Select AN7 as input channel                                            |           |

| (ADANSR_0)                  | ANS6      | 6     | 0: Unselect AN6 as input channel                                          | 0         |

|                             |           |       | 1: Select AN6 as input channel                                            | -         |

|                             | ANS5      | 5     | 0: Unselect AN5 as input channel                                          | 0         |

|                             |           |       | 1: Select AN5 as input channel                                            |           |

|                             | ANS4      | 4     | 0: Unselect AN4 as input channel                                          | 0         |

|                             |           |       | 1: Select AN4 as input channel                                            |           |

|                             | ANS3      | 3     | 0: Unselect AN3 as input channel                                          | 0         |

|                             |           |       | 1: Select AN3 as input channel                                            |           |

|                             | ANS2      | 2     | 0: Unselect AN2 as input channel                                          | 1         |

|                             |           |       | 1: Select AN2 as input channel                                            |           |

|                             | ANS1      | 1     | 0: Unselect AN1 as input channel                                          | 1         |

|                             |           |       | 1: Select AN1 as input channel                                            |           |

|                             | ANS0      | 0     | 0: Unselect AN0 as input channel                                          | 1         |

|                             |           |       | 1: Select AN0 as input channel                                            |           |

| A/D Data Register 0 (ADDR0) | Reserve   | 15-12 | _                                                                         | R         |

|                             | ADD[11:0] | 11-0  | A/D conversion result of analog input pin 0(AN0) (12bit)                  |           |

| A/D Data Register 1 (ADDR1) | Reserve   | 15-12 | -                                                                         | R         |

|                             | ADD[11:0] | 11-0  | A/D conversion result of analog input pin 1(AN1) (12bit)                  |           |

| Register Name               | Bit Name  | Bit   | Function                                                 | Set Value |

|-----------------------------|-----------|-------|----------------------------------------------------------|-----------|

| A/D Data Register 2 (ADDR2) | Reserve   | 15-12 | _                                                        | R         |

|                             | ADD[11:0] | 11-0  | A/D conversion result of analog input pin 2(AN2) (12bit) |           |

| A/D Data Register 3 (ADDR3) | Reserve   | 15-12 | _                                                        | R         |

|                             | ADD[11:0] | 11-0  | A/D conversion result of analog input pin 3(AN3) (12bit) |           |

| A/D Data Register 4 (ADDR4) | Reserve   | 15-12 | _                                                        | R         |

|                             | ADD[11:0] | 11-0  | A/D conversion result of analog input pin 4(AN4) (12bit) |           |

| A/D Data Register 5 (ADDR5) | Reserve   | 15-12 | _                                                        | R         |

|                             | ADD[11:0] | 11-0  | A/D conversion result of analog input pin 5(AN5) (12bit) |           |

| A/D Data Register 6 (ADDR6) | Reserve   | 15-12 | _                                                        | R         |

|                             | ADD[11:0] | 11-0  | A/D conversion result of analog input pin 6(AN6) (12bit) |           |

| A/D Data Register 7 (ADDR7) | Reserve   | 15-12 | _                                                        | R         |

|                             | ADD[11:0] | 11-0  | A/D conversion result of analog input pin 7(AN7) (12bit) |           |

Note: 1: ADF is automatically set to "1"

R: Read-only bit

#### Table 6 MTU2S Setting

| Register Name                         | Bit Name  | Bit | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Set<br>Value |

|---------------------------------------|-----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Timer Control Register_3S<br>(TCR_3S) | CCLR[2:0] | 7-5 | Select counter clear factor of timer counter_3S (TCNT_3S)<br>000: Prohibit clear<br>001: Clear by compare match/input capture of TGRA_3S<br>010: Clear by compare match/input capture of TGRB_3S<br>011: Clear by counter clear of other channel, which is<br>cleared/operated synchronically<br>100: Prohibit clear<br>101: Clear by compare match/input capture of TGRC_3S<br>110: Clear by compare match/input capture of TGRD_3S<br>111: Clear by counter clear of other channel, which is<br>cleared/operated synchronically | H'000        |

|                                       | CKEG[1:0] | 4-3 | Select input clock edge<br>Effective only when input clock is slower than MIΦ/4<br>When selected input clock is faster than MIΦ/4, it is counted at only<br>rising edge.<br>00: Count at rising edge<br>01: Count at falling edge<br>10: Count at both rising/falling edge<br>11: Count at both rising/falling edge                                                                                                                                                                                                               | H'00         |

|                                       | TPSC[2:0] | 2-0 | Select counter clock of timer counter_3S (TCNT_3S)<br>000: ΜΙΦ/1<br>001: ΜΙΦ/4<br>010: ΜΙΦ/16<br>011: ΜΙΦ/64<br>100: ΜΙΦ/256<br>101: ΜΙΦ/1024<br>110: External clock (TCLKA)<br>111: External clock (TCKLB)                                                                                                                                                                                                                                                                                                                       | H'000        |

| Timer Control Register_4S<br>(TCR_4S) | CCLR[2:0] | 7-5 | Select counter clear factor of timer counter_4S (TCNT_4S)<br>000: Prohibit clear<br>001: Clear by compare match/input capture of TGRA_4S<br>010: Clear by compare match/input capture of TGRB_4S<br>011: Clear by counter clear of other channel, which is<br>cleared/operated synchronically<br>100: Prohibit clear<br>101: Clear by compare match/input capture of TGRC_4S<br>110: Clear by compare match/input capture of TGRD_4S<br>111: Clear by counter clear of other channel, which is<br>cleared/operated synchronically | H'000        |

|                                       | CKEG[1:0] | 4-3 | Select input clock edge<br>Effective only when input clock is slower than MIΦ/4<br>When selected input clock is faster than MIΦ/4, it is counted at only<br>rising edge.<br>00: Count at rising edge<br>01: Count at falling edge<br>10: Count at both rising/falling edge<br>11: Count at both rising/falling edge                                                                                                                                                                                                               | H'00         |

| Register Name             | Bit Name  | Bit | Function                                             | Set<br>Value |

|---------------------------|-----------|-----|------------------------------------------------------|--------------|

| Timer Control Register_4S | TPSC[2:0] | 2-0 | Select counter clock of timer counter_4S (TCNT_4S)   | H'000        |

| (TCR_4S)                  |           |     | 000: MIФ/1                                           |              |

|                           |           |     | 001: ΜΙΦ/4                                           |              |

|                           |           |     | 010: MIФ/16                                          |              |

|                           |           |     | 011: МІФ/64                                          |              |

|                           |           |     | 100: MIФ/256                                         |              |

|                           |           |     | 101: MIФ/1024                                        |              |

|                           |           |     | 110: External clock (TCLKA)                          |              |

|                           |           |     | 111: External clock (TCKLB)                          |              |

| Timer Mode Register_3S    | Reserve   | 7   | -                                                    | 0            |

| (TMDR_3S)                 | Reserve   | 6   | -                                                    | 0            |

|                           | BFB       | 5   | 0: TGRB_3S and TGRD_3S are in normal operation       | 1            |

|                           |           |     | 1: TGRB_3S and TGRD_3S are in buffer operation       |              |

|                           | BFA       | 4   | 0: TGRA_3S and TGRC_3S are in normal operation       | 1            |

|                           |           |     | 1: TGRA_3S and TGRC_3S are in buffer operation       |              |

|                           | MD[3:0]   |     | 0000: Normal operation                               | H'1101       |

|                           |           |     | 0001: Setting prohibited                             |              |

|                           |           |     | 0010: PWM mode 1                                     |              |

|                           |           |     | 0011: Setting prohibited                             |              |

|                           |           |     | 0100: Setting prohibited                             |              |

|                           |           |     | 0101: Setting prohibited                             |              |

|                           |           |     | 0110: Setting prohibited                             |              |

|                           |           |     | 0111: Setting prohibited                             |              |

|                           |           |     | 1000: Reset-synchronized PWM mode                    |              |

|                           |           |     | 1001: Setting prohibited                             |              |

|                           |           |     | 1010: Setting prohibited                             |              |

|                           |           |     | 1011: Setting prohibited                             |              |

|                           |           |     | 1100: Setting prohibited                             |              |

|                           |           |     | 1101: Complementary PWM mode 1 (transfer at peaks)   |              |

|                           |           |     | 1110: Complementary PWM mode 2 (transfer at valleys) |              |

|                           |           |     | 1111: Complementary PWM mode 3 (transfer at peaks    |              |

|                           |           |     | and valleys)                                         |              |

| Register Name              | Bit Name | Bit | Function                                         | Set<br>Value |

|----------------------------|----------|-----|--------------------------------------------------|--------------|

| Timer Mode Register_4S     | Reserve  | 7   | _                                                | 0            |

| (TMDR_4S)                  | Reserve  | 6   | _                                                | 0            |

|                            | BFB      | 5   | 0: TGRB_4S and TGRD_4S are in normal operation   | 1            |

|                            |          |     | 1: TGRB_4S and TGRD_4S are in buffer operation   |              |

|                            | BFA      | 4   | 0: TGRA_4S and TGRC_4S are in normal operation   | 1            |

|                            |          |     | 1: TGRA_4S and TGRC_4S are in buffer operation   |              |

|                            | MD[3:0]  | 3-0 | 0000: Normal operation                           | H'0000       |

|                            |          |     | 0001: Setting prohibited                         | Note2        |

|                            |          |     | 0010: PWM mode 1                                 |              |

|                            |          |     | 0011: Setting prohibited                         |              |

|                            |          |     | 0100: Setting prohibited                         |              |

|                            |          |     | 0101: Setting prohibited                         |              |

|                            |          |     | 0110: Setting prohibited                         |              |

|                            |          |     | 0111: Setting prohibited                         |              |

|                            |          |     | 1000: Setting prohibited                         |              |

|                            |          |     | 1001: Setting prohibited                         |              |

|                            |          |     | 1010: Setting prohibited                         |              |

|                            |          |     | 1011: Setting prohibited                         |              |

|                            |          |     | 1100: Setting prohibited                         |              |

|                            |          |     | 1101: Setting prohibited                         |              |

|                            |          |     | 1110: Setting prohibited                         |              |

|                            |          |     | 1111: Setting prohibited                         |              |

| Timer Output Master Enable | Reserve  | 7-6 | _                                                | 3            |

| Register S (TOERS)         | OE4D     | 5   | 0: Prohibit MTU2S output by TIOC4DS pin          | 1            |

|                            |          |     | (Non-active level) Note2                         |              |

|                            |          |     | 1: Enable MTU2S output by TIOC4DS pin (*W-phase) |              |

|                            | OE4C     | 4   | 0: Prohibit MTU2S output by TIOC4CS pin          | 1            |

|                            |          |     | (Non-active level) Note2                         |              |

|                            |          |     | 1: Enable MTU2S output by TIOC4CS pin            |              |

|                            | OE3D     | 3   | 0: Prohibit MTU2S output by TIOC3DS pin          | 1            |

|                            |          |     | (Non-active level) Note2                         |              |

|                            |          |     | 1: Enable MTU2S output by TIOC3DS pin            |              |

|                            | OE4B     | 2   | 0: Prohibit MTU2S output by TIOC4BS pin          | 1            |

|                            |          |     | (Non-active level) Note2                         |              |

|                            |          |     | 1: Enable MTU2S output by TIOC4BS pin            |              |

|                            | OE4A     | 1   | 0: Prohibit MTU2S output by TIOC4AS pin          | 1            |

|                            |          | -   | (Non-active level) Note2                         |              |

|                            |          |     | 1: Enable MTU2S output by TIOC4AS pin            |              |

|                            | OE3B     | 0   | 0: Prohibit MTU2S output by TIOC3BS pin          | 1            |

|                            | 0130     | 0   | (Non-active level) Note2                         |              |

|                            |          |     | 1: Enable MTU2S output by TIOC3BS pin            |              |

|                            |          | L   |                                                  |              |

| Register Name                   | Bit Name | Bit | Function                                                                                                                                                                                                                                                                                                                                                             | Set<br>Value   |

|---------------------------------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Timer Gate Control Register S   | Reserve  | 7   | _                                                                                                                                                                                                                                                                                                                                                                    | 1              |

| (TGCRS)                         | BDC      | 6   | 0: Disable TGCRS register (this register) setting<br>1: Enable TGCRS register (this register) setting                                                                                                                                                                                                                                                                | 1              |

|                                 | N        | 5   | Select output state of antiphase output pin (TIOC3DS<br>(*U-phase),<br>TIOC4CS (*V-phase), TIOC4DS (*W-phase)) Note3<br>0: Level output<br>1: Reset-synchronized PWM/ Complementary PWM                                                                                                                                                                              | 1              |

|                                 | Ρ        | 4   | Select output state of positive phase output pin<br>(TIOC3BS (U-phase),<br>TIOC4AS (V-phase), TIOC4BS (W-phase)) Note3<br>0: Level output<br>1: Reset-synchronized PWM/ Complementary PWM                                                                                                                                                                            | 0              |

|                                 | FB       | 3   | <ul><li>0: Switch output phase by external input</li><li>1: Switch output phase by software<br/>(setting of UF, VF, and WF bit of TGCRS)</li></ul>                                                                                                                                                                                                                   | 1              |

|                                 | WF       | 2   | Set output phase by switching WF, VF, and UF bit Please refer Table 7                                                                                                                                                                                                                                                                                                | H'000<br>Note4 |

| Timer Output Control Register1S | Reserve  | 7   | _                                                                                                                                                                                                                                                                                                                                                                    | 0              |

| (TOCR1S)                        | PSYE     | 6   | 0: Prohibit toggle output synchronized to PWM cycle<br>1: Enable toggle output synchronized to PWM cycle                                                                                                                                                                                                                                                             | 0              |

|                                 | Reserve  | 5-4 | _                                                                                                                                                                                                                                                                                                                                                                    | 0              |

|                                 | TOCL     | 3   | 0: Enable write to TOCS, OLSN, and OLSP bit<br>1: Prohibit write to TOCS, OLSN, and OLSP bit                                                                                                                                                                                                                                                                         | 0              |

|                                 | TOCS     | 2   | Set output level in complementary PWM mode/reset-<br>synchronized<br>PWM mode<br>0: TOCR1 setting effective<br>1: TOCR2 setting effective                                                                                                                                                                                                                            | 0              |

|                                 | OLSN     | 1   | <ul> <li>Select antiphase output level in complementary/ resetsynchronized</li> <li>PWM mode</li> <li>0: Initial output → H, Active level → L,<br/>Compare match while up-count → H,<br/>Compare match while down-count → L</li> <li>1: Initial output → L, Active level → H,<br/>Compare match while up-count → L,<br/>Compare match while up-count → L,</li> </ul> | 0              |

|                                 | OLSP     | 0   | <ul> <li>Select positive phase output level in complementary/ reset-synchronized PWM mode</li> <li>0: Initial output → H, Active level → L,<br/>Compare match while up-count → L,<br/>Compare match while down-count → H</li> <li>1: Initial output → L, Active level → H,<br/>Compare match while up-count → H,<br/>Compare match while up-count → H,</li> </ul>    | 0              |

| Register Name                              | Bit Name | Bit  | Function                                                                                                                            | Set<br>Value    |

|--------------------------------------------|----------|------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Timer Counter_3S<br>(TCNT_3S)              |          | 15-0 | Counter of channel 3                                                                                                                | H'0000<br>Note5 |

| Timer Counter _4S<br>(TCNT_4S)             |          | 15-0 | Counter of channel 4                                                                                                                | H'0000<br>Note5 |

| Timer Cycle Data Register S<br>(TCDRS)     |          | 15-0 | A register been used only in complementary PWM<br>mode<br>Set PWM carrier period to 1/2                                             | H'0640          |

| Timer Dead Time Data<br>Register S (TDDRS) |          | 15-0 | A register been used only in complementary PWM<br>mode<br>Set dead time                                                             | H'0001          |

| Timer General Register A_3S<br>(TGRA_3S)   |          | 15-0 | When complementary PWM mode is set;<br>Set (1/2 of PWM carrier period + dead time)                                                  | H'0641          |

| Timer General Register B_3S<br>(TGRB_3S)   |          | 15-0 | When complementary PWM mode is set;<br>Compare register of TIOC3BS(U-phase)/TIOC3DS(*U-<br>phase) pin<br>output                     | H'00A0          |

| Timer General Register A_4S<br>(TGRA_4S)   |          | 15-0 | When complementary PWM mode is set;<br>Compare register of TIOC3AS(V-phase)/TIOC4CS(*V-<br>phase) pin<br>output                     | H'00A0          |

| Timer General Register B_4S<br>(TGRB_4S)   |          | 15-0 | When complementary PWM mode is set;<br>Compare register of TIOC4BS(W-phase)/<br>TIOC4DS(*W-phase) pin<br>output                     | H'00A0          |

| Timer Cycle Buffer Register S<br>(TCBRS)   |          | 15-0 | A register been used only in complementary PWM mode<br>Buffer register of TCDRS                                                     | H'0640          |

| Timer General Register C_3S<br>(TGRC_3S)   |          | 15-0 | When complementary PWM mode is set; Buffer<br>register of TGRA_3S<br>TGRC_3S is set when changing TGRA_3S during<br>timer operation | H'0641          |

| Timer General Register D_3S<br>(TGRD_3S)   |          | 15-0 | When complementary PWM mode is set; Buffer register of TGRB_3S<br>TGRD_3S is set when changing TGRB_3S during timer operation       | H'00A0          |

| Timer General Register C_4S<br>(TGRC_4S)   |          | 15-0 | When complementary PWM mode is set; Buffer<br>register of TGRA_4S<br>TGRC_4S is set when changing TGRA_4S during<br>timer operation | H'00A0          |

| Timer General Register D_4S<br>(TGRD_4S)   |          | 15-0 | When complementary PWM mode is set; Buffer<br>register of TGRB_4S<br>TGRD_4S is set when changing TGRB_4S during<br>timer operation | H'00A0          |

| Timer Dead Time Enable                     | Reserve  | 7-1  |                                                                                                                                     |                 |

| Register S<br>(TDERS)                      | TDER     | 0    | 0: Do not generate dead time<br>1: Generate dead time                                                                               | 1               |

## **Resolver Built-in DC Brushless Motor Control**

| Register Name          | Bit Name | Bit | Function                                      | Set<br>Value |

|------------------------|----------|-----|-----------------------------------------------|--------------|

| Timer Start Register S | CST4     | 7   | 0: Count stop of timer counter_4S (TCNT_4S)   | 0            |

| (TSTRS)                |          |     | 1: Count start of timer counter_4S (TCNT_4S)  | 1            |

|                        | CST3     | 6   | 0: Count stop of timer counter_3S (TCNT_3S)   | 0            |

|                        |          |     | 1: Count start of timer counter _3S (TCNT_3S) | 1            |

|                        | Reserve  | 5-3 | _                                             | 0            |

|                        | Reserve  | 2   | _                                             | 0            |

|                        | Reserve  | 1   | _                                             | 0            |

|                        | Reserve  | 0   | _                                             | 0            |

Note2 Non-active level complies TOCR1S/2S setting

Note3 U-phase, V-phase, and W-phase are positive phase.

\*U-phase, \*V-phase, and \*W-phase are antiphase.

Note4 Initial value. This control sample switches WF, VF, and UF bit depending on motor position.

Note5 Initial value.

Changes during timer operation.

#### Table 7 Output Level Select Function

| Bit 2 | Bit 1 | Bit 0 | Function |         |         |          |          |          |

|-------|-------|-------|----------|---------|---------|----------|----------|----------|

| WF    | VF    | UF    | TIOC3BS  | TIOC4AS | TIOC4BS | TIOC3DS  | TIOC4CS  | TIOC4D   |

|       |       |       | U-phase  | V-phase | W-phase | *U-phase | *V-phase | *W-phase |

| 0     | 0     | 0     | OFF      | OFF     | OFF     | OFF      | OFF      | OFF      |

| 0     | 0     | 1     | ON       | OFF     | OFF     | OFF      | OFF      | ON       |

| 0     | 1     | 0     | OFF      | ON      | OFF     | ON       | OFF      | OFF      |

| 0     | 1     | 1     | OFF      | ON      | OFF     | OFF      | OFF      | ON       |

| 1     | 0     | 0     | OFF      | OFF     | ON      | OFF      | ON       | OFF      |

| 1     | 0     | 1     | ON       | OFF     | OFF     | OFF      | ON       | OFF      |

| 1     | 1     | 0     | OFF      | OFF     | ON      | ON       | OFF      | OFF      |

| 1     | 1     | 1     | OFF      | OFF     | OFF     | OFF      | OFF      | OFF      |

#### Table 8 CMT\_0,1 Setting

| Register Name                        | Bit Name | Bit  | Function                                                                           | Set Valu |

|--------------------------------------|----------|------|------------------------------------------------------------------------------------|----------|

| Compare Match Timer Start            | Reserve  | 15-2 | —                                                                                  | 0        |

| Register (CMSTR)                     | STR1     | 1    | 0: Count stop of compare match counter_1                                           | 0        |

|                                      |          |      | 1: Count start of compare match counter_1                                          | 1        |

|                                      | STR0     | 0    | 0: Count stop of compare match counter_0                                           | 0        |

|                                      |          |      | 1: Count start of compare match counter_0                                          | 1        |

| Compare Match Timer Control          | Reserve  | 15-8 |                                                                                    | 0        |

| Register_0                           | CMF      | 7    | A flag which indicates match of compare match constant register_0 (CMCOR_0)        | 0        |

| (CMCSR_0)                            |          |      | value and compare match timer counter_0 (CMCNT_0) value.                           | *Note6   |

|                                      |          |      | 1 Set: CMCOR_0 and CMCNT_0 matches (automatically set by hardware)                 |          |

|                                      |          |      | 0 Clear: • Write "0"                                                               |          |

|                                      |          |      | <ul> <li>When CMT register is accessed while DTC module is activated by</li> </ul> |          |

|                                      |          |      | CMI_0 interrupt and MRB/DISEL bit of DTC is "0"                                    |          |

|                                      | CMIE     | 6    | 0: Prohibit compare match interrupt (CMI_0)                                        | 1        |

|                                      |          |      | 1: Enable compare match interrupt (CMI_0)                                          |          |

|                                      | Reserve  | 5-2  | _                                                                                  | 0        |

|                                      | CKS[1:0] | 1-0  | Select frequency for counting CMCNT_0                                              | H'00     |

|                                      |          |      | 00: РФ/8                                                                           |          |

|                                      |          |      | 01: PΦ/32                                                                          |          |

|                                      |          |      | 10: PΦ/128                                                                         |          |

| 0 N// 0 / 0                          |          | 45.0 | 11: PΦ/512                                                                         |          |

| Compare Match Counter_0<br>(CMCNT_0) |          | 15-0 | Counter for up-count                                                               | H'0000   |

| Compare Match Constant<br>Register_0 |          | 15-0 | Set the duration until matching with CMCNT_0                                       | H'00C8   |

| (CMCOR_0)                            |          |      |                                                                                    |          |

| Compare Match Timer Control          | Reserve  | 15-8 | _                                                                                  | 0        |

| Register_1                           | CMF      | 7    | A flag which indicates match of compare match constant register_1 (CMCOR_1)        | 0        |

| (CMCSR_1)                            |          |      | value and compare match timer counter_1 (CMCNT_1) value.                           | *Note6   |

|                                      |          |      | 1 Set: CMCOR_1 and CMCNT_1 matches (automatically set by hardware)                 |          |

|                                      |          |      | 0 Clear: • Write "0"                                                               |          |

|                                      |          |      | When CMT register is accessed while DTC module is activated by                     |          |

|                                      |          |      | CMI_1 interrupt and MRB/DISEL bit of DTC is "0"                                    |          |

|                                      | CMIE     | 6    | 0: Prohibit compare match interrupt (CMI_1)                                        | 1        |

|                                      |          | 5.0  | 1: Enable compare match interrupt (CMI_1)                                          |          |

|                                      | Reserve  | 5-2  | —                                                                                  | 0        |

|                                      | CKS[1:0] | 1-0  | Select frequency for counting CMCNT_1                                              | H'11     |

|                                      |          |      | 00: ΡΦ/8<br>01: ΡΦ/32                                                              |          |

|                                      |          |      | 01. ΡΦ/32<br>10: ΡΦ/128                                                            |          |

|                                      |          |      | 11: PΦ/512                                                                         |          |

| Compare MatchCounter_1<br>(CMCNT_1)  |          | 15-0 | Counter for up-count                                                               | H'0000   |

| Compare Match Constant               |          | 15-0 | Set the duration until matching with CMCNT_1                                       | H'C350   |

| Register_1<br>(CMCOR_1)              |          |      |                                                                                    |          |

Note6: CMF is automatically set to "1"

#### Table 9 PFC Setting

| Register Name              | Bit Name           | Bit    | Function                                                    | Set Value |

|----------------------------|--------------------|--------|-------------------------------------------------------------|-----------|

| Port E IO Register H       | Reserve            | 15-6   | _                                                           | 0         |

| (PEIORH)                   | PE21               | 5      | 0: PE21 pin (2pin) is input                                 | 1         |

|                            |                    |        | 1: PE21 pin (2pin) is output                                |           |

|                            | PE20               | 4      | 0: PE20 pin (4pin) is input                                 | 1         |

|                            |                    |        | 1: PE20 pin (4pin) is output                                |           |

|                            | PE19               | 3      | 0: PE19 pin (5pin) is input                                 | 1         |

|                            |                    |        | 1: PE19 pin (5pin) is output                                |           |

|                            | PE18               | 2      | 0: PE18 pin (6pin) is input                                 | 1         |

|                            |                    |        | 1: PE18 pin (6pin) is output                                |           |

|                            | PE17               | 1      | 0: PE17 pin (7pin) is input                                 | 1         |

|                            |                    |        | 1: PE17 pin (7pin) is output                                |           |

|                            | PE16               | 0      | 0: PE16 pin (8pin) is input                                 | 1         |

|                            |                    |        | 1: PE16 pin (8pin) is output                                |           |

| Port E Control Register H2 | Reserve            | 15-6   | —                                                           | 0         |

| (PECRH2)                   | PE21MD1            | 5      | 00: PE21 input/output (port)                                | H'01      |

|                            | PE21MD0            | 4      | 01: TIOC4DS input/output (MTU2S)                            |           |

|                            |                    |        | 10: WRL output (BSC)                                        |           |

|                            |                    |        | 11: Setting prohibited                                      |           |

|                            | Reserve            | 3-2    | _                                                           | 0         |

|                            | PE20MD1            | 1      | 00: PE20 input/output (port)                                | H'01      |

|                            | PE20MD0            | 0      | 01: TIOC4CS input/output (MTU2S)                            |           |

|                            |                    |        | 10: Setting prohibited                                      |           |

|                            |                    |        | 11: Setting prohibited                                      |           |

| Port E Control Register H1 | Reserve            | 15-14  | —                                                           | 0         |

| (PECRH1)                   | PE19MD1            | 13     | 00: PE19 input/output (port)                                | H'01      |

|                            | PE19MD0            | 12     | 01: TIOC4BS input/output (MTU2S)                            |           |

|                            |                    |        | 10: RD output (BSC)                                         |           |

|                            |                    |        | 11: Setting prohibited                                      |           |

|                            | Reserve            | 11-10  | —                                                           | 0         |

|                            | PE18MD1            | 9      | 00: PE18 input/output (port)                                | H'01      |

|                            | PE18MD0            | 8      | 01: TIOC4AS input/output (MTU2S)                            |           |

|                            |                    |        | 10: CS1 output (BSC)<br>11: Setting prohibited              |           |

|                            | Deserve            | 7.0    |                                                             | 0         |

|                            | Reserve            | 7-6    |                                                             | 0         |

|                            | PE17MD1            | 5      | 00: PE17 input/output (port)                                | H'01      |

|                            | PE17MD0            | 4      | 01: TIOC3DS input/output (MTU2S)                            |           |

|                            |                    |        | 10: CS0 output (BSC)<br>11: Setting prohibited              |           |

|                            | Reserve            | 2      |                                                             | 0         |

|                            |                    | 3      |                                                             |           |

|                            | PE16MD2            | 2      | 000: PE16 input/output (port)                               | H'01      |