#### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics atta abooks, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU ROHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# 32

SH7046 Series On-Chip Peripheral Functions — DTC Volume Application Note

Renesas 32-Bit RISC Microcomputer SuperH<sup>™</sup> RISC engine Family/ SH7046 Series

Renesas Electronics

Rev.1.00 2003.11

#### Renesas

Renesas 32-Bit RISC Microcomputer SuperH<sup>™</sup> RISC engine Family/SH7046 Series

# SH7046 Series On-Chip Peripheral Functions — DTC Volume —

# **Application Note**

REJ05B0275-01000

#### Cautions

Keep safety first in your circuit designs!

Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

Notes regarding these materials

- 1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein. The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors. Please also pay attention to information published by Renesas Technology Corp. by various

means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination. Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

#### RENESAS

## Preface

The SH7046F, SH7148, SH7047F, and SH7049 are high-performance microcomputers with a 32bit SH-2 CPU core that uses a RISC (Reduced Instruction Set Computer) type instruction set, and comprehensive on-chip peripheral functions.

On-chip peripherals include a CPU, ROM, RAM, a 16-bit multifunction timer pulse unit (MTU), serial communication interface (SCI), port output enable (POE), data transfer controller (DTC), and motor management timer (MMT), enabling these microcomputers to be used for a wide range of applications covering small to large-scale systems.

This Application Note includes sample tasks that use the SH7046 Series' on-chip peripheral functions, which we hope users will find useful as reference material in carrying out software design.

Although the operation of the task programs in this Application Note has been checked, operation should be confirmed again before any of these programs are actually used.

Rev. 1.00, 11/03, page vi of viii

### Contents

| Section 1.1<br>1.2 | on 1 Using the SH7046 Series Application Note<br>Organization of Application Note<br>Organization | 1  |

|--------------------|---------------------------------------------------------------------------------------------------|----|

| Casti              |                                                                                                   |    |

| Secu               | on 2 On-Chip Peripheral Functions — DTC Volume                                                    | 3  |

| 2.1                | Data Transfer Using DTC Normal Mode (CMT, DTC)                                                    | 3  |

| 2.2                | Data Transfer Using DTC Repeat Mode (CMT, DTC)                                                    | 22 |

| 2.3                | Data Transfer Using DTC Block Transfer Mode (CMT, DTC)                                            | 41 |

| 2.4                | Data Transfer Using DTC Chain Transfer (CMT, DTC)                                                 | 60 |

| 2.5                | Asynchronous Serial Data Simultaneous Transmission/Reception and DTC Data                         |    |

|                    | Transfer (SCI, DTC)                                                                               | 80 |

| 2.6                | Synchronous Serial Data Simultaneous Transmission/Reception and DTC Data                          |    |

|                    | Transfer (SCI, DTC) 1                                                                             | 07 |

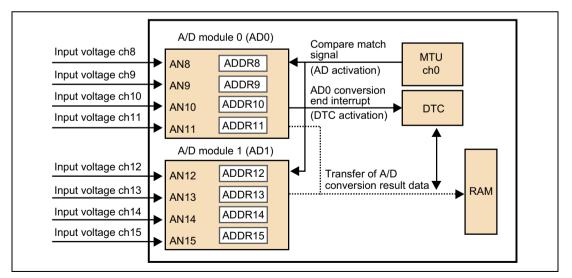

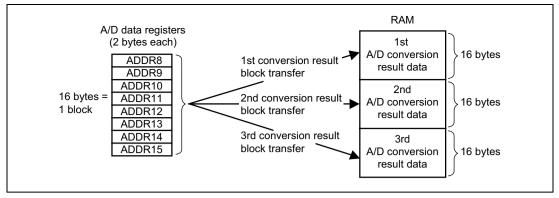

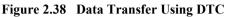

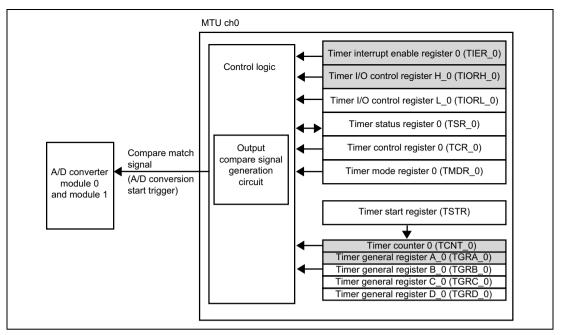

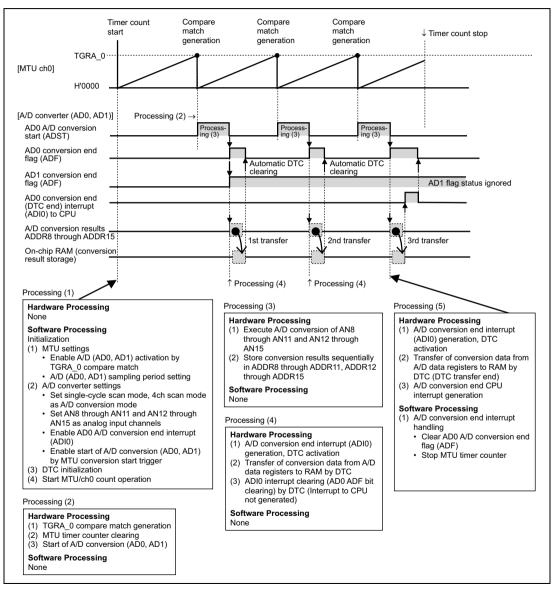

| 2.7                | Start of A/D Conversion by MTU, and Conversion Result Storage (A/D, DTC) 1                        | 33 |

| Secti              | on 3 Appendix                                                                                     | 57 |

Rev. 1.00, 11/03, page viii of viii

## Section 1 Using the SH7046 Series Application Note

#### 1.1 Organization of Application Note

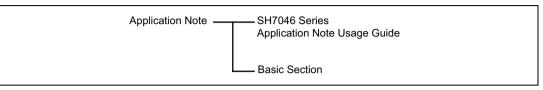

This Application Note consists of two parts, as shown in figure 1.1.

- SH7046 Series Application Note Usage Guide Explains how to use the SH7046 Series Application Note.

- (2) On-Chip Peripheral Functions DTC Volume

Mainly illustrates the use of the DTC among the SH7046 Series' on-chip peripheral functions, based on sample tasks.

#### 1.2 Organization

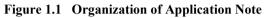

The layout shown in figure 1.2 is employed to describe the use of on-chip peripheral functions.

Figure 1.2 Organization

Rev. 1.00, 11/03, page 1 of 196

#### Renesas

#### (1) Specifications

Describes the system specifications for the sample task.

(2) Functions Used

Describes the features of the peripheral function(s) used in the sample task, and peripheral function assignment.

(3) Operation

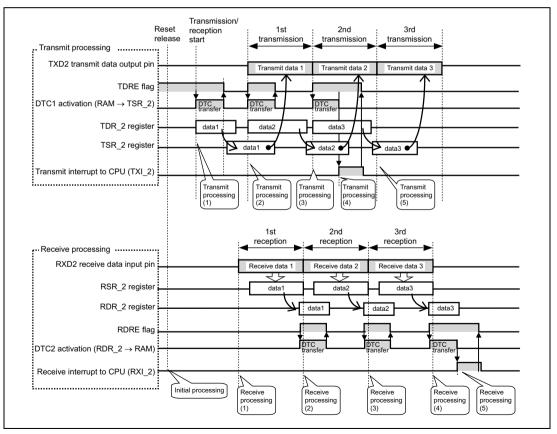

Describes the operation of the sample task, using a timing chart.

- (4) Software

- (a) Modules

Describes the software modules used in the operation of the sample task.

(b) Arguments

Describes the input arguments needed to execute the modules, and the output arguments after execution.

(c) Internal Registers Used

Describes the peripheral function internal registers (timer control registers, serial mode registers, etc.) set by the modules.

(d) RAM Used

Describes the labels and functions of RAM used by the modules.

(5) Flowcharts

Describes the software that executes the sample task, using flowcharts.

(6) Program Listing

Shows a program listing of the software that executes the sample task.

#### 2.1 Data Transfer Using DTC Normal Mode (CMT, DTC)

| Data Transfer Using DTC Normal Mode (CMT, DTC) | Functions Used: CMT, DTC |

|------------------------------------------------|--------------------------|

|------------------------------------------------|--------------------------|

#### **Specifications**

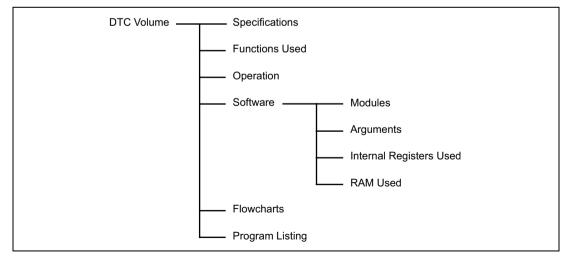

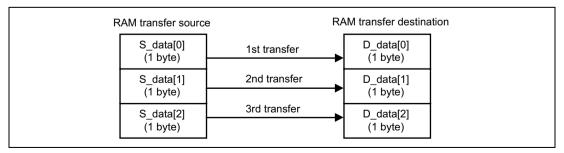

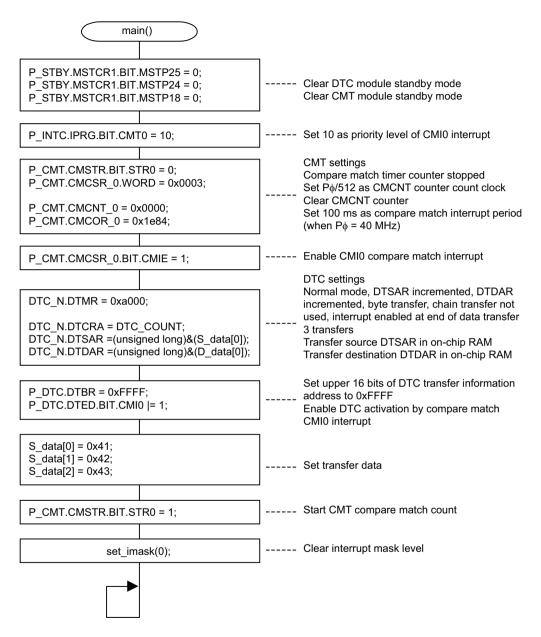

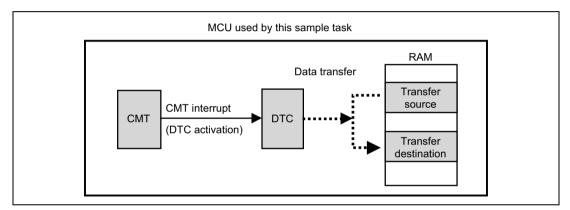

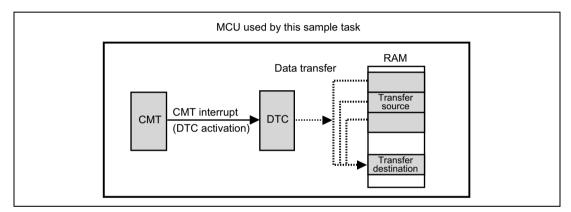

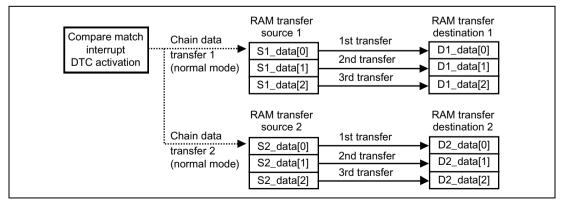

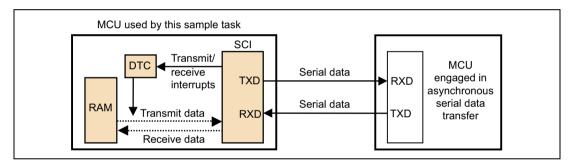

- (1) The data transfer controller (DTC) is activated by a compare match timer (CMT) compare match interrupt, and performs data transfer from on-chip RAM to on-chip RAM, as shown in figure 2.1.

- (2) Normal mode is used for DTC data transfer, with 3-byte transfer performed as shown in figure 2.2.

- (3) The DTC transfer conditions are shown in table 2.1.

Figure 2.1 Data Transfer Using DTC

Figure 2.2 Data Transfer Using DTC Normal Mode

#### Renesas

| Condition                    | Description                                                     |

|------------------------------|-----------------------------------------------------------------|

| Transfer mode                | Normal mode                                                     |

| Number of transfers          | 3                                                               |

| Transfer data size           | Byte transfer                                                   |

| Transfer source              | On-chip RAM                                                     |

| Transfer destination         | On-chip RAM                                                     |

| Transfer source address      | Transfer source address incremented after transfer              |

| Transfer destination address | Transfer destination address incremented after transfer         |

| Activation source            | Activated by CMT ch0 compare match interrupt (CMI0)             |

| Interrupt handling           | Interrupt to CPU enabled only at end of specified data transfer |

#### Table 2.1DTC Transfer Conditions

#### **Functions Used**

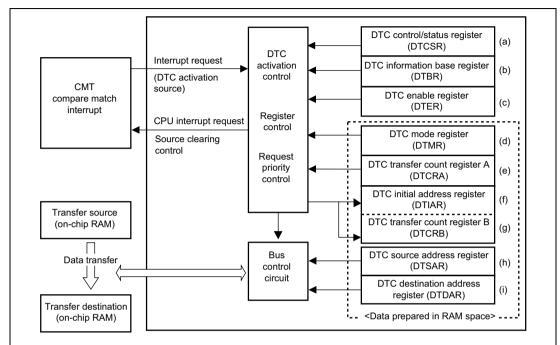

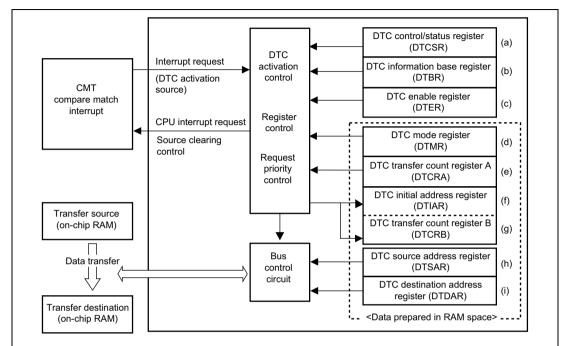

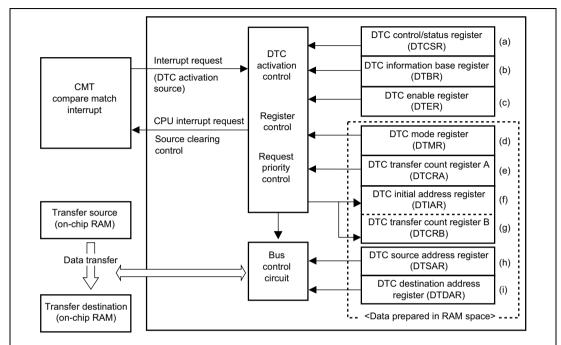

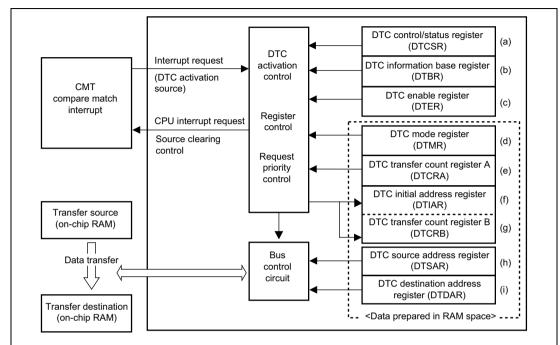

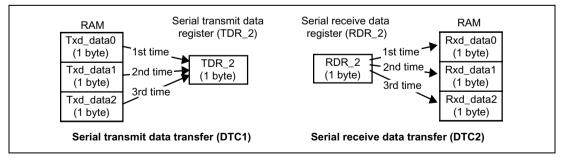

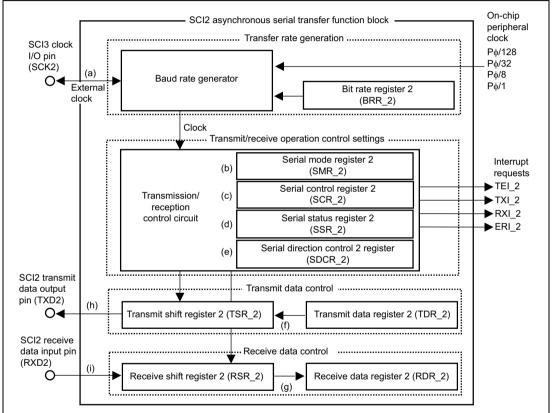

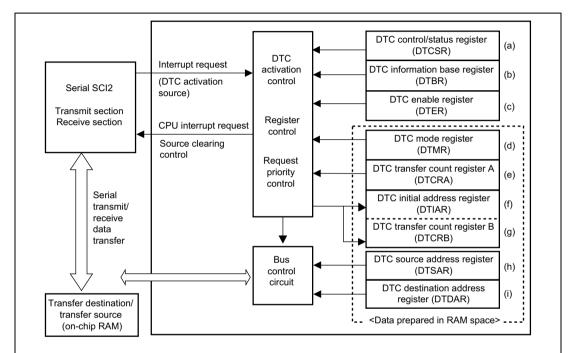

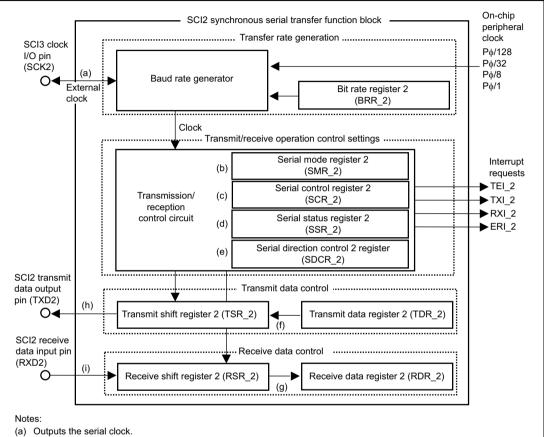

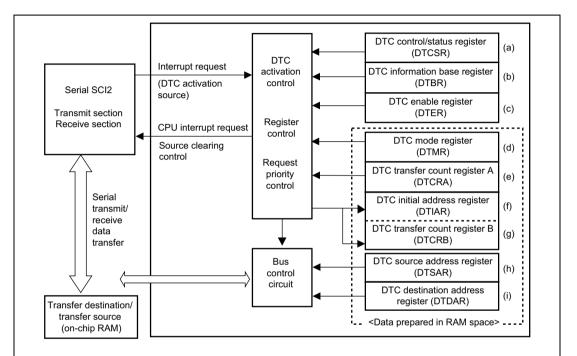

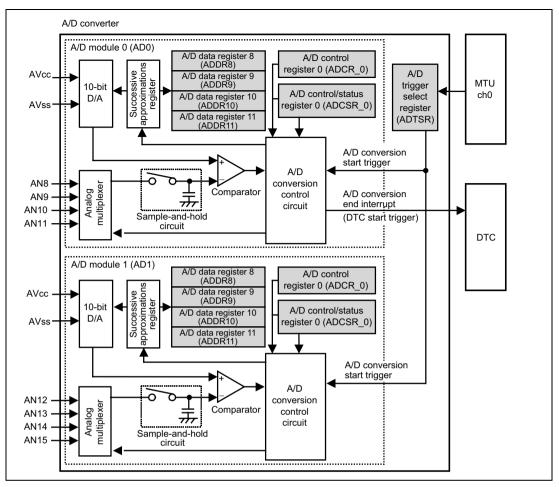

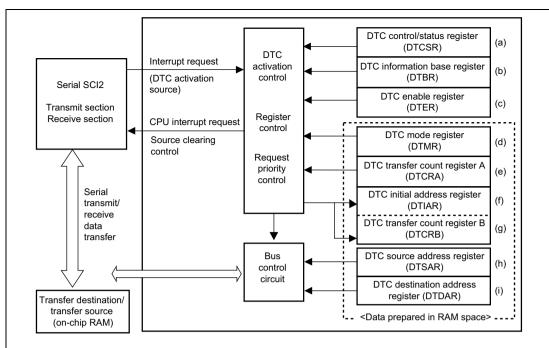

- (1) A block diagram of the DTC is shown below. Of the three DTC transfer modes normal mode, repeat mode, and block transfer mode —this sample task uses normal mode to perform data transfer. Data transfer is performed from on-chip RAM to on-chip RAM, using a CMT compare match interrupt as the DTC activation source. The block diagram is explained below.

- The DTC mode register (DTMR) is a 16-bit register that controls the DTC's operating mode.

- The DTC source address register (DTSAR) is a 32-bit register that specifies the transfer source address of data to be transferred by the DTC. An even address should be specified in the case of word size transfer, and an address that is a multiple of 4 in the case of longword transfer.

- The DTC destination address register (DTDAR) is a 32-bit register that specifies the transfer destination address of data to be transferred by the DTC. An even address should be specified in the case of word size transfer, and an address that is a multiple of 4 in the case of longword transfer.

- The DTC initial address register (DTIAR) is a 32-bit register that specifies the transfer source/transfer destination initial address in repeat mode. In repeat mode, when the DTS bit is 1, specify the initial transfer source address in the repeat area, and when the DTS bit is 0, specify the initial transfer destination address in the repeat area.

- DTC transfer count register A (DTCRA) is a 16-bit register that specifies the number of transfers in DTC data transfer. In normal mode, DTCRA functions as a transfer counter (1 to 65,536). In repeat mode, upper 8-bit DTCRAH holds the number of transfers, and lower 8-bit DTCRAL functions as an 8-bit transfer counter. In block transfer mode, DTCRA functions as a 16-bit transfer counter.

- DTC transfer count register B (DTCRB) is a 16-bit register that specifies the block length in block transfer mode.

- The DTC enable register (DTER) is used to select the interrupt source that activates the DTC, and comprises registers DTEA through DTEF.

- The DTC control/status register (DTCSR) is a 16-bit register that sets enabling/disabling of DTC activation by software, and sets a software activation DTC vector address. DTCSR also shows the DTC transfer status.

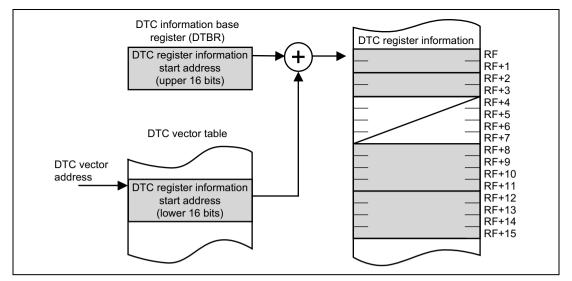

- The DTC information base register (DTBR) is a readable/writable 16-bit register that specifies the upper 16 bits of the memory address that stores DTC transfer information. Word or longword access must be used for DTBR. If byte access is used, the register contents will be undefined in the case of a write, and an undefined value will be returned in the case of a read.

- Information of six registers the DTC mode register (DTMR), DTC source address register (DTSAR), DTC destination address register (DTDAR), DTC initial address register (DTIAR), DTC transfer count register A (DTCRA), and DTC transfer count register B (DTCRB) cannot be accessed directly from the CPU. When a DTC activation

Rev. 1.00, 11/03, page 5 of 196

#### Renesas

source occurs, the relevant register information is transferred to these registers from information of an arbitrary set of registers located in on-chip RAM and DTC transfer is performed, and when transfer ends, the contents of these registers are returned to RAM. Therefore, register information should be prepared in arbitrary on-chip RAM in the user program.

Notes:

- (a) Performs enabling/disabling of DTC activation by software, and software activation DTC vector address setting.

- (b) Performs specification of the upper 16 bits of the memory address that stores DTC transfer information.

- (c) Selects the interrupt source that activates the DTC; comprises six registers, DTEA through DTEF.

- (d) Performs DTC operating mode setting.

- (e) Specifies the number of transfers in DTC data transfer.

- (f) In repeat mode, specifies the transfer source/transfer destination initial address in repeat mode. Not used in normal mode. In block transfer mode, functions as the DTCRB register.

- (g) In block transfer mode, specifies the block length. Not used in normal mode. In repeat mode, functions as the DTIAR register.

- (h) Specifies the transfer source address of data to be transferred by the DTC.

- (i) Specifies the transfer destination address of data to be transferred by the DTC.

#### Figure 2.3 DTC Block Diagram

#### Renesas

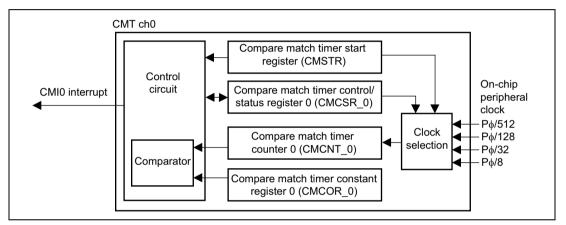

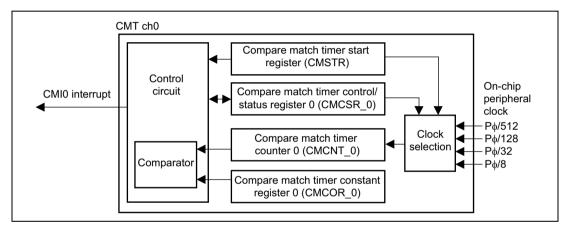

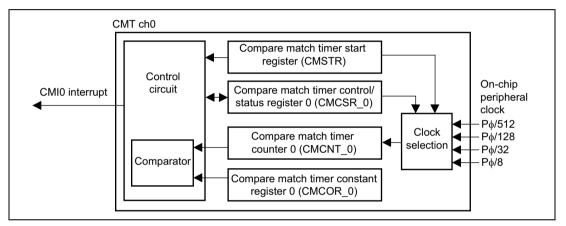

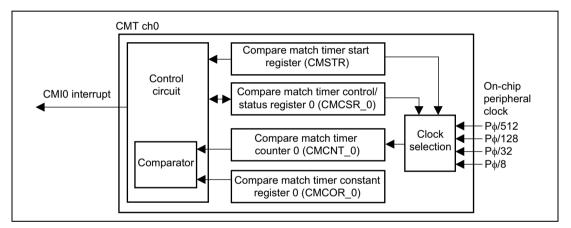

- (2) A block diagram of CMT ch0 is shown is the figure below. In this task, DTC data transfer is performed using a CMT ch0 compare match interrupt as the activation source. The block diagram is explained below.

- The compare match timer start register (CMSTR) is a 16-bit register that is used to set whether the channel 0 and 1 counters (CMCNT) are operated or stopped.

- Compare match timer control/status register 0 (CMCSR\_0) is a 16-bit register that performs compare match generation indication, interrupt enabling/disabling, and selection of the clock used for counting up.

- Compare match timer counter 0 (CMCNT\_0) is a 16-bit register used as an up-counter for generating an interrupt request.

- Compare match timer constant register 0 (CMCOR\_0) is a 16-bit register used to set the CMCNT compare match period.

Figure 2.4 CMT Block Diagram

(3) Table 2.2 shows the function assignments used in this sample task.

| Function | Туре    | Function Assignment                             |

|----------|---------|-------------------------------------------------|

| DTMR     | DTC     | Sets DTC to normal mode                         |

| DTCRA    | DTC     | Setting of number of transfers                  |

| DTSAR    | DTC     | Transfer source address setting                 |

| DTDAR    | DTC     | Transfer destination address setting            |

| DTBR     | DTC     | Setting of DTC vector upper 16 bits             |

| DTER     | DTC     | Enables DTC activation by CMT ch0 CMI interrupt |

| CMSTR    | CMT     | CMT count start                                 |

| CMCSR_0  | CMT ch0 | Count clock selection, interrupt control        |

| CMCNT_0  | CMT ch0 | Counter                                         |

| CMCOR_0  | CMT ch0 | Period setting                                  |

#### Table 2.2Function Assignments

#### Operation

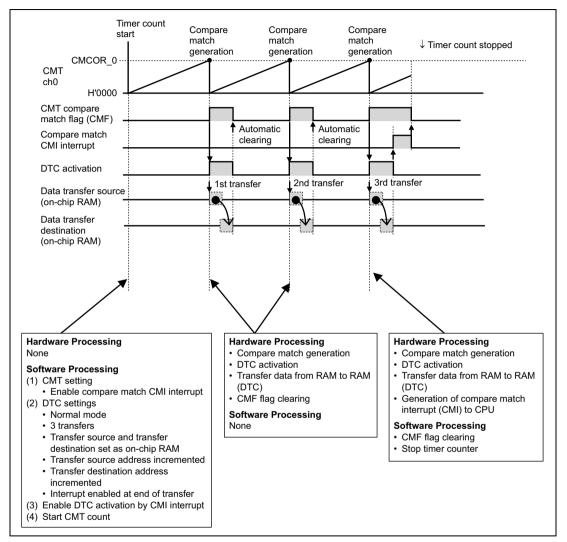

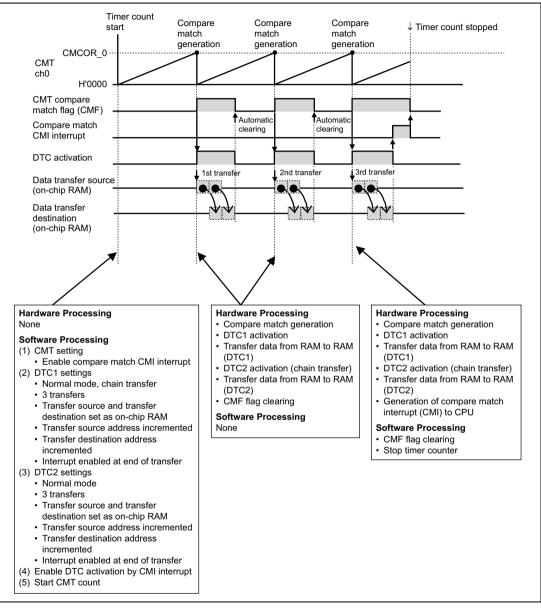

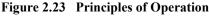

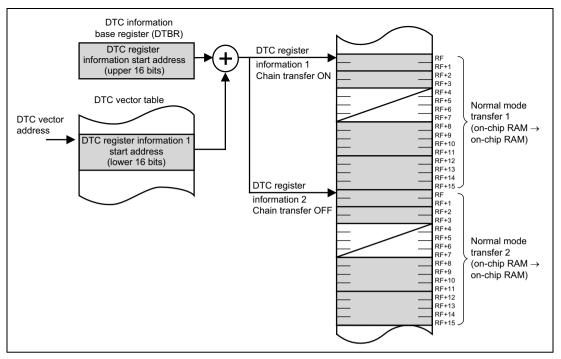

(1) The principles of operation of this sample task are shown in the figure below.

Data transfer from on-chip RAM to on-chip RAM is performed by the DTC by means of hardware and software processing as shown in the figure.

Figure 2.5 Principles of Operation

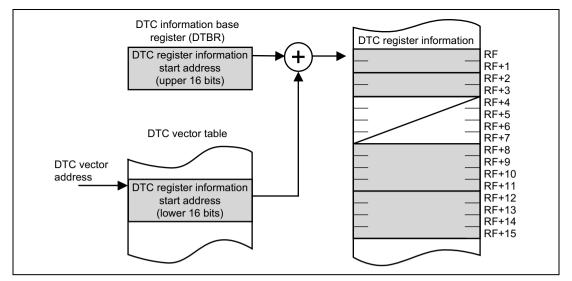

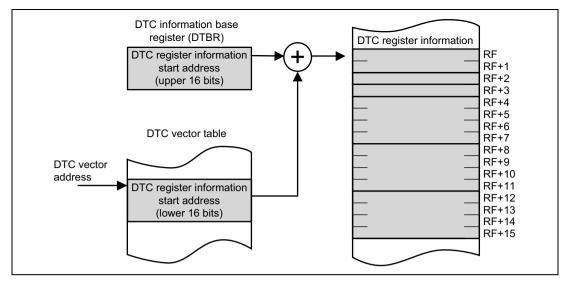

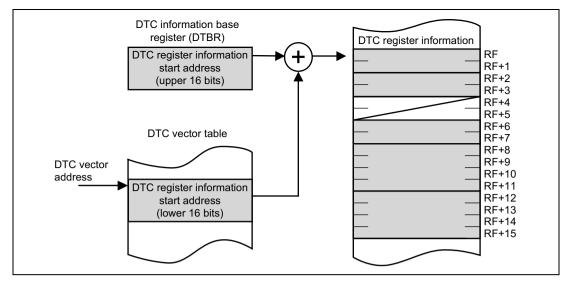

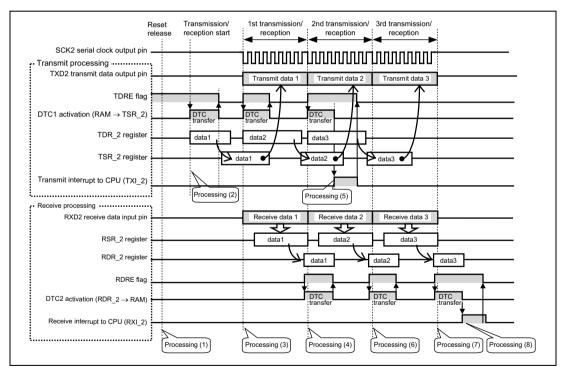

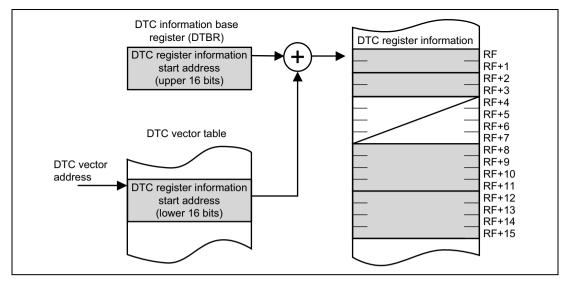

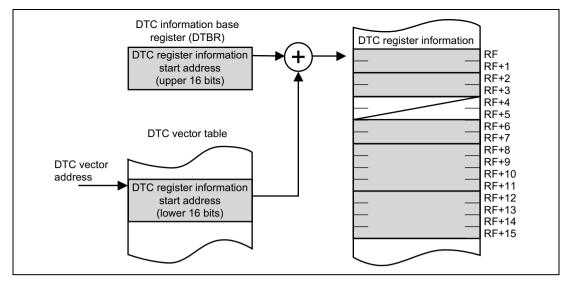

- (2) The principles of operation of DTC activation are shown in the figure below. When executing DTC transfer, the following settings should be made before an activation source occurs.

- Make DTC register information settings and place DTC register information in RAM.

- Set the lower 16 bits of the start address (32 bits) of DTC register information in the DTC vector table.

- Set the lower 16 bits of the start address (32 bits) of DTC register information in the DTC information base register.

The DTC is activated by the following processing.

- A DTC activation source interrupt is generated.

- The lower 16 bits of the start address of DTC register information are read from the address corresponding to the DTC vector table activation source.

- The upper 16 bits of the start address of DTC register information are read from the DTC information base register (DTMR).

- The 32-bit start address of DTC register information is generated from the read start address lower 16 bits and upper 16 bits.

- The start of DTC register information is read sequentially from the DTC register information start address, and data transfer is performed.

In this task, a CMT compare match interrupt is used as the DTC activation source.

The following table shows the register information configuration in normal transfer mode.

| Table 2.3 | DTC Register | Information | (Normal Mode) |

|-----------|--------------|-------------|---------------|

|-----------|--------------|-------------|---------------|

| Setting Address | Register Name                            | Data Length        |

|-----------------|------------------------------------------|--------------------|

| RF              | DTC mode register (DTMR)                 | Word (2 bytes)     |

| RF+2            | DTC transfer count register A (DTCRA)    | Word (2 bytes)     |

| RF+8            | DTC source address register (DTSAR)      | Longword (4 bytes) |

| RF+12           | DTC destination address register (DTDAR) | Longword (4 bytes) |

RF: DTC register information start address (in on-chip RAM)

Figure 2.6 Correspondence between DTC Vector Address and Transfer Information

#### Software

#### (1) Modules

The following table shows the modules used by this sample task.

#### Table 2.4 Modules

| Module Name                  | Label | Function                                                                                                 |

|------------------------------|-------|----------------------------------------------------------------------------------------------------------|

| Main routine                 | main  | CMT timer setting, DTC initialization, timer start                                                       |

| CMI0 interrupt cmt0_cmi0_dtc |       | CMT ch0 compare match interrupt (CMI0). Interrupt generation at end of specified number of DTC transfers |

#### (2) Arguments

The following table shows the arguments used by this sample task.

#### Table 2.5 Arguments

| Argument          | Function                                       | Module<br>Name  | Data<br>Length | Input/<br>Output |

|-------------------|------------------------------------------------|-----------------|----------------|------------------|

| S_data [0] to [2] | DTC transfer source transfer data storage      | Main<br>routine | 1 byte         | Output           |

| D_data [0] to [2] | DTC transfer destination transfer data storage | Main<br>routine | 1 byte         | Input            |

#### (3) Internal Registers Used

The following table shows the internal registers used by this sample task.

Table 2.6Internal Registers Used

| Register Name |        | Function                                                            | Address     | Set Value |

|---------------|--------|---------------------------------------------------------------------|-------------|-----------|

|               | Bits   | Function                                                            | Bi          | ts        |

| P_STBY.MSTCR1 | MSTP25 | Module standby control register 1                                   | H'FFFF861C  | B'00      |

|               | MSTP24 | DTC module standby control bits:                                    | Bit 9       |           |

|               |        | When MSTP25 = MSTP24 = 0, module standby release                    | Bit 8       |           |

|               |        | Same value is set for MSTP25 and MSTP24                             |             |           |

| P_STBY.MSTCR2 | MSTP12 | Module standby control register 2                                   | H'FFFF861E  | 0         |

|               |        | CMT module standby control bit:                                     | Bit 12      |           |

|               |        | When MSTP12 = 0, module standby release                             |             |           |

| P_INTC.IPRG   | CMT0   | Interrupt priority register G (IPRG)                                | H'FFFF8354  | 10        |

|               |        | CMT0 CMI0 interrupt priority level setting:                         | Bits 7 to 4 |           |

|               |        | When CMT0 = b'1010 (10), CMI0 interrupt is set to priority level 10 |             |           |

| P_CMT.CMSTR   |        | Compare match timer start register (CMTSR)                          | H'FFFF83D0  | H'0001    |

|               |        | 16-bit register that selects CMCNT operation/stoppage               |             |           |

|               | STR1   | Counter start 1:                                                    | Bit 1       |           |

|               |        | When STR1 = b'0, TCNT_1 count operation is stopped                  |             |           |

|               | STR0   | Counter start 0:                                                    | Bit 0       |           |

|               |        | When STR0 = b'1, TCNT_0 counts                                      |             |           |

| Register Name |      | Function                                                                       | Address    | Set Value |

|---------------|------|--------------------------------------------------------------------------------|------------|-----------|

|               | Bits | Function                                                                       | Bits       |           |

| P_CMT.CMCSR_0 |      | Compare match timer control/status register<br>0 (CMCSR_0)                     | H'FFFF83D2 | H'0043    |

|               |      | Compare match generation indication,<br>interrupt setting, timer clock setting |            |           |

|               | CMF  | Compare match flag:                                                            | Bit 7      |           |

|               |      | CMF is set to 1 when CMCNT and CMCOR values match                              |            |           |

|               | CMIE | Compare match interrupt enable:                                                | Bit 6      |           |

|               |      | When CMIE = 1, compare match interrupt<br>(CMI) is enabled                     |            |           |

|               | CKS1 | CMCNT counter clock selection:                                                 | Bit 1      |           |

|               | CKS0 | When CKS[1:0] = b'11, count is performed using internal clock Pø/512           | Bit 0      |           |

| P_CMT.CMCNT_0 |      | Compare match timer counter 0<br>(CMCNT_0)                                     | H'FFFF83D4 | H'0000    |

|               |      | 16-bit register used as up-counter for generating interrupt requests           |            |           |

| P_CMT.CMCOR_0 |      | Compare match timer constant register 0<br>(CMCOR_0)                           | H'FFFF83D6 | H'1e84    |

|               |      | 16-bit register used to set CMCNT compare match period                         |            |           |

|               |      | When CMCOR_0 = H'1e84, 100 ms<br>compare match period is used                  |            |           |

|               |      | (Ρφ/512 count, Ρφ = 40 MHz)                                                    |            |           |

| Register Name                                                                                      |       | Function                                                                                             | Address               | Set Value   |

|----------------------------------------------------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------|-----------------------|-------------|

|                                                                                                    | Bits  | Function                                                                                             | Bi                    | ts          |

| DTC_N.DTMR                                                                                         |       | DTC mode register (DTMR)                                                                             | Located in on-        | H'a000      |

|                                                                                                    |       | DTC operating mode control setting                                                                   | chip RAM              |             |

|                                                                                                    | SM1   | Source address mode:                                                                                 | Bit 15                |             |

|                                                                                                    | SM0   | When SM[1:0] = b'10, DTSAR is<br>incremented after transfer                                          | Bit 14                |             |

|                                                                                                    | DM1   | Destination address mode:                                                                            | Bit 13                |             |

|                                                                                                    | DM0   | When DM[1:0] = b'10, DTDAR is<br>incremented after transfer                                          | Bit 12                |             |

|                                                                                                    | MD1   | DTC transfer mode:                                                                                   | Bit 11                |             |

|                                                                                                    | MD0   | When MD[1:0] = b'00, normal mode                                                                     | Bit 10                |             |

|                                                                                                    | SZ1   | DTC data transfer size:                                                                              | Bit 9                 |             |

|                                                                                                    | SZ0   | When SZ[1:0] = b'00, byte (1-byte) transfer                                                          | Bit 8                 |             |

|                                                                                                    | DTS   | DTC transfer mode select:                                                                            | Bit 7                 |             |

|                                                                                                    |       | When DTS = b'0, destination side is block area                                                       |                       |             |

|                                                                                                    | CHNE  | DTC chain transfer enable:                                                                           | Bit 6                 |             |

|                                                                                                    |       | When CHNE = b'0, chain transfer is cleared                                                           |                       |             |

|                                                                                                    | DISEL | DTC interrupt select:                                                                                | Bit 5                 |             |

|                                                                                                    |       | When DISEL = b'0, interrupt request to<br>CPU is generated only at end of specified<br>data transfer |                       |             |

|                                                                                                    | NMIM  | DTC NMI mode:                                                                                        | Bit 4                 |             |

|                                                                                                    |       | When NMIM = b'0, DTC transfer is<br>suspended by NMI                                                 |                       |             |

| DTC_N.DTCRA                                                                                        |       | DTC transfer count register A (DTCRA)                                                                | Located in on-        | H'0003      |

|                                                                                                    |       | Specifies number of transfers in DTC data transfer                                                   | chip RAM              |             |

|                                                                                                    |       | Set to 3 transfers                                                                                   |                       |             |

| DTC_N.DTSAR                                                                                        |       | DTC source address register (DTSAR)                                                                  | Located in on- &S_dat | &S_data[0]; |

|                                                                                                    |       | 32-bit register that specifies transfer source address of data to be transferred by DTC              | chip RAM              |             |

| DTC_N.DTDAR                                                                                        |       | DTC destination address register (DTDAR)                                                             | Located in on-        | &D_data[0]; |

| 32-bit register that specifies transfer<br>destination address of data to be<br>transferred by DTC |       |                                                                                                      | chip RAM              |             |

| Register Name |      | Function                                                                                  | Address    | Set Value |

|---------------|------|-------------------------------------------------------------------------------------------|------------|-----------|

|               | Bits | Function                                                                                  | Bi         | ts        |

| P_DTC.DTBR    |      | DTC information base register (DTBR)                                                      | H'FFFF8708 | 0xFFFF    |

|               |      | Specifies upper 16 bits of memory address that stores DTC transfer information            |            |           |

| P_DTC.DTED    | CMI0 | DTC enable register D (DTED)                                                              | H'FFFF8703 | 1         |

|               |      | When set to 1, corresponding interrupt<br>source is selected as DTC activation<br>source: | Bit 5      |           |

|               |      | When CMI0 (DTED5) = b'1, CMT0 CMI0<br>interrupt is activation source                      |            |           |

#### (4) RAM Used

The following table shows the RAM used by this sample task.

#### Table 2.7 RAM Used

| Label  | Function                             | Address     | Module Using RAM |

|--------|--------------------------------------|-------------|------------------|

| S_data | DTC transfer data storage            | On-chip RAM | Main routine     |

|        | Array storing 3-byte data            |             |                  |

| D_data | Data storage after DTC data transfer | On-chip RAM | Main routine     |

|        | Array storing 3-byte data            |             |                  |

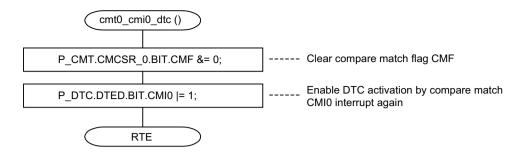

#### Flowcharts

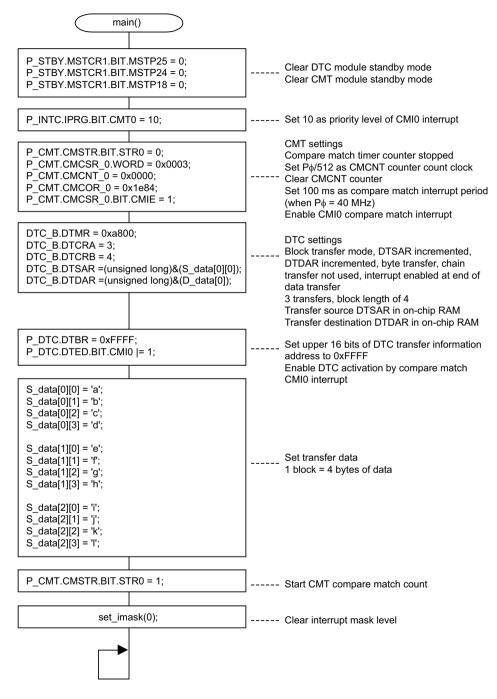

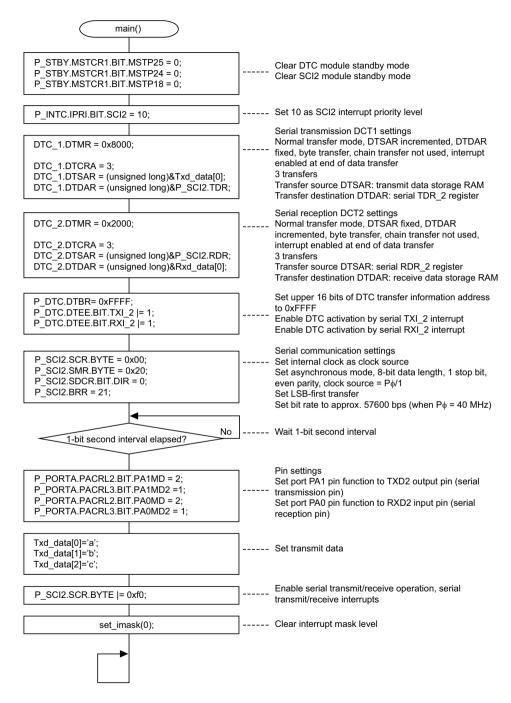

#### (a) Main processing

Renesas

Rev. 1.00, 11/03, page 17 of 196

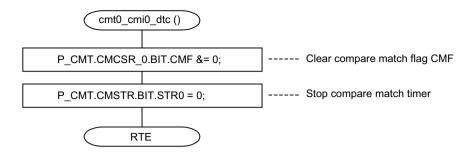

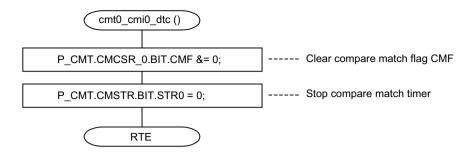

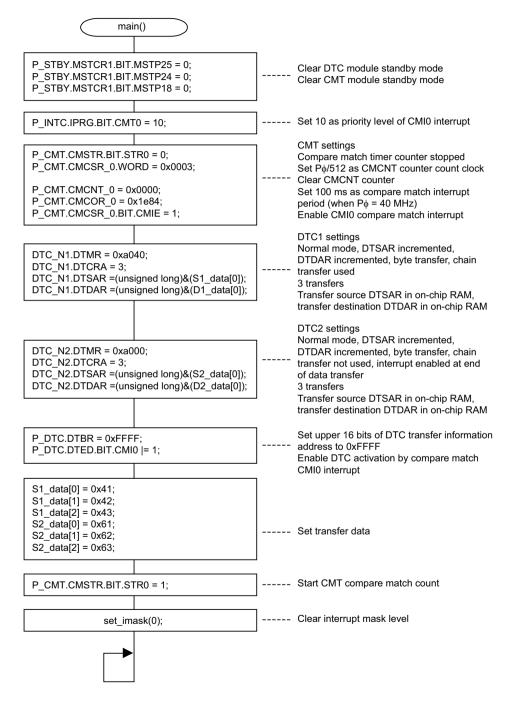

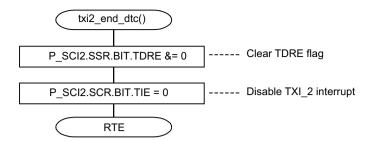

#### (b) Compare match interrupt handling

#### **Program Listing**

```

/* SH7046F Series -SH7047- Application Note

* /

/* Data transfer Controller(DTC)

* /

/* Normal mode

* /

/* Function

* /

/* :Data transfer Controller(DTC)

* /

/* :Compare Match Timer(CMT ch0)

* /

/*

*/

/* External input clock

:10MHz

*/

/* Internal CPU clock

:40MHz

* /

/* Internal peripheral clock :40MHz

*/

/*

*/

/* Written : 2002/3/1 Rev.1.0

* /

#include "iodefine 7047v13.1.h"

#include <machine.h>

/*----- Symbol Definition -----*/

* /

unsigned short DTMR; /* DTC Mode

unsigned short DTCRA; /* Transfer

unsigned short dummy1; /* Reserved

/* DTC Mode Register

*/

/* Transfer counter

*/

* /

unsigned short dummy2;

/* Reserved

*/

unsigned long DTSAR; /* source address register

unsigned long DTDAR; /* destination address register

* /

*/

};

#define DTC COUNT 3

/* DTC Transmit count

*/

#define DTC N (*(volatile struct st dtc normal*)0xFFFFE000)

/* DTC information address

* /

/*----- Function Definition -----*/

void main(void);

void cmt0 cmi0 dtc(void);

/*----- RAM allocation Definition -----*/

unsigned char S_data[DTC_COUNT]; /* source buffer memory

*/

unsigned char D_data[DTC_COUNT]; /* destination buffer memory

*/

* /

/* main Program

void main( void )

{

```

```

/* Set standby mode */

P STBY.MSTCR1.BIT.MSTP25 = 0;

/* Disable DTC standby mode

*/

/* Disable DTC standby mode

P STBY.MSTCR1.BIT.MSTP24 = 0;

*/

P_STBY.MSTCR2.BIT.MSTP12 = 0;

/* Disable CMT standby mode

*/

/* Set interrupt priority level (0 to 15) */

P_INTC.IPRG.BIT.CMT0 = 10;

/* CMT0 CMI0 interrupt level 10

*/

/* Initialize CMT0 for Interval timer */

P_CMT.CMSTR.BIT.STR0 = 0; /* timer count stop

*/

P_CMT.CMCSR_0.WORD = 0x0003;

*/

/* CMF=0;

clear compare match flag

/* CMIE=0;

compare match interrupt disable

* /

/* CKS[1:0]=b'11;

clock = peripheral clock(P\phi)/512

* /

/* timer counter clear

*/

P_CMT.CMCNT_0 = 0x0000;

P_CMT.CMCOR_0 = 0x1e84;

/* 100ms@P0=40MHz

*/

P_CMT.CMCSR_0.BIT.CMIE = 1; /* compare match interrupt enable

*/

/* DTC information */

DTC N.DTMR = 0 \times a000;

/*

*/

/* SM[1:0]=b'10; DTSAR is incremented

*/

/* DM[1:0]=b'10; DTDAR is incremented

*/

/* MD[1:0]=b'00; Normal transfer mode

*/

/* SZ[1:0]=b'00; byte-size transfer

*/

/* DTS=0;

destination is block area (not used)

*/

/* CHNE=0;

Chain transfer is disable

*/

*/

```

```

/* DISEL=0;

Interrupt->transfer ends

/* NMIM=0;

NMI->Terminate DTC transfer

*/

DTC N.DTCRA = DTC COUNT;

/* DTC transfer Count

*/

DTC_N.DTSAR =(unsigned long)&(S_data[0]); /* set source address

*/

DTC_N.DTDAR =(unsigned long)&(D_data[0]); /* set destination address

*/

*/

P_DTC.DTBR = 0xFFFF;

/* DTC information base register

/* DTC transmit enable */

P_DTC.DTED.BIT.CMI0 |= 1; /* interrupt sources CMT ch0(CMI0)

*/

/* set transmit data

*/

```

```

Rev. 1.00, 11/03, page 20 of 196

```

}

RENESAS

RENESAS

Rev. 1.00, 11/03, page 21 of 196

#### 2.2 Data Transfer Using DTC Repeat Mode (CMT, DTC)

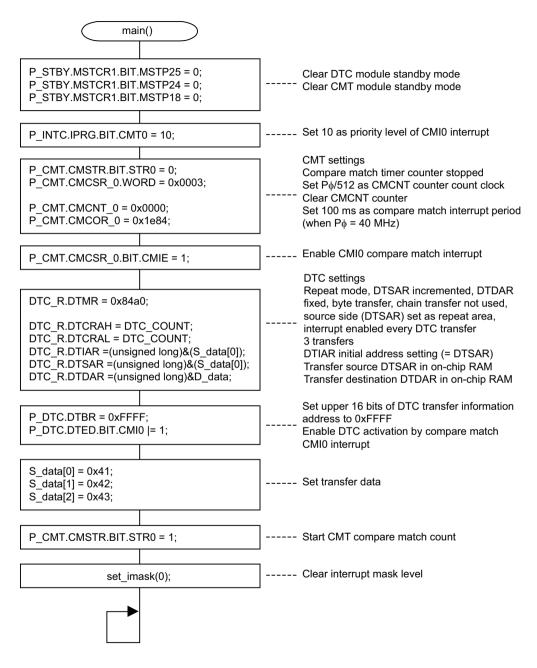

#### Specifications

- (1) The data transfer controller (DTC) is activated by a compare match timer (CMT) compare match interrupt, and performs data transfer from on-chip RAM to on-chip RAM, as shown in figure 2.7.

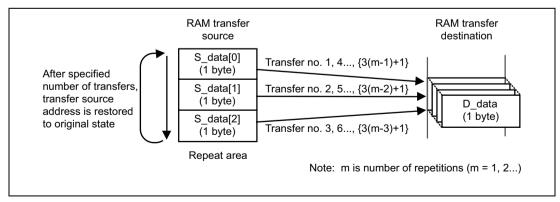

- (2) Repeat mode is used for DTC data transfer, with transfer source 3-byte data repeatedly transferred to a fixed area in on-chip RAM as shown in figure 2.8.

- (3) The DTC transfer conditions are shown in table 2.8.

Figure 2.7 Data Transfer Using DTC

Figure 2.8 Data Transfer Using DTC Repeat Mode

#### RENESAS

| Description                                               |  |

|-----------------------------------------------------------|--|

| Repeat mode, source side (transfer source) is repeat area |  |

| 3                                                         |  |

| Byte transfer                                             |  |

| On-chip RAM (repeat area)                                 |  |

| On-chip RAM                                               |  |

| Transfer source address incremented after transfer        |  |

| Transfer destination address fixed                        |  |

| Activated by CMT ch0 compare match interrupt (CMI0)       |  |

| Interrupt to CPU enabled every DTC transfer               |  |

|                                                           |  |

#### Table 2.8 DTC Transfer Conditions

#### **Functions Used**

- (1) A block diagram of the DTC is shown below. Of the three DTC transfer modes normal mode, repeat mode, and block transfer mode —this sample task uses normal mode to perform data transfer. Data transfer is performed from on-chip RAM to on-chip RAM, using a CMT compare match interrupt as the DTC activation source. The block diagram is explained below.

- The DTC mode register (DTMR) is a 16-bit register that controls the DTC's operating mode.

- The DTC source address register (DTSAR) is a 32-bit register that specifies the transfer source address of data to be transferred by the DTC. An even address should be specified in the case of word size transfer, and an address that is a multiple of 4 in the case of longword transfer.

- The DTC destination address register (DTDAR) is a 32-bit register that specifies the transfer destination address of data to be transferred by the DTC. An even address should be specified in the case of word size transfer, and an address that is a multiple of 4 in the case of longword transfer.

- The DTC initial address register (DTIAR) is a 32-bit register that specifies the transfer source/transfer destination initial address in repeat mode. In repeat mode, when the DTS bit is 1, specify the initial transfer source address in the repeat area, and when the DTS bit is 0, specify the initial transfer destination address in the repeat area.

- DTC transfer count register A (DTCRA) is a 16-bit register that specifies the number of transfers in DTC data transfer. In normal mode, DTCRA functions as a transfer counter (1 to 65,536). In repeat mode, upper 8-bit DTCRAH holds the number of transfers, and lower 8-bit DTCRAL functions as an 8-bit transfer counter. In block transfer mode, DTCRA functions as a 16-bit transfer counter.

- DTC transfer count register B (DTCRB) is a 16-bit register that specifies the block length in block transfer mode.

- The DTC enable register (DTER) is used to select the interrupt source that activates the DTC, and comprises registers DTEA through DTEF.

- The DTC control/status register (DTCSR) is a 16-bit register that sets enabling/disabling of DTC activation by software, and sets a software activation DTC vector address. DTCSR also shows the DTC transfer status.

- The DTC information base register (DTBR) is a readable/writable 16-bit register that specifies the upper 16 bits of the memory address that stores DTC transfer information. Word or longword access must be used for DTBR. If byte access is used, the register contents will be undefined in the case of a write, and an undefined value will be returned in the case of a read.

- Information of six registers the DTC mode register (DTMR), DTC source address

register (DTSAR), DTC destination address register (DTDAR), DTC initial address

register (DTIAR), DTC transfer count register A (DTCRA), and DTC transfer count

register B (DTCRB) cannot be accessed directly from the CPU. When a DTC activation

Rev. 1.00, 11/03, page 24 of 196

#### RENESAS

source occurs, the relevant register information is transferred to these registers from information of an arbitrary set of registers located in on-chip RAM and DTC transfer is performed, and when transfer ends, the contents of these registers are returned to RAM. Therefore, register information should be prepared in arbitrary on-chip RAM in the user program.

Notes:

- (a) Performs enabling/disabling of DTC activation by software, and software activation DTC vector address setting.

- (b) Performs specification of the upper 16 bits of the memory address that stores DTC transfer information.

- (c) Selects the interrupt source that activates the DTC; comprises six registers, DTEA through DTEF.

- (d) Performs DTC operating mode setting.

- (e) Specifies the number of transfers in DTC data transfer.

- (f) In repeat mode, specifies the transfer source/transfer destination initial address in repeat mode. Not used in normal mode. In block transfer mode, functions as the DTCRB register.

- (g) In block transfer mode, specifies the block length. Not used in normal mode. In repeat mode, functions as the DTIAR register.

- (h) Specifies the transfer source address of data to be transferred by the DTC.

- (i) Specifies the transfer destination address of data to be transferred by the DTC.

#### Figure 2.9 DTC Block Diagram

RENESAS

- (2) A block diagram of CMT ch0 is shown is the figure below. In this task, DTC data transfer is performed using a CMT ch0 compare match interrupt as the activation source. The block diagram is explained below.

- The compare match timer start register (CMSTR) is a 16-bit register that is used to set whether the channel 0 and 1 counters (CMCNT) are operated or stopped.

- Compare match timer control/status register 0 (CMCSR\_0) is a 16-bit register that performs compare match generation indication, interrupt enabling/disabling, and selection of the clock used for counting up.

- Compare match timer counter 0 (CMCNT\_0) is a 16-bit register used as an up-counter for generating an interrupt request.

- Compare match timer constant register 0 (CMCOR\_0) is a 16-bit register used to set the CMCNT compare match period.

Figure 2.10 CMT Block Diagram

(4) Table 2.9 shows the function assignments used in this sample task.

| Function | Туре    | Function Assignment                                                        |

|----------|---------|----------------------------------------------------------------------------|

| DTMR     | DTC     | Sets DTC to repeat mode, with source side (transfer source) as repeat area |

| DTCRA    | DTC     | Setting of number of transfers                                             |

| DTIAR    | DTC     | Sets transfer source (repeat area) initial address                         |

| DTSAR    | DTC     | Transfer source address setting                                            |

| DTDAR    | DTC     | Transfer destination address setting                                       |

| DTBR     | DTC     | Setting of DTC vector upper 16 bits                                        |

| DTER     | DTC     | Enables DTC activation by CMT ch0 CMI interrupt                            |

| CMSTR    | CMT     | CMT count start                                                            |

| CMCSR_0  | CMT ch0 | Count clock selection, interrupt control                                   |

| CMCNT_0  | CMT ch0 | Counter                                                                    |

| CMCOR_0  | CMT ch0 | Period setting                                                             |

## Table 2.9Function Assignments

## Operation

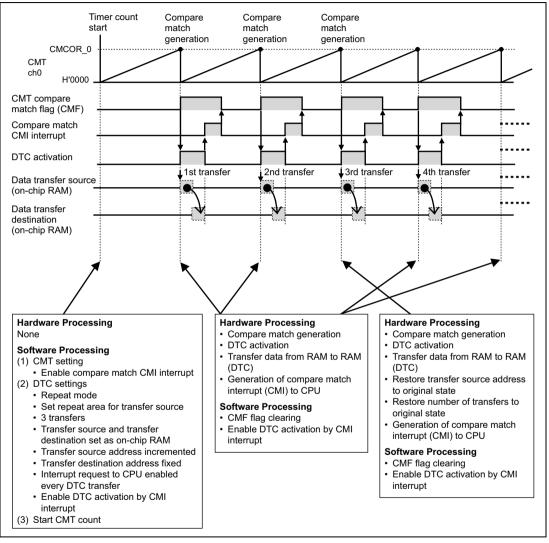

(1) The principles of operation of this sample task are shown in the figure below.

Data transfer from on-chip RAM to on-chip RAM is performed by the DTC by means of hardware and software processing as shown in the figure.

This sample task uses repeat mode.

Figure 2.11 Principles of Operation

- (2) The principles of operation of DTC activation are shown in the figure below. When executing DTC transfer, the following settings should be made before an activation source occurs.

- Make DTC register information settings and place DTC register information in RAM.

- Set the lower 16 bits of the start address (32 bits) of DTC register information in the DTC vector table.

- Set the lower 16 bits of the start address (32 bits) of DTC register information in the DTC information base register.

The DTC is activated by the following processing.

- A DTC activation source interrupt is generated.

- The lower 16 bits of the start address of DTC register information are read from the address corresponding to the DTC vector table activation source.

- The upper 16 bits of the start address of DTC register information are read from the DTC information base register (DTMR).

- The 32-bit start address of DTC register information is generated from the read start address lower 16 bits and upper 16 bits.

- The start of DTC register information is read sequentially from the DTC register information start address, and data transfer is performed.

In this task, a CMT compare match interrupt is used as the DTC activation source.

The following table shows the register information configuration in repeat transfer mode.

| <b>Table 2.10</b> | DTC Register | Information | (Repeat Mode) |

|-------------------|--------------|-------------|---------------|

|-------------------|--------------|-------------|---------------|

| Setting Address | Register Name                            | Data Length        |

|-----------------|------------------------------------------|--------------------|

| RF              | DTC mode register (DTMR)                 | Word (2 bytes)     |

| RF+2            | DTC transfer count register AH (DTCRAH)  | Byte (1 byte)      |

| RF+3            | DTC transfer count register AL (DTCRAL)  | Byte (1 byte)      |

| RF+4            | DTC initial address register (DTIAR)     | Longword (4 bytes) |

| RF+8            | DTC source address register (DTSAR)      | Longword (4 bytes) |

| RF+12           | DTC destination address register (DTDAR) | Longword (4 bytes) |

RF: DTC register information start address (in on-chip RAM)

Figure 2.12 Correspondence between DTC Vector Address and Transfer Information

## Software

## (1) Modules

The following table shows the modules used by this sample task.

## Table 2.11 Modules

| Module Name    | Label         | Function                                                                       |

|----------------|---------------|--------------------------------------------------------------------------------|

| Main routine   | main          | CMT timer setting, DTC initialization, timer start                             |

| CMI0 interrupt | cmt0_cmi0_dtc | CMT ch0 compare match interrupt (CMI0). Interrupt generated every DTC transfer |

## (2) Arguments

The following table shows the arguments used by this sample task.

### Table 2.12 Arguments

| Argument          | Function                                       | Module<br>Name  | Data<br>Length | Input/<br>Output |

|-------------------|------------------------------------------------|-----------------|----------------|------------------|

| S_data [0] to [2] | DTC transfer source transfer data storage      | Main<br>routine | 1 byte         | Output           |

| D_data            | DTC transfer destination transfer data storage | Main<br>routine | 1 byte         | Input            |

## (3) Internal Registers Used

The following table shows the internal registers used by this sample task.

Table 2.6Internal Registers Used

| Register Name    |                                                       | Function                                                            | Address     | Set Value |

|------------------|-------------------------------------------------------|---------------------------------------------------------------------|-------------|-----------|

|                  | Bits                                                  | Function                                                            | Bits        |           |

| P_STBY.MSTCR1    | MSTP25                                                | Module standby control register 1                                   | H'FFFF861C  | B'00      |

|                  | MSTP24                                                | DTC module standby control bits:                                    | Bit 9       |           |

|                  |                                                       | When MSTP25 = MSTP24 = 0, module<br>standby release                 | Bit 8       |           |

|                  |                                                       | Same value is set for MSTP25 and MSTP24                             |             |           |

| P_STBY.MSTCR2    | MSTP12                                                | Module standby control register 2                                   | H'FFFF861E  | 0         |

|                  |                                                       | CMT module standby control bit:                                     | Bit 12      |           |

|                  |                                                       | When MSTP12 = 0, module standby release                             |             |           |

| P_INTC.IPRG CMT0 |                                                       | Interrupt priority register G (IPRG)                                | H'FFFF8354  | 10        |

|                  |                                                       | CMT0 CMI0 interrupt priority level setting:                         | Bits 7 to 4 |           |

|                  |                                                       | When CMT0 = b'1010 (10), CMI0 interrupt is set to priority level 10 |             |           |

| P_CMT.CMSTR      |                                                       | Compare match timer start register (CMTSR)                          | H'FFFF83D0  | H'0001    |

|                  |                                                       | 16-bit register that selects CMCNT operation/stoppage               |             |           |

| STR1 C           |                                                       | Counter start 1:                                                    | Bit 1       |           |

|                  | When STR1 = b'0, TCNT_1 count operation<br>is stopped |                                                                     |             |           |

|                  | STR0                                                  | Counter start 0:                                                    | Bit 0       |           |

|                  |                                                       | When STR0 = b'1, TCNT_0 counts                                      |             |           |

| Register Name |      | Function                                                                       | Address    | Set Value |

|---------------|------|--------------------------------------------------------------------------------|------------|-----------|

|               | Bits | Function                                                                       | Bits       |           |

| P_CMT.CMCSR_0 |      | Compare match timer control/status register<br>0 (CMCSR_0)                     | H'FFFF83D2 | H'0043    |

|               |      | Compare match generation indication,<br>interrupt setting, timer clock setting |            |           |

|               | CMF  | Compare match flag:                                                            | Bit 7      | 1         |

|               |      | CMF is set to 1 when CMCNT and CMCOR values match                              |            |           |

|               | CMIE | Compare match interrupt enable:                                                | Bit 6      |           |

|               |      | When CMIE = 1, compare match interrupt<br>(CMI) is enabled                     |            |           |

|               | CKS1 | CMCNT counter clock selection:                                                 | Bit 1      |           |

|               | CKS0 | When CKS[1:0] = b'11, count is performed using internal clock P¢/512           | Bit 0      |           |

| P_CMT.CMCNT_0 | •    | Compare match timer counter 0 (CMCNT_0)                                        | H'FFFF83D4 | H'0000    |

|               |      | 16-bit register used as up-counter for<br>generating interrupt requests        |            |           |

| P_CMT.CMCOR_0 |      | Compare match timer constant register 0<br>(CMCOR_0)                           | H'FFFF83D6 | H'1e84    |

|               |      | 16-bit register used to set CMCNT compare<br>match period                      |            |           |

|               |      | When CMCOR_0 = H'1e84, 100 ms compare match period is used                     |            |           |

|               |      | (Ρφ/512 count, Ρφ = 40 MHz)                                                    |            |           |

| Register Name<br>Bits |       | Function                                                                            | Address                         | Set Value  |

|-----------------------|-------|-------------------------------------------------------------------------------------|---------------------------------|------------|

|                       |       | - Function                                                                          | Bits                            |            |

| DTC_R.DTMR            | 1     | DTC mode register (DTMR)                                                            | Located in on-                  | H'84a0     |

|                       |       | DTC operating mode control setting                                                  | chip RAM                        |            |

|                       | SM1   | Source address mode:                                                                | Bit 15                          |            |

|                       | SM0   | When SM[1:0] = b'10, DTSAR is incremented after transfer                            | Bit 14                          |            |

|                       | DM1   | Destination address mode:                                                           | Bit 13                          |            |

|                       | DM0   | When DM[1:0] = b'00, DTDAR is fixed                                                 | Bit 12                          |            |

|                       | MD1   | DTC transfer mode:                                                                  | Bit 11                          |            |

|                       | MD0   | When MD[1:0] = b'01, repeat mode                                                    | Bit 10                          |            |

|                       | SZ1   | DTC data transfer size:                                                             | Bit 9                           |            |

|                       | SZ0   | When SZ[1:0] = b'00, byte (1-byte) transfer                                         | Bit 8                           |            |

|                       | DTS   | DTC transfer mode select:                                                           | Bit 7                           |            |

|                       |       | When DTS = b'1, source side (DTSAR) is<br>repeat area                               |                                 |            |

|                       | CHNE  | DTC chain transfer enable:                                                          | Bit 6                           |            |

|                       |       | When CHNE = b'0, chain transfer is cleared                                          |                                 |            |

|                       | DISEL | DTC interrupt select:                                                               | Bit 5                           |            |

|                       |       | When DISEL = b'1, interrupt request to CPU is generated every DTC transfer          |                                 |            |

|                       | NMIM  | DTC NMI mode:                                                                       | Bit 4                           |            |

|                       |       | When NMIM = b'0, DTC transfer is<br>suspended by NMI                                |                                 |            |

| DTC_R.DTCRAH          |       | DTC transfer count register AH (DTCRAH)                                             | Located in on-                  | H'03       |

|                       |       | Specifies held value of number of transfers in DTC data transfer                    | chip RAM                        |            |

|                       |       | Set to 3 transfers                                                                  |                                 |            |

| DTC_R.DTCRAL          |       | DTC transfer count register AL (DTCRAL)                                             | Located in on- H'03<br>chip RAM |            |

|                       |       | Specifies number of transfers in DTC data transfer                                  |                                 |            |

|                       |       | Set to 3 transfers                                                                  |                                 |            |

| DTC_R.DTIAR           |       | DTC initial address register (DTIAR)                                                | Located in on-                  | &S_data[0] |

|                       |       | 32-bit register that specifies initial address of DTC transfer data transfer source | chip RAM                        |            |

| Register Name |      | Function                                                                                                                                                                                       | Address                    | Set Value  |

|---------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------|

|               | Bits | Function                                                                                                                                                                                       | Bit                        | ts         |

| DTC_R.DTSAR   |      | DTC source address register (DTSAR)<br>32-bit register that specifies transfer source<br>address of DTC transfer data                                                                          | Located in on-<br>chip RAM | &S_data[0] |

| DTC_R.DTDAR   |      | DTC destination address register (DTDAR)<br>32-bit register that specifies transfer<br>destination address of DTC transfer data                                                                | Located in on-<br>chip RAM | &D_data    |

| P_DTC.DTBR    |      | DTC information base register (DTBR)<br>Specifies upper 16 bits of memory address<br>that stores DTC transfer information                                                                      | H'FFFF8708                 | 0xFFFF     |

| P_DTC.DTED    | СМІО | DTC enable register D (DTED)<br>When set to 1, corresponding interrupt<br>source is selected as DTC activation source:<br>When CMI0 (DTED5) = b'1, CMT0 CMI0<br>interrupt is activation source | H'FFFF8703<br>Bit 5        | 1          |

# (4) RAM Used

The following table shows the RAM used by this sample task.

## Table 2.14 RAM Used

| Label  | Function                             | Address     | Module Using RAM |

|--------|--------------------------------------|-------------|------------------|

| S_data | DTC transfer data storage            | On-chip RAM | Main routine     |

|        | Array storing 3-byte data            |             |                  |

| D_data | Data storage after DTC data transfer | On-chip RAM | Main routine     |

|        | Array storing 1-byte data            |             |                  |

#### Flowcharts

#### (a) Main processing

#### (b) Compare match interrupt handling

#### **Program Listing**

```

/* SH7046F Series -SH7047- Application Note

* /

/* Data transfer Controller(DTC)

*/

/* Repeat mode

* /

/* Function

* /

/* :Data transfer Controller(DTC)

* /

/*

:Compare Match Timer(CMT ch0)

*/

*/

/*

/* External input clock :10MHz

/* Internal CPU clock :40MHz

*/

*/

/* Internal CPU clock

:40MHz

/* Internal peripheral clock

:40MHz

*/

/*

* /

/* Written : 2002/3/1 Rev.1.0

* /

#include "iodefine.h"

#include <machine.h>

/*----- Symbol Definition -----*/

*/

unsigned short DTMR; /* DTC Mode Register

*/

unsigned char DTCRAH; /* maintains the Transfer count

*/

unsigned char DTCRAL; /* Transfer counter

*/

unsigned long DTIAR; /* Initial Address Register

*/

unsigned long DTSAR; /* source address register

unsigned long DTDAR; /* destination address register

*/

* /

};

#define DTC COUNT 3

/* DTC Transmit count

*/

#define DTC_R (*(volatile struct st_dtc_repeat*)0xFFFFE000)

/* DTC information address

* /

/*----- Function Definition -----*/

void main(void);

void cmt0 cmi0 dtc(void);

/*----- RAM allocation Definition -----*/

unsigned char S_data[DTC_COUNT]; /* source buffer memory

*/

unsigned char D data; /* destination buffer memory

*/

/* main Program

* /

void main( void )

{

/* Set standby mode */

/* Disable DTC standby mode

*/

P_STBY.MSTCR1.BIT.MSTP25 = 0;

/* Disable DTC standby mode

P STBY.MSTCR1.BIT.MSTP24 = 0;

*/

P STBY.MSTCR2.BIT.MSTP12 = 0;

/* Disable CMT standby mode

*/

Rev. 1.00, 11/03, page 38 of 196

```

```

/* Initialize CMT0 for Interval timer */

P CMT.CMSTR.BIT.STR0 = 0; /* timer count stop

* /

P_CMT.CMCSR_0.WORD = 0x0003;

/* CMF=0;

clear compare match flag

* /

/* CMIE=0; compare match interrupt disable

*/

/* CKS[1:0]=b'11; clock = peripheral clock(P$\phi)/512

*/

*/

*/

* /

P_CMT.CMCSR_0.BIT.CMIE = 1; /* compare match interrupt enable

/* DTC information */

DTC R.DTMR = 0x84a0i

/* SM[1:0]=b'10; DTSAR is incremented

* /

/* DM[1:0]=b'00; DTDAR is fixed

* /

/* MD[1:0]=b'01; Repeat mode

* /

/* SZ[1:0]=b'00; byte-size transfer

*/

/* DTS=1; Source is Repeat area

/* CHNE=0; Chain transfer is disable

/* DISEL=1; Interrupt- every time

/* NMIM=0; NMI->Terminate DTC transfer

*/

*/

*/

*/

DTC R.DTCRAH = DTC COUNT;

/* maintains the Transfer count */

DTC_R.DTCRAL = DTC_COUNT;

/* DTC transfer Count

* /

*/

DTC_R.DTIAR = (unsigned long)&(S_data[0]); /* set Initial address

DTC_R.DTSAR = (unsigned long)&(S_data[0]); /* set source address

*/

DTC_R.DTDAR = (unsigned long)&D_data; /* set destination address */

P DTC.DTBR = 0 \times FFFF;

/* DTC information base register */

/* DTC transmit enable */

P DTC.DTED.BIT.CMI0 |= 1;

/* interrupt sources CMT ch0(CMI0) */

/* set transmit data */

S data[0] = 0x41;

S_data[1] = 0x42;

S_data[2] = 0x43;

P_CMT.CMSTR.BIT.STR0 = 1;

/* CMT0 timer count start

*/

set_imask(0);

/* clear interrupt mask level

*/

while(1);

```

}

Rev. 1.00, 11/03, page 39 of 196

RENESAS

}

Rev. 1.00, 11/03, page 40 of 196

# 2.3 Data Transfer Using DTC Block Transfer Mode (CMT, DTC)

| Data Transfer Using DTC Block Transfer Mode | Functions Used: CMT, DTC  |

|---------------------------------------------|---------------------------|

| (CMT, DTC)                                  | Functions Used: CWII, DIC |

## Specifications

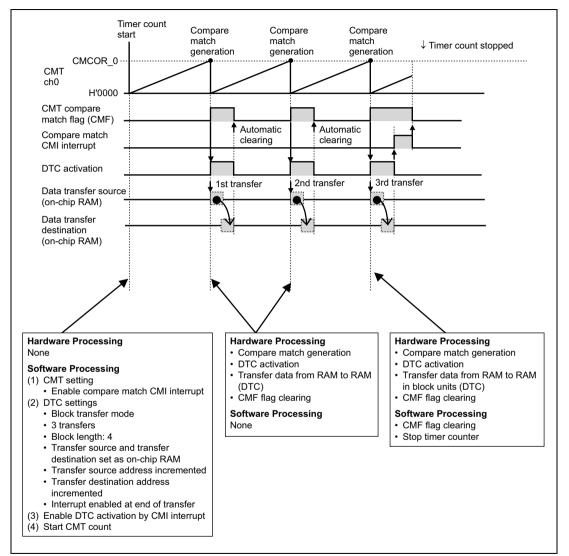

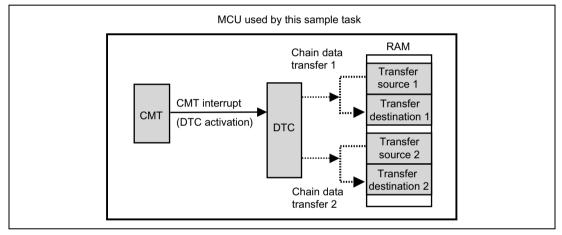

- (1) The data transfer controller (DTC) is activated by a compare match timer (CMT) compare match interrupt, and performs data transfer from on-chip RAM to on-chip RAM, as shown in figure 2.13.

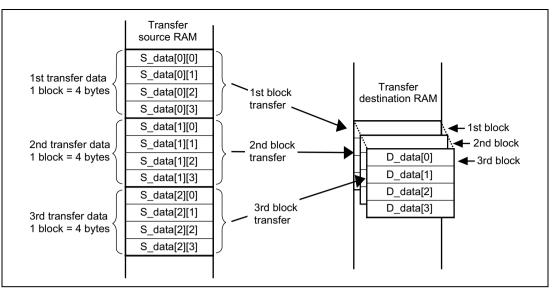

- (2) Block transfer mode is used for DTC data transfer, with 3 transfers of a 4-byte data block performed as shown in figure 2.14.

- (3) The DTC transfer conditions are shown in table 2.15.

Figure 2.13 Data Transfer Using DTC

Figure 2.14 Data Transfer in DTC Normal Mode

| Table 2.15 DIC Hansler Conditions | <b>Table 2.15</b> | DTC | Transfer | Conditions |

|-----------------------------------|-------------------|-----|----------|------------|

|-----------------------------------|-------------------|-----|----------|------------|

| Condition                    | Description                                                                    |

|------------------------------|--------------------------------------------------------------------------------|

| Transfer mode                | Block transfer mode, destination side (transfer destination) set as block area |

| Number of transfers          | 3                                                                              |

| Block length                 | 4                                                                              |

| Transfer data size           | Byte transfer                                                                  |

| Transfer source              | On-chip RAM                                                                    |

| Transfer destination         | On-chip RAM (block area)                                                       |

| Transfer source address      | Transfer source address incremented after transfer                             |

| Transfer destination address | Transfer destination address incremented after transfer                        |

| Activation source            | Activated by CMT ch0 compare match interrupt (CMI0)                            |

| Interrupt handling           | Interrupt to CPU enabled only at end of specified data transfer                |

## **Functions Used**

- (1) A block diagram of the DTC is shown below. Of the three DTC transfer modes normal mode, repeat mode, and block transfer mode —this sample task uses normal mode to perform data transfer. Data transfer is performed from on-chip RAM to on-chip RAM, using a CMT compare match interrupt as the DTC activation source. The block diagram is explained below.

- The DTC mode register (DTMR) is a 16-bit register that controls the DTC's operating mode.

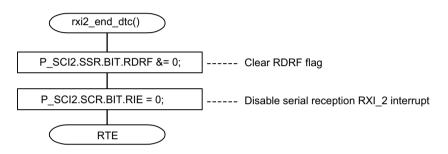

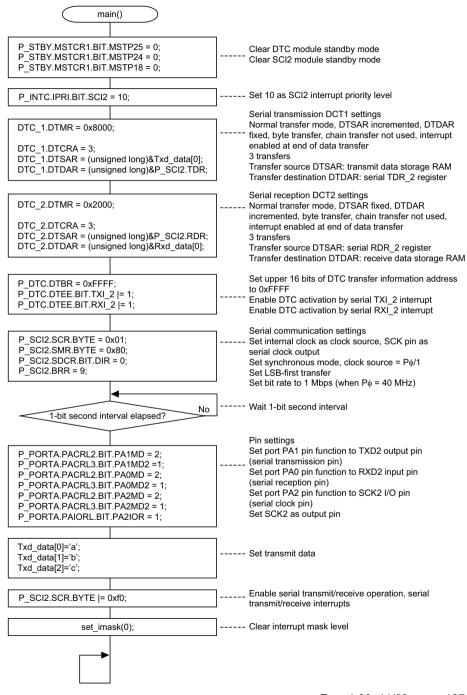

- The DTC source address register (DTSAR) is a 32-bit register that specifies the transfer source address of data to be transferred by the DTC. An even address should be specified in the case of word size transfer, and an address that is a multiple of 4 in the case of longword transfer.