# RX71M Group

SH7214/SH7216 to RX71M Microcontroller Migration Guide

R01AN4044EJ0100 Rev.1.00 Feb 27, 2018

# Summary

This application note describes points requiring special attention, points of difference, etc., that need to be borne in mind when replacing the SH7214 or SH7216 with the RX71M in a user system. For detailed information on each function, refer to the latest version of the User's Manual: Hardware.

In this application note the SH7214 and SH7216 are referred to collectively as the SH7216 Group, and the specifications of the SH7216 are treated as representative. Although there are minor differences in functions and pins among the products composing the SH7216 Group, functionally they are all basically equivalent to the SH7216. This application note therefore applies to the entire SH7216 Group.

Users are encouraged to make use of the available drivers for function modules such as the Ethernet controller, USB, and flash memory.

# **Target Device**

RX71M

# Contents

| 1. ( | CPU | Architecture                                                  | ; |

|------|-----|---------------------------------------------------------------|---|

| 1.1  | Da  | ta Format6                                                    | 5 |

| 1.2  | Sy  | stem Registers6                                               | 5 |

| 1.   | 2.1 | General-Purpose Registers6                                    | 5 |

| 1.   | 2.2 | Control Registers                                             | 7 |

| 1.3  | Op  | tion-Setting Memory10                                         | ) |

| 1.   | 3.1 | Outline of Option-Setting Memory10                            | ) |

| 1.   | 3.2 | Endian Setting                                                | 2 |

| 1.   | 3.3 | Specifying TM Identification Data and Setting TM Enable Flags | 3 |

| 1.   | 3.4 | OCD/Serial Programmer Settings13                              | 3 |

| 1.4  | Re  | set Function14                                                | ł |

| 1.   | 4.1 | Reset Sources14                                               | ł |

| 1.   | 4.2 | Reset Sources and Initialization Scope15                      | 5 |

| 1.   | 4.3 | Cold/Warm Start Determination Function17                      | , |

| 1.   | 4.4 | Write Protection17                                            | , |

| 1.5  | Clo | ock Settings17                                                | , |

| 1.   | 5.1 | Clock Sources                                                 | , |

| 1.   | 5.2 | Clock Generation Circuit17                                    | 1 |

| 1.   | 5.3 | Write Protection                                              | 3 |

| 1.6  | Ор  | eration Modes19                                               | ) |

| 1.   | 6.1 | Comparison of Operation Modes19                               | • |

| 1.   | 6.2 | Comparison of Memory20                                        | ) |

| 1.   | 6.3 | Operation Mode Settings23                                     | 3 |

|      |     |                                                               |   |

| 1.6.4  | Write Protection                                               | 23 |

|--------|----------------------------------------------------------------|----|

| 1.7 P  | ocessor Modes                                                  | 24 |

| 1.8 E  | cception Handling                                              | 25 |

| 1.8.1  | Types of Exception Handling                                    | 25 |

| 1.8.2  | Exception Handling Priority                                    | 25 |

| 1.8.3  | Basic Processing Sequence of Exception Handling                | 26 |

| 1.8.4  | Vector Configuration                                           | 27 |

| 1.8.5  | Interrupt Masking by SR (SH7216 Group) and PSW (RX71M)         | 28 |

| 1.9 In | terrupt Handling                                               | 29 |

| 1.9.1  | Interrupt Controller                                           | 29 |

| 1.9.2  | Interrupt Flag Management                                      | 32 |

| 1.9.3  | Fast Interrupt Control                                         | 34 |

| 1.9.4  | Noise Cancellation                                             | 35 |

| 1.9.5  | Multiple Interrupts                                            | 35 |

| 1.9.6  | Group Interrupts                                               | 37 |

| 1.9.7  | Software Configurable Interrupts                               | 38 |

| 2. On- | Chip Functions                                                 | 30 |

|        | st of On-Chip Functions                                        |    |

|        | ) Ports/Pin Function Controller (PFC)                          |    |

| 2.2 // | Number of I/O Ports                                            |    |

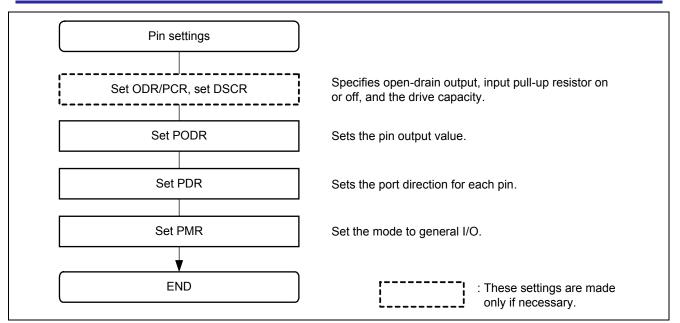

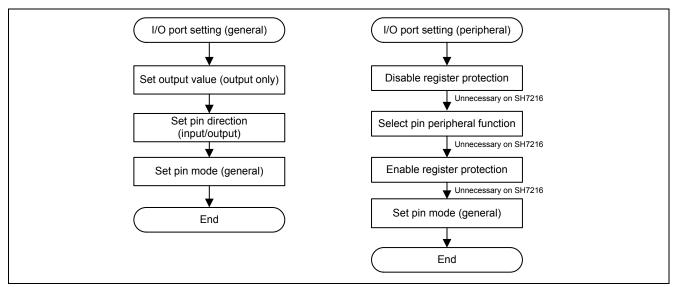

| 2.2.2  | I/O Settings                                                   |    |

| 2.2.2  | General I/O Setting Examples                                   |    |

|        | Jses                                                           |    |

| 2.3.1  | Comparison of Specifications                                   |    |

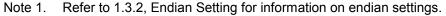

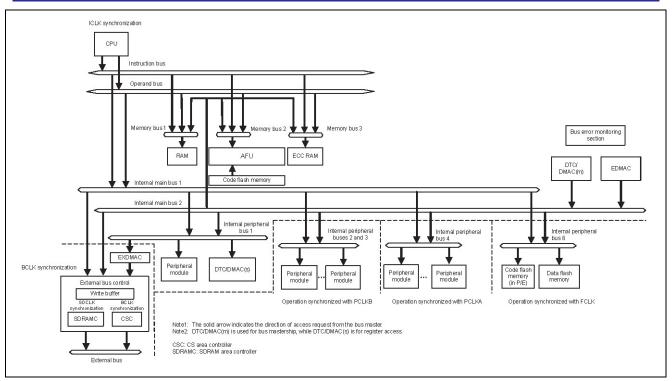

| 2.3.2  | Bus Block Diagrams                                             |    |

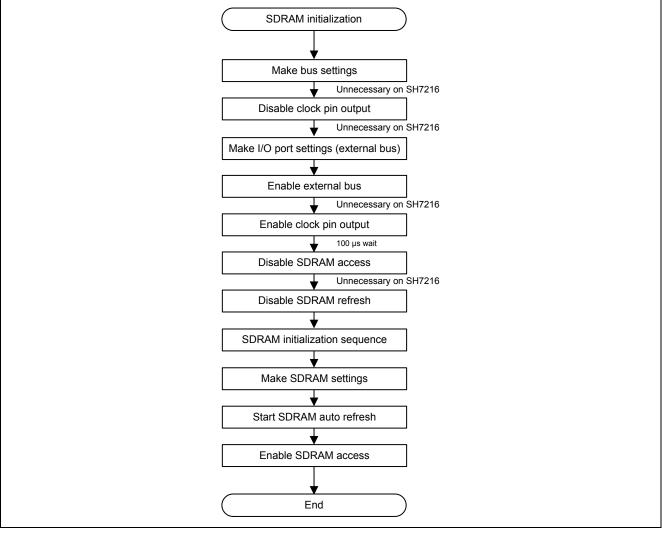

| 2.3.3  | SDRAM Read/Write Setting Example                               |    |

|        | terrupt Controller                                             |    |

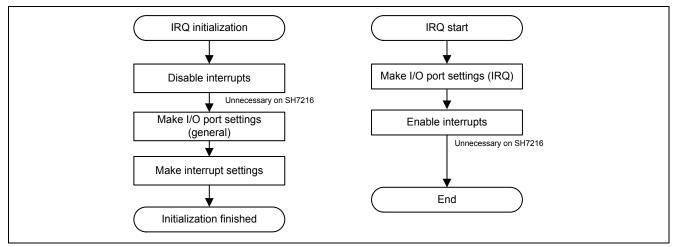

| 2.4.1  | IRQ Setting Example                                            |    |

|        | ata Transfer Controller (DTC)                                  |    |

| 2.5.1  | Comparison of Specifications                                   |    |

| 2.5.2  | Register Comparison                                            |    |

| 2.5.3  | Activation Source Settings                                     |    |

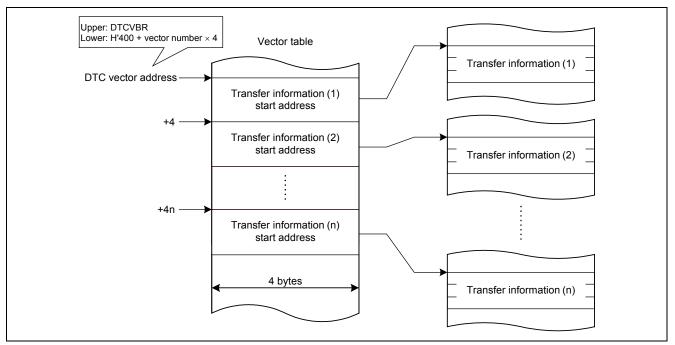

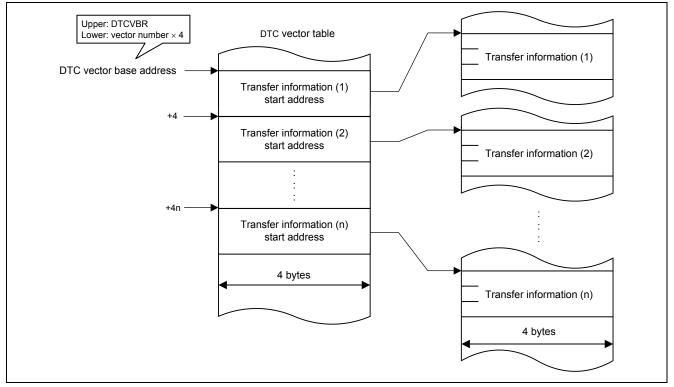

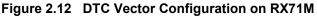

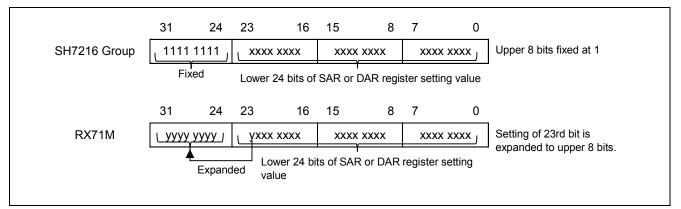

| 2.5.4  | DTC Vector Configuration                                       | 61 |

| 2.5.5  | Allocation of Transfer Information                             |    |

| 2.5.6  | Module Stop                                                    |    |

| 2.5.7  | Setting Examples for Data Transfer between SCI and On-Chip RAM |    |

| 2.6 D  | rect Memory Access Controller (DMAC)                           |    |

| 2.6.1  | Comparison of Specifications                                   |    |

|        |                                                                |    |

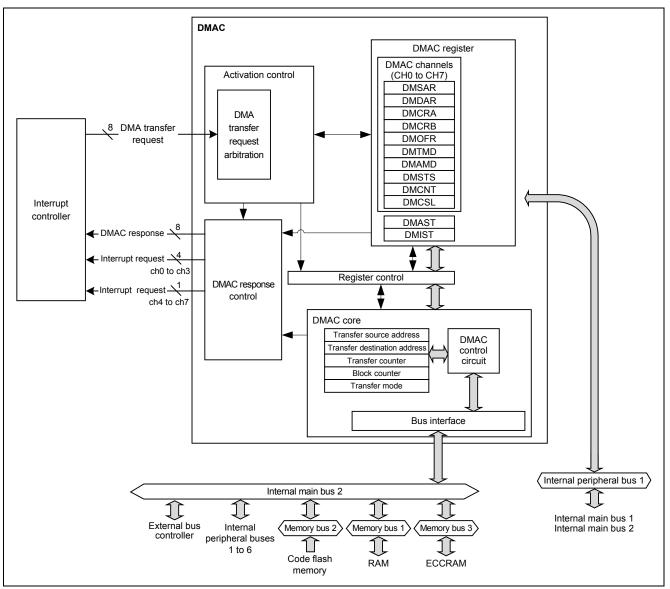

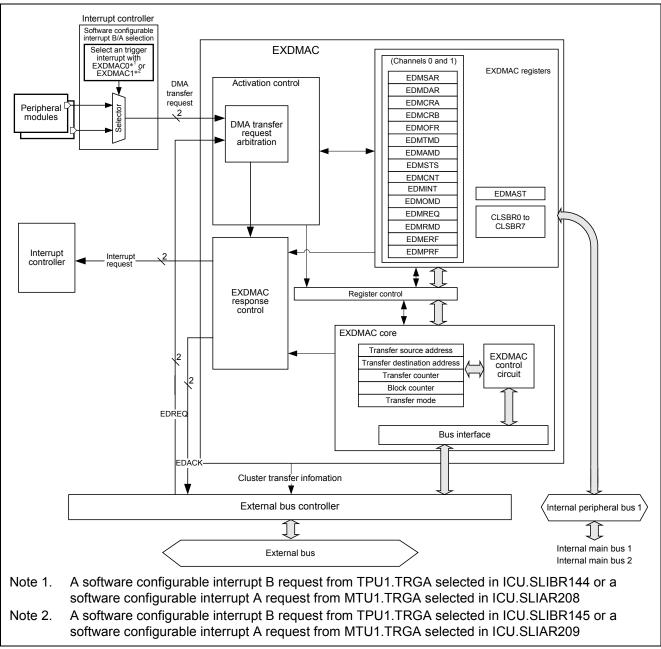

| 2.6.2  | DMAC Block Diagram                                             |    |

| 2.6.4   | Activation Source Settings                                             | 74  |

|---------|------------------------------------------------------------------------|-----|

| 2.6.5   | Transfer Count                                                         | 74  |

| 2.6.6   | Transfer Sources and Destinations                                      | 75  |

| 2.6.7   | Address Modes                                                          | 76  |

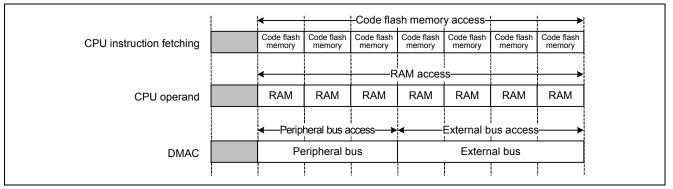

| 2.6.8   | Bus Modes                                                              | 76  |

| 2.6.9   | Module Stop                                                            | 76  |

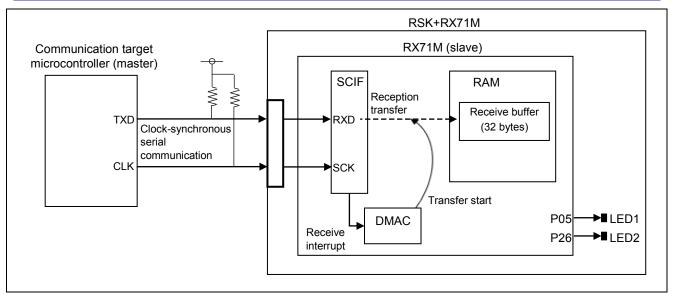

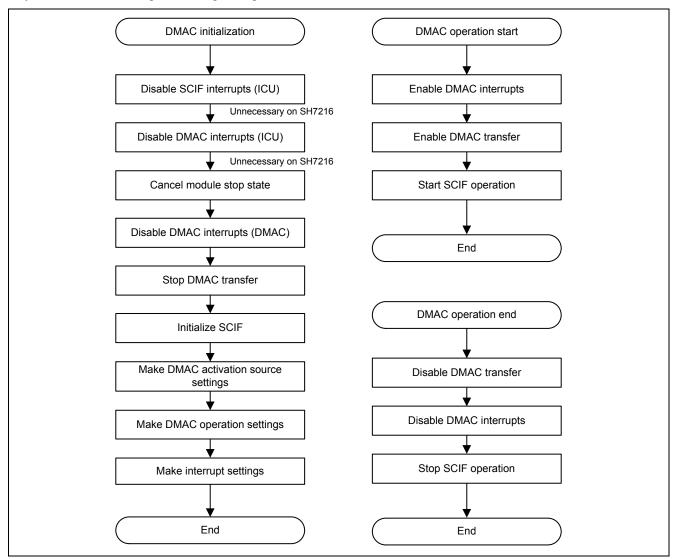

| 2.6.10  | Setting Example for Data Transfer between SCIF and On-Chip RAM         | 77  |

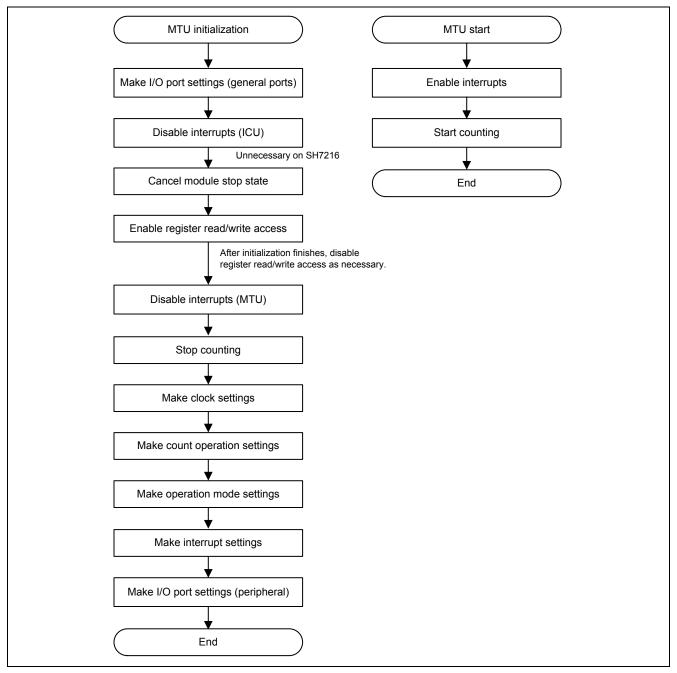

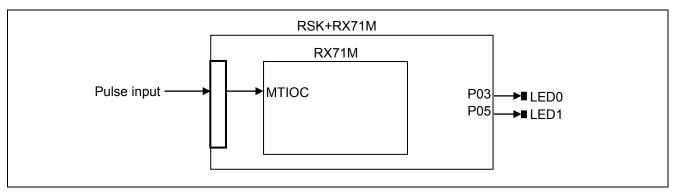

| 2.7 Mu  | Ilti-function Timer Pulse Unit (MTU)                                   | 83  |

| 2.7.1   | Comparison of Specifications                                           | 83  |

| 2.7.2   | Interrupts                                                             | 84  |

| 2.7.3   | Register Comparison                                                    | 85  |

| 2.7.4   | Module Stop                                                            | 87  |

| 2.7.5   | Compare Match Pulse Output Setting Examples                            | 88  |

| 2.7.6   | Input Capture Pulse Width Measurement Setting Examples                 | 91  |

| 2.8 Po  | rt Output Enable (POE)                                                 | 95  |

| 2.8.1   | Comparison of Specifications                                           | 95  |

| 2.8.2   | Input/Output Pins                                                      | 96  |

| 2.8.3   | Register Comparison                                                    | 97  |

| 2.8.4   | High-Impedance Control by Oscillation Stop Detection                   | 98  |

| 2.8.5   | Addition of High-Impedance Control Conditions                          | 98  |

| 2.8.6   | Interrupts                                                             | 98  |

| 2.9 Wa  | atchdog Timers (WDT)                                                   | 99  |

| 2.9.1   | Comparison of Specifications                                           | 99  |

| 2.9.2   | Count Start Conditions                                                 | 100 |

| 2.9.3   | Refresh Operation                                                      | 100 |

| 2.9.4   | Register Write Limitations                                             | 100 |

| 2.9.5   | Interrupts                                                             | 101 |

| 2.9.6   | All-Module Stop                                                        | 101 |

| 2.9.7   | Option Settings                                                        | 101 |

| 2.10 Se | rial Communication Interface (SCI)                                     | 102 |

| 2.10.1  | Comparison of Specifications                                           | 102 |

| 2.10.2  | Register Comparison                                                    | 104 |

| 2.10.3  | Clock Source Selection                                                 | 105 |

| 2.10.4  | Interrupts                                                             | 105 |

| 2.10.5  | Module Stop                                                            | 105 |

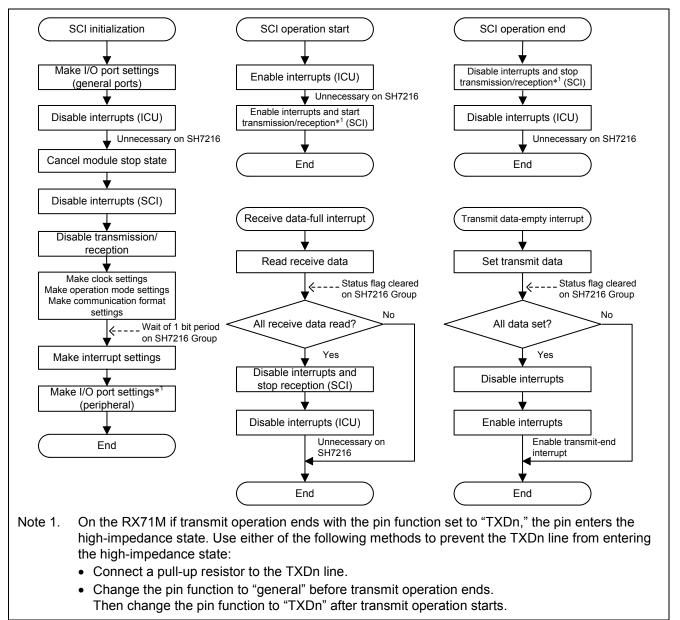

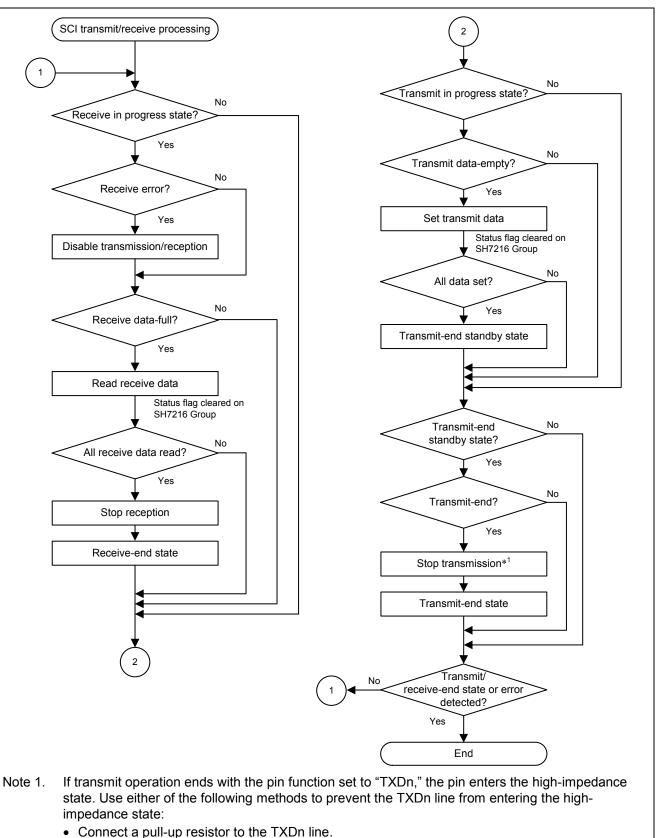

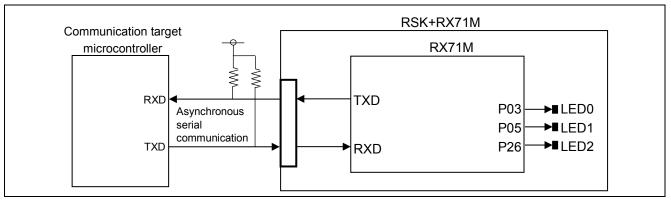

| 2.10.6  | Asynchronous Transmit/Receive Setting Examples (Interrupt/Polling)     | 106 |

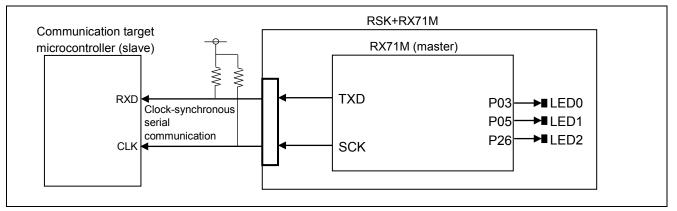

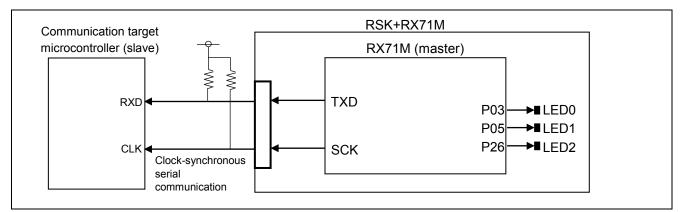

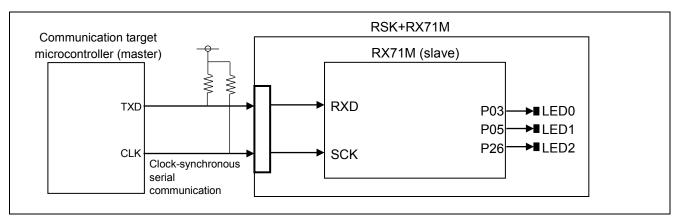

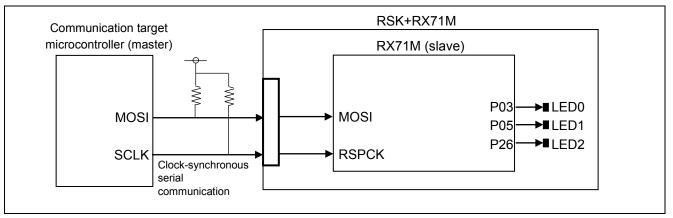

| 2.10.7  | Clock-Synchronous Master Transmit Setting Examples (Interrupt/Polling) | 114 |

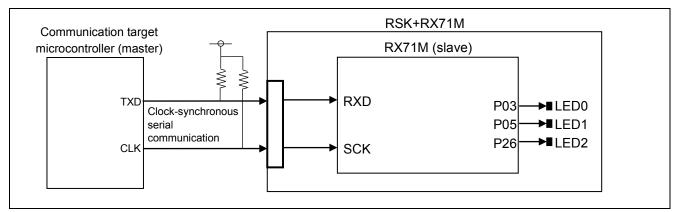

| 2.10.8  | Clock-Synchronous Slave Reception Setting Examples (Interrupt/Polling) | 117 |

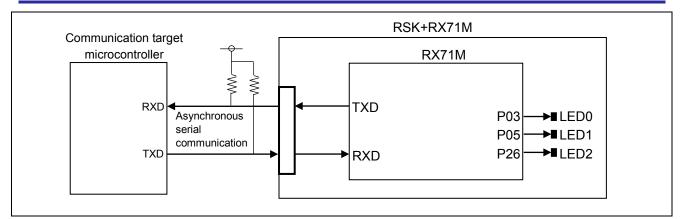

| 2.11 Se | rial Communications Interface with FIFO (SCIF)                         | 120 |

| 2.11.1  | Comparison of Specifications                                           | 120 |

| 2 11 2  | Register Comparison                                                    | 121 |

| 2.11.3                | Interrupts                                                            |     |

|-----------------------|-----------------------------------------------------------------------|-----|

| 2.11.4                | Module Stop                                                           | 122 |

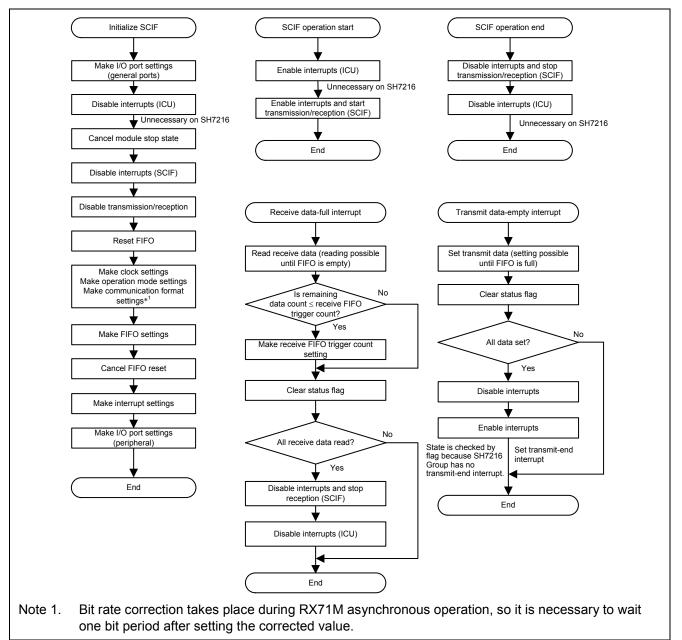

| 2.11.5                | Asynchronous Transmit/Receive Setting Examples                        | 123 |

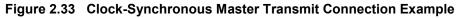

| 2.11.6                | Clock-Synchronous Master Transmit Setting Examples                    | 131 |

| 2.11.7                | Clock-Synchronous Slave Reception Setting Examples                    | 134 |

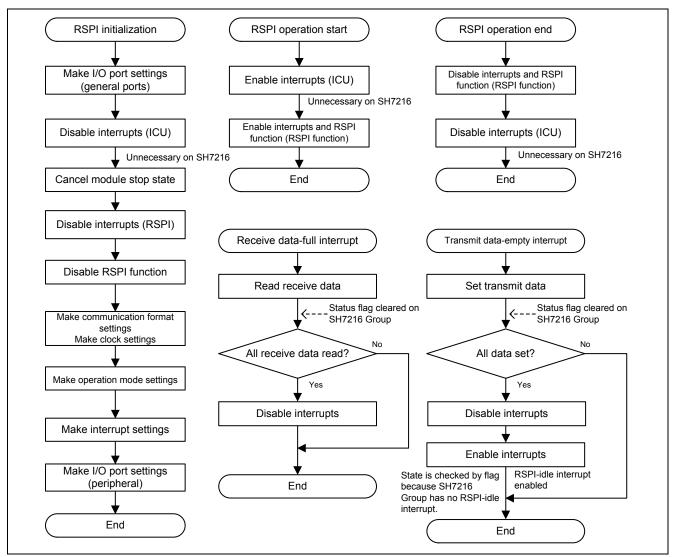

| 2.12 Se               | rial Peripheral Interface (RSPI)                                      |     |

| 2.12.1                | Comparison of Specifications                                          | 137 |

| 2.12.2                | Register Comparison                                                   | 138 |

| 2.12.3                | Interrupts                                                            | 138 |

| 2.12.4                | Module Stop                                                           |     |

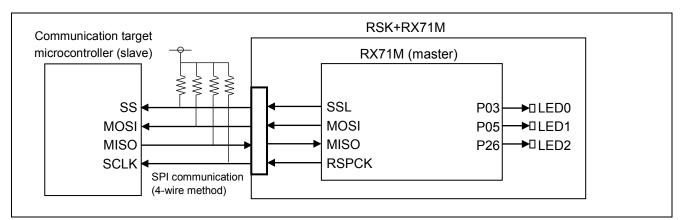

| 2.12.5                | Setting Example for Master Transmission/Reception Using SPI Operation | 139 |

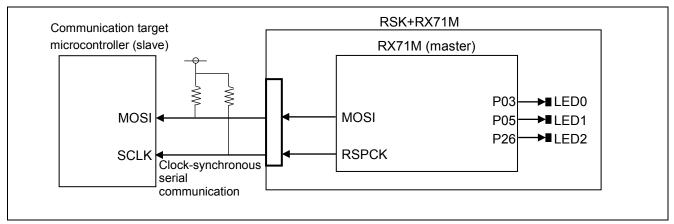

| 2.12.6                | Clock-Synchronous Master Transmission Setting Example                 | 147 |

| 2.12.7                | Clock-Synchronous Slave Reception Setting Example                     | 151 |

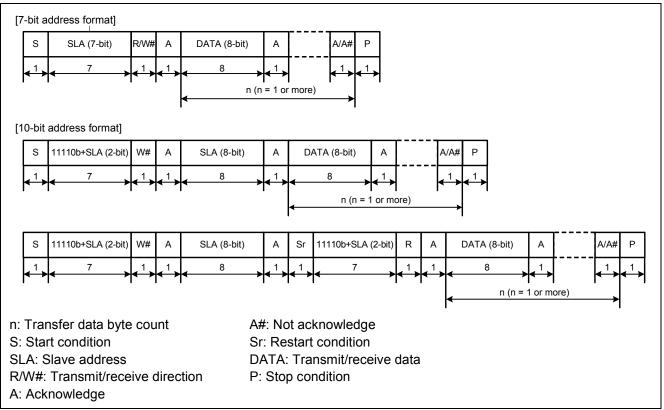

| 2.13 l <sup>2</sup> C | Bus Interface (IIC)                                                   | 155 |

| 2.13.1                | Comparison of Specifications                                          | 155 |

| 2.13.2                | Register Comparison                                                   | 156 |

| 2.13.3                | Address Detection                                                     | 157 |

| 2.13.4                | Arbitration Lost Detection                                            | 157 |

| 2.13.5                | Bus Hang-up                                                           | 157 |

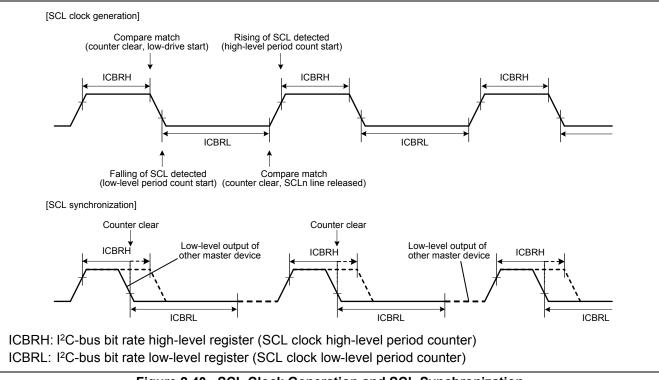

| 2.13.6                | SCL Clock                                                             | 158 |

| 2.13.7                | Noise Cancellation                                                    | 158 |

| 2.13.8                | Interrupts                                                            | 159 |

| 2.13.9                | Module Stop                                                           | 159 |

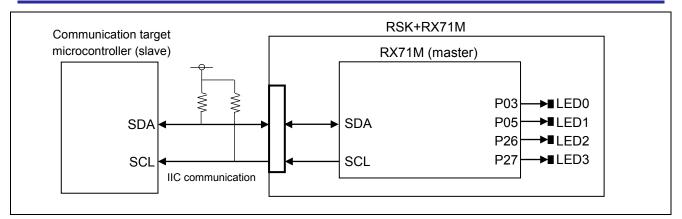

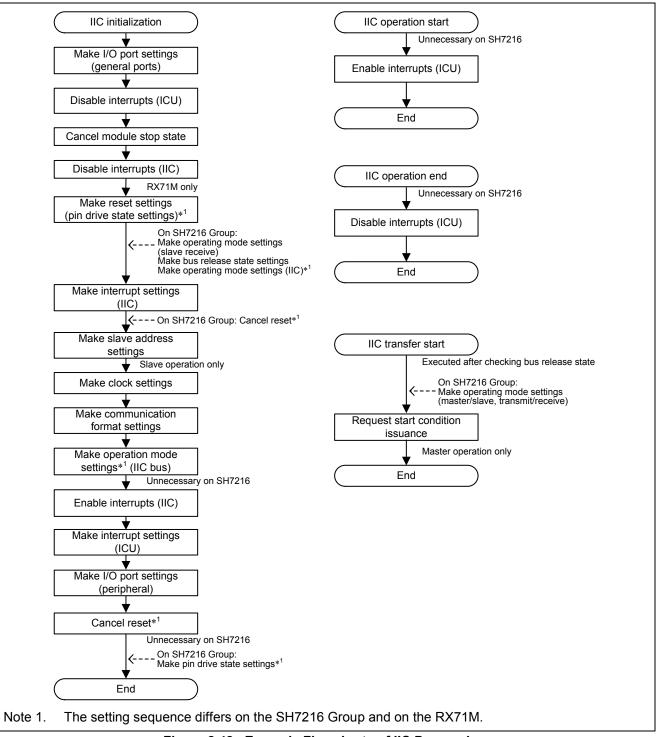

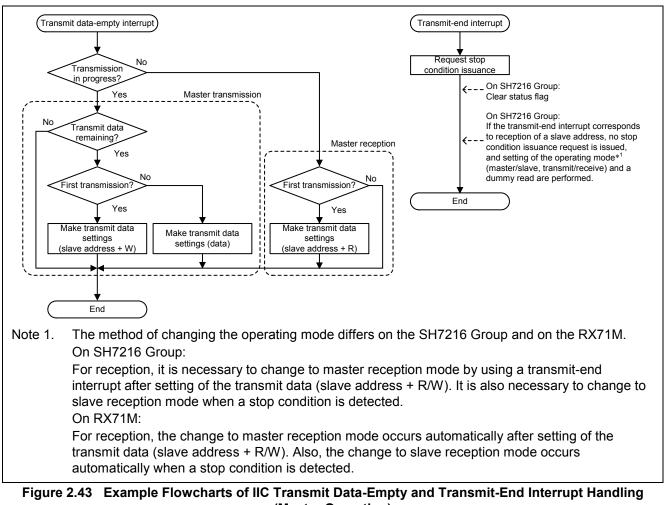

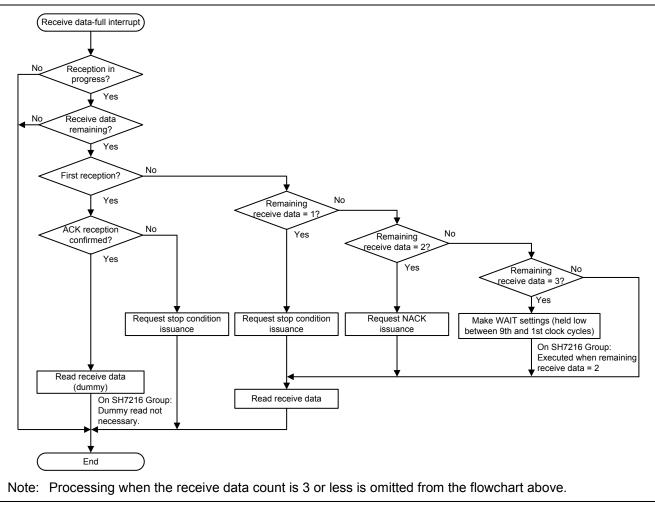

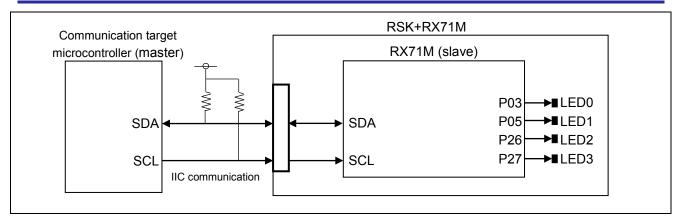

| 2.13.1                | 0Setting Example for Master Transmission/Reception                    |     |

| 2.13.1                | 1Setting Example for Slave Transmission/Reception                     | 170 |

| 2.14 A/               | D Converter (ADC)                                                     | 173 |

| 2.14.1                | Comparison of Specifications                                          | 173 |

| 2.14.2                | Input Channels                                                        |     |

| 2.14.3                | Scanning Sequence                                                     |     |

| 2.14.4                | Operating Modes                                                       |     |

| 2.14.5                | Interrupts                                                            |     |

| 2.14.6                | Module Stop                                                           |     |

| 2.14.7                | Setting Examples for A/D Conversion in Continuous Scan Mode           | 175 |

| 2.15 CA               | AN                                                                    |     |

| 2.15.1                | Comparison of Specifications                                          |     |

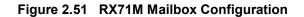

| 2.15.2                | Mailboxes                                                             |     |

| 2.15.3                | Acceptance Filtering                                                  |     |

| 2.15.4                | Transmission Priority                                                 |     |

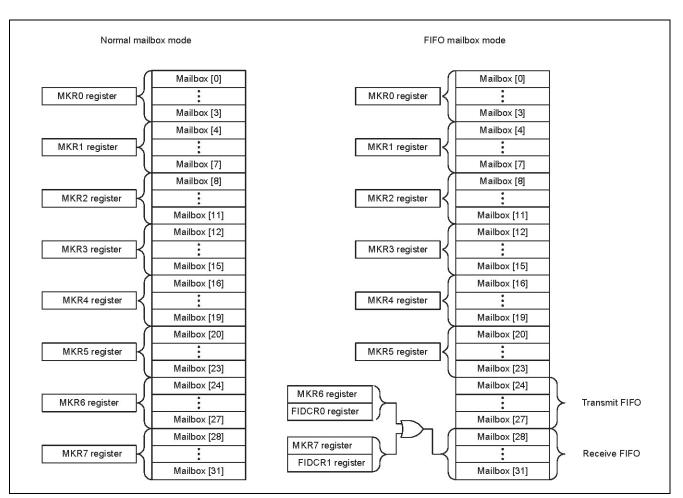

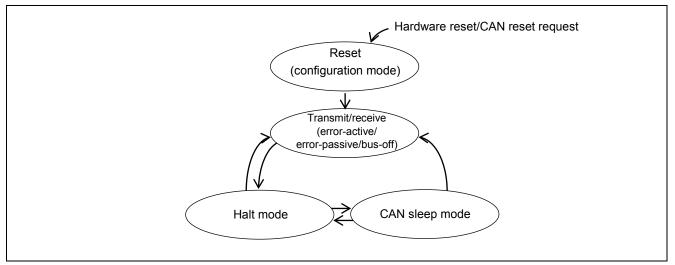

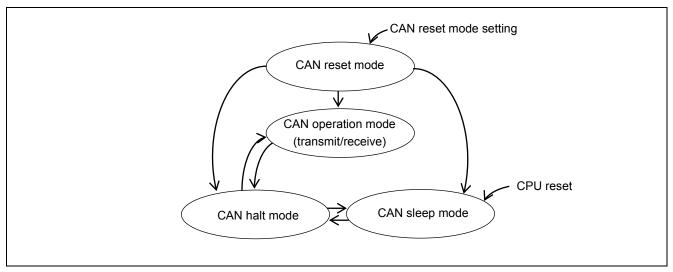

| 2.15.5                | Mode Transitions                                                      |     |

| 2.15.6                | Interrupts                                                            |     |

| 2.15.7                | Module Stop                                                           |     |

| 2.16 USB                                                     |     |

|--------------------------------------------------------------|-----|

| 2.16.1 Comparison of Specifications                          |     |

| 2.17 Ethernet Controller (EtherC)                            |     |

| 2.17.1 Comparison of Specifications                          |     |

| 2.18 Compare Match Timer (CMT)                               |     |

| 2.18.1 Comparison of Specifications                          |     |

| 2.18.2 Register Comparison                                   |     |

| 2.18.3 Interrupts                                            |     |

| 2.18.4 Module Stop                                           | 190 |

| 2.18.5 Compare Match Timer Setting Example                   |     |

| 2.19 Code Flash Memory                                       |     |

| 2.19.1 Comparison of Specifications                          | 195 |

| 2.20 Data Flash Memory                                       | 197 |

| 2.20.1 Comparison of Specifications                          | 197 |

| 2.21 Low Power Consumption Function                          |     |

| 2.21.1 Comparison of Mode Specifications                     |     |

| 2.21.2 Mode Transitions                                      |     |

| 2.21.3 Module-Stop State                                     |     |

| 2.21.4 Write Protection                                      |     |

| 2.21.5 Low-Power-Consumption Mode Transition Setting Example |     |

| 3. Sample Code                                               | 209 |

| 3.1 Operating Environment                                    |     |

| 3.2 Sample Code Configuration                                | 210 |

| 4. Reference Documents                                       | 212 |

| 4.1 Reference Documents                                      |     |

## 1. CPU Architecture

## 1.1 Data Format

The SH7216 Group supports double-precision floating-point data, but the RX71M does not.

# 1.2 System Registers

The points of difference between the registers of the SH7216 Group and the RX71M are described below.

#### 1.2.1 General-Purpose Registers

The SH7216 Group and RX71M each have 16 32-bit general-purpose registers. They differ in that the register used as the stack pointer (SP) is different.

- SH7216 Group: R15

- RX71M: R0

Figure 1.1 shows the general-purpose registers of the SH7217 Group and RX71M. On the SH7216 Group R0 is also used as an index register.

| SH7216 Group     |   |   | RX71M                 |   |

|------------------|---|---|-----------------------|---|

| 31               | 0 |   | 31                    | 0 |

| R0* <sup>1</sup> |   | , | R0 (SP)* <sup>2</sup> |   |

| R1               |   |   | R1                    |   |

| R2               |   | / | R2                    |   |

| R3               |   | / | R3                    |   |

| R4               |   |   | R4                    |   |

| R5               |   |   | R5                    |   |

| R6               |   |   | R6                    |   |

| R7               |   |   | R7                    |   |

| R8               |   |   | R8                    |   |

| R9               |   |   | R9                    |   |

| R10              |   |   | R10                   |   |

| R11              |   |   | R11                   |   |

| R12              |   |   | R12                   |   |

| R13              |   |   | R13                   |   |

| R14              |   |   | R14                   |   |

| R15 (SP)         |   |   | R15                   |   |

Note 1. Used as the index register in the indexed register indirect and indexed GBR indirect addressing modes. R0 may be fixed as the source or destination register, depending on the instruction.

Note 2. The stack pointer (SP) can be switched between operation as the interrupt stack pointer (ISP) and as the user stack pointer (USP) by means of the U bit in PSW.

Figure 1.1 Differences Between General-Purpose Registers

## 1.2.2 Control Registers

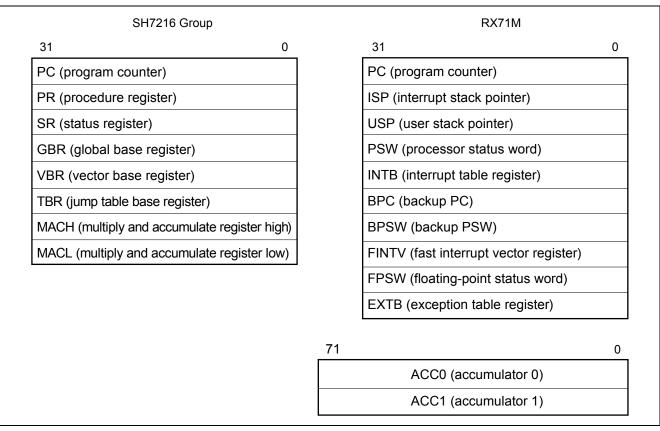

Figure 1.2 shows the points of difference between the CPU registers (other than the general-purpose registers) of the SH7216 Group and the RX71M.

Figure 1.2 Points of Difference Between CPU Registers (Excluding General-Purpose Registers)

The RX71M has no registers corresponding to PR, GBR, and TBR on the SH7216 Group. The ACC0 and ACC1 registers on the RX71M corresponds to MACH and MACL on the SH7216 Group. An outline of the control registers that are implemented on the RX71M but not on the SH7216 Group is presented below.

| Table 1.1 RX71M | Control Registers | Not Present on | SH7216 Group |

|-----------------|-------------------|----------------|--------------|

|-----------------|-------------------|----------------|--------------|

| Register Name                          | Description                                                                                                                                |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupt stack pointer (ISP)          | The RX71M has two types of stack pointers. The type of stack                                                                               |

| User stack pointer (USP)               | pointer used (ISP or USP) can be switched by means of the stack pointer select bit (U) in the processor status word (PSW) register.        |

| Interrupt table register (INTB)*1      | Specifies the start address of the interrupt vector table.                                                                                 |

| Exception table register (EXTB)*1      | Specifies the start address of the exception vector table.                                                                                 |

| Backup PC (BPC)                        | The RX71M supports fast interrupts in addition to ordinary                                                                                 |

| Backup PSW (BPSW)                      | interrupts. For fast interrupts, the contents of PC and PSW are                                                                            |

|                                        | saved to dedicated registers (BPC and BPSW), thereby reducing                                                                              |

|                                        | the processing time needed to save the register data.                                                                                      |

| Fast interrupt vector register (FINTV) | This register specifies the jump destination when a fast interrupt                                                                         |

|                                        | OCCURS.                                                                                                                                    |

| Floating-point status word (FPSW)      | This register indicates the status of the calculation result (floating-<br>point calculation result) generated by the RX71M's on-chip FPU. |

Note 1. The functionality of this register is equivalent to that of VBR on the SH7216 Group.

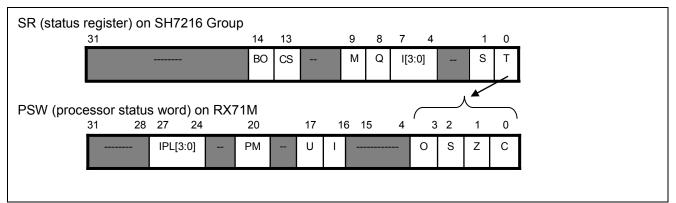

Figure 1.3 and Table 1.2 show the points of difference between the status registers of the SH7216 Group and the RX71M.

Figure 1.3 Differences Between SR (SH7216 Group) and PSW (RX71M)

| SH Bit Name | RX Bit Name | Description                                                                                                                                       |

|-------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Т           | С           | The calculation result (true/false, carry/borrow, etc.) indicated by the T                                                                        |

|             | Z           | bit on the SH7216 Group is shown by four flags (C, Z, S, and O) on the                                                                            |

|             | S           | RX71M.                                                                                                                                            |

|             | 0           | C: Carry flag (0/1 = No carry has occurred./A carry has occurred.)                                                                                |

|             |             | Z: Zero flag                                                                                                                                      |

|             |             | S: Sign flag                                                                                                                                      |

|             |             | O: Overflow flag                                                                                                                                  |

| S           | —           | Controls the functionality that prevents overflows during ALU arithmetic operations performed by the DSP unit of the SH7216 Group.                |

|             |             | On the RX71M there is no bit corresponding to the S bit, and the                                                                                  |

|             |             | occurrence of an overflow during a floating-point operation is reported                                                                           |

|             |             | by the FPSW flag. It is also possible to perform exception handling                                                                               |

|             |             | when an overflow occurs.                                                                                                                          |

| I[3:0]      | IPL[3:0]    | These are the interrupt mask bits.                                                                                                                |

|             |             | Both the SH7216 Group and the RX71M support level settings from 0                                                                                 |

|             |             | (lowest) to 15 (highest). Only interrupts with a priority level higher than                                                                       |

|             |             | this setting are accepted.                                                                                                                        |

| Q           |             | The Q bit is used by the DIVOU, DIVOS, and DIV1 instructions on the                                                                               |

|             |             | SH7216 Group. There is no corresponding bit on the RX71M.                                                                                         |

| Μ           |             | The M bit is used by the DIV0U, DIV0S, and DIV1 instructions on the                                                                               |

|             |             | SH7216 Group. There is no corresponding bit on the RX71M.                                                                                         |

| CS          |             | On the SH7216 Group the CS bit is used in CLIP instruction execution,                                                                             |

|             |             | but there is no equivalent bit on the RX71M.                                                                                                      |

| BO          |             | On the SH7216 Group the BO bit indicates that a register bank has                                                                                 |

|             |             | overflowed, but there is no equivalent bit on the RX71M.                                                                                          |

|             | I           | Interrupt enable bit                                                                                                                              |

|             |             | 0: Interrupts are disabled.                                                                                                                       |

|             |             | 1: Interrupts are enabled.                                                                                                                        |

|             |             | This bit is used to enable interrupt requests on the RX71M. The initial                                                                           |

|             |             | state is 0, so it is necessary to set this bit to 1 in order to accept interrupts. It is set to 1 when a WAIT instruction is accepted and cleared |

|             |             | to 0 when an exception is accepted.                                                                                                               |

|             |             | Note that the interrupt status flag of the interrupt controller is reset when                                                                     |

|             |             | an interrupt request occurs, regardless of the setting of this bit.                                                                               |

|             | U           | This bit specifies the stack pointer used by the RX71M.                                                                                           |

|             | 0           | 0: Interrupt stack pointer (ISP)                                                                                                                  |

|             |             | 1: User stack pointer (USP)                                                                                                                       |

|             |             |                                                                                                                                                   |

|             |             | This bit is cleared to 0 when an exception is accepted. It is set to 1 when a transition from supervisor mode to user mode occurs.                |

|             | PM          | This bit specifies the processor mode of the RX71M.                                                                                               |

|             | 1 111       | 0: Supervisor mode                                                                                                                                |

|             |             | 1: User mode                                                                                                                                      |

|             |             |                                                                                                                                                   |

|             |             | This bit is cleared to 0 when an exception is accepted.                                                                                           |

#### Table 1.2 Differences Between SR (SH7216 Group) and PSW (RX71M)

# 1.3 Option-Setting Memory

The RX71M is provided with an option-setting memory area containing registers for selecting the microcontroller state after a reset of the endian mode, watchdog timer operation, etc. Option-setting memory is allocated in the configuration setting area and user boot area of the flash memory, and the available setting methods are different for the two areas. For details, see the User's Manual: Hardware.

# 1.3.1 Outline of Option-Setting Memory

Figure 1.4 shows an outline of the option-setting memory area.

|                             | Register name                                     | Register overview                                                                                                                                                |

|-----------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address                     | —                                                 | _                                                                                                                                                                |

| 0012 0040h to<br>0012 0043h | Serial programmer command control register (SPCC) | Used to make settings for serial ID code protection,<br>serial programmer connection, block erasure<br>commands, programming commands, and read<br>commands.     |

|                             |                                                   | —                                                                                                                                                                |

| 0012 0048h to<br>0012 004Bh | TM enable flag register (TMEF)                    | Used to enable or disable the TM function.                                                                                                                       |

|                             |                                                   | —                                                                                                                                                                |

| 0012 0050h to<br>0012 005Fh | OCD/serial programmer ID setting register (OSIS)  | Used to store the ID code for the ID code protection function of the OCD/serial programmer.                                                                      |

| 0012 0060h to<br>0012 0063h | TM identification data register (TMINF)           | Area in which the user can store any 32 bits of data,<br>such as a code used to identify the program stored in<br>the area for which the TM function is enabled. |

| 0012 0064h to<br>0021 0067h | Endian select register (MDE)                      | Used to specify the endian setting of the CPU.                                                                                                                   |

| 0012 0068h to<br>0012 006Bh | Option function select register 0<br>(OFS0)       | Used to make settings for the independent watchdog timer (IWDT) and watchdog timer (WDT).                                                                        |

| 0012 006Ch to<br>0012 006Fh | Option function select register 1<br>(OFS1)       | Used to make settings for voltage monitoring after a reset and HOCO oscillation.                                                                                 |

|                             |                                                   | —                                                                                                                                                                |

| FF7F FFE8h to<br>FF7F FFEFh | UB code A                                         | Area for storing two 32-bit words required when using user boot mode (5573 6572h and 426F 6F74h).                                                                |

| FF7F FFF0h to<br>FF7F FFF7h | UB code B                                         | Area for storing two 32-bit words required when using user boot mode (FFFF FF07h and 0008 C04Ch).                                                                |

|                             | —                                                 | _                                                                                                                                                                |

Figure 1.4 RX71M Option-Setting Memory Area

Figure 1.5 to Figure 1.8 show sample settings for the option-setting memory.

```

/* Settings for enabling serial programmer connection and ID code protection after a reset. */

#pragma address SPCC_REG = 0x00120040 // SPCC register

const unsigned long SPCC_REG = 0x1EFFFFF;

/* ID code settings for OCD/serial programmer */

/* ID1 =0x01, ID2 =0x02, ID3 =0x03, ID4 =0x04 */

/* ID5 =0x05, ID6 =0x06, ID7 =0x07, ID8 =0x08 */

/* ID9 =0x09, ID10=0x0A, ID11=0x0B, ID12=0x0C */

/* ID13=0x0D, ID14=0x0E, ID15=0x0F, ID16=0x10 */

#pragma address OSIS1_REG = 0x00120050 // OSIS register

const unsigned long OSIS5_REG = 0x00120054 // OSIS register

const unsigned long OSIS5_REG = 0x00120058 // ID5, ID6, ID7, ID8

#pragma address OSIS9_REG = 0x00120058 // OSIS register

const unsigned long OSIS9_REG = 0x00120058 // ID5, ID10, ID11, ID12

#pragma address OSIS1_REG = 0x0012005C // OSIS register

```

#### Figure 1.6 RX71M OCD/Serial Programmer Setting Example

const unsigned long OSIS13\_REG = 0x100F0E0D; // ID13, ID14, ID15, ID16

/\* UB code A settings \*/

#pragma address UBA1\_REG = 0xFF7FFFE8 // UB code A\_1 register

const unsigned long UBA1\_REG = 0x55736572;

#pragma address UBA2\_REG = 0xFF7FFFEC // UB code A\_2 register

const unsigned long FAW2\_REG = 0x426F6F74;

#### Figure 1.7 RX71M UB Code A Setting Example

```

#pragma address OFS1_REG = 0x0012006C // OFS1 register

const unsigned long OFS1_REG = 0xFFFFFFFF;

#pragma address OFS0_REG = 0x00120068 // OFS0 register

const unsigned long OFS0_REG = 0xFFFFFFFF;

```

#### Figure 1.8 RX71M OFS0 and OFS1 Setting Example

## 1.3.2 Endian Setting

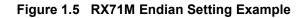

The SH7216 Group is fixed in big-endian mode. On the RX71M, instructions are fixed in little-endian, and the data order is selectable between little-endian and big-endian. The endian setting is specified by means of the endian select bits (MDE[2:0]) in the MDE register in the option-setting memory.

When switching from the SH7216 Group to the RX71M, it is possible to use big-endian order by specifying big-endian in the option settings of the genuine Renesas compiler. This allows migration without the need to be conscious of endianness in the user program.

The endian setting can be switched for each CS area in the external address space. However, instruction code cannot be allocated to an external space with an endian setting that differs from that of the MCU. When allocating instruction code to an external space, ensure that an area with the same endian setting as the MCU is used. (For details, see the User's Manual: Hardware.)

Endian settings based on the compiler option setting are illustrated in Figure 1.9. The files generated automatically based on the compiler option setting have been confirmed to run in the environment described in 3.1, Operating Environment.

Figure 1.9 RX71M Specifying Endianness by Compiler Option

## **1.3.3** Specifying TM Identification Data and Setting TM Enable Flags

The RX71M is provided with a trusted memory (TM) function to prevent third parties from reading software stored in blocks 8 and 9 of the code flash memory. The TM function prevents reading of some designated areas even internally by the microcontroller, such as the on-chip flash memory, and allows instruction execution only.

This function is useful when storing software for processing encryption algorithms, device control processing software incorporating valuable intellectual property, commercial middleware, or the like in the code flash memory.

## 1.3.4 OCD/Serial Programmer Settings

The RX71M supports selection of serial programming functions by means of serial programmer commands. The SPCC register is used to enable serial programming.

When an OCD/serial programmer is connected, the data written in the option-setting memory is used to determine whether or not to accept the connection. A check is performed to determine if the code sent by the OCD/serial programmer matches the ID code in the option-setting memory. The connection to the OCD/serial programmer is enabled if the codes match, but no connection is possible if the codes do not match. The ID code of the OCD/serial programmer is stored in the OSIS register.

## 1.4 Reset Function

#### 1.4.1 Reset Sources

Figure 1.3 lists the reset sources of the SH7216 Group and RX71M.

#### Table 1.3 Reset Sources

| ltem       | SH7216 Group                                                                                                                                                 | RX71M                                                                                                                                                                                                                                                                                                               |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset type | <ul> <li>Power-on reset<br/>(RES# pin reset/H-UDI reset assert<br/>command/WDT overflow)</li> <li>Manual reset<br/>(MRES# pin reset/WDT overflow)</li> </ul> | <ul> <li>RES# pin reset</li> <li>Power-on reset (internal reset)</li> <li>Voltage monitor 0 reset</li> <li>Voltage monitor 1 reset</li> <li>Voltage monitor 2 reset</li> <li>Deep software standby reset</li> <li>Independent watchdog timer reset</li> <li>Watchdog timer reset</li> <li>Software reset</li> </ul> |

#### (1) Reset Vector Configuration

The SH7216 Group has separate vectors for power-on resets and for manual resets (PC and SP).\*1

The RX71M has a single reset vector for multiple reset sources. The reset source is identified in reset status registers 0 to 2 during reset processing, and processing for the corresponding source is performed.

## (2) Stack Pointer

On the SH7216 Group, it is necessary to specify the end address (+1) of the stack area in the reset vector. There is no stack pointer setting area in the vector table on the RX71M, so the stack pointer is set in ISP and USP.

Note 1. See 1.8.4, Vector Configuration, for details of the vector tables.

|                | SH7216 Group                 |            | RX71M              |  |

|----------------|------------------------------|------------|--------------------|--|

| Vector table a | ddress offset                |            |                    |  |

| 0000 0000h     | Vector#0 (Power-on reset PC) |            |                    |  |

| 0000 0004h     | Vector#1 (Power-on reset SP) |            |                    |  |

| 0000 0008h     | Vector#2 (Manual reset PC)   |            |                    |  |

| 0000 000Ch     | Vector#3 (Manual reset SP)   |            |                    |  |

|                |                              |            |                    |  |

| 0000 07FCh     | Vector#511                   | FFFF FFFCh | Reset PC           |  |

|                | Vector table                 |            | Fixed vector table |  |

Figure 1.10 Reset Vector Comparison

## 1.4.2 Reset Sources and Initialization Scope

The initialization scope of the reset sources differs between the SH7216 Group and the RX71M. Table 1.4 lists the reset sources and their initialization scope on the SH7216 Group, and Table 1.5 lists the reset sources and their initialization scope on the RX71M. For details, see the User's Manual: Hardware.

| Table 1.4 | SH7216 Group Reset Sources and Initialization Scope |

|-----------|-----------------------------------------------------|

|-----------|-----------------------------------------------------|

| ltem     |                 | CPU<br>FPU | On-Chip Peripheral Module,<br>I/O Port | WRCSR of WDT,<br>FRQCR of CPG |

|----------|-----------------|------------|----------------------------------------|-------------------------------|

| Power-on | RES# pin reset  | 0          | 0                                      | 0                             |

| reset    | H-UDI command   | 0          | 0                                      | 0                             |

|          | WDT overflow    | 0          | 0                                      |                               |

| Manual   | MRES# pin reset | 0          | *1                                     |                               |

| reset    | WDT overflow    | 0          | *1                                     | —                             |

O: Reset —: No reset

Note 1. The BN bit in IBNR of the INTC is initialized.

## Table 1.5 RX71M Reset Sources and Initialization Scope

|                                                               | Reset Sources     |                   |                               |                                        |                            |                               |                               |                                      |                   |

|---------------------------------------------------------------|-------------------|-------------------|-------------------------------|----------------------------------------|----------------------------|-------------------------------|-------------------------------|--------------------------------------|-------------------|

| Reset Target                                                  | RES# Pin<br>Reset | Power-On<br>Reset | Voltage<br>Monitor 0<br>Reset | Independent<br>Watchdog<br>Timer Reset | Watchdog<br>Timer<br>Reset | Voltage<br>Monitor 1<br>Reset | Voltage<br>Monitor 2<br>Reset | Deep<br>Software<br>Standby<br>Reset | Software<br>Reset |

| Power-on reset<br>detection flag                              | 0                 | _                 | —                             | _                                      |                            | —                             | _                             | _                                    | _                 |

| Cold start/warm start determination flag                      | _                 | 0                 |                               | _                                      | _                          | —                             | _                             |                                      | —                 |

| Voltage monitor 0 reset detection flag                        | 0                 | 0                 | —                             | —                                      |                            | —                             |                               |                                      | —                 |

| Independent<br>watchdog timer reset<br>detection flag         | 0                 | 0                 | 0                             | —                                      | _                          | _                             | _                             | 0                                    | _                 |

| Independent<br>watchdog timer<br>registers                    | 0                 | 0                 | 0                             | _                                      | _                          | _                             | _                             | 0                                    | _                 |

| Watchdog timer reset detection flag                           | 0                 | 0                 | 0                             | 0                                      | _                          | _                             | _                             | 0                                    | _                 |

| Watchdog timer registers                                      | 0                 | 0                 | 0                             | 0                                      | _                          | —                             | —                             | 0                                    | —                 |

| Voltage monitor 1 reset detection flag                        | 0                 | 0                 | 0                             | 0                                      | 0                          | _                             | _                             | _                                    |                   |

| Voltage monitor<br>function 1 registers                       | 0                 | 0                 | 0                             | 0                                      | 0                          | _                             | _                             | *1                                   |                   |

| Voltage monitor 2 reset detection flag                        | 0                 | 0                 | 0                             | 0                                      | 0                          | 0                             | _                             | _                                    | _                 |

| Voltage monitor<br>function 2 registers                       | 0                 | 0                 | 0                             | 0                                      | 0                          | 0                             | _                             | *2                                   |                   |

| Deep software<br>standby reset<br>detection flag              | 0                 | 0                 | 0                             | 0                                      | 0                          | 0                             | 0                             | —                                    | _                 |

| Software reset detection flag                                 | 0                 | 0                 | 0                             | 0                                      | 0                          | 0                             | 0                             | 0                                    |                   |

| Realtime clock<br>registers* <sup>3</sup>                     | —                 | _                 | —                             | _                                      | _                          | —                             |                               |                                      |                   |

| High-speed on-chip<br>oscillator–related<br>registers         | 0                 | 0                 | 0                             | 0                                      | 0                          | 0                             | 0                             | _                                    | 0                 |

| Main clock oscillator-<br>related registers                   | 0                 | 0                 | 0                             | 0                                      | 0                          | 0                             | 0                             |                                      | 0                 |

| Pin states                                                    | 0                 | 0                 | 0                             | 0                                      | 0                          | 0                             | 0                             |                                      | 0                 |

| Low power<br>consumption-related<br>registers* <sup>4</sup>   | 0                 | 0                 | 0                             | 0                                      | 0                          | 0                             | 0                             | _                                    | 0                 |

| Registers other than<br>the above, CPU, and<br>internal state | 0                 | 0                 | 0                             | 0                                      | 0                          | 0                             | 0                             | 0                                    | 0                 |

O: Reset —: No reset

Note 1. Only LVD1CR1 and LVD1SR are initialized.

Note 2. Only LVD2CR1 and LVD2SR are initialized.

Note 3. Some control bits are initialized by all resets.

Note 4. The DPSBKRy registers are not initialized by any reset.

## 1.4.3 Cold/Warm Start Determination Function

On the RX71M it is possible to determine whether the most recent reset processing was caused by a power-on reset (cold start) or by a reset signal during operation (warm start).

When a power-on reset occurs because the external voltage (VCC) has exceeded the threshold, the cold/warm start determination flag (RSTSR1.CWSF) is cleared to 0, indicating a cold start. Since the flag is not cleared to zero by any other type of reset, 1 can be written to it by a program, indicating a warm start.

#### 1.4.4 Write Protection

The RX71M has a register write protection function to protect important registers from being overwritten if program runaway occurs. The software reset register is protected by this function.

If necessary, set protect bit 1 (PRCR.PRC1) to 1 to enable writes before writing to the software reset register.

# 1.5 Clock Settings

#### 1.5.1 Clock Sources

Table 1.6 lists the clock sources of the SH7216 Group and RX71M.

#### Table 1.6Clock Sources

| SH7216 Group                                                                       | RX71M                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oscillator (EXTAL and XTAL) + PLL circuit<br>USB oscillator (USBEXTAL and USBXTAL) | <ul> <li>Main clock oscillator (EXTAL and XTAL) + PLL circuit</li> <li>Subclock oscillator (XCIN and XCOUT)</li> <li>High-speed on-chip oscillator (HOCO) + PLL circuit</li> <li>Low-speed on-chip oscillator (LOCO)</li> <li>IWDT-dedicated on-chip oscillator</li> </ul> |

In the description below, the high-speed on-chip oscillator is referred to as the HOCO and the low-speed on-chip oscillator as the LOCO.

## 1.5.2 Clock Generation Circuit

On the SH7216 Group application of divider settings and oscillation stop detection control are performed in software. On the RX71M a variety of clock control operations are performed in software.

On the RX71M the LOCO operates as the clock source after a reset. The operation of necessary clock sources and PLL circuits other than the LOCO is started during system initialization, and various clocks are selected, such as the system clock and bus clocks. When making changes to clock-related settings, it is necessary to consider the register setting sequence and the oscillation and clock oscillation stabilization time.

See the following application note for details of the clock setting procedure.

RX71M Group Initial Settings (R01AN2459EJ)

## 1.5.3 Write Protection

The RX71M has a register write protection function to protect important registers from being overwritten if program runaway occurs, and the registers related to the clock generation circuit are protected by this function.

If necessary, set protect bit 0 (PRCR.PRC0) or protect bit 1 (PRCR.PRC1) to 1 to enable writes before writing to these registers.

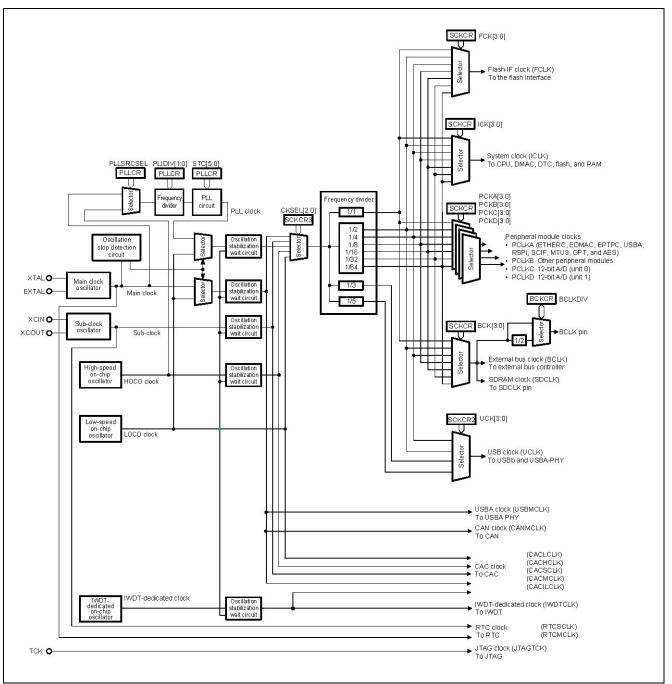

Figure 1.11 RX71M Block Diagram of Clock Generation Circuit

# 1.6 Operation Modes

# 1.6.1 Comparison of Operation Modes

Table 1.7 shows a comparison of the operation modes of the SH7216 Group and RX71M.

For details of each operation mode, see the User's Manual: Hardware.

| SH7216 Group                             | RX71M                                | Description                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCU extension<br>mode 0<br>MCU extension | On-chip ROM disabled extended mode   | An operation mode in which the on-chip ROM is disabled<br>and the external address space is enabled. The external<br>bus width differs from that of mode 0 and mode 1 on the                                                                                                                                                                    |

| mode 1                                   |                                      | SH7216 Group.                                                                                                                                                                                                                                                                                                                                   |

| MCU extension mode 2                     | On-chip ROM enabled<br>extended mode | An operation mode in which the on-chip ROM is enabled and the external address space is enabled                                                                                                                                                                                                                                                 |

| Single-chip mode                         | Single-chip mode                     | An operation mode in which the external address space is disabled                                                                                                                                                                                                                                                                               |

| Boot mode                                | Boot mode<br>(SCI interface)         | An operation mode in which the on-chip flash memory<br>modifying program (boot program), which is stored in a<br>dedicated area internal to the microcontroller, is run.<br>The on-chip ROM can be programmed by a device<br>external to the microcontroller by using the asynchronous<br>serial interface.                                     |

| USB boot mode                            | Boot mode<br>(USB interface)         | An operation mode in which the on-chip flash memory<br>modifying program (boot program), which is stored in a<br>dedicated area internal to the microcontroller, is run.<br>The on-chip ROM (code flash memory) can be<br>programmed by a device external to the microcontroller<br>by using the USB interface.                                 |

| User boot mode                           | User boot mode                       | An operation mode in which the on-chip flash memory<br>modifying program (user boot program), which is stored<br>in a dedicated area internal to the microcontroller, is run.<br>The user MAT can be programmed by using a user-<br>defined interface.<br>Transition to this mode is possible after a reset is<br>canceled.                     |

| User program mode                        |                                      | An operation mode in which the on-chip flash memory<br>modifying program (user boot program), which is stored<br>in a dedicated area internal to the microcontroller, is run.<br>The user MAT can be programmed by using a user-<br>defined interface.<br>Transition to this mode is possible from MCU extension<br>mode 2 or single-chip mode. |

Table 1.7

Comparison of Operation Modes

# 1.6.2 Comparison of Memory

Figure 1.12 shows a comparison of memory maps in on-chip ROM enabled mode.

|                          | SH7216<br>MCU extension mode 2 |                          | RX71M on-chip ROM enabled extended mode              |

|--------------------------|--------------------------------|--------------------------|------------------------------------------------------|

| 0000 0000h               | On-chip flash memory           | 0000 0000h               | On-chip RAM                                          |

| 0010 0000h               | Reserved area                  | 0008 0000h<br>000A 4000h | Peripheral I/O registers<br>Standby RAM              |

| 0040 2000h               | FCU firmware area              | 000A 6000h               | Peripheral I/O registers                             |

| 0040 4000h               | Reserved area                  | 0010 0000h               | On-chip ROM<br>(data flash memory)                   |

| 0200 0000h               | CS0 area                       | 0011 0000h<br>0012 0040h | Reserved area<br>On-chip ROM (option-setting memory) |

| 0400 0000h               | CS1 area                       | 0012 0070h<br>007E 0000h | Reserved area On-chip ROM (dedicated for programming |

| 0800 0000h               |                                | 007F 0000h<br>007F 8000h | Reserved area<br>FCU-RAM area                        |

| 0C00 0000h               | CS2 area                       | 007F 9000h               | Reserved area                                        |

| 1000 0000h               | CS3 area                       | 007F E000h               | Peripheral I/O registers                             |

|                          | CS4 area                       | 0080 0000h               | Reserved area                                        |

| 1400 0000h               | CS5 area                       | 00FF 8000h               | ECC-RAM area                                         |

| 1800 0000h               | CS6 area                       | 0100 0000h               |                                                      |

| 1C00 0000h               | CS7 area                       |                          | External address space<br>(CS area)                  |

| 2000 0000h               | Reserved area                  |                          |                                                      |

| 8010 0000h               | Data flash                     | 0800 0000h               | External address space                               |

| 8010 8000h               | Reserved area                  | 1000 0000h               | (SDRAM area)                                         |

| 80FF 8000h               | FCURAM                         |                          |                                                      |

| 80FF A000h               | Reserved area                  |                          | Reserved area                                        |

| FFF8 0000h               | On-chip RAM                    | FEFF F000h               | On-chip ROM                                          |

| FFFA 0000h               | Reserved area                  | FF00 0000h               | (FCU firmware)                                       |

| FFFC 0000h               | BSC, UBC, Etherc, etc.         | FF7F 8000h               | Reserved area<br>On-chip ROM                         |

| FFFD 0000h               |                                | FF80 0000h               | (user boot)<br>Reserved area                         |

|                          | Reserved area                  | FFC0 0000h               | On-chip ROM                                          |

| FFFE 0000h<br>FFFF FFFFh | Peripheral I/O                 | FFFF FFFFh               | (program ROM)                                        |

Figure 1.12 Memory Map Comparison (On-Chip ROM Enabled Mode)

Figure 1.13 shows a comparison of memory maps in single-chip mode.

|                                        | SH7216 single-chip mode                                                 |                                        | RX71M single-chip mode                                                         |

|----------------------------------------|-------------------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------|

| 0000 0000h                             | On-chip flash memory                                                    | 0000 0000h                             | On-chip RAM                                                                    |

| 0010 0000h                             | Reserved area                                                           | 0008 0000h                             | Peripheral I/O registers                                                       |

|                                        | Reserved area                                                           | 000A 4000h                             | Standby RAM                                                                    |

| 0040 2000h                             | FCU firmware area                                                       | 000A 6000h                             | Peripheral I/O registers                                                       |

|                                        | FCO IIIIiware area                                                      | 0010 0000h                             | On-chip ROM                                                                    |

| 0040 4000h                             |                                                                         |                                        | (data flash memory)                                                            |

|                                        |                                                                         | 0011 0000h                             | Reserved area                                                                  |

|                                        |                                                                         | 0012 0040h                             | On-chip ROM (option-setting memory)                                            |

|                                        |                                                                         | 0012 0070h                             | Reserved area                                                                  |

|                                        |                                                                         | 007E 0000h                             | On-chip ROM (dedicated for programming                                         |

|                                        |                                                                         | 007F 0000h                             | Reserved area                                                                  |

|                                        |                                                                         | 007F 8000h                             | FCU-RAM area                                                                   |

|                                        |                                                                         | 007F 9000h                             |                                                                                |

|                                        |                                                                         |                                        | Reserved area                                                                  |

|                                        | Reserved area                                                           | 007F E000h                             | Peripheral I/O registers                                                       |

|                                        |                                                                         | 0080 0000h                             | Reserved area                                                                  |

|                                        |                                                                         | 00FF 8000h                             | ECC-RAM area                                                                   |

|                                        |                                                                         |                                        |                                                                                |

| 8010 0000h                             | Data flash                                                              |                                        | Reserved area                                                                  |

| 8010 8000h                             | Reserved area                                                           |                                        | Reserved area                                                                  |

| 80FF 8000h                             | FCURAM                                                                  |                                        |                                                                                |

|                                        |                                                                         |                                        |                                                                                |

| 80FF A000h                             | Reserved area                                                           |                                        |                                                                                |

| 80FF A000h<br>FFF8 0000h               |                                                                         |                                        |                                                                                |

| FFF8 0000h                             | Reserved area                                                           | FEFF F000h                             | On-chip ROM<br>(ECU firmware)                                                  |

|                                        | Reserved area                                                           |                                        | (FCU firmware)                                                                 |

| FFF8 0000h<br>FFFA 0000h               | Reserved area<br>On-chip RAM                                            | FF00 0000h                             | (FCU firmware)<br>Reserved area                                                |

| FFF8 0000h                             | Reserved area<br>On-chip RAM                                            |                                        | (FCU firmware)<br>Reserved area<br>On-chip ROM                                 |

| FFF8 0000h<br>FFFA 0000h<br>FFFC 0000h | Reserved area<br>On-chip RAM<br>Reserved area                           | FF00 0000h<br>FF7F 8000h               | (FCU firmware)<br>Reserved area<br>On-chip ROM<br>(user boot)                  |

| FFF8 0000h<br>FFFA 0000h               | Reserved area<br>On-chip RAM<br>Reserved area<br>BSC, UBC, Etherc, etc. | FF00 0000h<br>FF7F 8000h<br>FF80 0000h | (FCU firmware)<br>Reserved area<br>On-chip ROM                                 |

| FFF8 0000h<br>FFFA 0000h<br>FFFC 0000h | Reserved area<br>On-chip RAM<br>Reserved area                           | FF00 0000h<br>FF7F 8000h               | (FCU firmware)<br>Reserved area<br>On-chip ROM<br>(user boot)<br>Reserved area |

| FFF8 0000h<br>FFFA 0000h<br>FFFC 0000h | Reserved area<br>On-chip RAM<br>Reserved area<br>BSC, UBC, Etherc, etc. | FF00 0000h<br>FF7F 8000h<br>FF80 0000h | (FCU firmware)<br>Reserved area<br>On-chip ROM<br>(user boot)                  |

Figure 1.13 Memory Map Comparison (Single-Chip Mode)

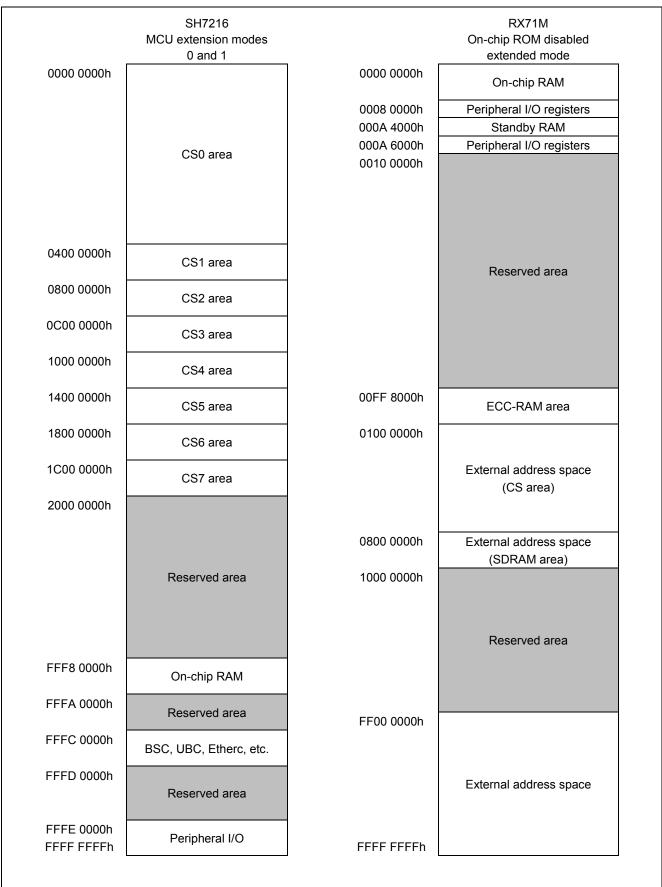

Figure 1.14 shows a comparison of memory maps in on-chip ROM disabled mode.

Figure 1.14 Memory Map Comparison (On-Chip ROM Disabled Mode)

- On the RX71M the RAM is allocated to addresses adjacent to 0000 0000h and ROM (for reading data) to addresses adjacent to FFFF FFFFh.

- On the RX71M the peripheral I/O registers are allocated within the address range from 0008 0000h to 000A 3FFFh and 000A 6000h to 000F FFFFh, and only the flash-related registers are allocated within the address range from 007F E000h to 007F FFFFh.

- On the RX71M the external address space is allocated within the address ranges from 0100 0000h to 0FFF FFFFh and FF00 0000h to FFFF FFFFh, and configured as up to eight CS spaces of 16 MB each and a 128 MB SDRAM space. In on-chip ROM enabled extended mode the CS0 area from FF00 0000h to FFFF FFFFh is disabled.

## 1.6.3 Operation Mode Settings

Whereas on the SH7216 Group operation mode settings are made only with the MD1, MD0, and FWE pins, on the RX71M operation mode settings can be made by means of the MD and UB pins when a reset is canceled, or by software after a reset is canceled.

Table 1.8 lists the operation modes that are determined by pin settings, and Table 1.9 lists the operation modes that are set in software after a reset is canceled.

| Pin  |      |                           |  |

|------|------|---------------------------|--|

| MD   | UB   | Mode Name                 |  |

| High |      | Single-chip mode          |  |

| Low  | Low  | Boot mode (SCI interface) |  |

|      | High | Boot mode (USB interface) |  |

|      |      | User boot mode            |  |

#### Table 1.8 Pin Settings and Operation Modes on RX71M

#### Table 1.9 SYSCR0 Register Settings and Operation Modes on RX71M

| EXBE Bit                    | Mode Name                                                                                        |  |

|-----------------------------|--------------------------------------------------------------------------------------------------|--|

| 0 (external bus disabled)   | Single-chip mode, user boot mode                                                                 |  |

| 0 (external bus disabled)*2 |                                                                                                  |  |

| 1 (external bus enabled)    | On-chip ROM disabled extended mode                                                               |  |

| 1 (external bus enabled)    | On-chip ROM enabled extended mode                                                                |  |

|                             | 0 (external bus disabled)<br>0 (external bus disabled)* <sup>2</sup><br>1 (external bus enabled) |  |

Note 1. Once the ROME bit is cleared to 0 it cannot be set to 1 again.

Note 2. After the STSCR0 register is reset, ROME = 1 and EXBE = 0.

## 1.6.4 Write Protection

The RX71M has a register write protection function to protect important registers from being overwritten if program runaway occurs, and the operation mode–related registers are protected by this function.

If necessary, set protect bit 1 (PRCR.PRC1) to 1 to enable writes before writing to these registers.

# 1.7 Processor Modes

The RX71M supports two processing modes: supervisor mode and user mode. These processor modes enable hierarchical CPU resource protection.

| Table 1.10 | RX71M | Processor | Modes |

|------------|-------|-----------|-------|

|------------|-------|-----------|-------|

| Processor Modes | Transition Conditions                                                                                                                                                                                                                                                    | Outline                                                                                                                                                                                                                                                 |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Supervisor mode | <ul> <li>Reset cancellation</li> <li>Exception occurrence<br/>(PSW.PM bit cleared to 0)</li> </ul>                                                                                                                                                                       | All CPU resources are accessible, and all<br>instructions can be executed (no limitations)<br>This is the mode in which the OS and other<br>system programs ordinarily operate.                                                                         |  |

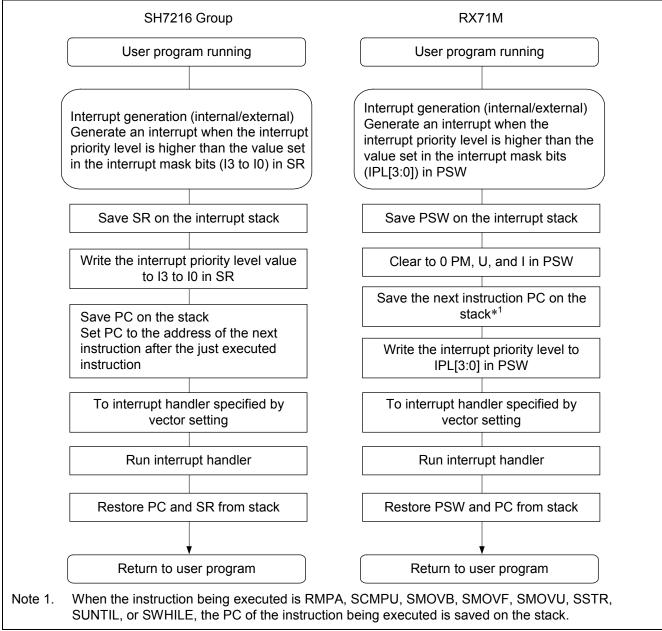

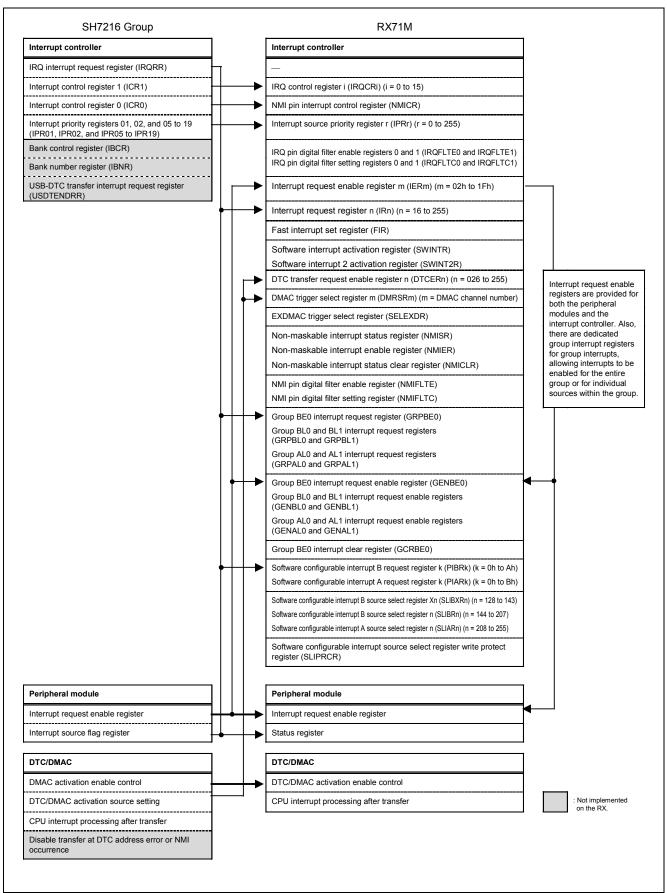

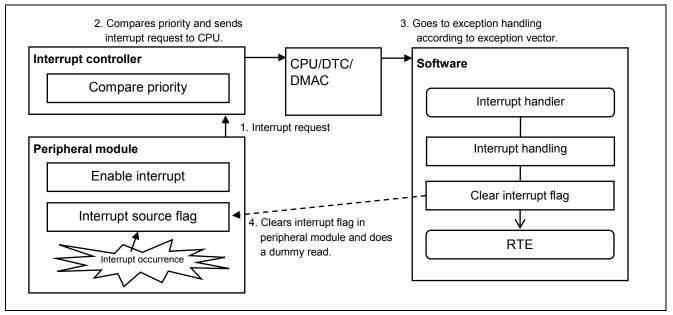

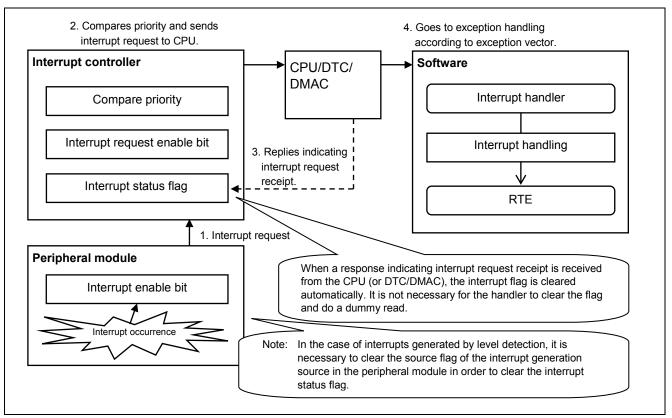

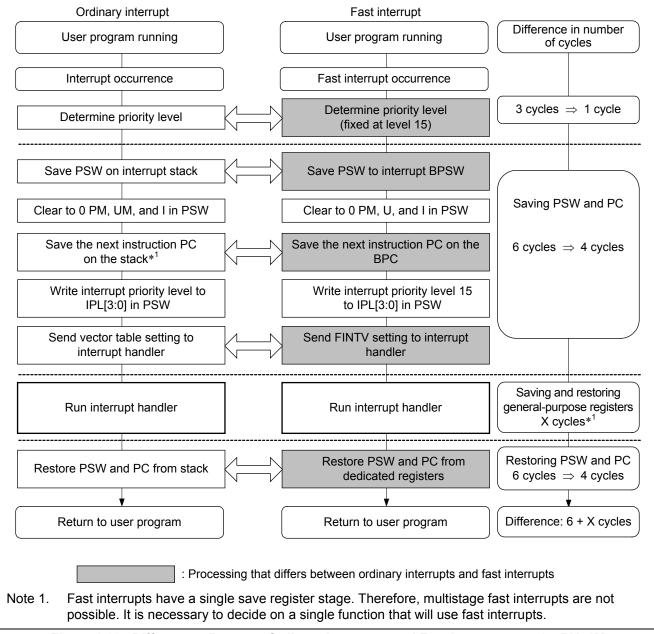

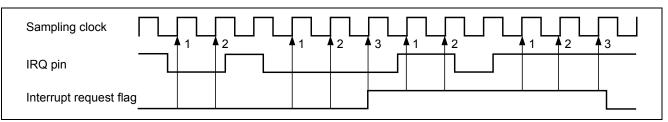

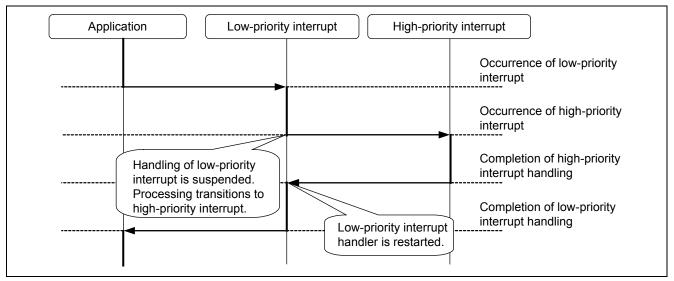

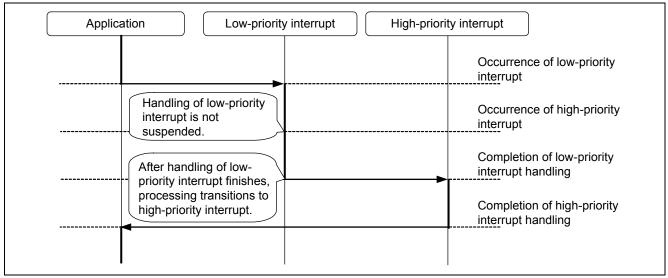

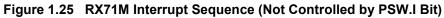

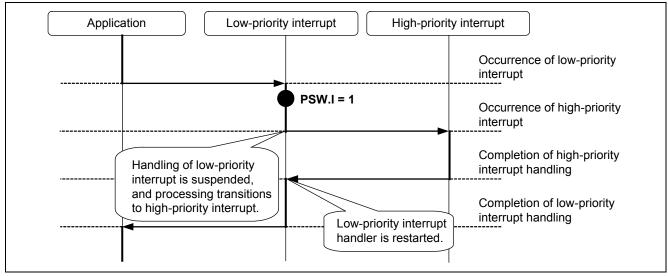

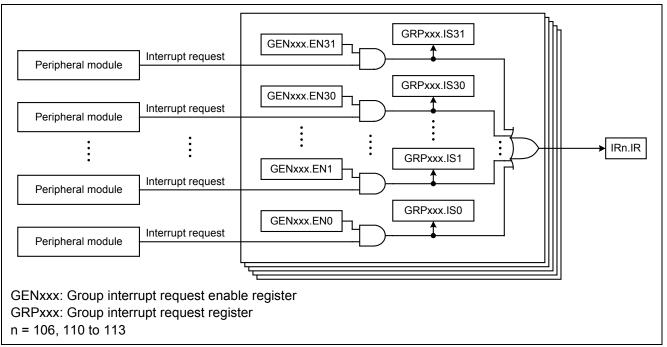

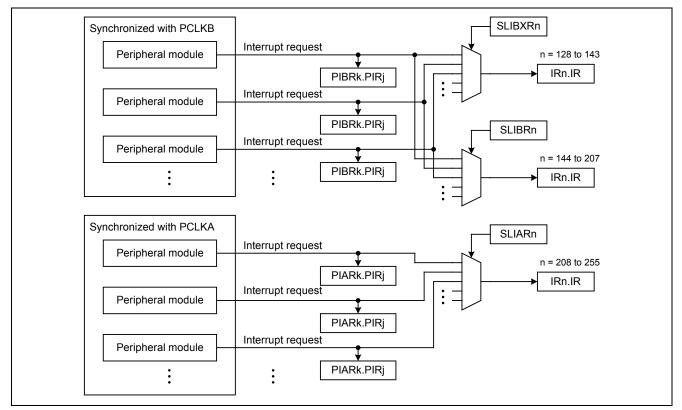

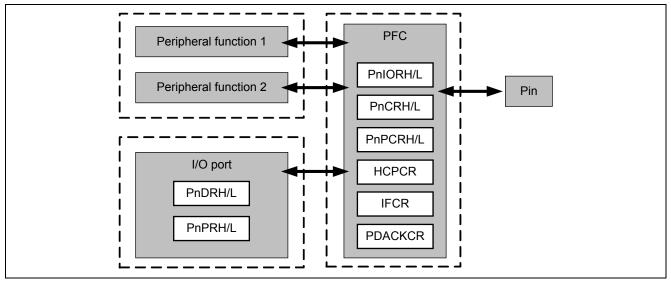

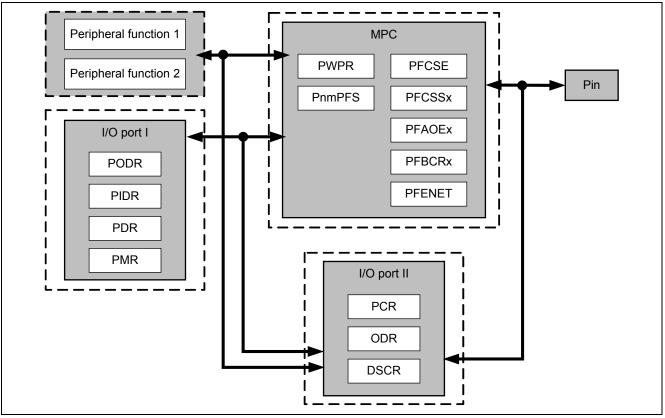

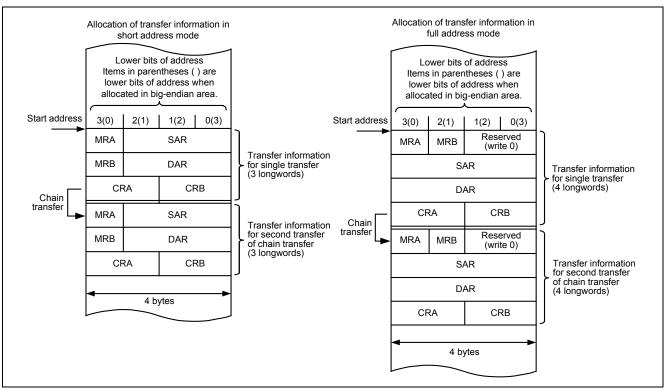

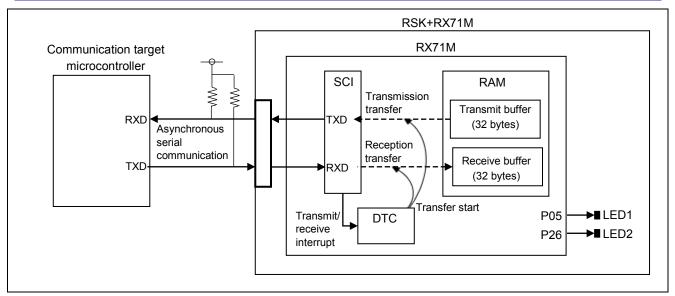

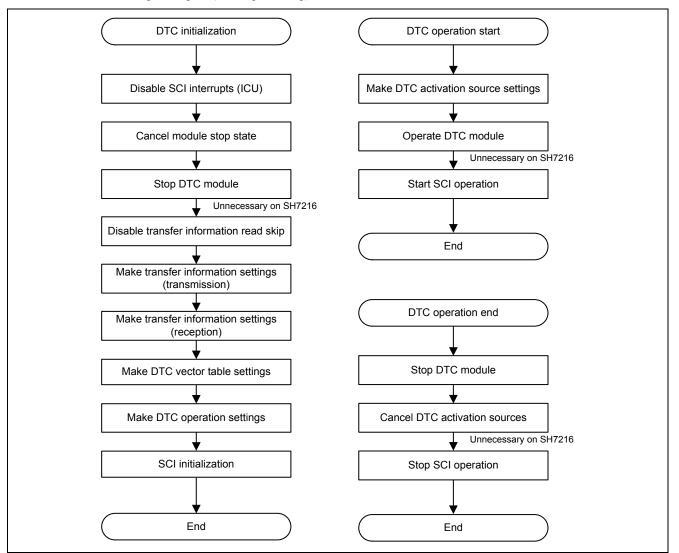

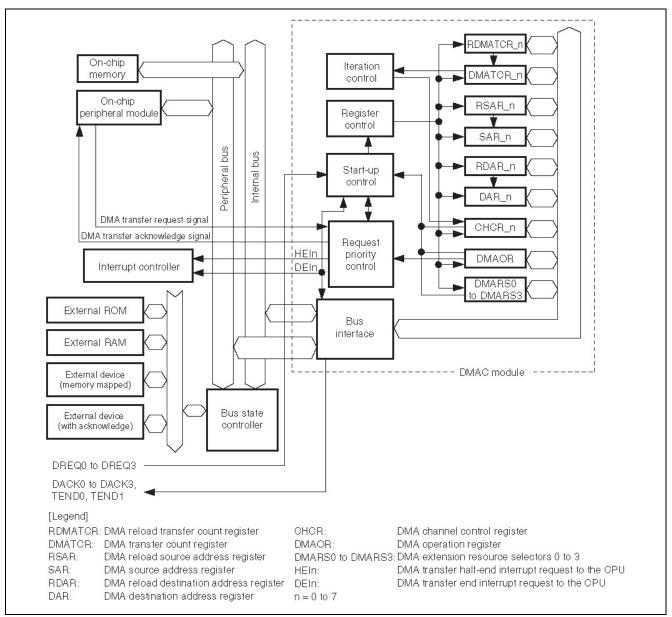

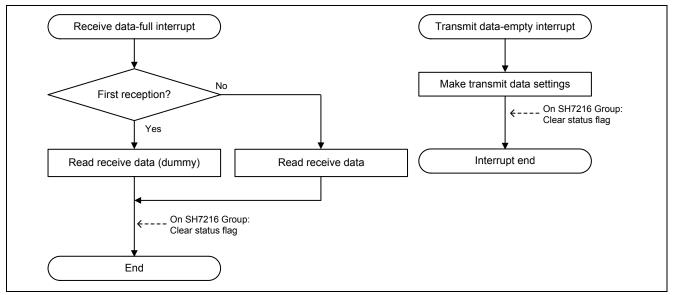

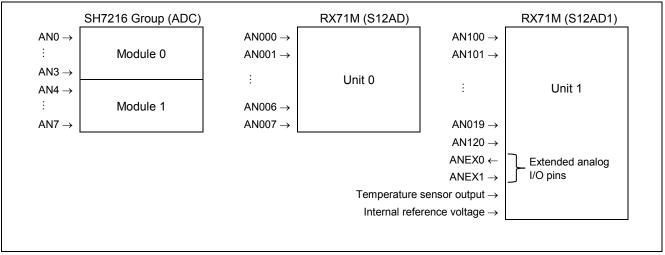

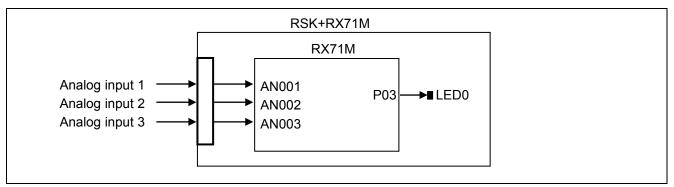

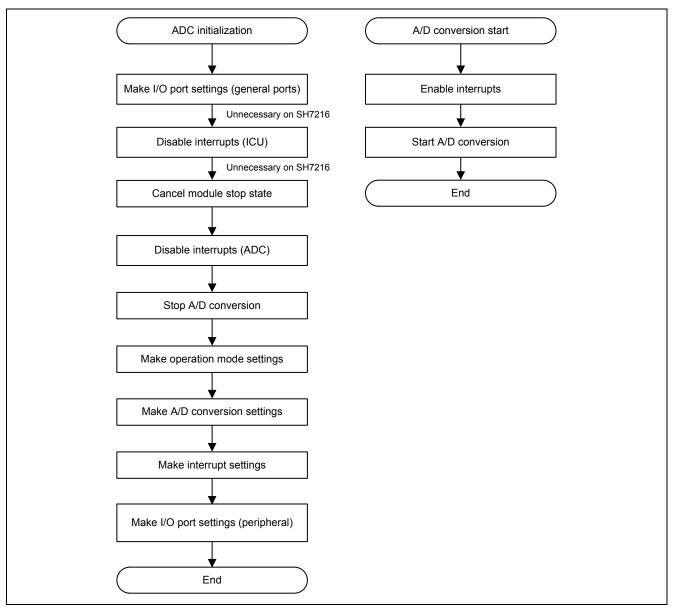

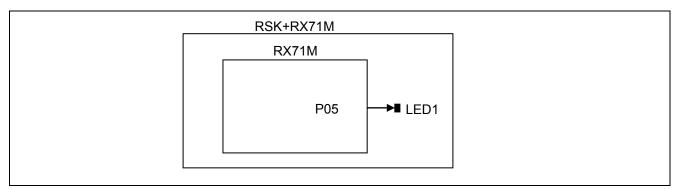

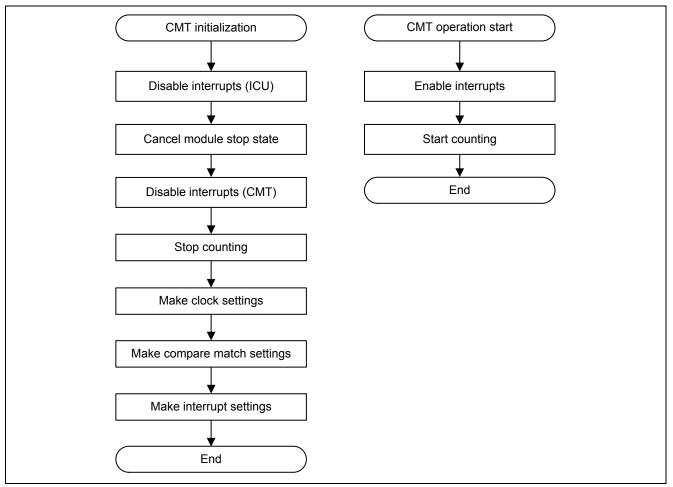

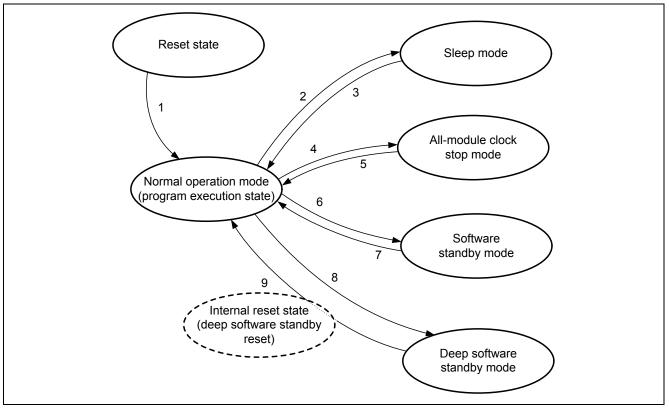

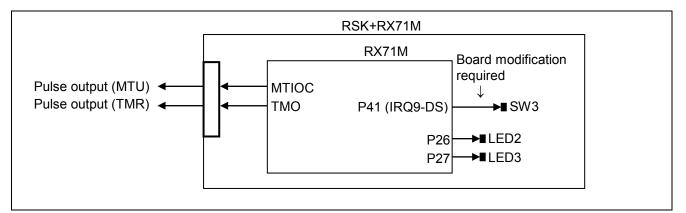

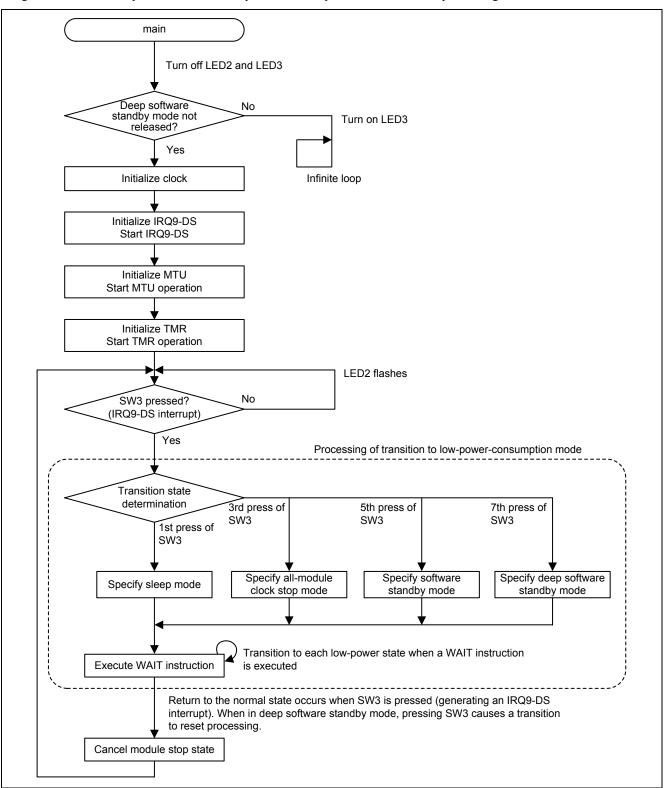

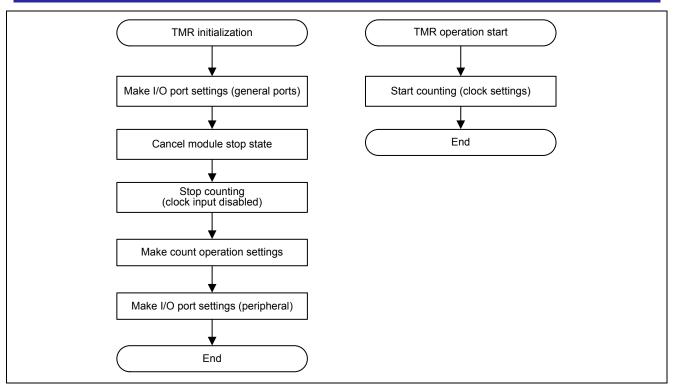

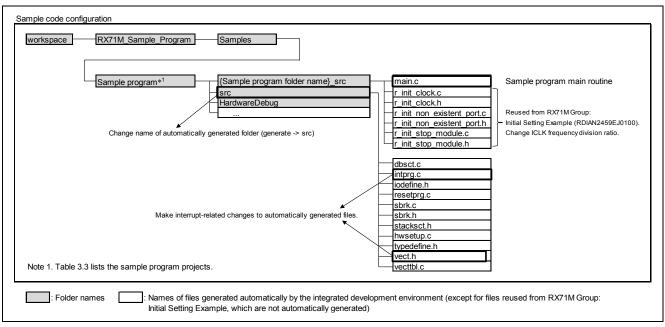

|                 | When an exception occurs a transition to supervisor mode takes place, but the processor mode preceding the exception is restored following return from the exception handler.                                                                                            |                                                                                                                                                                                                                                                         |  |