# **RX Family**

R01AN3361EJ0100 Rev.1.00 Aug 10, 2016

# RAM Soft Error Diagnosis Example

# Introduction

This document explains a static RAM soft error diagnosis based on a doubly RAM access method and a bit operation.

# **Target Device**

This example supports the following device.

- RX64M Group

- RX71M Group

When using this application note with other Renesas MCUs, careful evaluation is recommended after making modifications to comply with the alternate MCU.

# Contents

| 1. O       | verview                                                 | . 4 |

|------------|---------------------------------------------------------|-----|

| 1.1        | RAM Soft Error Diagnosis Example                        | . 4 |

| 1.2        | Related documents                                       | . 4 |

| 1.3        | Hardware Structure                                      | . 5 |

| 1.4        | Software Structure                                      | . 5 |

| 1.5        | File Structure                                          | . 6 |

| 1.6        | Outline of Functions                                    | . 7 |

| 2. Fi      | unctional Information                                   | . 8 |

| 2.1        | Hardware Requirements                                   | . 8 |

| 2.2        | Hardware Resource Requirements                          | . 8 |

| 2.3        | Software Requirements                                   | . 8 |

| 2.4        | Limitations                                             | . 8 |

| 2.5        | Supported Toolchains                                    | . 8 |

| 2.6        | Header Files                                            | . 8 |

| 2.7        | Integer Types                                           | . 8 |

| 2.8        | Configuration Overview                                  | . 9 |

| 2.9        | Data Structures1                                        | 10  |

| 2.10       | Return Values1                                          | 11  |

| 3. SI      | pecification of This Example                            | 12  |

| 3.1        | Environment and Execution                               |     |

| 3.2        | Operation Sequence                                      |     |

| 3.3        | Reducing Biased Data1                                   |     |

| 3.4        | Performance of Safety Data Access (Measurement Example) |     |

| 3.5        | Software Operation Flow                                 |     |

| 3.6        | Board Setting                                           |     |

| 4          |                                                         |     |

|            | PI Functions                                            |     |

| 4.1<br>4.2 | FlashInit ()                                            |     |

| 4.2<br>4.3 | load_seed ()                                            |     |

| 4.3<br>4.4 | crt_bitpat ()                                           |     |

| 4.4<br>4.5 | load_bitpat ()                                          |     |

| 4.6        | upd_bitpat ()                                           |     |

| 4.0        | ers_bitpat ()                                           |     |

| 4.7        | exec_bitop ()                                           |     |

| 4.8<br>4.9 | RAM_Init ()                                             |     |

|            | RAM_Write ()                                            |     |

|            | RAM_SafetyWrite ()                                      |     |

| 4.11       |                                                         | זכ  |

| 4.    | 12 RAM_Read ()       | 39   |

|-------|----------------------|------|

| 4.    | 13 RAM_SafetyRead () | 40   |

|       |                      |      |

| 5.    | Reference Documents  | . 41 |

| Weh   | osite and Support    | 41   |

| VV CL |                      |      |

# 1. Overview

Recently, a soft error of the static RAM (hereafter, SRAM) has become an un-negligible problem proportional to increasing memory capacity and more detailed process scale. The soft error induces inversing bit values of the SRAM memory and is probabilistic phenomena due to alpha particles included as the impurity of package and neutron beams radiated from the cosmic rays.

This document explains the SRAM soft error diagnosis based on a doubly RAM access method (hereafter, double RAM operation [1]) and a bit operation. The bit operation is executed a user's safety data with random (or sequential, constant) bit pattern stored on the Data Flash Memory. Thereafter, those operated data are written in the double RAM area. The bit operation to which applied is exclusive OR makes balance the number of 0's and 1's [2]. As the result, it can be easy to detect 0 or 1 fixed error and enhanced the error detection rate. The bit pattern itself is also applied to the double RAM method for safety viewpoint when it is updated.

This example is released to the project form using plural firmware integration technology (FIT) modules.

# 1.1 RAM Soft Error Diagnosis Example

This example is implemented in a project and used as the application example of SRAM soft error diagnosis using plural FIT modules.

# 1.2 Related documents

[1] Functional safety of electrical/electronic/programmable electronic safety-related systems, IEC61508, Edition 2.0, Apr, 2010

[2] Measurement and Reporting of Alpha Particle and Terrestrial Cosmic Ray-Induced Soft Errors in Semiconductor

Devices, JESD89A, Oct 2006, JEDEC Solid State Technology Association.

[3] RX Family Board Support Package Module Using Firmware Integration Technology, Rev.3.31, Document No. R01AN1685EJ0331, May 19, 2016

[4] RX Family Flash Module Using Firmware Integration Technology, Rev.1.60, Document No. R01AN2184EU0160, Nov 17, 2015

[5] RX Family Open Source FAT File System [M3S-TFAT-Tiny] Module Firmware Integration Technology, Rev.3.02, Document No. R20AN0038EJ0302, Mar 01, 2015

[6] Renesas USB MCU USB Basic Host and Peripheral Driver Using Firmware Integration Technology, Rev.1.11,

Document No. R01AN2025EJ0111, Sep 30, 2015

[7] Renesas USB MCU USB Host Mass Storage Class Driver (HMSC) Using Firmware Integration Technology,

Rev.1.11, Document No. R01AN2026EJ0111, Sep 30, 2015

[8] RX64M Group Renesas Starter Kit+ User's Manual For e<sup>2</sup> studio, Rev. 1.10, Document No. R20UT2593EG0110, Jun 25, 2015

[9] RX71M Group Renesas Starter Kit+ User's Manual, Rev. 1.00, Document No. R20UT3217EG0100, Jan 23, 2015

# 1.3 Hardware Structure

This example uses the RAM and Data Flash Memory peripheral modules of the RX64M/71M. As for the RAM, the without ECC error area is only target of this sample and with ECC area is out of scope.

In detail, please refer to RX64M/71M Group User's Manual: Hardware.

# 1.4 Software Structure

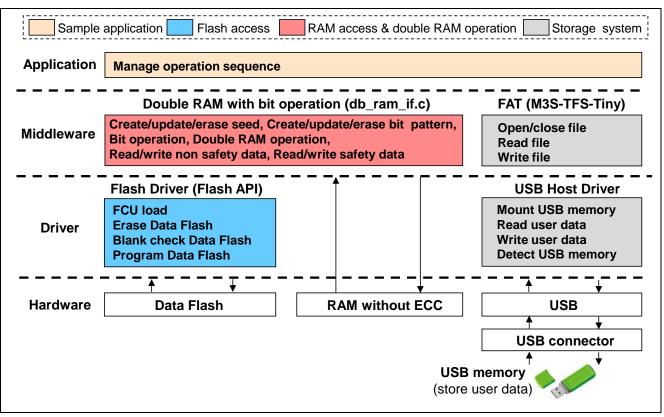

This sample is operations example of the application and middleware layer using the plural FIT modules whose common initial setting are supplied by a Board Support Package [3]. Figure 1.1 shows the typical structure and functional overview of the software. The application manages the operation sequence composed of the Data Flash access, the RAM without ECC part access, the double RAM operation and USB memory access storage system. The double RAM with bit operation (db\_ram.c) creates/update/erases an initial value to create random number (hereafter, seed) and a bit pattern, does the bit operation to user data with bit pattern, does the double RAM operation, reads/writes non safety data, and reads/writes safety data. The flash driver (Flash API) [4] erases/writes the seed and the bit pattern from/to the Data Flash. The FAT file system (M3S-TFAT-Tiny) [5] manages the data<sup>1</sup> in the USB memory as the file using the USB Host driver<sup>2</sup>. The USB Host driver [6], [7] accesses the USB memory as the logical block unit.

<sup>1</sup> Assume the safe data transferred from the USB memory is guaranteed

<sup>2</sup>Diagnosis of the USB Host driver is out of scope

Figure 1.1 Software structure of this sample

# 1.5 File Structure

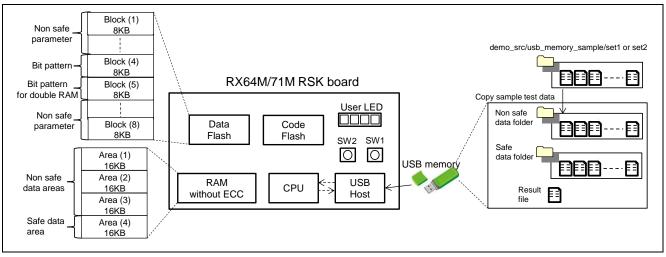

This sample codes are stored the "demo\_src" and lower hierarchical folders. Figure 1.2 shows the source and header file structures of this sample. The two set samples of non safety and safety data are stored in the USB memory. As for the detailed information of the FIT based modules (BSP, Flash Driver, FAT file system and USB Drivers), please refer to the documentation of the each FIT module.

| demo_src: main operation                                 | r_bsp: BSP (Board Support Package) FIT module               |

|----------------------------------------------------------|-------------------------------------------------------------|

| sample main.c                                            | 1_bsp. bor (board Support ackage) in module                 |

| sample_main.h                                            | r_config: configuration setting of FIT modules              |

|                                                          | r_bsp_config.h                                              |

| + db ram: Double RAM with bit operation                  |                                                             |

|                                                          | r_bsp_interrupt_config.h                                    |

| db_ram.c                                                 | r_flash_rx_config.h                                         |

| db_ram.h                                                 | r_usb_basic_config.h                                        |

|                                                          | r_usb_hmsc_config.h                                         |

| + tfat_if: File system IF to USB driver                  |                                                             |

| file_if.c                                                | r_flash_rx: Flash Driver (Flash API) FIT module             |

| file_if.h                                                |                                                             |

| r_data_file.c                                            | r_tfat_rx: FAT file system (M3S-TFS-Tiny) FIT module        |

| r_data_file.h                                            | <pre>r_tfat_lib.h ;FAT library header file</pre>            |

| <pre>r_tfat_drv_if.c ;USB driver interface</pre>         | + lib: FAT library stored folder                            |

|                                                          | r_mw_version.h; middleware version information              |

| + usb_if: USB Host memory access control                 | r_stdint.h ; integer type definition                        |

| r_usb_hmsc_defep.c                                       | tfat_rx600_big.lib ; big endian                             |

| usb_memory_access.c                                      | tfat_rx600_little.lib ; little endian                       |

|                                                          |                                                             |

| + usr: LED control                                       |                                                             |

| l led.c                                                  | r usb basic: USB driver (USB basic operation) FIT module    |

| l led.h                                                  |                                                             |

|                                                          | r usb hmsc: USB driver (Host Mass Storage Class) FIT module |

| + usb_memory_sample: Sample of USB memory data           |                                                             |

| + set1, set2; two set samples                            |                                                             |

| + NON: SRC_X.txt ; Non safety data file (X = 1,2,3)      |                                                             |

| + SAFE: SRC_X.txt; Safety data file (X = $0,1,2,3,4,5$ ) | - C 7)                                                      |

| +                                                        | ,0,1)                                                       |

|                                                          |                                                             |

Figure 1.2 File structure of this example

# **1.6 Outline of Functions**

The functions of application layer shows Table 1.1 and the API functions related to the double RAM with bit operation shows Table 1.2.

| Item               | Contents                                             |  |  |  |  |

|--------------------|------------------------------------------------------|--|--|--|--|

| main()             | Main operation of this project.                      |  |  |  |  |

| led_init()         | Initialize user LED.                                 |  |  |  |  |

| led_ctrl()         | Update user LED pattern.                             |  |  |  |  |

| prm_init()         | Initialize operation parameter.                      |  |  |  |  |

| usb_memory_start() | USB memory task start.                               |  |  |  |  |

| Sample_Task()      | Sample application task.                             |  |  |  |  |

| file_start()       | USB memory start.                                    |  |  |  |  |

| file_read()        | File reading operation.                              |  |  |  |  |

| file_write()       | File writing operation.                              |  |  |  |  |

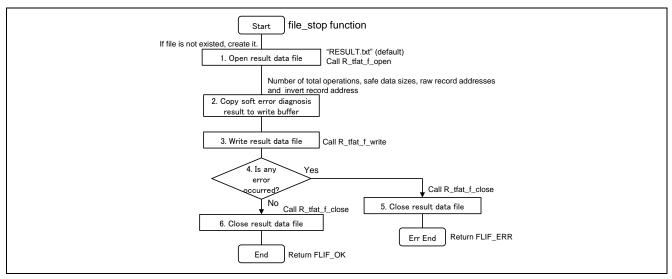

| file_stop()        | File finalizing and operation result save operation. |  |  |  |  |

| file_err()         | File error retrieval operation.                      |  |  |  |  |

| Item              | Contents                                                    |  |  |  |  |  |

|-------------------|-------------------------------------------------------------|--|--|--|--|--|

| FlashInit()       | Initialize flash driver (flash API).                        |  |  |  |  |  |

| load_seed()       | Load seed from data flash.                                  |  |  |  |  |  |

| upd_seed()        | Update seed to data flash.                                  |  |  |  |  |  |

| crt_bitpat()      | Create bit pattern data.                                    |  |  |  |  |  |

| load_bitpat()     | Load bit pattern from data flash with double RAM operation. |  |  |  |  |  |

| upd_bitpat()      | Update bit pattern to data flash with double RAM operation. |  |  |  |  |  |

| ers_bitpat()      | Erase bit pattern from data flash.                          |  |  |  |  |  |

| exec_bitop()      | Execute bit operation.                                      |  |  |  |  |  |

| RAM_Init()        | Initialize RAM.                                             |  |  |  |  |  |

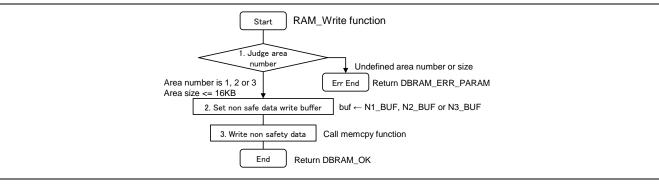

| RAM_Write()       | Write non safety data to RAM.                               |  |  |  |  |  |

| RAM_SafetyWrite() | Write safety data to RAM.                                   |  |  |  |  |  |

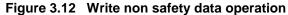

| RAM_Read()        | Read non safety data from RAM.                              |  |  |  |  |  |

| RAM_SafetyRead()  | Read safety data from RAM.                                  |  |  |  |  |  |

# 2. Functional Information

This example is developed by the following principles.

#### 2.1 Hardware Requirements

This example requires your MCU supports the following feature:

- RAM<sup>1</sup>

- Data Flash

- USB

<sup>1</sup>without ECC error correction only use.

#### 2.2 Hardware Resource Requirements

This section details the hardware peripherals that this example requires. Unless explicitly stated, these resources must be reserved for the following driver, and the user cannot use them.

#### 2.2.1 RAM

This example uses the SRAM without ECC error correction to store non safety data and bit operated safety data.

#### 2.2.2 Data Flash

This example uses the Data Flash to store the seed and the bit pattern.

#### 2.2.3 USB Channel

This example uses the USB 2.0 FS Host/Function Module to read test data from the USB memory and write operation result data to the USB memory.

#### 2.3 Software Requirements

This example depends on the following packages (FIT modules):

- r\_bsp

- r\_flash\_rx

- r\_tfat\_rx

- r\_usb\_basic

- r\_usb\_hmsc

#### 2.4 Limitations

There are following limitations in this example:

- Diagnosis of USB driver is out of scope in this example.

- Assumption the safe data transferred from USB is guaranteed.

#### 2.5 Supported Toolchains

This example is tested and works with the following toolchain:

• Renesas RX Toolchain v2.04.01

#### 2.6 Header Files

Each function call is accessed by including a single file, *sample\_main.h*, *led.h*, *file\_if.h*, *r\_usb\_basic\_if.h* db\_ram.h or *r\_frash\_rx\_if.h* which is supplied with this project code.

#### 2.7 Integer Types

This project uses ANSI C99. These types are defined in *stdint.h.*

# 2.8 Configuration Overview

The configuration options in this project are specified in *sample\_main.h*, *db\_ram.h* and *r\_data\_file.h*. The option names and setting values are listed in the table below.

|                                                                                                                             | Configuration options                                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| #define NUM_REQ<br>- Default value = 8                                                                                      | Specify the total number of safety data record (equal to double RAM operation times).<br>- Set 1 to 8 in this example.                                                                                                                                      |

| <pre>#define MAX_DAT_SIZE - Default value = 16*1024</pre>                                                                   | Maximum size of testdata file.<br>- Set 16*1024 (=16KB) in this example.                                                                                                                                                                                    |

| #define READ_DIR_NON<br>- Default value "NON"                                                                               | String of no safety test data directory.                                                                                                                                                                                                                    |

| <pre>#define READ_DIR_SAFE - Default value "SAFE"</pre>                                                                     | String of safety test data directory.                                                                                                                                                                                                                       |

| #define READ_FILE<br>- Default value "SRC"                                                                                  | The header string of test data file name.<br>This string is concatenated the file number assigned access area and<br>the file extension equal to ".txt".<br>Ex. "SRC_0.txt", "SRC_1.txt", "SRC_7.txt"                                                       |

| <pre>#define WRITE_DIR_NCMP - Default value "NCMP"</pre>                                                                    | String of no safety operated data directory.                                                                                                                                                                                                                |

| #define WRITE_DIR_SCMP<br>- Default value "SCMP"                                                                            | String of safety operated data directory.                                                                                                                                                                                                                   |

| #define RESULT_FILE<br>- Default value "RESULT"                                                                             | Specify the file name of the operation result file to indicate safety data file size, raw record area begin address and inverted record area begin address.<br>This string is concatenated to the file extension equal to ".txt".<br>Ex. "RESULT.txt"       |

| <pre>#define UPD_NXT_SEED - undefined</pre>                                                                                 | Update seed value for next operation or not?<br>- If defined, update the seed value for next operation after current<br>operation completed.                                                                                                                |

| #define FORCE_ERASE_BPAT<br>- undefined                                                                                     | <ul><li>Erase saved bit pattern from the data flash or not?</li><li>If defined, forcing erase the bit pattern from the data flash after current operation completed.</li></ul>                                                                              |

| <pre>#define BIT_PAT_MODE #define BIT_PAT_RAN (0) #define BIT_PAT_SEQ (1) #define BIT_PAT_CNT (2) - Default value = 0</pre> | <ul> <li>Specify the bit pattern setting.</li> <li>When this is set to 0, the bit pattern is random pattern.</li> <li>When this is set to 1, the bit pattern is sequential pattern.</li> <li>When this is set to 2, the bit pattern is constant.</li> </ul> |

| <pre>#define CONST_PAT - Default value = 0x00</pre>                                                                         | Set constant data pattern.<br>This setting is only relevant, if the bit pattern is constant<br>(="BIT_PAT_CNT").                                                                                                                                            |

| <pre>#define SEED_BLOCK_ADDR - Default value = 0x00100000 (FLASH_DF_BLOCK_0)</pre>                                          | Set the seed value stored address.                                                                                                                                                                                                                          |

| <pre>#define NUM_BIT_SEG - Default value = 8</pre>                                                                          | Set number of bit pattern segment.<br>Please set this default value in this version.                                                                                                                                                                        |

| <pre>#define BIT_SEG_SIZE - Default value = 1024</pre>                                                                      | Set bit pattern segment size.<br>Please set this default value in this version.                                                                                                                                                                             |

| <pre>#define NUM_NON_BLK - Default value = 3</pre>                                                                          | Set number of no safety areas.<br>Please set this default value in this version.                                                                                                                                                                            |

| <pre>#define NON1_AREA_SIZE - Default value = 16*1024 (16KB) </pre>                                                         | Set size of no safety data area No.1.<br>Please set this default value in this version.                                                                                                                                                                     |

| <pre>#define NON2_AREA_SIZE - Default value = 16*1024 (16KB)</pre>                                                          | Set size of no safety data area No.2.<br>Please set this default value in this version.                                                                                                                                                                     |

| <pre>#define NON3_AREA_SIZE - Default value = 16*1024 (16KB)</pre>                                                          | Set size of no safety data area No.3.<br>Please set this default value in this version.                                                                                                                                                                     |

| <pre>#define NUM_RAW_REC - Default value = 8</pre>                                                                          | Set number of raw record for safety data.<br>Please set this default value in this version.                                                                                                                                                                 |

|                                          | Configuration options                                        |  |  |  |  |

|------------------------------------------|--------------------------------------------------------------|--|--|--|--|

| #define NUM_INV_REC                      | Set number of invert record for safety data.                 |  |  |  |  |

| - Default value = 8                      | Please set this default value in this version.               |  |  |  |  |

| #define RAW_REC_SIZE                     | Set size of raw record for safety data.                      |  |  |  |  |

| - Default value = 1024 (1KB)             | Please set this default value in this version.               |  |  |  |  |

| <pre>#define INV_REC_SIZE</pre>          | Set size of invert record for safety data.                   |  |  |  |  |

| - Default value = 1024 (1KB)             | Please set this default value in this version.               |  |  |  |  |

| #define KND_BIT_OP                       | Specify the kind of bit operation.                           |  |  |  |  |

| #define OP_NONE (0)                      | - When this is set to 0, no bit operation is executed.       |  |  |  |  |

| <pre>#define OP_EXOR (1)</pre>           | - When this is set to 1, exclusive or operation is executed. |  |  |  |  |

| <pre>- Default value = 1 (OP_EXOR)</pre> |                                                              |  |  |  |  |

| #define FILESIZE                         | Specify the FAT file system data buffer size                 |  |  |  |  |

| - Default value = 2048                   | - Set 2048 in this sample.                                   |  |  |  |  |

# 2.9 Data Structures

This section details the data structures that are used with the functions of this example. Those data structures in this project are located in *sample\_main.h and db\_ram.h* as the prototype declaration.

```

/* USB access state */

typedef enum

{

APL START = 0, /* Operation start state */

APL_NREAD, /* Non safety data read state */

/* Non safety data RAM access state */

APL NRAM,

APL NWRITE,

/* Non safety data write state */

APL SREAD,

/* Safety data read state */

APL SRAM,

/* Safety data RAM access state */

APL SWRITE,

/* Safety data write state */

APL STOP,

/* Operation stop state */

} APLState;

```

```

/* Kind of RAM area */

typedef enum

{

AREA_NON1 = 0, /* Non safety data area No.1 */

AREA_NON2, /* Non safety data area No.2 */

AREA_NON3, /* Non safety data area No.3 */

AREA_SAFE, /* Safety data area */

} RAMArea;

/* Data access information structure */

typedef struct

{

```

```

uint16_t size; /* Data size */

int8_t *src; /* Address of read data from USB */

int8_t *dst; /* Address of write data to USB */

int8_t area; /* Kind of RAM area */

} ACCInfo;

```

```

/* Bit pattern segment address */

const flash block_address_t bp_addr[NUM_BIT_SEG] =

{ /* Refer to "r flash rx/src/targets/rx64m/r flash rx64m.h or

rx71m/r flash rx71m.h". */

FLASH DF BLOCK 384, /* 0x00106000 to 0x001063FF (1KB) */

FLASH DF BLOCK 400, /* 0x00106400 to 0x001067FF (1KB) */

FLASH DF BLOCK 416, /* 0x00106800 to 0x00106BFF (1KB) */

FLASH DF BLOCK 432, /* 0x00106C00 to 0x00106FFF (1KB) */

FLASH_DF_BLOCK_448, /* 0x00107000 to 0x001073FF (1KB) */

FLASH_DF_BLOCK_464, /* 0x00107400 to 0x001077FF (1KB) */

FLASH DF BLOCK 480, /* 0x00107800 to 0x00107BFF (1KB) */

FLASH DF BLOCK 496, /* 0x00107C00 to 0x00107FFF (1KB) */

};

/* Bit pattern for double RAM segment address */

const flash_block_address_t bpc_addr[NUM_BIT_SEG] =

{ /* Refer to "r_flash_rx/src/targets/rx64m/r_flash_rx64m.h or

rx71m/r_flash_rx71m.h". */

FLASH DF BLOCK 512, /* 0x00108000 to 0x001083FF (1KB) */

FLASH_DF_BLOCK_528, /* 0x00108400 to 0x001087FF (1KB) */

FLASH_DF_BLOCK_544, /* 0x00108800 to 0x00108BFF (1KB) */

FLASH DF BLOCK 560, /* 0x00108C00 to 0x00108FFF (1KB) */

FLASH DF BLOCK 576, /* 0x00109000 to 0x001093FF (1KB) */

FLASH_DF_BLOCK_592, /* 0x00109400 to 0x001097FF (1KB) */

FLASH DF BLOCK 608, /* 0x00109800 to 0x00109BFF (1KB) */

FLASH DF BLOCK 624, /* 0x00109C00 to 0x00109FFF (1KB) */

};

```

#### 2.10 Return Values

This section describes return values of the functions of this example. Those return values in the test project are located in *db\_ram.h and file\_if.h* as the prototype declarations.

```

/* Double RAM operation return value */

typedef enum

{

DBRAM_ERR_FLERASE = -8, /* Flash erase error */

DBRAM_ERR_FLWRITE = -7, /* Flash write error */

DBRAM_ERR_FLVERIFY = -6, /* Flash verify error */

DBRAM_ERR_FLDBRAM = -5, /* Flash double RAM error */

DBRAM_ERR_PARAM = -4, /* Parameter error */

DBRAM_ERR_BOP = -3, /* Bit operation error */

DBRAM_ERR_CMP = -2, /* Double RAM compare error */

DBRAM_ERR = -1, /* General error */

DBRAM ERR = -1,

/* General error */

DBRAM_OK = 0,

} dbram t;

/* File access return value */

typedef enum

{

FLIF ERR = -1, /* General error */

FLIF OK = 0,

```

} flif t;

# 3. Specification of This Example

#### 3.1 Environment and Execution

Execution of this example needs a RX64M/71M RSK boards<sup>1</sup> and a USB memory.

The outline of the execution sequence is following.

- Write the project execution code to the code Flash of in the RX64M/71M RSK board (hereafter, RSK board).

- Insert the USB memory to the USB port in the RSK board. The USB memory stores the test data composed of the not safety data and safety ones to/from which wrote/read RAM without ECC. In case of safety data, double Ram with bit operation is applied.

- The test data sample is prepared in the project and it is stored the demo\_src/usb\_memory\_sample/set1 or set2 folder. You can use it copying it to root layer of the USB memory.

- Power on the RSK board.

- When the RSK board finishes the initialization and start process of FAT file system and USB driver, creation to bit pattern data, updating bit pattern with double RAM operation, and loading seed value, the user LED composed of LED3, LED2, LED1 and LED0 shows the "1" pattern (LED3: OFF, LED2: OFF, LED1: OFF, LED0: ON).

- Push the SW1 switch of the RSK board and starts the operation described in the Section 3.2.

- When the double RAM operation of the safety data to each area is completed, the user LED shows the last access record number from "0" to "7". As for the detail of RAM area, please refer to the Section 3.2.

- Push the SW2 switch of the RSK board and starts the double RAM operation to next area.

- When the operation finished without any error, the user LED shows the all-on pattern (LED3: ON, LED2: ON, LED1: ON, LED0: ON).

- If any error detected during the operation, the user LED shows the following pattern depend on the error.

Flash access error - LED3: ON, LED2: OFF, LED1: OFF, LED0: OFF. ("8" pattern)

Safety access error - LED3: ON, LED2: OFF, LED1: OFF, LED0: ON. ("9" pattern)

Not safety access error - LED3: ON, LED2: OFF, LED1: ON, LED0: OFF. ("A" pattern)

Seed creation error - LED3: ON, LED2: OFF, LED1: ON, LED0: ON. ("B" pattern)

Bit pattern erasing error – LED3: ON, LED2: ON, LED1: OFF, LED0: OFF. ("C" pattern)

<sup>1</sup>Product name is a Renesas Starter Kit+ for RX64M [8] or a Renesas Starter Kit+ for RX71M [9].

Figure 3.1 shows the environments of this example.

Figure 3.1 Environment

# 3.2 Operation Sequence

In this section, explain the operation sequence in this example when the total number of safety data record are 8 specified to "NUM\_REC".

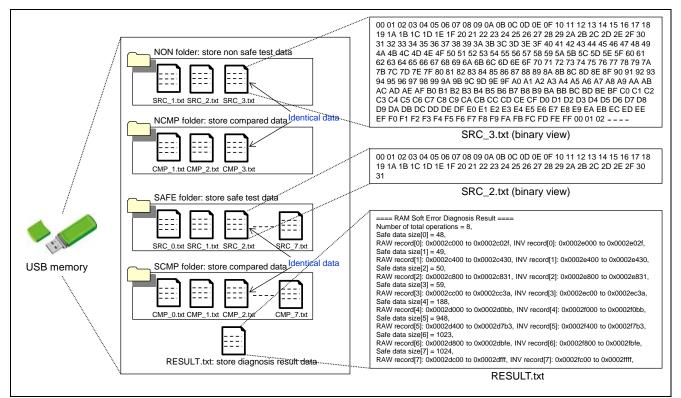

Figure 3.2 shows the USB memory contents. There are NON folder, NCMP folder, SAFE folder, SCMP folder, and RESULT.txt file in the USB memory. The NON folder stores the non safe test data in the files from "SRC\_1.txt" to "SRC\_3.txt". The NCMP folder stores the compared data after the normal read/write operation in the files from "CMP\_1.txt" to "CMP\_3.txt". The SAFE folder stores the safe test data in the files from "SRC\_0.txt" to "SRC\_7.txt". The SCMP folder stores the compared data after the double RAM operation in the files from "CMP\_0.txt" to "CMP\_7.txt". The contents of SAFE (NON) folder and SCMP (NCMP) folder are identical each other if operation finished without error. Figure 3.2 also shows the contents of SRC\_3.txt of the non safe test data and SRC\_2.txt of the safe test data respectively as example. The RESULT.txt stores the number of the total test times, sizes of the safe test data, and the addresses of raw and invert records of the safe test data.

Figure 3.2 USB memory Contents

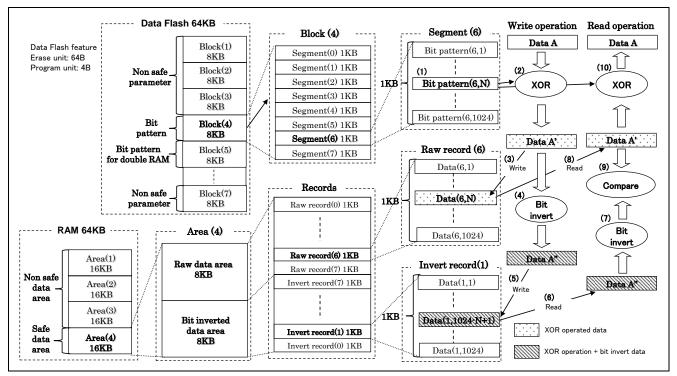

This example uses the 16KB data flash area and 64KB RAM without ECC area. The erase unit and program unit of RX64M/71M's data flash are 64B and 4B respectively<sup>1</sup>.

A portion of the data flash divided by eight defines the block (Block(1) to Block(8)). Furthermore, each 1KB unit of the block defines the segment (Segment(0) to Segment(7)). Allocating one block as the bit pattern stored area, the other block as the bit pattern for double RAM stored area, and remaining blocks are used as the not safety parameter stored areas.

The last 16KB RAM area, defining Area(4), assigns the safe data stored area and remaining 3x16KB areas uses the not safety data stored areas (Area(1) to Area(4)). Forward 8KB of the Area(4) allocates a raw data area (Raw record(0) to Raw record(7)) and backward 8KB uses a bit invert area (Invert record(0) to Invert record(7)). Each 1KB unit of them defines a raw record or invert record.

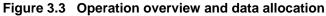

Figure 3.3 explains the operation overview in relation to the data allocation when 1byte safety data (hereafter, Data A) write after read operation. And then, Data A is stored at Nth byte of 7th raw record and exclusive OR operation (hereafter, XOR) is applied.  $(1 \le N \le 1024)$

(1) Update bit pattern in the data flash. Thereafter, verify updated bit pattern applied to double RAM operation.

- (2) Execute XOR Data A with Bit pattern(6,N). This operated data defines Data A'.

- (3) Write Data A' to Nth byte of 7th raw record.

- (4) Execute bit invert operation to Data A'. This operated data defines Data A".

- (5) Write Data A" to (1024 N + 1)th byte of 2nd invert record.

- (6) Read Data A" from (1024 N + 1)th byte of 2nd invert record.

- (7) Execute bit invert operation to Data A".

- (8) Read Data A' to Nth byte of 7th raw record.

(9) Compare the bit invert Data A" at sequence(7) to the Read Data A' at sequence(8). If not compare match each other, any RAM soft error detected.

(10) Execute XOR Data A' with Bit pattern(6,N). This operated data retrieves Data A due to XOR feature. And then, return Data A to user application.

<sup>1</sup>As for more detailed feature, please refer to RX64M/71M user's manual.

#### 3.3 Reducing Biased Data

In general, the safe data of user application are not balanced (biased 0's or 1's) and difficult to detect RAM's 0 or 1 fixed error effectively. Therefore, XOR make equivalent data pattern of safe data stored in the RAM and enhances the error detection rate.

Figure 3.4 shows the example of reducing user application's biased data by XOR and the operation is same as described Figure 3.3. Store the sequential bit pattern such as 0x00 to 0xFF by 256 byte unit in the Segment(6). In this case, both of  $P_N$  and  $P_I$  closes nearly 1/2 because the number of b'0 and b'1 are 4096 unit respectively and each safe data is applied to XOR with the bit pattern ( $P_N$ : probability preserving the current bit value,  $P_I$ : the probability inverting the current bit value). If the number of b'0 and b'1 in the user application data are N unit and (8192 – N) unit respectively, XOR makes the number of b'0 or b'1 approximately becomes 4092 unit and reduces the biased data in view of probabilistically (N = 0, 1, 2,,, 8192).

The error detection rate improves proportional to the data size of user application because the more data size,  $P_N$  and  $P_I$  become closer to 1/2.

If bit pattern is created from random data, the same degree of result can be expected because the number of b'0 and b'1 are approximately equivalent.

Figure 3.4 Reducing biased data by XOR

# 3.4 Performance of Safety Data Access (Measurement Example)

Table 3.1 and Table 3.2 show the access time of RX64M and RX71M respectively as the typical examples. Those access time are measured by the execution interval of safety write function (RAM\_SafetyWrite) or safety read function (RAM\_SafetyRead) with bit operation and those safety data are used the safety data set<sup>1</sup> stored in the SAFE folder.

Please keep your mind those result are depend on the condition and environment.

<sup>1</sup> Stored at demo\_src/usb\_memory\_sample/set1 and set2.

#### Table 3.1 RX64M access time

| Board                                                             | CPU f                             | requency       | Co                           | ode area         | Data area        |          | Cor            | npiler                                                             | Optimizatio        | n setting          |  |

|-------------------------------------------------------------------|-----------------------------------|----------------|------------------------------|------------------|------------------|----------|----------------|--------------------------------------------------------------------|--------------------|--------------------|--|

| RX64M RSK boa<br>(R0K50564MC001                                   | . 12                              | 0MHz           | Internal ROM<br>Read: 1cycle |                  |                  |          |                | C-RX - Opt level: 2<br>.04.01 - Opt method: si<br>- Inter module o |                    |                    |  |

| - set1 with bit operation                                         |                                   |                |                              |                  |                  |          |                |                                                                    |                    |                    |  |

| - set1 with bit op                                                | eration                           |                |                              |                  |                  |          |                |                                                                    |                    |                    |  |

| <ul> <li>Set1 with bit op</li> <li>Data size (Byte)</li> </ul>    | eration<br>48                     | 49             |                              | 50               | 59               |          | 188            | 948                                                                | 1023               | 1024               |  |

| '                                                                 |                                   | 49 22,61       | 6                            | 50<br>23,083     | 59<br>27,141     |          | 188<br>5,008   | 948<br>426,216                                                     | 1023<br>459,941    | 1024<br>460,333    |  |

| Data size (Byte)                                                  | 48                                |                | -                            |                  |                  | 85       |                |                                                                    |                    | -                  |  |

| Data size (Byte)<br>Write (ns)<br>Read (ns)                       | 48<br>22,150<br>22,891            | 22,61          | -                            | 23,083           | 27,141           | 85       | 5,008          | 426,216                                                            | 459,941            | 460,333            |  |

| Data size (Byte)<br>Write (ns)<br>Read (ns)                       | 48<br>22,150<br>22,891            | 22,61          | <sup>7</sup> 5               | 23,083           | 27,141           | 85<br>87 | 5,008          | 426,216                                                            | 459,941            | 460,333            |  |

| Data size (Byte)<br>Write (ns)<br>Read (ns)<br>• set2 with bit op | 48<br>22,150<br>22,891<br>eration | 22,61<br>23,37 | 75<br>1                      | 23,083<br>23,858 | 27,141<br>28,066 | 85<br>87 | 5,008<br>7,941 | 426,216<br>441,025                                                 | 459,941<br>475,916 | 460,333<br>476,325 |  |

#### Table 3.2RX71M access time

| Board                                       | 0                       | CPU fre               | quency         | C                             | ode area         | Data area                       |          | Cor            | npiler             | Optimizatio                                                                                  | n setting          |

|---------------------------------------------|-------------------------|-----------------------|----------------|-------------------------------|------------------|---------------------------------|----------|----------------|--------------------|----------------------------------------------------------------------------------------------|--------------------|

| RX64M RSK board<br>(R0K50571MC000BR)        |                         | 2401                  | MHz            | Internal ROM<br>Read: 2cycles |                  | Internal RAN<br>Read/Write: 1cy |          |                |                    | Default setting<br>- Opt level: 2<br>- Opt method: size priority<br>- Inter module opt: none |                    |

| - set1 with bit op                          | eration                 | ı                     |                | set1 with bit operation       |                  |                                 |          |                |                    |                                                                                              |                    |

|                                             |                         |                       |                |                               |                  |                                 |          |                |                    |                                                                                              |                    |

| Data size (Byte)                            | 48                      | 8                     | 49             |                               | 50               | 59                              |          | 188            | 948                | 1023                                                                                         | 1024               |

| Write (ns)                                  | 48<br>17,9              | -                     | 49<br>18,35    | 0                             | 50<br>18,733     | 59<br>22,033                    |          | 188<br>9,250   | 948<br>347,516     |                                                                                              | 1024<br>375,333    |

|                                             |                         | 983                   |                | -                             |                  |                                 | 69       |                |                    | 375,000                                                                                      |                    |

| Write (ns)<br>Read (ns)                     | 17,9<br>18,3            | 983<br>316            | 18,35          | -                             | 18,733           | 22,033                          | 69       | 9,250          | 347,516            | 375,000                                                                                      | 375,333            |

| Write (ns)<br>Read (ns)<br>set2 with bit op | 17,9<br>18,3            | 983<br>316<br>1       | 18,35          | 8                             | 18,733           | 22,033                          | 69<br>70 | 9,250          | 347,516            | 375,000                                                                                      | 375,333            |

|                                             | 17,9<br>18,3<br>eration | 983<br>316<br>1<br>50 | 18,35<br>18,70 | 8                             | 18,733<br>19,083 | 22,033<br>22,458                | 69<br>70 | 9,250<br>9,666 | 347,516<br>354,875 | 375,000<br>382,950<br>723                                                                    | 375,333<br>383,300 |

# 3.5 Software Operation Flow

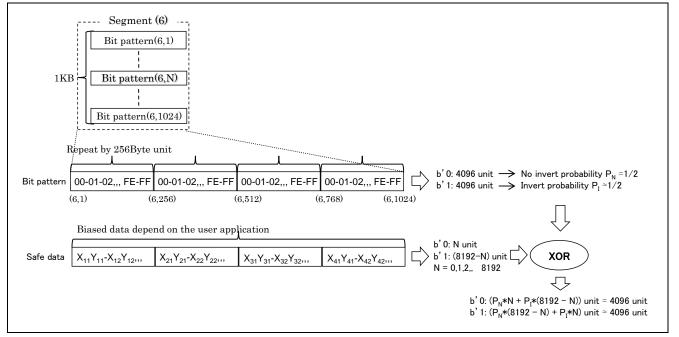

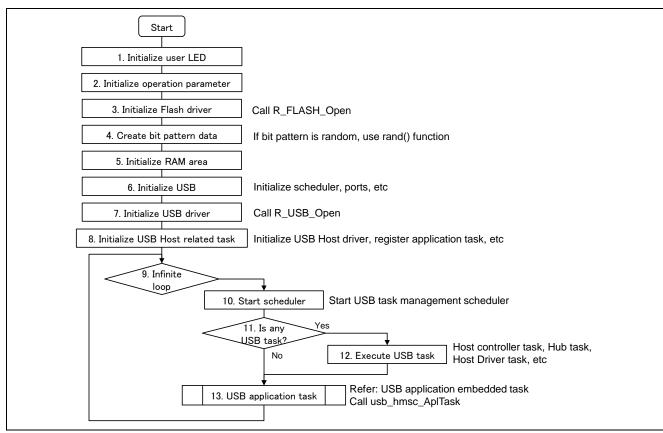

In this section, describes the software operation flow of this sample.

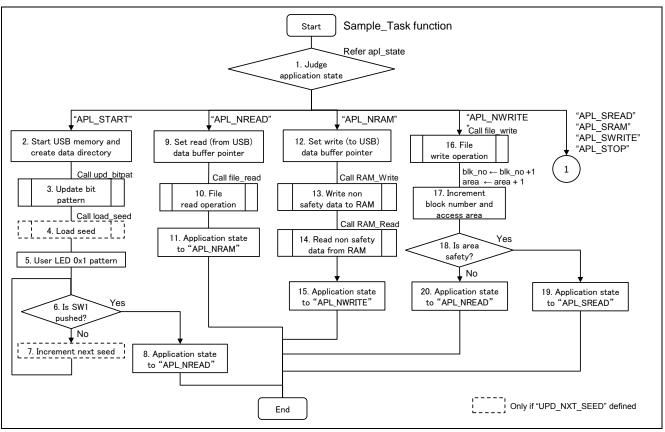

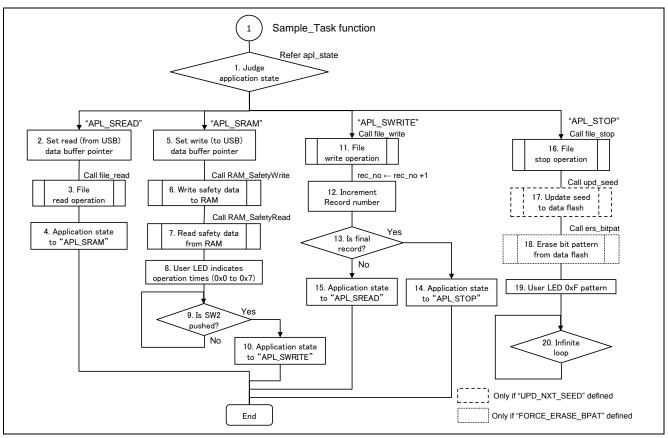

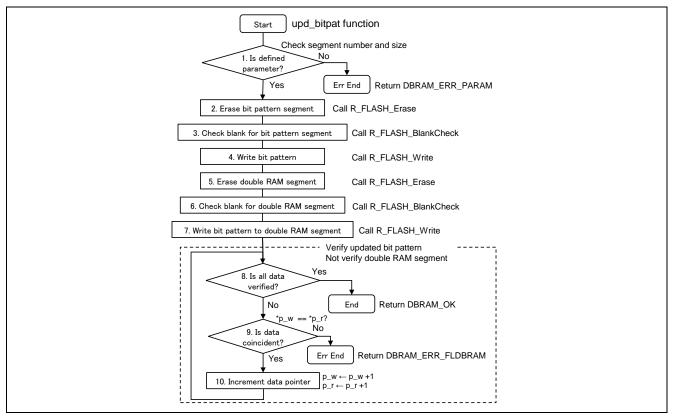

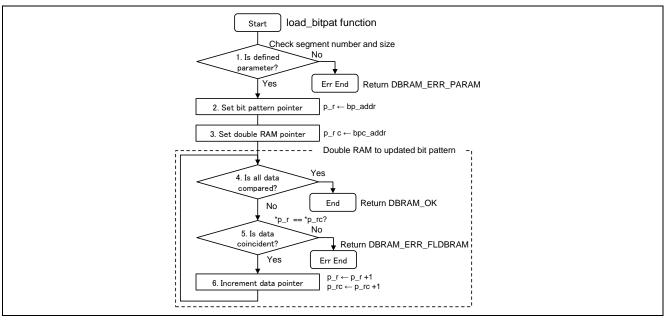

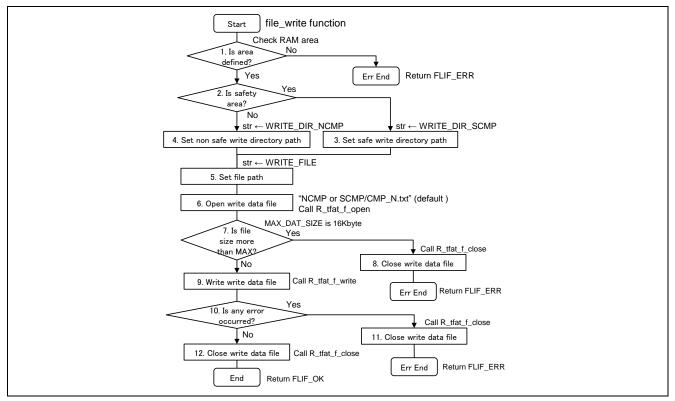

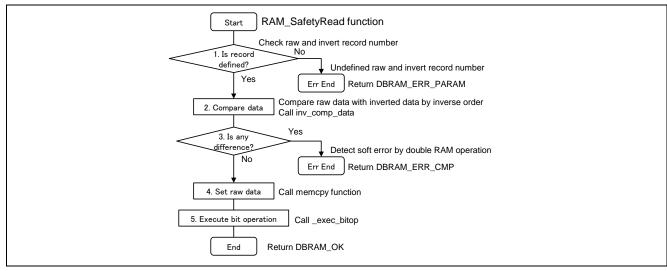

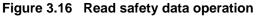

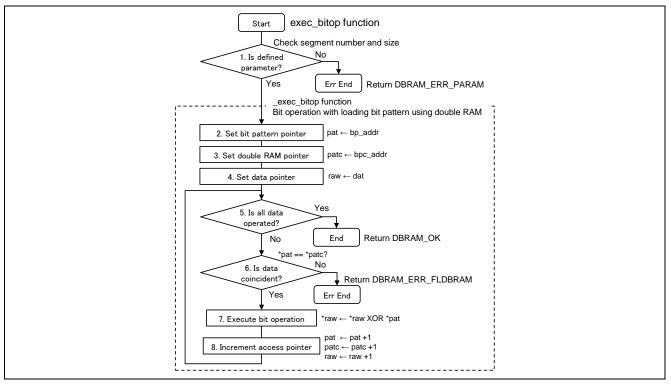

Figure 3.5 shows from the initialize process to the infinite loop. This sample task (Sample\_Task function) is called via USB application task showed by Figure 3.6 within the infinite loop. Figure 3.7 and Figure 3.8 show the each task structure managed by the application state. Figure 3.9 to Figure 3.20 are software operation flows related to the double RAM with bit operation.

Figure 3.5 Initial operation

Figure 3.6 USB application embedded task

Figure 3.7 Sample application task (1)

Figure 3.8 Sample application task (2)

Figure 3.9 Update bit pattern operation

Figure 3.10 Load bit pattern operation

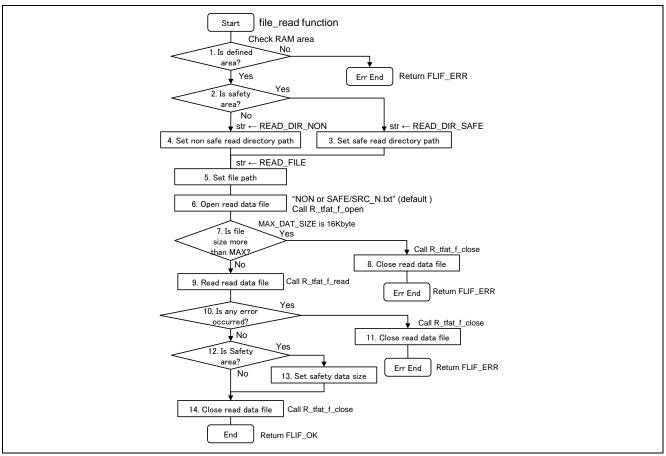

Figure 3.11 File read operation

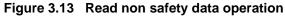

Figure 3.14 File write operation

Figure 3.17 Execute bit operation

Figure 3.18 File stop operation

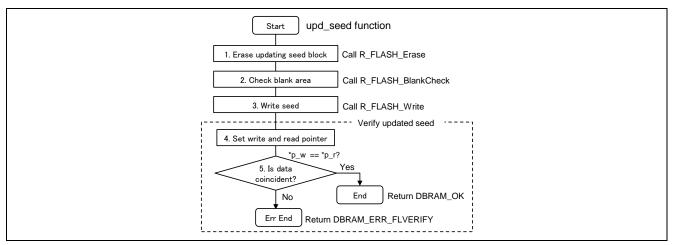

Figure 3.19 Update seed operation

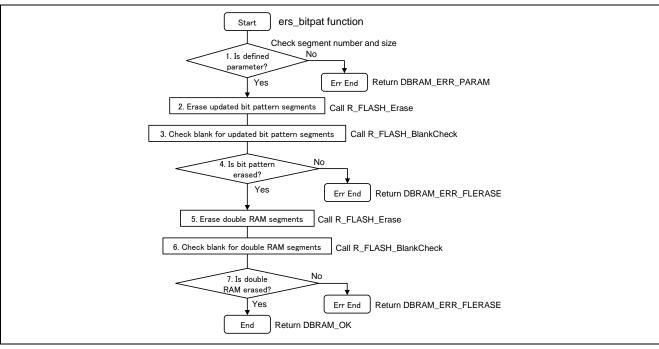

Figure 3.20 Erase bit pattern operation

# 3.6 Board Setting

There are two jumpers changing from the default setting of the RX64M/71M RSK board to execute this example. When the product name of the RX64M/71M RSK board is R0K50564MC001BR or R0K5RX71MC010BR, Table 3.3 indicates their changing. And when the product name of the RX71M RSK board is R0K50571MC000BR, Table 3.4 indicates their changing.

#### Table 3.3 Jumper setting

| - USB access setting |                       |              |                       |  |  |  |  |  |  |

|----------------------|-----------------------|--------------|-----------------------|--|--|--|--|--|--|

| Jumper               | Board default setting | This example | Functional use        |  |  |  |  |  |  |

| J2                   | 2-3                   | 1-2          | USB Enables Host Mode |  |  |  |  |  |  |

| J6                   | 1-2                   | 2-3          | USB USB0VBUSEN        |  |  |  |  |  |  |

|                      |                       |              |                       |  |  |  |  |  |  |

#### Table 3.4 Jumper setting

| - USB access setting |                       |              |                       |  |

|----------------------|-----------------------|--------------|-----------------------|--|

| Jumper               | Board default setting | This example | Functional use        |  |

| J1                   | 2-3                   | 1-2          | USB Enables Host Mode |  |

| J3                   | 1-2                   | 2-3          | USB USB0VBUSEN        |  |

|                      |                       |              |                       |  |

# 4.1 FlashInit ()

This function initializes flash driver (flash API).

#### Format

dbram\_t FlashInit(void);

#### Parameters

None

#### **Return Values**

DBRAM\_OK: Processing completed successfully DBRAM\_ERR: Any error occurred

# **Properties**

Prototyped in "db\_ram.h".

#### Description

This function initializes flash driver (flash API).

- If bit pattern setting is random (BIT\_PAT\_RAN == BIT\_PAT\_MODE), load seed from data flash and set initial seed by srand function.

#### Reentrant

Function is reentrant.

# Example

Example showing this function being used.

```

#include <stdlib.h>

#include "db ram.h"

#include "r flash rx if.h"

static int8 t BPT BUF[BIT SEG SIZE]; /* Bit pattern data buffer */

dbram t db ret;

/* Initialize flash API and set initial seed */

db ret = FlashInit();

if (DBRAM OK != db ret)

{

goto Err end; /* error */

}

/* Create bit pattern data */

crt_bitpat(BPT BUF, sizeof(BPT BUF));

/* Initializes RAM area */

RAM Init();

/* Update bit pattern to 7th segment */

db ret = upd bitpat(6, (uint8 t*)BPT BUF, BIT SEG SIZE);

if (DBRAM OK != db ret)

{

goto Err end; /* error */

}

return;

```

#### **Special Notes**

This function need to be executed at least once after the system was started, if bit pattern setting is random.

# 4.2 load\_seed ()

This function loads seed from data flash.

#### Format

uint32\_t load\_seed(void);

#### Parameters

None

Return Values Seed data

**Properties** Prototyped in "db\_ram.h".

**Description** This function loads seed from data flash.

# Reentrant

Function is reentrant.

# Example

Example showing this function being used.

```

#include "db ram.h"

```

```

dbram_t db_ret;

uint32_t seed;

/* Load seed from data flash */

seed = load_seed();

/* Update bit pattern to 7th segment */

db_ret = upd_seed(&next_seed);

if (DBRAM_OK != db_ret)

{

goto Err_end; /* error */

}

return;

```

#### **Special Notes**

This function is only used, if bit pattern setting is random (BIT\_PAT\_RAN == BIT\_PAT\_MODE).

# 4.3 upd\_seed ()

This function updates seed to data flash.

#### Format

dbram\_t upd\_seed(uint32\_t \*dat);

#### Parameters

dat - seed data.

#### **Return Values**

DBRAM\_OK: Processing completed successfully DBRAM\_ERR\_FLERASE: Flash erase error DBRAM\_ERR\_FLWRITE: Flash write error DBRAM\_ERR\_FLVERIFY: Flash verify error

#### **Properties**

Prototyped in "db\_ram.h".

#### Description

This function updates seed to data flash.

#### Reentrant

Function is reentrant.

#### Example

Example is same as "4.2 load\_seed".

#### **Special Notes**

This function is only used, if bit pattern setting is random (BIT\_PAT\_RAN == BIT\_PAT\_MODE).

# 4.4 crt\_bitpat ()

This function creates bit pattern data.

#### Format

void crt\_bitpat(int8\_t \*dat, int32\_t size);

#### Parameters

dat - bit pattern data.

size – bit pattern size.

Return Values

**Properties** Prototyped in "db\_ram.h".

# Description

This function creates bit pattern data.

- If bit pattern setting is random (BIT\_PAT\_RAN == BIT\_PAT\_MODE), create random data by rand function.

- If bit pattern setting is sequential (BIT\_PAT\_SEQ == BIT\_PAT\_MODE), create sequential data composed of repeating 0x00 to 0xff by 256 byte unit.

- If bit pattern setting is constant (BIT\_PAT\_CNT == BIT\_PAT\_MODE), create constant data whose value is specified by constant data pattern (CONST\_PAT).

#### Reentrant

Function is reentrant.

#### Example

Example is same as "4.1 FlashInit".

#### **Special Notes**

Need to allocate buffer more than creating bit pattern.

# 4.5 load\_bitpat ()

This function loads bit pattern from data flash with double RAM operation.

#### Format

dbram\_t load\_bitpat(int32\_t seg\_no, uint8\_t \*dat, int32\_t size);

#### **Parameters**

seg\_no – segment number.

dat – bit pattern data.

size - bit pattern size.

#### **Return Values**

DBRAM\_OK: Processing completed successfully DBRAM\_ERR\_FLDBRAM: Flash double RAM error DBRAM\_ERR\_PARAM: Parameter error

#### **Properties**

Prototyped in "db\_ram.h".

#### Description

This function loads bit pattern from data flash with double RAM operation.

#### Reentrant

Function is reentrant.

#### Example

Example showing this function being used.

```

#include <stdio.h>

#include "db_ram.h"

static uint8_t BUF[4]; /* Bit pattern data buffer */

dbram t db ret;

/* Load bit pattern from 3rd segment, */

db_ret = load_bitpat(2, (uint8_t*)BUF, 4);

if (DBRAM_OK != db_ret)

{

goto Err_end; /* error */

}

printf("Bit pattern data = %8x\n", BUF);

return;

```

# **Special Notes**

# 4.6 upd\_bitpat ()

This function updates bit pattern to data flash with double RAM operation.

#### Format

dbram\_t upd\_bitpat(int32\_t seg\_no, uint8\_t \*dat, int32\_t size);

#### Parameters

seg\_no – segment number.

dat – bit pattern data.

size – bit pattern size.

#### **Return Values**

DBRAM\_OK: Processing completed successfully DBRAM\_ERR\_PARAM: Parameter error DBRAM\_ERR\_FLERASE: Flash erase error DBRAM\_ERR\_FLWRITE: Flash write error DBRAM\_ERR\_FLVERIFY: Flash verify error

# **Properties**

Prototyped in "db\_ram.h".

# Description

This function updates bit pattern to data flash with double RAM operation following procedures.

- Erase bit pattern segment, check blank for bit pattern segment and write bit pattern.

- Erase double RAM segment, check blank for double RAM segment and write bit pattern to double RAM segment.

- Verify updated bit pattern (Not verify double RAM segment).

Reentrant Function is reentrant.

**Example** Example is same as "4.1 FlashInit".

Special Notes None.

# 4.7 ers\_bitpat ()

This function erases bit pattern from data flash.

#### Format

dbram\_t ers\_bitpat(int32\_t seg\_no, int32\_t num\_seg);

#### Parameters

seg\_no - erase segment number.

num\_seg - number of erase segment.

#### **Return Values**

DBRAM\_OK: Processing completed successfully DBRAM\_ERR\_PARAM: Parameter error DBRAM\_ERR\_FLERASE: Flash erase error **Properties** Prototyped in "db\_ram.h".

#### Description

This function erases bit pattern from data flash with double RAM blocks.

#### Reentrant

Function is reentrant.

#### Example

Example showing this function being used.

```

#include <stdio.h>

#include "db_ram.h"

dbram_t db_ret;

/* Erase bit pattern of 4th segment, */

db_ret = ers_bitpat(3, 1);

if (DBRAM_OK != db_ret)

{

goto Err_end; /* error */

}

printf("Bit pattern erased of 4th segment\n");

return;

```

#### **Special Notes**

This function erases not only bit pattern data itself but also the double RAM data.

#### 4.8 exec\_bitop ()

This function executes bit operation.

#### Format

dbram\_t exec\_bitop(int32\_t seg\_no, int8\_t \*dat, uint16\_t size);

#### Parameters

seg\_no – segment number.

dat - bit operation data.

size - bit operation data size.

#### **Return Values**

DBRAM\_OK: Processing completed successfully DBRAM\_ERR\_FLDBRAM: Flash double RAM error DBRAM\_ERR\_PARAM: Parameter error **Properties**

Prototyped in "db\_ram.h".

#### Description

This function executes bit operation with loading bit pattern using double RAM.

#### Reentrant

Function is reentrant.

#### Example

Example showing this function being used.

```

#include <string.h>

#include "db ram.h"

static int8 t USER BUF[1024];

#pragma section RAW AREA

static int8 t R BUF[NUM RAW REC][RAW REC SIZE]; /* Raw data area (8*1024) byte

*/

#pragma section

#pragma section INV AREA

static int8 t I BUF[NUM INV REC][INV REC SIZE]; /* Invert data area (8*1024)

byte */

#pragma section

int32 t ret;

int32 t *dat;

/* Compare 1st record raw data with inverted data by 1KB */

ret = inv comp data(R BUF[0], &(I BUF[0][BIT SEG SIZE-1]), 1024);

if ((-1) != ret)

{

ErrPtr = ret; /* set error byte */

goto Err_end; /* compare error */

}

/* Set user buffer pointer */

dat = USER BUF;

/* Set raw data */

memcpy(dat, R BUF[0], 1024);

```

/\* Execute bit operation \*/

```

_exec_bitop(rec_no, dat, size);

return;

```

# **Special Notes**

No bit operation is executed, if kind of bit operation is no operation (OP\_NONE == KND\_BIT\_OP).

# 4.9 RAM\_Init ()

This function initializes RAM.

#### Format

void RAM\_Init(void);

#### Parameters

None

# Return Values None

**Properties** Prototyped in "db\_ram.h".

# Description

This function initializes following RAM areas.

- Non safe areas: Area(1), Area(2) and Area(3).

- Safe areas: raw data area and bit inverted data area.

#### **Reentrant** Function is reentrant.

**Example** Example is same as "4.1 FlashInit".

# Special Notes None.

# 4.10 RAM\_Write ()

This function writes non safety data to RAM.

#### Format

dbram\_t RAM\_Write(int32\_t area\_no, int8\_t \*dat, uint16\_t size);

#### **Parameters**

area\_no - area number.

dat - write data.

size - data size.

#### **Return Values**

DBRAM\_OK: Processing completed successfully DBRAM\_ERR\_PARAM: Parameter error **Properties** Prototyped in "db\_ram.h".

#### Description

This function writes non safety data to RAM specified by area number and size.

#### Reentrant

Function is reentrant.

#include <stdio.h>

#### Example

Example showing this function being used.

```

#include "db ram.h"

static int8 t W BUF[1024]; /* write buffer */

static int8 t R BUF[1024]; /* read buffer */

dbram t db ret;

int32 t i;

/* Write non safe data to Area(1) by 1KB */

db ret = RAM Write(1, W BUF, sizeof(W BUF));

if (DBRAM OK != db ret)

{

printf("Write error occurred\n");

goto Err end;

}

/* ==== Add user operation ==== */

/* Read non safe data from Area(1) by 1KB */

db ret = RAM Read(1, R BUF, sizeof(R BUF));

if (DBRAM OK != db ret)

{

printf("Read error occurred\n");

goto Err end;

}

/* Compare read and write data by 1KB */

for (i = 0; i < 1024; i++)

{

if (R BUF[i] != W BUF[i])

{

printf("Data error detected at %d\n", i);

goto Err_end; /* compare error */

```

```

}

printf("Non safe data access completed\n");

return;

```

# **Special Notes**

# 4.11 RAM\_SafetyWrite ()

This function writes safety data to RAM.

#### Format

dbram\_t RAM\_SafetyWrite(int32\_t rec\_no, int8\_t \*dat, uint16\_t size);

#### **Parameters**

rec\_no - record number.

dat - write data.

size - data size.

#### **Return Values**

DBRAM\_OK: Processing completed successfully DBRAM\_ERR\_FLDBRAM: Flash double RAM error DBRAM\_ERR\_PARAM: Parameter error

#### Properties

Prototyped in "db\_ram.h".

#### Description

This function writes safety data to RAM specified by record number and size.

- Execute bit operation with loading bit pattern using double RAM.

- Write the bit operated data to raw records.

- Write bit inverting data after bit operation to invert records.

#### Reentrant

Function is reentrant.

#### Example

Example showing this function being used.

```

#include <stdio.h>

#include "db ram.h"

static int8 t W BUF[128]; /* write buffer */

static int8_t R_BUF[128]; /* read buffer */

dbram_t db_ret;

int32_t i;

/* Write safe data to record(6)by 128B */

db ret = RAM SafetyWrite (6, W BUF, sizeof(W BUF));

if (DBRAM OK != db ret)

{

printf("Write error occurred\n");

goto Err end;

}

/* ==== Add user operation ==== */

/* Read safe data from record(6)by 128B */

db ret = RAM SafetyRead(6, R BUF, sizeof(R BUF));

if (DBRAM OK != db ret)

{

printf("Read error occurred\n");

goto Err end;

}

/* Compare read and write data by 128B */

```

```

RX Family

```

```

for (i = 0; i < 1024; i++)

{

if (R BUF[i] != W BUF[i])

{

printf("Data error detected at %d\n", i);

goto Err_end; /* compare error */

}

}

printf("Safe data access completed\n");

return;

```

# **Special Notes**

# 4.12 RAM\_Read ()

This function reads non safety data from RAM.

#### Format

dbram\_t RAM\_Read(int32\_t area\_no, int8\_t \*dat, uint16\_t size);

#### Parameters

area\_no - area number.

dat - read data.

size - data size.

#### **Return Values**

DBRAM\_OK: Processing completed successfully DBRAM\_ERR\_PARAM: Parameter error **Properties**

Prototyped in "db\_ram.h".

#### Description

This function reads non safety data from RAM specified by block number and size.

#### Reentrant

Function is reentrant.

# Example

Example is same as "4.10 RAM\_Write".

#### **Special Notes**

# 4.13 RAM\_SafetyRead ()

This function reads safety data from RAM.

#### Format

dbram\_t RAM\_SafetyRead(int32\_t rec\_no, int8\_t \*dat, uint16\_t size);

#### Parameters

rec\_no - record number.

dat - read data.

size - data size.

#### **Return Values**

DBRAM\_OK: Processing completed successfully DBRAM\_ERR\_FLDBRAM: Flash double RAM error DBRAM\_ERR\_PARAM: Parameter error DBRAM\_ERR\_CMP: Double RAM compare error Properties

#### Properties

Prototyped in "db\_ram.h".

#### Description

This function reads safety data from RAM specified by record number and size.

- Compare data read from raw record with data read by inverse address order from inverted record. If there was any difference, a soft error was detected by the double RAM.

- Copy data from raw record to user buffer.

- Execute bit operation with loading bit pattern using double RAM.

#### Reentrant

Function is reentrant.

#### Example

Example is same as "4.11 RAM\_SafetyWrite".

# **Special Notes**

# 5. Reference Documents

User's Manual: Hardware

RX64M Group User's Manual: Hardware Rev.1.00 (R01UH0377EJ) RX71M Group User's Manual: Hardware Rev.1.00 (R01UH0493EJ) The latest version can be downloaded from the Renesas Electronics website.

User's Manual: Software

RX Family RXv2 Instruction Set Architecture User's Manual: Hardware Rev.1.00 (R01US0071EJ) The latest version can be downloaded from the Renesas Electronics website.

Technical Update/Technical News

The latest information can be downloaded from the Renesas Electronics website.

# Website and Support

Renesas Electronics Website <u>http://www.renesas.com/</u>

Inquiries http://www.renesas.com/contact/

All trademarks and registered trademarks are the property of their respective owners.

# **Revision History**

|      |                   | Descript | tion                  |

|------|-------------------|----------|-----------------------|

| Rev. | Date              | Page     | Summary               |

| 1.00 | Aug 10, 2016      | _        | First edition issued. |

|      | <b>3</b> <i>i</i> |          |                       |

#### General Precautions in the Handling of Microprocessing Unit and Microcontroller Unit Products

The following usage notes are applicable to all Microprocessing unit and Microcontroller unit products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

1. Handling of Unused Pins

Handle unused pins in accordance with the directions given under Handling of Unused Pins in the manual.

- The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

- 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

- The reserved addresses are provided for the possible future expansion of functions. Do not access

these addresses; the correct operation of LSI is not guaranteed if they are accessed.

- 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

- When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal.

Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

- 5. Differences between Products

Before changing from one product to another, i.e. to a product with a different part number, confirm that the change will not lead to problems.

— The characteristics of Microprocessing unit or Microcontroller unit products in the same group but having a different part number may differ in terms of the internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a system-evaluation test for the given product.

#### Notice

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for

the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use

of these circuits, software, or information.

- Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- \*Standard\*: Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

Refer to "http://www.renesas.com/" for the latest and detailed information

#### SALES OFFICES

**Renesas Electronics Corporation**

http://www.renesas.com

Renesas Electronics America Inc.

2801 Scott Boulevard Santa Clara, CA 95050-2549, U.S.A.

Tei: +1-408-588-6000, Fax: +1-408-588-6130

Renesas Electronics Canada Limited

9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3

Tei: +1-408-537-2004

Renesas Electronics Europe Limited

Dukes Meadow, Milboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K

Tei: +44-1628-585-100, Fax: +44-1628-585-900

Renesas Electronics Corpe GmbH

Arcadiastrasse 10, 40472 Düsseldorf, Germany

Tei: +496-10-235-1155, Fax: +49-211-6503-1327

Renesas Electronics (China) Co., Ltd.

Rono T709, Quantum Pitza, No. 27 Zh:ChunLu Haidian District, Beijing 100191, P.R.China

Tei: +861-0-235-1155, Fax: +861-0-2325-7679

Renesas Electronics (Shanghai) Co., Ltd.

Nuit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, P. R. China 200333

Tei: +862-12226-0888, Fax: +862-12226-0999

Renesas Electronics Wang Co., Ltd.

1011 101-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong

Tei: +882-2265-6888, Fax: +862-12226-0999

Renesas Electronics Singapore Place

11301, Tower 3, Century Diace, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong

Tei: +886-2415-2000, Fax: +885-2415-0970</td