# **RX** Family

Clock Synchronous Control Module for Serial NOR Flash Memory Access

# Introduction

This application note explains how to control and use serial flash memory with microcontrollers manufactured by Renesas Electronics. Refer to "Target Devices" below for a list of the supported serial flash memory products.

The control software accompanying this application note is upper-layer software that controls the serial flash memory as a slave device.

Lower-layer software (clock synchronous single master control software) for controlling the SPI mode on the individual microcontroller, operating as a master device, is available separately; it can be obtained from the webpage below. Note that although the clock synchronous single master control software may support newer microcontrollers, there may be cases where the control software presented in this application note has not yet been updated to match. For information on the latest supported microcontrollers and matching control software releases, see the "Clock Synchronous Single Master Control Software (Lower-level layer of the software)" section of the following webpage:

#### Serial Flash Memory Driver

http://www.renesas.com/driver/spi\_serial\_flash

The control software uses Firmware Integration Technology (FIT). It is referred to as the serial flash memory FIT module in the documentation of development tools with FIT support. Other similar function control modules using FIT are referred to as FIT modules or as "function name" FIT modules.

When using development tools that do not support FIT, the software code can be imported with the FIT functionality disabled.

### **Target Devices**

Device on which operation has been confirmed:

Serial NOR flash memory

Macronix International Co., Ltd.

- MX25/66L family serial NOR flash memory 32Mbit 1Gbit

- MX25R family serial NOR flash memory 64Mbit

- MX25U family serial NOR flash memory 64Mbit

Renesas Electronics.

• AT25QF family serial NOR flash memory 64Mbit

RX Family microcontrollers

Microcontrollers on which operation has been confirmed:

RX111, RX110, RX113 and RX130 Group (RSPI) RX230, RX231, RX23T and RX24T Group (RSPI) RX65N, RX64M and RX71M Group (RSPI, QSPI, SCI) RX72T and RX72N Group (RSPI, SCI) RX671 Group (QSPIX, RSCI, SCI)

When applying the information in this application note to a microcontroller other than the above, modifications should be made as appropriate to match the specification of the microcontroller and careful evaluation performed.

The following abbreviations are used in this application note:

### RX Family Clock Synchronous Control Module for Serial NOR Flash Memory Access

- Single-SPI (communication in single-SPI mode)

- Dual-SPI (communication in dual-SPI mode)

- Quad SPI (communication in quad-SPI mode)

### **Target Compilers**

- Renesas Electronics C/C++ Compiler Package for RX Family

- GCC for Renesas RX

- IAR C/C++ Compiler for Renesas RX

For details of the confirmed operation contents of each compiler, refer to "5.1 Confirmed Operation Environment".

### **FIT Related Documents**

- Firmware Integration Technology User's Manual (R01AN1833)

- RX Family Board Support Package Module Using Firmware Integration Technology (R01AN1685)

# RX Family Clock Synchronous Control Module for Serial NOR Flash Memory Access

# Contents

| 1.    | Overview                                                                                   | 5    |

|-------|--------------------------------------------------------------------------------------------|------|

| 1.1   | FIT Support of Serial flash Memory Control Software                                        | 6    |

| 1.2   | Overview of APIs                                                                           | 6    |

| 1.3   | Related Application Notes                                                                  | 8    |

| 1.3.1 | FIT Module–Related Application Notes                                                       | 8    |

| 1.4   | Using Serial Flash Memory Module                                                           | 8    |

| 1.4.1 | Using Serial Flash Memory Module in C++ project                                            | 8    |

| 1.5   | Hardware Settings                                                                          | 9    |

| 1.5.1 | Hardware Configuration Example                                                             | 9    |

| 1.6   | Software                                                                                   | . 12 |

| 1.6.1 | Operation Overview                                                                         | . 12 |

| 1.6.2 | Serial Flash Memory Chip Select Pin Control                                                | . 13 |

| 1.6.3 | Software Structure                                                                         | . 14 |

| 1.6.4 | Relationship Between Control Software and Clock Synchronous Single Master Control Software | . 15 |

| 1.6.5 | Data Buffers and Transmit/Receive Data                                                     | . 16 |

| 1.6.6 | State Transition Diagram                                                                   | . 17 |

| ~     |                                                                                            | 4.0  |

|       | API Information                                                                            |      |

| 2.1   | Hardware Requirements                                                                      |      |

| 2.2   | Software Requirements                                                                      |      |

| 2.3   | Supported Toolchain                                                                        |      |

| 2.4   | Header Files                                                                               |      |

| 2.5   | Integer Types                                                                              |      |

| 2.6   | Compile Settings                                                                           |      |

| 2.7   | Arguments                                                                                  |      |

| 2.8   | Code Size                                                                                  |      |

| 2.9   | Return Values                                                                              |      |

|       | Adding the Driver to Your Project                                                          |      |

| 2.11  | Using the Serial Flash Memory Control Software in Other Than an FIT Module Environment     |      |

| 2.12  | Pin States                                                                                 |      |

| 2.13  | "for", "while" and "do while" statements                                                   | . 28 |

| 3.    | API Functions                                                                              | 29   |

|       | ASH_SPI_Open()                                                                             |      |

|       | ASH_SPI_Close()                                                                            |      |

|       | ASH_SPI_Read_Status()                                                                      |      |

|       | ASH_SPI_Read_Status2()                                                                     |      |

| _     | ASH_SPI_Read_Status3()                                                                     |      |

|       | ASH_SPI_Set_Write_Protect()                                                                |      |

|       |                                                                                            |      |

| RX Family         | Clock Synchronous Control Module for Serial NOR Flash Mem | ory Access |

|-------------------|-----------------------------------------------------------|------------|

| R_FLASH_SPI_W     | rite_Di()                                                 | 41         |

| R_FLASH_SPI_Re    | ead_Data()                                                | 42         |

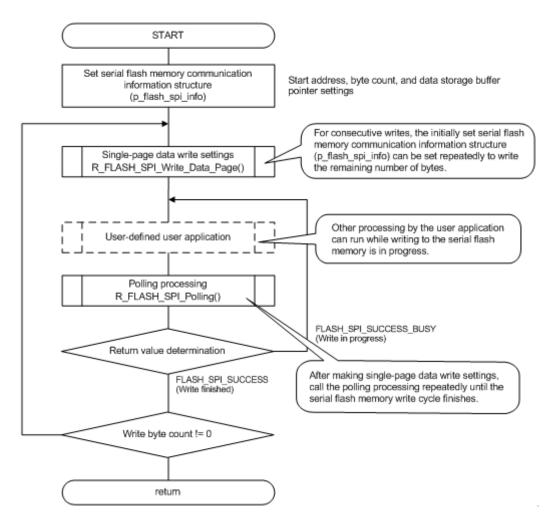

| R_FLASH_SPI_W     | rite_Data_Page()                                          | 44         |

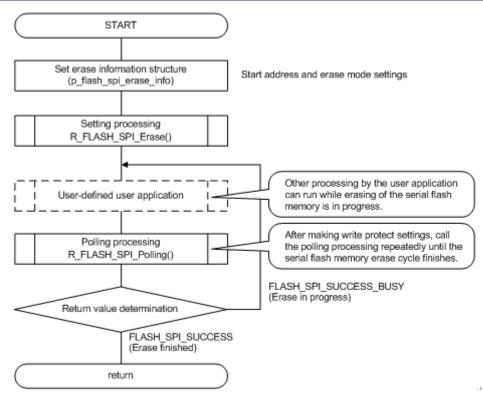

| R_FLASH_SPI_Er    | ase()                                                     | 47         |

| R_FLASH_SPI_Pc    | lling()                                                   | 50         |

| R_FLASH_SPI_Re    | ead_ID()                                                  | 51         |

| R_FLASH_SPI_Ge    | etMemoryInfo()                                            | 52         |

| R_FLASH_SPI_Re    | ead_Configuration()                                       | 53         |

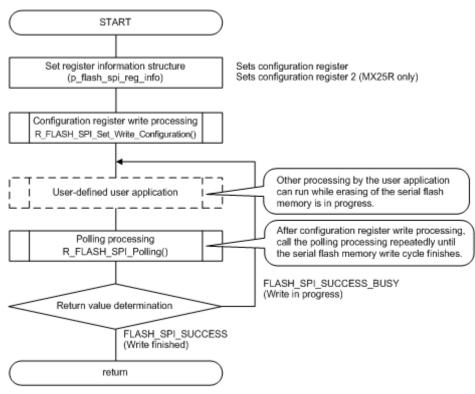

| R_FLASH_SPI_W     | rite_Configuration()                                      | 55         |

| R_FLASH_SPI_W     | rite_Status()                                             | 59         |

| R_FLASH_SPI_W     | rite_Status2()                                            | 61         |

| R_FLASH_SPI_W     | rite_Status3()                                            | 63         |

| R_FLASH_SPI_Se    | et_4byte_Address_Mode()                                   | 65         |

| R_FLASH_SPI_Re    | ead_Security()                                            | 66         |

| R_FLASH_SPI_Re    | ead_Data_Security_Page()                                  | 68         |

| R_FLASH_SPI_W     | rite_Data_Security_Page()                                 | 70         |

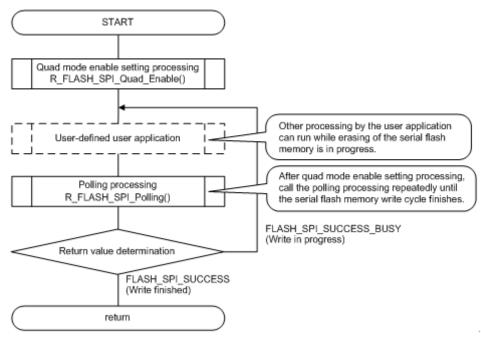

| R_FLASH_SPI_Qu    | uad_Enable()                                              | 72         |

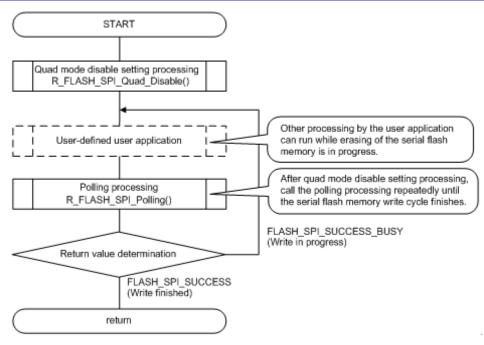

| R_FLASH_SPI_Qu    | uad_Disable()                                             | 75         |

| R_FLASH_SPI_Ge    | etVersion()                                               | 78         |

| R_FLASH_SPI_Se    | et_LogHdlAddress()                                        | 79         |

| R_FLASH_SPI_Lo    | g()                                                       | 80         |

| R_FLASH_SPI_1m    | ns_Interval()                                             | 81         |

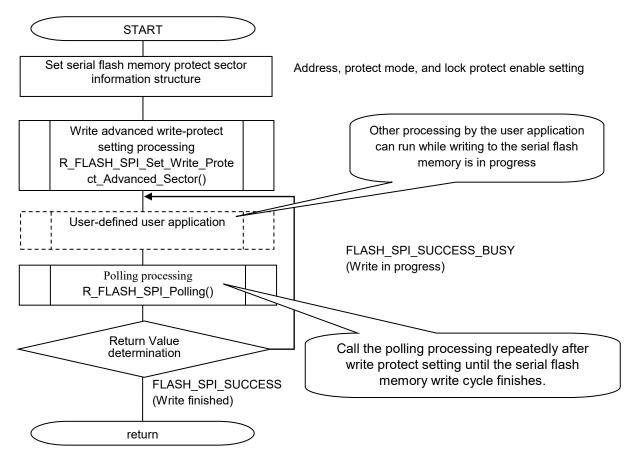

| R_FLASH_SPI_Se    | et_Write_Protect_Advanced_Sector()                        |            |

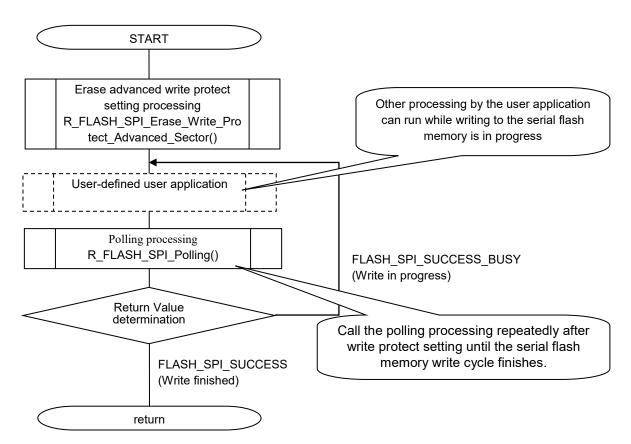

| R_FLASH_SPI_Er    | ase_Write_Protect_Advanced_Sector()                       |            |

| 4. Demo Projec    | cts                                                       | 88         |

| 4.1 rx65n_rsk_fl  | ash_spi_sample, rx65n_rsk_flash_spi_sample_gcc            |            |

| 4.2 rx671_ek_fla  | ash_spi_sample, rx671_ek_flash_spi_sample_gcc             |            |

| 5. Appendices.    |                                                           | 89         |

| 5.1 Confirmed C   | Operation Environment                                     |            |

| 5.2 Recommend     | led serial NOR flash memory products                      | 94         |

| 6. Reference D    | ocuments                                                  | 95         |

| Related Technica  | al Updates                                                | 95         |

| Revision History. |                                                           | 96         |

# 1. Overview

This software controls serial flash memory, using a Renesas microcontroller.

A clock synchronous single master control software specific to the microcontroller model used (available separately) is required.

Table 1.1 lists the peripheral devices used and their applications, and figure 1.1 shows a usage example.

The functions of the module are described briefly below.

- Block type device driver using the Renesas microcontroller as the master device and the serial flash memory as the slave device

- Control in SPI mode of target serial communication FIT module, using the microcontroller's built-in serial communication functionality (clock synchronous mode) (See 1.3.1, FIT Module–Related Application Notes.)

- RSPI FIT module

- QSPI FIT module

- SCI FIT module

- QSPIX FIT module

- RSCI FIT module

- Ability to control up to two serial flash memory devices

- Ability to make serial flash memory settings on a per-device basis

- · Support for both big-endian and little-endian byte order

#### Table 1.1 Peripheral Devices Used and Their Uses

| Peripheral Device                                                                      | Use                                                                                                                                                 |

|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Microcontroller's on-chip serial<br>communication function<br>(clock synchronous mode) | Communication with SPI slave device using serial communication<br>functionality (clock synchronous mode): Single or multiple channels<br>(required) |

| Port                                                                                   | For slave device selection control signals: A number of ports equal to the number of devices used are necessary (required).                         |

| MCU                                 |                                                              |                     |

|-------------------------------------|--------------------------------------------------------------|---------------------|

| Port<br>Clock synchronous<br>serial | Slave device select control signal<br>Clock output, data I/O | Serial flash memory |

#### Figure 1.1 Sample Configuration

### 1.1 FIT Support of Serial flash Memory Control Software

The serial flash memory control software can be combined with other FIT modules, allowing easy integration into your project.

The serial flash memory control software can also be integrated into your project as an API. For information on adding the serial flash memory control software, see 2.10, Adding the Driver to Your Project.

### **1.2 Overview of APIs**

Table 1.2 lists the API functions of the serial flash memory control software.

#### Table 1.2 API Functions

| Function Name                                     | Description                                                |

|---------------------------------------------------|------------------------------------------------------------|

| R_FLASH_SPI_Open()                                | Control software initialization processing                 |

| R_FLASH_SPI_Close()                               | Control software end processing                            |

| R_FLASH_SPI_Read_Status()                         | Status Register read processing                            |

| R_FLASH_SPI_Read_Status2()                        | Status Register 2 read processing                          |

| R_FLASH_SPI_Read_Status3()                        | Status Register 3 read processing                          |

| R_FLASH_SPI_Set_Write_Protect()                   | Write protect setting processing                           |

| R_FLASH_SPI_Write_Di()                            | WRDI command processing                                    |

| R_FLASH_SPI_Read_Data()*1                         | Data read processing                                       |

| R_FLASH_SPI_Write_Data_Page()*1                   | Data write (Single-page write) processing                  |

| R_FLASH_SPI_Erase()                               | Erase processing                                           |

| R_FLASH_SPI_Polling()                             | Polling processing                                         |

| R_FLASH_SPI_Read_ID()                             | ID read processing                                         |

| R_FLASH_SPI_GetMemoryInfo()                       | Memory size acquisition processing                         |

| R_FLASH_SPI_Read_Configuration()                  | Configuration Register read processing                     |

| R_FLASH_SPI_Write_Configuration()                 | Configuration Register write processing                    |

| R_FLASH_SPI_Write_Status()                        | Status Register 1 write processing                         |

| R_FLASH_SPI_Write_Status2()                       | Status Register 2 write processing                         |

| R_FLASH_SPI_Write_Status3()                       | Status Register 3 write processing                         |

| R_FLASH_SPI_Set_4byte_Address_Mode()              | 4-byte address mode setting processing                     |

| R_FLASH_SPI_Read_Security()                       | Security register read processing                          |

| R_FLASH_SPI_Read_Data_Security_Page()             | Data Security Page read processing                         |

| R_FLASH_SPI_Write_Data_Security_Page()            | Data Security Page write processing                        |

| R_FLASH_SPI_Quad_Enable()                         | Quad mode enable setting processing                        |

| R_FLASH_SPI_Quad_Disable()                        | Quad mode disable setting processing                       |

| R_FLASH_SPI_GetVersion()                          | Control software version information                       |

|                                                   | acquisition processing                                     |

| R_FLASH_SPI_Set_LogHdlAddress()                   | LONGQ FIT module handler address setting                   |

|                                                   | processing                                                 |

| R_FLASH_SPI_Log()                                 | Error log acquisition processing using LONGQ<br>FIT module |

| R_FLASH_SPI_1ms_Interval()*2                      | Clock synchronous single master control                    |

|                                                   | software interval timer counter processing                 |

| R_FLASH_SPI_Set_Write_Protect_Advanced_Sector()   | Write advanced write-protect setting                       |

|                                                   | processing                                                 |

| R_FLASH_SPI_Erase_Write_Protect_Advanced_Sector() | Erase advanced write-protect setting                       |

|                                                   | processing                                                 |

- Notes: 1. To speed up data transfers, align the start address with a 4-byte boundary when specifying transmit and receive data storage buffer pointers. There is a limitation on the data size when using DMAC transfer or DTC transfer. Refer to the documentation of the clock synchronous single master control software for the microcontroller used regarding the allowable data size setting range.

- 2. This function must be called at 1 ms intervals, using a hardware or software timer, in order to implement timeout detection when using DMAC transfer or DTC transfer.

# **1.3 Related Application Notes**

Application notes related to the serial flash memory control software are listed below. Refer to them alongside this application note.

### 1.3.1 FIT Module–Related Application Notes

- RX Family RSPI Module Using Firmware Integration Technology(R01AN1827)

- RX Family QSPI Clock Synchronous Single Master Control Module Using Firmware Integration Technology(R01AN1940)

- RX Family Application Note SCI Multi-Mode Module Using Firmware Integration Technology(R01AN1815)

- RX Family QSPIX Module Using Firmware Integration Technology(R01AN5685)

- RX Family RSCI Module Using Firmware Integration Technology(R01AN5759)

- RX Family DMAC Module Using Firmware Integration Technology(R01AN2063)

- RX Family DTC Module Using Firmware Integration Technology(R01AN1819)

- RX Family CMT Module Using Firmware Integration Technology(R01AN1856)

- RX Family GPIO Module Using Firmware Integration Technology(R01AN1721)

- RX Family MPC Module Using Firmware Integration Technology(R01AN1724)

- RX Family LONGQ Module Using Firmware Integration Technology(R01AN1889)

- RX Family Clock Synchronous Control Module for EEPROM Access Firmware Integration Technology(R01AN2325)

- RX Family Memory Access Driver Interface Module Using Firmware Integration Technology(R01AN4548)

# 1.4 Using Serial Flash Memory Module

### 1.4.1 Using Serial Flash Memory Module in C++ project

For C++ project, add Serial Flash Memory Module header file within extern "C"{}: extern "C"

{

```

#include "r_smc_entry.h"

#include "r flash spi if.h"

```

}

### 1.5 Hardware Settings

### **1.5.1 Hardware Configuration Example**

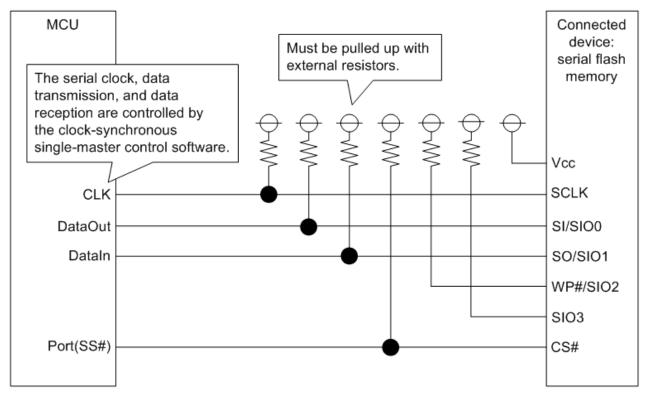

Figure 1.2 is a connection diagram. The pin names differ according to the microcontroller and serial interface used. Refer to the listing of pins and functions in table 1.3 and assign pins on the specific microcontroller used.

To achieve high-speed operation, consider adding damping resistors or capacitors to improve the circuit matching of the various signal lines.

### 1.5.1.1 Single-SPI Configuration Example

An example wiring diagram when using single-SPI is shown below.

- The names of the pins used by the microcontroller for serial I/O depend on the microcontroller version.

- In the example WP# and RESET# are not used. When using WP# and RESET#, be sure to check the specifications of the device to be used.

#### Figure 1.2 Sample Wiring Diagram for MCU and SPI Slave Device Using Single-SPI

| Table 1.3 | Single-SPI Pins Used and Functions |

|-----------|------------------------------------|

|-----------|------------------------------------|

| Pin Name                        | I/O    | Description                      |

|---------------------------------|--------|----------------------------------|

| CLK                             | Output | Clock output                     |

| DataOut                         | Output | Master data output               |

| DataIn                          | Input  | Master data input                |

| Port (Port (SS#) of figure 1.2) | Output | Slave device select (SS#) output |

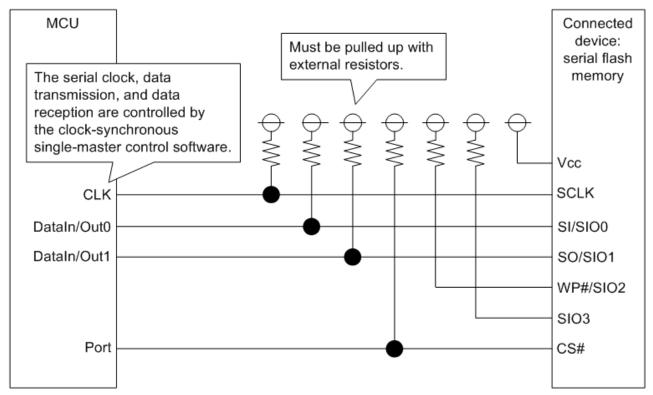

### 1.5.1.2 Dual-SPI Configuration Example

An example wiring diagram when using dual-SPI is shown below.

In order to use dual-SPI the target microcontroller must be equipped with quad serial peripheral interface functionality.

- The names of the pins used by the microcontroller for serial I/O depend on the microcontroller version.

- In the example WP# and RESET# are not used. When using WP# and RESET#, be sure to check the specifications of the device to be used.

#### Figure 1.3 Sample Wiring Diagram for MCU and SPI Slave Device Using Dual-SPI

| Pin Name                        | I/O    | Description                      |

|---------------------------------|--------|----------------------------------|

| CLK                             | Output | Clock output                     |

| DataIn/Out0                     | I/O    | Master data I/O 0                |

| DataIn/Out1                     | I/O    | Master data I/O 1                |

| Port (Port (SS#) of figure 1.3) | Output | Slave device select (SS#) output |

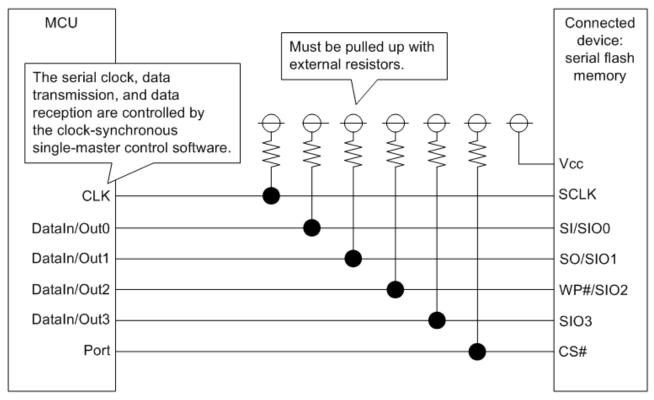

### 1.5.1.3 Quad-SPI Configuration Example

An example wiring diagram when using quad-SPI is shown below.

In order to use quad-SPI the target microcontroller must be equipped with quad serial peripheral interface functionality.

- The names of the pins used by the microcontroller for serial I/O depend on the microcontroller version.

- In the example WP# and RESET# are not used. When using WP# and RESET#, be sure to check the specifications of the device to be used.

### Figure 1.4 Sample Wiring Diagram for MCU and SPI Slave Device Using Quad-SPI

| Table 1.5 | <b>Quad-SPI</b> | Pins | Used and | d Functions |

|-----------|-----------------|------|----------|-------------|

|-----------|-----------------|------|----------|-------------|

| Pin Name                        | I/O    | Description                      |

|---------------------------------|--------|----------------------------------|

| CLK                             | Output | Clock output                     |

| DataIn/Out0                     | I/O    | Master data I/O 0                |

| DataIn/Out1                     | I/O    | Master data I/O 1                |

| DataIn/Out2                     | I/O    | Master data I/O 2                |

| DataIn/Out3                     | I/O    | Master data I/O 3                |

| Port (Port (SS#) of figure 1.4) | Output | Slave device select (SS#) output |

### 1.6 Software

### **1.6.1** Operation Overview

Utilizing the clock synchronous serial communication functionality of the microcontroller, clock synchronous single master control is implemented using the internal clock.

Refer to the User's Manual: Hardware of the microcontroller and the data sheet of the slave device to determine the usable serial clock frequencies.

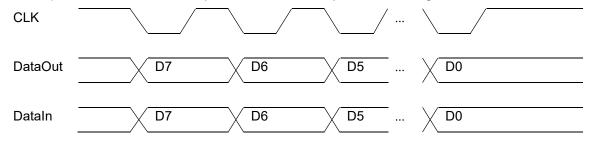

#### 1.6.1.1 Single-SPI Control

Control is performed in SPI mode 3 (CPOL = 1, CPHA = 1), as shown in figure 1.5.

•MCU->Slave device transmission:Transmission of transmit data is started on the falling edge of the transfer clock.

•Slave device ->MCU reception : The receive data is taken in on the rising edge of the transfer clock.

·MSB-first mode transfer.

•The level of the CLK pin is held high when no transfer processing is in progress.

#### Figure 1.5 Timing of Controllable Slave Devices for Single-SPI

#### 1.6.1.2 Dual-SPI Control

Control is performed in SPI mode 3 (CPOL = 1, CPHA = 1), as shown in figure 1.6. CLK DataIn/Out0 D6 D4 D2 D0 DataIn/Out1 D7 D5 D3 D1

•MCU->Slave device transmission:Transmission of transmit data is started on the falling edge of the transfer clock.

•Slave device ->MCU reception : The receive data is taken in on the rising edge of the transfer clock.

•MSB-first mode transfer.

•The level of the CLK pin is held high when no transfer processing is in progress.

Figure 1.6 Timing of Controllable Slave Devices for Dual-SPI

### 1.6.1.3 Quad-SPI Control

| Control is perfo | rmed in SPI mode 3 (CF | POL = 1, CPHA = 1), as shown in figure 1.7. |

|------------------|------------------------|---------------------------------------------|

| CLK              |                        |                                             |

| DataIn/Out0      | D4                     | D0                                          |

| DataIn/Out1      | D5                     | D1                                          |

| DataIn/Out2      | D6                     | D2                                          |

| DataIn/Out3      | D7                     | D3                                          |

•MCU->Slave device transmission:Transmission of transmit data is started on the falling edge of the transfer clock.

·Slave device ->MCU reception : The receive data is taken in on the rising edge of the transfer clock.

•MSB-first mode transfer.

•The level of the CLK pin is held high when no transfer processing is in progress.

#### Figure 1.7 Timing of Controllable Slave Devices for Quad-SPI

### 1.6.2 Serial Flash Memory Chip Select Pin Control

The chip select pin of the serial flash memory is connected to a port of the microcontroller and controlled by general port output from the microcontroller.

Control is performed in the software to wait during the chip select setup time of the serial flash memory, which is the time interval from the falling edge of the serial flash memory's chip select (microcontroller port (SS#)) signal to the falling edge of the serial flash memory's clock (microcontroller CLK) signal.

In like manner, control is performed in the software to wait during the chip select hold time of the serial flash memory, which is the time interval from the rising edge of the serial flash memory's clock (microcontroller CLK) signal to the rising edge of the serial flash memory's chip select (microcontroller port (SS#)) signal.

In this module the wait intervals for the chip select setup time and chip select hold time are each approximately 1  $\mu$ s.

### 1.6.3 Software Structure

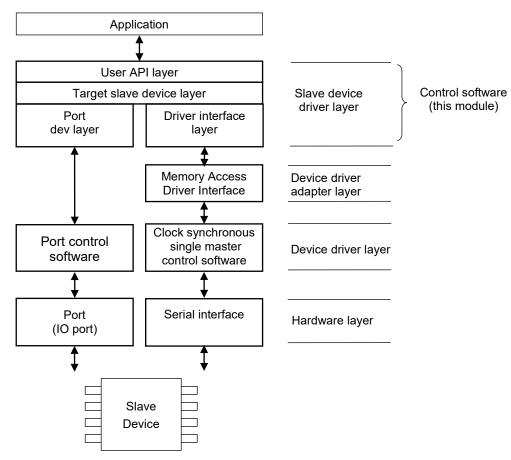

Figure 1.8 shows the software structure.

Use the control software to create software for controlling slave devices.

Figure 1.8 Software Structure

(a) User API layer (r\_flash\_spi.c)

The user interface, this portion of the software is not dependent on lower-layer device drivers.

- (b) Target slave device layer (r\_flash\_spi\_type.c) The serial flash memory control module, this portion of the software is not dependent on lower-layer device drivers.

- (c) Driver interface (I/F) layer (r\_flash\_spi\_drvif.c)

The common module for connecting to lower-layer device drivers. A separate driver interface function is required to match the clock synchronous single master control module for each microcontroller model.

- (d) Port dev layer (r\_flash\_spi\_dev\_port.c) The control module for controlling the slave device select signal (SS#) with a microcontroller port. The GPIO FIT module and MPC FIT module can be used.

- (e) Application

Sample code for controlling MX25L, MX66L, MX25R, or MX25U family serial NOR flash memory, manufactured by Macronix International Co., Ltd., is provided for reference.

Sample code for controlling AT25QF family serial NOR flash memory, manufactured by Renesas Electronics., is provided for reference.

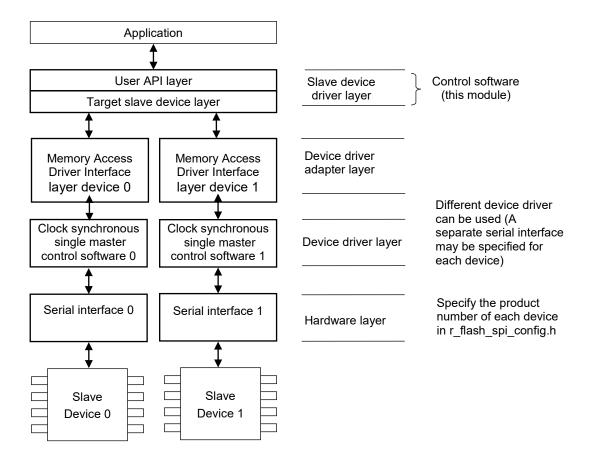

### 1.6.4 Relationship Between Control Software and Clock Synchronous Single Master Control Software

The method whereby the control software and the clock synchronous single master control software are combined is described below.

Control of up to two slave devices, using up to two clock synchronous single master control modules, is supported. Register the clock synchronous single master control module (or modules) used as the driver interface function (or functions).

As shown below, it is possible to specify a separate driver for each device. For each device number, create processing code using the device driver API in the driver interface function that constitutes the driver interface layer.

Figure 1.9 Software Configuration with Clock Synchronous Single Master Control Modules

### RX Family Clock Synchronous Control Module for Serial NOR Flash Memory Access

### 1.6.5 Data Buffers and Transmit/Receive Data

The control software is a block type device driver that sets transmit and receive data pointers as arguments. The arrangement of data in the data buffer in RAM and the transmit and receive sequences are illustrated below. Regardless of the endian mode and the serial communication function, data is transmitted in the order in which it is arranged in the transmit data buffer, and it is written to the receive data buffer in the order in which it is received.

Master transmit

Transmit data buffer in RAM (numbers indicate bytes)

| 0    | 1      |                 | 508  | 509 | 510 | 511     |

|------|--------|-----------------|------|-----|-----|---------|

| Data | transm | ission sequence | <br> |     |     | <b></b> |

|      |        |                 |      |     |     |         |

Writing to slave device (numbers indicate bytes)

| 0    | 1       |             | 508 | 509 | 510 | 511 |

|------|---------|-------------|-----|-----|-----|-----|

| Data | recepti | on sequence |     |     |     | →   |

Master receive

Reading from slave device (numbers indicate bytes)

| 0    | 1 | ••• | 508 | 509 | 510 | 511 |

|------|---|-----|-----|-----|-----|-----|

| Data |   |     |     |     |     |     |

Data transmission sequence -

Data buffer in RAM (numbers indicate bytes)

| 0      | 1       | •••               | 508 | 509 | 510 | 511 |

|--------|---------|-------------------|-----|-----|-----|-----|

| Writin | g to re | ceive data buffer |     |     |     |     |

#### Figure 1.10 Data Buffers and Transmit/Receive Data

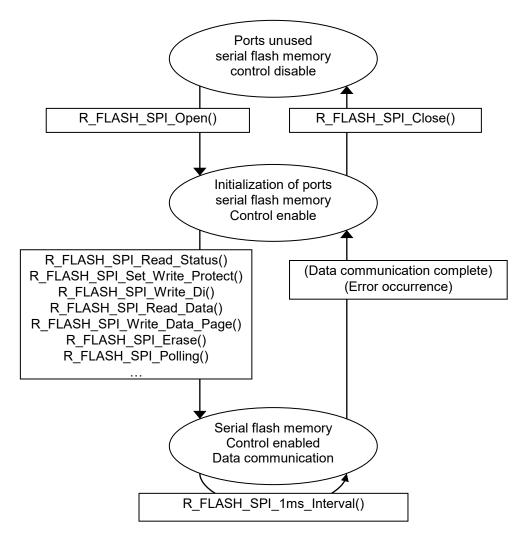

### 1.6.6 State Transition Diagram

Figure 1.11 State Transition Diagram

### 2. API Information

The names of the APIs of the control software follow the Renesas API naming standard.

### 2.1 Hardware Requirements

The microcontroller used must support the following functionality. Note that separate clock synchronous single master control software is required.

I/O port

### 2.2 Software Requirements

When used with FIT support enabled, the control software is dependent on the following packages.

- r\_bsp Rev.5.00 or higher

- r\_memdrv\_rx Rev.1.04 or higher

- r\_rspi\_rx (when using the RSPI FIT module)

- r\_qspix\_rx (when using the QSPIX FIT module)

- r\_rsci\_rx (when using the RSCI FIT module)

- r\_qspi\_smstr\_rx (when using the QSPI FIT module for clock synchronous single master control)

- r\_scifa\_smstr\_rx (when using the SCIFA FIT module for clock synchronous single master control)

- r\_dmaca\_rx (only when using the DMACA FIT module for DMAC transfers)

- r\_dtc\_rx (only when using the DTC FIT module for DTC transfers)

- r\_cmt\_rx (only when using DMAC transfer or DTC transfer and the compare match timer (CMT) FIT module) Another timer or a software timer can be used instead.

- r\_gpio\_rx (only when using the GPIO and MPC FIT modules to control the GPIO)

- r\_mpc\_rx (only when using the GPIO and MPC FIT modules to control the MPC)

### 2.3 Supported Toolchain

The operation of the control software has been confirmed with the toolchain listed in 5.1,Confirmed Operation Environment.

### 2.4 Header Files

All the API calls and interface definitions used are listed in r\_flash\_spi\_if.h.

Configuration options for individual builds are selected in r\_flash\_spi\_config.h. The included statements should be in the following order.

```

#include "r_flash_spi_if.h"

#include "r flash spi config.h"

```

### 2.5 Integer Types

This project uses ANSI C99. These types are defined in stdint.h.

# 2.6 Compile Settings

The configuration option settings for the control software are specified in r\_flash\_spi\_config.h. The option names and setting values are described below.

| Configuration options in <i>r_flash_spi_config.h</i>                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| #define FLASH_SPI_CFG_WEL_CHK<br>Note: The default value is "1 (enabled)".                                                                                                                                                                                                                                                                                                                     | Selects whether or not the WEL bit is checked after the WREN command is issued. (1: enabled, 0: disabled)                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| #define FLASH_SPI_CFG_LONGQ_ENABLE<br>Note: The default value is "0 (disabled)".                                                                                                                                                                                                                                                                                                               | Selects whether or not error log acquisition processing is<br>performed for debugging, when using the BSP environment of a<br>FIT module. (1: enabled, 0: disabled)<br>When this option is set to "disabled", code for the relevant<br>processing is omitted.<br>When this option is set to "enabled", code for the relevant<br>processing is included.<br>To use this functionality, the LONGQ FIT module is also<br>required.<br>In addition, enable #define xxx_LONGQ_ENABLE in the clock<br>synchronous single master control software of the specified<br>device. |  |  |  |  |  |

| #define FLASH_SPI_CFG_USE_GPIO_MPC_FIT<br>Note: The default value is "0 (disabled)".<br>#define FLASH_SPI_CFG_DEVx_INCLUDED                                                                                                                                                                                                                                                                    | Selects whether the GPIO FIT module or MPC FIT module is<br>used to control the SS# pin. (1: enabled, 0: disabled)<br>When this option is set to "disabled", neither the GPIO FIT<br>module nor the MPC FIT module controls the SS# pin.<br>When this option is set to "enabled", the GPIO FIT module or<br>MPC FIT module controls the SS# pin.<br>To use this functionality, the GPIO FIT module or MPC FIT<br>module is also required.<br>This definition is related to device x. (1: enabled, 0: disabled)                                                         |  |  |  |  |  |

| Note: The default value for device 0 is "1 (enabled)".<br>The "x" in DEVx represents the device number $(x = 0 \text{ or } 1)$ .                                                                                                                                                                                                                                                               | This option must be set to "enabled" for at least one device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| <ul> <li>#define FLASH_SPI_CFG_DEVx_MX25L</li> <li>#define FLASH_SPI_CFG_DEVx_MX66L</li> <li>#define FLASH_SPI_CFG_DEVx_MX25R</li> <li>#define FLASH_SPI_CFG_DEVx_AT25QF</li> <li>#define FLASH_SPI_CFG_DEVx_MX25U</li> <li>Note: The default values for device 0 are<br/>FLASH_SPI_CFG_DEVx_MX25L: 1, other: 0.<br/>The "x" in DEVx represents the device number<br/>(x = 0 or 1).</li> </ul> | Select only one serial flash memory device to be controlled for device x (1: control target, 0: not control target).                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| RX Family | Clock S | vnchronous | Control Modul | le for Serial | NOR Flash   | Memory Access  |

|-----------|---------|------------|---------------|---------------|-------------|----------------|

|           |         | ynchionous | Control Modul |               | INOIN LIASI | I MEMOLY ACCES |

| Configuration opti                                     | ons in <i>r_flash_spi_config.h</i>                                |

|--------------------------------------------------------|-------------------------------------------------------------------|

| #define FLASH_SPI_CFG_DEVx_SIZE_512K                   | Select only one serial flash memory capacity to be controlled for |

| #define FLASH_SPI_CFG_DEVx_SIZE_2M                     | device x (1: control target, 0: not control target).              |

| #define FLASH_SPI_CFG_DEVx_SIZE_4M                     |                                                                   |

| #define FLASH_SPI_CFG_DEVx_SIZE_8M                     |                                                                   |

| #define FLASH_SPI_CFG_DEVx_SIZE_16M                    |                                                                   |

| #define FLASH_SPI_CFG_DEVx_SIZE_32M                    |                                                                   |

| #define FLASH_SPI_CFG_DEVx_SIZE_64M                    |                                                                   |

| #define FLASH_SPI_CFG_DEVx_SIZE_128M                   |                                                                   |

| #define FLASH_SPI_CFG_DEVx_SIZE_256M                   |                                                                   |

| #define FLASH_SPI_CFG_DEVx_SIZE_512M                   |                                                                   |

| #define FLASH_SPI_CFG_DEVx_SIZE_1G                     |                                                                   |

| Note: The default values for device 0 are              |                                                                   |

| FLASH_SPI_CFG_DEVx_SIZE_64M: 1,<br>other: 0.           |                                                                   |

| The "x" in DEVx represents the device number           |                                                                   |

| (x = 0  or  1).                                        |                                                                   |

| #define FLASH_SPI_CS_DEVx_CFG_PORTNO                   | Specifies the port number assigned to SS# for device x.           |

| Note: The default value for device 0 is "X".           | Enclose the setting value in single quotation marks (' ').        |

| The "x" in DEVx represents the device number ( $x = 0$ | Configure Device x Port Number with 0 - 9, A - X.                 |

| or 1).                                                 |                                                                   |

| #define FLASH_SPI_CS_DEVx_CFG_BITNO                    | Specifies the bit number assigned to SS# for device x.            |

| Note: The default value for device 0 is "'0".          | Enclose the setting value in single quotation marks (' ').        |

| The "x" in DEVx represents the device number ( $x = 0$ | Configure Device x Bit Number with 0 – 7.                         |

| or 1).                                                 |                                                                   |

### 2.7 Arguments

The structure for the arguments of the API functions is shown below. This structure is listed in r\_flash\_spi\_if.h, along with the prototype declarations of the API functions.

```

/* FLASH Memory information */

typedef struct

{

/* Address to issue a command */

/* Number of bytes to be read/written */

uint32_t addr;

uint32_t cnt;

uint32_t data_cnt;

/* Temporary counter or Number of bytes to be written in a page

*/

uint8_t * p_data; /* Data storage buffer pointer

flash_spi_opmode_t op_mode; /* SPI operating mode; ignore it when

*/

using write/read data in a Security register page */

/* 20 bytes

*/

} flash spi info t;

/* FLASH Memory size information */

typedef struct

{

uint32_t mem_size;

uint32_t wpag_size;

/* Max memory size

*/

/* Write page size

*/

*/

} flash spi mem info t;

/* 8 bytes

/* FLASH Memory erase information */

typedef struct

{

uint32_t addr; /* Address to issue a command

flash_spi_erase_mode_t mode; /* Mode of erase

*/

*/

*/

} flash spi erase info t;

/* 8 bytes

/* FLASH Memory register information */

typedef struct

{

uint8_t status;

uint8_t config1;

uint8_t config2;

uint8_t rsv[1];

/* Status register

*/

/* Configuration or Configuration-1 register */

/* Configuration-2 register

*/

*/

/* Flash memory advanced sector protection information */

typedef struct

{

uint32 t addr;

/* Address to issue a command */

flash_spi_protect_mode_t protect_mode; /* Advanced protection mode */

bool lock_protect_enable; /* prevent further modification*/

} flash spi protect sector info t;

```

### 2.8 Code Size

The sizes of ROM, RAM and maximum stack usage associated with this module are listed below.

The ROM (code and constants) and RAM (global data) sizes are determined by the build-time configuration options described in 2.6, Compile Settings.

The values in the table below are confirmed under the following conditions.

Module Revision: r\_flash\_spi rev.3.50

Compiler Version: Renesas Electronics C/C++ Compiler Package for RX Family V3.06.00

(The option of "-lang = c99" is added to the default settings of the integrated development environment.)

GCC for Renesas RX 8.3.0.202411

(The option of "-std = gnu99" is added to the default settings of the integrated development environment.)

IAR C/C++ Compiler for Renesas RX version 5.10.1

(The default settings of the integrated development environment.)

Configuration Options: Default settings

Operating frequency: RX113 ICLK: 32 MHz, PCLKB: 32 MHz

RX231 ICLK: 54 MHz, PCLKB: 27 MHz

RX64M ICLK: 120MHz, PCLKA: 120MHz, PCLKB: 60MHz

RX71M ICLK: 240MHz, PCLKA: 120MHz, PCLKB: 60MHz

Operating voltage: 3.3V

Endian: Little endian

The clock synchronous single master control software: RSPI

Data transfer mode: Software

Confirmation conditions: r\_flash\_spi.c, r\_flash\_spi\_dev\_port\_iodefine.c, r\_flash\_spi\_drvif.c, r\_flash\_spi\_type.c, r\_flash\_spi\_type\_sub.c

| ROM, RAM and Stack Code Sizes |          |                  |             |              |  |  |

|-------------------------------|----------|------------------|-------------|--------------|--|--|

| Device                        | Category | Memory Used      |             |              |  |  |

|                               |          | Renesas Compiler | GCC         | IAR Compiler |  |  |

| RX113                         | ROM      | 7,316 bytes      | 8,756 bytes | 15,772 bytes |  |  |

|                               | RAM      | 9 bytes          | 0 bytes     | 36 bytes     |  |  |

|                               | STACK    | 80 bytes         | -           | 148 bytes    |  |  |

| RX231                         | ROM      | 7,331 bytes      | 8,748 bytes | 15,772 bytes |  |  |

|                               | RAM      | 9 bytes          | 0 bytes     | 36 bytes     |  |  |

|                               | STACK    | 80 bytes         | -           | 148 bytes    |  |  |

# RX Family Clock Synchronous Control Module for Serial NOR Flash Memory Access

|        | ROM, RAM and Stack Code Sizes |                  |             |              |  |  |  |

|--------|-------------------------------|------------------|-------------|--------------|--|--|--|

| Device | Category                      | Memory Used      |             |              |  |  |  |

|        |                               | Renesas Compiler | GCC         | IAR Compiler |  |  |  |

| RX64M  | ROM                           | 7,331 bytes      | 8,748 bytes | 16,564 bytes |  |  |  |

|        | RAM                           | 9 bytes          | 0 bytes     | 38 bytes     |  |  |  |

|        | STACK                         | 80 bytes         | -           | 148 bytes    |  |  |  |

| RX71M  | ROM                           | 7,331 bytes      | 8,764 bytes | 16,560 bytes |  |  |  |

|        | RAM                           | 9 bytes          | 128 bytes   | 50 bytes     |  |  |  |

|        | STACK                         | 80 bytes         | -           | 148 bytes    |  |  |  |

### 2.9 Return Values

The API function return values are shown below. This enumerated type is listed in r\_flash\_spi\_if.h, along with the prototype declarations of the API functions.

```

typedef enum e_flash_status

{

FLASH_SPI_SUCCESS_BUSY = 1, /* Successful operation (EERPOM is busy) */

FLASH_SPI_SUCCESS = 0, /* Successful operation */

FLASH_SPI_ERR_PARAM = -1, /* Parameter error */

FLASH_SPI_ERR_HARD = -2, /* Hardware error */

FLASH_SPI_ERR_MP = -4, /* Write-protection error */

FLASH_SPI_ERR_TIMEOUT = -6, /* time out error */

FLASH_SPI_ERR_OTHER = -7, /* Other error */

FLASH_SPI_ERR_WP_ADVANCED = -8 /* Advanced write-protection error */

} flash_spi_status_t;

```

### 2.10 Adding the Driver to Your Project

This module must be added to each project in which it is used. Renesas recommends the method using the Smart Configurator described in (1) or (2) or (4) below. However, the Smart Configurator only supports some RX devices. Please use the methods of (3) for RX devices that are not supported by the Smart Configurator.

- (1) Adding the FIT module to your project using the Smart Configurator in e<sup>2</sup> studio By using the Smart Configurator in e<sup>2</sup> studio, the FIT module is automatically added to your project. Refer to "RX Smart Configurator User's Guide: e<sup>2</sup> studio (R20AN0451)" for details.

- (2) Adding the FIT module to your project using the Smart Configurator in CS+ By using the Smart Configurator Standalone version in CS+, the FIT module is automatically added to your project. Refer to "RX Smart Configurator User's Guide: CS+ (R20AN0470)" for details.

- (3) Adding the FIT module to your project in CS+ In CS+, please manually add the FIT module to your project. Refer to "RX Family Adding Firmware Integration Technology Modules to CS+ Projects (R01AN1826)" for details.

- (4) Adding the FIT module to your project using the Smart Configurator in IAREW By using the Smart Configurator Standalone version, the FIT module is automatically added to your project. Refer to "RX Smart Configurator User's Guide: IAREW (R20AN0535)" for details.

### 2.11 Using the Serial Flash Memory Control Software in Other Than an FIT Module Environment

To use the serial flash memory control software in an environment in which FIT modules such as r\_bsp are not used, perform the following.

Comment out the line #include "platform.h" in #r\_flash\_spi\_if.h.

Include the following header files in #r\_flash\_spi\_if.h.

#include "iodefine.h"

#include <stdint.h>

#include <stdbool.h>

#include <stddef.h>

#include <machine.h>

Disable the option #define FLASH\_SPI\_CFG\_USE\_FIT in #r\_flash\_spi\_if.h.

Add the definition #define FLASH\_SPI\_CFG\_xxx (replacing xxx with the microcontroller name using all capital letters) to #r\_flash\_spi\_if.h. For example, for the RX64M microcontroller use the string FLASH\_SPI\_CFG\_RX64M.

In # r\_flash\_spi\_if.h add the enum definitions shown below. Also add the #define definitions shown below. Set the system clock (ICLK) value in BSP\_ICLK\_HZ. Note that it is possible that some of these definitions may duplicate other FIT module definitions. Insert the lines #ifndef SMSTR\_WAIT and #define SMSTR\_WAIT at the beginning of the definitions and insert #endif as the last line.

```

#ifndef SMSTR_WAIT

#define SMSTR_WAIT

typedef enum

{

BSP_DELAY_MICROSECS = 1000000,

BSP_DELAY_MILLISECS = 1000,

BSP_DELAY_SECS = 1

} bsp_delay_units_t;

#define BSP_ICLK_HZ (12000000) /* ICLK = 120MHz */

#endif /* #ifndef SMSTR WAIT */

```

### 2.12 Pin States

Table 2.1 lists the pin states after a power on reset and after execution of various API functions.

As shown in 1.5.1 (1), Single-SPI Control, this module supports SPI mode 3 (CPOL = 1, CPHA = 1). Regardless of the hardware configuration, **after a power on reset, control the GPIO from the user side and put the select pin into the high-output state to use this mode**.

Also, the slave device select pin is in the GPIO high-output state after R\_FLASH\_SPI\_Close() runs. Review the pin settings if necessary.

Table 2.1 Pin States after Function Execution

| Function Name             | Slave Device Select Pin* |

|---------------------------|--------------------------|

| (After power on reset)    | GPIO input state         |

| Before R_FLASH_SPI_Open() | GPIO high-output state   |

|                           | Set on user side         |

| After R_FLASH_SPI_Open()  | GPIO high-output state   |

|                           | Set by this module       |

| After R_FLASH_SPI_Close() | GPIO high-output state   |

|                           | Set by this module       |

Note: \* Use an external resistor to pull up the slave device select pin. See 1.5.1, Hardware Configuration Example.

### 2.13 "for", "while" and "do while" statements

In this module, "for", "while" and "do while" statements (loop processing) are used in processing to wait for register to be reflected and so on. For these loop processing, comments with "WAIT\_LOOP" as a keyword are described. Therefore, if user incorporates fail-safe processing into loop processing, user can search the corresponding processing with "WAIT\_LOOP".

The following shows example of description.

```

while statement example :

/* WAIT LOOP */

while(0 == SYSTEM.OSCOVFSR.BIT.PLOVF)

{

/* The delay period needed is to make sure that the PLL has stabilized. */

}

for statement example :

/* Initialize reference counters to 0. */

/* WAIT LOOP */

for (i = 0; i < BSP REG PROTECT TOTAL ITEMS; i++)

{

g_protect_counters[i] = 0;

}

do while statement example :

/* Reset completion waiting */

do

{

reg = phy read(ether channel, PHY REG CONTROL);

count++;

} while ((reg & PHY CONTROL RESET) && (count < ETHER CFG PHY DELAY RESET)); /* WAIT LOOP */

```

### 3. API Functions

# R\_FLASH\_SPI\_Open()

This function is run first when using the APIs of the serial flash memory control software.

### Format

flash\_spi\_status\_t R\_FLASH\_SPI\_Open( uint8\_t devno

)

### Parameters

*devno* Device number (0, 1)

**Return Values**

FLASH\_SPI\_SUCCESS FLASH\_SPI\_ERR\_PARAM /\* Successful operation \*/ /\* Parameter error \*/

### **Properties**

Prototype declarations are contained in r\_flash\_spi\_if.h.

### Description

Initializes the slave device select pin of the device number specified by the argument devno. After initialization the pin is in the general output port high-output state. Do not call this function when communication is in progress. Communication cannot be guaranteed if the function is called when communication is in progress.

#### Example

flash\_spi\_status\_t ret = FLASH\_SPI\_SUCCESS;

ret = R\_FLASH\_SPI\_Open(FLASH\_SPI\_DEV0);

### **Special Notes**

After calling this user API function, it is recommended that R\_FLASH\_SPI\_Polling() be used to confirm that the serial flash memory write cycle has completed. The next read or write processing will not be accepted while the serial flash memory write cycle is in progress.

However, it is possible to access the serial flash memory during the write cycle by, for example, issuing a system reset while the serial flash memory write cycle is in progress and restarting serial flash memory control from the beginning.

### R\_FLASH\_SPI\_Close()

This function is used to close the serial flash memory control software when it is in use.

#### Format

```

flash_spi_status_t R_FLASH_SPI_Close(

uint8_t devno

```

)

### Parameters

devno

Device number (0, 1)

### **Return Values**

FLASH\_SPI\_SUCCESS/\* Successful operation \*/FLASH\_SPI\_ERR\_PARAM/\* Parameter error \*/FLASH\_SPI\_ERR\_OTHER/\* Other error \*/

#### **Properties**

Prototype declarations are contained in r\_flash\_spi\_if.h.

#### Description

Sets the slave device select pin of the device number specified by the argument devno to function as a general I/O port. After the function runs, the pin is in the general output port high-output state. Do not call this function when communication is in progress. Communication cannot be guaranteed if the function is called when communication is in progress.

#### Example

flash\_spi\_status\_t ret = FLASH\_SPI\_SUCCESS; ret = R FLASH SPI Close(FLASH SPI DEVO);

#### **Special Notes**

The state of the slave device select pin after this function is called is different from its state after a reset (general input port state). Review the pin settings if necessary.

Before calling this user API function, it is recommended that R\_FLASH\_SPI\_Polling() be used to confirm that the serial flash memory write cycle has completed. This makes it possible to restart serial flash memory control because the serial flash memory has not transitioned to the write cycle.

### **R\_FLASH\_SPI\_Read\_Status()**

This function is used to read the status register.

#### Format

```

flash_spi_status_t R_FLASH_SPI_Read_Status(

uint8_t devno,

uint8_t * p_status

)

```

#### **Parameters**

devno

Device number (0, 1)

\* p\_status

Status register storage buffer (size: 1 byte)

#### **Return Values**

| FLASH_SPI_SUCCESS   | /* Successful operation */                           |

|---------------------|------------------------------------------------------|

| FLASH_SPI_ERR_PARAM | /* Parameter error */                                |

| FLASH_SPI_ERR_HARD  | /* Hardware error */                                 |

| FLASH_SPI_ERR_OTHER | /* Other task has acquired clock synchronous single  |

|                     | master control software resources, or other error */ |

### **Properties**

Prototype declarations are contained in r\_flash\_spi\_if.h.

### Description

Reads the status register and stores the contents in p\_status. The following information is stored in p\_status: Refer to the data sheet for information on protected areas and protected bits.

• <MX25L, MX66L, MX25R, or MX25U family serial NOR flash memory of Macronix International Co., Ltd.>

#### Table 3.1 MX25L, MX66L, MX25R, or MX25U family serial NOR flash memory

| Bit 7          | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1         | Bit 0        |

|----------------|--------------|--------------|--------------|--------------|--------------|---------------|--------------|

| SRWD           | QE           | BP3          | BP2          | BP1          | BP0          | WEL           | WIP          |

| (status        | (quad        | (level of    | (level of    | (level of    | (level of    | (write        | (write in    |

| register write | enable)      | protected    | protected    | protected    | protected    | enable        | progress     |

| protect)       |              | block)       | block)       | block)       | block)       | latch)        | bit)         |

| 1 = status     | 1 = quad     | *1           | *1           | *1           | *1           | 1 = write     | 1 = write    |

| register write | enable       |              |              |              |              | enable        | operation    |

| disable        | 0 = not quad |              |              |              |              | 0 = not write | 0 = not in   |

|                | enable       |              |              |              |              | enable        | write        |

|                |              |              |              |              |              |               | operation    |

| Non-volatile   | Non-volatile | Non-volatile | Non-volatile | Non-volatile | Non-volatile | Volatile bit  | Volatile bit |

| bit            | bit          | bit          | bit          | bit          | bit          |               |              |

Note 1: Set to 1, a designated memory area is protected from PROGRAM and ERASE operations.

<AT25QF family serial NOR flash memory of Renesas Electronics.>

| Bit | Mnemonic | Name                             | Туре |    | Description                                |

|-----|----------|----------------------------------|------|----|--------------------------------------------|

| 7   | SRP0     | Status Register Protection bit 0 | R/W  |    | *4                                         |

| 6   | SEC      | Block Protection                 | R/W  | *3 | *4                                         |

| 5   | ТВ       | Top or Bottom Protection         | R/W  | *2 | *4                                         |

| 4   | BP2      | Block Protection bit 2           | R/W  | *1 | *4                                         |

| 3   | BP1      | Block Protection bit 1           | R/W  | *1 | *4                                         |

| 2   | BP1      | Block Protection bit 0           | R/W  | *1 | *4                                         |

| 1   | WEL      | Write Enable Latch Status        | R    | 0  | Device is not Write Enable (default).      |

| I   | VVEL     |                                  | ĸ    | 1  | Device is Write Enable.                    |

| 0   | RDY /BSY | Ready/Busy Status                | Б    | 0  | Device is ready.                           |

| 0   |          |                                  | R    | 1  | Device is busy with an internal operation. |

Table 3.2 AT25QF family serial NOR flash memory

Note 1: Set to 0 or 1, determine how much of the array is protected.

Note 2: Set to 0 or 1, selects between top of the array or bottom of the array protection.

Note 3: Set to 0 or 1, selects between large and small block size protection.

Note 4: See the specification of Flash memory.

### Example

```

flash_spi_status_t ret = FLASH_SPI_SUCCESS;

uint32_t stat = 0;

```

ret = R FLASH SPI Read Status(FLASH SPI DEV0, &stat);

#### **Special Notes**

The clock synchronous single master control software resources are acquired at the start of the processing, and the resources are released and the end of the processing.

### R\_FLASH\_SPI\_Read\_Status2()

This function is used to read the status register 2. It is a dedicated API function for AT25QF family serial NOR flash memory of Renesas Electronics.

#### Format

### Parameters

devno

Device number (0, 1)

\* p\_status

Status register storage buffer (size: 1 byte)

### **Return Values**

| FLASH_SPI_SUCCESS   | /* Successful operation */                           |

|---------------------|------------------------------------------------------|

| FLASH_SPI_ERR_PARAM | /* Parameter error */                                |

| FLASH_SPI_ERR_HARD  | /* Hardware error */                                 |

| FLASH_SPI_ERR_OTHER | /* Other task has acquired clock synchronous single  |

|                     | master control software resources, or other error */ |

### **Properties**

Prototype declarations are contained in r\_flash\_spi\_if.h.

#### Description

Reads the status register 2 and stores the contents in p\_status. The following information is stored in p\_status:

#### • <AT25QF family serial NOR flash memory of Renesas Electronics.>

| Bit     | Mnemonic | Name                          | Туре | Description |                                                   |

|---------|----------|-------------------------------|------|-------------|---------------------------------------------------|

| 7 E_SUS |          | Erasa Suspand Status          | R    | 0           | Erase operation is not suspended (default).       |

|         | ⊑_303    | Erase Suspend Status          |      | 1           | Erase operation is suspended.                     |

| 6       | CMP      | Complement Block Protection   | R/W  | *1          | *2                                                |

|         |          | Lock Security Register 3      | R/W  | 0           | Security Register page-3 is not locked (default). |

| 5       | LB3      |                               |      | 1           | Security Register page-3 cannot be                |

|         |          |                               |      |             | erased/programmed. * <sup>3</sup>                 |

| 4 LB2   |          | Lock Security Register 2      | R/W  | 0           | Security Register page-2 is not locked (default). |

|         | LB2      |                               |      | 1           | Security Register page-2 cannot be                |

|         |          |                               |      |             | erased/programmed. *3                             |

|         |          | Lock Security Register 1      | R/W  | 0           | Security Register page-1 is not locked (default). |

| 3       | BP1      |                               |      | 1           | Security Register page-1 cannot be                |

|         |          |                               |      |             | erased/programmed. *3                             |

| 2       |          | Program Suspend Status        | R/   | 0           | Program operation is not suspended (default).     |

| 2       | P_SUS    |                               |      | 1           | Program operation is suspended.                   |

|         | QE       | Quad Enable                   | R/W  | 0           | HOLD and WP function normally.                    |

| 1       |          |                               |      |             |                                                   |

|         |          |                               |      | 1           | HOLD and WP are I/O pins (default).               |

| 0       | SRP1     | Status Register Protect bit 1 | R/W  |             | *2                                                |

#### Table 3.3 AT25QF family serial NOR flash memory

Note 1: Set to 0 or 1, complements the effect of the other bits.

Note 2: See the specification of Flash memory.

Note 3: Once a Lock Bit is set to 1, the corresponding Security Register is permanently locked. The Erase Security Register Page instruction is ignored for Security Registers with their Lock Bit set.

#### Example

flash\_spi\_status\_t ret = FLASH\_SPI\_SUCCESS; uint32\_t stat = 0;

ret = R\_FLASH\_SPI\_Read\_Status2(FLASH\_SPI\_DEV0, &stat);

#### **Special Notes**

The clock synchronous single master control software resources are acquired at the start of the processing, and the resources are released and the end of the processing.

### R\_FLASH\_SPI\_Read\_Status3()

This function is used to read the status register 3. It is a dedicated API function for AT25QF family serial NOR flash memory of Renesas Electronics.

#### Format

```

flash_spi_status_t R_FLASH_SPI_Read_Status3(

uint8_t devno,

uint8_t * p_status

)

Parameters

```

```

devno

Device number (0, 1)

* p_status

Status register storage buffer (size: 1 byte)

```

### **Return Values**

| FLASH_SPI_SUCCESS   | /* Successful operation */                           |

|---------------------|------------------------------------------------------|

| FLASH_SPI_ERR_PARAM | /* Parameter error */                                |

| FLASH_SPI_ERR_HARD  | /* Hardware error */                                 |

| FLASH_SPI_ERR_OTHER | /* Other task has acquired clock synchronous single  |

|                     | master control software resources, or other error */ |

### **Properties**

Prototype declarations are contained in r\_flash\_spi\_if.h.

#### Description

Reads the status register 3 and stores the contents in p\_status. The following information is stored in p\_status:

#### • <AT25QF family serial NOR flash memory of Renesas Electronics.>

#### Table 3.4 AT25QF family serial NOR flash memory

| Bit | Mnemonic | Name           | Туре | Description |                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|----------|----------------|------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Res      | Reserved       | R    | 0           | Reserved bit.                                                                                                                                                                                                                                                                                                                                                                                    |

| 6:5 | DRV[1:0] | Drive Strength | R/W  | 11          | Drive level. Th DRV1 and DRV0 bits are used to<br>determine the output drive strength during read<br>operations. One of the setting of below allows the<br>drive strength to be set by hardware based on the<br>VCC level. Four drive settings are supported.<br>This field is encoded as follows:<br>11: Auto (7pF base on VCC level.<br>10: 50% (15pF).<br>01: 75% (22pF).<br>00: 100% (30pF). |

| 4:0 | Res      | Reserved       | R    | 0           | Reserved bit.                                                                                                                                                                                                                                                                                                                                                                                    |

#### Example

flash\_spi\_status\_t ret = FLASH\_SPI\_SUCCESS; uint32\_t stat = 0;

ret = R\_FLASH\_SPI\_Read\_Status3(FLASH\_SPI\_DEV0, &stat);

#### **Special Notes**

The clock synchronous single master control software resources are acquired at the start of the processing, and the resources are released and the end of the processing.

# R\_FLASH\_SPI\_Set\_Write\_Protect()

This function is used to make write protect settings.

#### Format

```

flash_spi_status_t R_FLASH_SPI_Set_Write_Protect(

uint8_t devno,

uint8_t wpsts

)

```

#### **Parameters**

devno Device number (0, 1) wpsts Write protect setting data

#### **Return Values**

FLASH\_SPI\_SUCCESS FLASH\_SPI\_ERR\_PARAM FLASH\_SPI\_ERR\_HARD FLASH\_SPI\_ERR\_WP FLASH\_SPI\_ERR\_OTHER /\* Successful operation \*/ /\* Parameter error \*/ /\* Hardware error \*/ /\* Write-protection error \*/ /\* Other task has acquired clock synchronous single master control software resources, or other error \*/

## **Properties**

Prototype declarations are contained in r\_flash\_spi\_if.h.

## Description

Make write protect settings. SRWD is cleared to 0. Specify the write protect setting data (wpsts) as indicated below. Refer to the data sheet for information on protected areas and protected bits.

#### <MX25L, MX66L, MX25R, or MX25U family serial NOR flash memory of Macronix International Co., Ltd>

| wpsts | BP3 | BP2 | BP1 | BP0 |

|-------|-----|-----|-----|-----|

| 0x00  | 0   | 0   | 0   | 0   |

| 0x01  | 0   | 0   | 0   | 1   |

| 0x02  | 0   | 0   | 1   | 0   |

| 0x03  | 0   | 0   | 1   | 1   |

| 0x04  | 0   | 1   | 0   | 0   |

| 0x05  | 0   | 1   | 0   | 1   |

| 0x06  | 0   | 1   | 1   | 0   |

| 0x07  | 0   | 1   | 1   | 1   |

| 0x08  | 1   | 0   | 0   | 0   |

| 0x09  | 1   | 0   | 0   | 1   |

| 0x0a  | 1   | 0   | 1   | 0   |

| 0x0b  | 1   | 0   | 1   | 1   |

| 0x0c  | 1   | 1   | 0   | 0   |

| 0x0d  | 1   | 1   | 0   | 1   |

| 0x0e  | 1   | 1   | 1   | 0   |

| 0x0f  | 1   | 1   | 1   | 1   |

Make top and bottom settings during configuration write processing.

#### • <AT25QF family serial NOR flash memory of Renesas Electronics>

Make large and small block size, top, and bottom settings during status register 1 write processing.

Make compliment settings during status register 2 write processing.

| wpsts | BP2 | BP1 | BP0 |

|-------|-----|-----|-----|

| 0x00  | 0   | 0   | 0   |

| 0x01  | 0   | 0   | 1   |

| 0x02  | 0   | 1   | 0   |

| 0x03  | 0   | 1   | 1   |

| 0x04  | 1   | 0   | 0   |

| 0x05  | 1   | 0   | 1   |

| 0x06  | 1   | 1   | 0   |

| 0x07  | 1   | 1   | 1   |

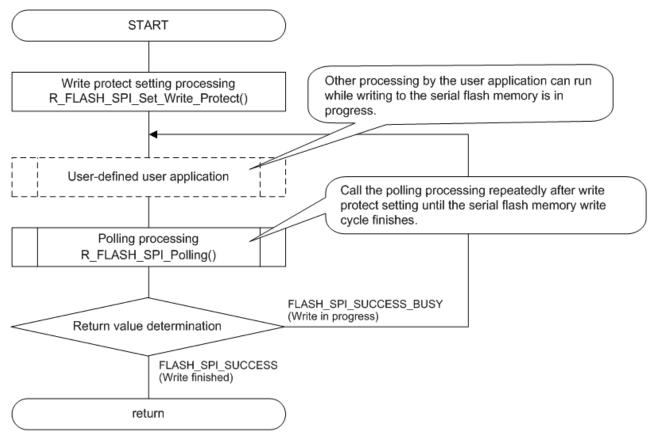

When this user API function completes successfully, the serial flash memory transitions to a write cycle. Do not fail to confirm write completion with R\_FLASH\_SPI\_Polling(). If the next read or write processing starts when a previous write cycle is in progress, the serial flash memory will not accept the new processing. R\_FLASH\_SPI\_Polling() can be called at any time specified by the user. This allows a user application to perform other processing while a write cycle is in progress. See Figure 3.1 for details.

```

Example

#define FLASH_WR_BUSY_WAIT (uint32_t)(40) /* 40 * 1ms = 40ms */

flash spi status t ret = FLASH SPI SUCCESS;

uint32 t

loop cnt = 0;

flash spi poll mode t mode;

ret = R FLASH SPI Set Write Protect(FLASH SPI DEV0, 0);

if (FLASH SPI SUCCESS > ret)

{

/* Error */

}

loop cnt = FLASH WR BUSY WAIT;

mode = FLASH SPI MODE REG WRITE POLL;

do

{

/* FLASH is busy.

User application can perform other processing while flash is busy. */

ret = R FLASH SPI Polling(FLASH_SPI_DEV0, mode);

if (FLASH SPI SUCCESS BUSY != ret)

{

/* FLASH is ready or error. */

break;

}

loop cnt--;

}

while (0 != loop cnt);

if ((0 == loop cnt) || (FLASH SPI SUCCESS > ret))

{

/* Error */

}

```

# RX Family Clock Synchronous Control Module for Serial NOR Flash Memory Access

Figure 3.1 R\_FLASH\_SPI\_Set\_Write\_Protect() Processing Example

## R\_FLASH\_SPI\_Write\_Di()

This function is used to disable write operation.

#### Format

```

flash_spi_status_t R_FLASH_SPI_Write_Di(

uint8_t devno

```

)

```

Parameters

```

devno

Device number (0, 1)

#### **Return Values**

FLASH\_SPI\_SUCCESS FLASH\_SPI\_ERR\_PARAM FLASH\_SPI\_ERR\_HARD FLASH\_SPI\_ERR\_OTHER /\* Successful operation \*/ /\* Parameter error \*/ /\* Hardware error \*/ /\* Other task has acquired clock synchronous single master control software resources, or other error \*/

#### **Properties**

Prototype declarations are contained in r\_flash\_spi\_if.h.

#### Description

Transmits the WRDI command and clears the WEL bit in the status register.

#### Example

flash\_spi\_status\_t ret = FLASH\_SPI\_SUCCESS;