# RH850/U2A EVA Group

# CAN Configuration (CAN FD Mode)

#### Summary

This application note explains the procedure example for CAN configuration in the RH850/U2A series of automotive single-chip microcontrollers from Renesas Electronics (hereafter referred to as U2A).

These documents and programs are intended to understand the RH850/U2A built-in function, and are not intended for mass production design.

Aim of this document and software is to provide supplemental information for the function on RH850/U2A. It is not intended to implement in the design for mass production.

There is no guarantee to update in this document and software to reflect the latest manual, errata, technical update and development environment. You are fully responsible for the incorporation or any other use of the information of this document in the design of your product or system, and please refer to latest manual, errata, technical update and development environment.

#### **Target Device**

RH850/U2A-EVA Group

**Target Integrated Development Environment**

CS+ (from Renesas Electronics)

Version : V8.07.00

Device File : DR7F702300.DVF

: DR7F702301.DVF

: DR7F702302.DVF

#### Reference Document

RH850/U2A-EVA User's Manual: Hardware

For function details and electrical characteristics, please refer to "User's Manual: Hardware".

This application note is based on the following manual.

RH850/U2A-EVA User's Manual (Rev.1.20): R01UH0864EJ0120

The register name in this text omits "RSCFDnCFD".

# Contents

| 1.  | CAN Configuration                                 | 3  |

|-----|---------------------------------------------------|----|

| 2.  | CAN State (Mode) Transition                       | 10 |

| 3.  | Communication Speed                               | 14 |

| 4.  | Global Function                                   | 17 |

| 5.  | Receive Rule Table                                | 23 |

| 6.  | Buffer, FIFO Buffer                               | 32 |

| 7.  | Global Error Interrupt                            | 46 |

| 8.  | Channel Function                                  | 48 |

| 9.  | CAN-related Interrupt                             | 56 |

| 10. | DMA Trigger                                       | 59 |

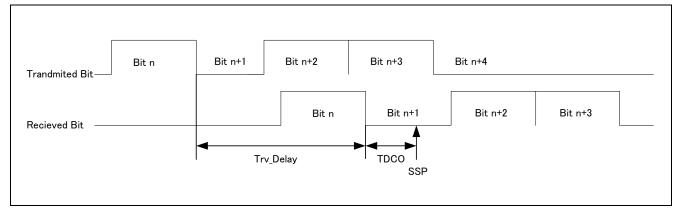

| 11. | Transmitter Delay Compensation (Only CAN FD Mode) | 61 |

| 12. | Precautions for Processing Flow                   | 62 |

| 12  | Annendiy                                          | 6/ |

# 1. CAN Configuration

CAN configuration means to setup the required function for performing CAN communication. Perform the configuration to start or restart CAN communication after MCU reset, recovery from bus failure detection, wake-up, etc.

CAN configuration can be performed in certain CAN status. Refer to the following for the details.

For CAN State (Mode), refer to "2. CAN State (Mode) Transition".

- 1.1 CAN Configuration after MCU Reset

- 1.2 CAN Configuration after Global Reset Mode

- 1.3 CAN Configuration after Channel Reset Mode

- 1.4 CAN Configuration after Channel Halt Mode

The required functions when setting CAN configuration are shown below. For details of each process, refer to the following chapters.

- 2. \_\_\_CAN State (Mode) Transition

- 3. Communication Speed

- 4. Global Function

- 5. Receive Rule Table

- 6. Buffer, FIFO Buffer

- 7. Global Error Interrupt

- 8. Channel Function

- 9. CAN-related Interrupt

- 10. DMA Trigger

- 11. Transmitter Delay Compensation (Only CAN FD Mode)

# 1.1 CAN Configuration after MCU Reset

#### 1.1.1 CAN Configuration after MCU Reset

This section shows the intialization processing procedure of entire RS-CANFD module after MCU reset.

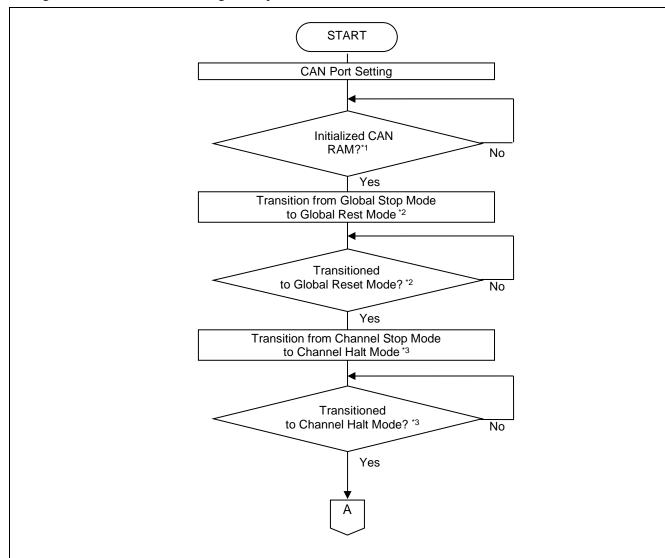

### 1.1.2 Setting Procedure of CAN Configuration after MCU Reset

Figure 1-1 and 1-2 shows the configuration procedure after MCU reset.

- Note 1. After resetting the MCU, do not access to CAN RAM before initializing the CAN RAM (during the GRAMINIT bit of the GSTS register is set to "1").

- Note 2. If you change the global mode (the GSLPR bit and the GMDC [1:0] bit of the GCTR register), check that the mode is switched in the GSTS register. Do not change the GMDC[1:0] bit until the mode is switched

- Note 3. If you change the channel mode (the CSLPR bit and the CHMDC [1:0] bit of the CmCTR register), check that the mode is switched in the CmSTS register. Do not change the CHMDC[1:0] bit until the mode is switched.

Figure 1-1 Configuration Procedure after MCU Reset 1/2

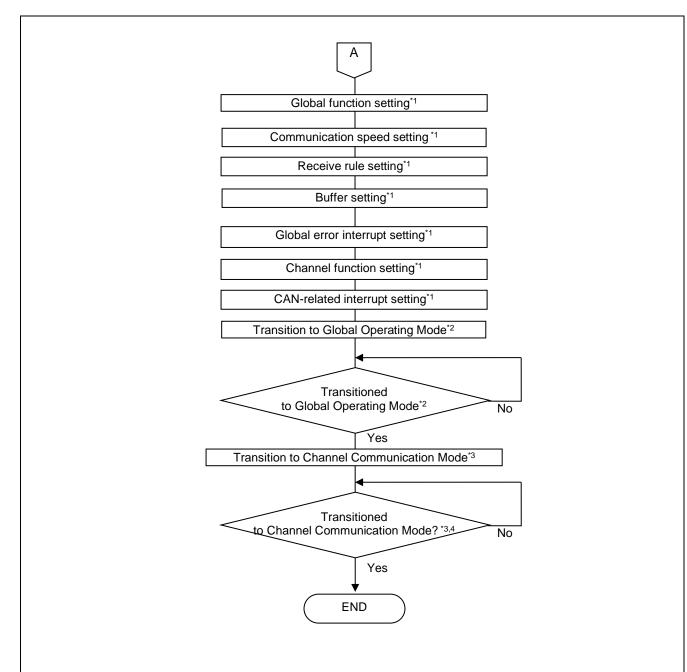

- Note 1. For processes of each function, refer to the following chapters.

- Note 2. If you change the global mode (the GSLPR bit and the GMDC [1:0] bit of the GCTR register), check that the mode is switched in the GSTS register. Do not change the GMDC[1:0] bit until the mode is switched.

- Note 3. If you change the channel mode (the CSLPR bit and the CHMDC [1:0] bit of the CmCTR register), check that the mode is switched in the CmSTS register. Do not change the CHMDC[1:0] bit until the mode is switched.

- Note 4. After the transition to channel communication mode, when 11 consecutive recessive bits have been detected, communication is ready (the COMSTS flag in the CmSTS register is "1") and transmission and reception are enabled on the CAN network as an active node. At this time, transmission and reception of messages can be started.

Figure 1-2 Configuration Procedure after MCU Reset 2/2

# 1.2 CAN Configuration after Global Reset Mode

#### 1.2.1 CAN Configuration after Global Reset Mode

This section shows the intialization processing procedure of entire RS-CANFD module after transitioned to global reset mode.

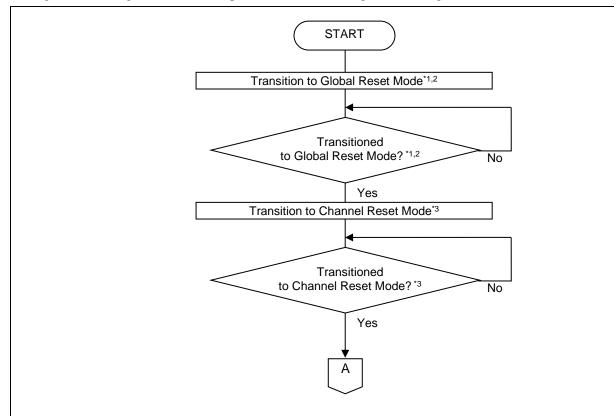

# 1.2.2 Setting Procedures of CAN Configuration after Global Reset Mode

Figure 1-3 and Figure 1-4 shows the procedure of CAN configuration after global reset mode.

- Note 1. When changing the global mode (the GSLPR bit and the GMDC [1:0] bits of the GCTR register), confirm with the GSTS register that the mode has been switched. Do not change the GMDC [1:0] bits until the mode is switched.

- Note 2. Channel modes may transition in accordance with transitions of global modes. For details, refer to "2.3 Change of Channel Mode by Transition of Global Mode".

- Note 3. When changing the channel mode (the CSLPR bit and the CHMDC [1:0] bits of the CmCTR register), confirm with the CmSTS register that the mode has been switched. Do not change the CHMDC[1:0] bits until the mode is switched.

Figure 1-3 Procedure of CAN Configuration after Global Reset Mode 1/2

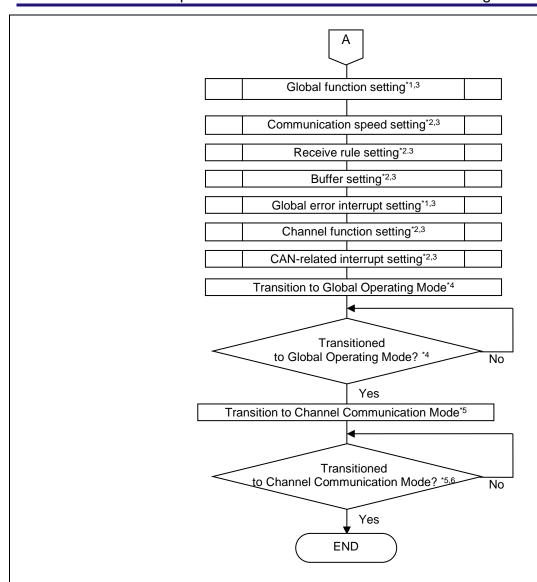

- Note 1. These settings do not always have to be executed because the values are not reset in the transition to Global Reset Mode.

- Note 2. These settings do not always have to be executed because the values of these settings are not reset in the transition to Channel Reset Mode.

- Note 3. For processes of each function, refer to the following chapters.

- Note 4. When changing the global mode (the GSLPR bit and the GMDC [1:0] bits of the GCTR register), confirm with the GSTS register that the mode has been switched. Do not change the GMDC [1:0] bits until the mode is switched.

- Note 5. When changing the channel mode (the CSLPR bit and the CHMDC [1:0] bits of the CmCTR register), confirm with the CmSTS register that the mode has been switched. Do not change the CHMDC [1:0] bits until the mode is switched.

- Note 6. After the transition to channel communication mode, when 11 consecutive recessive bits have been detected, communication is ready (the COMSTS flag in the CmSTS register is "1") and transmission and reception are enabled on the CAN network as an active node. At this time, transmission and reception of messages can be started.

Figure 1-4 Procedure of CAN Configuration after Global Reset Mode 2/2

# 1.3 CAN Configuration after Channel Reset Mode

#### 1.3.1 CAN Configuration after Channel Reset Mode

This section shows the CAN channel intialization processing procedure after transitioned to channel reset mode.

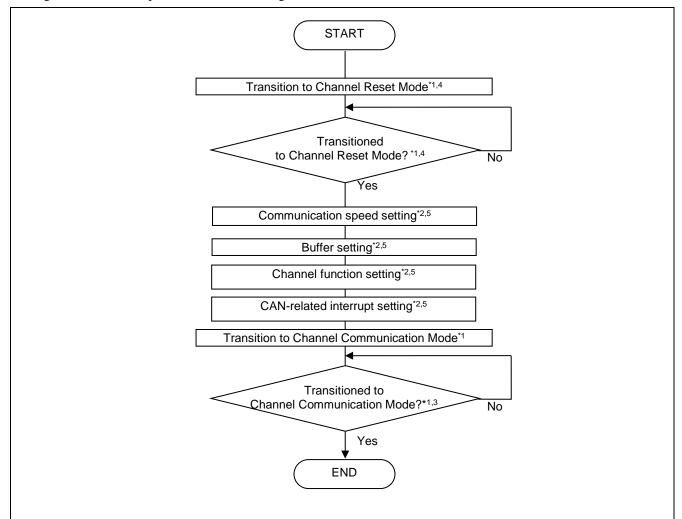

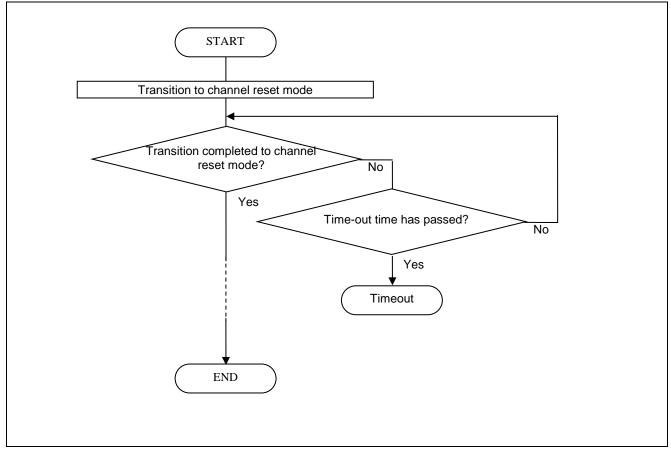

### 1.3.2 Setting Procedure of CAN Configuration after Channel Reset Mode

Figure 1-5 shows the procedure of CAN configuration after channel reset mode.

- Note 1. When changing the channel mode (the CSLPR bit and the CHMDC[1:0] bit of the CmCTR register), confirm with the CmSTS register that the mode has been switched. Do not change the CHMDC[1:0] bits until the mode is switched.

- Note 2. These settings do not always have to be executed because the values are not reset in the transition of channel reset mode.

- Note 3. After the transition to channel communication mode, when 11 consecutive recessive bits have been detected, communication is ready (the COMSTS flag in the CmSTS register is "1") and transmission and reception are enabled on the CAN network as an active node. At this time, transmission and reception of messages can be started.

- Note 4. Transition to Channel Reset Mode does not wait for communication to complete. To allow transition to channel reset mode after communication is completed, confirm that communication has been completed and transitioned to Channel Halt Mode, and then transition to channel reset mode.

- Note 5. For processes of each function, refer to the following chapters.

Figure 1-5 Procedure of CAN Configuration after Channel Reset Mode

# 1.4 CAN Configuration after Channel Halt Mode

#### 1.4.1 CAN Configuration after Channel Halt Mode

This section shows the CAN channel intialization processing procedure after transitioned to Chanel Halt Mode.

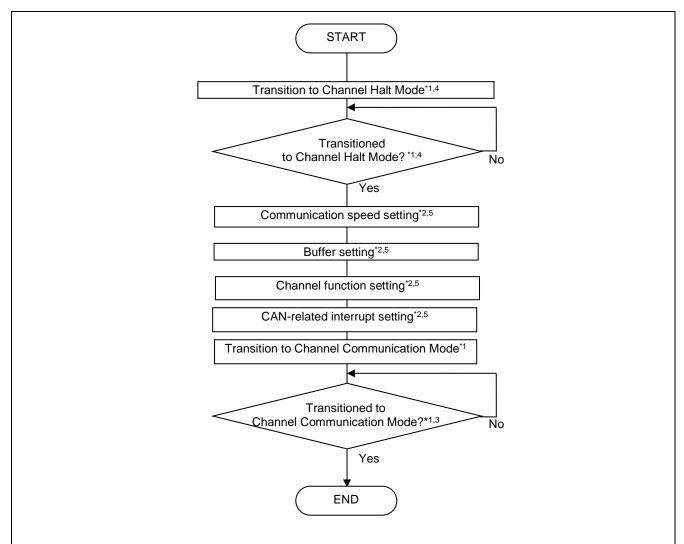

#### 1.4.2 Setting Procedures of CAN Configuration after Channel Halt Mode

Figure 1-6 shows the procedure of CAN configuration after channel halt mode.

- Note 1. When changing the channel mode (the CSLPR bit and the CHMDC[1:0] bits in the CmCTR register), confirm with the CmSTS register that the mode has been switched. Do not change the CHMDC[1:0] bits until the mode is switched.

- Note 2. These settings do not always have to be executed because the values are not reset in the transition to Channel Halt Mode.

- Note 3. After the transition to channel communication mode, when 11 consecutive recessive bits have been detected, communication is ready (the COMSTS flag in the CmSTS register is "1") and transmission and reception are enabled on the CAN network as an active node. At this time, transmission and reception of messages can be started.

- Note 4. While the CAN bus is locked to the dominant level (BLF flag in the CmERFLL register is "1"), transition to channel halt mode is not made. In that case, enter channel reset mode.

- Note 5. For processes of each function, refer to the following chapters.

Figure 1-6 Procedure of CAN Configuration after Channel Halt Mode

# 2. CAN State (Mode) Transition

RS-CANFD module has the state of entire channels (hereinafter called Global) and each channel (mode).

The states (modes) of the RS-CANFD module are shown below.

- 2.1 Global Mode

- 2.1.1 Global Stop Mode

- 2.1.2 Global Reset Mode

- 2.1.3 Global Test Mode

- 2.1.4 Global Operating Mode

- 2.2 Channel Mode

- 2.2.1 Channel Stop Mode

- 2.2.2 Channel Reset Mode\_

- 2.2.3 Channel Halt Mode

- 2.2.4 Channel Communication Mode

#### 2.1 Global Mode

This is the mode of entire RS-CANFD mode. Channel modes may transition in accordance with transitions of global modes. Refer to "2.3 Change of Channel Mode by Transition of Global Mode" for the details

# 2.1.1 Global Stop Mode

This mode stops RS-CANFD module clocks. The CAN clocks do not run and therefore power consumption is reduced. CAN registers can be read, but writing data to them is prohibited. Register values are retained.

#### 2.1.2 Global Reset Mode

This mode is used to configure the entire RS-CANFD module. When the RS-CANFD module transitions to global reset mode, some registers are initialized. Refer to the latest user's manual: hardware for the registers to be initialized.

#### 2.1.3 Global Test Mode

This mode is used to set test-related registers. When the RS-CANFD module transitions to global test mode, all CAN communications are disabled.

# 2.1.4 Global Operating Mode

This mode operates entire RS-CANFD module. When do a communication using each channel, transition to global operating mode is required.

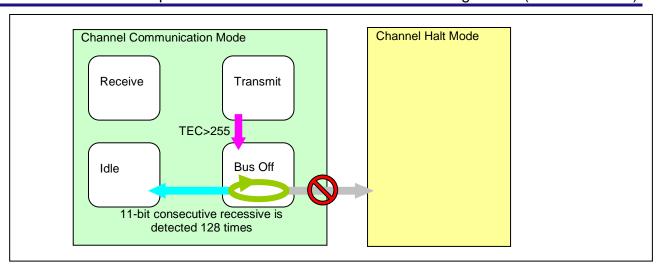

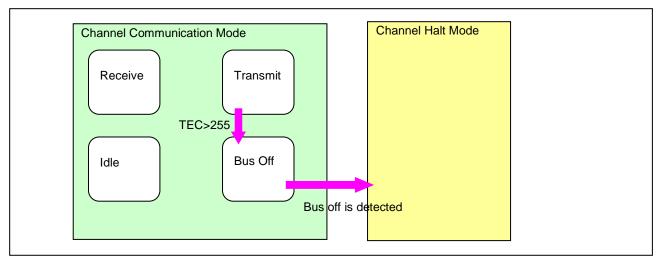

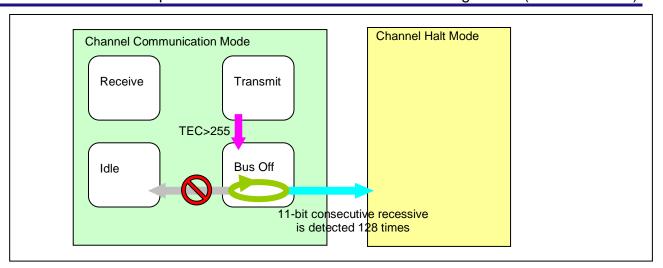

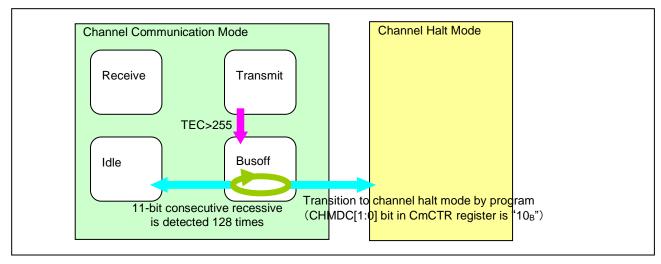

#### 2.2 Channel Mode

Refer to "User's Manual Hardware: Figure 23.11 Channel Mode State Transition Chart" for the transition chart of channel mode.

# 2.2.1 Channel Stop Mode

This mode stops the clock supply to a channel. CAN clock do not runt and therefore power consumption is reduced. CAN registers can be read, but writing data to them is prohibited. Register values are retained.

#### 2.2.2 Channel Reset Mode

This mode is used to configure channel settings. When a transitions to channel reset mode, some channel-related registers are initialized. Refer to the latest user's manual: hardware for initialized register.

#### 2.2.3 Channel Halt Mode

This mode is used to set test-related registers of channels. When a channel transitions to Channel Halt Mode, CAN communication of the channel stops.

#### 2.2.4 Channel Communication Mode

This mode performs CAN communication. Each channel is in the following communication states during CAN communication.

• Idle

Neither reception nor transmission is in progress.

• Reception

Receiving a message sent from another node.

Transmission

Transmitting a message.

• Bus off

Isolated from CAN communication.

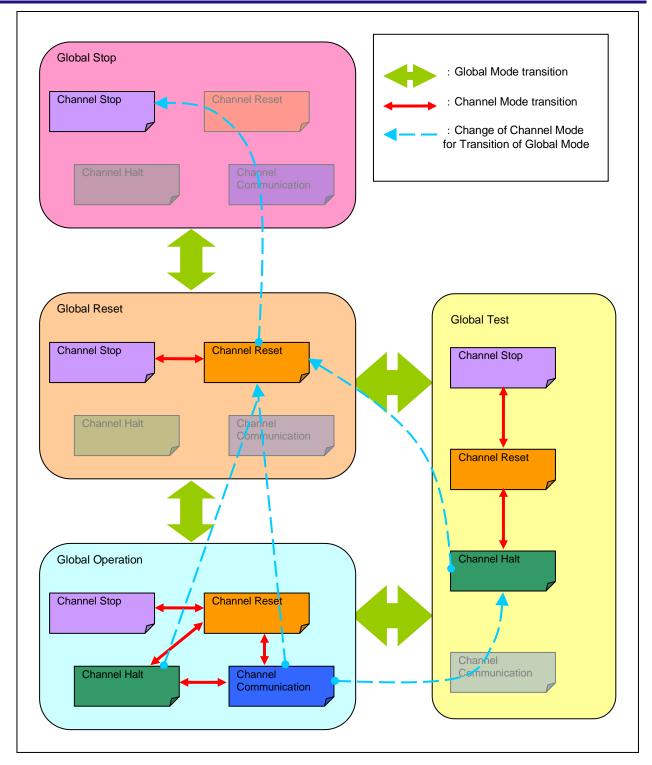

# 2.3 Change of Channel Mode by Transition of Global Mode

Channel modes may transition in accordance with transitions of global modes. Figure 2-1 shows the transitions of channel modes depending on the global mode setting. Refer to "User's Manual Hardware: Table 23.135 Possible CAN channel Modes versus Global Module Modes" for the details.

Figure 2-1 Transition of Global Mode and Channel Mode

### 3. Communication Speed

Set the communication speed for CAN communication. You need to perform the following settings to determine CAN communication speed.

- 3.1 CAN Bit Timing Setting

- 3.2 Setting of Communication Speed

- 3.3 Setting Procedure of CAN Bit Timing and Communication Speed

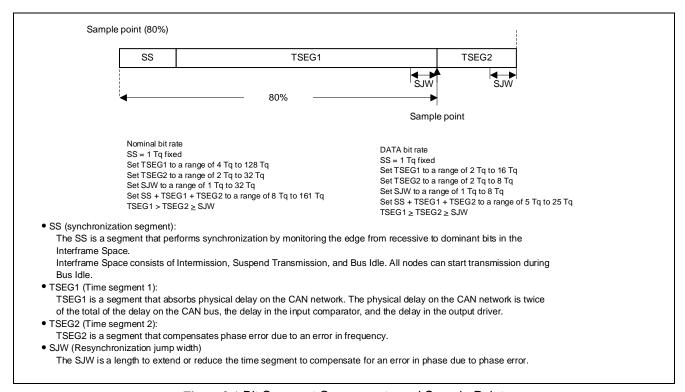

#### 3.1 CAN Bit Timing Setting

In this CAN bit timing setting of RS-CANFD module, one bit of a communication frame consists of three segments. Figure 3-1 shows segments of bits and sample point.

In these segments, Time Segment 1(hereinafter called TSEG1) and Time Segment 2 (hereinafter called TSEG2) indicate the sample point. Also, it can be changed the timing for sampling by changing the values of segments. CAN FD mode has 2 types of bit rate (nominal bit rate and data bit rate), and each should be set.

The minimum unit for this timing setting is called 1 Time Quantum (hereinafter called Tq) and is determined by the clock frequency supplied to the RS-CANFD module and the baud rate prescaler division value.

Figure 3-1 Bit Segment Components and Sample Point

# 3.2 Setting of Communication Speed

Communication speed is determined by CAN clock (fCAN) that is clock source of RS-CANFD module, baud rate prescaler division value, and Tq count per bit. The maximum communication speed that can be set is 1 Mbps at the normal bit rate and 8 Mbps at the data bit rate. Either clkc or clk\_xincan can be used as fCAN. For fCAN setting, refer to "4.5 CAN Clock Source Setting".

Refer to "User's Manual Hardware: Table 23.143 Nominal Baud Rate calculation formula and example CAN communication configurations" and "User's Manual Hardware: Table 23.144 Baud Rate calculation example for nominal and data bit rate CAN communication configurations" for the calculation formula and implementation example. Refer to "User's Manual Hardware: Table 23.142 Bit timing examples" for the bit timing setting example.

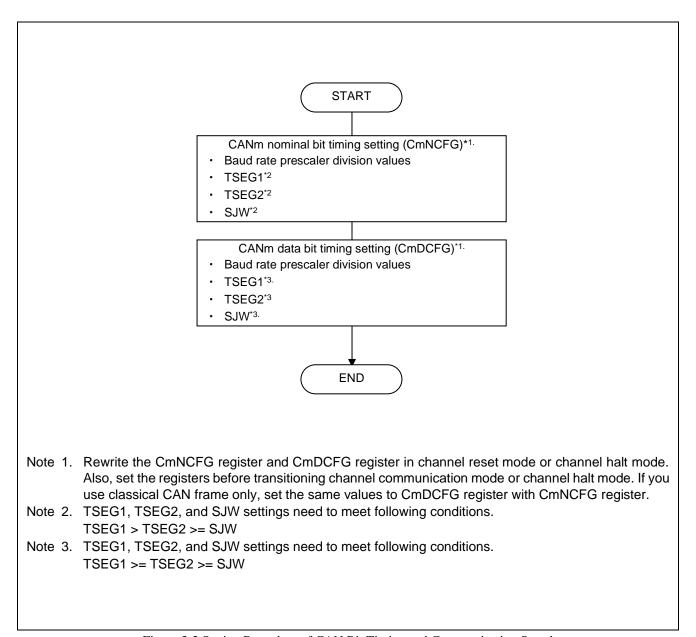

# 3.3 Setting Procedure of CAN Bit Timing and Communication Speed

Figure 3-2 shows the setting procedure of CAN bit timing and communication speed.

Perform these setting during CAN configuration.

Refer to "1. CAN Configuration" for the procedure of CAN configuration.

Figure 3-2 Setting Procedure of CAN Bit Timing and Communication Speed

#### 4. Global Function

Set the following functions that are common to entire RS-CANFD module (all channels).

- 4.1 Transmit Priority Setting

- 4.2 DLC Check Setting

- 4.3 DLC Replacement Function Setting

- 4.4 Mirror Function Setting

- 4.5 CAN Clock Source Setting

- 4.6 Payload Overflow Mode Setting

- 4.7 Timestamp Clock Setting

- 4.8 Interval Timer Prescaler Setting

# 4.1 Transmit Priority Setting

Set the transmit priority when transmit requests are issued from multiple transmit buffers or transmit queues in the same channel.

It is not able to set the transmit priority for each channel because the transmit priority is common to entire channels. You can choose following two of judgment methods.\*1

#### • ID Priority

The messages are transmitted according to the priority of stored message IDs. Priority of IDs conforms to the CAN bus arbitration specification defined in the CAN specification.

Targets of priority determination are IDs of messages placed in transmit buffers, transmit/receive FIFO buffers (set to transmit mode or gateway mode), and transmit queues.

When transmit/receive FIFO buffers are used, the oldest message in a FIFO buffer becomes a target of priority determination.

When a message is being transmitted from a transmit/receive FIFO buffer, the next message in the same FIFO buffer becomes a target of priority determination.

When transmit queues are used, all messages in transmit queues are targets of priority determination.

When the message that has same ID with the stored message into the transmit queue is stored, the transmission of message that has same stored ID is aborted or cancelled.

#### • Transmit Buffer Number Priority

The message in the transmit buffer whose number is the lowest among buffers having transmit requests is transmitted first.

When transmit/receive FIFO buffers are linked to transmit buffers, transmit priority is determined according to the linked transmit buffer numbers.

When messages are retransmitted due to an arbitration-lost or an error, transmit priority determination is made again whichever transmit priority is selected.

<sup>\*1</sup> When using the transmit queue, it is not possible to select the method; please select ID Priority.

# 4.2 DLC Check Setting

Set to enable or disable DLC check function.

When the DLC check function is enabled, DLC filter processing is performed for messages that pass through the acceptance filter processing.

When the DLC check function is disabled, DLC check is not performed after performing acceptance filter processing. In DLC check, when the DLC value in a message is equal to or larger than the DLC value set in the receive rule, the message passes through the DLC filter processing. When the DLC value of the received message is smaller than that of the receive rule, the message does not pass through the DLC filter processing. In this case, the message is not stored in the receive buffer or the FIFO buffer and a DLC error is present.

Please refer to "5. Receive Rule Table" for the receive rule.

# 4.3 DLC Replacement Function Setting

Set to enable or disable DLC replacement function.

DLC replacement is effective only when DLC check function is enabled.

When DLC replacement is enabled, the DLC value of the receive rule is stored in the buffer instead of the DLC value of he received message after the DLC value has passed through the DLC filter. In this case, a value of " $00_H$ " is stored in each data byte that exceeds the DLC value of the receive rule.

When DLC replacement is disabled, the DLC value of the received message is stored in the buffer after the DLC value has passed through the DLC filter. In this case, all the data bytes in the received message are stored in the buffer.

Please refer to "5. Receive Rule Table" for the receive rule.

Table 4-1 DLC Filter Processing and DLC Replacement Processing

| GCFG            | Register           | Received Message DLC                     | Received 1          | Message              |

|-----------------|--------------------|------------------------------------------|---------------------|----------------------|

| DCE Bit         | DRE Bit            | / Receive Rule DLC                       | Processing          | Stored DLC           |

| 0<br>(DLC check | 0 (DLC replacement | Received message DLC < Receive rule DLC  |                     |                      |

| disabled)       | is disabled)       | Received message DLC >= Receive rule DLC |                     |                      |

|                 |                    | Receive rule DLC = 0                     | G 1 . CC *1         | Received             |

|                 | 1 (DLC replacement | Received message DLC < Receive rule DLC  | Stores to buffer *1 | message DLC          |

|                 | is enabled)        | Received message DLC                     |                     |                      |

|                 |                    | >= Receive rule DLC                      |                     |                      |

|                 |                    | Receive rule DLC = 0                     |                     |                      |

| 1               | 0                  | Received message DLC                     | Discard (DLC error) | _                    |

| (DLC check      | (DLC replacement   | < Receive rule DLC                       |                     |                      |

| enabled)        | is disabled)       | Received message DLC                     | Stores to buffer    | Received             |

|                 |                    | >= Receive rule DLC                      |                     | message DLC          |

|                 |                    | Receive rule DLC = 0                     | Stores to buffer    | Received message DLC |

|                 | 1                  | Received message DLC                     | Discard (DLC error) |                      |

|                 | (DLC replacement   | < Receive rule DLC                       |                     |                      |

|                 | is enabled)        | Received message DLC                     | Stores to buffer    | Receive rule DLC     |

|                 |                    | >= Receive rule DLC                      |                     | *2                   |

|                 |                    | Receive rule DLC = 0                     | Stores to buffer    | Received             |

|                 |                    |                                          |                     | message DLC          |

-

<sup>&</sup>lt;sup>1</sup> DLC check itself is not performed.

$<sup>^2\,</sup>$  "00H" is stored in each data byte that exceeds than the DLC of the receive rule.

### 4.4 Mirror Function Setting

Set to enable or disable mirror function.

The mirror function allows reception of own transmitted messages.

When the mirror function is in use, receive rules for which the GAFLLB bit in the GAFLIDj register is set to 0 are applied to the data processing for messages received from other CAN nodes. When own transmitted messages are received, receive rules for which the GAFLLB bit in the GAFLIDj register is set to 1.

Please refer to "Section 5, Receive Rule Table" for the receive rule.

Table 4-2 Message Targeted for Data Processing by Mirror Function

| MME Bit of GCFGL Register     | GAFLLB Bit of<br>GAFLIDj Register | Message Targeted for Data Processing of Receive rule |

|-------------------------------|-----------------------------------|------------------------------------------------------|

| 0                             | 0                                 | Message received from other CAN node                 |

| (Mirror function is disabled) | 1                                 | No targeted message                                  |

| 1                             | 0                                 | Message transmitted from other CAN node              |

| (Mirror function is enabled)  | 1                                 | Own transmitted message transmitted                  |

# 4.5 CAN Clock Source Setting

Set the CAN clock (fCAN) which is CAN clock source in DCS bit of GCFG register. The clocks available as the CAN clock source are shown below.

- · clk xincan

- clkc

#### 4.6 Payload Overflow Mode Setting

Set the payload overflow mode in the CMPOC bit of the GCFG register. Select the operation when the payload length of the received message exceeds the payload storage size of the storage buffer.

When the bit is set to "0", the received message which overflows the payload is not stored in the buffer.

When the bit is set to "1", the received message which overflows the payload is stored in the buffer. Also, the received DLC value or the DLC value of the receive rule table is stored in the buffer depending on the DRE bit. At the time, the payloads exceeding the buffer's payload storage size are discarded.

Set the payload storage size of the buffer by following bits.

- Receive buffer: RMPLS[2:0] bits in the RMNB register.

- Receive FIFO buffer: RFPLS[2:0] bits in the RFCCx register

- Transmit/receive FIFO buffer: CFPLS[2:0] bits in the CFCCk register

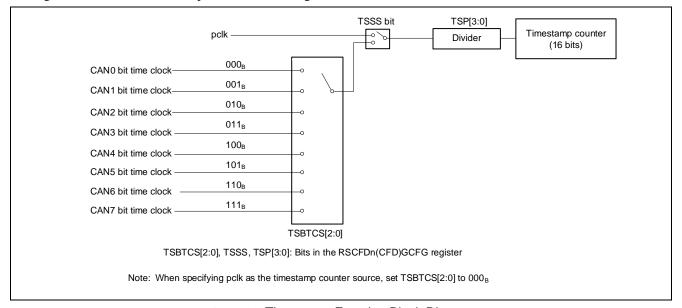

# 4.7 Timestamp Clock Setting

Set the clock source and the division ratio for using timestamp clock.

The timestamp counter is a 16-bit free-running counter used for recording the message reception time and transmission time. The timestamp counter value is fetched at the timing set with the TSCCFG[1:0] bits in the GFDCFG register and is then stored in a receive buffer or a FIFO buffer together with the message ID and data during data reception.

You can select the following clocks for using timestamp.

- pclk

- CANm nominal bit time clock

When the nominal CANm bit time clock is used as a clock source, the timestamp counter stops when the corresponding channel transitions to channel reset mode or channel halt mode. When pclk is used as a clock source, the timestamp function is not affected by channel mode.

Figure 4-1 shows the timestamp function block diagram.

Figure 4-1 Timestamp Function Block Diagram

# 4.8 Interval Timer Prescaler Setting

Set the prescaler value when pclk is selected as an interval timer count source.

Please refer to "6.3.4 Interval Timer Counter Setting" for interval timer function.

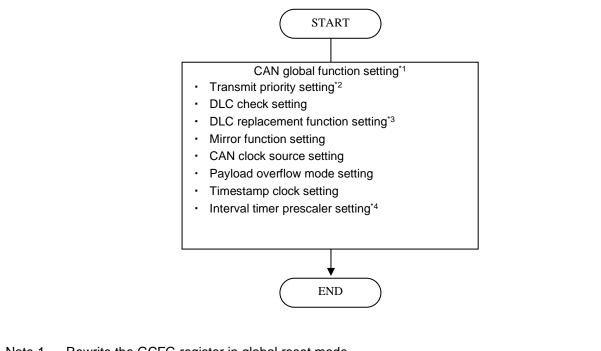

# 4.9 Global Function Setting

Figure 4-2 shows global function setting procedures.

Perform these settings during CAN configuration.

Please refer to "1. CAN Configuration" for CAN configuration setting procedure.

- Note 1. Rewrite the GCFG register in global reset mode.

- Note 2. Select the ID priority (TPRI bit of GCFG register is "0") when using transmit queue.

- Note 3. If you disabled the DLC check function (DCE bit in the GCFG register is set to "0"), disable the function after setting "0" to DLC of receive rule table (GAFLDLC bit of GAFLP0j register).

- Note 4. If you use pclk for interval timer counter source, do not set 0000<sub>H</sub> to interval timer prescaler (ITRCP [15:0] bit of GCFG register).

Figure 4-2 Global Function Setting Procedure

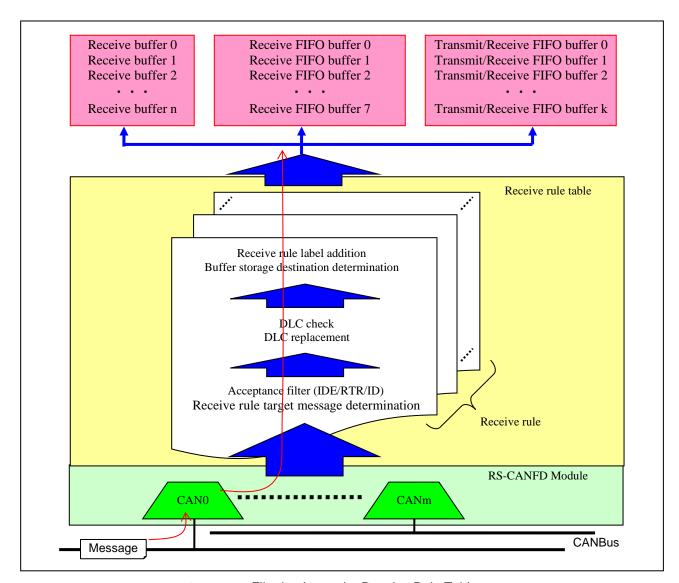

#### 5. Receive Rule Table

Set the receive rule table for filtering received message.

Data processing using the receive rule table stores selected messages to the specified buffer. Data processing includes acceptance filter processing, DLC filter processing, routing processing, label addition processing, and mirror function processing.

The following settings are required for receive rule.

- 5.1 Number of Receive Rules Setting

- 5.2 IDE/RTR/ID Setting

- 5.3 Receive Rule Target Message Setting

- 5.4 IDE Mask/RTR Mask/ID Mask Setting

- 5.5 DLC Check Value Setting

- 5.6 Routing Processing

- 5.7 Receive Rule Label Setting

- 5.8 Storage Buffer Setting

- 5.9 Use Example of Receive Rule

- 5.10 Receive Rule Table Setting Procedures

Figure 5-1 Filtering Image by Receive Rule Table

# 5.1 Number of Receive Rules Setting

Set the number of receive rules for each channel.

The number of receive rules for the entire module is  $192 \times$  number of channels for U2A-EVA, U2A16 and U2A8, and  $128 \times$  number of channels for U2A6. The maximum number of receive rules that can be registered per channel is 384 for U2A-EVA, U2A16 and U2A8, and 255 for U2A6.

Check processes begin with the lowest-numbered receive rule in ascending order. When all the bits to be compared in a received message match the bits set in the receive rule or when all the receive rules are compared without any match, filter processing stops. When there is no matching receive rule, the received message is not stored in the receive buffer or FIFO buffer.

Table 5-1 shows the limitations on the number of receive rules that can be registered.

Table 5-1 Limitations on the number of receive rules

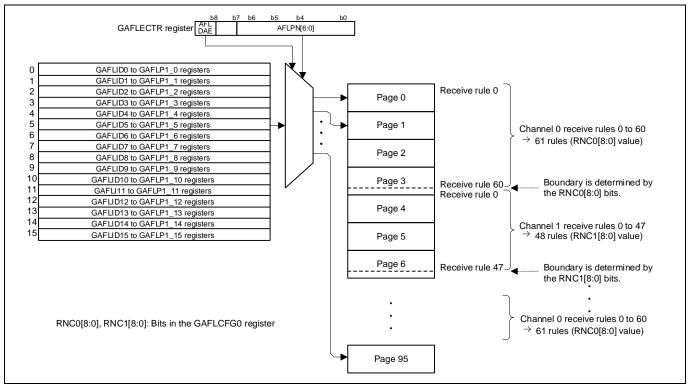

Figure 5-2 shows the receive rule example.

Figure 5-2 Receive Rule Register Example

### 5.2 IDE/RTR/ID Setting

Set the ID format (standard ID or extended ID), frame format (data frame or remote frame), and receive ID of the received message.

### 5.3 Receive Rule Target Message Setting

When you set a message transmitted from another CAN node as a target (GAFLLB bit of GAFLIDj register is "0"), data processing using the receive rule is performed when a message transmitted from another CAN node is received.

When you set the own transmitted message as the target when using the mirror function (GAFLLB bit is "1"), data processing using the receive rule is performed when the own transmitted message is received.

Please refer to "4.4 Mirror Function Setting" for mirror function.

#### 5.4 IDE Mask/RTR Mask/ID Mask Setting

Set mask values for IDR/RTR/ID values.

The bits that are not masked in IDE mask/RTR mask/ID mask become effective in the acceptance filter processing.

# 5.5 DLC Check Value Setting

Set DLC value of the receive rule to be compared with DLC value of received message when the DLC check is enabled.

Please refer to "4.2 DLC Check Setting" for DLC check.

#### 5.6 Routing Processing

When the payload length of the received message exceeds the payload storage size of the storage buffer, the CMPOF flag in the GERFL register is set to 1 (payload overflow) and the processing is handled according to the CMPOC bit in the GCFG register. When the CMPOC bit is "0", the received message which exceeds the payload storage size is not stored in the buffer. When the CMPOC bit is "1", the received message is stored in the buffer with payloads exceeding the storage size being discarded.

## 5.7 Receive Rule Label Setting

Set added 12-bit label information when message that passed through filter processing is stored to buffer.

Any value can be set as a label, and it is able to freely use received message label by program. For example, if you set the receiving channel number to the label, it is possible to check which channel the message with same ID in the receive FIFO buffer was received.

# 5.8 Storage Buffer Setting

Set the buffer to store message that passed through filter processing.

The buffers that can be selected as a storage destination are shown below.

- Receive buffer q (Only one buffer can be selectable per receive rule.)

- Receive FIFO buffer q

- Transmit/Receive FIFO buffer k (receive mode)

- Transmit Queue

Maximum 8 storage buffers are selectable for 1 receive rule. However, it is only possible to select one receive buffer as storage destination. (For example, it is not possible to store to receive buffer 0 and 1.)

Setting example of maximum storage destination)

Example 1)

C: Receive buffer 1 + Receive FIFO buffer 0,2,4 + Transmit/Receive FIFO buffer 0,3,6,9 (Total 8 buffers)

Example 2)

C: Transmit FIFO buffer 0,1,2,3 + Transmit/Receive FIFO buffer 0,3,6,9(Total 8 buffers)

Impossible setting example)

Example 3)

$\times$ : Store to the receive buffer 0, receive buffer 1, Receive FIFO buffer 2 \*Storing in two receive buffers is impossible.

# 5.9 Use Example of Receive Rule

Use example of receive rule are shown below.

• Example 1

Example of each register is shown when the following messages are received.

ID format : Standard IDMessage format : Data frame

— Mirror Function : Message receive from another CAN node

— Receive ID

—  $120_H$ ,  $121_H$ ,  $122_H$ ,  $123_H$  — DLC

: Receive message DLC ≥ 6

— Label :  $010_H$

— Storage destination buffer : Receive buffer 3, Receive FIFO buffer 0, 1, 2

|                          |                             | GAFLIDE | GAFLIDEM | GAFLRTR | GAFLRTRM | GAFLLB | GAFLID/GAFLIDM  |                    |                       |                       |  |

|--------------------------|-----------------------------|---------|----------|---------|----------|--------|-----------------|--------------------|-----------------------|-----------------------|--|

|                          |                             |         | 1        |         | 4        |        | Bit28-24        | Bit23-16           | Bit15-8               | Bit7-0                |  |

| GAFLIDj                  |                             | 0       | 1        | 0       | -        | 0      | $00000_{\rm B}$ | $00000000_{\rm B}$ | 00000001 <sub>B</sub> | $00100000_{\rm B}$    |  |

| GAFLMj                   |                             | -       | 1        | -       | 1        | _      | $00000_{B}$     | 00000000B          | 00000111 <sub>B</sub> | 11111100 <sub>B</sub> |  |

|                          | 120 <sub>H</sub>            |         |          |         |          |        | В               | В                  | 001 <sub>B</sub>      | $00100000_{\rm B}$    |  |

| Receivable               | Receivable 121 <sub>H</sub> |         | 0        | 0       | _        | 0      | В               | В                  | 001 <sub>B</sub>      | 00100001 <sub>B</sub> |  |

| message 122 <sub>H</sub> |                             | 0       | U        | U       | 0        | U      | В               | В                  | 001 <sub>B</sub>      | $00100010_{\rm B}$    |  |

|                          | 123 <sub>H</sub>            |         |          |         |          |        | в               | В                  | 001 <sub>B</sub>      | 00100011 <sub>B</sub> |  |

|         | GAFLDLC | GAFLPTR       | GAFLRMV | GAFLRMDP | GAFLSRD2 | GAFLSRD1 | GAFLSRD0 | GAFLFDP           |

|---------|---------|---------------|---------|----------|----------|----------|----------|-------------------|

| GAFLP0j | 6       | $010_{\rm H}$ | 1       | 3        | 0        | 0        | 0        | _                 |

| GAFLP1j | _       | _             | _       | _        | _        | _        | _        | $0000007_{\rm H}$ |

• Example 2

Example of each register is shown when below messages are received.

ID format : Extension IDMessage format : Data flame

— Mirror function : Receive message from another CAN node.

Receive ID : 130<sub>H</sub>, 131<sub>H</sub>, 2130<sub>H</sub>, 2131<sub>H</sub>

DLC : Unused DLC check

— Label : 130<sub>H</sub>

— Storage destination buffer : Receive FIFO buffer 4, 6, Transmit FIFO buffer 1, 2 (ch0)

|            | GAFLIDE           | GAFLIDEM | GAFLRTR | GAFLRTRM | GAFLLB | GAFLID/GA | AFLIDM             |                       |                       |                       |

|------------|-------------------|----------|---------|----------|--------|-----------|--------------------|-----------------------|-----------------------|-----------------------|

|            |                   |          | V       |          | М      |           | Bit28-24           | Bit23-16              | Bit15-8               | Bit7-0                |

| GAFLIDj    |                   | 1        | 1       | 0        | ı      | 0         | $00000_{B}$        | $00000000_{B}$        | 0000001 <sub>B</sub>  | $00110000_{B}$        |

| GAFLMj     |                   | -        | 1       | -        | 1      | 1         | 11111 <sub>B</sub> | 11111111 <sub>B</sub> | 11011111 <sub>B</sub> | 11111110 <sub>B</sub> |

|            | 130 <sub>H</sub>  |          |         |          |        |           | $00000_{\rm B}$    | $00000000_{\rm B}$    | 00000001 <sub>B</sub> | 00110000 <sub>B</sub> |

| Receivable | 131 <sub>H</sub>  | 1        | 0       | 0        | 0      | 0         | $00000_{\rm B}$    | $00000000_{\rm B}$    | 00000001 <sub>B</sub> | 00110001 <sub>B</sub> |

| Message    | 2130 <sub>H</sub> | 1        | U       | U        | U      | U         | $00000_{B}$        | $00000000_{B}$        | 00100001 <sub>B</sub> | 00110000 <sub>B</sub> |

|            | 2131 <sub>H</sub> |          |         |          |        |           | $00000_{\rm B}$    | $00000000_{\rm B}$    | 00100001 <sub>B</sub> | 00110001 <sub>B</sub> |

|         | GAFLDLC | GAFLPTR       | GAFLRMV | GAFLRMDP | GAFLSRD2 | GAFLSRD1 | GAFLSRD0 | GAFLFDP            |

|---------|---------|---------------|---------|----------|----------|----------|----------|--------------------|

| GAFLP0j | 0       | $130_{\rm H}$ | 1       | 3        | 0        | 0        | 0        | _                  |

| GAFLP1j | _       | _             | _       | -        | -        | -        | _        | $00000650_{\rm H}$ |

# Example 3

• Example of each register is shown when below messages are received.

— ID format : Unused ID check— Message format : Data frame

— Mirror function : Receive message from another CAN node.

— Receive ID : All ID (Standard ID/Extension ID)

— DLC : DLC≥0xF (64 bytes) of receive message

— Label :  $010_H$

— Storage destination buffer : CAN0 transmit queue 0

|                             | GAFLIDE   | GAFLIDEM | GAFLRTR | GAFLRTRM | GAFLLB | GAFLID/GA | FLIDM       |                    |                    |                    |

|-----------------------------|-----------|----------|---------|----------|--------|-----------|-------------|--------------------|--------------------|--------------------|

|                             |           |          | 1       |          | ^      |           | Bit28-24    | Bit23-16           | Bit15-8            | Bit7-0             |

| GAFLIDj                     |           | 0        | -       | 0        | -      | 0         | В           | В                  | В                  | В                  |

| GAFLMj                      |           | -        | 0       | -        | 1      | -         | $00000_{B}$ | $00000000_{\rm B}$ | $00000000_{\rm B}$ | $00000000_{\rm B}$ |

| Receivable xxx <sub>B</sub> |           | 0        | 0       | 0 0      |        | 0         | В           | В                  | xxx <sub>B</sub>   | XXXXXXXX           |

| Message                     | XXXXXXXXB | 1        | 0       | 0        | 0      | 0 0       | XXXXXB      | XXXXXXXXB          | XXXXXXXXB          | XXXXXXXX           |

|         | GAFLDLC | GAFLPTR       | GAFLRMV | GAFLRMDP | GAFLSRD2 | GAFLSRD1 | GAFLSRD0 | GAFLFDP            |

|---------|---------|---------------|---------|----------|----------|----------|----------|--------------------|

| GAFLP0j | $F_{H}$ | $010_{\rm H}$ | 0       | 0        | 0        | 0        | 1        | _                  |

| GAFLP1j | _       | _             | _       | _        | -        | -        | _        | $00000100_{\rm H}$ |

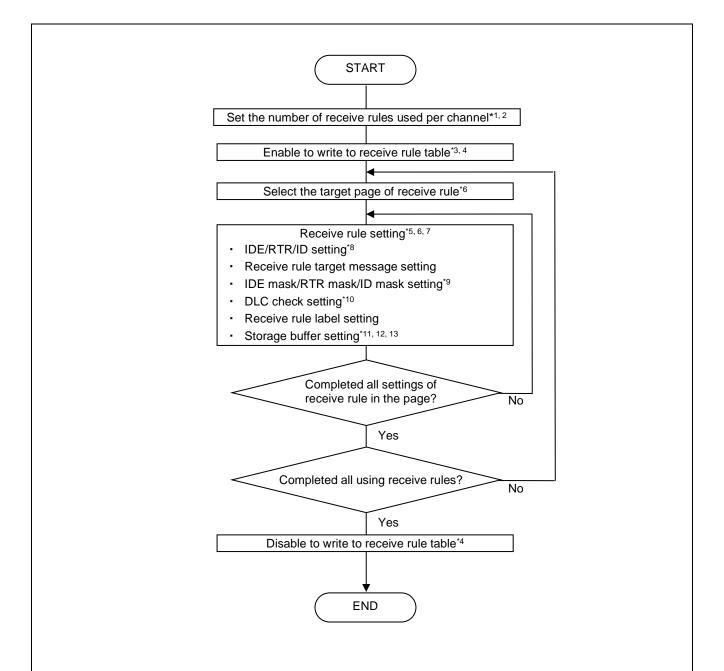

# 5.10 Receive Rule Table Setting Procedures

Figure 5-3 shows the receive rule table setting procedure.

Set these settings during CAN configuration.

Please refer to "1. CAN Configuration" for CAN configuration processing.

- Note 1. Rewrite number of receive rule setting (RNC(0 + v \* 2)[8:0] bits and RNC(1 + v \* 2)[8:0] bits in GAFLCFGv registers) in global reset mode.

- Note 2. Meet following conditions for the number of receive rules used per channel(RNC(0 + v \* 2)[8:0] bits and RNC(1 + v \* 2)[8:0] bits).

- Set the number of rules per channel to 384 or less.

- The total of the number of rules allocated to each channel is not larger than the number of rules permitted to the entire module.

- Note 3. After completion of writing to the receive rule table, set write disabled (AFLDAE bit in the GAFLECTR register is set to "0").

- Note 4. Do not set the page more than number of pages that can be set in module to setting target page (AFLPN[6:0] in the GAFLECTR register).

- Note 5. Rewrites receive rule(GAFLIDj register, GAFLMj register, GAFLP0j register, GAFLP1j register) under the condition of receive rule table write enable (AFLDAE bit is "1") and global reset mode.

- Note 6. Set the receive rules for each channel consecutively. It is not possible to share or alternately set them with other channels.

- Note 7. In standard ID, set standard ID values to bits 10 to 0 of ID (AFLID [28:0] bits in GAFLIDj register), and set "0" to bits 28 to 11.

- Note 8. If IDE bit is not compared (GAFLIDEM bit in GAFLMj register is "0"), set all ID bits to not compare (set all GAFLIDM[28:0] bits in the GAFLMj register to 0).

- Note 9. It is valid only when the DLC check function is enabled (DCE bit in the GCFG register is set to 1).

- Note 10. Up to eight FIFO buffers can be selected. However, when the message is stored in the receive buffer (GAFLRMV bit in the GAFLP0) register is set to 1), up to seven FIFO buffers can be selected.

- Note 11. Select only receive FIFO buffers or transmit/receive FIFO buffers set to receive mode or gateway mode.

- Note 12. When selecting a receive buffer as the storage destination, enable storing to the receive buffer (GAFLRMV bit is "1"), and set the number smaller than the number of receive buffers to be used (setting value to NRXMBm[7:0] bit of RMNBy register).

Figure 5-3 Receive Rule Table Setting Procedure

#### Buffer, FIFO Buffer

Set buffers and FIFO buffers used for transmission and reception. Following buffer and FIFO buffer setting are required.

- 6.1 Receive Buffer Setting

- 6.2 Receive FIFO Buffer Setting

- 6.3 Transmit/Receive FIFO Buffer Setting

- 6.4 Transmit Buffer Setting

- 6.5 Transmit Queue Setting

- 6.6 Transmit History Buffer Settings

- 6.7 Buffer Setting Procedures

- 6.8 Flexible CAN Mode

Table 6-1 shows the limitations on the number of buffers that can be set for receive buffers, receive FIFO buffers, and transmit/receive FIFO buffers. Refer to "User's Manual Hardware: Figure 23.27 Message Buffer Configuration" for each buffers configuration.

Table 6-1 Limitations on the number of buffers

|       |                                     | U2A-EVA<br>U2A16<br>U2A8                                               | U2A6<br>(BGA292)        | U2A6<br>(BGA176) | U2A6<br>(BGA156) | U2A6<br>(QFP144) |  |  |  |  |  |  |

|-------|-------------------------------------|------------------------------------------------------------------------|-------------------------|------------------|------------------|------------------|--|--|--|--|--|--|

| Chan  | nels                                | 16ch                                                                   | 12ch                    | 11ch             | 8ch              | 7ch              |  |  |  |  |  |  |

| Buffe | ers                                 | 5120 buffers                                                           | 1152 buffers            | 1056 buffers     | 768 buffers      | 672 buffers      |  |  |  |  |  |  |

| Indiv | idual buffer for                    | 1024                                                                   | 384 buffers             | 352 buffers      | 256 buffers      | 224 buffers      |  |  |  |  |  |  |

| each  | channel                             | (64×16ch)                                                              | $32\times$ (chs)        |                  |                  |                  |  |  |  |  |  |  |

|       | Transmit<br>buffer                  | Each channel<br>64 buffers                                             | Each channel 32 buffers |                  |                  |                  |  |  |  |  |  |  |

|       | Transmit queue                      | 4 queues for each channel                                              |                         |                  |                  |                  |  |  |  |  |  |  |

| Share | d buffer                            | 4096 buffers                                                           | 768 buffers             | 704 buffers      | 512 buffers      | 448 buffers      |  |  |  |  |  |  |

| betwe | een channels                        | (256×16ch)                                                             |                         | 64×(number       | of channels)     |                  |  |  |  |  |  |  |

|       | Receive buffer                      | 256 buffers<br>(16×16ch)                                               |                         |                  |                  |                  |  |  |  |  |  |  |

|       | Receive FIFO buffer                 | 8 FIFO (Up to 128 buffers can be allocated per FIFO.)                  |                         |                  |                  |                  |  |  |  |  |  |  |

|       | Transmit/recei<br>ve FIFO<br>buffer | 3 FIFO for each channel (Up to 128 buffers can be allocated per FIFO.) |                         |                  |                  |                  |  |  |  |  |  |  |

U2A6 has a limited number of transmit buffers compared to other U2A devices.

Also, note that the index values pointing to the transmit buffers for U2A6 are discontinuous.

Refer to "User's Manual Hardware: Table 23.4 Indices for Individual Products" for details.

# 6.1 Receive Buffer Setting

Set number of buffers assigned to receive buffers and payload size that can be stored per buffer. It is possible to assign buffers of  $0\sim16\times$  number of channels to receive buffer. Receive buffer is not able to use if "0" is set to number of receive buffer.

There are no interrupt-related settings because there are no receive buffer-related interrupts.

# 6.2 Receive FIFO Buffer Setting

The required settings to use the receive FIFO buffer are shown below.

- Number of buffers and payload size setting

- Interrupt enable/disable setting, and interrupt source setting

#### 6.2.1 Number of Buffers setting

Set number of buffers assigned to the receive FIFO buffer and payload size.

There are 8 receive buffers, and maximum 128 buffers can be assigned.

Number of buffers assigned to receive FIFO buffer can be selected from 0\*3, 4, 8, 16, 32, 48, 64, 128.

#### 6.2.2 Interrupt enable/disable Setting, and Interrupt Source Setting

Receive FIFO Interrupt

Enable/Disable the receive FIFO interrupt and set the interrupt source. When using the receive FIFO interrupt, the interrupt source can be selected from the following.

- Receive FIFO interrupt occurs when the following condition selected by RFIGCV[2:0] bits in the RFCCx register is met. (RFIM bit in the RFCCx register is set to "0".)

- When a message is stored up to 1/8 of the receive FIFO buffer.\*4

- When a message is stored up to 2/8 of the receive FIFO buffer.

- When a message is stored up to 3/8 of the receive FIFO buffer.\*2

- When a message is stored up to 4/8 of the receive FIFO buffer.

- When a message is stored up to 5/8 of the receive FIFO buffer. \*2

- When a message is stored up to 6/8 of the receive FIFO buffer.

- When a message is stored up to 7/8 of the receive FIFO buffer. \*2

- When receive FIFO buffer is full.

- Receive FIFO interrupt occurs every time when a message reception is completed (RFIM bit of RFCCx register is "1").

If you do not use receive FIFO buffer, set 0 message (RFDC[2:0] bit of RFCCx register is "000<sub>B</sub>") to the number of buffers in the receive FIFO buffer.

When setting 4 messages to the number of buffers in the receive FIFO buffer (setting 001B to the RFDC[2:0] bits), do not select this condition.

Receive FIFO Full Interrupt Processing

If enables the receive FIFO buffer (RFFIE bit of RFCCx register is "1".), the receive FIFO full interrupt is occurred when the receive FIFO buffer is full.

Even if the use of receive FIFO buffer is disabled (RFE bit is "0") while interrupt request is occurred (RFFIF flag of RFSTSx register is "1"), the interrupt request flag (RFFIF flag) does not become "0" automatically. Set "0" to the interrupt request flag by the program.

### 6.3 Transmit/Receive FIFO Buffer Setting

Required settings for using transmit/receive FIFO are shown below.

- Number of buffers setting

- Interrupt enable/disable setting, and interrupt source setting

- Transmit/Receive FIFO mode setting

- Interval timer counter setting (Transmit mode, gateway mode)

- Transmit buffer link setting (Transmit mode, gateway mode)

# 6.3.1 Number of buffers setting

Set the number of buffers for the transmit/receive FIFO buffer.

There are three transmit/receive FIFO buffers for each channel, and maximum 128 buffers can be assigned. Number of buffers assigned to transmit/receive FIFO buffer can be selected from 0\*5, 4, 8, 16, 32, 48, 64, 128.

\_

<sup>&</sup>lt;sup>5</sup> If the transmit/receive FIFO buffer is not used, set the number of buffers in the transmit/receive FIFO buffer to 0 message (CFDC[2:0] bits in the CFCCLk register to "000<sub>B</sub>").

# 6.3.2 Interrupt Enable, Disable, Interrupt Source Setting

Set interrupt enable/disable setting, and interrupt source setting of each transmit/receive FIFO buffer. Table 6-2 shows settable interrupt source for each transmit/receive FIFO mode. Transmit/Receive FIFO transmission completion interrupt is the occurrence fact of CANm transmit interrupt. Refer to "9. CAN-related Interrupt" for CANm transmit interrupt occurrence factor.

Table 6-2 Transmit/Receive FIFO Buffer Interrupt Source

| Transmit/Receive<br>FIFO Mode | Interrupt Source                                              | e          |   | Interrupt Factor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------|---------------------------------------------------------------|------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receive mode                  | Transmit/Receive<br>FIFO receive interrupt                    |            | 0 | When the number of received messages reaches the condition set in CFIGCV[2:0] bits in the CFCCk register, a transmit/receive FIFO receive complete interrupt occurs.  CFIGCV[2:0] bit setting  000 <sub>B</sub> : When a message is stored up to 1/8 of the transmit/receive FIFO buffer.*6  001 <sub>B</sub> : When a message is stored up to 2/8 of the transmit/receive FIFO buffer.  010 <sub>B</sub> : When a message is stored up to 3/8 of the transmit/receive FIFO buffer.*1  011 <sub>B</sub> : When a message is stored up to 4/8 of the transmit/receive FIFO buffer.  100 <sub>B</sub> : When a message is stored up to 5/8 of the transmit/receive FIFO buffer.*1  101 <sub>B</sub> : When a message is stored up to 6/8 of the transmit/receive FIFO buffer.  110 <sub>B</sub> : When a message is stored up to 7/8 of the transmit/receive FIFO buffer.  110 <sub>B</sub> : When a message is stored up to 7/8 of the transmit/receive FIFO buffer.  111 <sub>B</sub> : When the transmit/receive FIFO buffer is full.  Receive complete interrupt of transmit/receive FIFO is occurred when a message reception is completed. |

|                               | Transmit/Receiv<br>FIFO one-frame rec<br>interrupt            | eive       | • | Trasnmit/Receive FIFO receives 1 frame message.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                               | Transmit/Receive F<br>Full interrupt                          | TFO        | 1 | Transmit/Receive FIFO is full.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Transmit mode                 | Transmit/Receive<br>FIFO transmission<br>completion interrupt | CFCCk.CFIM | 0 | Receive complete interrupt of transmit/receive FIFO is occurred when buffer becomes empty by completed message transmit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Transmit mode                 |                                                               |            | 1 | Receive complete interrupt of transmit/receive FIFO is occurred when a message transmit is completed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                               | Transmit/Receiv<br>FIFO one-frame tran<br>interrupt           |            |   | Trasnmit/Receive FIFO transmits 1 frame message.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

\_

<sup>&</sup>lt;sup>6</sup> Do not set if you set 4 messages (RFDC[2:0] bit is " $001_B$ ") to the number of buffers in the transmit/receive FIFO buffer.

# 6.3.3 Transmit/Receive FIFO Mode Setting

Set transmit/receive FIFO buffer mode. Settable from receive mode, transmit mode, and gateway mode.

- Receive mode

- It operates as receive FIFO buffer.

- Transmit mode

- It operates as transmit FIFO buffer

# 6.3.4 Interval Timer Counter Setting

Set counter source of interval timer counter and transmission interval. The interval timer counter is effective in transmit mode and gateway mode.

Table 6-3 shows the count source of interval timer counter and formula of interval time.

Table 6-3 Count Source of Interval Timer Counter and Formula of Interval Time

| CFITR bit and   | Count Source                                                                                 | Formula*                                         |

|-----------------|----------------------------------------------------------------------------------------------|--------------------------------------------------|

| CFITSS bit of   |                                                                                              |                                                  |

| CFCCk register  |                                                                                              |                                                  |

| 00 <sub>B</sub> | Clock obtained by dividing pclk by the value of ITRCP[15:0] bits in GCFGH register.          | $1/f_{CLK} \times 2 \times a \times b$           |

| 10 <sub>B</sub> | Clock obtained by dividing pclk by 10 times the value of ITRCP[15:0] bits in GCFGH register. | $1/f_{CLK} \times 2 \times a \times 10 \times b$ |

| x1 <sub>B</sub> | CANm nominal bit time clock                                                                  | $1/f_{CANBIT} \times b$                          |

a : pclk prescaler value (setting value of ITRCP[15:0] bits)

b : Setting value of message transmit interval (CFITT[7:0] bits in CFCCk register)

$f_{CLK}$ : pclk frequency

f<sub>CANBIT</sub> : CANm nominal bit time clock frequency

## 6.3.5 Transmit Buffer Link Setting

Link transmit/receive FIFO buffer to transmit buffer. Linking to the transmit buffer is valid only in transmit mode and gateway mode.

Do not assign transmit buffer linked to transmit/receive FIFO buffer to transmit quee. Only one transmit/receive FIFO buffer can be linked to one transmit buffer. Do not link multiple transmit/receive FIFO buffers to the same numbered transmit buffer.

#### 6.3.6 Transmit/Receive FIFO Buffer Overwrite Mode

In the gateway mode, if a transmit/receive FIFO buffer attempts to receive a new message while the transmit/receive FIFO buffer is full, the oldest data buffer is overwritten with the received message or the message is discarded. This operation is determined by the CFMOWN in the CFCCEk register.

|                  | Ü                                                                       |

|------------------|-------------------------------------------------------------------------|

| CFMOWM bit in    | Transmit/Receive FIFO Buffer Operation                                  |

| CFCCEk register  |                                                                         |

| $0_{\mathrm{B}}$ | If the transmit/receive FIFO buffer is full, the received message is    |

|                  | discarded.                                                              |

| $1_{\mathrm{B}}$ | If the transmit/receive FIFO buffer is full, the buffer with the oldest |

|                  | data is overwritten with the received message.                          |

## 6.4 Transmit Buffer Setting

Set to enable or disable the transmit complete interrupt for each transmit buffer.

There are 64 transmit buffers per channel for U2A-EVA, U2A16, and U2A8, and 32 buffers per channel for U2A6, which can be used for either transmit buffers, for linking to transmit/receive FIFO buffers (in transmit mode or gateway mode), or for transmit queues.

When using the transmit buffer as a link to the transmit/receive FIFO buffer (in transmit mode or gateway mode) or as a transmit queue, the corresponding TMCp register should be set to "00". The TMIEp bit of the corresponding TMIECy register should be set to "0" (interrupt disabled).

In addition, the transmit complete interrupt becomes a source of CANm transmit interrupt. Refer to "9. CAN-related Interrupt" for the occurrence factor of CANm.

## 6.5 Transmit Queue Setting

The settings required to use the transmit queue are shown below.

- Number of buffers setting

- Interrupt enable/disable setting, and interrupt source setting

## 6.5.1 Number of Buffers Settings

Set the number of buffers in the transmit queue.

There are four transmit queues per channel, and up to 32 buffers can be allocated to each transmit queue for U2A-EVA, U2A16, and U2A8, and up to 16 buffers for U2A6.

Table 6-4 shows the access window, number of stages, buffer allocation direction, routing, CPU access, and DMA access for TXQ0 to TXQ3.

Queue **Buffer Allocation** HW CPU DMA Access Satges Window U2A-EVA U2A6 U2A-EVA U2A6 routing access access U2A16 U2A16 access\* U2A8 U2A8 TXQ0 TXMB0 0,3-320,3-16TXMB0 -> TXMB0 -> Possible Possible Possible TXMB31 TXMB15 TXQ1 TXMB31 0.3 - 320,3-16 TXMB31 -> TXMB15 -> Possible Possible Impossible TXMB0 TXMB0 TXQ2 0,3-32 0,3-16 TXMB32 -> TXMB32 -> TXMB32 Possible Possible Impossible TXMB63 TXMB47

Table 6-4 TXQ0 to 3 Setting

HW routing access and CPU access/DMA access can not be used at the same time.

0,3-16

When using transmit queue 0 and transmit queue 1, set the total number of stages to 32 or less for U2A-EVA, U2A16, and U2A8, and 16 or less for U2A6.

TXMB63 ->

TXMB32

TXMB47 ->

TXMB32

Impossible

When using transmit queue 2 and transmit queue 3, set the total number of stages to 32 or less for U2A-EVA, U2A16, and U2A8, and 16 or less for U2A6.

When using a transmit queues, the transmit priority should be set to ID Priority.

\_

TXQ3

TXMB63

0,3-32

Possible

Possible

<sup>\*</sup> Access by gateway mode.

## 6.5.2 Interrupt Enable/Disable Setting, and Interrupt Source Settings

Set interrupt enable/disable settings and interrupt sources for the transmit queue. The table 6-5 shows the configurable insterrupt sources when using the transmit queue interrupt.

Table 6-5 Transmit Queue Interrupt Source

| Queue<br>Status | Interrupt Source                             |             |   | Interrupt Source                                                                                                                              |

|-----------------|----------------------------------------------|-------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------|

|                 | Transmit queue transmit                      | TXQCC.TXQIM |   | When the buffer becomes empty due to the completion of message transmission, the transmit queue transmit completion interrupt request occurs. |

| In<br>Transmit  | completion interrupt                         | .TXQIM      | 1 | Transmit queue transmit completion interrupt request occurs for each message transmission completed.                                          |

|                 | Transmits queue one-frame transmit interrupt |             |   | When the transmit queue transmitted a message for one frame.                                                                                  |

| GW<br>Mada*l    | Transmits queue one-frame receive inetrrupt  |             |   | When the transmit queue received a message for one frame.                                                                                     |

| Mode*1          | Transmit queue full interrupt                |             | - | When the transmit queue is full.                                                                                                              |

The transmit queue interrupt is also a source of CANm transmit-related interrupt. Refer to "9. CAN-related Interrupts" for the source of CANm transmit interrupts.

#### 6.5.3 Transmit Queue Overwrite Mode

The transmission queue overwrite mode setting allows the user to select message overwrite/discard when a message with the same ID is stored in the transmission queue.

• When the transmit queue overwrite mode is selected\*2

When a message with the same ID as the message stored in the transmit queue is stored, the stored message with the same ID is overwritten.

\_

<sup>\*1</sup> The transmit queue 3 cannot be set to GW mode.

<sup>\*2</sup> The transmit queue overwrite mode can be set for each transmit queue, set by the TXQOWE bit of TXQCC0 to 3m register.

## 6.6 Transmit History Buffer Settings

The settings required to use the transmit history buffer are shown below.

The transmit history buffer can store 64 transmit history data per channel.

- Storage target buffer setting

- Interrupt enable/disable and interrupt source settings

## 6.6.1 Storage Target Buffer Setting

Set target buffer for storing transmit history data to transmit history buffer. The target buffer to be stored can be selected from the following.

Also, you can set whether or not to store the transmit history data of the message at the time of storing the transmit message.

- Entries from transmit/receive FIFO buffers and transmit queues.

- Entries from transmit buffers, transmit/receive FIFO buffers, and transmit queues.

## 6.6.2 Interrupt Enable/Disable and Interrupt Source Settings

Set transmit history interrupt enable/disable setting and interrupt source. Transmit history buffer interrupt sources are shown below.

- Transmit history interrupt is occurred when data is stored up to 3/4 of the number of transmission history buffer stages.

- Transmit history interrupt is occurred each time a transmit history data storage is completed.

In addition, transmit history interrupt becomes a source of CANm transmit interrupt. Refer to "9. CAN-related Interrupts" for the source of CANm transmit interrupts.

## 6.7 Buffer Setting Procedures

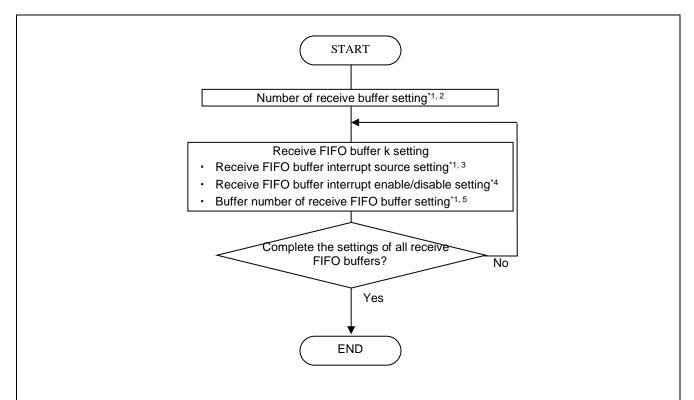

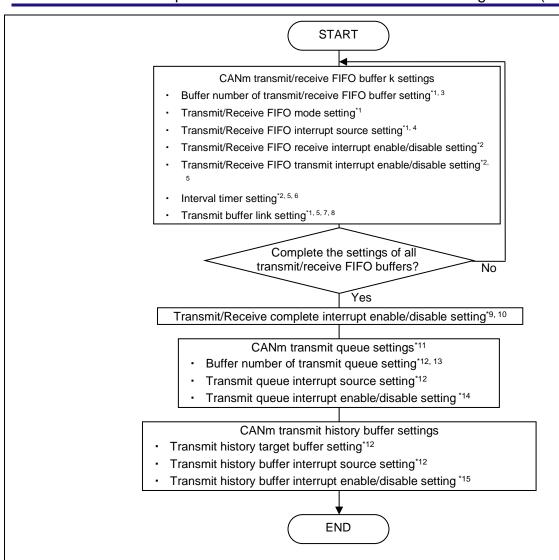

Figure 6-1 shows the procedure for setting the receive buffer and receive FIFO buffer, and Figure 6-2 shows the procedure for setting the transmit FIFO buffer, transmit buffer, and transmit history buffer.

These settings should be performed during CAN configuration.

Please refer to "1 CAN Configuration" for CAN configuration procedure.

- Note 1. Rewrite the RMNB register, the RFIGCV[2:0] bits, the RFIM bit, and the RFDC[2:0] bits in the RFCCx register in the global reset mode.

- Note 2. The receive buffer cannot be used if the number of receive buffer (NRXMB[7:0] bits in RMNB register) is set to "0". Also, set the number in the range of 0 to 16 x number of channels.

- Note 3. If you set the number of buffers in the receive FIFO buffer to 4 messages (RFDC [2:0] bit is "001<sub>B</sub>"), please set the RFIGCV[2:0] bits to "001<sub>B</sub>", "011<sub>B</sub>", "101<sub>B</sub>", or "111<sub>B</sub>".

- Note 4. Perform the receive FIFO buffer enable/disable (RFIE bit in RFCCx register) settings in the state the receive FIFO buffer is not used (RFE bit of RFCCx register is "0").

- Note 5. Do not use receive FIFO buffer if buffer number of receive FIFO buffer is set to "0" (RFDC[2:0] bits are "000<sub>B</sub>").

Figure 6-1 Receive Buffer and Receive FIFO Buffer Setting Procedures

- Note 1. Rewrite the CFDC [2:0] bits, the CFIM bit, the CFIGCV [2:0] bits, the CFM[1:0] bits, and the CFTML[4:0] bits in the CFCCk register in the global reset mode.

- Note 2. Rewrite the CFRXIE bit, the CFTXIE bit, the CFITR bit, the CFITSS bit, and the CFITT [7:0] bits in the CFCCk register in the state the transmit/receive FIFO buffer is not used (CFE bit in CFCCk register is "0").

- Note 3. Set it to zero message (CFDC [2:0] bit to "000<sub>B</sub>") if the transmit/receive FIFO buffer is not used.

- Note 4. If you set four messages (CFDC [2:0] bit is "001<sub>B</sub>") to the number of buffers in the transmit/receive FIFO buffer, please set "001<sub>B</sub>", "011<sub>B</sub>", "101<sub>B</sub>", or "111<sub>B</sub>" to CFIGCV [2:0] bit.

- Note 5. Valid only for transmit/receive FIFO buffers set to transmit mode or gateway mode.

- Note 6. Set "0" to the message transmit interval (CFITT [7:] bits in CFCCk register) if the interval timer is not used.

- Note 7. Set the different values to the link destination (CFTML [4:0] bit) of the transmit/receive FIFO buffers (transmit mode, gateway mode) in the same channel.

- Note 8. Do not set the transmit buffer assigned to the transmit queue to the link destination (CFTML[4:0] bits) of the transmit/receive FIFO buffer (transmit mode and gateway mode).

- Note 9. Perform the transmit buffer interrupt enable/disable (TMIEp bit of TMIECy register) setting when the corresponded transmit buffer has no transmit request (TMTR flag in TMSTSp register is "0").

- Note 10. Set the TMIEp bit corresponding to the transmit buffer linked to the transmit FIFO buffer or the transmit buffer assigned to the transmit queue to "0".

- Note 11. When using the transmit queue, set the transmit priority to ID priority (TPRI bit in the GCFG register to "0").

- Note 12. Rewrite the TXQDC[4:0] bits and TXQIM bit in the TXQCC0 to 3m register and the THLDTE bit and THLIM bit in the THLCCm register in the channel reset mode.

- Note 13. The transmit queue cannot be used if the number of buffers (TQDC[4:0] bits) of the transmit queue is set to "0". Also, do not set "1".

- Note 14. Perform the transmit queue interrupt enable/disable (TXQFIE bit, TXQOFRXIE bit and TXQOFTXIE bit in TXQCC0 to 3m register) settnig when the transmit queue is not in use (TQE bit is "0").

- Note 15. Rewrite when the transmit history buffer is not in use (THLE bit in THLCCm register is "0").

Figure 6-2 Transmit Buffer, Transmit/Receive FIFO Buffer, and Transmit History Buffer Setting Procedures

#### 6.8 Flexible CAN Mode

In Flexible CAN mode, two channels can be connected and treated like a single CAN channel.

Refer to "User's Manual Hardware: Figure 23.58 Diagram of the Flexible CAN" for flexible CAN mode channel connection.

The pairs of CAN channels that can be connected in flexible CAN mode are shown below.

- Channel 0 and channel 1 (Set FLXC0 bit in GFCMC register)

- Channel 2 and channel 3 (Set FLXC1 bit in GFCMC register)

- Channel 4 and channel 5 (Set FLXC2 bit in GFCMC register)

- Channel 6 and channel 7 (Set FLXC3 bit in GFCMC register)

In Flexible CAN mode, odd-numbered channels (channels 1, 3, 5, 7) use the input/output pins of even-numbered channels (channels 0, 2, 4, 6). The input/output pins of odd-numbered channels (channels 1, 3, 5, 7) set to Flexible CAN mode cannot be used.

In Flexible CAN mode, each channel performs communication processing independently, but if one channel is performing transmission, the other channel does not return the ACK bit.

#### 6.9 Transmit Buffer Allocation

There are 64 transmission buffers per channel, but by using the flexible transmission buffer assignment function, up to 64 + 32 (U2A-EVA, U2A16, U2A8) or 16 (U2A6) transmission buffers can be allocated. Refer to "Figure 23.60 Flexible transmission buffer assignment" for the buffer allocation example in the flexible CAN mode.

The channels that can lend and borrow buffers between each channel are shown below.

- Channel 0 and channel 1 (FLXMB0 bit in GFTBAC register)

- Channel 2 and channel 3 (FLXMB1 bit in GFTBAC register)

- Channel 4 and channel 5 (FLXMB2 bit in GFTBAC register)

- Channel 6 and channel 7 (FLXMB3 bit in GFTBAC register)

The number of allocated buffers can be set for each pair with the FLXMBv [3: 0] bits in the GFTBAC register. Table 6-6 shows the number of buffers that can be set and the setting value of FLXMBv.

Table 6-6 Setting the number of allocated buffers

| Number of allocated buffers | FLXMBv setting value*1 |

|-----------------------------|------------------------|

| 0                           | $0000_{\rm B}$         |

| 4                           | 0001 <sub>B</sub>      |

| 8                           | $0010_{\rm B}$         |

| 12                          | 0011 <sub>B</sub>      |

| 16                          | $0100_{\rm B}$         |

| 20                          | 0101 <sub>B</sub>      |

| 24                          | $0110_{\rm B}$         |

| 28                          | 0111 <sub>B</sub>      |

| 32                          | $1000_{\rm B}$         |

It is prohibited to set GFTBAC (buffer allocation) and GFCMC (configuration) at the same time.

The lending buffer interrupt occurs on the lending channel.

In the case of using transmit queues, allocate a buffer for each channel to the transmit queue for each channel.

The state of the buffer changes depending on the mode of the lending channel.

Example) If the flexible transmission buffer assignment function is used on channels 0-1, channel 0 cannot lend a buffer on channel 1 if channel 1 is reset.

<sup>\*1</sup> Setting values for FLXMBv other than those shown in Table 6-6 are prohibited.

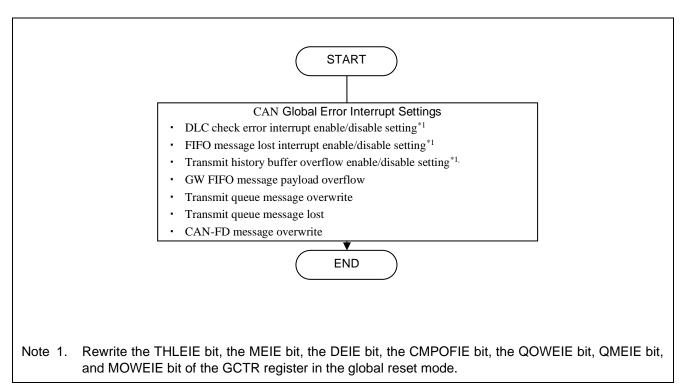

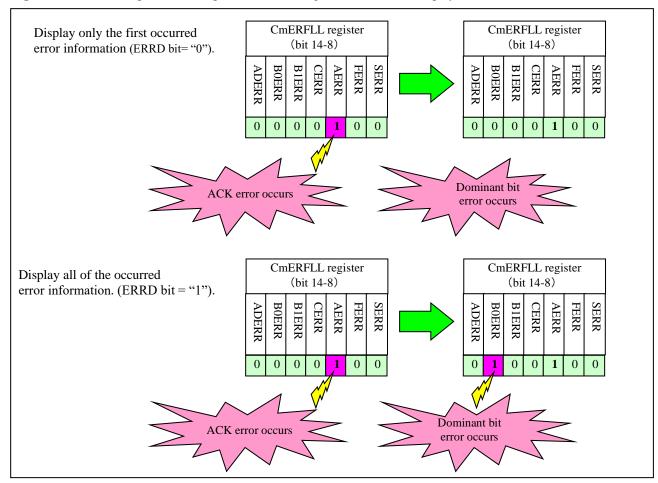

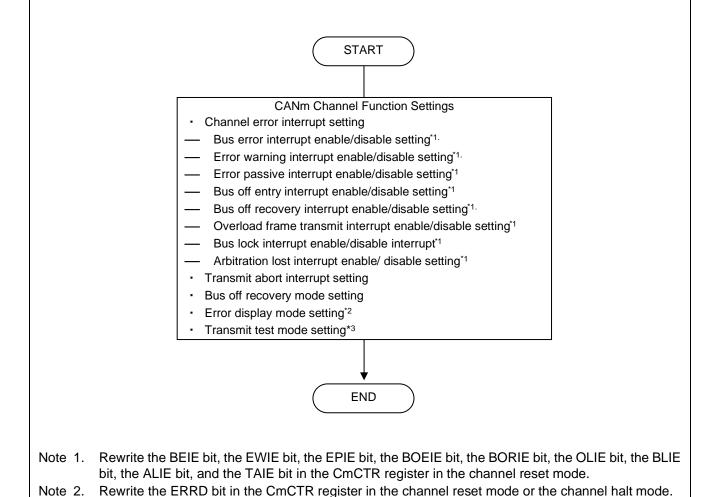

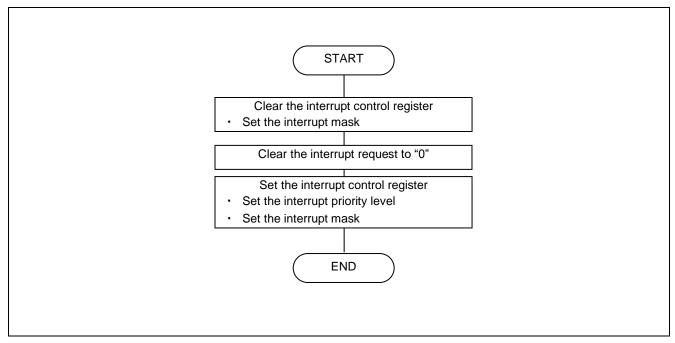

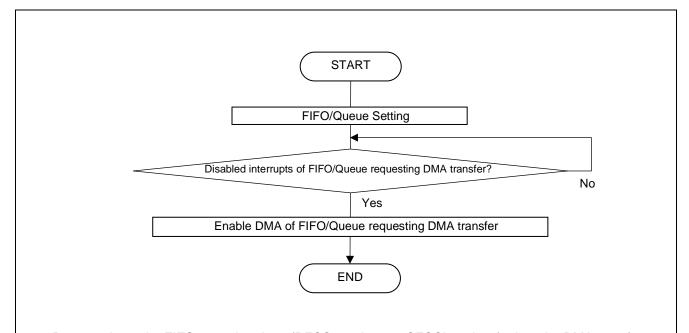

## Global Error Interrupt