# RENESAS

# Implementing Cell Balancing with the RAA489206/ISL94216A BFE

Cell balancing is the process of modifying the level of charge in cells on a cell-by-cell basis. This application note reviews basic concepts on cell balancing and provides guidelines to configure and use the cell balancing functionalities of the RAA489206 and ISL94216A Battery Front Ends (BFEs).

### Contents

| 1. | Causes and Consequences of Cells Imbalance |                          |                                                        |  |  |

|----|--------------------------------------------|--------------------------|--------------------------------------------------------|--|--|

| 2. | Cell Balancing                             |                          |                                                        |  |  |

|    | 2.1                                        | Definitio                | n                                                      |  |  |

|    | 2.2                                        | Methods                  | s                                                      |  |  |

|    | 2.3                                        | When to                  | Perform                                                |  |  |

|    |                                            | 2.3.1                    | Relation of Open Circuit Voltage and State of Charge 4 |  |  |

|    |                                            | 2.3.2                    | Internal Impedance                                     |  |  |

| 3. | Cell Balancing Implementation              |                          |                                                        |  |  |

|    | 3.1                                        | Automatic Cell Balancing |                                                        |  |  |

|    |                                            | 3.1.1                    | Constant Current (CC)                                  |  |  |

|    |                                            | 3.1.2                    | Constant Current (CC) / Constant Voltage (CV)7         |  |  |

|    |                                            | 3.1.3                    | Sequence                                               |  |  |

|    | 3.2 Manual Cell Balancing                  |                          |                                                        |  |  |

|    |                                            | 3.2.1                    | Sequence Description                                   |  |  |

| 4. | Sample Code                                |                          |                                                        |  |  |

| 5. | Conclusion                                 |                          |                                                        |  |  |

| 6. | Revis                                      | Revision History         |                                                        |  |  |

### 1. Causes and Consequences of Cells Imbalance

Battery packs consist of several cells connected in series and parallel. Cells in series allow for achieving the required voltage range the application requires, whereas parallel cells provide the target capacity. All battery pack cells should be identical for optimal usage of the contained energy. They should have matched intrinsic parameters such as internal impedance, coulomb efficiency, capacity, terminal voltage, and State of Charge (SOC). However, these properties diverge from cell to cell in the packs, even if they belong to the same production lot. This divergence varies with extrinsic factors such as temperature and tends to increase during the battery life due to internal reactions and aging processes that do not occur equally in each cell. This imbalance results in suboptimal use and progressive degradation of the battery pack's usable capacity, lifetime, and performance.

Depending on the design and application, different criteria and setpoints are used to determine whether the cells of a battery pack are balanced. In this application note, battery pack cells are considered balanced when all cells have the same voltage per cell in a fully charged or discharged state. Therefore, the imbalance is caused by any process or event that makes a cell voltage diverge from another. For example, the difference in the coulomb efficiency determines the amount of effective charge transferred in or out of the cells. If cells have the same SOC and share the same current, but their coulomb efficiency is different, the SOC and Open Circuit Voltage (OCV) of the cells diverge. Another cause is the net current through the cells. The net current consists of the battery pack current (the main component) and the self-discharge and leakage currents (secondary components). The pack current is the same for all cells, whereas both secondary components can differ. This results in the different net current drawing through the cells and, consequently, different SOC and cell voltage. Coulomb efficiency and net current are temperature-dependent, so the lack of uniform temperature along the battery pack can worsen the imbalance.

Other parameters that make cell voltages diverge are total capacity and impedance difference. As the cells age, their full capacity deteriorates differently. Therefore, the SOC of each cell is different when cells are discharged by an equal amount from their fully charged state, causing imbalance of cells' OCV. Similarly, the internal impedance of cells varies differently due to aging processes, which does not cause differences in cells' OCV because there is no current flowing through the cells. The imbalance is only observable during discharge or charge when the internal impedance causes a voltage drop, resulting in lower terminal voltage. Consequently, weak cells with higher impedance exhibit lower voltage than those with lower impedance.

The consequences of having imbalanced cells in a battery pack are diverse. Weak cells (with lower total capacity and/or higher impedance) tend to be exposed to Overvoltage (OV) events because they exhibit higher voltage when the pack is being charged. Continuous exposure to OV accelerates cell degradation of weak cell capacity, increasing the imbalance cyclically and making OV exposure even more frequent. OV events degrade the pack performance and increase the risk of hazardous events. To prevent safety issues, the RAA489206 BFE features Overvoltage protection. By setting the BFE cell OV threshold according to the manufacturer's specifications, the BFE prevents cell voltage from exceeding its safe operation value. The cell OV threshold is usually set slightly greater than the value of the pack voltage divided by the number of cells to allow some imbalance between cells. However, a cell with a higher impedance hits the OV threshold before the other cells. Hitting early VCell OV does not allow the cells with lower impedance to achieve their fully charged state, so less energy is available for the application.

On the other hand, the same weak cells hit the Undervoltage (UV) threshold first. When VCell UV is reached by a weak cell, the BFE interrupts the charge transfer to the application, so cells whose voltage has not reached the limit and still have a releasable charge cannot deliver it. Not using the total capacity for which the battery pack is designed decreases the application's run time. The RAA489206 offers features enabling the designer to set up the part to perform automatic cell balancing or implement his own algorithm. The following sections provide detailed information about using RAA489206 features and the concepts and considerations to consider while implementing cell balancing.

# 2. Cell Balancing

### 2.1 Definition

Cell balancing aims to maximize the energy contained in the battery pack and extend its lifetime. In accordance with the definition of a balanced state based on cell voltage measurements, cell balancing is the procedure of equalizing the voltages among the cells of a battery pack. Ideally, cells are balanced when all cell voltages match perfectly, but this condition is impractical. The balanced state is defined as when the difference between each cell voltage and the minimum cell voltage ( $V_{cell-min}$ ) is lower than the Cell Balancing Minimum Delta Threshold

(V<sub>CB-min-delta</sub>).

The value of  $V_{CB-min-delta}$  must be defined by the battery pack designer considering design goals and specifications such as measurement accuracy, cell chemistry, and convergence time. The balanced state may not be achieved if  $V_{CB-min-delta}$  is set near the voltage measurement error. If the value is too small, the cell balancing procedure may take too long or not converge to the balanced state. Conversely, assigning a large value to  $V_{CB-min-delta}$  may not significantly reduce cell imbalance, so capacity use and the cell's lifetime are not maximized as intended. Regarding cell chemistry, some Li-ion cells have excellent quality control, so cells can be balanced to a 15mV match or better. LiPoly cells, on the other hand, may have problems reaching such matching levels and tend to suffer imbalance due to temperature, the difference in coulomb efficiency and self-discharge rate, and total capacity degradation. Cell quality can vary widely between sources.

### 2.2 Methods

Cell balancing methods are classified into two general groups: active and passive. Active methods use balancing circuits based on capacitors, transformers/inductors, or DC/DC converter techniques to move charge between cells. Passive methods discharge the cells by providing alternate paths for the current to flow through shunt resistors. Because the charge drained from the cell can be lost, balancing should be done while the battery is being charged so that the charger provides the additional charge necessary to balance all cells. Performing cell balancing during discharge is discouraged as it is a waste of energy. This application note refers to passive methods during charge; active methods and cell balancing during discharge are out of its scope.

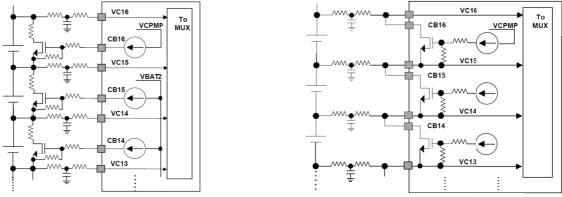

In passive balancing circuits, the balancing current is usually enabled by a FET that routes some of the charge current around the cells with the highest voltage. Figure 1 shows the cell balancing configurations featured by the RAA489206. The internal cell balancing configuration helps save space and is ideal for low current and slow battery charging applications. The external balancing FETs are used with large capacity and/or fast-charging battery packs.

a) Internal Cell Balancing Configuration

b) External Cell Balancing Configuration

### 2.3 When to Perform

Cell balancing can be performed along the whole charge cycle. However, there are some aspects the designer should consider when cell balancing is performed based on voltage measurements.

### 2.3.1 Relation of Open Circuit Voltage and State of Charge

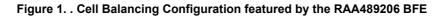

The OCV of cells and their SOC are in direct correlation. Figure 2 shows the relationship between the OCV and the SOC of a commercial cell. Although this relationship is different among cells of varying chemistry, geometry, and manufacturer, cell voltage tends to exhibit high variation regarding SOC (the derivate dOCV/dSOC) in the values near fully charged (100%) or fully discharged (0%) states. For example, the two data points in Figure 2 show the OCV for 0% and ~ 2% and their respective OCV values, 2.837V and 3.286V. It indicates that an increment of just 2% in the SOC results in a voltage imbalance of ~450mV. The variation can get even higher during charge due to the internal impedance and its inverse dependence on the SOC. Therefore, a slight imbalance in the SOC charge conveys a significant voltage difference near the fully discharged state, which may suggest the urgency of cell balancing. If cell balancing is performed under these conditions, discharging strong cells results in high voltage changes that either worsen the imbalance or prevent cell balancing from converging to the balanced state. Therefore, cell balancing should be performed in linear sections of the SOC-OCV curve when the slope dOCV/dSOC is low. For the example shown in Figure 2, the two linear sections between 20% and 40% and ~99% are good options for cell balancing.

Figure 2. Relation of Open Circuit Voltage (OCV) and State of Charge (SOC) of a Commercial Cell

#### 2.3.2 Internal Impedance

When there is DC current flowing through the battery pack, the cell voltage can be modeled as Equation 1, where the SOC-OCV relation gives OCV(SOC), I is the current passing through the cell (negative for discharging current, positive for charging current), and R is the cell Internal Resistance or Impedance, which is a function of the cell SOC and increases rapidly at low SOC.

(EQ. 1)  $V_{CELL} = OCV(SOC) + I \times R(SOC)$

During charge, the current is positive, so the voltage of cells with higher impedance is higher. This wrongly implies that these cells are strong and should be discharged to reach the balanced state, which is another reason for avoiding cell balancing at low SOC values. In addition, the internal impedance of cells is lower at high SOC values, so less energy is wasted as heat, which lowers the risk of increasing temperature differences among the cells. The imbalance caused by impedance difference can be recognized if the cells are in a balanced state when the battery pack is not being used (I = 0 A), and then charging or discharging the pack makes the cell voltage diverge.

The RAA489206 provides configuration settings for passive cell balancing during charge. Set the part to automatically select the cells to discharge or perform cell balancing on cells chosen by your algorithm deployed in the system managing the BFE. The following section details the use and setup of the automatic cell balancing features of the RAA489206.

# 3. Cell Balancing Implementation

Cell balancing can be performed while charging or discharging the battery pack. However, Renesas recommends performing cell balancing during the charging process because the energy to balance lower-voltage cells is taken from the charger, an external energy source. If cell balancing occurs during discharge, the energy stored in higher-voltage cells is wasted and can reduce the overall run-time of the battery pack. In addition, cell balancing during charge is safer because cell voltage is kept under control and the current is limited, so thermal runway and over/undervoltage or overcurrent events are less likely to occur.

Although the specific steps for balancing cells depend on the type of charger and the type of battery cells, the general process is as follows:

- 1. Connect the RAA489206 to the battery cells: The RAA489206 includes multiple channels for monitoring each cell's voltage, current, and temperature in the battery pack. Connect the appropriate voltage, current, and temperature sense lines to each cell as recommended in the RAA489206 datasheet.

- 2. Configure the RAA489206: Use the SPI or I2C interface to configure the BFE with the appropriate settings for your application, such as the number of cells in the battery pack, the voltage, current, and temperature threshold settings.

- 3. Select between the two cell balancing modes the RAA489206 features: Automatic Cell Balancing and Manual Cell Balancing. In automatic cell balancing, the RAA489206 selects and balances cells autonomously according to the device settings. In manual cell balancing, the master device must determine the cells to be balanced, select them in the RAA489206, and trigger the balancing operation.

- 4. Monitor the cell voltages: The RAA489206 monitors the voltage of each cell in the battery pack. When the maximum cell voltage is within a given range, and the threshold settings are met, the RAA489206 activates the cell balancing function if it is set to automatic mode. If the BFE is set to manual mode, the master device must select the cells to be balanced and trigger the cell balancing function.

- 5. Balance the energy between cells: The RAA489206 turns on the FETs that switch and close the circuit of the cells that should be discharged.

- 6. Monitor the balance state: In automatic mode, the RAA489206 continuously monitors the balance state of the cells, and when cell voltages and/or pack current meet the thresholds and conditions, the BFE stops performing the balancing function. In manual mode, the master device must monitor the values reported by the BFE and stop performing cell balancing when the required values are reached.

The following sections detail the configuration settings and behavior of functionalities to perform automatic and manual cell balancing with the RAA489206.

### 3.1 Automatic Cell Balancing

To set the RAA489206 to Automatic Cell Balancing, the master device must set the CB EN and Auto CB EN bits (0x25.[7,6]) to '11. Cell balancing can occur only when the maximum cell voltage is between the voltages specified by the Cell Balancing Minimum Threshold register (0x2C CBMIN Threshold) and the Cell Balancing Maximum Threshold register (0x2B CBMAX Threshold). Bits 0x25.0 CB CHRG, 0x25.1 CB EOC, and 0x25.3 IEOC EN determine the behavior of the automatic functionalities relative to 0x2D VEOC Threshold and 0x10 IEOC Threshold. The behavior of auto-cell balancing in relation to these bits and thresholds is described in the following subsections, which assume charging, automatic cell balancing is enabled, and at least one cell needs to be balanced. In addition, the voltage set by the Cell Overvoltage threshold register (0x06 VCell OV) is assumed to be set to the same value or slightly below the CBMAX Threshold to avoid overvoltage events. It is crucial to meet the battery manufacturer's maximum voltage ratings and safety recommendations to prevent hazardous events due to overvoltage.

The settings and behaviors described as follows, independent of the choice of internal versus external cell balancing and are grouped according to the charging method they support: Constant Current (CC) or Constant Current/Constant Voltage (CC/CV). The following figures show the behavior of the cell balancing functionalities that are intended to support CC and CC/CV chargers. Blue areas indicate the period during which cell balancing is

performed, whereas red areas indicate the period when cell balancing does not occur. The depicted values illustrate the general behavior and vary according to the battery pack design, charger, and battery type. Therefore, these values should not be assumed as references for Battery Management System (BMS) designs.

#### 3.1.1 Constant Current (CC)

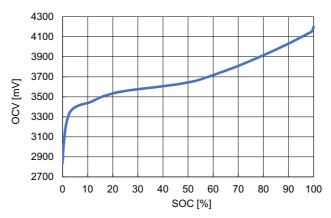

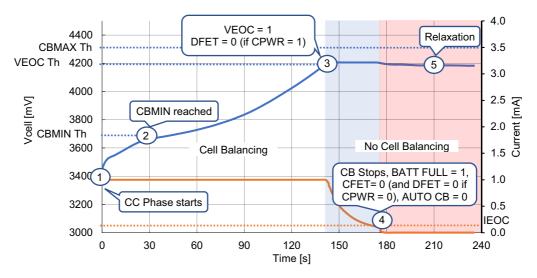

Figure 3 depicts the behavior of the BFE when CB CHRG = 1, IEOC EN = 0, CB EOC = 0. (1) Charge starts at constant current. (2) Cell balancing starts when a cell needing balancing is greater than CBMIN and less than CBMAX. (3) VEOC sets when the maximum cell voltage exceeds the VEOC threshold; this triggers BAT FULL to set, which stops Cell Balancing, shuts off CFET (and DFET if CPWR = 0), and clears AUTO CB. DFET remains on if CPWR = 1. (4) The cell voltage decreases slowly towards its post charge relaxation voltage.

Figure 3. Cell Balancing during Constant Current Charging with CB CHRG = 1, IEOC EN = 0, CB EOC = 0

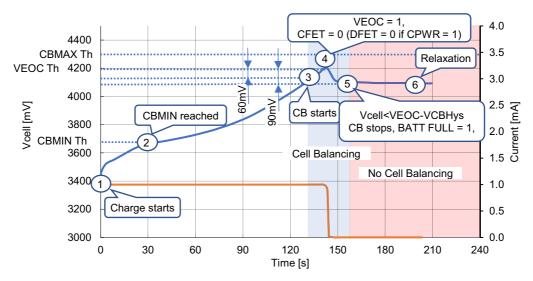

Figure 4 depicts the behavior of the BFE when CB CHRG = 1, IEOC EN = 0, CB EOC = 1. (1) Charge starts at constant current. (2) Cell voltage reaches CBMIN value, but cell balancing does not start until (3) cell voltages are within ~60mV of the VEOC threshold. (4) VEOC sets when the maximum cell voltage exceeds the VEOC threshold; this shuts off CFET (and DFET if CPWR = 0), which stops the charging process. Cell balancing continues until (5) cell voltages fall below VEOC – VCHys (~90mV), which stops cell balancing, sets BATT FULL bit and clears the AUTO CB bit. DFET remains on if CPWR= 1. (6) The cell voltage relaxes.

Figure 4. Cell Balancing during Constant Current Charging with CB CHRG = 1, IEOC EN = 0, CB EOC = 1

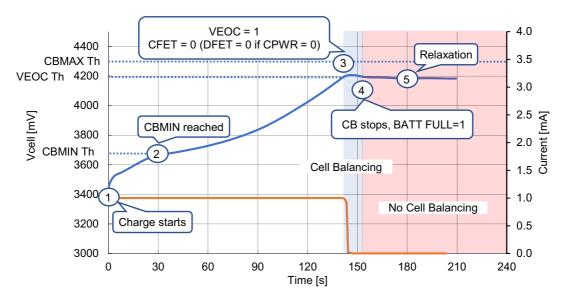

Figure 5 depicts the behavior of the BFE when CB CHRG = 0, IEOC EN = 0, and CB EOC = 1. (1) Charge starts at constant current. (2) Cell voltage reaches CBMIN value, but cell balancing does not start yet. Cells are charged until (3) the VEOC threshold is exceeded and the VEOC bit sets, which shuts off CFET (and DFET if CPWR = 0) and starts cell balancing. Cell balancing continues until (4) cell voltages fall below VEOC and stop, the BATT FULL bit is set, and AUTO CB is cleared. (5) The cell voltage relaxes.

Figure 5. Cell Balancing during Constant Current Charging with CB CHRG = 0, IEOC EN = 0, CB EOC = 1

#### 3.1.2 Constant Current (CC) / Constant Voltage (CV)

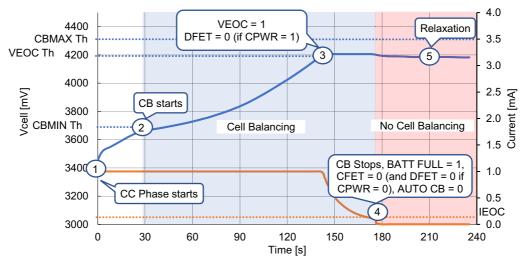

Figure 6 depicts the behavior of the BFE when CB CHRG = 1, IEOC EN = 1, and CB EOC = 0. (1) The CC charge phase starts. (2) Cell balancing starts when a cell needing balancing is greater than CBMIN and less than CBMAX. (3) VEOC sets when the highest cell voltage exceeds the VEOC threshold, and then cell balancing and DFET (if CPWR = 1) shut off. The charger changes from constant current to constant voltage. (4) When the charge current drops below the IEOC limit (0x10, page 80), BATT FULL is set, CFET (and DFET if CPWR = 0) is shut off, and AUTO CB is cleared. (5) The cell voltage relaxes.

Figure 6. Cell Balancing during Constant Current Charging with CB CHRG = 1, IEOC EN = 1, CB EOC = 0

Figure 7 depicts the behavior of the BFE when CB CHRG = 1, IEOC EN = 1, and CB EOC = 1. (1) The CC charge phase starts. (2) Cell balancing starts when a cell needing balancing is greater than CBMIN and less than CBMAX. (3) Cell balancing continues after VEOC is reached and the VEOC bit is set, but DFET shuts off if CPWR = 1. The charger changes from constant current to constant voltage. Cell balancing continues until (4) the charge current drops below the IEOC limit; next, BATT FULL is set, CFET (and DFET if CPWR = 0) is shut off, and AUTO CB is cleared. (5) The cell voltage relaxes.

Figure 7. Cell Balancing during Constant Current Charging with CB CHRG = 1, IEOC EN = 1, CB EOC = 1

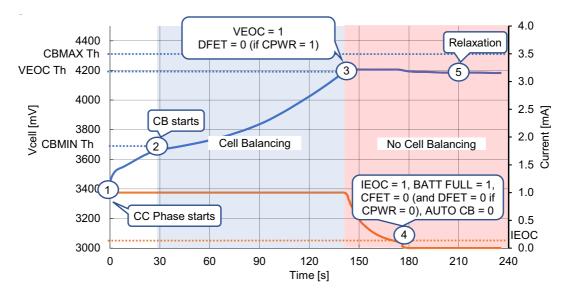

Figure 8 depicts the behavior of the BFE when CB CHRG = 0, IEOC EN = 1, and CB EOC = 1. (1) The CC charge phase starts. (2) Cell voltage reaches CBMIN value, but cell balancing does not start until (3) the VEOC threshold is exceeded, which sets VEOC and shuts off DFET if CPWR = 1. The charger changes from constant current to constant voltage. Cell balancing occurs when one or more cell voltages are above the VEOC limit and the charge current is above the IEOC limit. (4) BAT FULL is set when the charge current drops below the IEOC limit. When BATT FULL is set, CFET is shut off (and DFET if CPWR = 0), and AUTO CB is cleared. (5) The cell voltage relaxes.

Figure 8. Cell Balancing during Constant Current Charging with CB CHRG = 0, IEOC EN = 1, CB EOC = 1

#### 3.1.3 Sequence

Registers 0x26-27 CB Cell State specify the cells automatically determined by the chip to need cell balancing following the most recent set of cell voltage measurements during the scan before automatic cell balancing.

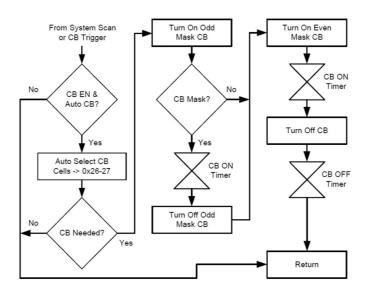

Figure 9 illustrates the Automatic Cell Balancing sequence. *Important*: Write all settings to the RAA489206 before executing the bit 0x01.0 System Trigger. This example assumes the RAA489206 is in SCAN mode; the system is charging the battery pack and the sequence reached the Cell Balance step. The same sequence is followed if AUTO CB is enabled and cell balancing is started by setting the bit 0x25.4 CB Trigger.

Figure 9. Automatic Cell Balancing Sequence

#### 3.1.3.1 Sequence Description

- CB EN & Auto CB? If 0x25.7 CB EN and 0x25.6 Auto CB EN are enabled, the CB sequence moves to the next step; otherwise, it exits and returns to the System Scan sequence step Scan Delay (see datasheet).

- Auto Select CB Cells For the three cases of automatic cell balancing where IEOC EN = 1 OR CB EOC = 0, the chip finds the minimum of all the cell voltages and calculates the difference between each cell voltage and the minimum. For cells with a calculated difference higher than the 0x2A CB Min Delta Threshold, the CB Cell State bit is set to 1. For other cells, it is set to 0.

For automatic cell balancing cases with IEOC EN = 0 AND CB EOC = 1, the CB Cell State bit is set to 1 for cells that exceed the voltage set by the register 0x2D VEOC Threshold minus four bits. For other cells, it is set to 0.

CB Needed? – If no cells require cell balancing or the criteria determined by the settings of bits CB CHRG, IEOC EN, and CB EOC are not met, the cell balance sequence exits and returns to step Scan Delay. Otherwise, the CB sequence moves to the next step.

Note: If ALITO CB EN = 0, the bit 0x66 0 Need CB is an indicator to the user.

*Note*: If AUTO CB EN = 0, the bit 0x66.0 Need CB is an indicator to the user.

- Turn On Odd Mask CB Cell balance devices for the odd-numbered cells that were automatically determined to require balancing as indicated by the CB Cell State registers 0x26-27 are turned on.

- CB Mask? If the bit 0x25.2 CB Mask is clear (0), the sequence moves to the Turn On Even Mask CB step; otherwise, the CBON Timer is activated per the following step.

- CBON Timer The timer setting 0x28 CBON determines how long the cell balance FETs are enabled for each balancing cycle. The sequence moves to the next step after the CBON Timer times out.

- Turn Off Odd Mask CB Cell balance FETs for the odd cells are turned off.

- Turn On Even Mask CB The cell balance FETs for the even-numbered cells that were automatically determined to require balancing as indicated by the CB Cell State registers 0x26-27 are turned on.

- CBON Timer The timer setting 0x28 CBON determines how long the cell balance FETs are enabled for each balancing cycle. The sequence moves to the next step after the CBON Timer times out.

- Turn Off CB Cell Balance FETs are turned off.

- CBOFF Timer The timer setting 0x29 CBOFF determines how long the cell balance FETs are disabled following each balancing cycle. This step is necessary when long cell balancing times are relative to the setting of 0x2E.2:0 Scan Delay are used. The CBOFF timer also manages power dissipation. The sequence moves to the next step after the CBOFF Timer times out.

- Return The CB state machine exits and returns to the Scan sequence at Scan Delay after the CBOFF Timer times out.

### 3.2 Manual Cell Balancing

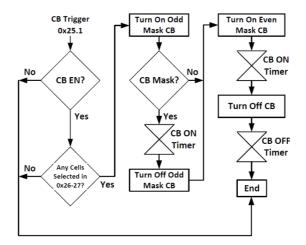

Figure 10 shows the manual cell balancing sequence, which is similar to that of Automatic Cell Balancing with a few important differences. Bit 0x25.7 CB EN must be set to 1 to enable manual cell balancing and bit 0x25.6 Auto CB EN must be set to 0 to disable automatic cell balancing.

Figure 10. Manual Cell Balancing Sequence

The master must determine the cells to be balanced and write the bits in registers 0x26-27 CB Cell State. A 1 is written to cell locations selected for charge reduction, and a 0 is written to cell locations that receive the full charge current.

Bit 0x25.2 CB Mask controls whether all cells that need balancing are turned on simultaneously or in separate ON cycles.

The master should put the RAA489206 in SCAN mode by setting bits 0x2E.7:6 System Mode to 01 before triggering a cycle of manual cell balancing.

Important: Write all relevant settings to the RAA489206 before cell balancing is triggered (0x25.4 CB Trigger).

#### 3.2.1 Sequence Description

CB Trigger – With the RAA489206 in SCAN mode (0x01.1 Scan Select must be set to 1 for single scan), the

master must set the bits in registers 0x26-27 CB Cell State to 1 for cells that have charged to relatively higher

voltages than the rest of the pack. Bits for the other cells are set to 0 so they receive the full charge current. For

manual cell balancing, the criteria used to determine which cells to get the reduced charge current is

determined by the user.

When ready, the master triggers Cell Balancing by writing a 1 to 0x25.4 CB Trigger.

- CB EN? - If bit 0x25.7 CB EN is not set to 1, the CB sequence exits, otherwise it moves to the next step.

- Any Cells Selected in 0x26-27? The master must determine the cells to be balanced and write the bits in registers 0x26-27 CB Cell State before the CB Trigger. If no cell is selected the cell balance sequence exits.

- Note: With Auto CB EN set to 0 for Manual Cell Balancing the NEED CB bit has no function.

- Turn On Odd Mask CB The cell balance FETs for the odd numbered cells that were manually determined to require balancing as indicated by the CB Cell State registers 0x26-27 are turned on.

- CB Mask If the bit 0x25.2 CB Mask is clear (0), the CB sequence moves to the Turn On Even Mask CB step, otherwise the CBON Timer is activated per the next step.

- CBON Timer The Timer setting 0x28 CBON determines how long the cell balance FETs are enabled for each balancing cycle. The sequence moves to the next step after the CBON Timer times out.

- Turn Off Odd Mask CB Cell balance FETs for the odd cells are turned off.

- Turn On Even Mask CB The cell balance FETs for the even numbered cells that were manually determined to require balancing as indicated by the registers 0x26-27 CB Cell State are turned on.

- CBON Timer The timer setting 0x28 CBON determines how long the cell balance FETs are enabled for each balancing cycle. The sequence moves to the next step after the CBON Timer times out.

- Turn Off CB Cell balance FETs are turned off.

- CBOFF Timer The timer setting 0x29 CBOFF determines how long the cell balance FETs are disabled for each balancing cycle. The sequence moves to the next step after the CBOFF Timer times out.

- End The CB state machine exits after the CBOFF Timer times out.

### 4. Sample Code

Refer to the *Application Note R16AN0015: MCU Sample Code for Driving the RAA489206 16-Cell Battery Front End* and its accompanying code for detailed information about the Command Line Interface (CLI) that provides commands to set and use the cell balancing features of the RAA489206 BFE.

### 5. Conclusion

Cell balancing is an essential process in battery management systems as it ensures that all cells in a battery pack reach 100% capacity at full charge, resulting in optimal performance and helping to prolong the life of the battery pack. This application note reviews the basics of cell balancing and the causes of imbalance, which should be considered to decide when to perform cell balancing in a battery pack. In addition, this application note provides detailed information about the cell balancing functionalities featured in the RAA489206 and shows how to use them to monitor and balance the cell voltages of a battery pack to achieve the balanced state.

### 6. Revision History

| Revision | Date         | Description      |

|----------|--------------|------------------|

| 1.00     | Feb 21, 2023 | Initial release. |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use o any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners. **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <u>www.renesas.com/contact/</u>