# 82P338XX/9XX

### Introduction

The IDT82P338XX/9XX **S**ynchronization **M**anagement **U**nit (SMU) for IEEE 1588 and Synchronous Ethernet (SyncE) provides tools to manage timing references. It has several different modes to align the output clocks, to control the skew, clock sources and timing paths for IEEE 1588 / Precision Time Protocol (PTP) and Synchronous Ethernet (SyncE) based clocks.

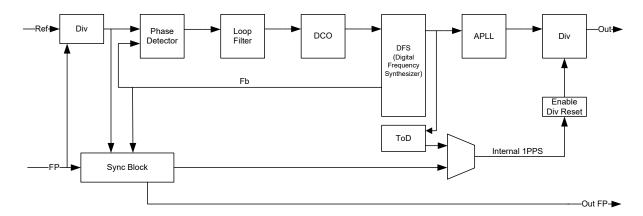

### Figure 1: 82P338XX/9XX Block Diagram

### Procedure to program clock phase skew

The 82P338XX/9XX enables the capability to manage phase skew of a physical clock at it's inputs, outputs and/or input-to-output. This application note describes the procedure to program the 82P338XX/9XX skews from its power-up default state; and it describes how to dynamically adjust skews needed for certain applications, such as 'snapping' a 1PPS clock representing a 1588 PTP clock. It also presents the measured skew offsets of 82P338XX/9XX for a typical configuration example.

# Overview of clock skew capabilty

### **Per-Input skew control**

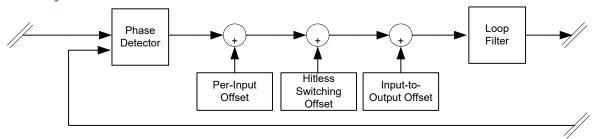

Figure 2: 82P338XX/9XX Input Clock & System Skew Block Diagram

# RENESAS

Each input provides a means to apply an independent phase skew offset to the reference clock. This skew is applied when the reference input is selected by the DPLL, after the phase detector. The value is a signed 7-bit digital value with units of 0.61ns, providing a range from [+77.5 ns,-78.1ns] of skew control.

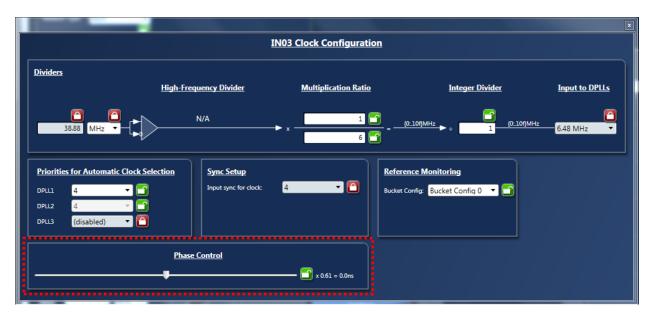

### Figure 3: 82P33831 Timing Commander Input Clock Skew Settings

Since this offset is applied after the phase detector, any changes to the skew will be filter and phase limited by the DPLL.

### Input-to-output skew control

Each DPLL provides a means to apply a system level phase skew offset to the clock. This skew is applied at the phase detector, and represents a phase offset of the feedback clock (internal or external) from the selected input reference clock. The value is a signed 28-bit digital value with units of 0.0745ps, providing a range from [+20µs,-20µs] of skew control.

| DPLL1 Configur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ation                                                                     | Quick Profile: G.8262 Option 1                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating Mode         Automatic <ul> <li>Information (24,704 MHz; SONET)</li> <li>Input:</li> <li>GPS (40,000 MHz; SONET)</li> <li>GPS (40,000 Mz; SONET)</li> <li>GPS (40,000 Mz; SONET)</li> <li>GPS (40,000 Mz; SONET)</li></ul> | Sync Setup<br>Sync Frequency: 8kHz<br>Auto Ex Sync: Enabled if DPLL locks | Phase Control<br>Phase Limit: 7.5 µs/s ▼<br>☐<br>Input-to-Output Phase Offset Enabled<br>Offset: 0 ☐ x.0745ps = 0ps                                                                                                                                                                                                                                              |

| Bandwidth and Damping<br>Auto-Selection: Always use locked bw/damping<br>Locked Damping: ≤ 0.15 dB ▼                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Locked Bandwidth: 1.1 Hz                                                  | Holdover Configuration<br>Manual Holdover<br>Auto Average? Use Averaged Value<br>History Mode: current averaged value<br>Average Mode: 1.5 mHz<br>Temp Holdover: Use instantaneous value<br>Temp Holdover: Use instantaneous value<br>Temp Holdover: Use instantaneous value<br>Temp Holdover: Use instantaneous value<br>Temp Holdover: Use instantaneous value |

| Combo mode setup Combo mode: Normal DPLL mod Pass to DPLL2 when in combo mode: phase + frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | le 🔹 🔽 😭<br>y offset (same as DCO input value) 🔹 📑                        | Master/Slave Mode Configuration<br>Expected role: Master  Input clock for DPLL ref: IN03                                                                                                                                                                                                                                                                         |

### Figure 4: 82P33831 Timing Commander Input-to-Output Clock Skew Settings

Since this offset is applied after the phase detector, any changes to the skew will be filter and phase limited by the DPLL.

This 28-bit register is also used to apply the phase offset value when operating in Write Phase DCO mode.

### **Per-Output skew control**

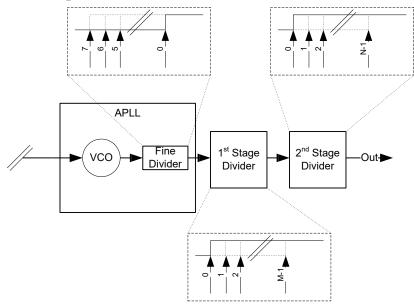

### Figure 5: 82P338XX/9XX Output Clock Skew Block Diagram

Each output (OUT01~08<sup>1</sup>) provides a means to apply an independent phase skew offset of the synthesized clock. This skew represents a phase offset from the DPLL, which means any changes to the skew will cause a 'snap' of the output clock edge. There are three (3) adjustments available: up to two coarse adjustments in the positive direction, and one fine adjustment (APLL synthesized clock only) in the negative direction; which provides +/-180° of skew control.

The output skew adjustment is analogue based, providing very precise adjustments that are based on the APLL VCO or DFS engine clock edges.

<sup>&</sup>lt;sup>1</sup> OUT08 for 82P33x10/x14, OUT07 for 82P33x31

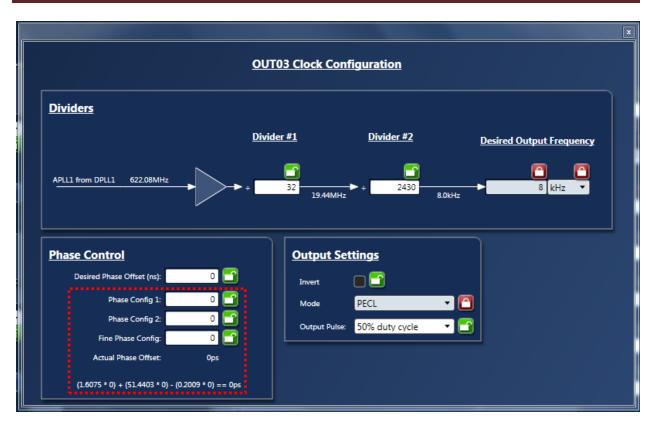

### Figure 6: 82P33831 Timing Commander Output Clock Skew Settings

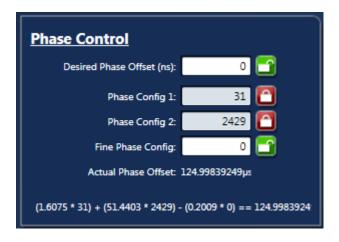

The first coarse value is a 5-bit value with units determined by either the APLL VCO frequency or the clock frequency from the DFS engine. For the example above using an APLL with VCO=622.08MHz, the unit would be 1/622.08M=1.6075ns. The max value that can be programmed is determined by the first stage divider value (M) minus 1. For the example above, the maximum value would be 31 for up to +49.8328ns of skew adjustment.

The second coarse value is a 27-bit value with units determined by the clock frequency from the first stage divider. For the example above using a /32 on the APLL clock (19.44MHz), the unit would be 1/19.44M= 51.4403ns. The max value that can be programmed is determined by the second stage divider value (N) minus 1. For the example above, the maximum value would be 2429 for up to + 124.9486µs of skew adjustment.

The total range with the two coarse adjustments would be [0,+124.9984] µs.

Figure 7: Output Clock Coarse Skew Setting Example

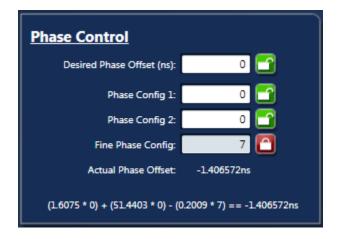

The fine value is a 3-bit value with units determined by the APLL VCO frequency \* 8. Only a clock from the APLL has a fine skew adjustment. For the example above using an APLL with VCO=622.08MHz, the unit would be 1/(622.08M\*8)= 200.9ps. The max value is 7 for a range of [0, -1.4066]ns of skew adjustment.

Figure 8: Output Clock Fine Skew Setting Example

### **Power-up Default State**

Upon power-up, if there is no external EEPROM available, then the 82P338XX/9XX loads its register configurations from the metal defaults. With the qualification and locking to any input reference clock, the 82P338XX/9XX will exhibit typical delays as shown in Table 1.

|                               | Min                                                                                                                          | Max                      | Range                |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------|

| Output                        | (ns)                                                                                                                         | (ns)                     | (ns <sub>pp</sub> )  |

|                               |                                                                                                                              |                          | 9                    |

| Any Input to Any APLL Output  | 10                                                                                                                           | 19                       | (+/-4.5 around mean) |

| Any input to [M]FRSYNC Output | 0                                                                                                                            | 8                        | 8                    |

|                               | 1. The measurements in the above table takes into account any delays in the clock path from any input to any output; through |                          |                      |

|                               | either DPLL1 or DPLL2 and either APLL1 or APLL2.                                                                             |                          |                      |

|                               | 2. The measurements in the above table are over operational                                                                  |                          |                      |

|                               |                                                                                                                              | g power supply and rep   | peated power on/off  |

|                               | cycle.                                                                                                                       |                          |                      |

|                               |                                                                                                                              | e taken using an ideal F | -                    |

| NOTES                         | System clock to accou                                                                                                        | unt for only internal de | elays in the device. |

### Table 1: Input-to-Output Delay for 82P338XX/9XX with Power-Up Default Configuration

Looking at a specific output clock, the 82P338XX/9XX will exhibit typical delays as shown in Table 2.

|                                 | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Max      | Range                |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------|

| Output                          | (ns)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (ns)     | (ns <sub>pp</sub> )  |

| Any LVCMOS Input to any of      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | 6                    |

| OUT01, OUT02, OUT07, OUT08*     | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19       | (+/-3 around mean)   |

| Any LVPECL/LVDS Input to any of |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | 5                    |

| OUT03, OUT04, OUT05, OUT06      | 11.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16.5     | (+/-2.5 around mean) |

|                                 | <ol> <li>The measurements in the above table takes into account any<br/>delays in the clock path from any input to any output; through<br/>either DPLL1 or DPLL2 and either APLL1 or APLL2.</li> <li>The measurements in the above table are over operational<br/>temperature, varying power supply and repeated power on/off<br/>cycle.</li> <li>Measurements are taken using an ideal REF input and an ideal<br/>System clock to account for only internal delays in the device.</li> </ol> |          |                      |

| NOTES                           | * OUT08 for 82P33x10/x13/                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | x14 only |                      |

#### Table 2: Input-to-Output Delay for 82P338XX/9XX

For the associated output clock pair, the 82P338XX/9XX will exhibit delays as shown in Table 3.

|                                   | Min  | Max  |

|-----------------------------------|------|------|

| Output                            | (ps) | (ps) |

| Output to Output, APLL LVCMOS     |      |      |

| (OUT01 to OUT02, OUT07 to OUT08*) | -110 | 110  |

| Output to Output, LVPECL/LVDS     |      |      |

| (OUT03 to OUT04, OUT05 to OUT06)  | -85  | 85   |

### Table 3: Output-to-Output Delay for 82P338XX/9XX

IDT Confidential Information

### Programming Output Skew for SETS Application

For SETS applications, the input to output delay is typically not a factor as measurements are taken at the TO output. However, a general rule is to try maintain a less than 10ns variation on the output in relationship to the input reference clock (excluding LPF response).

For this reason, Table 1 can be used to determine an initial skew offset by taking the Minimum number and writing an applicable coarse phase offset value. In this case, a value of 10ns would be used.

## Programming Output Skew for T-GM(-P) Application

For T-GM(-P) applications, the input to output delay is critical to minimize any additional Time Error on the synthesized clocks in relationship to the PRTC. In this case, Table 2 should be used to determine an initial skew offset by taking the mean value and writing an applicable coarse & fine phase offset value. For example, if a 1PPS pulse is configured for OUT01 (LVCMOS), then a value of 16ns would be used. If a 125MHz clock is configured for OUT03 (LVPECL), then a value of 14ns would be used.

One note is if [M]FRSYNC is being used to represent the frame or sync pulse, in this case you may want to use the minimum value to make sure that the output clock never leads the [M]FRSYNC pulse.

# Programming Output Skew for DCO (1588) Application

For DCO applications, the input to output delay is not applicable, as the "phase detector" is now at the timestamper; meaning that the synthesized clock from the 82P338XX/9XX now represents the "feedback" clock. However, when representing the PTP clock with a 1PPS output, there will be a need to snap the edge of the 1PPS clock to represent the nanosecond rollover (since pulling in +/-500ms via DCO would take too long).

For example, at start-up, all the clocks will be arbitrarily aligned to the internal 1PPS clock. This means that the 1PPS output may be up to +/-500ms off from the GM reference clock. To snap this phase, the output divider control may be used once the DCO has been syntonized to the GM clock (i.e. frequency locked).

For example, if a 1PPS pulse is to be moved by +125ms, then the following coarse & fine offsets can be used.

| OUT02 Clock Configuration                                |                                                |  |  |  |

|----------------------------------------------------------|------------------------------------------------|--|--|--|

| Dividers                                                 |                                                |  |  |  |

|                                                          |                                                |  |  |  |

|                                                          | Divider #1 Divider #2 Desired Output Frequency |  |  |  |

|                                                          |                                                |  |  |  |

| APLL1 from DPLL1 622.08MHz                               | > ÷ 32 → ÷ 19440000 → 1 Hz ▼                   |  |  |  |

|                                                          | 19.44MHz 1.0PPS                                |  |  |  |

|                                                          |                                                |  |  |  |

| Phase Control                                            | Output Settings                                |  |  |  |

| Desired Phase Offset (ns): 125000000                     |                                                |  |  |  |

| Phase Config 1: 1                                        | Output Pulse: 1.028806µs (20T)                 |  |  |  |

| Phase Config 2: 2430000                                  |                                                |  |  |  |

| Fine Phase Config: 7                                     |                                                |  |  |  |

| Actual Phase Offset: 125.0000002005                      |                                                |  |  |  |

| (1.6075 * 1) + (51.4403 * 2430000) - (0.2009 * 7) == 125 | 25.00000                                       |  |  |  |

|                                                          |                                                |  |  |  |

### Figure 9: 1PPS Output Clock Snap Example

For questions related to device configurations, please contact IDT application support at <u>support-sync@idt.com</u>.

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.