# Application note Suspend and Resume AN-PM-007

## **Abstract**

This document describes how to achieve suspend and resume behaviour with Dialog DA9052, DA9053, DA9021 and DA9022 PMIC devices.

# **Contents**

| Ab   | ostract                                                                          | 1  |

|------|----------------------------------------------------------------------------------|----|

| Co   | ontents                                                                          | 2  |

| Fiç  | gures                                                                            | 2  |

| 1    | Terms and definitions                                                            | 3  |

| 2    | References                                                                       | 3  |

| 3    | Introduction                                                                     | 4  |

| 4    | Definition of SUSPEND                                                            | 4  |

| 5    | Preparation for SUSPEND                                                          | 4  |

| 6    | The SUSPEND RESUME sequence                                                      | 5  |

|      | 6.1 Configure the PMIC for SUSPEND                                               |    |

|      | 6.2 SUSPEND                                                                      |    |

|      | 6.3 RESUME                                                                       |    |

| 7    | System Power Off                                                                 | 9  |

| Αp   | pendix A Power Commander script                                                  | 10 |

| Re   | evision history                                                                  | 11 |

|      |                                                                                  |    |

|      |                                                                                  |    |

| Fi   | igures                                                                           |    |

| Fic  | gure 1: Normal start-up                                                          | 5  |

| Fig  | gure 2: SUSPEND triggered by SW SYS_EN                                           | 6  |

|      | gure 3: SUSPEND triggered by hardware SYS_EN low                                 |    |

|      | gure 4: RESUME triggered by nONKEY                                               |    |

|      | gure 5: Expanded view of RESUME triggered by nONKEY                              |    |

|      | gure 6: Resume triggered by rising SYS_EN<br>gure 7: Resume triggered by charger |    |

|      | gure 8: RESUME triggered by RTC Alarm                                            |    |

|      | gure 9: RESUME Triggered by GPIO4 rising edge                                    |    |

| ٠. ١ | jaio 0. 11200112 111990100 by 01 104 1101119 0090                                | 0  |

## 1 Terms and definitions

DA905x For this document this will be used to represent DA9021, DA9022, DA9052,

DA9053 and DA9057

OTP One Time Programmable: The type of memory used to store the configuration of

the PMIC

PMIC Power Management Integrated Circuit

## 2 References

[1] Power Commander User Guide, Dialog Semiconductor

© 2016 Dialog Semiconductor

## **Suspend and Resume**

#### 3 Introduction

In many applications the system is required to enter a low power suspend or standby state, where at least some of the system configuration is maintained to allow the system to wake quickly and resume normal activity. This application note describes how this can be achieved with most members of the DA905x family. This note assumes that the system has already been configured so that it can achieve the normal active state. For the examples in this document, a DA9053 was used with the OTP programmed with the Dialog 3F configuration. For this document, the low power state will be referred to as Suspend.

## 4 Definition of SUSPEND

SUSPEND is a low power state that differs from POWERDOWN or OFF state in that a minimum number of supply rails are left on to allow the system to maintain a level of configuration so that normal operation can be resumed without the requirement to follow the normal boot sequence.

# 5 Preparation for SUSPEND

There is some basic information that is required to prepare the system to enter the SUSPEND state.

- 1. How will the system enter the SUSPEND state? Is it a hardware signal or an I<sup>2</sup>C/SPI command? There are two possible triggers for the PMIC to enter the SUSPEND state. The first is a register write to the SYS\_EN bit of the CONTROL\_A register (bit 0 of address 0x0E). Clearing the SYS\_EN bit causes the sequencer to step down from its current state to the POWERDOWN state. The alternative to the register write is to configure GPIO8 as a hardware SYS\_EN. A transition on this hardware signal then triggers the sequencer.

- 2. What retention voltages are required to maintain the required system information/configuration? For this example it is assumed that the required regulators to be left on are:

BUCKCORE 0.85 V

BUCKPRO 0.95 V

LDO7 1.2 V

LDO10 1.2 V

The nRESET signal should not trigger a reset of the processor during SUSPEND. Set NRES\_MODE,,bit 0 of the ID\_0\_1 Register (R29) to '0' to prevent the assertion of NRESET in SUSPEND.

3. What will trigger the system to Resume?

There are multiple options to wake up the system from the SUSPEND state:

- o nONKEY

- The hardware signal SYS\_EN

- A valid charger

- o An RTC alarm

- An alternative signal, such as a GPIO

Each of these events can be generated on the DA905x. The descriptions below show how each one can be implemented.

4. The SYS\_PRE control, Bit 2 of the ID\_0\_1 register (R29), can be used to change the behaviour of the SYS\_UP signal during SUSPEND. For correct SUSPEND functionality, Dialog recommend that SYS\_PRE is set to '1' so that the SYS\_UP signal will go low during SUSPEND.

# 6 The SUSPEND RESUME sequence

This section describes the sequence of actions and events during one suspend resume cycle. The system is assumed to be booted up in the ACTIVE state.

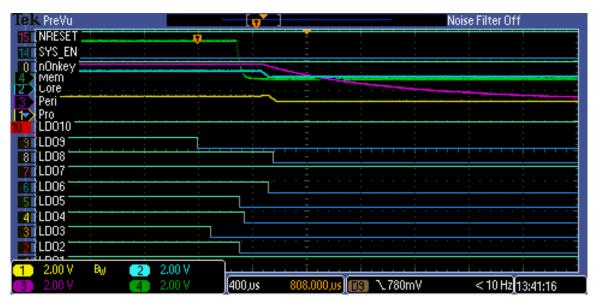

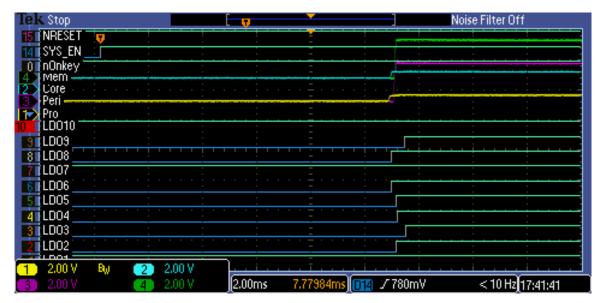

Figure 1: Normal start-up

Note that in Figure 1 nRESET goes high just after the period captured. Also note that the LDOs were connected to digital channels on the oscilloscope. The plot therefore indicates whether the LDO is on or off, but not the actual LDO voltage level.

#### 6.1 Configure the PMIC for SUSPEND

| Set NRES_MODE to '0' in R29  | // nRESET must not be asserted during SUSPEND                                                      |

|------------------------------|----------------------------------------------------------------------------------------------------|

| Set DEF_SUPPLY to '0' in R29 | // This must be cleared to allow the pre-set voltage mode to function                              |

| Set SEQ_TIMER (R43) to 0x00  | $\ensuremath{/\!/}$ This sets the sequence time to minimum, for a fast in and fast out of SUSPEND. |

| Set R46 to 0x8E              | // Set the CONF bit and the pre-set voltage of BUCKCORE to 0.85 $\ensuremath{\text{V}}$            |

| Set R47 to 0xD2              | // Set the CONF bit and the pre-set voltage of BUCKPRO to 0.95 $\ensuremath{\text{V}}$             |

| Set R56 to 0xC0              | // Set the CONF bit and the pre-set voltage of LDO_7 to 1.2 V                                      |

| Set R59 to 0xC0              | // Set the CONF bit and the pre-set voltage of LDO_10 to 1.2 V                                     |

The NRES\_MODE bit (bit 0 of R29) defines whether the nRESET signal is asserted when the PMIC enters the POWERDOWN state with regulators left enabled via the CONF bits. With NRES\_MODE set to '0', nRESET is not asserted. With NRES\_MODE set to '1', nRESET is asserted when powering down.

The CONF bit, which is the MSB of each of the LDO and buck registers, sets the regulator into preconfigure mode. With the CONF bit set, the voltage can then be configured without immediately changing the voltage of the regulator. The new voltage is applied when the sequence pointer next reaches the active slot for that particular regulator. For the CONF bits to function correctly, DEF\_SUPPLY (bit 1 of R29) must be set to '0'.

#### 6.2 SUSPEND

Clear the SYS\_EN bit in the CONTROL\_A register to go to the SUSPEND state.

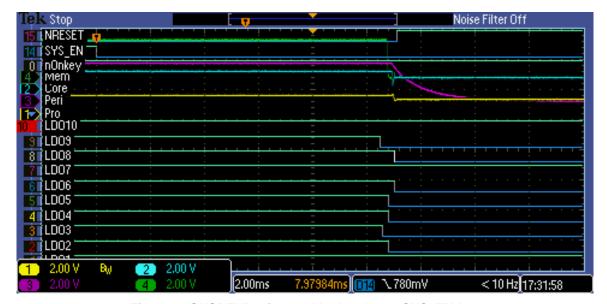

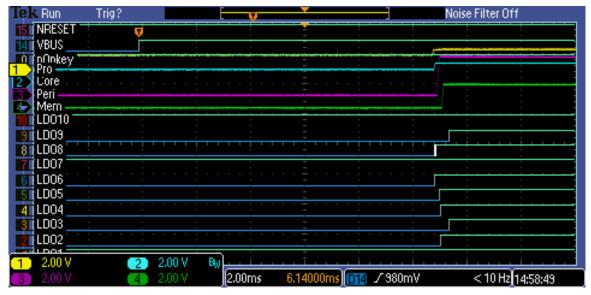

Figure 2: SUSPEND triggered by SW SYS\_EN

BUCKCORE and BUCKPRO can be seen to change their voltage but remain active, as do LDOs 1, 7 and 10. All other supplies are disabled.

Figure 3: SUSPEND triggered by hardware SYS\_EN low

To permit the hardware SYS\_EN signal to trigger the SUSPEND state, GPIO8 must be configured to be hardware SYS\_EN. SYS\_EN can be configured as active high or low. The GPIO is configured via R25.

#### 6.3 RESUME

When the RESUME event occurs, the supplies revert to their OTP programmed values. For this to happen correctly, the OTPREAD\_EN (bit 3) of register CONTROL\_B (R15) must be set. This bit triggers a partial OTP read on leaving the POWERDOWN state of the sequencer. The partial OTP read will read the buck and LDO registers to reset the regulator voltages to the original OTP programmed values. The CONTROL\_A register is also read during this partial read: this can be used to reconfigure the SYS\_EN bit to allow the sequencer to continue.

The figures below show the RESUME triggered by the various options.

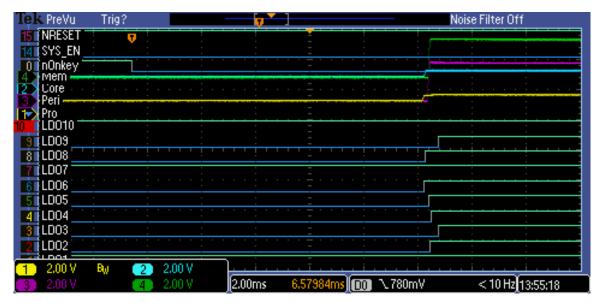

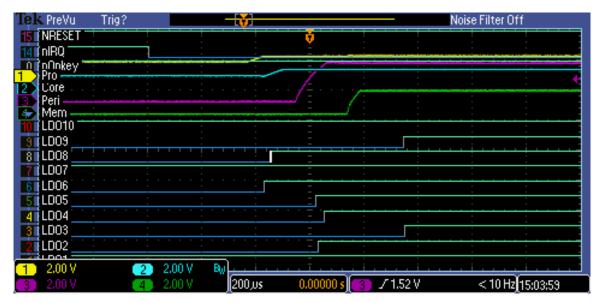

Figure 4: RESUME triggered by nONKEY

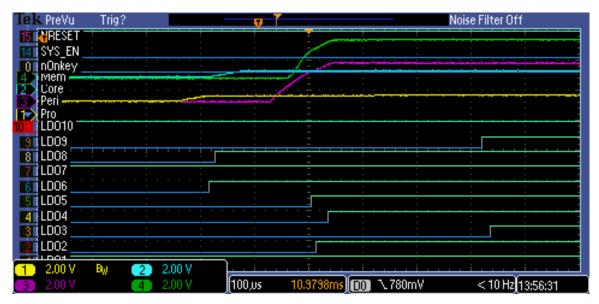

Figure 5: Expanded view of RESUME triggered by nONKEY

Figure 5 illustrates only slight increases in voltage on BUCKPRO (yellow trace) and BUCKCORE (blue trace), rising from 0.95 V and 0.85 V, respectively; BUCKMEM (green trace) and BUCKPERI (magenta trace) resume from the OFF state.

Figure 6: RESUME triggered by rising SYS\_EN

To permit the hardware SYS\_EN pin to trigger a resume, R25 should be configured with GPIO8 set as hardware SYS\_EN and debounce enabled.

The value for the lower four bits of GPIO\_8-9 (R25) should be 0xC for an active high SYS\_EN and 0x8 for an active low SYS\_EN.

Figure 7: RESUME triggered by charger

The wake-up may be triggered by a valid charger detection on either VBUS or DCIN. In Figure 7 the charger is connected to VBUS and it is shown that the resume sequence starts 10 ms after the charger is detected. The 10 ms delay is due to the debounce on the charger detect.

Figure 8: RESUME triggered by RTC Alarm

Figure 8 shows the RESUME triggered by an alarm from the RTC. In this case the trigger event is seen as the interrupt (nIRQ). The RTC wakeup can either be the RTC alarm or the RTC tick function.

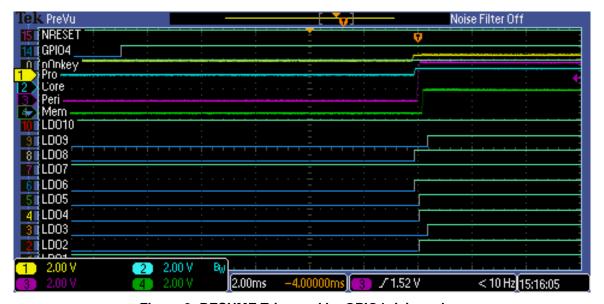

Figure 9: RESUME Triggered by GPIO4 rising edge.

Figure 9 shows the RESUME triggered by a rising edge on GPIO4. To use a GPIO, it must be programmed as a GPI and debounce must be enabled to trigger the wake-up.

# 7 System Power Off

While SUSPEND and RESUME are used to reduce power consumption during the normal operation of the system, the system will at some time be powered off.

When a system is using SUSPEND and RESUME, it is important that NRES\_MODE (bit 0 of R29) is set back to '1' before the system is shutdown. This ensures nRESET is correctly asserted when the device is fully powered down. This can safely be performed as part of the system shutdown procedure.

# **Appendix A Power Commander script**

While performing the above tests, a simple Power Commander script was used to configure the part.

To use the script, cut and paste the text below into a text file and save into the data directory under the Power Commander installation.

The script can then be executed using the 'File Operations' option in the Power Commander GUI. See the Power Commander User Guide for further information on using scripts.

//Configure the PMIC for SUSPEND using hardware SYS EN

| PMIC | 0x1D | 0x00 |

|------|------|------|

| PMIC | 0x2B | 0x00 |

| PMIC | 0x2E | 0xCE |

| PMIC | 0x2F | 0xD2 |

| PMIC | 0x38 | 0xC0 |

| PMIC | 0x3B | 0xC0 |

| PMIC | 0x19 | 0x7C |

|      |      |      |

# **Revision history**

| Revision | Date        | Description                                            |

|----------|-------------|--------------------------------------------------------|

| 1.0      | 22-Mar-2012 | Initial version.                                       |

| 1.1      | 02-Jun-2015 | Updated to use new template.                           |

| 1.2      | 10-Jul-2015 | Minor corrections following review.                    |

| 1.3      | 26-Jan-2016 | Expanded DA905x to list of relevant parts in abstract. |

|          |             |                                                        |

#### **Status definitions**

| Status               | Definition                                                                                                                   |

|----------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED or unmarked | The content of this document has been approved for publication.                                                              |

#### **Disclaimer**

Information in this document is believed to be accurate and reliable. However, Dialog Semiconductor does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information. Dialog Semiconductor furthermore takes no responsibility whatsoever for the content in this document if provided by any information source outside of Dialog Semiconductor.

Dialog Semiconductor reserves the right to change without notice the information published in this document, including without limitation the specification and the design of the related semiconductor products, software and applications.

Applications, software, and semiconductor products described in this document are for illustrative purposes only. Dialog Semiconductor makes no representation or warranty that such applications, software and semiconductor products will be suitable for the specified use without further testing or modification. Unless otherwise agreed in writing, such testing or modification is the sole responsibility of the customer and Dialog Semiconductor excludes all liability in this respect.

Customer notes that nothing in this document may be construed as a license for customer to use the Dialog Semiconductor products, software and applications referred to in this document. Such license must be separately sought by customer with Dialog Semiconductor.

All use of Dialog Semiconductor products, software and applications referred to in this document are subject to Dialog Semiconductor's Standard Terms and Conditions of Sale, unless otherwise stated.

© Dialog Semiconductor. All rights reserved.

#### **RoHS Compliance**

Dialog Semiconductor complies to European Directive 2001/95/EC and from 2 January 2013 onwards to European Directive 2011/65/EU concerning Restriction of Hazardous Substances (RoHS/RoHS2). Dialog Semiconductor's statement on RoHS can be found on the customer portal https://support.diasemi.com/. RoHS certificates from our suppliers are available on request.

# **Contacting Dialog Semiconductor**

United Kingdom (Headquarters)

Dialog Semiconductor (UK) LTD Dialog Semiconductor Inc. Phone: +44 1793 757700

Germany

Dialog Semiconductor GmbH Phone: +49 7021 805-0

The Netherlands

Dialog Semiconductor B.V. Phone: +31 73 640 8822

enquiry@diasemi.com

North America

Phone: +1 408 845 8500

Japan

Dialog Semiconductor K. K. Phone: +81 3 5425 4567

Dialog Semiconductor Taiwan Phone: +886 281 786 222

Web site:

www.dialog-semiconductor.com

China (Shenzhen)

Dialog Semiconductor China Phone: +86 755 2981 3669

China (Shanghai)

Dialog Semiconductor China Phone: +86 21 5424 9058

**Application note Revision 1.3** 13-Jan-2016

Dialog Semiconductor Singapore

Dialog Semiconductor Hong Kong

Phone: +65 64 8499 29

Phone: +852 3769 5200

Phone: +82 2 3469 8200

Dialog Semiconductor Korea

Hong Kong

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.