# **Application Note**DA9062 / Atlas7 Power Connections

**AN-PM-083**

# **Abstract**

This document outlines the connectivity between the Dialog DA9062 Power Management Integrated Circuit (PMIC) and Qualcomm® Atlas7™ system processor.

# **Contents**

| Αk  | strac           | rt                                                              | 1  |  |

|-----|-----------------|-----------------------------------------------------------------|----|--|

| Cc  | ntent           | ts                                                              | 2  |  |

| Fi  | gures           |                                                                 | 2  |  |

| Та  | bles .          |                                                                 | 2  |  |

| 1   | Tern            | ns and Definitions                                              | 3  |  |

| 2   | Refe            | erences                                                         | 3  |  |

| 3   | Intro           | oduction                                                        | 4  |  |

| 4   | Timing Diagrams |                                                                 |    |  |

| -   | 4.1             | Cold Boot                                                       |    |  |

|     | 4.2             | Power-Down / Suspend by Atlas7                                  |    |  |

|     | 4.3             | Warm Boot                                                       |    |  |

|     | 4.4             | Watchdog Timeout                                                | 9  |  |

|     | 4.5             | Temperature Warning and Temperature Error                       | 10 |  |

|     | 4.6             | System Supply Under-Voltage                                     | 11 |  |

| 5   | Soft            | ware Driver                                                     | 12 |  |

| 6   | Dev             | elopment Support Tools and PMIC Configuration Files             | 12 |  |

| Re  | visio           | n History                                                       | 13 |  |

|     |                 |                                                                 |    |  |

|     |                 |                                                                 |    |  |

| E   | gur             |                                                                 |    |  |

|     |                 |                                                                 |    |  |

| •   | ,               | : Qualcomm Atlas7 Platform                                      |    |  |

|     |                 | B: Timing Diagram for Power Down by Atlas7                      |    |  |

| Fίζ | jure 4          | : Timing Diagram for Warm Boot                                  | 8  |  |

|     |                 | : Timing Diagram for a Watchdog Timeout                         |    |  |

|     |                 | 5: Timing Diagram for Temperature Warning and Temperature Error |    |  |

| ΓI  | gure 7          | : Timing Diagram for System Supply Under-Voltage                | 11 |  |

| Ta  | able            | es                                                              |    |  |

| Ta  | ble 1·          | GPIO Mapping for Atlas7                                         | F  |  |

© 2022 Renesas Electronics

# 1 Terms and Definitions

GUI Graphical User Interface

Atlas7 Qualcomm CSRatlas7™ SoC, formerly known as SiRFatlas7™

SoC System on a Chip

PMIC Power Management Integrated Circuit

PWRC Power Controller

# 2 References

- [1] DA9062, Datasheet, Dialog Semiconductor

- [2] SiRFatlas7, http://www.csr.com/tw/node/6376i [Accessed 01-Nov-2016]

- [3] The Linux Kernel Archives, https://kernel.org/ [Accessed 13-Sep-2016]

## 3 Introduction

This document provides details of integrating the DA9062 with the CSRatlas7 ('Atlas7') SoC [2], suitable for highly-integrated display audio solutions.

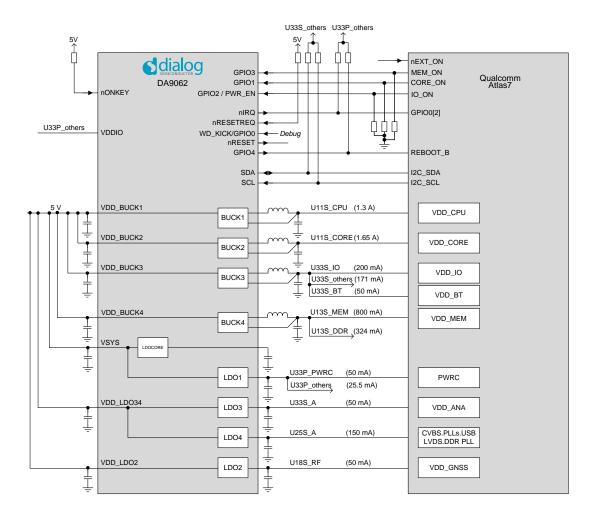

Figure 1: Qualcomm Atlas7 Platform

- Note 1 The WD\_KICK/GPIO0 input requires a pulse every 2 s (as set by register control TWDSCALE).

Alternatively, by setting register control WDG\_MODE='1', the input can be permanently asserted using a pull-up to U33S\_others. This may be useful during application debugging.

- Note 2 DA9062 nONKEY is not used. System start-up is initiated by nEXT\_ON.

- Note 3 nRESET is not used.

**Table 1: GPIO Mapping for Atlas7**

| GPIO           | Function | Description                                                                                                                                                                                                                                                             |

|----------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO0          | WD_KICK  | Watchdog kick – for debug                                                                                                                                                                                                                                               |

| GPIO1          | CORE_ON  | Active-high GPI enables Buck1 and Buck2                                                                                                                                                                                                                                 |

| GPIO3          | MEM_ON   | Active-high GPI enables Buck4                                                                                                                                                                                                                                           |

| GPIO4          | REBOOT_B | Reboots processor, including the PWRC block. Active-low. GPIO4 is configured as an open-drain output. (External pull-up used to avoid reliance on 'soft' configuration of PMIC internal pull-up.)                                                                       |

|                |          | On power-up, the signal is driven a steady high. This allows the PWRC to start up. The signal remains high unless there is a watchdog timeout.                                                                                                                          |

|                |          | On a watchdog timeout, the PMIC powers down through the sequence. The sequence is modified by the PMIC itself at the beginning of the power-down so that a high-low-high pulse is created on GPIO4. (The pulse is defined by controls GP_RISE5_STEP and GP_FALL5_STEP). |

| GPIO2 / PWR_EN | IO_ON    | Enables the LDOs and Buck3 via the sequencer. GPIO2 is configured as an active-high input.                                                                                                                                                                              |

The GPIOs configured as outputs can be supplied internally from VDDIO and driven with a push-pull stage, or with an open-drain stage with an optional internal pull-up to VDDIO. Similarly, nIRQ and nRESET can be driven with a push-pull or with an open-drain stage but an external pull-up is required (as shown in Figure 1). The PMIC nRESET line is not used in this application.

# 4 Timing Diagrams

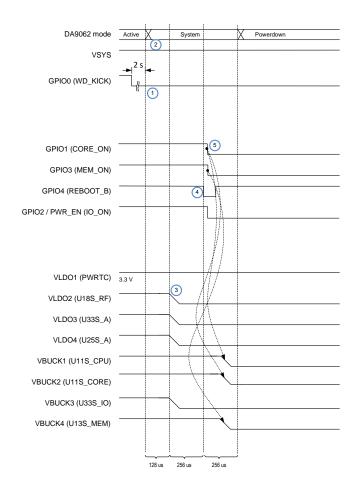

#### 4.1 Cold Boot

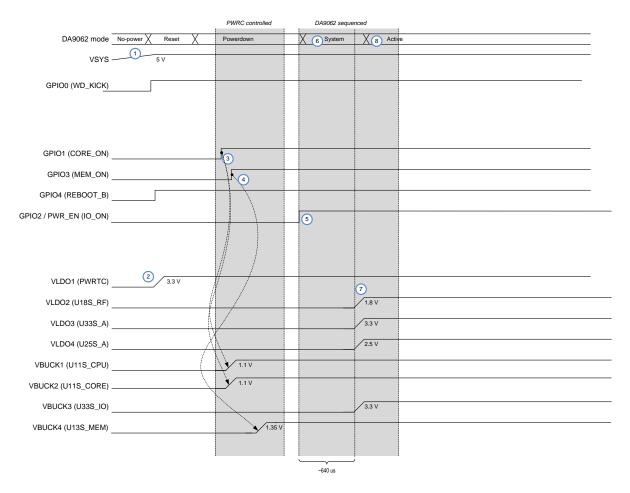

Figure 2: Timing Diagram for Cold Boot

- The system supply rises above a threshold value after which the internal digital core supply of DA9062 is enabled and the device enters RESET mode. It then automatically proceeds to POWERDOWN mode.

- 2. The always-on supply LDO1 (U33P\_PWRC) is enabled while the device is in RESET mode.

- 3. With U33P\_PWRC powered up, the Atlas7 PWRC asserts GPIO1 (CORE\_ON). CORE\_ON directly enables Buck1 (U11S\_CPU) and Buck2 (U11S\_CORE). This is therefore asynchronous to the DA9062 start-up sequence.

- 4. The Atlas7 PWRC asserts GPIO3 (MEM\_ON) which directly enables Buck4 (U13S\_MEM). This is also asynchronous to the DA9062 start-up sequence.

- 5. The Atlas7 PWRC asserts IO\_ON which drives GPIO2 configured as PWR\_EN. The assertion of this signal causes the DA9062 to wake up from POWERDOWN mode.

- 6. The DA9062 executes the power-up sequence. It firstly passes through the SYSTEM state without any changes to the supplies.

- 7. The power-up sequencer continues. The DA9062 turns on LDO2 (U18S\_RF), LDO3 (U33S\_A), LDO4 (U25S\_A) and VBUCK3 (U33S\_IO).

- 8. The sequencer continues and the PMIC reaches ACTIVE mode. The watchdog kick on GPIO0 (WD\_KICK) must be asserted for the PMIC to reach ACTIVE mode.

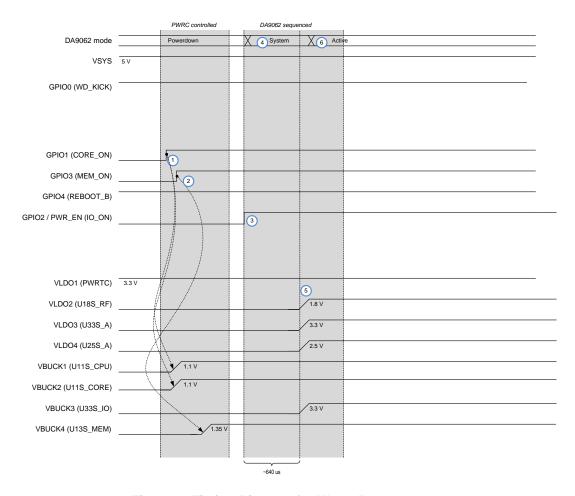

# 4.2 Power-Down / Suspend by Atlas7

Figure 3: Timing Diagram for Power Down by Atlas7

This sequence shows a system power-down controlled by the Atlas7 processor. It is similar to the cold boot sequence reversed, except that it leaves the PMIC in the SYSTEM state.

- 1. Atlas7 initiates the power-down by de-asserting IO\_ON.

- 2. The de-assertion of IO\_ON (PWR\_EN) causes the DA9062 to begin the power-down sequence from the ACTIVE state to the SYSTEM state.

- 3. The sequencer includes the power-down of LDO2 (U18S\_RF), LDO3 (U33S\_A), LDO4 (U25S\_A) and VBUCK3 (U33S\_IO).

- 4. The Atlas7, some time later, may continue to power itself down by de-asserting MEM\_ON.

- 5. The Atlas7, some time later, may continue to power itself down by also de-asserting CORE\_ON.

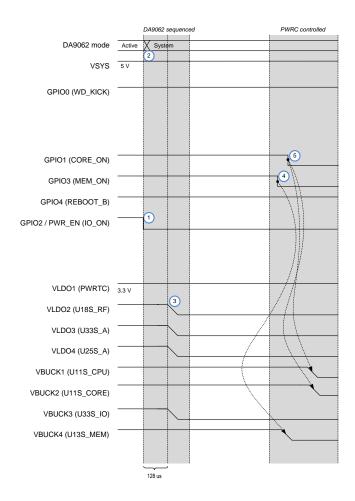

### 4.3 Warm Boot

Figure 4: Timing Diagram for Warm Boot

When the DA9062 is in POWERDOWN mode, the PWRC is on but the Atlas7 core, memory and IOs are powered down. The system therefore requires a warm boot to power up again. The sequence is identical to the later portion of the cold boot sequence.

- 1. With the PMIC in POWERDOWN and the Atlas7 PWRC powered, the PWRC asserts GPIO1 (CORE\_ON). CORE\_ON directly enables Buck1 (U11S\_CPU) and Buck2 (U11S\_CORE). This is therefore asynchronous to the DA9062 start-up sequence.

- 2. The Atlas7 PWRC then asserts GPIO3 (MEM\_ON) which directly enables Buck4 (U13S\_MEM). This is also asynchronous to the DA9062 start-up sequence.

- 3. The Atlas7 PWRC then asserts IO\_ON which drives GPIO2 configured as PWR\_EN. The assertion of this signal causes the DA9062 to wake up from POWERDOWN mode.

- 4. The DA9062 executes the power-up sequence. It firstly passes through its SYSTEM state without any changes to the supplies.

- 5. The power-up sequencer continues. The DA9062 turns on LDO2 (U18S\_RF), LDO3 (U33S\_A), LDO4 (U25S\_A) and VBUCK3 (U33S\_IO).

- 6. The sequencer continues and the PMIC reaches ACTIVE mode. The watchdog kick on GPIO0 (WD\_KICK) must be asserted for the PMIC to reach ACTIVE mode.

# 4.4 Watchdog Timeout

Figure 5: Timing Diagram for a Watchdog Timeout

The watchdog feature is enabled in OTP. The DA9062 requires GPIO0 (WD\_KICK) to be asserted or pulsed in order to enter and maintain ACTIVE mode. If the input is not asserted within 2 s (set by control TWDSCALE), then a timeout has occurred and the system powers down by the following sequence:

- 1. The GPIO0 (WD\_KICK) input remains de-asserted for >2 s. This initiates the watchdog timeout.

- The DA9062 powers down through its sequence, transitioning from the ACTIVE state to the SYSTEM state.

- 3. The DA9062 sequence turns off LDO2 (U18S\_RF), LDO3 (U33S\_A), LDO4 (U25S\_A) and VBUCK3 (U33S\_IO).

- 4. The sequencer leaves the SYSTEM state and continues towards the POWERDOWN state. This part of the power-down sequence includes a low-going pulse on REBOOT\_B. The pulse duration is  $128 \mu s$ .

- 5. The REBOOT\_B assertion immediately causes the Atlas7 PWRC to shut down the remaining rails by de-asserting IO\_ON, MEM\_ON and CORE\_ON. The DA9062 therefore turns off these remaining rails.

The system passes through a reset state controlled by the Atlas7 processor. After completing its reset procedure, the system restarts.

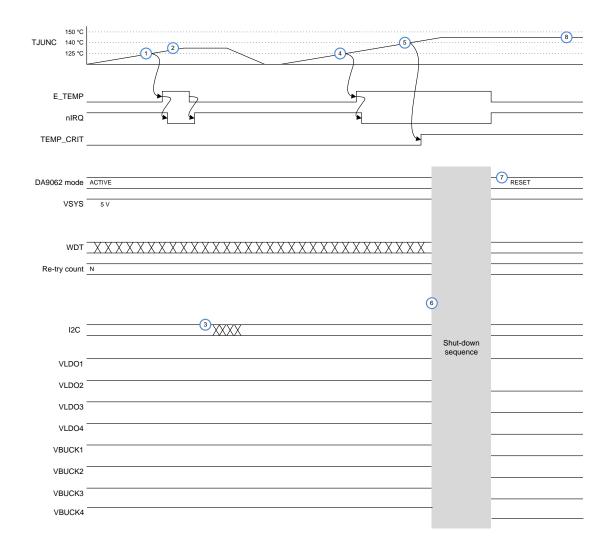

# 4.5 Temperature Warning and Temperature Error

Figure 6: Timing Diagram for Temperature Warning and Temperature Error

- 1. The die temperature exceeds TEMP\_WARN which causes the event E\_TEMP to be asserted. The event, if not masked, asserts nIRQ.

- 2. Atlas7 software sees the temperature warning and reduces the activity of the platform.

- 3. Atlas7 software clears the event E\_TEMP. If no other events are active, this de-asserts nIRQ.

- 4. The die temperature exceeds TEMP\_WARN again which causes the event E\_TEMP to be asserted. The event, if not masked, asserts nIRQ.

- 5. The die temperature exceeds TEMP\_CRIT which causes the temperature error flag TEMP\_CRIT to be asserted, and a shutdown sequence is triggered.

- The DA9062 executes the shutdown sequence which is the same as the power-down sequence

described in Section 4.2, although a shutdown sequence triggered by a temperature error

proceeds directly to the RESET mode.

- 7. The DA9062 completes the shutdown sequence and enters the RESET mode. The retry count is reset, but the temperature error flag is not reset.

- The DA9062 remains in RESET mode as long as the die temperature stays above TEMP\_CRIT.

After this, the power-up sequence is executed in the same way as in the cold boot, as described in Section 4.1.

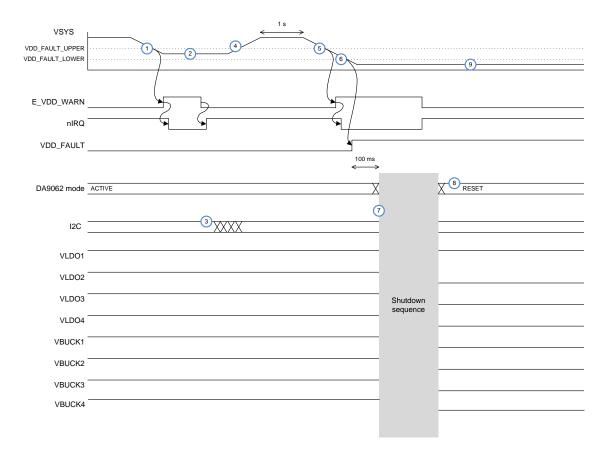

# 4.6 System Supply Under-Voltage

Figure 7: Timing Diagram for System Supply Under-Voltage

- 1. The system supply (VSYS) drops below VDD\_FAULT\_UPPER which causes the event E VDD WARN to be asserted. The event, if not masked, then asserts nIRQ.

- 2. Atlas7 software sees the system supply warning and reduces the activity of the platform. This should reduce the current draw of the platform and stabilize the system supply.

- 3. Atlas7 software clears the event E\_VDD\_WARN. If no other events are active, this de-asserts nIRQ.

- 4. The system supply recovers above the VDD\_FAULT\_UPPER threshold. After this, there is a 1 s debounce period for VSYS. During this period, the system supply comparators are not enabled and, if VSYS drops below VDD\_FAULT\_UPPER, no event is generated.

- 5. The system supply (VSYS) drops below VDD\_FAULT\_UPPER again which causes the event E VDD WARN to be asserted. The event, if not masked, asserts nIRQ.

- 6. The system supply drops below VDD\_FAULT\_LOWER which causes the system supply error flag VDD\_FAULT to be set, and a shutdown sequence is triggered.

- 7. DA9062 executes a shutdown sequence which is the same as the power-down sequence described in Section 4.2, but a shutdown sequence triggered by a voltage error proceeds straight to the RESET mode.

- 8. DA9062 completes the shutdown sequence and enters the RESET mode. The retry count is reset, but the system supply error flag is not.

- DA9062 stays in RESET mode as long as the system supply stays below VDD\_FAULT\_UPPER.

After this, the power-up sequence is executed in the same way as in the cold boot described in Section 4.1.

## 5 Software Driver

After the DA9062 has started the Atlas 7 system, software can read and write to the PMIC via the I<sup>2</sup>C bus. This can be used for further PMIC configuration, such as the GPIOs, interrupt servicing, watchdog 'keep-alive' writes, and so on. Dialog drivers for Linux™ are available in the Linux kernel from https://kernel.org/ [3] or, if interim assistance is required, from your Dialog Sales representative.

# 6 Development Support Tools and PMIC Configuration Files

To assist with hardware and software development, Dialog provides the following:

DA9062 Evaluation Kit

This contains motherboard and daughterboard for hardware evaluation and software development. It also includes the SmartCanvas™ GUI software.

SmartCanvas GUI

This is PC-driven software to provide easy access to a device under test (DUT). The GUI is used to exercise the DUT using the I<sup>2</sup>C interface. Control or measurement of analog and digital pins is supported. SmartCanvas supports the Dialog PMIC OTP configuration file (.ini file) format.

• OTP configuration .ini file DA9062-0A Atlas7 v01 2949.ini

This file defines the configuration of the DA9062 at boot. The file is available from the Dialog Support website. The .ini file is opened using the SmartCanvas GUI.

• Linux software driver. See Section 5.

For further information with development support tools, see the Dialog Support Site <a href="https://support.dialog-semiconductor.com/">https://support.dialog-semiconductor.com/</a>, and website <a href="https://www.dialog-semiconductor.com/">https://www.dialog-semiconductor.com/</a>.

# **Revision History**

| Revision | Date        | Description                                                |

|----------|-------------|------------------------------------------------------------|

| 1.0      | 30-Nov-2016 | Initial release                                            |

| 2.0      | 18-Feb-2022 | File was rebranded with new logo, copyright and disclaimer |

#### **Status Definitions**

| Status               | Definition                                                                                                                   |

|----------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED or unmarked | The content of this document has been approved for publication.                                                              |

## **RoHS Compliance**

Dialog Semiconductor's suppliers certify that its products are in compliance with the requirements of Directive 2011/65/EU of the European Parliament on the restriction of the use of certain hazardous substances in electrical and electronic equipment. RoHS certificates from our suppliers are available on request.

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.