# **Application Note**Smart PWM Fan Driver

**AN-CM-332**

# **Abstract**

This application note describes the High Voltage GreenPAK IC configured as an integrated smart PWM fan driver. The design implements fan lock detection without the need for 3-wire fans for temperature proportional speed control.

The application note comes complete with a design file which can be found in the Reference section.

# **Contents**

| Αb  | stract       |                                                                                                                                   | 1        |  |  |  |  |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|

| Со  | ntent        | s                                                                                                                                 | 2        |  |  |  |  |

| Fig | jures.       |                                                                                                                                   | 2        |  |  |  |  |

| Tal | bles         |                                                                                                                                   | 2        |  |  |  |  |

| 1   |              | ns and Definitions                                                                                                                |          |  |  |  |  |

| 2   | Refe         | erences                                                                                                                           |          |  |  |  |  |

| 3   | Intro        |                                                                                                                                   |          |  |  |  |  |

| 4   | Cons         | struction and Operating Principle                                                                                                 | <u>5</u> |  |  |  |  |

| 5   | HVPAK Design |                                                                                                                                   |          |  |  |  |  |

| •   | 5.1          | Voltage-Proportional Fan Speed Control                                                                                            |          |  |  |  |  |

|     | 5.2          | Lock Detection and Auto-Restart                                                                                                   |          |  |  |  |  |

|     | 5.3          | Start-up Timer                                                                                                                    | 11       |  |  |  |  |

|     | 5.4          | Minimum Speed and Stop Threshold                                                                                                  | 11       |  |  |  |  |

| 6   | Resu         | ılts                                                                                                                              | 12       |  |  |  |  |

| 7   | Cond         | clusion                                                                                                                           | 14       |  |  |  |  |

| Re  | visior       | History                                                                                                                           | 15       |  |  |  |  |

|     |              |                                                                                                                                   |          |  |  |  |  |

| Fi  | gure         | es e                                                                                          |          |  |  |  |  |

|     |              | Brushless DC Fan used in this Application                                                                                         |          |  |  |  |  |

|     |              | Typical Application Circuit                                                                                                       |          |  |  |  |  |

|     |              | Prototype                                                                                                                         |          |  |  |  |  |

|     |              | Fan Speed Control Block                                                                                                           |          |  |  |  |  |

|     |              | Output PWM and Input Voltage                                                                                                      |          |  |  |  |  |

|     |              | Lock Detection and Auto-restart Block                                                                                             |          |  |  |  |  |

|     |              | Simplified Internal Circuit of a Brushless DC FanFan Current Waveform During Normal Operation (the signal on the sensor pin is an |          |  |  |  |  |

|     |              | or 120 for measurement purposes)                                                                                                  |          |  |  |  |  |

| Fig | ure 10       | ): Fan Current During Lock                                                                                                        | 10       |  |  |  |  |

| Fig | ure 1        | 1: Start-up Timer Block                                                                                                           | 11       |  |  |  |  |

| Fig | ure 12       | 2: Temperature Threshold Detection                                                                                                | 11       |  |  |  |  |

| Fig | ure i        | 3: Output Waveform (C1) with Vin ≈ 1V (C2)<br>4: Output Waveform (C1) with Vin ≈ 1.5V (C2)                                        | 12<br>12 |  |  |  |  |

| Fig | ure 1        | 5: Output Waveform (C1) with Vin ≈ 2.4V (C2)                                                                                      | 112      |  |  |  |  |

| Fia | ure 16       | 6: Fan Current (C1) and Fault Output (C2) when the Fan is Forced to Stop                                                          | 13       |  |  |  |  |

|     |              | 7: Output Waveform (C1) and Input Voltage (C2)                                                                                    |          |  |  |  |  |

| Te  | ables        |                                                                                                                                   |          |  |  |  |  |

|     |              |                                                                                                                                   | =        |  |  |  |  |

| Ιal | ble 1:       | Fan Parameters                                                                                                                    | 5        |  |  |  |  |

## 1 Terms and Definitions

**CCMP** Current comparator

CMP Comparator

CNT Counter

DC Direct current

DLY Delay

HV High voltage IC Integrated Circuit LUT Look-up Table

PWM Pulse width modulation

## 2 References

For related documents and software, please visit:

https://www.dialog-semiconductor.com/configurable-mixed-signal.

Download our free GreenPAK Designer software [1] to open the .gp files [2] and view the proposed circuit design. Use the GreenPAK development tools [3] to freeze the design into your own customized IC in a matter of minutes. Find out more in complete library of application notes [4] featuring design examples as well as explanations of features and blocks within the GreenPAK IC.

- [1] GreenPAK Designer Software, Software Download and User Guide

- [2] AN-CM-332 Smart PWM Fan Driver.gp, GreenPAK Design File

- [3] GreenPAK Development Tools, GreenPAK Development Tools Webpage

- [4] GreenPAK Application Notes, GreenPAK Application Notes Webpage

## 3 Introduction

Cooling fans are widely used and extremely important for electronic devices, especially for those that are constantly running, such as power supplies, servers, computers, and telecommunication equipment.

Low-cost cooling systems are often based on 2-wire fans that constantly run at full speed. The absence of temperature proportional speed control and the inability to detect fan lock (usually possible only with more expensive 3-wire fans) shortens the fan life and can lead to fatal damage for the system being cooled.

This application note describes how to configure the SLG47105 IC to implement a smart PWM fan driver with temperature proportional speed control and lock detection for a 12V 2-wire fan. This represents a low-cost solution with minimal external components.

Figure 1: Brushless DC Fan used in this Application

The most common types of cooling fan use brushless DC motors with a simple internal commutation circuit based on a Hall sensor, powered with a DC voltage. The speed of the fan is proportional to the DC voltage and can be controlled with PWM.

# 4 Construction and Operating Principle

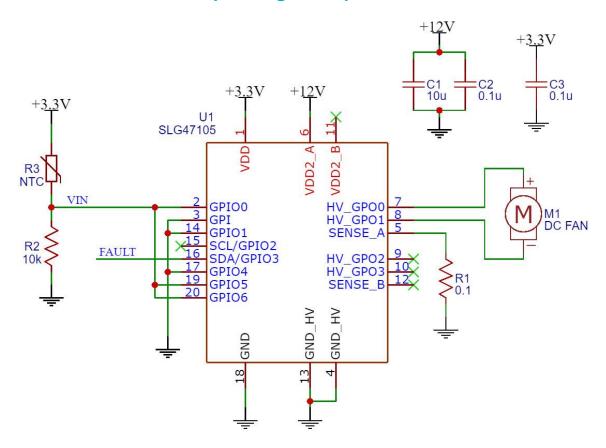

**Figure 2: Typical Application Circuit**

This design has 4 inputs and 1 output:

PIN#2 – Analog input to control the fan speed

PIN#3 - Control mode selection input

PIN#14 – PWM input for direct control of the output driver

PIN#17 - Shutdown input, to disable the fan

PIN#16 - Fault output, active low

In the application circuit depicted above, the mode input is connected to GND and the design works in "analog mode" (the fan speed is proportional to the voltage on PIN#2). The design also allows one to control the output driver directly with a PWM signal on PIN#14. In this case, the mode input must be connected to VDD ("digital mode").

PIN#19 and PIN#20 are used to detect temperature thresholds. They must both be connected to PIN#2 in "analog mode" and both connected to VDD in "digital mode".

**Table 1: Fan Parameters**

| Part Number  | Rated Voltage (V) | Input Current (A) | Input Power (W) | Speed (R.P.M.) |

|--------------|-------------------|-------------------|-----------------|----------------|

| KF0410S1M-03 | 12                | 0.07              | 0.84            | 5400           |

Application Note Revision 1.0 09-Mar-2022

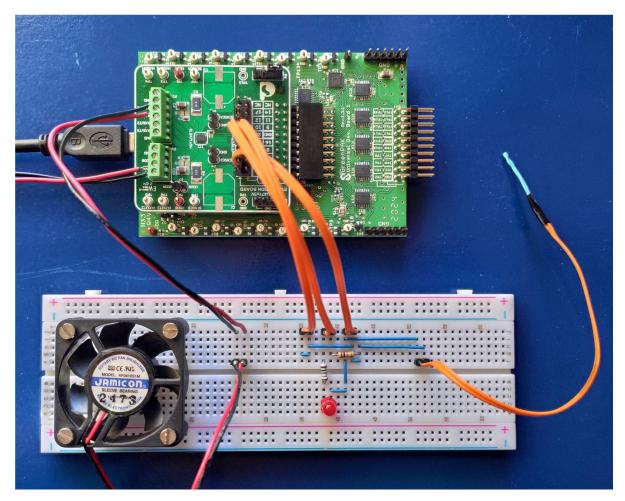

Figure 3: Prototype

# 5 HVPAK Design

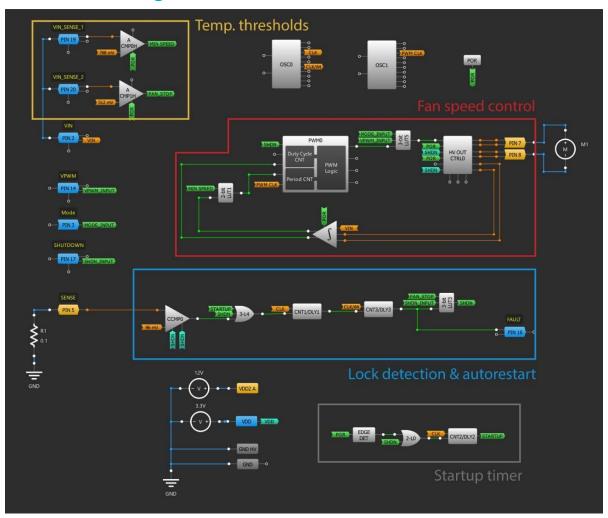

Figure 4: HVPAK Design

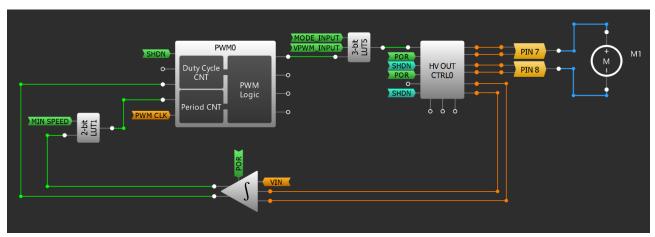

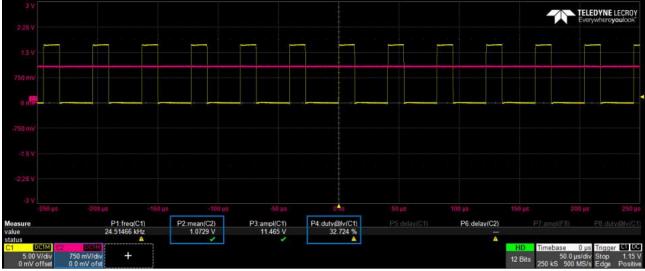

# 5.1 Voltage-Proportional Fan Speed Control

This block allows one to control the fan speed using a voltage input. The duty-cycle of the PWM that drives the fan is proportional to the input voltage (between 0V and 3V).

Figure 5: Fan Speed Control Block

The differential amplifier with integrator and comparator macrocell amplifies the voltage on the HV outputs, extracts the mean value, and compares it with the reference voltage (the voltage Vin on PIN#2). The macrocell activates the "equal" or the "upword" outputs according to the result of the comparison.

The PWM macrocell uses the "equal" and "upword" signals to increment or decrement the duty-cycle counter, which stores an 8-bit value representing the duty-cycle of the generated PWM waveform.

In this way, the block implements a loop that adjusts the duty-cycle to keep the following expression true:

Vmean = 4\*VIN

where Vmean is the mean voltage on the fan, and the constant 4 is the gain of the differential amplifier.

Because of this, the output duty-cycle depends on the input voltage according to the following equation:

$dc (\%) = (4*VIN / VDD2_A)*100$

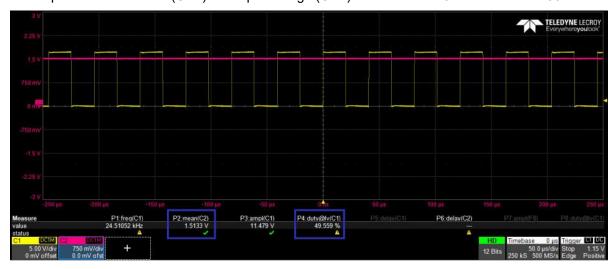

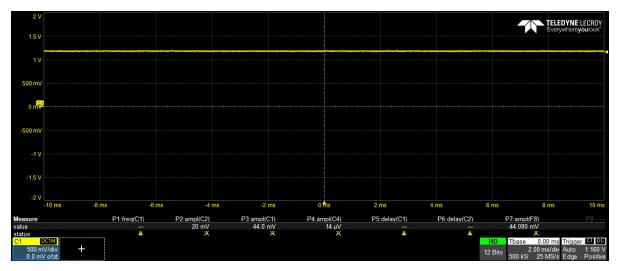

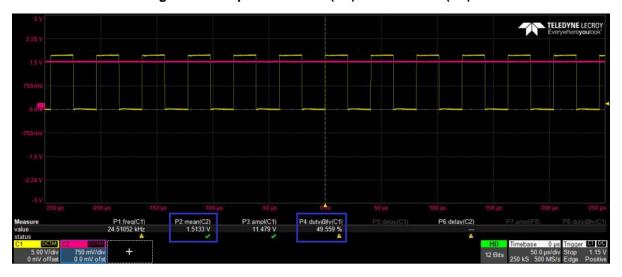

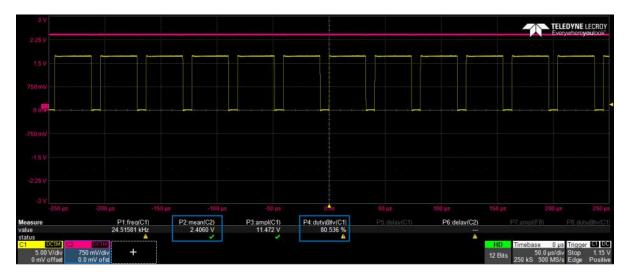

In this example, where VDD2\_A is 12V, we get a duty-cycle of 100% with VIN = 3V. Figure 6 shows the output PWM waveform (CH1) and input voltage (CH2) where VIN  $\approx$  1.5V and thus dc  $\approx$  50%.

Figure 6: Output PWM and Input Voltage

#### 5.2 Lock Detection and Auto-Restart

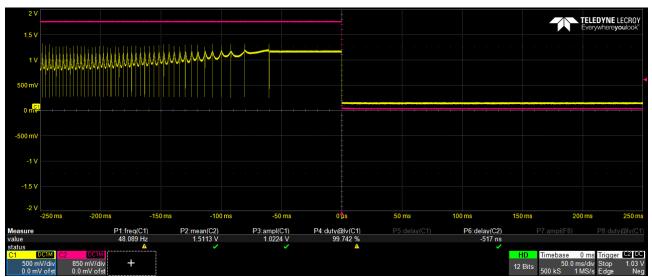

This block can detect if the fan stops, either because it is forced to stop or because it is disconnected from the driver. When a lock is detected, the output driver is disabled. In the first case, this is also necessary to protect the fan from fatal damage. In both cases the block is useful to activate a fault output so that the system can protect itself from overheating.

In addition, when a lock is detected, this block attempts to automatically restart the fan after a programmable delay time.

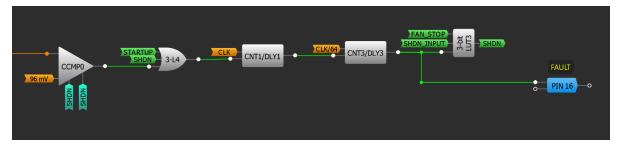

Figure 7: Lock Detection and Auto-restart Block

This block is based on current measurement by means of a resistor connected in series with the driver. The resistor provides a voltage signal proportional to the motor current at the sensor input.

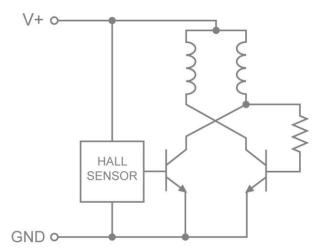

To understand how to detect fan lock, we need to understand the circuitry of a DC brushless fan.

Figure 8: Simplified Internal Circuit of a Brushless DC Fan

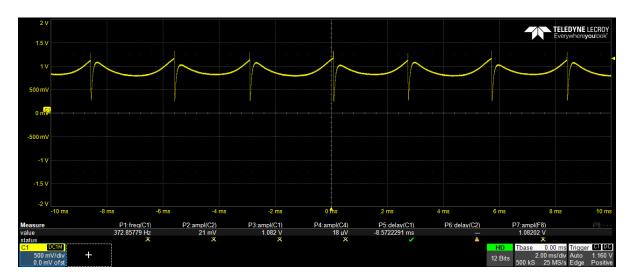

Brushless DC fans use a simple switching circuit like the one depicted in Figure 8. The Hall sensor switches on one of the two transistors according to the rotor position to activate the correct coil and ensure rotation. These commutations cause short and periodic interruptions of the fan current, as shown in Figure 9. On the other hand, if the fan is locked, there is no commutation and no current interruption, as shown in Figure 10.

Figure 9: Fan Current Waveform During Normal Operation (the signal on the sensor pin is amplified by a factor 120 for measurement purposes)

Figure 10: Fan Current During Lock

The comparator CCMP0 is used to provide a pulse every time there is a current interruption. The falling edges of these pulses keep triggering the CNT1/DLY1 macrocell (configured in delay mode), which will hold its output low as long as the pulses keep coming. If no pulses occur for about 50ms, the output will go high, triggering the CNT3/DLY3 (configured in one shot mode) to provide a negative pulse with a duration of 5 seconds. During this interval, the output driver is disabled. The fault output is active low, and it is driven by the CNT3/DLY3 output.

After 5 seconds, the output driver is enabled again. If the fan is still locked, the device will enter the fault state again.

The 3-input OR is used to disable the lock detection logic as described in the following section.

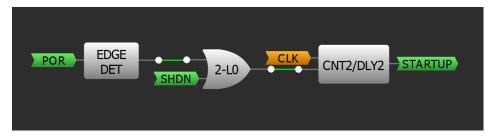

# 5.3 Start-up Timer

Since the fan can't start spinning instantly due to its inertia, the lock detection logic might detect a false fault condition and disable the output driver prematurely. This block is used to bypass the lock detection logic during the start-up of the motor to avoid this unwanted condition.

Figure 11: Start-up Timer Block

The block uses the CNT2/DLY2 in one shot mode activated on the falling edge. The falling edge is generated either by the POR and by the "SHDN" signal. In the first case, a rising edge detector generates a short pulse triggered by POR so that the start-up signal is generated at power-on. A falling edge of the "SHDN" signal instead corresponds to all the cases in which the fan is being restarted.

When the falling edge is detected, the "STARTUP" output goes high for about 125ms, forcing a logic 1 at the input of CNT1/DLY1 (see Figure 7) no matter what signal is coming from CCMP0. This allows one to disable the lock detection chain that is triggered by falling edges (the "STARTUP" signal could just generate a rising edge, but it will have no effect).

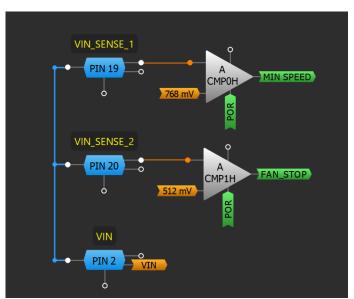

# 5.4 Minimum Speed and Stop Threshold

The design allows one to set a minimum fan speed and a minimum temperature below which the fan is disabled.

Figure 12: Temperature Threshold Detection

For this purpose, two voltage comparators are used. The inputs of the comparators are connected to the Vin voltage that controls the speed of the fan and which is proportional to the sensed temperature.

Due to the direct proportionality between input voltage and speed (as shown in Section 5.1), it's possible to set the minimum fan speed by setting the voltage threshold on the comparator. When the input voltage goes below the threshold, the output of the comparator (MIN SPEED) goes low and, through the 2-bit LUT, forces high the "keep" input of the PWM macrocell. In this way, the output duty-cycle can't decrease any further as long as the input voltage is below the threshold, thus setting a minimum fan speed.

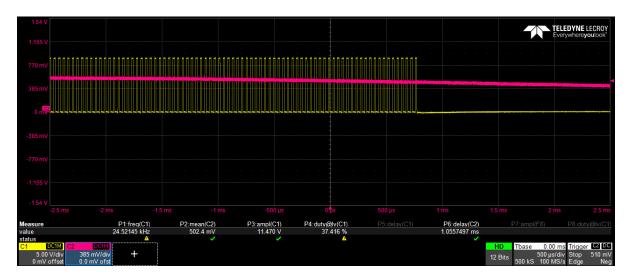

A similar concept is valid for the other comparator. In this case, the voltage threshold must correspond to the minimum temperature according to the temperature sensor used. When the input voltage goes below the threshold, the output of the comparator (FAN STOP) goes low and disables the output driver, stopping the fan.

For both the comparators a 32mV hysteresis is used.

#### 6 Results

Proportionality between the input voltage and the output duty-cycle:

Figure 13: Output Waveform (C1) with Vin ≈ 1V (C2).

Figure 14: Output Waveform (C1) with Vin ≈ 1.5V (C2).

Figure 15: Output Waveform (C1) with Vin ≈ 2.4V (C2).

#### Lock detection:

Figure 16: Fan Current (C1) and Fault Output (C2) when the Fan is Forced to Stop.

Minimum temperature (the fan is stopped when the input voltage goes below a minimum threshold):

Figure 17: Output Waveform (C1) and Input Voltage (C2)

# 7 Conclusion

This application note shows how the High Voltage GreenPAK IC SLG47105 can be configured to implement a smart PWM fan driver with minimal external components. The design is very flexible and can be adapted to a wide variety of fans thanks to the high-current capable integrated driver. The design also allows one to easily configure parameters including PWM frequency, minimum speed, and minimum temperature.

# **Revision History**

| Revision | Date        | Description     |

|----------|-------------|-----------------|

| 1.0      | 09-Mar-2022 | Initial version |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

# **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.