# Application Note Adjustable Analog Filter AN-CM-310

# **Abstract**

This application note illustrates how to use the SLG47004 to implement an adjustable analog filter and describes different ways to adjust the filter's cutoff frequency.

The application note comes complete with design files which can be found in the References section.

### **Contents**

| Abs | stract | t         |                                            | 1  |

|-----|--------|-----------|--------------------------------------------|----|

| Cor | ntent  | s         |                                            | 2  |

| 1   | Term   | ns and D  | Definitions                                | 2  |

|     |        |           |                                            |    |

|     |        |           |                                            |    |

|     |        |           | rview                                      |    |

|     |        |           | Block Architecture                         |    |

|     | 5.1    |           | Rheostat Data                              |    |

|     | 5.2    |           | ing Rheostat Data                          |    |

|     |        | 5.2.1     |                                            |    |

|     |        | 5.2.2     | Changing Rheostat Value via Internal Logic | 6  |

|     | 5.3    | Macroc    | cells Settings                             | g  |

|     | 5.4    |           | re Simulation                              |    |

|     | 5.5    | Hardwa    | are Testing                                | 13 |

| Cor | nclus  | ions      |                                            | 14 |

| Rev | /isior | n History | /                                          | 15 |

### 1 Terms and Definitions

ADC Analog-to-digital converter

CNT Counter

DFF D flip-flop

LUT Look up table

OpAmp Operational amplifier

### 2 References

For related documents and software, please visit:

https://www.renesas.com/us/en/products/programmable-mixed-signal-asic-ip-products/greenpak-programmable-mixed-signal-products

Download our free GreenPAK Designer software [1] to open the .gp files [2] and view the proposed circuit design. Use the GreenPAK development tools [3] to freeze the design into your own customized IC in a matter of minutes. Find out more in a complete library of application notes [4] featuring design examples, as well as explanations of features and blocks within the GreenPAK IC.

- [1] GreenPAK Designer Software, Software Download and User Guide

- [2] AN-CM-310 Adjustable Analog Filter.gp, GreenPAK Design File

- [3] GreenPAK Development Tools, GreenPAK Development Tools Webpage

- [4] GreenPAK Application Notes, GreenPAK Application Notes Webpage

- [5] Analog Filter Wizard, Filter Design Tool Webpage, Analog Devices

Author: Marian Hryntsiv

### 3 Introduction

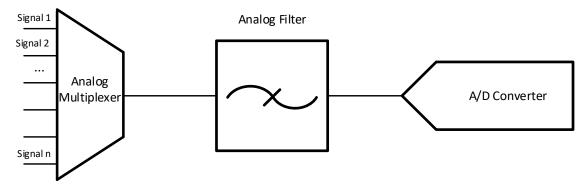

There are a variety of applications where signals from different sources (for example, sensors) are sensed with one ADC. Such systems require an analog multiplexer with analog filters for each channel, because each signal source may have its own set of filter requirements (for example, different cutoff frequencies). An alternative space-efficient and cost-efficient solution is to use one tunable analog filter for all channels (Figure 1). The SLG47004 IC solves this task perfectly.

Figure 1: Analog Interface with One Tunable Filter

# 4 System Overview

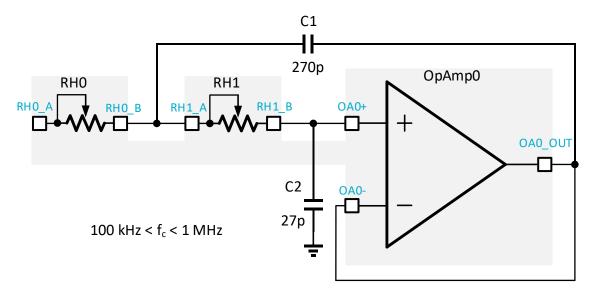

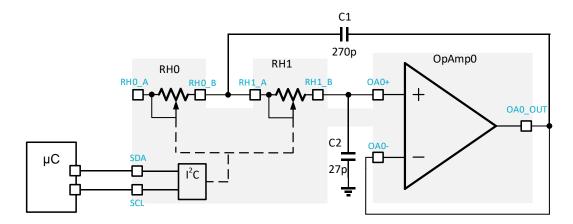

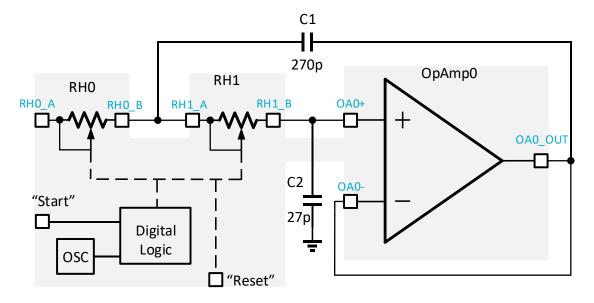

This application note demonstrates the implementation of the adjustable analog filter by highlighting an example second-order, programmable, active low-pass Sallen-Key filter (Figure 2).

This filter is implemented with two resistors, two capacitors, and an operational amplifier. Two resistors in this circuit are replaced with the SLG47004 Digital Rheostats, and one of the SLG47004 operational amplifiers is used as an active element.

Figure 2: Sallen-Key Filter Based on the SLG47004

By adjusting two Digital Rheostats the cutoff frequency and the approximation method of this active filter can be changed. The Butterworth approximation method was used in this application note. The

frequency behavior of the Butterworth filter is maximally flat in the magnitude response in the passband. The rate of attenuation in the transition band is better than the Bessel filter, though not as good as the Chebyshev filter. There is no ringing in the stopband. The step response of the Butterworth filter has some overshoot and ringing in the time domain, though this is comparatively less than the Chebyshev filter.

The equation for the low-pass filter configuration on Figure 2 is:

$$\frac{V_{OUT}}{V_{IN}} = \frac{K/(RH_1RH_2C_1C_2)}{s^2 + s(1/RH_1C_1 + 1/RH_2C_1 + 1/RH_2C_2 - K/RH_2C_2) + 1/RH_1RH_2C_1C_2}$$

where K = 1:

This formula can be used to calculate the appropriate resistance and capacitance. Alternatively, it is possible to determine the capacitors and resistors values using filter design tools [5].

The capacitor values in the filter circuit are kept constant while the resistive elements are adjusted. For this project, capacitor values chosen are: C1 = 270 pF and C2 = 27 pF.

The SLG47004 contains two 10-bit Digital Rheostats. The full resistance for both Digital Rheostats is  $100~\text{k}\Omega$ . The range of digital code that corresponds to the rheostat resistance is from 0 to 1023 (1024 taps). Code 0 corresponds to the minimum resistance between the RHx\_A and RHx\_B terminals. As the code value increases, the resistance between the RHx\_A and RHx\_B terminals monotonically increases. Consequently, when the code value decreases, the resistance between the RH0\_A and RH0\_B terminals decreases as well. The voltage on any rheostat pin can be in the range from AGND to VDDA, and can be dynamically changed during operation.

The values calculated for this filter design are summarized in Table 1. This table also includes the closest resistance values for RH0 and RH1 along with the digital program code.

Table 1: The Butterworth Filter Design Adjusting the Resistors through a Digital Rheostat

| Cutoff<br>Frequency,<br>kHz | Calculated<br>RH0<br>Value, Ω | Closest<br>Digital<br>Rheostat RH0<br>Value, Ω | Digital<br>Rheostat<br>RH0 Code | Calculated<br>RH1 Value,<br>kΩ | Closest<br>Digital<br>Rheostat RH1<br>Value, kΩ | Digital<br>Rheostat<br>RH1 Code |

|-----------------------------|-------------------------------|------------------------------------------------|---------------------------------|--------------------------------|-------------------------------------------------|---------------------------------|

| 100                         | 4400                          | 4395                                           | 44                              | 78.900                         | 78.906                                          | 807                             |

| 1000                        | 440                           | 490                                            | 4                               | 7.890                          | 7.910                                           | 80                              |

### 5 Functional Block Architecture

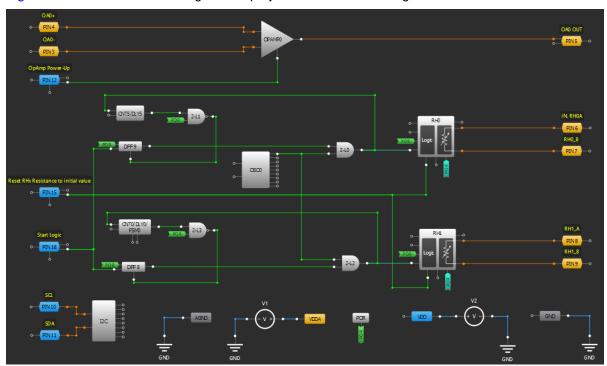

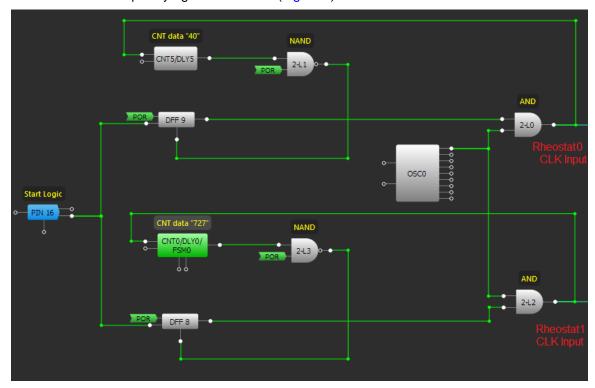

Figure 3 shows the internal design of the project in GreenPAK Designer software.

Figure 3: GreenPAK Designer Project

### 5.1 Setting Rheostat Data

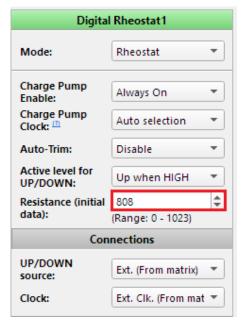

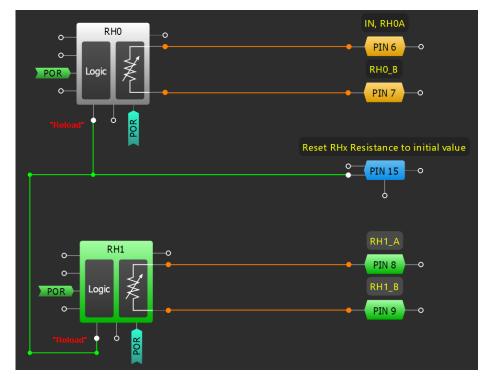

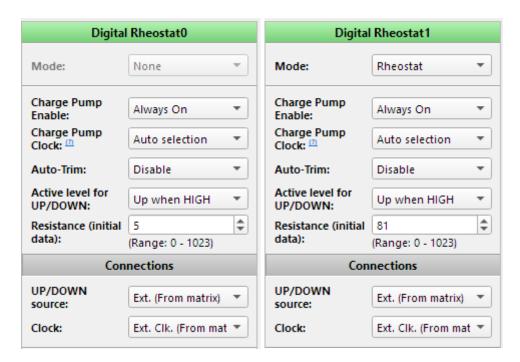

Both rheostats allow setting "Resistance (Initial data)" in their properties and thus setting the desired filter's cutoff frequency (Figure 4).

Figure 4: Digital Rheostat 1 Properties

### 5.2 Changing Rheostat Data

There are two ways to change Digital Rheostats value: using I<sup>2</sup>C, and using internal logic.

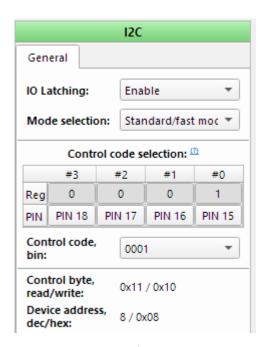

### 5.2.1 Changing Rheostat Value via I<sup>2</sup>C

The SLG47004 has an I<sup>2</sup>C macrocell, which allows reading and writing data to Digital Rheostats (Figure 5). The rheostats resistance data is stored in the registers [C0, C1] for RH0 and [D0, D1] for RH1. The I<sup>2</sup>C master can write data to these registers and thus can adjust the cutoff frequency of the filter according to the digital code in Table 1. Note that to read the rheostat data, the I<sup>2</sup>C master should read the registers [C2, C3], [D2, D3]

Figure 5: I<sup>2</sup>C Connection to Change Rheostats Resistance

### 5.2.2 Changing Rheostat Value via Internal Logic

Adjusting the cutoff frequency by I<sup>2</sup>C is a simple and convenient method, but it requires an I<sup>2</sup>C master. An alternative method can be implemented with two pins and internal logic (Figure 6).

Figure 6: Internal Logic Block Diagram to Change Rheostats Resistance

A High level signal on the Start (Pin 16) and Reset (Pin 15) pins allows switching between two different frequencies. When the rheostat's initial value is set to 100 kHz cutoff frequency, the High level signal on Pin16 starts changing this frequency to 1 MHz (Figure 7). The High level signal on Pin15 resets the frequency again to 100 kHz (Figure 8).

Figure 7: Internal Logic for Changing Rheostat Resistance

Figure 8: Rheostat Reloading Unit

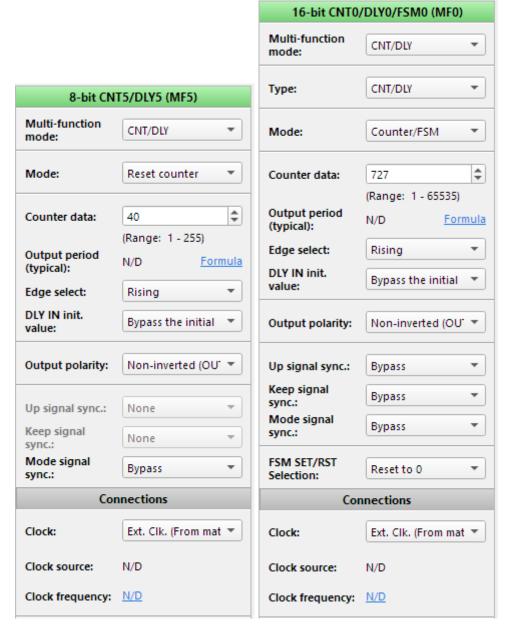

To detail this behavior further, for 1 MHz cutoff frequency RH0 resistance is 488  $\Omega$  (code 4) and RH1 is 7.910 k $\Omega$  (code 80). To change the frequency to 100 kHz the RH0 resistance = 4.395 k $\Omega$  (code 44) and RH1 resistance = 78.906 k $\Omega$  (code 807). So, for RH0 the digital code value must be increased by 40 and for RH1 by 727. To increase the resistance in the rheostat's settings "Active level for UP/DOWN" must be set to "Up when High".

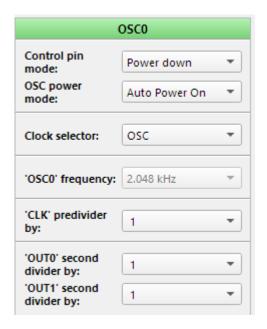

8-bit and 16-bit Counters can be configured to provide the necessary number of clock pulses from the oscillator to the rheostats. 8-bit Counter data must be set to "40" and 16-bit Counter to "727".

CNTs stop is provided by the internal logic (Figure 7). When "Start Logic" signal goes High, DFFs will trigger on its rising edge. A High level on DFFs outputs will cause a clock signal on LUT0 and LUT2 outputs. After that, Counters values start going down and when they reach "0" a High level will appear at LUT1 and LUT3 inputs respectively. As these LUTs are NAND gates, a High level of signals on their inputs will reset the corresponding flip-flop and will stop counting.

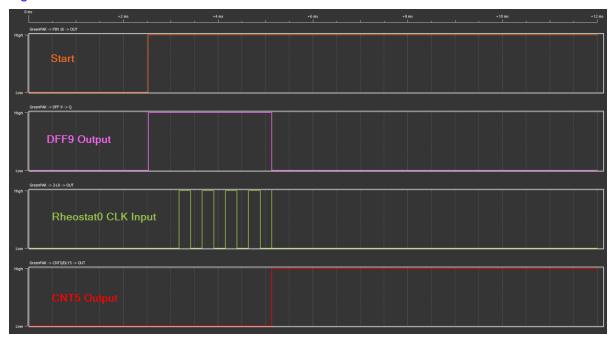

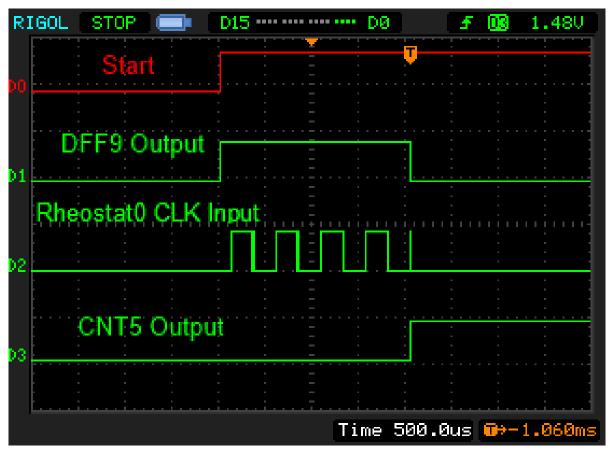

Software simulation results for this internal logic are shown in Figure 9. For hardware testing refer to Figure 10.

Figure 9: Software Simulation of Internal Logic at CNT5 Data = 5

Figure 10: Hardware Testing Waveforms for Internal Logic at CNT5 Data = 5

For resetting the cutoff frequency Pin15 works as a Digital Input and is connected to "Reload" input of the rheostats. When Reload signal goes High, the rheostat value stored in the MTP NVM will be loaded into the rheostat (Register and Counter) overwriting any current setting. For the normal rheostat operation "FIFO nReset" input should have a logic High level (Figure 7).

# **5.3 Macrocells Settings**

**Table 2: LUTs Settings**

| IN1 | IN0 | 2-bit LUT0 OUT | 2-bit LUT1 OUT | 2-bit LUT2 OUT | 2-bit LUT3 OUT |

|-----|-----|----------------|----------------|----------------|----------------|

| 0   | 0   | 0              | 1              | 0              | 1              |

| 0   | 1   | 0              | 1              | 0              | 1              |

| 1   | 0   | 0              | 1              | 0              | 1              |

| 1   | 1   | 1              | 0              | 1              | 0              |

**Table 3: DFFs Settings**

| Properties         | DFFs 8, 9 |

|--------------------|-----------|

| Туре               | DFF/LATCH |

| Mode               | DFF       |

| nSET/nRESET option | nRESET    |

| Initial polarity   | Low       |

Application Note Revision 1.0 18-Nov-2020

| Properties               | DFFs 8, 9        |

|--------------------------|------------------|

| Q output polarity        | Non-Inverted (Q) |

| Active level for RST/SET | Low Level        |

**Table 4: PINs Settings**

| Properties     | PINs 3, 4, 5, 6, 7, 8, 9 | PINs 10, 11                           | PINs 12, 15, 16                       |

|----------------|--------------------------|---------------------------------------|---------------------------------------|

| I/O selection  | Analog input/output      | Digital input                         | Digital input                         |

| Input mode     | Analog input/output      | Digital in without<br>Schmitt trigger | Digital in without<br>Schmitt trigger |

| Output mode    | Analog input/output      | None                                  | None                                  |

| Resistor       | Floating                 | Floating                              | Pull Down                             |

| Resistor value | Floating                 | Floating                              | 100 kΩ                                |

**Table 5: OpAmp Settings**

| Properties               | OpAmp0        |

|--------------------------|---------------|

| Mode                     | OpAmp Mode    |

| Bandwidth Selection      | 8 MHz         |

| Charge Pump              | Enable CP     |

| Supporting Blocks On/Off | Follows OpAmp |

| Vref Connection          | Disconnected  |

Figure 11: I<sup>2</sup>C Settings

Figure 12: OSC Settings

Figure 13: Digital Rheostat Settings for 1 MHz Cutoff Frequency

Figure 14: Counter Settings

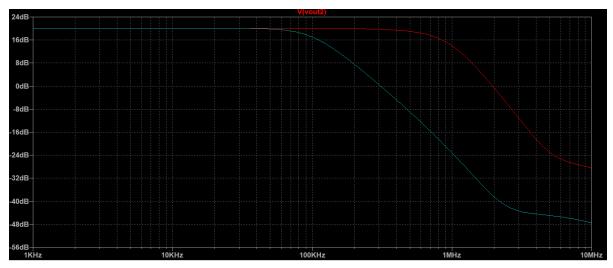

### 5.4 Software Simulation

The frequency response of the second-order, active low-pass Sallen-Key filter ( for 100 kHz and 1 MHz corner cutoff frequencies) is shown in Figure 15.

Figure 15: Simulated Frequency Response of Filter for Two Cutoff Frequencies

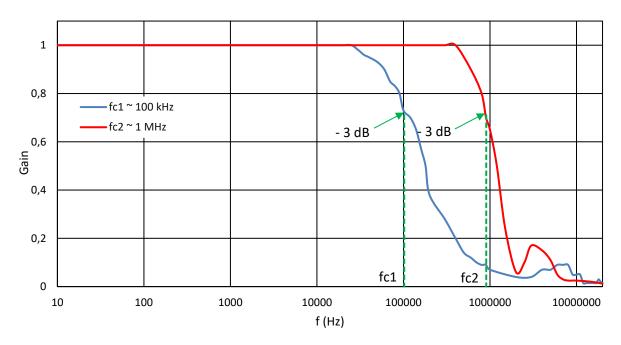

### 5.5 Hardware Testing

Results of prototype testing for both cutoff frequencies are shown in Figure 16.

Figure 16: Frequency Response of Prototype Filter for Two Cutoff Frequencies

### **Conclusions**

The SLG47004 has the necessary internal resources to implement advanced analog features. This application note illustrates how to implement an adjustable analog filter as a functional replacement of multiple standard products. Using one tunable analog filter for different cutoff frequencies provides a more flexible, cost-efficient solution that yields a smaller PCB footprint and lower power consumption. Due to the configurable nature of the SLG47004, this application note's approach can be easily expanded for augmented functionality, such as adjusting other filter requirements like the filter approximation method.

# **Revision History**

| Revision | Date        | Description     |

|----------|-------------|-----------------|

| 1.0      | 18-Nov-2020 | Initial Version |

### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.