## ClockMatrix™ - Channel Control for PTP with the Time of Day Counter

A PTP system needs to process the PTP packets and provide updates to the frequency, phase and time of day in the clock synthesis device via register access. In LinuxPTP for example, the ptpt4l application serves as the PTP packet processor with a simple optional filter. The filter provides clock updates via the Linux PHC API to control a channel in ClockMatrix™. The PHC API has functions to adjust the frequency and phase of the channel. It also has functions to control the time of day (ToD) counter. The ClockMatrix clock synthesizer will then align its outputs to the 1Hz (or one pulse per second) rollover of the PTP ToD counter for use by the time stamper or other system blocks that need phase. Besides an explanation of how a PTP system works, this document also shows an example ClockMatrix configuration for use with SyncE and PTP.

## Contents

|                                                                    |    |

|--------------------------------------------------------------------|----|

| 1. Introduction.....                                               | 2  |

| 2. General Operation of a PTP System .....                         | 2  |

| 3. Aligning the Clock Synthesizer to the Time Stamper.....         | 3  |

| 4. Clock Control using the Linux PTP Hardware Clock (PHC) API..... | 4  |

| 5. Example GUI Configuration for SyncE/PTP on 8A34001.....         | 5  |

| 6. Revision History .....                                          | 10 |

## 1. Introduction

This application note explains how the PTP driver controls a channel in ClockMatrix by using the Time of Day (ToD) counter to align the device outputs to the 1Hz/1PPS (pulse per second) rollover of the counter. (The rollover of the counter is when the nanoseconds and sub-nanoseconds parts of the counter are zero.) The PTP driver also controls the clock used by the counter for both rough and fine adjustment of the output.

In a typical PTP system, there is a clock synthesizer channel with both frequency and phase control from the external software. This channel clocks a ToD counter. The counter value is incremented by the period of the channel clock on every edge. The outputs from the device use the ToD rollover clock for output alignment. In addition, the ToD counter can use different triggers to get values into and out of the counter including external 1Hz clocks, the internal rollover clock or a software command.

This application note describes how the PTP software will processes the packets, control the DPLL channel and control ToD counter. A separate program coordinates the ToD in the clock synthesizer and the time stamper. Both of these programs use the PHC functions to control of clocks and ToD in the different hardware devices.

In the last section of the document, there is ClockMatrix GUI configuration for an example PTP/SyncE system.

## 2. General Operation of a PTP System

To implement PTP, a system has four main tasks:

- Decode the incoming PTP packets to extract the signaling and time stamps.

- Create the sets of local time stamps and extracted time stamps from the incoming packets.

- A simple filter or complicated servo to transform the time stamp groups into clock updates.

- Finally, it needs an interface to send the clock updates to hardware.

The PHC API contains the code to translate the clock and ToD update functions into the register sequences specific for each device.

In an example Linux system running LinuxPTP in standalone mode, ptpt4l will process the packets, extract the local and remote time stamps for processing, process the time stamps using its filter and send clock updates to the clock synchronizer via the PHC functions. When locking to a new master, the ptpt4l software via the PHC API will adjust the ToD counter rollover to phase align all the output to the PTP 1 PPS from the master.

(The operation of Renesas PTP Clock Manager for Linux, pcm4l, is similar. The ptpt4l program will still process the packets and create the time stamp groups as in standalone ptpt4l. Then, the unfiltered time stamp groups go from ptpt4l to pcm4l via a socket interface. Within pcm4l is an advanced non-linear adaptive servo to provide frequency and time transfer over more challenging networks. Like ptpt4l, pcm4l will send the resulting updates to the clock synthesizer via the PHC API.)

When the system starts, the clock synthesizer will have an arbitrary frequency and phase before locking to a master. As ptpt4l locked to the master, it will go through its internal states as defined in Table 1.

Table 1. Ptp4l State Definitions

| Number | Name                | Description                                                                                  |

|--------|---------------------|----------------------------------------------------------------------------------------------|

| 0      | SERVO_UNLOCKED      | The servo is not yet ready to track the master clock.                                        |

| 1      | SERVO_JUMP          | The servo is ready to track and requests a clock adjustment to correct the estimated offset. |

| 2      | SERVO_LOCKED        | The servo is tracking the master clock.                                                      |

| 3      | SERVO_LOCKED_STABLE | The Servo has stabilized.                                                                    |

Note: These definitions are in servo.h in the ptpt4l distribution.

First, ptpt4l will wait for packets in the SERVO\_UNLOCKED (S0) state.

Once ptpt4l starts receiving packets, it will go to the SERVO\_JUMP (S1) state. Ptpt4l will estimate the phase offset between the master and the local clock. If it is larger than **first\_step\_threshold** in seconds, ptpt4l will send an adjust time command to jump the ToD counter by the estimate of the offset via the PHC API. This will align the ToD counter to the local estimate of the master 1-PPS phase. Based on the internal output from the ToD counter, the device will align its output clocks to the new 1-PPS alignment of the ToD counter on the next ToD rollover. Finally, ptpt4l will start collecting time stamp groups and make a new estimate of the offset.

(As of LinuxPTP version 3.2, ptpt4l will discard packets after the phase adjustment. The delay to allow the time stamper to match to the new ToD alignment. The **step\_window** parameter defines the number of packets to discard before continuing.)

If the offset is still larger than the **step\_threshold** parameter in units of seconds in ptpt4l.cfg, ptpt4l will perform another phase adjustment. Typically, both **first\_step\_threshold** and **step\_threshold** are set to 20 microseconds. (The **step\_window**, **first\_step\_threshold** and **step\_threshold** parameters are in the ptpt4l configuration file.)

Once the estimated offset is small enough, ptpt4l will switch to the SERVO\_LOCKED (S2) state and the filter will switch to frequency offsets via the PHC API to pull-in the remaining phase offset between the local ToD and the estimate of the master ToD. For LinuxPTP version 3.0 or newer, the servo will switch to the SERVO\_LOCKED\_STABLE (S3) state when the offset is small. In the S3 state, the filter will switch to phase offsets via the PHC API to get the best alignment with the master. To get to the S3 state, the last **servo\_num\_offset\_values** values of the locally estimated offset to the master are less than **servo\_offset\_threshold** as defined in the ptpt4l configuration file. For ClockMatrix, the recommended value for **servo\_offset\_threshold** is 100 in units of nanoseconds and the value for **servo\_num\_offset\_values** is 64 in units of packets. (The **servo\_offset\_threshold** and the **servo\_num\_offset\_values** parameters are also in the ptpt4l configuration file.)

### 3. Aligning the Clock Synthesizer to the Time Stamper

As the clock synthesizer aligns the ToD to the master, the system also needs to align the time stamper to the clock synthesizer. The clock synthesizer typically sends two physical clocks to the time stamper: a PTP clock (high frequency usually 250MHz) and a PTP time stamp event (1Hz). A system can use other low frequency clocks from 0.5Hz to 4kHz as long as the time stamper can identify the clock edge corresponding to the rollover event. The time stamper uses the frequency from the PTP clock to increment its ToD counter. It uses the low frequency clock to latch a time stamp to coordinate between the ToD in the clock synthesizer and the time stamper.

A PTP system needs a method to align the ToD in the time stamper with the ToD in the clock synthesizer. In LinuxPTP, the ts2phc program coordinates between the clock synthesizer and time stampers when they are in separate devices. Under the control of ts2phc, the time stamper latches its ToD at the instant when the edge of the external 1PPS input arrives from the clock synthesizer. Ts2phc requests this ToD value via the PHC API to determine the difference between the seconds on the clock synthesizer ToD and the value from the time stamper and requests a ToD adjustment on the time stamper via the PHC API. Depending on the time stamper, the resulting ToD alignment can be less than 100 ns by accurately sampling the 1PPS clock and assuming that the nanoseconds and sub-nanoseconds part of the arrival of the 1Hz clock edge is zero. After the phase adjustment, the clock synthesizer changes the time stamper ToD phase via small frequency or phase changes via the high-speed PTP clock.

## 4. Clock Control using the Linux PTP Hardware Clock (PHC) API

The PTP application uses the PTP Hardware Clock (PHC) subsystem to request frequency, phase and ToD changes to the clock.

In LinuxPTP, each clock synthesizer used for PTP has its own PHC interface. The purpose of the PHC APIs is to translate the control commands from the PTP software to specific register sequences for each device. The Linux PHC drivers for ClockMatrix are part of the kernel.

A typical PHC driver supports the functions in Table 2.

**Table 2. PHC API Functions**

| Name     | Description                                                                                                                                                              |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| getTime  | Gets to the ToD counter value (immediate).                                                                                                                               |

| setTime  | Set the ToD counter to a specific value (immediate).                                                                                                                     |

| adjTime  | Make a relative change to the ToD counter.                                                                                                                               |

| adjFine  | Change the frequency offset to the specified value (resolution is ppb). This function replaced the adjFreq in earlier version of the PHC interface.                      |

| adjPhase | Using the write phase mode in ClockMatrix, adjust the phase by the specified value.                                                                                      |

| EXTTS    | Latch the ToD counter on the edge of an external signal (usually 1 PPS) where EXTTS is an EXTERNAL Time Stamp event.                                                     |

| PEROUT   | Control the periodic outputs on the device (used to control the 1 PPS output from the clock generator to the time stamper for frequency/phase distribution in a system). |

The hardware (clock synthesizer or time stamper) processes the getTime and setTime functions when the command arrives. There may be variable delays in accessing the hardware depending on the system and the serial bus loading. As a result, the system does not use these commands for fine control of the ToD. The adjTime command is very precise since it is relative to the last ToD value and any application delays do not impair its accuracy. While PTP software can use either adjFreq or adjFine to adjust the frequency of the device, the adjFine is preferred due to higher accuracy updates.

For ClockMatrix specifically, PHC API functions have an “idtcm” prefix. The idtcm\_settime PHC command will set the ToD in the clock synthesizer to an arbitrary value using an immediate write while the idtcm\_adjtime PHC command will set the ToD to a relative value using a relative write. Both are expected step the ToD and clock synthesizer will align the output signals to the new ToD rollover phase after the ToD is changed.

The ClockMatrix PHC driver switches the channel mode between “write frequency” for idtcm\_adjfine and “write phase” for idtcm\_adjphase modes as needed. For the idtcm\_adjfine and idtcm\_adjphase PHC commands, the phase change relative to the previous frequency or phase of the output, so the outputs maintain their alignment to the ToD counter rollover.

For all PHC functions, the PHC driver and the ClockMatrix hardware handles the alignment of the outputs without additional effort from the higher-level application.

## 5. Example GUI Configuration for SyncE/PTP on 8A34001

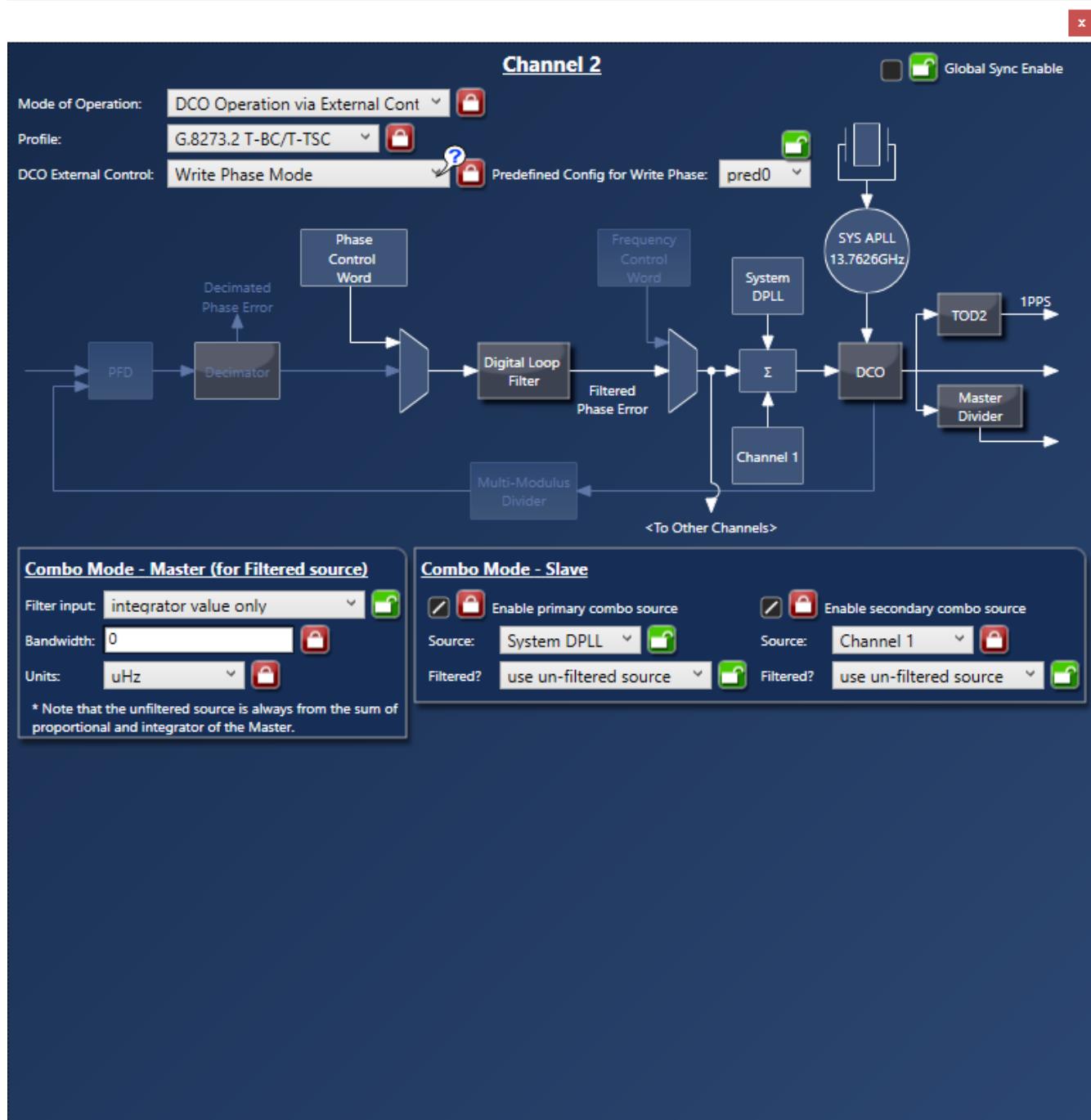

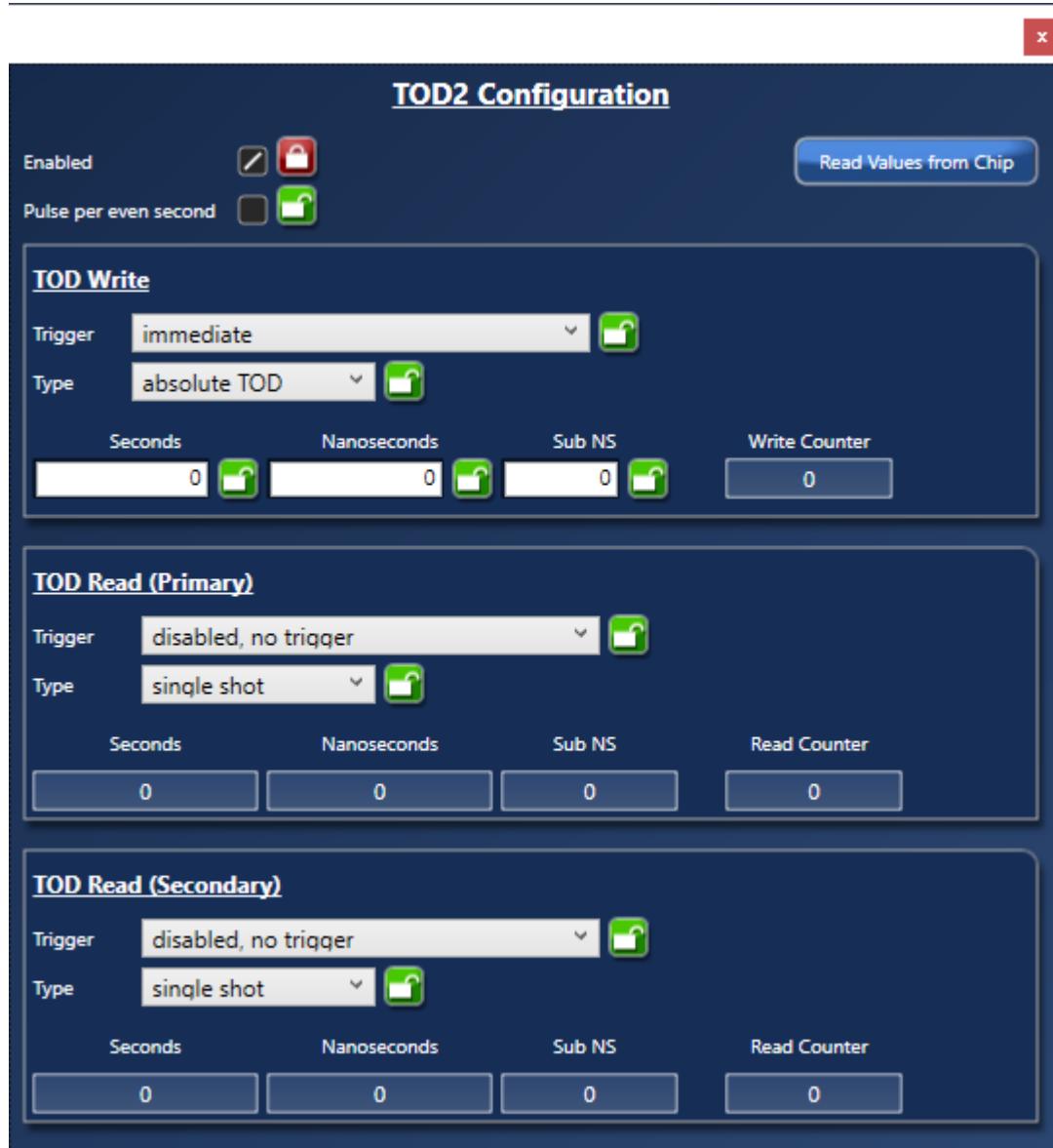

For this example, the SyncE is on channel 1 and the PTP is on channel 2. The SyncE recovered input is on clk4 and the SyncE transmit clock output is on Q3. The PTP Clock is on Q4. The PTP 1PPS is on Q5. For this configuration, the ToD counter and ToD counter output alignment are enabled for the PTP channel. (Other channels with PTP outputs would need frequency from the PTP channel and optionally alignment from the PTP channel's ToD counter.)

The PHC driver uses a .bin file for configuration. The .bin file must be in the target file system usually in the /lib/firmware directory. The .bin file has two pieces: the driver configuration and an optional set of device configuration registers. The driver configuration contains the channel, ToD and output list. If the registers are in the bin file, the driver resets the device after loading the registers and the loading process may interrupt the output clocks.

For this example, the GUI would generate a .bin file with a driver configuration and a full set of register values.

Figure 1. Overall Configuration

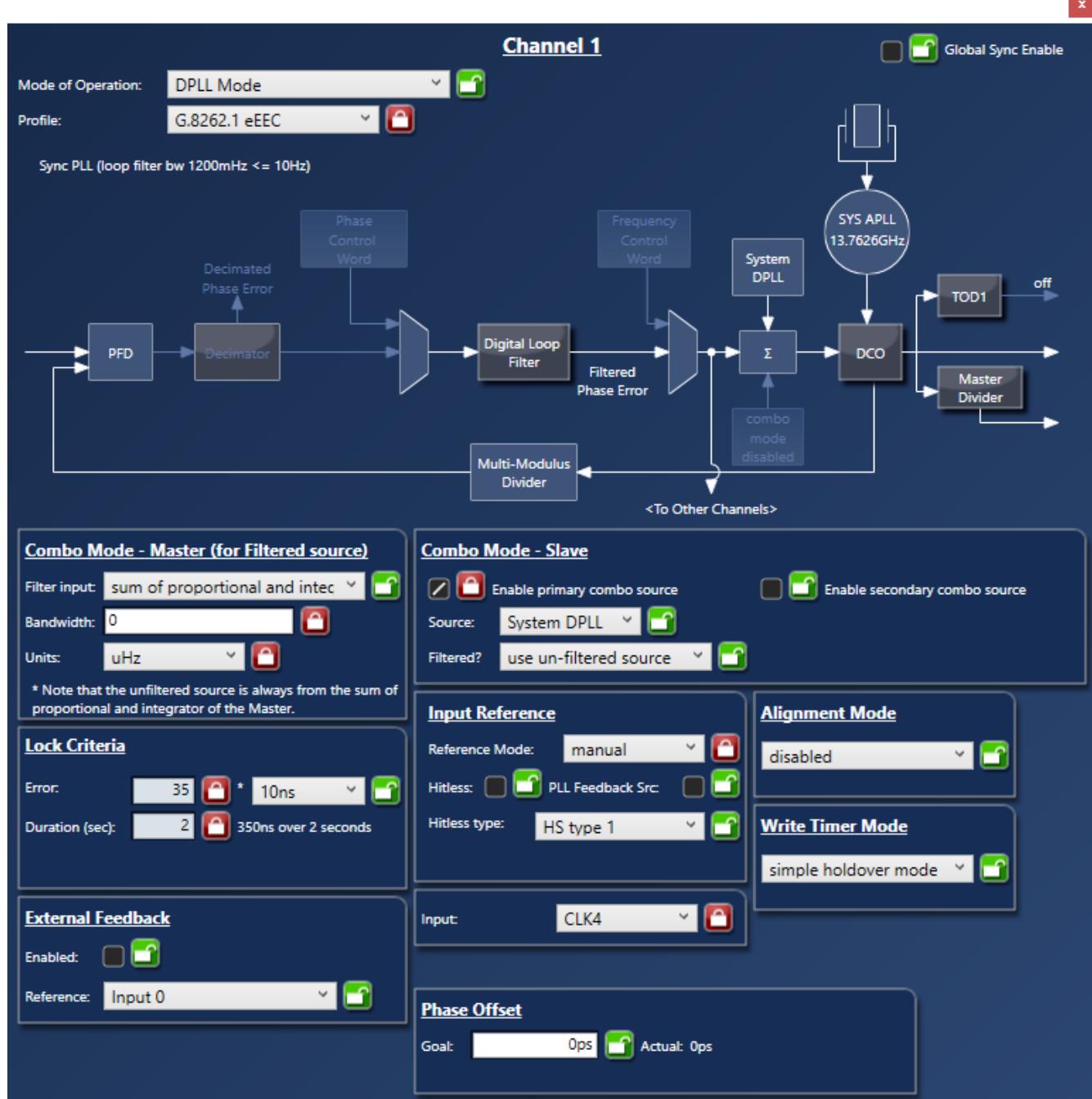

Figure 2. SyncE (DPLL) Channel Configuration

Figure 3. PTP (DCO) Channel Configuration

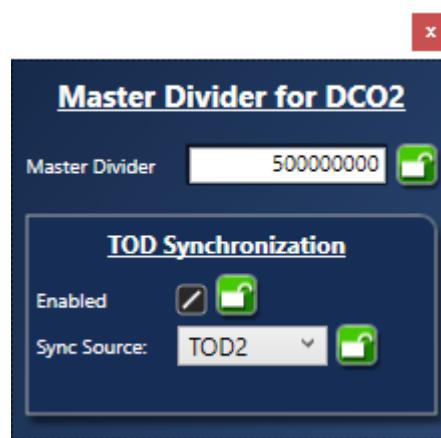

Figure 4. PTP Master Divider Configuration

Figure 5. PTP ToD0 Configuration

X

**Configuration for PTP HW Clock (PHC) Driver**

| <u>PTP Channel</u> | <u>TOD</u> | <u>Outputs</u> |

|--------------------|------------|----------------|

| DPLL2              | TOD2       | Q4,Q5          |

[Generate BIN File](#)

**Defining PTP HW Clocks**

1. Designate the PLL controlling the alignment by selecting a PTP profile (e.g., 8273.2, 8273.4 or 8263).

2. Configure satellite PLLs to the controlling PLL (optional)

- Select the controlling PLL as the primary or secondary combo source OR

- Select the controlling PLL as the feedback source

All outputs driven by the controlling PLL or any satellite PLLs will be aligned.

Figure 6. Generate Configuration for PHC Driver (.bin file)

## 6. Revision History

| Revision | Date         | Description     |

|----------|--------------|-----------------|

| 1.0      | Jun 11, 2021 | Initial release |

## IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit [www.renesas.com/contact-us/](http://www.renesas.com/contact-us/).