# APPLICATION NOTE

HIP4081A, 80V High Frequency H-Bridge Driver

## Introduction

RENESAS

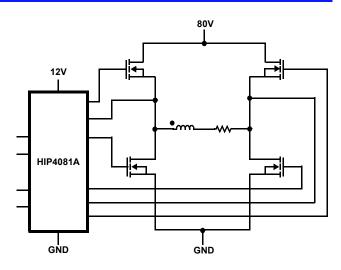

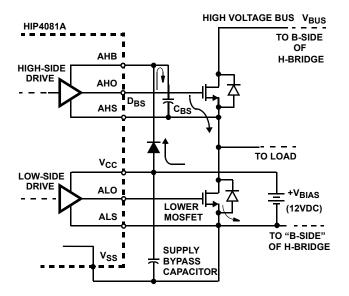

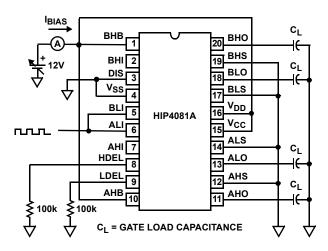

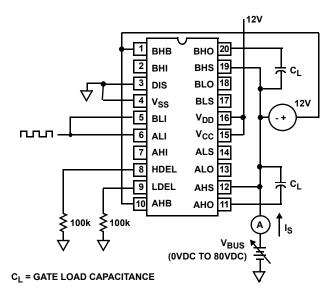

The HIP4081A is a member of the HIP408x family of High Frequency H-Bridge Driver ICs. A simplified application diagram of the HIP4081A IC is shown in Figure 1. The HIP408x family of H-Bridge driver ICs provide the ability to operate from 10VDC to 80VDC busses for driving H-Bridges, whose switch elements are comprised of power N-channel MOSFETs. The HIP408x family, packaged in both 20 pin DIP and 20 pin SOIC DIPs, provide peak gate current drive of 2.5A. The HIP4081A includes undervoltage protection, which sends a continuous gate turn-off pulse to all gate outputs when the  $V_{\mbox{\scriptsize DD}}$  voltage falls below a nominal 8.25V. The start-up sequence of the HIP4081A is initiated when the  $V_{DD}$  voltage returns above a nominal 8.75V. Of course, the DIS pin must be in the low state for the IC to be enabled. The startup sequence turns on both low side outputs, ALO and BLO, so that the bootstrap capacitors for both sides of the H-bridge can be fully charged. During this time the AHO and BHO gate outputs are held low continuously to insure that no shoot-through can occur during the nominal 400ns bootstrap refresh period. At the end of the bootstrap refresh period the outputs respond normally to the state of the input control signals.

A combination of bootstrap and charge pumping techniques is used to power the circuitry which drives the upper halves of the H-Bridge. The bootstrap technique supplies the high instantaneous current needed for turning on the power devices, while the charge pump provides enough current to "maintain" bias voltage on the upper driver sections and MOSFETs. Since voltages on the upper bias supply pin "float" along with the source terminals of the upper power switches, the design of this family provides voltage capability for the upper bias supply terminals to 95VDC.

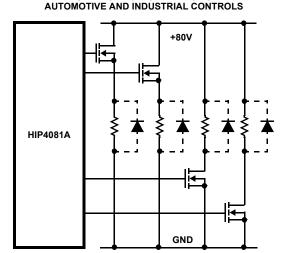

The HIP4081A can drive lamp loads for automotive and industrial applications as shown in Figure 2. When inductive loads are switched, flyback diodes must be placed around the loads to protect the MOSFET switches.

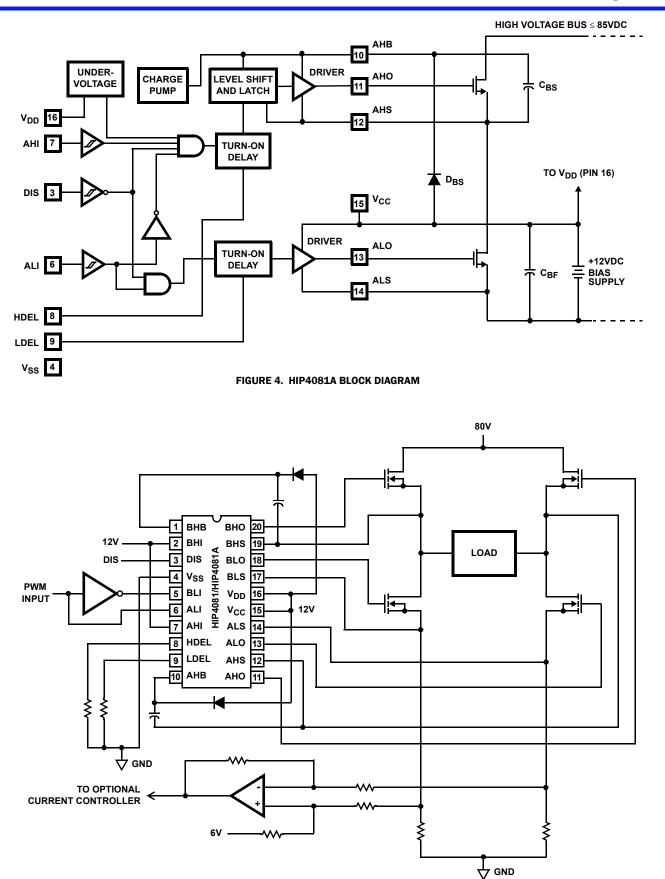

Many applications utilize the full bridge topology. These are voice coil motor drives, stepper and DC brush motors, audio amplifiers and even power supply inverters used in uninterruptable power supplies, just to name a few. The HIP408x family of devices is fabricated using a proprietary Intersil IC process which allows this family to switch at frequencies over 250kHz. Therefore, the HIP408x family is ideal for use in various high frequency converter applications, such as motor drives, switching power amplifiers, and high-performance DC/DC converters. A typical application is shown in Figure 5 on page 3. AN9405 Rev 6.00 Dec 24, 2014

FIGURE 1. HIP4081A SIMPLIFIED APPLICATION DIAGRAM

DUAL HIGH/LOW SWITCHES FOR

FIGURE 2. HIP4081A AS LAMP SWITCH DRIVER

To provide accurate dead-time control for shoot-through avoidance and duty-cycle maximization, two resistors tied to pins HDEL and LDEL provide precise delay matching of upper and lower propagation delays, which are typically only 55ns. The HIP4081A H-Bridge driver has enough voltage margin to meet all SELV (UL classification for operation at £ 42.0V) applications and most Automotive applications where "load dump" capability over 65V is required. This capability makes the HIP408x family a more cost-effective solution for driving N-Channel power MOSFETs than either discrete solutions or other solutions relying on transformer- or opto-coupling gate drive techniques.

The biggest difference between the HIP4080A and the HIP4081A is that the HIP4081A allows separate and individual control of the 4 MOSFET gates, whereas the HIP4080A does not. Also the HIP4081A does not include an internal comparator which can create a PWM signal directly within the HIP4080A.

# **Description of the HIP4081A**

The block diagram of the HIP4081A relating to driving the A-side of the H-Bridge is shown in Figure 4. The blocks associated with each half of the H-Bridge are identical, so the B-side is not shown for simplicity.

The V<sub>CC</sub> and V<sub>DD</sub> terminals on the HIP4081A should be tied together. They were separated within the HIP4081A IC to avoid possible ground loops internal to the IC. Tying them together and providing a decoupling capacitor from the common tie-point to V<sub>SS</sub> greatly improves noise immunity.

## **Input Logic**

The HIP4081A has 4 inputs, ALI, BLI, AHI and BHI, which control the gate outputs of the H-Bridge. The DIS, "Disable," pin disables gate drive to all H-Bridge MOSFETs regardless of the command states of the input pins above. The state of the bias voltage, V<sub>DD</sub>, also can disable all gate drive as discussed in the introduction. With external pull-ups on the high input terminals, AHI and BHI, the bridge can be totally controlled using only the lower input control pins, ALI and BLI, which can greatly simplify the external control circuitry needed to control the HIP4081A. <u>Table 1</u> suggests that the lower inputs ALI and BLI dominate the upper inputs. That is, when one of the lower input is, because the lower will turn on and the upper will remain off.

|          | INPU     | OUTPUT |     |          |          |

|----------|----------|--------|-----|----------|----------|

| ALI, BLI | AHI, BHI | U/V    | DIS | ALO, BLO | AHO, BHO |

| х        | x        | х      | 1   | 0        | 0        |

| 1        | x        | 0      | 0   | 1        | 0        |

| 0        | 1        | 0      | 0   | 0        | 1        |

| 0        | 0        | 0      | 0   | 0        | 0        |

| х        | х        | 1      | Х   | 0        | 0        |

TABLE 1. INPUT LOGIC TRUTH TABLE

NOTE: X signifies that input can be either a "1" or "0".

The input sensitivity of the DIS input pin is best described as "enhanced TTL" levels. Inputs which fall below 1.0V or rise above 2.5V are recognized, respectively, as low level or high level inputs.

# **Propagation Delay Control**

Propagation delay control is a major feature of the HIP4081A. Two identical sub-circuits within the IC delay the commutation of the power MOSFET gate turn-on signals for both A and B sides of the H-Bridge. The gate turn-off signals are not delayed. Propagation delays related to the level-translation function (see section on Level-Translation) cause both upper on/off propagation delays to naturally be longer than the lower on/off propagation delays. Four delay trim sub-circuits are incorporated to better match the H-bridge delays, two for upper delay control and two for lower gate control.

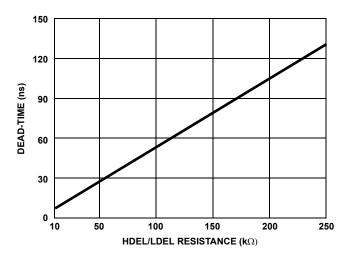

Users can tailor the low-side to high-side commutation delay times by placing a resistor from the HDEL pin to the V<sub>SS</sub> pin. Similarly, a resistor connected from LDEL to V<sub>SS</sub> controls the high-side to low-side commutation delay times of the lower power switches. The HDEL resistor controls both upper commutation delays and the LDEL resistor controls the lower commutation delays. Each of the resistors sets a current which is inversely proportional to the created delay. The delay is added to the falling edge of the "off" pulse associated with the MOSFET, which is being commutated off. When the delay is complete, the "on" pulse is initiated. This has the effect of "delaying" the commanded on pulse by the amount set by the delay, thereby creating dead-time.

Proper choice of resistor values connected from HDEL and LDEL to V<sub>SS</sub> provides a means for matching the commutation dead times whether commutating high-to-low or low-to-high. Values for the resistors ranging from 10k $\Omega$  to 200k $\Omega$  are recommended. Figure 3 shows the dead-time delays obtainable as a function of the resistor values used.

FIGURE 3. MINIMUM DEAD-TIME vs DEL RESISTANCE

## HIP4081A, 80V High Frequency H-Bridge Driver

FIGURE 5. TYPICAL APPLICATION (PWM MODE SWITCHING)

## **Level Translation**

The lower power MOSFET gate drive signals from the propagation delay and control circuits go to amplification circuits which are described in more detail in the "Driver Circuits" section. The upper power MOSFET gate drive signals are directed first to the level translation circuits before going to the upper power MOSFET "Driver Circuits".

The Level-Translation circuit communicate "on" and "off" pulses from the Propagation Delay subcircuit to the upper logic and gate drive sub-circuits which "float" at the potential of the upper power MOSFET source connections. This voltage can be as much as 85V when the bias supply voltage is only 10V (the sum of the bias supply voltage and bus voltages must not exceed 95VDC).

In order to minimize power dissipation in the level-shifter circuit, it is important to minimize the width of the pulses translated because the power dissipation is proportional to the product of switching frequency and pulse energy in joules. The pulse energy in turn is equal to the product of the bus voltage magnitude, translation pulse current and translation pulse duration. To provide a reliable, noise free pulse requires a nominal current pulse magnitude of approximately 3mA. The translated pulses are then "latched" to maintain the "on" or "off" state until another level translation pulse comes along to set the latch to the opposite state. Very reliable operation can be obtained with pulse widths of approximately 80ns. At a switching frequency of even 1.0MHz, with an 80VDC bus potential, the power developed by the level-translation circuit will be less than 0.08W.

# **Charge Pump Circuits**

There are two charge pump circuits in the HIP4081A, one for each of the two upper logic and driver circuits. Each charge pump uses a switched capacitor doubler to provide about  $30\mu A$  to  $50\mu A$  of gate load current. The sourcing current charging capability drops off as the floating supply voltage increases. Eventually the gate voltage approaches the level set by an internal zener clamp, which prevents the voltage from exceeding about 15V, the safe gate voltage rating of most commonly available MOSFETs.

# **Driver Circuits**

Each of the four output drivers are comprised of bipolar high speed NPN transistors for both sourcing and sinking gate charge to and from the MOSFET switches. In addition, the sink driver incorporates a parallel-connected N-channel MOSFET to enable the gate of the power switch gate-source voltage to be brought completely to OV.

The propagation delays through the gate driver sub-circuits while driving 500pF loads is typically less than 10ns. Nevertheless, the gate driver design nearly eliminates all gate driver shoot-through, which significantly reduces IC power dissipation.

## **Application Considerations**

To successfully apply the HIP4081A the designer should address the following concerns:

- · General bias supply design Issues

- Upper bias supply circuit design

- Bootstrap bias supply circuit design

## **General Bias Supply Design Issues**

The bias supply design is simple. The designer must first establish the desired gate voltage for turning on the power switches. For most power MOSFETs, increasing the gate-source voltage beyond 10V yields little reduction in switch drain-source voltage drop.

Overcharging the power switch's gate-source capacitance also delays turn-off, increases MOSFET gate switching losses and increases the power dissipation of the HIP4081A. Overcharging the MOSFET gate-source capacitance also can lead to "shoot-through" (both upper and lower MOSFETs in a single bridge leg find themselves conducting simultaneously), thereby shorting out the high voltage DC. Bias supply voltages close to 12V are optimum for  $V_{DD}$  and  $V_{CC}$ , although the HIP4081A will operate up to 15V.

## **Lower Bias Supply Design**

Since most applications use identical MOSFETs for both upper and lower power switches, the bias supply requirements with respect to driving the MOSFET gates will also be identical. In case switching frequencies for driving upper and lower MOSFETs differ, two sets of calculations must be done; one for the upper switches and one for the lower switches. The bias current budget for upper and lower switches will be the sum of each calculation.

Always keep in mind that the lower bias supply must supply current to the upper gate drive and logic circuits as well as the lower gate drive circuits and logic circuits. This is due to the fact that the low-side bias supplies ( $V_{CC}/V_{DD}$ ) charge the bootstrap capacitors and the charge pumps, which maintain voltage across the upper power switch's gate-source terminals.

Good layout practice and capacitor bypassing technique avoids transient voltage dips of the bias power supply to the HIP4081A. Always place a low ESR (equivalent series resistance) ceramic capacitor adjacent to the IC, connected between the bias terminals V<sub>CC</sub> and V<sub>DD</sub> and the common terminal, V<sub>SS</sub> of the IC. A value in the range of 0.22µF and 0.5µF is usually sufficient.

Minimize the effects of Miller feedback by keeping the source and gate return leads from the MOSFETs to the HIP4081A short. This also reduces ringing, by minimizing the length and the inductance of these connections. Another way to minimize inductance in the gate charge/discharge path, in addition to minimizing path length, is to run the outbound gate lead directly "over" the source return lead. Sometimes the source return leads can be made into a small "ground plane" on the back side of the PC board making it possible to run the outbound gate lead "on top" of the board. This minimizes the "enclosed area"

of the loop, thus minimizing inductance in this loop. It also adds some capacitance between gate and source which shunts out some of the Miller feedback effect.

## **Upper Bias Supply Circuit Design**

Before discussing bootstrap circuit design in detail, it is worth mentioning that it is possible to operate the HIP4081A without a bootstrap circuit altogether. Even the bootstrap capacitor, which functions to supply a reservoir of charge for rapidly turning on the MOSFETs is optional in some cases. In situations where very slow turn-on of the MOSFETs is tolerable, one may consider omitting some or all bootstrap components. Applications such as driving relays or lamp loads, where the MOSFETs are switched infrequently and switching losses are low, may provide opportunities for boot strapless operation. Generally, loads with lots of resistance and inductance are possible candidates.

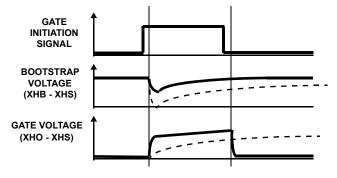

Operating the HIP4081A without a bootstrap diode and/or capacitor will severely slow gate turn-on. Without a bootstrap capacitor, gate current only comes from the internal charge pump. The peak charge pump current is only about 30mA to 50mA. The gate voltage waveform, when operating without a bootstrap capacitor, will appear similar to the dotted line shown in Figure 6.

If a bootstrap capacitor value approximately equal to the equivalent MOSFET gate capacitance is used, the upper bias supply (labeled "bootstrap voltage" in <u>Figure 6</u>) will drop approximately in half when the gate is turned on. The larger the bootstrap capacitance used, the smaller is the instantaneous drop in bootstrap supply voltage when an upper MOSFET is turned on.

Although not recommended, one may employ a bootstrap capacitor without a bootstrap diode. In this case the charge pump is used to charge up a capacitor whose value should be much larger than the equivalent gate-source capacitance of the driven MOSFET. A value of bootstrap capacitance about 10 times greater than the equivalent MOSFET gate-source capacitance is usually sufficient. Provided that sufficient time elapses before turning on the MOSFET again, the bootstrap capacitor will have a chance to recharge to the voltage value that the bootstrap capacitor had prior to turning on the MOSFET. Assuming 2 $\Omega$  of series resistance is in the bootstrap change path, an output frequency of up to should allow sufficient refresh time.

A bootstrap capacitor 10 times larger than the equivalent gatesource capacitance of the driven MOSFET prevents the drop in bootstrap supply voltage from exceeding 10% of the bias supply voltage during turn-on of the MOSFET. When operating without the bootstrap diode the time required to replenish the charge on the bootstrap capacitor will be the same time as it would take to charge up the equivalent gate capacitance from OV. This is because the charge lost on the bootstrap capacitor is exactly equal to the charge transferred to the gate capacitance during turn-on. Note that the very first time that the bootstrap capacitor is charged up, it takes much longer to do so, since the capacitor must be charged from OV. With a bootstrap diode, the initial charging of the bootstrap supply is almost instantaneous, since the charge required comes from the low-side bias supply. Therefore, before any upper MOSFETs can initially be gated, time must be allowed for the upper bootstrap supply to reach full voltage. Without a bootstrap diode, this initial "charge" time can be excessive.

If the switching cycle is assumed to begin when an upper MOSFET is gated on, then the bootstrap capacitor will undergo a charge withdrawal when the source driver connects it to the equivalent gate-source capacitance of the MOSFET. After this initial "dump" of charge, the quiescent current drain experienced by the bootstrap supply is infinitesimal. In fact, the quiescent supply current is more than offset by the charge pump current.

The charge pump continuously supplies current to the bootstrap supply and eventually would charge the bootstrap capacitor and the MOSFET gate capacitance back to its initial value prior to the beginning of the switching cycle. The problem is that "eventually" may not be fast enough when the switching frequency is greater than a few hundred Hz.

## **Bootstrap Bias Supply Circuit Design**

For high frequency applications all bootstrap components, both diodes and capacitors, are required. Therefore, one must be familiar with bootstrap capacitor sizing and proper choice of bootstrap diode.

Just after the switch cycle begins and the charge transfer from the bootstrap capacitor to the gate capacitance is complete, the voltage on the bootstrap capacitor is the lowest that it will ever be during the switch cycle. The charge lost on the bootstrap capacitor will be very nearly equal to the charge transferred to the equivalent gate-source capacitance of the MOSFET as shown in Equation 1.

$$Q_{G} = (V_{BS1} - V_{BS2}) \times C_{BS}$$

(EQ. 1)

where:

- V<sub>BS1</sub> = Bootstrap capacitor voltage just after refresh

- $V_{BS2}$  = Bootstrap voltage immediately after upper turn-on

- C<sub>BS</sub> = Bootstrap Capacitance

- Q<sub>G</sub> = Gate charge transferred during turn-on

Were it not for the internal charge pump, the voltage on the bootstrap capacitor and the gate capacitor (because an upper MOSFET is now turned on) would eventually drain down to zero due to bootstrap diode leakage current and the very small

supply current associated with the level-shifters and upper gate driver subcircuits.

In PWM switch-mode, the switching frequency is equal to the reciprocal of the period between successive turn-on (or turn-off) pulses. Between any two turn-on gate pulses exists one turn-off pulse. Each time a turn-off pulse is issued to an upper MOSFET, the bootstrap capacitor of that MOSFET begins its "refresh" cycle. A refresh cycle ends when the upper MOSFET is turned on again, which varies depending on the PWM frequency and duty cycle. As the duty cycle approaches 100%, the available "off-time", t<sub>OFF</sub> approaches zero. Equation 2 shows the relationship between t<sub>OFF</sub>, f<sub>PWM</sub> and the duty cycle.

$$t_{OFF} = (1 - DC)/f_{PWM}$$

(EQ. 2)

As soon as the upper MOSFET is turned off, the voltage on the phase terminal (the source terminal of the upper MOSFET) begins its descent toward the negative rail of the high voltage bus. When the phase terminal voltage becomes less than the V<sub>CC</sub> voltage, refreshing (charging) of the bootstrap capacitor begins. As long as the phase voltage is below V<sub>CC</sub> refreshing continues until the bootstrap and V<sub>CC</sub> voltages are equal.

The off-time of the upper MOSFET is dependent on the gate control input signals, but it can never be shorter than the dead-time delay setting, which is set by the resistors connecting HDEL and LDEL to  $V_{SS}$ . If the bootstrap capacitor is not fully charged by the time the upper MOSFET turns on again, incomplete refreshing occurs. The designer must insure that the dead-time setting be consistent with the size of the bootstrap capacitor in order to guarantee complete refreshing. Figure 7 illustrates the circuit path for refreshing the bootstrap capacitor.

NOTE: Only "A-side" of H-Bridge Is shown for simplicity. Arrows show bootstrap charging path.

#### FIGURE 7. BOOTSTRAP CAPACITOR CHARGING PATH

The bootstrap charging and discharging paths should be kept short, minimizing the inductance of these loops as mentioned in <u>"Lower Bias Supply Design" on page 4</u>.

## **Bootstrap Circuit Design - An Example**

Equation 1 describes the relationship between the gate charge transferred to the MOSFET upon turn-on, the size of the bootstrap capacitor and the change in voltage across the bootstrap capacitor which occurs as a result of turn-on charge transfer.

The effects of reverse leakage current associated with the bootstrap diode and the bias current associated with the upper gate drive circuits also affect bootstrap capacitor sizing. At the instant that the upper MOSFET turns on and its source voltage begins to rapidly rise, the bootstrap diode becomes rapidly reverse biased resulting in a reverse recovery charge, which further depletes the charge on the bootstrap capacitor. To completely model the total charge transferred during turn-on of the upper MOSFETs, these effects must be accounted for as shown in Equation 3.

$$C_{BS} = \frac{Q_{G} + Q_{RR} + \frac{(I_{DR} + I_{QBS})}{f_{PWM}}}{V_{BS1} - V_{BS2}}$$

(EQ. 3)

Where:

I<sub>DR</sub> = Bootstrap diode reverse leakage current

I<sub>OBS</sub> = Upper supply quiescent current

Q<sub>RR</sub> = Bootstrap diode reverse recovered charge

Q<sub>G</sub> = Turn-on gate charge transferred

f<sub>PWM</sub> = PWM operating frequency

V<sub>BS1</sub> = Bootstrap capacitor voltage just after refresh

V<sub>BS2</sub> = Bootstrap capacitor voltage just after upper turn on

C<sub>BS</sub> = Bootstrap capacitance

From a practical standpoint, the bootstrap diode reverse leakage and the upper supply quiescent current are negligible, particularly since the HIP4081A's internal charge pump continuously sources a minimum of about 30mA. This current more than offsets the leakage and supply current components, which are fixed and not a function of the switching frequency. The higher the switching frequency, the lower is the charge effect contributed by these components and their effect on bootstrap capacitor sizing is negligible, as shown in Equation 3. Supply current due to the bootstrap diode recovery charge component increases with switching frequency and generally is not negligible. Hence the need to use a fast recovery diode. Diode recovery charge information can usually be found in most vendor data sheets.

For example, if we choose a Intersil IRF520R power MOSFET, the data book states a gate charge, Qg, of 12nC typical and 18nC maximum, both at  $V_{DS}$  = 12V. Using the maximum value of 18nC the maximum charge we should have to transfer will be less than 18nC.

Suppose a General Instrument UF4002, 100V, fast recovery, 1A, miniature plastic rectifier is used. The data sheet gives a reverse recovery time of 25ns. Since the recovery current waveform is approximately triangular, the recovery charge can be approximated by taking the product of half the peak reverse current magnitude (1A peak) and the recovery time duration (25ns). In this case the recovery charge should be 12.5nC.

Since the internal charge pump offsets any possible diode leakage and upper drive circuit bias currents, these sources of discharge current for the bootstrap capacitor will be ignored. The bootstrap capacitance required for the example above can be calculated as shown in <u>Equation 4</u>, using <u>Equation 2</u>.

$$C_{BS} = \frac{18nC + 12.5nC}{12.0 - 11.0}$$

(EQ. 4)

Therefore a bootstrap capacitance of  $0.033\mu$ F will result in less than a 1.0V droop in the voltage across the bootstrap capacitor during the turn-on period of either of the upper MOSFETs. If typical values of gate charge and bootstrap diode recovered charge are used rather than the maximum value, the voltage droop on the bootstrap supply will be only about 0.5V

## **Special Gate Drive Considerations**

The dead-time adjustment range provided for in the HIP4081A and HIP4080A parts is usually long enough for driving small to medium size MOSFETs. Often when driving larger MOSFETs, such as RFP25N06 and above, it may be necessary to extend the dead-time adjustment available through adjustment of the RDEL resistors by adding a Schottky diode in parallel with an appropriately sized gate resistor. The gate resistor slows down the turn-on rate of the MOSFET, while the other MOSFET in each of the bridge legs can rapidly turn off through the Schottky diode.

A Schottky diode is recommended in order to keep the drop across it to a minimum which also aids in holding off a MOSFET in the process of turning off during the time that the Miller Effect is trying to turn it back on.

An added protection feature to keep the AHS and BHS pins from flying below ground (VSS) potential when an upper MOSFET turns off is achieved by adding a series resistor between the upper MOSFET source terminals and the AHS and BHS terminals of the driver, respectively. The value of this resistor can usually be in the order of several ohms. Using it, however, provides a means to tailor the turn-off time of the upper MOSFETs in an effort to control how hard the source drives down (and often past) the VSS potential. It is desirable in order to protect the HIP4081A driver that the extent of the undershoot of VSS does not exceed about 4V. Often, the source return resistor recommended above is sufficient to limit the current pulled out of the HIP4081A when the source of the upper MOSFET flies below VSS for a small period of time during the turn-off transient of the upper MOSFETs. Sometimes it is necessary in addition to adding the source return resistor to also add another diode, cathode to AHS and BHS, and anode(s) to VSS close to the VSS terminal of the HIP4081A.

# Power Dissipation and Thermal Design

One way to model the power dissipated in the HIP4081A is by lumping the losses into static losses and dynamic (switching) losses. The static losses are due to bias current losses for the upper and lower sections of the IC and include the sum of the I<sub>CC</sub> and I<sub>DD</sub> currents when the IC is not switching. The quiescent current is approximately 9mA. Therefore with a 12V bias supply, the static power dissipation in the IC is slightly over 100mW.

The dynamic losses associated with switching the power MOSFETs are much more significant and can be divided into the following categories:

- Low voltage gate drive (charge transfer)

- High voltage level-shifter (V-I) losses

- High voltage level-shifter (charge transfer)

In practice, the high voltage level-shifter and charge transfer losses are small compared to the gate drive charge transfer losses.

The more significant low voltage gate drive charge transfer losses are caused by the movement of charge in and out of the equivalent gate-source capacitor of each of the 4 MOSFETs comprising the H-Bridge. The loss is a function of PWM (switching) frequency, the applied bias voltage, the equivalent gate-source capacitance and a minute amount of CMOS gate charge internal to the HIP4081A. The low voltage charge transfer losses are given by Equation 5.

$$P_{SWLO} = f_{PWM} \times (Q_G + Q_{IC}) \times V_{BIAS}$$

(EQ. 5)

The high voltage level-shifter power dissipation is much more difficult to evaluate, although the equation which defines it is simple as shown in Equation 6. The difficulty arises from the fact that the level-shift current pulses,  $I_{ON}$  and  $I_{OFF}$ , are not perfectly in phase with the voltage at the upper MOSFET source terminals, V<sub>SHIFT</sub> due to propagation delays within the IC. These time-dependent source voltages (or "phase" voltages) are further dependent on the gate capacitance of the driven MOSFETs and the type of load (resistive, capacitive or inductive) which determines how rapidly the MOSFETs turn on. For example, the level-shifter I<sub>ON</sub> and I<sub>OFF</sub> pulses may come and go and be latched by the upper logic circuits before the phase voltage even moves. As a result, little level-shift power dissipation may result from the I<sub>ON</sub> pulse, whereas the I<sub>OFF</sub> pulse may have a significant power dissipation associated with it, since the phase voltage generally remains high throughout the duration of the I<sub>OFF</sub> pulse.

$$P_{SHIFT} = \frac{I}{T} \int_{0}^{T} (I_{ON}(t) + I_{OFF}(t)) \times V_{SHIFT}(t) \times dt$$

(EQ. 6)

Lastly, there is power dissipated within the IC due to charge transfer in and out of the capacitance between the upper driver circuits and  $V_{SS}$ . Since it is a charge transfer phenomena, it closely resembles the form of <u>Equation 5</u>, except that the capacitance is much smaller than the equivalent gate-source capacitances associated with power MOSFETs. On the other hand, the voltages associated with the

level-shifting function are much higher than the voltage changes experienced at the gate of the MOSFETs. The relationship is shown in Equation 7.

$$P_{TUB} = C_{TUB} \times V_{SHIFT}^2 \times f_{PWM}$$

(EQ. 7)

The power associated with each of the two high voltage tubs in the HIP4081A derived from Equation 7 is quite small, due to the extremely small capacitance associated with these tubs. A "tub" is the isolation area which surrounds and isolates the high-side circuits from the ground referenced circuits of the IC. The important point for users is that the power dissipated is linearly related to switching frequency and the square of the applied bus voltage.

The tub capacitance in Equation 7 varies with applied voltage,  $V_{SHIFT}$ , making its solution difficult, and the phase shift of the  $I_{ON}$  and  $I_{OFF}$  pulses with respect to the phase voltage,  $V_{SHIFT}$ , in Equation 6 are difficult to measure. Even the  $Q_{IC}$  in Equation 5 is not easy to measure. Hence the use of Equations 5 through 7 to calculate total power dissipation is at best difficult. The equations do, however, allow users to understand the significance that MOSFET choice, switching frequency and bus voltage play in determining power dissipation. This knowledge can lead to corrective action when power dissipation becomes excessive.

Fortunately, there is an easy method which can be used to measure the components of power dissipation rather than calculating them, except for the tiny "tub capacitance" component.

## Power Dissipation, the Easy Way

The average power dissipation associated with the IC and the gate of the connected MOSFETs can easily be measured using a signal generator, an averaging millimeter and a voltmeter.

# **Low Voltage Power Dissipation**

Two sets of measurements are required. The first set uses the circuit of Figure 8 and evaluates all of the low voltage power dissipation components. These components include the MOSFET gate charge and internal CMOS charge transfer losses shown in Equation 5 as well as the quiescent bias current losses associated with the IC. The losses are calculated very simply by calculating the product of the bias voltage and current measurements as performed using the circuit shown in Figure 9. For measurement purposes, the phase terminals (AHS and BHS) for both A and B phases are both tied to the chip common, V<sub>SS</sub> terminal, along with the lower source terminals, ALS and BLS. Capacitors equal to the equivalent gate source capacitance of the MOSFETs are connected from each gate terminal to VSS. The value of the capacitance chosen comes from the MOSFET manufacturers data sheet. Notice that the MOSFET data sheet usually gives the value in units of charge (usually nano-coulombs) for different drain source voltages. Choose the drain source voltage closest to the particular dc bus voltage of interest.

Simply substituting the actual MOSFETs for the capacitors,  $C_L$ , doesn't yield the correct average current because the Miller capacitance will not be accounted for. This is because the drains don't switch using the test circuit shown in Figure 8. Also the gate capacitance of the devices you are using may not represent the maximum values, which only the data sheet will provide.

FIGURE 8. LOW VOLTAGE POWER DISSIPATION TEST CIRCUIT

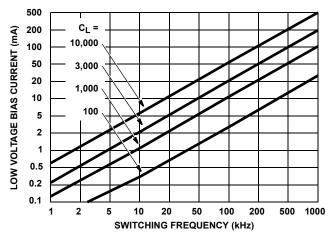

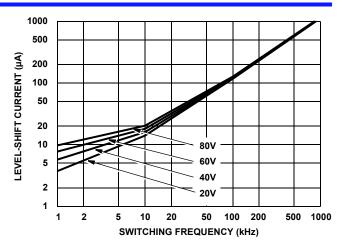

The low voltage charge transfer switching currents are shown in Figure 9 that does not include the quiescent bias current component, which is the bias current which flows in the IC when switching is disabled. The quiescent bias current component is approximately 10mA. Therefore the quiescent power loss at 12V would be 120mW. Note that the bias current at a given switching frequency grows almost proportionally to the load capacitance, and the current is directly proportional to switching frequency, as previously suggested by Equation 5.

## **High Voltage Power Dissipation**

The high voltage power dissipation component is largely comprised of the high voltage level-shifter component as described by Equation 6. All of the difficulties associated with the time variance of the  $I_{ON}$  and  $I_{OFF}$  pulses and the level shift voltage,  $V_{SHIFT}$ , under the integrand in Equation 6 are avoided. For completeness, the total loss must include a small leakage current component, although the latter is usually smaller compared to the level-shifter component. The high voltage power loss calculation is the product of the high voltage bus voltage level,  $V_{BUS}$ , and the average high voltage bus current,  $I_{BUS}$ , as measured by the circuit shown in Figure 10. Averaging meters should be used to make the measurements.

FIGURE 9. LOW VOLTAGE BIAS CURRENT vs FREQUENCY AND LOAD CAPACITANCE

FIGURE 10. HIGH VOLTAGE LEVEL-SHIFT CURRENT TEST CIRCUIT

Figure 11 shows that the high voltage level-shift current varies directly with switching frequency. This result should not be surprising, since Equation 6 can be rearranged to show the current as a function of frequency, which is the reciprocal of the switching period, 1/T. Notice that the current increases somewhat with applied bus voltage. This is due to the finite output resistance of the level-shift transistors in the IC.

FIGURE 11. HIGH VOLTAGE LEVEL-SHIFT CURRENT vs FREQUENCY AND BUS VOLTAGE

# **Layout Problems and Effects**

In fast switching, high frequency systems, proper PC board layout is crucial. To consider PCB layout. The HIP4081A pin configuration encourages tight layout by placing the gate drive output terminals strategically along the right side of the chip (pin 1 is in the upper left-hand corner). This provides for short gate and source return leads connecting the IC with the power MOSFETS.

Always minimize the series inductance in the gate drive loop by running the gate leads to the MOSFETs over the top of the source return leads of the MOSFETs. A double-sided PCB makes this easy. The PC board separates the traces and provides a small amount of capacitance as well as reducing the loop inductance by reducing the encircled area of the gate drive loop. The result is reduced ringing which can similarly reduce drain current modulate in the MOSFET. <u>Table 2</u> summarizes some layout problems which can occur and the corrective action to take.

The bootstrap circuit path should also be kept short. This minimizes series inductance that may cause the voltage on the bootstrap capacitor to ring, slowing down refresh or causing an overvoltage on the bootstrap bias supply.

A compact power circuit layout (short circuit path between upper/lower power switches) minimizes ringing on the phase lead(s) keeping BHS and AHS voltages from ringing excessively below the  $V_{SS}$  terminal which can cause excessive charge extraction from the substrate and possible malfunction of the IC.

#### TABLE 2. LAYOUT PROBLEMS AND EFFECTS

| PROBLEM                                                                                               | EFFECT                                                                                                                                                                                                                           |  |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bootstrap circuit<br>path too long                                                                    | Inductance may cause voltage on bootstrap<br>capacitor to ring, slowing down refresh and/or<br>causing an overvoltage on the bootstrap bias<br>supply.                                                                           |  |

| Lack of tight power<br>circuit layout (long<br>circuit path between<br>upper/lower power<br>switches) | Can cause ringing on the phase lead(s)<br>causing BHS and AHS to ring excessively<br>below the V <sub>SS</sub> terminal causing excessive<br>charge extraction from the substrate and<br>possible malfunction of the IC.         |  |

| Excessive gate lead<br>lengths                                                                        | Can cause gate voltage ringing and<br>subsequent modulation of the drain current<br>and impairs the effectiveness of the sink<br>driver from minimizing the miller effect when<br>an opposing switch is being rapidly turned on. |  |

# **Quick Help Table**

The quick help table has been included to help locate solutions to problems you may have in applying the HIP4081A.

| TABLE 3. | QUICK HELP TABL | Е |

|----------|-----------------|---|

|----------|-----------------|---|

| PROBLEM                                            | EFFECT                                                                                                                                                                                                                                                                  |  |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Low chip bias voltages (V $_{CC}$ and V $_{DD})$   | May cause the IC to go into ${\rm U}/{\rm V}$ trip.                                                                                                                                                                                                                     |  |

| High chip bias voltages (V $_{CC}$ and V $_{DD}$ ) | At $V_{DD}$ voltages above about 12V, the charge pump limiter will begin to operate, in turn drawing heavier $V_{DD}$ current. Above 16V, Breakdown may occur.                                                                                                          |  |

| Bootstrap capacitor(s) too<br>small                | May cause insufficient or soft charge<br>delivery to MOSFETs at turn-on causing<br>MOSFET overheating. Charge pump will<br>pump charge, but possibly not quickly<br>enough to avoid excessive switching<br>losses.                                                      |  |

| Bootstrap capacitor(s) too<br>large                | Dead time may need to be increased in<br>order to allow sufficient bootstrap<br>refresh time. The alternative is to<br>decrease bootstrap capacitance.                                                                                                                  |  |

| R <sub>GATE</sub> too small                        | Smaller values of R <sub>GATE</sub> reduces<br>turn-on/off times and may cause<br>excessive EMI problems. Incorporating a<br>series gate resistor with an anti-parallel<br>diode can solve EMI problem and add to<br>the dead time, reducing shoot-through<br>tendency. |  |

| R <sub>GATE</sub> too large                        | Increases switching losses and MOSFET<br>heating. If anti-parallel diode mentioned<br>above is in backwards, turn-off time is<br>increased, but turn-on time is not,<br>possibly causing a shoot-through fault.                                                         |  |

| Dead time too small                                | Reduces "refresh" time as well as dead time, with increased shoot-through tendency. Try increasing HDEL and LDEL resistors (don't exceed $250k\Omega$ ).                                                                                                                |  |

| HIP4081A IC gets too hot                          | Reduce bus voltage, switching<br>frequency, choose a MOSFET with lower<br>gate capacitance or reduce bias voltage<br>(if it is not below the U/V trip level).<br>Shed some of the low voltage gate<br>switching losses in the HIP4081A by<br>placing a small amount of series<br>resistance in the leads going to the<br>MOSFET gates, thereby transferring<br>some of the IC losses to the resistors. |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lower MOSFETs turn on, but<br>upper MOSFETs don't | Check that the HEN terminal is not tied low inadvertently.                                                                                                                                                                                                                                                                                                                                             |

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard" Computers: office equipment: communications equipment: test and measurement equipment: audio and visual equipment: home electronic appliances; machine tools; personal electronic equipment: industrial robots: etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc. Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics oroducts outside of such specified ranges

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Plea e contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

#### SALES OFFICES

#### **Renesas Electronics Corporation**

http://www.renesas.com

Refer to "http://www.renesas.com/" for the latest and detailed information Renesas Electronics America Inc. 1001 Murphy Ranch Road, Milpitas, CA 95035, U.S.A. Tel: +1-408-432-8888, Fax: +1-408-434-5351 Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 Tel: +1-905-237-2004 Renesas Electronics Europe Limited Dukes Meadow, Miliboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tei: +44-1628-651-700, Fax: +44-1628-651-804 Renesas Electronics Europe GmbH Arcadiastrasse 10, 40472 Düsseldorf, Germar Tel: +49-211-6503-0, Fax: +49-211-6503-1327 Renesas Electronics (China) Co., Ltd. Room 1709 Quantum Plaza, No.27 ZhichunLu, Haidian District, Beijing, 100191 P. R. China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679 Renesas Electronics (Shanghai) Co., Ltd. Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, 200333 P. R. China Tel: +86-21-2226-0888, Fax: +86-21-2226-0999 Renesas Electronics Hong Kong Limited Unit 1601-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +852-2265-6688, Fax: +852 2886-9022 Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670 Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300 Renesas Electronics Malaysia Sdn.Bhd. Unit 1207, Block B, Menara Amcorp, Amco Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Unit 1207, Block B, Menara Amcorp, Amcorp Tel: +60-3-7955-9390, Fax: +60-3-7955-9510 Renesas Electronics India Pvt. Ltd. No.777C, 100 Feet Road, HAL 2nd Stage, Indiranagar, Bangalore 560 038, India Tel: +91-80-67208700, Fax: +91-80-67208777 Renesas Electronics Korea Co., Ltd. 17F, KAMCO Yangjae Tower, 262, Gangnam-daero, Gangnam-gu, Seoul, 06265 Korea Tei: +822-558-3737, Fax: +822-558-5338