## APPLICATION NOTE

### Introduction

The 82P33x13 Synchronization Management Unit (SMU) for IEEE 1588 and Synchronous Ethernet (SyncE) provides tools to manage timing references, clock sources and timing paths for IEEE 1588 / Precision Time Protocol (PTP) and Synchronous Ethernet (SyncE) based clocks. In its power-up default state the 82P33813 enables certain unused functional blocks that consume power. This application note describes the power dissipation of the 82P33813 in its power-up default state; and it describes how to disable the unused functional blocks and the power dissipation of the device after the unused blocks have been disabled. It also presents the power dissipation of 82P33813 for a typical configuration example.

### **Power-up Default State**

Upon power-up, if there is no external EEPROM available, then the 82P33813 loads its register configurations from the metal defaults. The 82P33813, when configured as a master and with a 12.8MHz oscillator, will exhibit typical power dissipation as shown in Table 1.

Table 1. Typical Power Dissipation for 82P33813 with Power-Up Default Configuration

|             | 3.3V/1.8V (Nominal VDD) |           | 3.63V/1.98V (VDD+10%) |           |

|-------------|-------------------------|-----------|-----------------------|-----------|

| Supply Rail | Measured Current (A)    | Power (W) | Measured Current (A)  | Power (W) |

| IDDA        | 0.322                   | 1.064     | 0.323                 | 1.173     |

| IDDD        | 0.029                   | 0.096     | 0.030                 | 0.109     |

| IDDD1p8     | 0.045                   | 0.080     | 0.050                 | 0.100     |

| IDDDO       | 0.042                   | 0.138     | 0.043                 | 0.157     |

| IDDAO       | 0.116                   | 0.381     | 0.116                 | 0.422     |

| Total:      |                         | 1.759     |                       | 1.962     |

# **Disabling Unused Functional Blocks to Reduce Power Dissipation**

The unused functional blocks in 82P33813 can be disabled and powered down by following the power-down procedure described below either by using the serial interface (I2C/SPI) or by configuring from an external EEPROM after reset:

Set the following control register bits to 1:

Control Register bit 4 at offset address 0x381

Control Register bit 0 at offset addresses 0x330, 0x33C and 0x348

Control Register bit 1 at offset addresses 0x330 and 0x33C

This power-down procedure is automatically implemented by IDT's Timing Commander Software using the 82P33813 personality.

After powering-up in the default state and after implementing the power-down procedure, the 82P33813, when configured as a master and with a 12.8MHz oscillator, will exhibit typical power dissipation as shown in Table 2.

Table 2. Power Dissipation for 82P33813 after Disabling Unused Blocks

|             | 3.3V/1.8V (Nominal VDD) |           | 3.63V/1.98V (VDD+10%) |           |

|-------------|-------------------------|-----------|-----------------------|-----------|

| Supply Rail | Measured Current (A)    | Power (W) | Measured Current (A)  | Power (W) |

| IDDA        | 0.216                   | 0.712     | 0.216                 | 0.784     |

| IDDD        | 0.030                   | 0.098     | 0.029                 | 0.104     |

| IDDD1p8     | 0.049                   | 0.088     | 0.056                 | 0.111     |

| IDDDO       | 0.029                   | 0.096     | 0.031                 | 0.111     |

| IDDAO       | 0.059                   | 0.195     | 0.060                 | 0.217     |

| Total:      |                         | 1.189     |                       | 1.327     |

## Power Dissipation Example for 82P33813 in a Typical Configuration

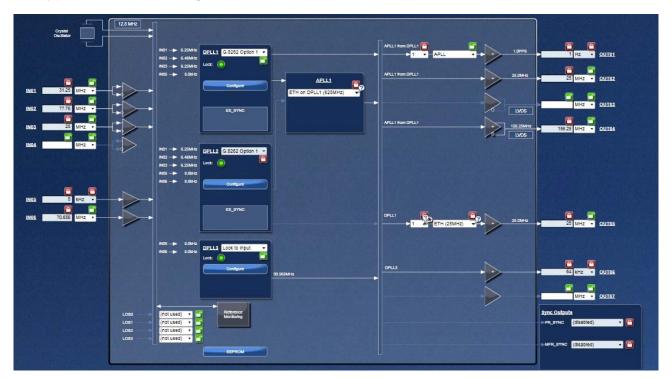

The Timing Commander personality for 82P33813 disables all unused functional blocks to reduce power dissipation. The 82P33813 power dissipation for a specific application will depend on its configuration. Figure 1 shows an example 82P33813 configuration and Table 3 summarizes the power dissipation of this example.

Figure 1. Typical Example Configuration

Figure 2. DPLL Status for the Typical Configuration

Table 3. Power Dissipation for 82P33813 in a Typical Configuration

|             | VDD = 3.3V/1.8V (Nominal VDD) |           | VDD = 3.63V/1.98V (VDD+10%) |           |

|-------------|-------------------------------|-----------|-----------------------------|-----------|

| Supply Rail | Measured Current (A)          | Power (W) | Measured Current (A)        | Power (W) |

| IDDA        | 0.214                         | 0.707     | 0.215                       | 0.779     |

| IDDD        | 0.018                         | 0.058     | 0.019                       | 0.068     |

| IDDD1p8     | 0.059                         | 0.106     | 0.066                       | 0.131     |

| IDDDO       | 0.022                         | 0.072     | 0.022                       | 0.081     |

| IDDAO       | 0.057                         | 0.189     | 0.058                       | 0.210     |

| Total:      |                               | 1.132     |                             | 1.269     |

For questions related to device configurations, please contact IDT application support at <a href="mailto:support-sync@idt.com">support-sync@idt.com</a>

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.