## 8A3xxxx

## Using an External Trigger for Loading/Latching ToD

### Abstract

This document explains in detail the required steps to use the 8A3xxxx CLKs or GPIOs for loading/latching Time of Day (ToD). Both register locations and Timing Commander screenshots are shown. Contact Renesas <u>support</u> for clarifications, errors, or feedback regarding this document.

# Contents

| 1. | Overview |                                                 |   |

|----|----------|-------------------------------------------------|---|

|    | 1.1      | FoD Configuration                               | 2 |

| 2. | ToD      | and GPIO/CLK Configuration                      | 3 |

|    | 2.1      | ToD Write                                       | 3 |

|    | 2.2      | ToD Read                                        | 4 |

| 3. | Fixe     | d Delays in ToD Loading (Write)/Latching (Read) | 5 |

| 4. | Revi     | sion History                                    | 5 |

| 5. | Refe     | rences                                          | 5 |

## **Figures**

| Figure 1. DPLL and TOD Configuration Locations in GUI | 2 |

|-------------------------------------------------------|---|

| Figure 2. GPIO Configurations                         | 3 |

| Figure 3. TOD1 Configuration - Write                  | 4 |

| Figure 4. TOD1 Configuration - Read                   | 5 |

## 1. Overview

The 8A3xxxx supports up to four independent ToD accumulators (DPLL0~3). There are several ways to load/latch each ToD accumulator, including using CLKs or GPIOs. When using CLKs/GPIOs for ToD loading/latching signals, actual values are pre-written or post-read from registers through a serial port. Any of the 8A3xxxx GPIOs can be used (configurable) and any of the CLKs can be used.

There is a read or write inaccuracy when using CLKs/GPIOs. This is because of the different clock domains used for sampling the CLK/GPIO and for loading/latching the ToD accumulator value. The two main contributors are the internal System clock (200MHz) and the ToD accumulator's FoD (Fractional Output Divider) clock (500MHz – 1GHz).

- CLKn as a trigger: uncertainty of a \*compensated ToD value from ToD accumulator is ±(2 x FoD clock period)

- **GPIOn as a trigger:** uncertainty of a \*compensated ToD value from ToD accumulator is ±(2 x FoD clock period) + (1 x system clock period)

\*compensated is (ToD\_value + 2ns) for a write (load) trigger and (ToD\_value - 2ns) for a read (latch) trigger

### **1.1 FoD Configuration**

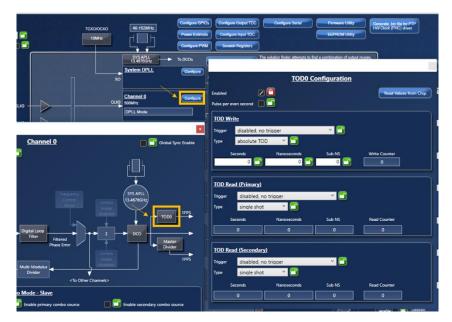

The ToDs are incremented by the associated DPLL0~3's FoD. DPLL0/1 support a FoD frequency of 500MHz to 1GHz and DPLL2/3 support a FoD frequency of 500MHz to 750MHz when working with the ToD accumulators<sup>1</sup>. Configuration of the DPLLs and FoDs is done using the 8A3xxxx TCP and Timing Commander. The ToDs are timed from the FoD clock, but they work separately. One operation does not affect the other. Any value can be stored (write) or latched (read) from a ToD without affecting DPLL functionality. Figure 1 shows where the DPLL configuration and the TOD configuration exist in the GUI.

Figure 1. DPLL and TOD Configuration Locations in GUI

<sup>&</sup>lt;sup>1</sup> All DPLLs support a FoD frequency of 500MHz to 1GHz when the TOD accumulators are not used.

# 2. ToD and GPIO/CLK Configuration

After the configuration of the FoD, you need to program the ToD of the DPLL and associated GPIO, assuming a GPIO is used as the trigger. Below is an example for DPLL1 ToD1 accumulator using GPIO3 as a load/trigger (highlighted numbers can be interchanged with applicable DPLL0~3 and/or GPIO0~15). Register names and how to modify them are shown, followed by Timing Commander screenshots performing the same function.

If a CLK is used as the trigger, Steps 1 through 3 can be skipped.

### 2.1 ToD Write

- 1. Write a 1 to GPIO\_3.GPIO\_OUT\_CTRL\_0.GPIO\_FUNCTION\_EN[0]. Enables GPIO3.

- 2. Write a 1010 to GPIO\_3.GPIO\_OUT\_CTRL\_0.GPIO\_FUNCTION[7:4]. Selects ToD trigger input.

- 3. Write a 1 to GPIO\_3.GPIO\_TOD\_TRIG.TOD\_TRIG\_1[1]. Selects ToD of DPLL1 to be triggered by GPIO3.

| ,<br>]           | 49.152MHz                      | Power Estimate Cont             | gure Output TDC Configure Serial Firmware Utility General<br>gure Ionut TDC EEPROM Utility HW Clo<br>atch Registers |

|------------------|--------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------|

|                  |                                |                                 | GPIO CONFIG                                                                                                         |

| Supply N         | Node: <u>1.8 V</u><br>Function | Pin Description                 | ×                                                                                                                   |

| <u>ario</u><br>0 |                                | user control (direction: input) | GPIO3 CONFIG                                                                                                        |

| 1                | edit                           | user control (direction: input) | CMOS/OD Mode: cmos  CMOS/OD Mode: cmos  CMOS/OD Mode: 2                                                             |

| 3                | edit                           | ToD trigger (in) (Triggers: 1)  | Time of Day Trigger Config                                                                                          |

| 4                |                                | user control (direction: input) | Trigger 0                                                                                                           |

| 6                |                                | user control (direction: input) | Trigger 2                                                                                                           |

Figure 2. GPIO Configurations

- 4. Write a 1 to TOD\_1.TOD\_CFG.TOD\_ENABLE[0]. Enables the TOD1 accumulator.

- 5. Writing to TOD\_WRITE\_1.TOD\_WRITE\_CMD.TOD\_WRITE\_SELECTION[3:0]:

- a. Write a 0110 to TOD\_WRITE\_1.TOD\_WRITE\_CMD.TOD\_WRITE\_SELECTION[3:0]. Selects the GPIO as the trigger.

- b. Write a 0010 to TOD\_WRITE\_1.TOD\_WRITE\_CMD.TOD\_WRITE\_SELECTION[3:0]. Selects the CLK as the trigger. CLK0 is chosen by default. To change the CLK input, write to TOD1\_WRITE\_REF\_INDEX[3:0].

- 6. Write the 88-bit ToD value into TOD\_WRITE\_1.TOD\_WRITE.SECONDS[87:40].NS[39:8].SUBNS[7:0]. Enters the Time of Day.

- 7. Rising Edge Occurrence:

- a. Cause a rising edge to occur on GPIO3. Value is written internally, and trigger select goes back to reset state.

- b. Cause a rising edge to occur on CLK0. Value is written internally, and trigger select goes back to reset state.

- 8. Read the ToD Write Counter at TOD\_WRITE\_1.TOD\_WRITE\_COUNTER.WRITE\_COUNTER[7:0]. This counter increments to indicate completion.

Figure 3. TOD1 Configuration - Write

### 2.2 ToD Read

- 9. Writing to TOD\_READ\_PRIMARY\_1.TOD\_READ\_PRIMARY\_CMD.TOD\_READ\_TRIGGER[3:0]

- a. Write a 0111 to TOD\_READ\_PRIMARY\_1.TOD\_READ\_PRIMARY\_CMD.TOD\_READ\_TRIGGER[3:0]. Selects the GPIO as the trigger. Keep the TOD\_READ\_PRIMARY\_1.TOD\_READ\_PRIMARY\_CMD.TOD\_READ\_TRIGGER\_MODE[4] to single shot. The other option is continuous, which means you do not need to retrigger the next time.

- b. Write a 0011 to TOD\_READ\_PRIMARY\_1.TOD\_READ\_PRIMARY\_CMD.TOD\_READ\_TRIGGER[3:0]. Selects the CLK0 as the trigger. CLK0 is chosen by default. To change the CLK input, write to TOD1\_READ\_PRIMARY\_REF\_INDEX.

- 10. Ensure Steps 1-3 are still active. This step is skipped when using CLKx as a trigger.

- 11. Rising Edge Occurrence:

- a. Cause a rising edge to occur on GPIO3. The 88-bit TOD value is transferred to TOD\_READ\_PRIMARY\_1.TOD\_READ\_PRIMARY and the trigger select goes back to reset state.

- b. Cause a rising edge to occur on CLK0. The 88-bit TOD value is transferred to TOD\_READ\_PRIMARY\_1.TOD\_READ\_PRIMARY and the trigger select goes back to reset state.

#### 12. Read the ToD Read Counter at

TOD\_READ\_PRIMARY\_1.TOD\_READ\_PRIMARY\_COUNTER.READ\_COUNTER[7:0]. This counter increments to indicate completion.

# 3. Fixed Delays in ToD Loading (Write)/Latching (Read)

As previously mentioned there is an uncertainty of 1 x system clock period (200MHz) from the GPIO edge until the ToD value is loaded (written) or latched (read). If a CLK is used as the trigger, the system clock period uncertainty is not present. In addition, there is a fixed delay that may be applied for pre- or post-compensation of the ToD value, which is (ToD\_value + 2ns) for a write (load) trigger and (ToD\_value - 2ns) for a read (latch) trigger.

## 4. Revision History

| Revision Date | Description of Change |

|---------------|-----------------------|

| Oct.27.20     | Initial release       |

### 5. References

8A3xxxx Family Programming Guide v4.7

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.