# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

# Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

"Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# **Application Note**

# 78K0R/Kx3

# Sample Program (I<sup>2</sup>S Bus Interface)

# Interface Between Audio Codec and I<sup>2</sup>S Bus

This document summarizes the operations of the sample program and describes how to use the sample program and how to set and use the I<sup>2</sup>S bus interface in order to use an audio codec connected to the microcontroller. This sample program is used for transferring audio data between the microcontroller and audio codec as well as recording and playing back voices input from a microphone via the I<sup>2</sup>S bus interface. The I<sup>2</sup>C bus interface is used for setting the registers in the audio codec while the SPI interface is used for writing data to or reading data from EEPROM.

# Target devices

78K0R/KE3 microcontroller 78K0R/KF3 microcontroller 78K0R/KG3 microcontroller 78K0R/KH3 microcontroller 78K0R/KJ3 microcontroller

# CONTENTS

| CHAPI | ER I OVERVIEW                                                          | 3     |

|-------|------------------------------------------------------------------------|-------|

| CHAPT | ER 2 CIRCUIT DIAGRAM                                                   | 6     |

| 2.1   | Circuit Diagram                                                        | 6     |

| 2.2   | Peripheral Hardware                                                    | 7     |

| CHAPT | ER 3 SOFTWARE                                                          | 8     |

| 3.1   | File Structure                                                         |       |

| 3.2   | On-Chip Peripheral Functions to Be Used                                | 9     |

| 3.3   | Initial Settings and Operational Overview of Peripheral Hardware to Be |       |

|       | Used                                                                   | 11    |

| 3.4   | Flowcharts                                                             |       |

| 3.5   | I <sup>2</sup> S Bus Interface Format                                  | 21    |

| CHAPT | ER 4 SETTING METHODS                                                   | 23    |

| 4.1   | Settings for Using I <sup>2</sup> S Bus Interface                      | 24    |

| 4.2   | Definitions of Variables and Constants                                 | 41    |

| 4.3   | Initial Settings of Peripheral Hardware to Be Used                     | 45    |

| 4.4   | Main Processing                                                        | 63    |

| 4.5   | INTTM00 Interrupt Servicing                                            | 71    |

| 4.6   | INTCSI00 Interrupt Servicing                                           | 74    |

| 4.7   | INTCSI10 Interrupt Servicing                                           | 81    |

| 4.8   | INTDMA0 Interrupt Servicing                                            |       |

| 4.9   | INTDMA1 Interrupt Servicing                                            |       |

| 4.10  | I <sup>2</sup> C Bus Interface Write Processing                        |       |

| CHAPT | ER 5 RELATED DOCUMENTS                                                 | . 101 |

| APPEN | IDIX A PROGRAM LIST                                                    | . 102 |

| ADDEN | IDIV B BEVICION HICTORY                                                | 400   |

Document No. U19514EJ1V0AN00 (1st edition)

Date Published February 2009 N

- The information in this document is current as of February, 2009. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior

written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may

appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative

purposes in semiconductor product operation and application examples. The incorporation of these

circuits, software and information in the design of a customer's equipment shall be done under the full

responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by

customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

- The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

(Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

M8E 02.11-1

# **CHAPTER 1 OVERVIEW**

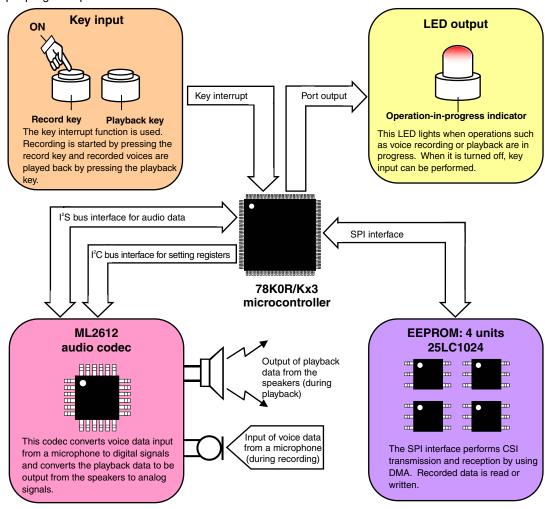

This sample program uses the I<sup>2</sup>S bus interface to transfer audio data between the microcontroller and an audio codec. The LR clock (LRCLK) for selecting whether to use channel L or channel R of the I<sup>2</sup>S bus interface is used in the interval timer mode of the timer array unit (TAU) and is output from TO00. CSI00 of channel 0 of serial array unit 0 (SAU0) is used for outputting the clock used for transferring data (BCLK) and for receiving data (SDOUT), and transmitting data (SDIN).

ML2612 made by OKI Semiconductor is used as the audio codec. The I<sup>2</sup>C bus interface is used for setting the registers in the audio codec and the I<sup>2</sup>S bus interface is used for transferring audio data. When the record key is pressed, the audio codec receives the voice data input from a microphone and saves the data to EEPROM. When the playback key is pressed, the recorded data is transmitted to the audio codec and the output as sound from the speakers. The SPI interface between the microcontroller and EEPROM uses CSI10 of channel 2 of serial array unit 0 (SAU0) to continuously perform CSI transmission or reception by using the DMA controller. Whether recording or playback is in progress is indicated by an LED (operation-in-progress indicator) to which a signal is output from P72.

In this sample program, voices are recorded and played back by using an audio codec IC applied to the I<sup>2</sup>S bus interface. Note, however, that voices can also be recorded and played back solely by the microcontroller by using the ADPCM-SP library.

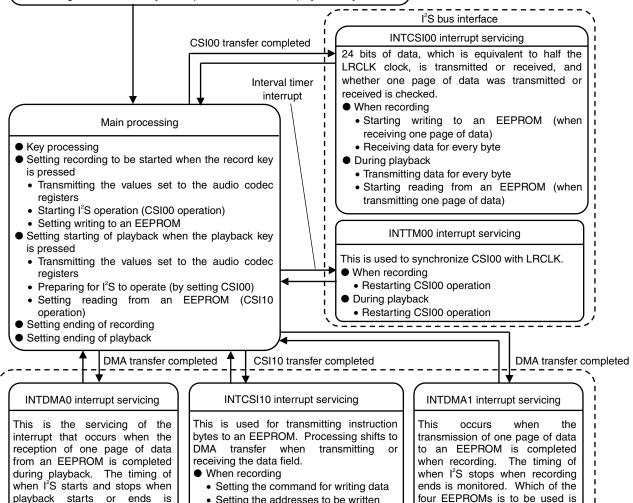

### [Operational overview]

Sample program operations are summarized below.

The sample program processing is summarized below.

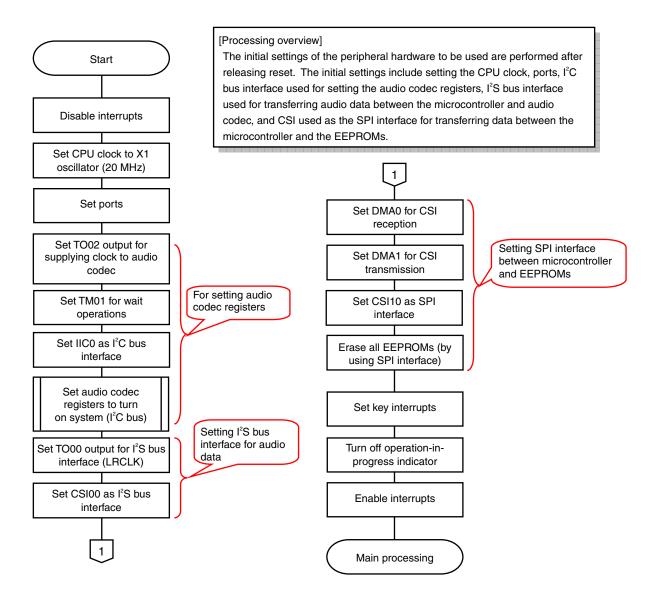

# (1) Main initial settings for peripheral hardware

The main initial settings for the peripheral hardware to be used are described below.

- Disabling interrupts

- Setting the CPU or peripheral hardware clock frequency to the X1 oscillation clock (when used at 20 MHz)

- Setting ports

- Setting the audio codec

- Supplying a clock to the audio codec

- Setting a timer for inserting waits in the program

- Outputting a reset signal to the audio codec

- Setting the I<sup>2</sup>C interface used for setting registers

- Turning on the system by setting the registers in the audio codec

- Setting the I<sup>2</sup>S bus interface used for the audio data of the audio codec

- Using TO00 output (16 kHz) for setting the output of LRCLK

- Setting CSI00

- Setting the SPI interface of EEPROM

- Setting CSI10 for transmitting and receiving data

- Setting DMA0 for reception and DMA1 for transmission

- Erasing all EEPROMs (all 0FFH)

- Starting key data retrieval

- Enabling interrupts

# (2) Main processing

The main processing is described below.

- Key processing

- · Setting start of recording

- Setting start of playback

- Setting termination of recording

- Setting termination of playback

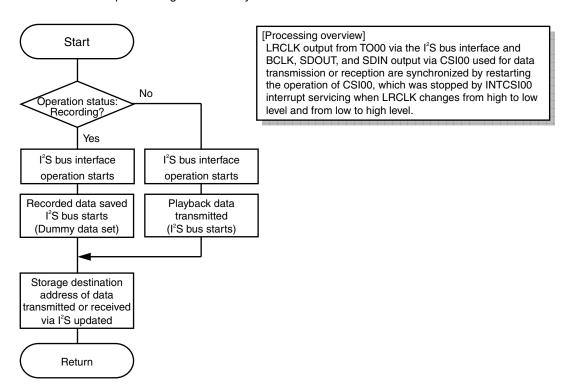

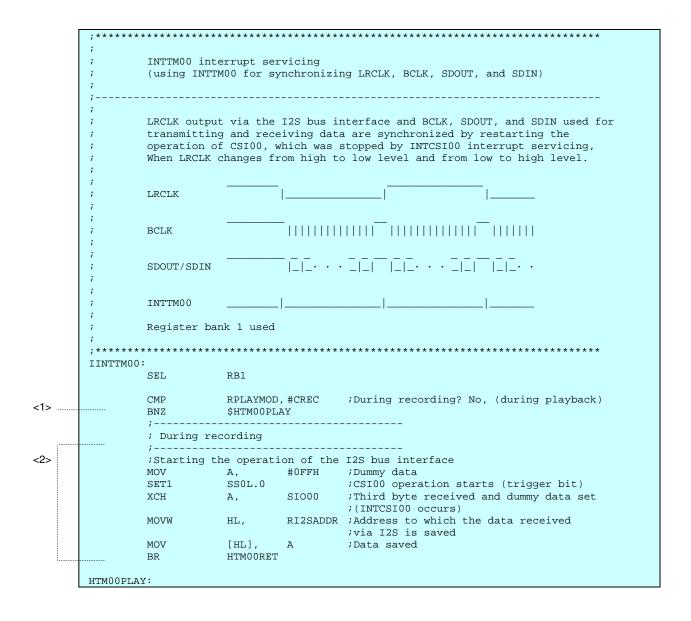

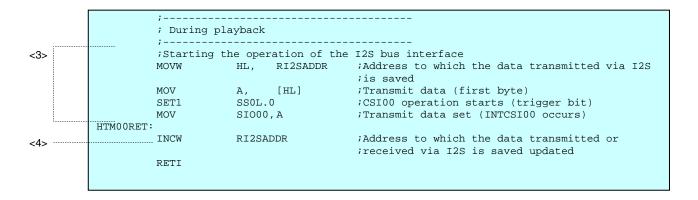

# (3) Main INTTM00 interrupt servicing (using INTTM00 for synchronizing LRCLK, BCLK, SDOUT, and SDIN)

In INTTM00 interrupt servicing, the I<sup>2</sup>S bus interface is started to synchronize LRCLK, BCLK, SDOUT, and SDIN.

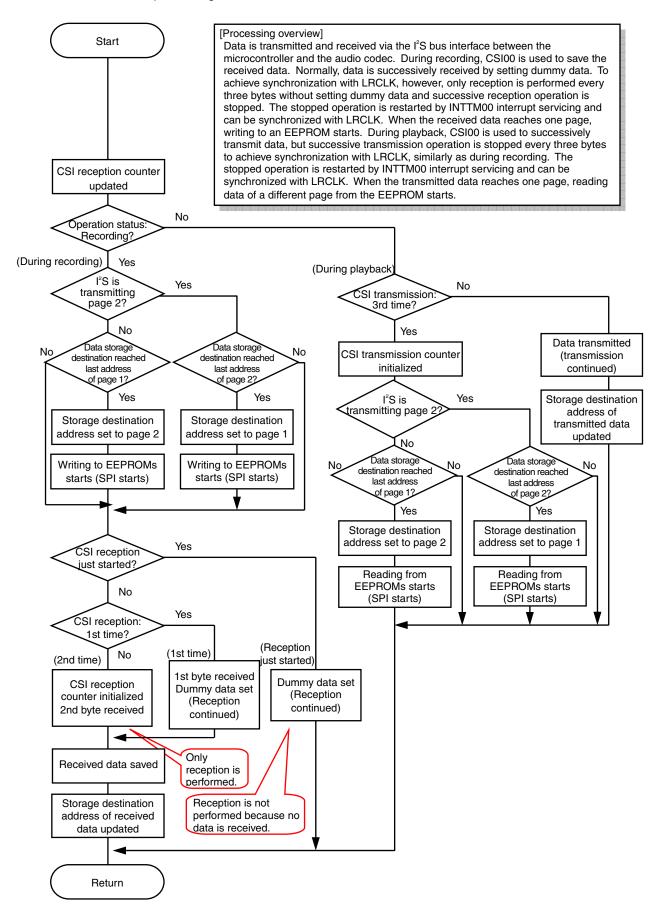

# (4) Main INTCSI00 interrupt servicing (using INTCSI00 for CSI transmission or reception)

The main INTCSI00 interrupt servicing is described below.

- Transmitting or receiving data via the I<sup>2</sup>S bus interface

- Saving the received data

- Starting writing to EEPROM

- Starting reading from EEPROM

Application Note U19514EJ1V0AN

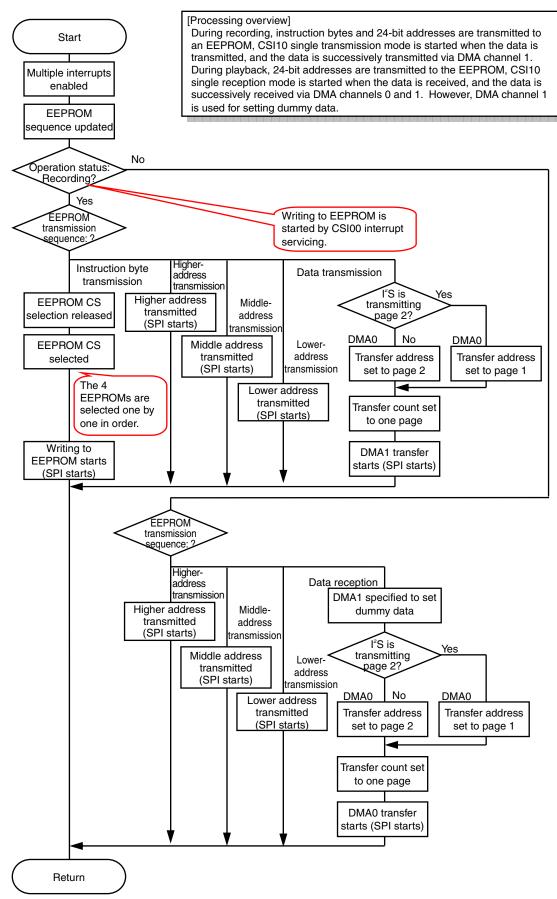

# (5) Main INTCSI10 interrupt servicing (using INTCSI10 for CSI transmission or reception)

The main INTCSI10 interrupt servicing is described below.

- Transmitting instruction bytes to EEPROM

- Transmitting 24-bit addresses to EEPROM

- Starting receiving data from EEPROM by using DMA0 or DMA1

- Starting transmitting data to EEPROM by using DMA1

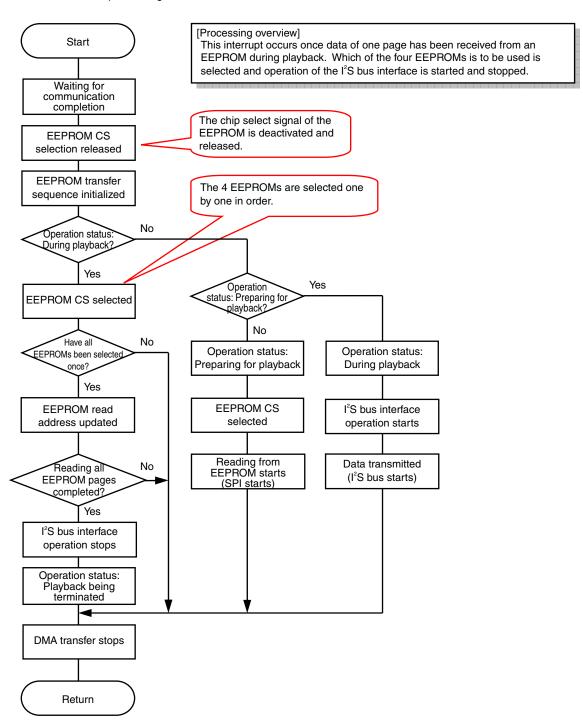

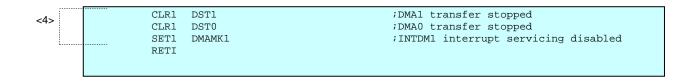

# (6) Main INTDMA0 interrupt servicing (using INTDMA0 for CSI reception)

The main INTDMA0 interrupt servicing is described below.

- Starting reading from EEPROM

- Starting the I2S bus interface

- Selecting EEPROM

- Stopping the I<sup>2</sup>S bus interface

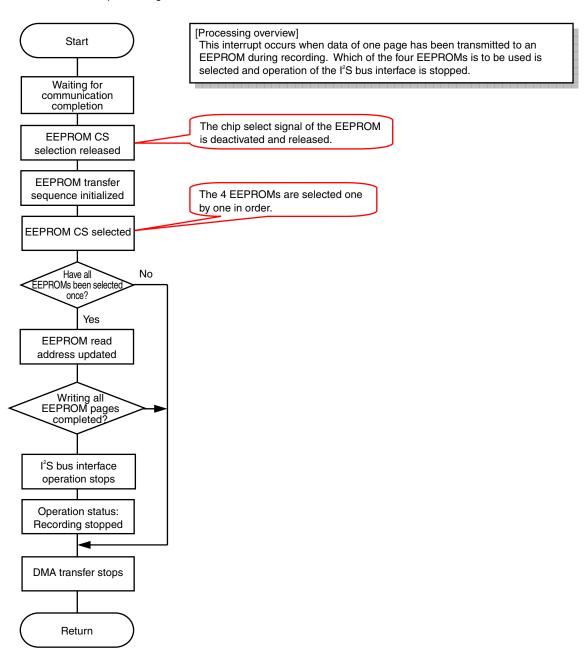

# (7) Main INTDMA1 interrupt servicing (using INTDMA1 for CSI transmission)

The main INTDMA1 interrupt servicing is described below.

- Selecting EEPROM

- Stopping the I2S bus interface

# **CHAPTER 2 CIRCUIT DIAGRAM**

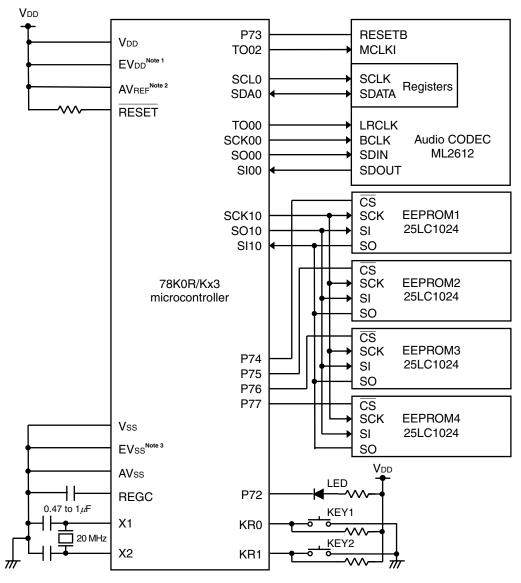

This chapter describes the circuit diagram when using this sample program as well as the peripheral hardware.

# 2.1 Circuit Diagram

The circuit diagram is shown below.

Notes 1. This is EVDD0 and EVDD1 in the 78K0R/KG3, 78K0R/KH3, and 78K0R/KJ3 microcontrollers.

- 2. This is AVREF0 and AVREF1 in the 78K0R/KF3, 78K0R/KG3, 78K0R/KH3, and 78K0R/KJ3 microcontrollers.

- 3. This is EVsso and EVss1 in the 78K0R/KG3, 78K0R/KH3, and 78K0R/KJ3 microcontrollers.

# Cautions 1. Use the microcontroller within a voltage range of 2.7 V $\leq$ VDD $\leq$ 3.6 V.

- 2. Make the potential of the AVss pin the same as that of EVss and Vss, and directly connect the pin to GND.

- 3. Make the potential of EVDD the same as that of VDD.

- 4. Connect REGC to Vss via a capacitor (0.47 to 1  $\mu$ F).

- 5. Leave all unused port pins other than those shown in the circuit open, because they function as output ports.

# 2.2 Peripheral Hardware

The following peripheral hardware is used.

# (1) ML2612 audio codec made by OKI Semiconductor

This audio codec is used for inputting voice data input from a microphone and outputting voice data to be output from the speakers.

# (2) 25LC1024 EEPROMs (EEPROM1, EEPROM2, EEPROM3, EEPROM4)

These EEPROMs are used for saving voice data.

# (3) Keys (key 1, key 2)

The keys are used as inputs for controlling the starting of recording and playback.

# (4) LED

An LED is used to indicate the status when key input is disabled during recording and playback.

The following pin functions are used.

|            | Shared Pin                                                                                                        |                |  |  |  |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|--|--|

| Name       | Name Function                                                                                                     |                |  |  |  |  |  |

| P73        | Resets the ML2612 audio codec.                                                                                    | KR3            |  |  |  |  |  |

| TO02       | Supplies the master clock to the ML2612 audio codec.                                                              | P17/TI02       |  |  |  |  |  |

| SCL0       | Outputs the I <sup>2</sup> C bus interface clock to the registers of the ML2612 audio codec.                      | P60            |  |  |  |  |  |

| SDA0       | Outputs or inputs data for the I <sup>2</sup> C bus interface from or to the registers of the ML2612 audio codec. | P61            |  |  |  |  |  |

| TO00       | Outputs the LR clock for the I <sup>2</sup> S bus interface of the ML2612 audio codec.                            | P01            |  |  |  |  |  |

| SCK00      | Outputs the bit clock for the I <sup>2</sup> S bus interface of the ML2612 audio codec.                           | P10/SCL10      |  |  |  |  |  |

| SI00       | Inputs the data for the I <sup>2</sup> S bus interface of the ML2612 audio codec.                                 | P11/RxD0       |  |  |  |  |  |

| SO00       | Outputs the data for the I <sup>2</sup> S bus interface of the ML2612 audio codec.                                | P12/TxD0       |  |  |  |  |  |

| P74 to P77 | Output a chip select signal from the 25LC1024 EEPROMs. (4 EEPROMs are used.)                                      | P74 to P77     |  |  |  |  |  |

| SCK10      | Outputs the clock for the SPI interface from the 25LC1024 EEPROMs.                                                | P04/SCL10      |  |  |  |  |  |

| SI10       | Inputs the data for the SPI interface to the 25LC1024 EEPROMs.                                                    | P03/RxD1/SDA10 |  |  |  |  |  |

| SO10       | Outputs the data for the SPI interface to the 25LC1024 EEPROMs.                                                   | P02/TxD1       |  |  |  |  |  |

| P72        | Outputs the data for indicating the operating status to the LED.                                                  | KR2            |  |  |  |  |  |

| KR0        | Functions as input from the playback key.                                                                         | P70            |  |  |  |  |  |

| KR1        | Functions as input from the record key.                                                                           | P71            |  |  |  |  |  |

# **CHAPTER 3 SOFTWARE**

This chapter describes the structure of the compressed files to be downloaded, the peripheral functions of the microcontroller to be used, the initial settings and an operational overview of the peripheral hardware to be used in the sample program, and flowcharts.

# 3.1 File Structure

The structure of the compressed files to be downloaded is described below.

| File Name                                                        | Description                                                                                                             | Compressed Files (zip) |                     |  |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------|--|

|                                                                  |                                                                                                                         | Included               |                     |  |

|                                                                  |                                                                                                                         | 210                    | PM<br>1101<br>11-32 |  |

| main.asm (assembly language version) main.c (C language version) | Source file for the hardware initialization processing, main processing, and interrupt servicing of the microcontroller | Note                   | Note                |  |

| I2sApplication.prw                                               | Workspace file for the integrated development environment PM+                                                           |                        | •                   |  |

| I2sApplication.prj                                               | Project file for the integrated development environment PM+                                                             |                        | •                   |  |

Note The assembly language version includes main.asm and the C language version includes main.c.

Remark

: Only the source file is included.

: The files to be used in the integrated development environment PM+ are included.

# 3.2 On-Chip Peripheral Functions to Be Used

In this sample program, the following peripheral functions incorporated in the microcontroller are used.

• TO00 output of channel 0 of timer array unit 0 (TAU0):

This output is used at 16 kHz for outputting the LR clock for the l<sup>2</sup>S bus interface from the ML2612 audio codec.

• Interval timer of channel 1 of timer array unit 0 (TAU0):

This timer is used in the 5 ms interval timer mode for creating wait time in the program.

• TO02 output of channel 2 of timer array unit 0 (TAU0):

This output is used at 10 MHz for supplying the master clock to the ML2612 audio codec.

• CSI00 of channel 0 of serial array unit 0 (SAU0)

This is used at an 833 kHz transfer speed for inputting or outputting the bit data for the I<sup>2</sup>S bus interface to or from the ML2612 audio codec.

• CSI10 of channel 2 of serial array unit 0 (SAU0)

This is used at a 2.5 MHz transfer speed for inputting or outputting the data for the SPI interface to or from the 25LC1024 EEPROMs.

• Channels 0 (DMA0) and 1 (DMA1) of DMA controller:

These channels are used for transmission and reception via CSI10, which is used as the SPI interface for the 25LC1024 EEPROMs.

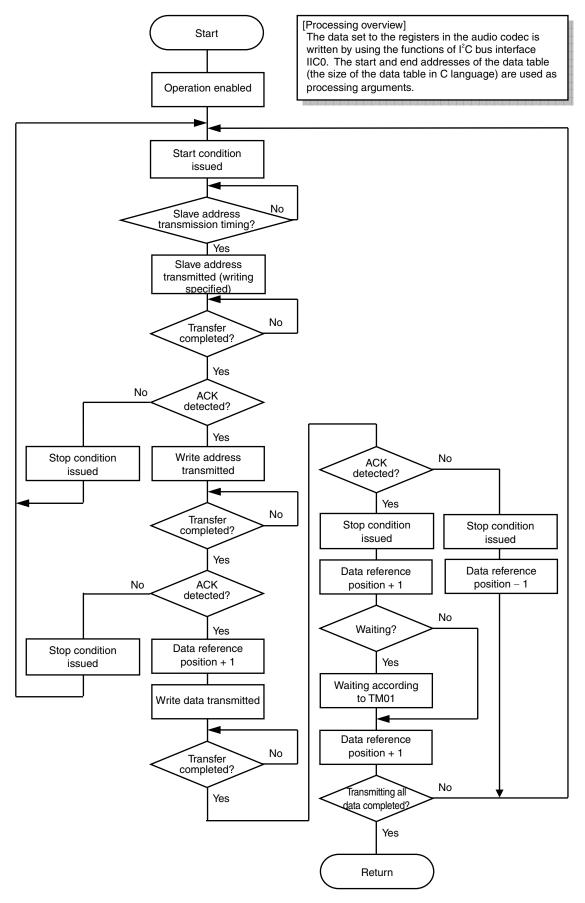

· Serial interface IIC0:

This interface is used for setting the registers of the ML2612 audio codec. It is used at a 208 kHz transfer speed for inputting and outputting data via the I<sup>2</sup>C bus interface.

• Key interrupts:

Key interrupts are used as interrupts for inputs from the record and playback start keys.

# • Pin functions:

The following pin functions are used.

|            | Shared Pin                                                                                                        |                |

|------------|-------------------------------------------------------------------------------------------------------------------|----------------|

| Name       | Function                                                                                                          |                |

| P73        | Resets the ML2612 audio codec.                                                                                    | KR3            |

| TO02       | Supplies the master clock to the ML2612 audio codec.                                                              | P17/TI02       |

| SCL0       | Outputs the I <sup>2</sup> C bus interface clock to the registers of the ML2612 audio codec.                      | P60            |

| SDA0       | Outputs or inputs data for the I <sup>2</sup> C bus interface from or to the registers of the ML2612 audio codec. | P61            |

| TO00       | Outputs the LR clock for the I <sup>2</sup> S bus interface of the ML2612 audio codec.                            | P01            |

| SCK00      | Outputs the bit clock for the I <sup>2</sup> S bus interface of the ML2612 audio codec.                           | P10/SCL10      |

| SI00       | Inputs the data for the I <sup>2</sup> S bus interface of the ML2612 audio codec.                                 | P11/RxD0       |

| SO00       | Outputs the data for the I <sup>2</sup> S bus interface of the ML2612 audio codec.                                | P12/TxD0       |

| P74 to P77 | Output a chip select signal from the 25LC1024 EEPROMs. (4 EEPROMs are used.)                                      | P74 to P77     |

| SCK10      | Outputs the clock for the SPI interface from the 25LC1024 EEPROMs.                                                | P04/SCL10      |

| SI10       | Inputs the data for the SPI interface to the 25LC1024 EEPROMs.                                                    | P03/RxD1/SDA10 |

| SO10       | Outputs the data for the SPI interface to the 25LC1024 EEPROMs.                                                   | P02/TxD1       |

| P72        | Outputs the data for indicating the operating status to the LED.                                                  | KR2            |

| KR0        | Functions as input from the playback key.                                                                         | P70            |

| KR1        | Functions as input from the record key.                                                                           | P71            |

# 3.3 Initial Settings and Operational Overview of Peripheral Hardware to Be Used

In this sample program, the clock frequency is selected, the timer array unit and serial array unit to be used for the I<sup>2</sup>S bus interface are set, serial interface IIC0 to be used for the I<sup>2</sup>C bus interface is set, the serial array unit used for the SPI interface is set, the timer array unit used for wait operations in the program is set, and the key interrupts to be used as record and playback key inputs are set as part of the initial settings of the peripheral hardware to be used.

When the initial settings of the peripheral hardware to be used are complete, the processing shifts to the main processing.

If there is an input from the record key, recording will start. Before starting recording, the audio codec registers must be set via the I<sup>2</sup>C interface. The voices input from a microphone can then be received from the audio codec via the I<sup>2</sup>S bus interface as audio data. Every time data equivalent to one page<sup>Note</sup> is received, that data is transmitted to an EEPROM via the SPI interface. When the four EEPROMs are filled with data transmitted to EEPROM, transmission ends and the audio codec registers are set via the I<sup>2</sup>C interface to stop recording using the audio codec.

If there is an input from the playback key, playing back the recorded data is started. Before starting playback, the audio codec registers must be set via the I<sup>2</sup>C interface. Recorded data equivalent to two pages is received from an EEPROM via the SPI interface, which is transmitted as audio data to the audio codec via the I<sup>2</sup>S bus interface, and then output from the speakers as playback data. Every time data equivalent to one page<sup>Note</sup> is transmitted, playback data is received from an EEPROM via the SPI interface. Once all the data in the four EEPROMs is received, reception ends and the audio codec registers are set via the I<sup>2</sup>C interface to stop playback using the audio codec.

The operation-in-progress indicator (LED) connected to P72 is lit to indicate that the microcontroller is operating during recording or playback.

See the status transition diagram shown on the next page for details.

**Note** A total of six bytes of audio data is transmitted or received in one LR clock, because 24 bits of audio data is included in the range of half the LR clock. The size of one EEPROM page is 256 bytes; but in this sample program, 252 bytes, which is audio data of 42 LR clocks, is assumed to be one page.

### Initial settings of peripheral hardware to be used

- Disabling interrupts

- Setting the CPU or peripheral hardware clock frequency to the X1 oscillation clock (when used at 20 MHz)

- Setting ports

- Enabling interrupts

- For the audio codec registers

- Setting TO02 as the output (10 MHz) for supplying the clock to the audio

- Setting IIC0 as the interface for transmitting the values set to the audio codec reaisters

- Transmitting the values set to the audio codec registers

- For the I2S bus interface between the microcontroller and the audio codec

- Using TO00 for outputting LRCLK (16 kHz)

- Setting CSI00 as the interface for BCLK, SDOUT, and SDIN

- For the SPI bus interface between the microcontroller and the EEPROMs

- Setting CSI10

- Setting DMA0 and DMA1 to be used for transmitting and receiving data (not used when transmitting commands)

- Erasing all EEPROMs (when not using interrupt servicing)

- Enabling KR0 and KR1 key interrupts as the record and playback keys

### Application Note U19514EJ1V0AN

· Setting the addresses to be written

During playback

and DMA1

interrupts)

Starting transmitting data by using

DMA1 (disabling INTCSI10 interrupts)

• Setting the command for reading data

• Starting receiving data by using DMA0

(disabling INTCSI10

· Setting the addresses to be read

selected.

used

Selecting the EEPROM to be

Stopping I<sup>2</sup>S operation

Stopping DMA operation

monitored. Which of the four

EEPROMs is to be used is

Acquiring two pages of data

Selecting the EEPROM to be

before starting I<sup>2</sup>S

Starting I<sup>2</sup>S operation

Stopping I<sup>2</sup>S operation Stopping DMA operation SPI interface --

selected.

used

### 3.4 Flowcharts

The flowcharts of this sample program are shown below.

<Initial settings of the peripheral hardware to be used after releasing reset>

Caution Set the option byte by using the linker options of the RA78K0R. See the RA78K0R Assembler Package User's Manual for information about how to set the option byte.

The option byte is used to set the following.

- Watchdog timer operation

- Setting of LVI when releasing reset (when starting the power supply)

- On-chip debug operations

#### <Main processing> [Processing overview] Start The inputs from the record and playback keys are retrieved by using the key interrupt function. When the record key is pressed, the audio codec registers are set and reception of the audio data input from a microphone via the I2S bus interface is started. When the playback key is pressed, the audio codec registers are set and the recorded data saved to the EEPROMs is read to the internal RAM. Other settings of the audio codec registers are made according to the operation status. No Key input? Yes **INTKR** interrupt request cleared No Operation status Stopped? Yes No Key enabled? Yes No eration status Recording erminated? No No peration status Record key Yes Playback pressed? erminated2 (Recording (Playback Yes starts) starts) Audio codec registers Operation-in-progress Operation-in-progress Audio codec set to end recording indicator turned on indicator turned on registers set to end (I2C bus) playback (I2C bus) Key input disabled Key input disabled Operation status: Operation status: Preparation for playback Key input enabled Recording started Audio codec registers Audio codec registers Operation status: set to start recording Key input is enabled set to start playback Stopped only when the (I2C bus) (I<sup>2</sup>C bus) operation status is Operation-in-progress stopped. The I2S bus interface ready I2S bus interface ready indicator turned off operation-in-progress to receive data to transmit data indicator is set to be turned off when key Writing to EEPROMs Reading from input is enabled. **EEPROMs** set set Reading from I2S bus interface EEPROMs starts operation starts (SPI starts) When recording starts, one page of audio data received via the I2S bus interface is written to an EEPROM. When playback starts, two pages of audio data read from the EEPROMs are set to be transmitted via the I2S bus interface.

# <INTTM00 interrupt servicing for LRCLK synchronization>

### <INTCSI00 interrupt servicing for I2S bus interface>

<INTCSI10 interrupt servicing for SPI interface>

### <INTDMA0 interrupt servicing>

# <INTDMA1 interrupt servicing>

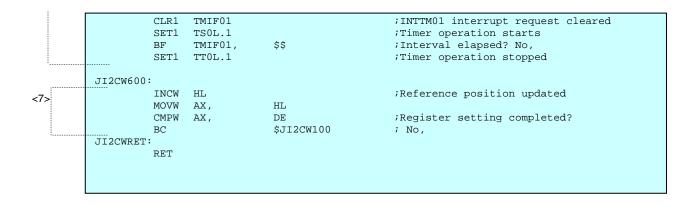

<I2C bus interface write processing for setting audio codec registers>

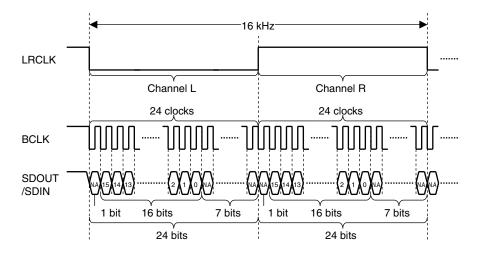

# 3.5 I'S Bus Interface Format

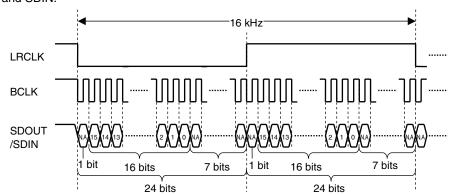

The format of the I2S bus interface is described below.

[Waveform transmitted to or received from the audio codec]

The waveform transmitted to or received from the audio codec is shown below.

# LRCLK:

This is the audio data sampling frequency.

In the program, TO00 output is performed at  $16 \times 2$  kHz intervals by using the interval timer mode of channel 0 of the timer array unit (TAU). Channel 0 of the timer array unit (TAU) can also generate INTTM00 interrupts and synchronized with BCLK, SDOUT, and SDIN.

# BCLK/SDOUT/SDIN:

These are used to input and output audio data.

In the program, successive master transmission or reception is performed by using CSI00 of channel 0 of serial array unit 0 (SAU0). The transfer speed is set to 833 kHz so that three bytes of data can be transferred within half the LRCLK clock. Channel 0 of serial array unit 0 (SAU0) can also generate buffer empty interrupts (INTCSI00) and perform successive transmission and reception.

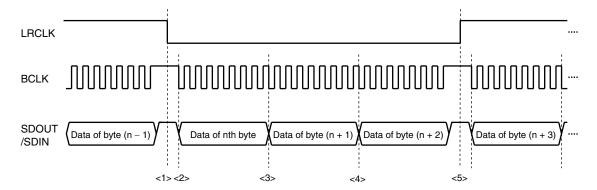

## [Timing in the program]

The timing in the program is described below.

# <1> INTTM00 interrupt timing

- During transmission, the data of the nth byte is written to the transmission and reception buffer register (SIO00) (lower eight bits of the SDR00 register) and successive master transmission of CSI00 is restarted.

- During reception, the transmission and reception buffer register (SIO00) is read and the data of byte (n 1) is saved. Dummy data is set to the transmission and reception buffer register (SIO00) and successive master reception of CSI00 is restarted.

# <2> Timing of first INTCSI00 buffer empty interrupt

- During transmission, data of byte (n + 1) is written to the transmission and reception buffer register (SIO00).

- During reception, the transmission and reception buffer register (SIO00) is not read because it contains no valid data. Dummy data is set to the transmission and reception buffer register (SIO00) to continue successive reception.

# <3> Timing of second INTCSI00 buffer empty interrupt

- During transmission, the data of byte (n + 2) is written to the transmission and reception buffer register (SIO00).

- During reception, the transmission and reception buffer register (SIO00) is read and the data of the nth byte is saved. Dummy data is set to the transmission and reception buffer register (SIO00) to continue successive reception.

## <4> Timing of third INTCSI00 buffer empty interrupt

- During transmission, restart of the operation at <5> is awaited without data being transmitted.

- During reception, only the transmission and reception buffer register (SIO00) is read and the data of byte (n + 1) is saved. Restart of the operation at <5> is awaited without dummy data being set.

Application Note U19514EJ1V0AN

# **CHAPTER 4 SETTING METHODS**

This chapter describes the settings for using the I<sup>2</sup>S bus interface and the initial settings of the peripheral hardware to be used. It also describes the main processing, each interrupt servicing, and the subroutines.

See the 78K0R/Kx3 Sample Program (Initial Settings of Peripheral Hardware to Be Used) LED Lighting Switch Control Application Note for details of how to perform the initial settings.

See each product user's manual (78K0R/KE3, 78K0R/KF3, 78K0R/KG3, 78K0R/KH3, 78K0R/KJ3) for details of how to set the registers.

See the 78K0R Microcontrollers Instructions User's Manual for details about assembler instructions.

# 4.1 Settings for Using I<sup>2</sup>S Bus Interface

In this sample program, the I<sup>2</sup>S bus interface is connected, the TO00 output of channel 0 of the timer array unit (TAU) is set to output the LR clock so that the audio data can be transmitted or received, and CSI00 of channel 0 of serial array unit 0 (SAU0) is set for transmitting or receiving the data.

[Setting of timer array unit (TAU)]

## (1) Controlling the input clock of the timer array unit (TAU)

Peripheral enable register 0 (PER0), which enables the use of peripheral hardware macros, is set so that the timer array unit (TAU) can be used. Power consumption and noise can be reduced by stopping clock supply to unused hardware.

Figure 4-1. Format of Peripheral Enable Register 0 (PER0)

| Address: F00F0I | 1     |        |        |        |        |     |     | _                                                    |

|-----------------|-------|--------|--------|--------|--------|-----|-----|------------------------------------------------------|

| RTCEN DACEN     | ADCEN | IIC0EN | SAU1EN | SAU0EN | TAU1EN | TAU | 0EN |                                                      |

|                 |       |        |        |        |        | 1   | ime | r array unit input clock control (TAU0EN)            |

|                 |       |        |        |        |        |     | _   | top supplying the input clock.                       |

|                 |       |        |        |        |        |     | •   | The SFRs used by the timer array unit cannot be      |

|                 |       |        |        |        |        |     | ١,  | written.                                             |

|                 |       |        |        |        |        |     | •   | The timer array unit is in the reset status.         |

|                 |       |        |        |        |        |     | 1 S | upply the input clock.                               |

|                 |       |        |        |        |        |     | •   | The SFRs used by the timer array unit can be read or |

|                 |       |        |        |        |        |     | ,   | written.                                             |

- Cautions 1. Be sure to set TAU0EN = 1 before setting the timer array unit. If TAU0EN = 0, writing to the timer array unit control register is ignored and only the initial values are read (except timer input select register 0 (TIS0), input switch control register (ISC), noise filter enable register 1 (NFEN1), port mode registers 0, 1, 3, 4, 13, 14 (PM0, PM1, PM3, PM4, PM13, PM14), and port registers 0, 1, 3, 4, 13, 14 (P0, P1, P3, P4, P13, P14)).

- 2. TAU1EN is provided only in the 78K0R/KJ3 and 78K0R/KH3. DACEN is provided only in the 78K0R/KJ3, 78K0R/KH3, 78K0R/KG3, and 78K0R/KF3. Be sure to set non existent bits to "0".

# (2) Selecting the operation clock (CK00)

Timer clock select register 0 (TPS0) is set to select which of the two operation clocks (CK00 or CK01) will be supplied to channels 0, 1, and 2 of the timer array unit (TAU). CK01 is selected by using bits 7 to 4 and CK00 is selected by using bits 3 to 0 of TPS0.

In this sample program, the operation clock CK00 is used by channels 0 and 2 and the operation clock CK01 is used by channel 1. CK00 is used by channel 0 as the LR clock of the I<sup>2</sup>S bus interface.

Figure 4-2. Format of Timer Clock Select Register 0 (TPS0)

Caution Be sure to set bits 15 to 8 to "0".

Remark folk: CPU or peripheral hardware clock frequency

# (3) Operation mode and other settings

Timer mode register 00 (TMR00) is used to select the operation clock (MCK) to be used for the timer array unit (TAU), whether to use the input of the timer clock (TCLK), the valid edge of the timer input pin, and the operation mode for the LR clock of the  $l^2S$  bus interface.

Figure 4-3. Format of Timer Mode Register 00 (TMR00)

Address: F0190H, F0191H

CKS00 0 0 CCS00 MASTER00 STS002 STS001 STS000 CIS001 CIS000 0 0 MD003 MD002

| CKS00 0 0 CCS00 MASTER00 STS002 STS001 STS000 | CIS001 | CI                                                   | S00 | 00 0         | 0 MD003 MD002 MD00                                                       | 01 MD000            |              |

|-----------------------------------------------|--------|------------------------------------------------------|-----|--------------|--------------------------------------------------------------------------|---------------------|--------------|

|                                               |        | 0                                                    |     |              |                                                                          |                     |              |

|                                               |        |                                                      |     | inei<br>03 t | 0 operation mode setting Channel 0 operation                             | TCR count           | Stand-       |

|                                               |        |                                                      |     | 000          |                                                                          | operation           | alone        |

|                                               |        |                                                      |     |              | 3                                                                        |                     | operation    |

|                                               |        | 0                                                    | 0   | 0 1/         | 0 Interval timer mode                                                    | Down-count          | Possible     |

|                                               |        | 0                                                    | 1 ( | 0 1/         | 0 Capture mode                                                           | Up-count            | Possible     |

|                                               |        | 0                                                    | 1   | 1 0          | Event counter mode                                                       | Down-count          | Not          |

|                                               |        |                                                      |     |              |                                                                          |                     | possible     |

|                                               |        |                                                      |     |              | 0 One-count mode                                                         | Down-count          | Possible     |

|                                               |        | 1                                                    | 1 ( | 0 0          | · ·                                                                      | Up-count            | Possible     |

|                                               |        | Ш                                                    |     |              | mode                                                                     |                     |              |

|                                               |        |                                                      |     |              | valid edge selection<br>alling edge                                      |                     | 1            |

|                                               |        | 0                                                    | +   | _            | ising edge                                                               |                     |              |

|                                               |        | 1                                                    | 4   | _            | oth edges (when measurii                                                 | na low-level wic    | lth)         |

|                                               |        | l .                                                  | `   |              | Start trigger: Falling edge                                              | ig ion lovel me     |              |

|                                               |        |                                                      |     |              | Capture trigger: Rising ed                                               | ge                  |              |

|                                               |        | 1                                                    | 1   | 1 B          | oth edges (when measuri                                                  | ng high-level wi    | dth)         |

|                                               |        |                                                      |     |              | Start trigger: Rising edge                                               |                     |              |

|                                               |        |                                                      |     | -            | Capture trigger: Falling ed                                              | ge                  |              |

|                                               |        |                                                      |     |              | 0 start trigger and capture                                              |                     |              |

|                                               |        | 0                                                    | 0   |              | Only software trigger start                                              | is valid (other t   | rigger       |

|                                               |        | _                                                    | 0   | -            | sources are deselected).                                                 | TIOO nin innut fo   | ar both tho  |

|                                               |        | ľ                                                    | U   |              | Use the valid edge of the start and capture triggers.                    | rioo piir iriput it | or bour trie |

|                                               |        | 0                                                    | 1   | 0            | Jse the rising and falling e                                             | edges of the TIC    | 00 pin       |

|                                               |        | input separately for the start and capture triggers. |     |              |                                                                          |                     |              |

|                                               |        | 1                                                    | 0   |              | Jse the master channel in                                                |                     |              |

|                                               |        | L                                                    | Ш   | -            | slave channel is used in a                                               | successive ope      | eration).    |

|                                               |        | _                                                    |     |              | Setting prohibited                                                       |                     |              |

|                                               |        | m                                                    | ode | e ar         | n of whether channel n<br>nd whether channel n is t<br>ve operation mode |                     |              |

|                                               |        | 0                                                    |     |              | ate in standalone mode or                                                |                     | cessive      |

|                                               |        |                                                      | _   |              | ation mode as the slave ch                                               |                     |              |

|                                               |        | 1                                                    |     | •            | ate as the master channel                                                | in the success      | ive          |

|                                               |        | L                                                    |     | •            | ation mode.                                                              |                     |              |

|                                               |        | Cl                                                   |     |              | 0 count clock (TCLK) sele                                                |                     | 14000 1 11   |

|                                               |        | 10                                                   | _   | -            | ation clock MCK specified                                                |                     |              |

|                                               |        | 1                                                    |     |              | edge of the signal input fr                                              |                     | ı            |

|                                               |        | Cl                                                   |     |              | 0 operation clock (MCK) s                                                |                     |              |

|                                               |        | L                                                    |     | •            | ation clock CK00 set by us                                               |                     | _            |

|                                               |        | 1                                                    | U   | per          | ation clock CK01 set by us                                               | sing the PRS re     | egister      |

Caution Be sure to set bits 14, 13, 5, and 4 to "0".

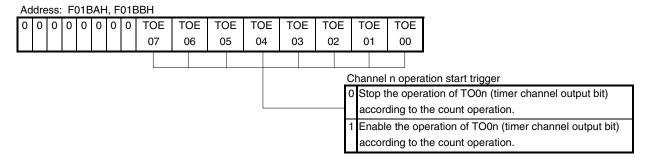

## (4) Enabling timer output

Timer output is enabled for each channel by using timer output enable register 0 (TOE0). For the LR clock of the I<sup>2</sup>S bus interface, timer output is enabled by using the TOE00 bit of channel 0.

Figure 4-4. Format of Timer Output Enable Register 0 (TOE0)

- Cautions 1. Be sure to set bits 15 to 8 of TOE0 to "0".

- 2. TOE07 is provided only in the 78K0R/KJ3, 78K0R/KH3, 78K0R/KG3, and 78K0R/KF3. Be sure to set non existent bits to "0".

**Remark** n: Channel number (n = 0 to 7)

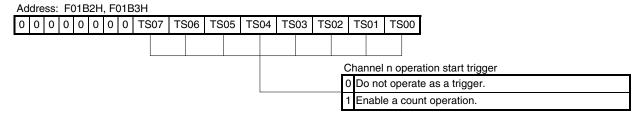

# (5) Enabling start of count operations

Starting timer count operations is enabled for each channel by using timer channel start register 0 (TS0). Timer channel start register 0 (TS0) will be cleared when a timer count operation is enabled, because it is a trigger register.

When the operation of the LR clock of the I2S bus interface is started, the TS00 bit of channel 0 is set to 1.

Figure 4-5. Format of Timer Channel Start Register 0 (TS0)

Caution Be sure to set bits 15 to 8 of TS0 to "0".

**Remark** n: Channel number (n = 0 to 3)

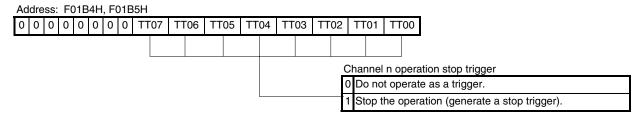

# (6) Enabling stopping of count operations

Timer count operations are stopped for each channel by using timer channel stop register 0 (TT0). Timer channel stop register 0 (TT0) will be cleared when a timer count operation is stopped, because it is a trigger register.

When the operation of the LR clock of the I2S bus interface is stopped, the TT00 bit of channel 0 is set to 1.

Figure 4-6. Format of Timer Channel Stop Register 0 (TT0)

[Setting of serial array unit 0 (SAU0)]

# (1) Controlling the input clock of serial array unit 0 (SAU0)

Peripheral enable register 0 (PER0), which enables the use of peripheral hardware macros, is set so that serial array unit 0 (SAU0) can be used. Power consumption and noise can be reduced by stopping clock supply to unused hardware.

Figure 4-7. Format of Peripheral Enable Register 0 (PER0)

Address: F00F0H

RTCEN DACEN ADCEN IIC0EN SAU1EN SAU0EN TAU1EN TAU0EN

Serial array unit 0 input clock control (SAU0EN)

O Stop supplying the input clock.

• The SFRs used by serial array unit 0 is in the reset status.

Serial array unit 0 is in the reset status.

1 Supply the input clock.

• The SFRs used by serial array unit 0 can be read or written.

- Cautions 1. Be sure to set SAUmEN = 1 before setting serial array unit m. If SAUmEN = 0, writing to the serial array unit m control register is ignored and only the initial values are read (except input switch control register (ISC), noise filter enable register (NFEN0), port input mode register (PIM0), port output mode register (POM0), port mode registers (PM0, PM1), and port registers (P0, P1)).

- 2. Set the SPSm register at least four clocks after setting the PER0 register to "1".

- 3. TAU1EN is provided only in the 78K0R/KJ3 and 78K0R/KH3. DACEN is provided only in the 78K0R/KJ3, 78K0R/KH3, 78K0R/KG3, and 78K0R/KF3. Be sure to set non existent bits to "0".

**Remark** m: Unit number (m = 0, 1)

# (2) Selecting the operation clock (CK00)

Serial clock select register 0 (SPS0) is set to select which of the two operation clocks (CK00 or CK01) will be supplied to both channels 0 and 2 of serial array unit 0 (SAU0). CK01 is selected by using bits 7 to 4 and CK00 is selected by using bits 3 to 0 of SPS0.

In this sample program, the operation clock CK00 is used both by channels 0 and 2. CK00 is used by channel 0 for the I<sup>2</sup>S bus interface.

Address: F0126H, F0127H 0 0 0 0 0 0 0 0 PRS013 PRS012 PRS011 PRS010 PRS003 PRS002 PRS001 PRS000 Operation clock (CK00) selection 0 0 fclk 0 0 0 0 1 fcьк/2 0 1 0 fclk/2<sup>2</sup> 0 1 1 fclк/2<sup>3</sup> 0 1 0 0 fclк/2<sup>4</sup> 0 0 1 0 1 fclk/2⁵ 0 1 0 fclк/2<sup>6</sup> 1 0 1 1 1 fclk/27 fclk/28 0 0 0 0 fclk/2<sup>s</sup> 0 1 0 1 0 fclk/2<sup>10</sup> 1 1 0 1 1 fclk/2<sup>11</sup> 1 1 1 INTTM02 Other than Setting prohibited above Operation clock (CK01) selection (not used in this sample program) 0 0 0 fclk 0 0 0 1 fclk/2 1 0 fclk/2<sup>2</sup> 0 0 0 fclk/23 0 1 1 0 1 0 0 fclk/2⁴ 1 0 1 fclк/2<sup>5</sup> 0 0 1 1 0 fclк/2<sup>6</sup> 1 1 fclk/2<sup>7</sup> 0 1 0 0 fclk/2<sup>8</sup> 1 0 0 0 1 fclk/29 1 0 fclk/2<sup>10</sup> 0 fclk/2<sup>11</sup> 0 1 1 INTTM02 1 1 1 Other than Setting prohibited above

Figure 4-8. Format of Serial Clock Select Register 0 (SPS0)

Cautions 1. Be sure to set bits 15 to 8 to "0".

2. Set the SPS0 register at least four clocks after setting the PER0 register to "1".

Remark folk: CPU or peripheral hardware clock frequency

# (3) Operation mode and other settings

Serial mode register 00 (SMR00) is used to select the operation clock (MCK) to be used for CSI00 of serial array unit 0 (SAU0), whether to use the input of the serial clock (SCK), the start trigger, the operation mode (CSI, UART, I<sup>2</sup>C), and the interrupt source for data transmission and reception via the I<sup>2</sup>S bus interface.

Address: F0110H, F0111H CKC00 CCS00 0 0 0 0 0 STS00 0 SIS000 1 0 0 MD002 MD001 MD000 Channel 0 interrupt source selection Transfer completion interrupt Buffer empty interrupt Channel 0 operation mode setting CSI mode 0 1 UART mode 1 0 Simplified I<sup>2</sup>C mode 1 Setting prohibited Control of inverting the level of data received in channel 0 in UART mode (not used) O Detect the falling edge as the start bit. The input communication data is retrieved as is. Detect the rising edge as the start bit. The input communication data is inverted and then retrieved. Start trigger source selection Only the software trigger is valid (selected in CSI, UART transmission, or simplified I2C mode). 1 Valid edge of the RxD pin (selected during UART reception) Channel 0 transfer clock (TCLK) selection Operation clock MCK is divided according to the ratio specified by using the CKS00 bit. 1 Clock input from the SCK pin (slave transfer in CSI mode) Channel 0 operation clock (MCK) selection O Prescaler output clock CK00 set by using the PRS register Prescaler output clock CK01 set by using the PRS register

Figure 4-9. Format of Serial Mode Register 00 (SMR00)

Caution Be sure to set bits 13 to 9, 7, 4, and 3 to "0" and bit 5 to "1".

# (4) Setting division of the operation clock

Division of the operation clock (MCK) to be used for CSI00 of serial array unit 0 (SAU0) is set by using the higher seven bits of serial data register 00 (SDR00), a 16-bit register. Note that the lower eight bits of serial data register 00 (SDR00) function as the transmission and reception data register (SIO00).

Address: FFF10H, FFF11H (SDR00), FFF12H, FFF13H (SDR01)

Operation clock (MCK) division setting (SDR00[15:9], SDR01[15:9])

O 0 0 0 0 0 0 0 0 MCK/2

0 0 0 0 0 0 1 MCK/4

0 0 0 0 0 1 MCK/8

0 0 0 0 1 MCK/8

0 0 0 1 MCK/2

1 1 1 1 1 1 0 MCK/254

1 1 1 1 1 1 1 MCK/256

Figure 4-10. Format of Serial Data Register 00 (SDR00)

Caution Be sure to set bit 8 to "0".

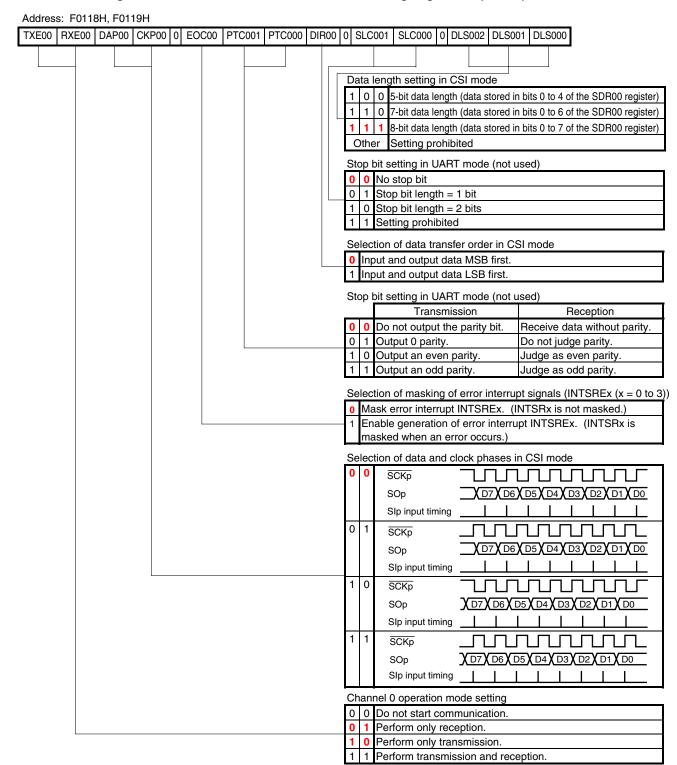

### (5) Setting communication operations

Communication operations are set by using serial communication setting register 00 (SCR00). SCR00 is used to specify settings such as the data transmission and reception mode, the data and clock phases, and the data length.

Figure 4-11. Format of Serial Communication Setting Register 00 (SCR00)

Caution Be sure to set bits 11, 6, and 3 to "0" and bit 2 to "1".

### (6) Setting the initial output level

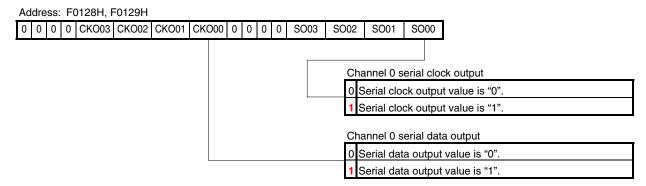

The initial output level of serial array unit 0 (SAU0) in CSI transmission and reception is set by using serial output register 0 (SO0).

For data transmission and reception via the I<sup>2</sup>S bus interface, both the CK00 and SO00 bits of channel 0 are set to 1 in the initial settings of the peripheral hardware to be used.

Figure 4-12. Format of Serial Output Register 0 (SO0)

Caution Be sure to set bits 15 to 12 and 7 to 4 of SO0 to "0". CKO03 and SO03 are provided only in the 78K0R/KJ3 and 78K0R/KH3 microcontrollers. CKO01 and SO01 are provided only in the 78K0R/KJ3, 78K0R/KH3, 78K0R/KG3, and 78K0R/KF3 microcontrollers. When they are not provided, be sure to set CKO01, CKO03, SO01, and SO03 to "1".

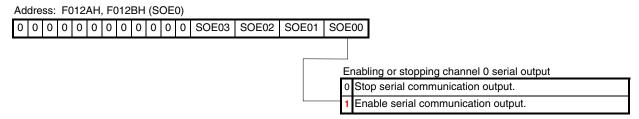

### (7) Enabling or stopping the output of serial communication

Serial communication by CSI00 of serial array unit 0 (SAU0) is enabled or stopped by using serial output enable register 0 (SOE0). The value reflected as a result of communication is output from the serial data output pin for channels for which serial output has been enabled.

For data transmission via the I<sup>2</sup>S bus interface, the SOE00 bit of channel 0 is set to 1 when the output of CSI00 transmission is enabled in the initial settings of the peripheral hardware to be used.

Figure 4-13. Format of Serial Output Enable Register 0 (SOE0)

Caution Be sure to set bits 15 to 4 of SOE0 to "0". SOE03 is provided only in the 78K0R/KJ3 and 78K0R/KH3 microcontrollers. SOE01 is provided only in the 78K0R/KJ3, 78K0R/KH3, 78K0R/KG3, and 78K0R/KF3 microcontrollers. Be sure to set non existent bits to "0".

Application Note U19514EJ1V0AN

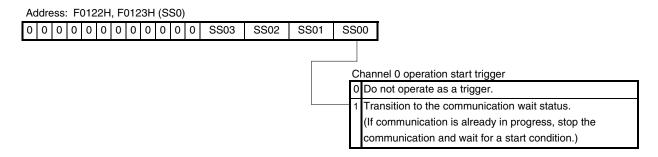

## (8) Enabling start of serial communication and counting

Starting serial communication and counting by CSI00 of serial array unit 0 (SAU0) is enabled for each channel by using serial channel start register 0 (SS0). Serial channel start register 0 (SS0) will be cleared when serial transmission or reception is enabled, because it is a trigger register.

When data transmission or reception via the I<sup>2</sup>S bus interface starts, the SS00 bit of channel 0 (CSI00) is set to 1.

Figure 4-14. Format of Serial Channel Start Register 0 (SS0)

Caution Be sure to set bits 15 to 4 of SS0 to "0".

## (9) Enabling stopping of serial communication and counting

Stopping communication and counting is enabled for each channel by using serial channel stop register 0 (ST0). Serial channel stop register 0 (ST0) will be cleared when serial transmission or reception is stopped, because it is a trigger register.

When data transmission or reception via the I<sup>2</sup>S bus interface stops, the ST00 bit of channel 0 (CSI00) is set to 1.

Address: F0124H, F0125H (ST0)

0 0 0 0 0 0 0 0 0 0 0 0 0 ST03 ST02 ST01 ST00

Channel 0 operation stop trigger

Do not operate as a trigger.

Stop communication.

(Communication stops by retaining the values of the control and shift registers and the statuses of the serial clock I/O pins, serial data output pin, and error flags FEF, PEF, and OVF.)

Figure 4-15. Format of Serial Channel Stop Register 0 (ST0)

Caution Be sure to set bits 15 to 4 of ST0 to "0".

[Example] Enabling support of an I<sup>2</sup>S bus interface, such as the one shown below (same description as in the sample program)

Successive master transmission and reception is executed by using LRCLK in the interval timer mode of channel 0 of the timer array unit (TAU), outputting TO00 at 16  $\times$  2 kHz intervals, and using CSI00 of channel 0 of serial array unit 0 (SAU0) for inputting and outputting the audio data of BCLK, SDOUT, and SDIN.

## Setting procedure

- <1> Performing initial setting of the port output latch for timer array unit 0 (setting P01 to 1)

- <2> Setting the port mode for timer array unit 0 (setting PM01 to 0)

- <3> Supplying the input clock to timer array unit 0 (setting TAU0EN to 1)

- <4> Selecting the operation clock of timer array unit 0 (TPS0)

- <5> Setting the operation mode of channel 0 of timer array unit 0 (TMR00)

- <6> Setting the timer counter of channel 0 of timer array unit 0 (TDR00)

- <7> Supplying the input clock to serial array unit 0 (setting SAU0EN to 1)

- <8> Selecting the operation clock of channel 0 of serial array unit 0 (SPS0)

- <9> Setting the transfer clock of channel 0 of serial array unit 0 (SDR00)

- <10> Setting the operation mode of channel 0 of serial array unit 0 (SMR00)

- <11> Setting the initial data output of channel 0 of serial array unit 0 (SO00)

- <12> Enabling the output of channel 0 of serial array unit 0 (SOE0)

- <13> Performing initial setting of the port output latch for channel 0 of serial array unit 0 (P10, P12)

- <14> Setting the port mode for channel 0 of serial array unit 0 (PM10, PM11, PM12)

- <15> Starting the operation of channel 0 of serial array unit 0 (setting SS00 to 1)

- <16> Clearing the interrupt request flag corresponding to INTCSI00 (setting CSIIF00 to 0)

- <17> Clearing the interrupt mask flag corresponding to INTCSI00 (CSIMK00)

- <18> Executing the EI instruction and enabling interrupts

- <19> Setting the serial data register of serial array unit 0 (SDR00)

- <20> Setting the communication format of channel 0 of serial array unit 0 (SCR00)

- <21> Enabling the timer output of channel 0 of timer array unit 0 (setting TOE00 to 1)

- <22> Clearing the interrupt request flag corresponding to INTTM00 (setting PIF0 to 0)

- <23> Clearing the interrupt mask flag corresponding to INTTM00 (PMK0)

- <24> Starting the operation of CSI00 of channel 0 of serial array unit 0 (setting SS00 to 1)

- <25> Setting the initial output of the port output latch of channel 0 for timer array unit 0 (setting P01 to 0)

- <26> Starting the operation of channel 0 of timer array unit 0 (setting TS00 to 1)

- <27> Setting dummy data to SIO00 of channel 0 of serial array unit 0

Steps <1> to <27> above correspond to steps <1> to <27> on the next page.

Program example in assembly language (same description as in the sample program)

```

···(omitted)···

; Port 0 settings

<1>

MOV

#00011010B

;Output latches of POO, PO2, PO5, and PO6 set

;to low level and those of PO1, PO3, and PO4 set

;to high level

<2>

;P00 to P06 set as output ports

VOM -

PMO,

#10000000B

···(omitted)···

; Timer array unit timer clock selection

<3>

SET1 ! TAUOEN

;Input clock supplied to the timer array unit

<4>-

--- MOV! TPSOL,

#10010000B

;Operation clock selection

; | | | | ++++---- CK00: fCLK

;++++---- CK01: fCLK/2^9

···(omitted)···

<5>

MOVW AX,

#0000000000000000B ;Operation mode setting

||||||||+++- MD003 to MD000: Interval timer mode

||||++---- <Fixed to 00>

|||||++---- CIS001 and CIS000: Unused

;

+++---- STS002 to STS000: Only software trigger start

;

; |

enabled

;

----- MASTER00: Standalone operation

----- CSS00: Macro clock MCK specified by using the

;

;

CKS00 bit

----- <Fixed to 00>

;+----- CKS00: Operating clock CK00 set by using the

PRS register

MVVOM

!TMR00,

AX

WV/OM.

TDR00.

#625-1

;Interval set: 16 kHz output (32 kHz)

<6>

···(omitted)···

-SET1

!SAUOEN

; Input clock of the serial array unit supplied

<7>

;Waiting

NOP

NOP

NOP

NOP

#0000000B

;Operation clock selection: fCLK

<8>

-MOV

!SPSOL,

; | | | | ++++----- PRS003 to PRS000: fCLK

;++++----- PRS013 to PRS010: Unused

WVOM-

SDR00,

;Bits 15 to 7: Transfer clock set (833 kHz)

<9>

#(12-1) shl 9

<10>

#0000000000100001B;Operation mode selected: CSI mode

MOVW AX,

;|||||||||+- MD000: Buffer empty interrupt

||||||++-- MD002 and MD001: CSI mode

||||+++--- <Fixed to 100>

|||||+---- SIS000: Unused

;

;

||+---- <Fixed to 0>

----- STS00: Only software trigger enabled (fixed

;

;

in CSI mode)

; [

----- <Fixed to 00000>

+----- CSS00: Transfer clock set to a clock obtained

;

by dividing operation clock MCK as

;

specified by using the CKS00 bit

; |

----- CKS00: Operation clock set to prescaler

output clock CK00 set by using the

PRS register

MOVW

!SMR00,

AΧ

···(omitted)···

```

```

;Initial data output

<11>

; MOVW AX,

#0000000100000001B

;Setting of initial outputs of the SO and SCK pins

;|||||||++++++---- S00n to S000: Used for transmission

++++---- CKOn to CKOO: Serial clock output of channels

n to 0

; MOVW ! SOO,

AX

···(omitted)···

<12>

SET1 SOEOL. 0

;Output enabled

<13>

SET1

P_SCK00

;SCK00 latch: High level

<14>

CLR1

PM_SCK00

;SCK00 pin output set

<14>-

SET1

PM_SI00

;SI00 pin input set

<13> ··· <14> ···

SET1

P S000

;SO00 latch: High level

CLR1

PM_SO00

;SO00 pin output set

<15>.

SET1

SSOL.0

;CSI00 operation starts (trigger bit)

<16>

CSIIF00

;INTCSI00 interrupt request cleared

CLR1

<17>

CLR1

CSIMK00

;INTCSI00 interrupt servicing enabled

···(omitted)···

<18>....

; Enabling interrupts

...RT

···(omitted)···

···(omitted)···

;Preparation of the I2S bus interface

;CSI00 transmission counter

MOV

RCSI00CNT,#0

#(12-1) shl 9

;Bits 15 to 7: Transfer clock set (833 kHz)

MOVW

SDR00,

<19>

#010000000000111B

MOVW

AX,

;Communication format setting

<20>

|||||||||+++---- DLS002 to DLS000: 8-bit data length

|||||+----<Fixed to 0>

| ++---- SLC001 and SLC000: Unused (fixed to 0)

----- <Fixed to 0>

+----- DIR00: Input and output performed MSB first

----- PTC001 and PTC000: Unused (fixed to 00)

-- EOC00: Unused (fixed to 0)

;

----- <Fixed to 0>

CKP00/DAP00: Phases of data and clock in CSI

;

;

mode selected

[00 selected]

----- TXE00/RXE00: Only transmission performed

;++

MOVW

!SCR00,

#0000000B

MOV

TOOL,

;Initial output set to low level

<21>....

;Operation of TOOO enabled by a count operation

SET1

TOEOL.O

; (LRCLK)

<22>

CLR1

TMIF00

;INTTM00 interrupt request cleared

<23>

-CLR1

TMMK00

;INTTM00 interrupt servicing enabled

···(omitted)···

;Starting I2S operation

<24>

;CSI00 operation starts (trigger bit)

SET1 SSOL.0

<25>

CLR1

P_LRCLK

;LRCLK operation starts

<26>

-SET1 TSOL.0

;TO00 output operation starts (trigger bit)

<27>

SIO00, #0FFH

;Dummy data set (INTCSI00 occurs)

MOV

···(omitted)···

```

Remark <1> to <27> above correspond to steps <1> to <27> in the setting procedure.

Program example in C language (same description as in the sample program)

```

....(omitted)....(Before processing the program).... #pragma directive enabling description of the name of a special function register (SFR)

#pragma SFR

/* Enable description of special function

register (SFR) names */

#pragma EI

/* Enable description of EI instructions */

···(omitted)···(Before processing the program)···

#pragma directive enabling description of the interrupt enable (EI) instruction

Port 0 settings

<1> ...

/* Output latches of P00, P02, P05, and P06 set to

---P0 = 0b00011010;

low level and those of PO1, PO3, and PO4 set to

high level */

--PM0 = 0b10000000;

/* P00 to P06 set as output ports */

<2>

···(omitted)···

/* Timer array unit timer clock selection */

/* Input clock supplied to the timer array unit */

<3>

TAU0EN = 1;

<4>

TPSOL = 0b10010000;

/* Operation clock selection */

||||++++---- CK00: fCLK */

||||++++----- CK01: fCLK/2^9 */

/*

···(omitted)···

TMR00 = 0b0000000000000000; /* Operation mode setting */

<5>

|||||||||||+++---- MD003 to MD000: Interval timer mode */

|||||++----- <Fixed to 00> */

|||||||++----- CIS001 and CIS000: Unused */

| +++---- STS002 to STS000: Only software trigger start

enabled */

----- MASTER00: Standalone operation */

----- CSS00: Macro clock MCK specified by using

the CKS00 bit */

------<Fixed to 00> */

+----- CKS00: Operating clock CK00 set by using

the PRS register */

<6>

-TDR00 = 625-1;

/* Interval set: 16 kHz output (32 kHz) */

···(omitted)···

<7>

SAUOEN = 1;

/* Input clock of the serial array unit supplied */

NOP();

/* Waiting */

NOP();

NOP();

NOP();

SPSOL = 0b0000000;

/* Operation clock selection: fCLK */

<8>

||||++++----- PRS003 to PRS000: fCLK */

++++----- PRS013 to PRS010: Unused */

<9> -

SDR00 = (12-1) << 9; /* Bits 15 to 7: Transfer clock set (833 kHz) */

<10>

SMR00 = 0b0000000000100001; /* Operation mode selected: CSI mode */

|||||||||||||+--- MD000: Buffer empty interrupt */

||||++--- MD002 and MD001: CSI mode */

||||||+++----- <Fixed to 100> */

|||||||+---- SIS000: Unused */

||||+-----<Fixed to 0> */

+----- STS00: Only software trigger enabled

(fixed in CSI mode) */

----- CSS00: Transfer clock set to a clock

obtained by dividing operation clock

MCK as specified by using the CKS00

bit */

----- CKS00: Operation clock set to prescaler

output clock CK00 set by using

the PRS register */

```

```

···(omitted)···

/* Initial data output (at the same time as setting CSI10) */

SOO = 0b0000000100000001; /* Setting of initial outputs of the SO and SCK pins */

|||||||+++++++----- SOOn to SOOO: Used for transmission */

++++++++ CKOn to CKOO: Serial clock output of channels n

to 0 */

<12>

SOE0L.0 = 1;

/* Output enabled */

<13> -

----P SCK00 = 1;

/* SCK00 latch: High level */

---PM_SCK00 = 0;

/* SCK00 pin output set */

<14> -

<14>

-PM_SI00 = 1;

/* SI00 pin input set */

/* SO00 latch: High level */

---P_SO00 = 1;

<13>

-PM_SO00 = 0;

/* S000 pin output set */

<14>

/* CSI00 operation starts (trigger bit) */

<15>

-SS0L.0 = 1;

-CSIIF00 = 0;

/* INTCSI00 interrupt request cleared */

<16>

/* INTCSI00 interrupt servicing enabled */

CSIMK00 = 0;

<17>