# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# 740 Family

740 Family Sample Programs Collection

## Contents

| 1.                                                         | Distinctive Features of 740 Family Instruction Set                                                                                                                                                                                                                                                                                                                           | 2                                                                            |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 2.<br>2.1<br>2.2<br>2.3<br>2.4                             | Effective use of 740 Family MCU Distinctive Instructions<br>Memory-to-Memory Operations<br>Bit Branch Instructions<br>Bit Managing (Set/Reset)<br>Rotate Shift                                                                                                                                                                                                               | 3<br>5<br>7                                                                  |

|                                                            | Basic Processing Program Example<br>RAM Clear<br>Data Transfer (RAM)<br>Data Transfer (ROM address fixed)<br>Data Transfer (ROM address variable)<br>Data Sort<br>16-Bit Data Add (Binary)<br>16-Bit Data Subtract (Binary)<br>16-Bit Data Add (BCD)<br>16-Bit Data Add (BCD)<br>16-Bit Subtract (BCD)<br>16-Bit Data Multiply (Binary)<br>16-Bit Data Divide (Binary)       | . 11<br>. 13<br>. 15<br>. 17<br>. 20<br>. 25<br>. 27<br>. 28<br>. 31<br>. 33 |

| 4.<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8 | Application Program Example.<br>File Handling (transfer)<br>File Handling (exchange)<br>Code Conversion (packed BCD $\rightarrow$ unpacked BCD).<br>Code Conversion (unpacked BCD $\rightarrow$ packed BCD).<br>Code Conversion (BIN $\rightarrow$ BCD).<br>Code Conversion (BCD $\rightarrow$ BIN).<br>SGN Function<br>BCD 12-digit Floating Point Arithmetic Calculations. | . 42<br>. 44<br>. 47<br>. 51<br>. 55<br>. 60<br>. 65                         |

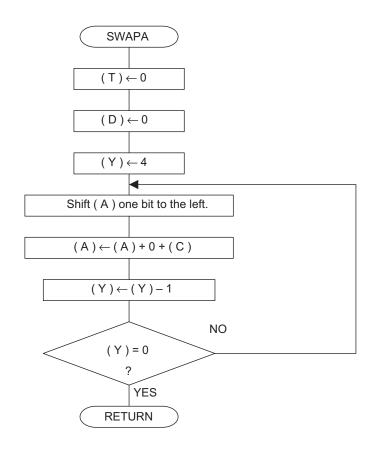

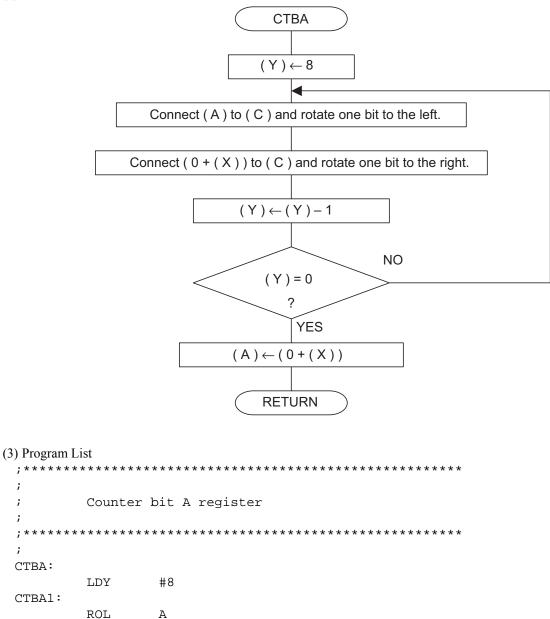

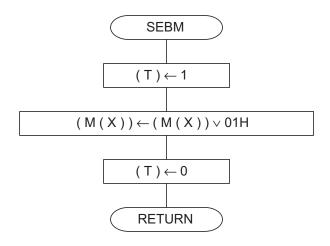

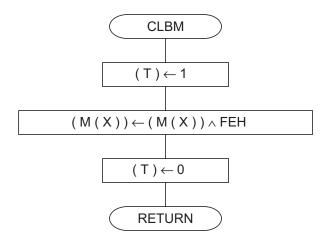

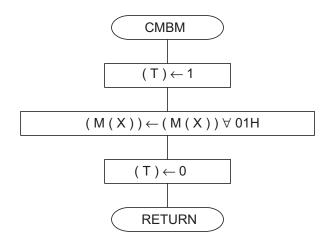

| 5.<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>6.                | Substitute Instruction<br>Swap Accumulator<br>Counter Bit Accumulator<br>Memory Set Bit<br>Memory Clear Bit<br>Memory Bit Reversal<br>Program Usage Notes                                                                                                                                                                                                                    | . 77<br>. 78<br>. 79<br>. 80<br>. 81                                         |

| 5.                                                         |                                                                                                                                                                                                                                                                                                                                                                              |                                                                              |

## 1. Distinctive Features of 740 Family Instruction Set

The 740 Family instruction set offers the following distinctive features.

- (1) An efficient instruction set with many addressing modes allowing the effective use of user program area.

- (2) The same bit set/clear, bit test, and branch instructions can be applied for Accumulator, Memory and I/O area.

- (3) Multiple interrupts allow a variety of servicing of periodic or non-periodic events.

- (4) Powerful indexed addressing performs various byte and table-reference operations.

- (5) Decimal mode does not require any software correction for decimal operations.

- (6) Accumulator does not need to be used in operations using memories and/or I/Os.

## 2. Effective use of 740 Family MCU Distinctive Instructions

## 2.1 Memory-to-Memory Operations

#### (1) Addition (mnemonic ADC)

When X Modified Operation Mode Flag T is "1", the ADC instruction adds the contents of M (X), Memory M and Carry Flag C and stores the results in M (X) and Carry Flag C. At this point, the contents of Accumulator A remain the same, but the status flags are changed. In this case, M (X) represents the contents of the memory at the address indicated by Index Register X.

Example:

| CLC |         | (a) |

|-----|---------|-----|

| SET |         | (b) |

| LDX | #ADDATA | (c) |

| ADC | \$10, X | (d) |

| CLT |         | (e) |

Explanation:

- (a) Set Carry Flag C to "0".

- (b) Set X Modified Operation Mode Flag T to "1".

- (c) Load #ADDATA (example: 70H) to Index Register X.

- (d) Add the contents of the memory at address 70H, contents of address 80H (70H + 10H) and contents of Carry Flag C; store the results in address 70H and Carry Flag C.

(e) Set X Modified Operation Mode Flag T to "0".

For example, if the contents of address 70H are 53H and the contents of address 80H are 21H, the contents of address 70H will be 74H and Carry Flag C will be "0" after execution of the instructions in steps (a) to (e).

(2) Subtraction (mnemonic SBC)

When X Modified Operation Mode Flag T is "1", the SBC instruction subtracts the value of Memory M and the complement of Carry Flag C from the contents of M (X), and stores the results in M (X) and Carry Flag C. At this point, the contents of Accumulator A remain the same, but the status flags are changed. In this case, M (X) represents the contents of the memory at the address indicated by Index Register X.

Example:

| SEC |         | (a) |

|-----|---------|-----|

| SET |         | (b) |

| LDX | #SBDATA | (c) |

| SBC | \$10, X | (d) |

| CLT |         | (e) |

Explanation:

- (a) Set Carry Flag C to "1".

- (b) Set X Modified Operation Mode Flag T to "1".

- (c) Load #SBDATA (example: \$80) to Index Register X.

- (d) Subtract the contents of address 90H (80H + 10H) and the complement of Carry Flag C from the contents of the memory at address 80H; store the results in address 80H and Carry Flag C.

(e) Set X Modified Operation Mode Flag T to "0".

For example, if the contents of address 80H are 53H and the contents of address 90H are 21H, the contents of address 80H will be 32H and Carry Flag C will be "1" after execution of the instructions in steps (a) to (e).

## 2.2 Bit Branch Instructions

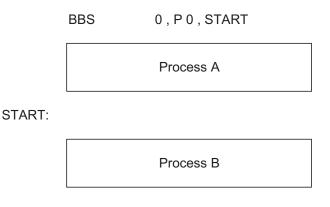

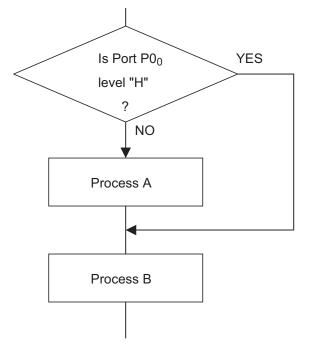

#### (1) Branch On Bit Set (mnemonic BBS)

The BBS instruction tests the designated bit i of Accumulator A or Memory M. If the bit is "1", the program branches to the specified address. The branch address is specified by a relative address. If the bit is "0", the next instruction is executed.

#### Example:

#### **Explanation:**

If bit 0 of Port P0 is "1", the program branches to START. If bit 0 of Port P0 is "0", the program continues on the next instruction.

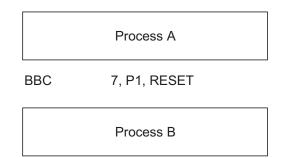

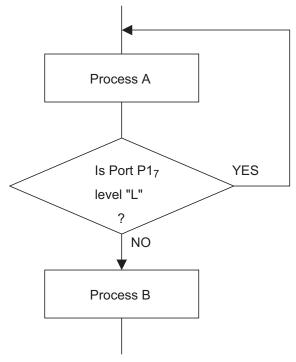

#### (2) Branch On Bit Clear (mnemonic BBC)

The BBC instruction tests the designated bit i of Accumulator A or Memory M. If the bit is "0", the program branches to the specified address. The branch address is specified by a relative address. If the bit is "1", the next instruction is executed.

#### Example:

RESET:

## **Explanation:**

If bit 7 of Port P1 is "0", the program branches to RESET. If bit 7 of Port P1 is "1", the program continues on the next instruction.

## 2.3 Bit Managing (Set/Reset)

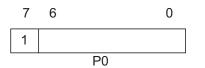

(1) Set Bit (mnemonic SEB)

The SEB instruction sets the contents of the designated bit i of Accumulator A or Memory M to "1".

#### Example:

SEB 7, P0

#### **Explanation:**

The contents of bit 7 of Port P0 are set to "1".

For example, if the contents of Port P0 are 53H, the contents will be D3H after the instruction is executed.

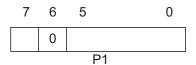

#### (2) Clear Bit (mnemonic CLB)

The CLB instruction sets the contents of the designated bit i of Accumulator A or Memory M to "0".

#### Example:

CLB 6, P1

#### **Explanation:**

The contents of bit 6 of Port P1 are set to "0".

For example, if the contents of Port P1 are 53H, the contents will be 13H after the instruction is executed.

## 2.4 Rotate Shift

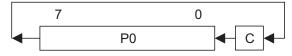

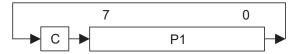

#### (1) Rotate One Bit Left (mnemonic ROL)

The ROL instruction puts the contents of Accumulator A or Memory M and Carry Flag C together as a 9-bit row and rotates the contents one bit to the left. Then, the contents of Carry Flag C are stored in bit 0 of Accumulator A or Memory M, and the contents of bit 7 of Accumulator A or Memory M are stored in Carry Flag C.

#### Example:

ROL P0

#### **Explanation:**

Port P0 is connected to Carry Flag C and their contents are rotated one bit to the left.

For example, if the contents of Port P0 are 53H and Carry Flag C is "1", the contents of Port P0 will be A7H and Carry Flag C will be "0" after the instruction is executed.

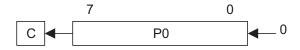

(2) Arithmetic Shift Left (mnemonic ASL)

The ASL instruction shifts all bits of Accumulator A or Memory M one bit to the left. In this case, bit 0 of Accumulator A or Memory M will be "0", and the contents of bit 7 of Accumulator A or Memory M are stored in Carry Flag C.

#### Example:

ASL P0

#### **Explanation:**

All Port P0 bits are shifted one bit to the left.

For example, if the contents of Port P0 are 53H and Carry Flag C is "1", the contents of Port P0 will be A6H and Carry Flag C will be "0" after the instruction is executed.

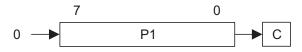

#### (3) Rotate One Bit Right (mnemonic ROR)

The ROR instruction puts the contents of Accumulator A or Memory M and Carry Flag C together as a 9-bit row and rotates the contents one bit to the right. Then, the contents of Carry Flag C are stored in bit 7 of Accumulator A or Memory M, and the contents of bit 0 of Accumulator A or Memory M are stored in Carry Flag C.

#### Example:

ROR P1

#### Explanation:

Port P1 and Carry Flag C are connected and their contents are rotated one bit to the right.

For example, if the contents of Port P1 are 53H and Carry Flag C is "1", the contents of Port P1 will be 29H and Carry Flag C will remain as "1" after the instruction is executed.

#### (4) Logical Shift Right (mnemonic LSR)

The LSR instruction shifts all bits of Accumulator A or Memory M one bit to the right. In this case, bit 7 of Accumulator A or Memory M will be "0", and the contents of bit 0 of Accumulator A or Memory M are stored in Carry Flag C.

#### Example:

LSR P1

#### **Explanation:**

All bits of Port P1 are shifted one bit to the right.

For example, if the contents of Port P1 are 53H and Carry Flag C is "1", the contents of Port P1 will be 29H and Carry Flag C will remain as "1" after the instruction is executed.

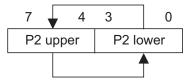

(5) Rotate Right of Four Bits (mnemonic RRF)

The RRF instruction rotates the contents of Memory M four bits to the right. As a result, the contents of the upperorder and lower-order four bits of Memory M are reversed, but the order of the respective four bits does not change.

#### Example:

RRF P2

#### **Explanation:**

The contents of the upper-order and lower-order four bits of Port P2 are reversed.

For example, if the contents of Port P2 are 53H, the contents will be 35H after the instruction is executed.

## 3. Basic Processing Program Example

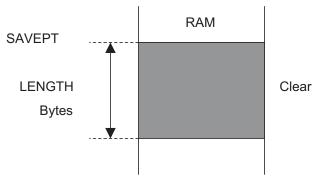

## 3.1 RAM Clear

#### (1) Description

This program sets the area and clears the RAM.

#### (2) Explanation

The program clears LENGTH Bytes of RAM from RAM address SAVEPT.

(4) Program List ;\*\*\*\*\*\*

| ;                   |               |                           |                                         |

|---------------------|---------------|---------------------------|-----------------------------------------|

| ;                   | RAM c         | lear routine              |                                         |

| ;                   |               |                           |                                         |

| ; * * * * * * * * * | * * * * * * * | * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

| ;                   |               |                           |                                         |

| RAM_CLR:            |               |                           |                                         |

|                     | LDX           |                           | #LENGTH ;RAM length                     |

|                     | LDA           | #\$00                     |                                         |

| RAMCL1:             | STA           | SAVEPT-1,X                | ;Clear from SAVEPT                      |

|                     | DEX           |                           | ; -to SAVEPT+LENGTH-1                   |

|                     | BNE           |                           | RAMCL1 ;Clear end ?                     |

|                     | RTS           |                           | ;Yes                                    |

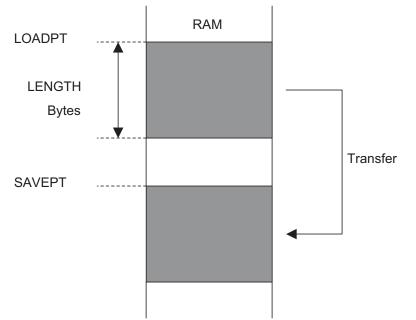

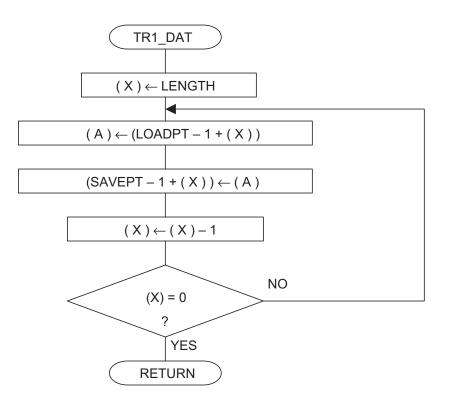

## 3.2 Data Transfer (RAM)

#### (1) Description

Data is transferred within the RAM area.

#### (2) Explanation

LENGTH Bytes of data are transferred from RAM address LOADPT to addresses starting at SAVEPT.

(4) Program List

| ; * * * * * * * | ******* | * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

|-----------------|---------|---------------------------------|-----------------------------------------|

| ;               |         |                                 |                                         |

| ;               | RAM c   | lata transfer r                 | routine                                 |

| ;               |         |                                 |                                         |

| ; * * * * * * * | ******* | * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

| ;               |         |                                 |                                         |

| TR1_DAT:        |         |                                 |                                         |

|                 | LDX     | #LENGTH                         | ;RAM length                             |

| TR1_01:         | LDA     | LOADPT-1,X                      | ;Transfer data from LOADPT              |

|                 | STA     | SAVEPT-1,X                      | ; -to SAVEPT                            |

|                 | DEX     |                                 |                                         |

|                 | BNE     | TR1_01                          | ;Transfer end ?                         |

|                 | RTS     |                                 | ;Yes                                    |

|                 |         |                                 |                                         |

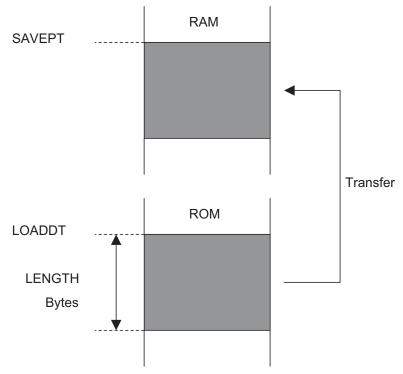

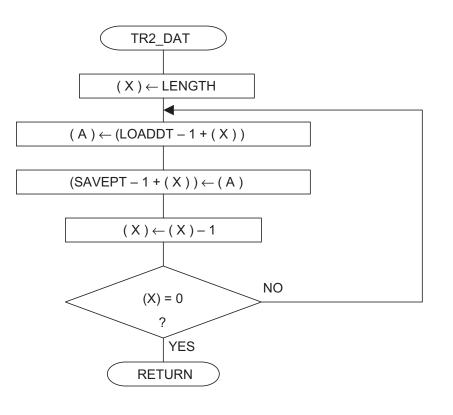

## 3.3 Data Transfer (ROM address fixed)

## (1) Description

Data (address fixed) is transferred from the ROM area.

(2) Explanation

LENGTH Bytes of data are transferred from ROM address LOADDT to continuous RAM addresses, starting at SAVEPT.

(4) Program List

| ;******  | ***** | * * * * * * * * * * * * * *   | * * * * * * * * * * * * * * * * * * * * |

|----------|-------|-------------------------------|-----------------------------------------|

| ;        |       |                               |                                         |

| ;        | ROM c | lata transfer                 | routine(address fixed)                  |

| ;        |       |                               |                                         |

| ;******  | ***** | * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

| ;        |       |                               |                                         |

| TR2_DAT: |       |                               |                                         |

|          | LDX   | #LENGTH                       | ;ROM length                             |

| TR2_01:  | LDA   | LOADDT-1,X                    | ;Transfer data from LOADDT              |

|          | STA   | SAVEPT-1,X                    | ; -to SAVEPT                            |

|          | DEX   |                               |                                         |

|          | BNE   | TR2_01                        | ;Transfer end ?                         |

|          | RTS   |                               | ;Yes                                    |

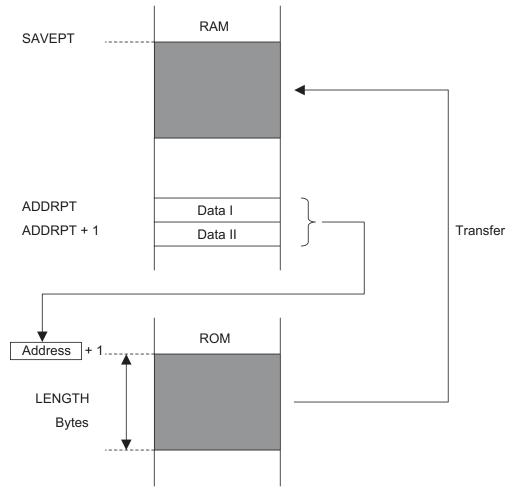

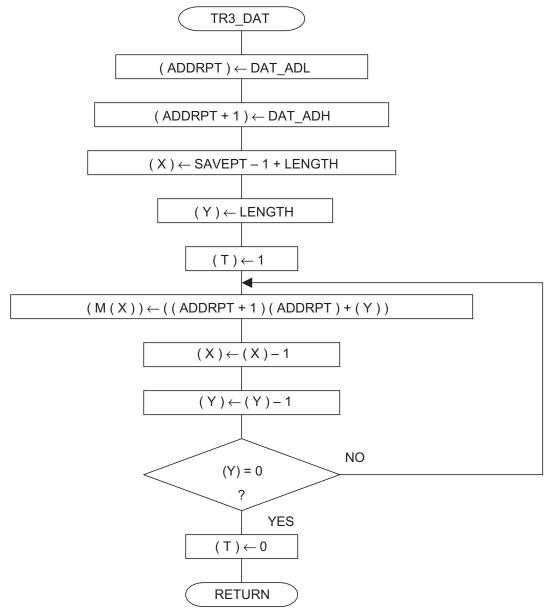

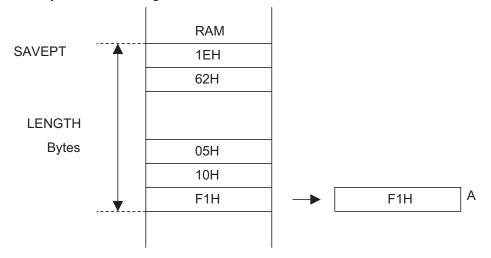

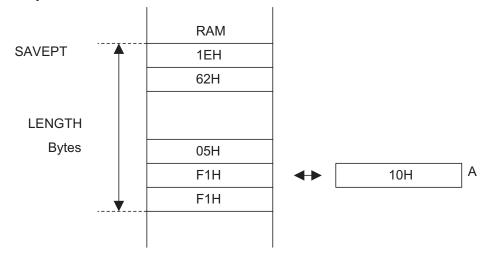

## 3.4 Data Transfer (ROM address variable)

#### (1) Description

Data (address variable) is transferred from the ROM area.

(2) Explanation

LENGTH Bytes of data are transferred to continuous RAM addresses, starting at SAVEPT, from the ROM address +1 specified in the contents of RAM address ADDRPT +1 and ADDRPT.

Note: M (X) represents the memory of the address indicated by Index Register X.

(4) Program List ; ROM data transfer routine(address float) ; ; ; TR3\_DAT: LDM #DAT\_ADL, ADDRPT #DAT\_ADH,ADDRPT+1 LDM ;-----LDX #SAVEPT-1+LENGTH LDY #LENGTH ;ROM length SET ;Transfer data from TR3\_01: (ADDRPT),Y ; -(ADDRPT+1)(ADDRPT)+1 LDA DEX ; -to SAVEPT DEY ; BNE TR3\_01 ;Transfer end ? CLT;Yes RTS

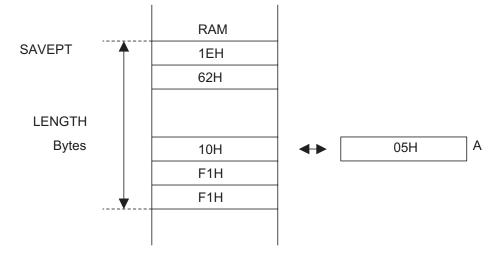

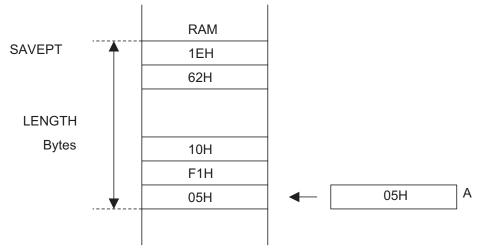

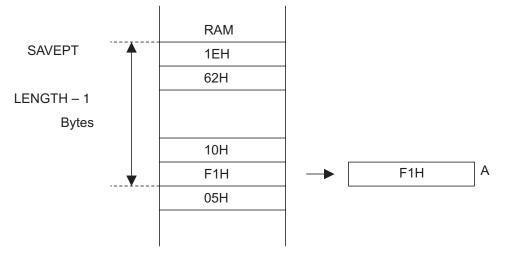

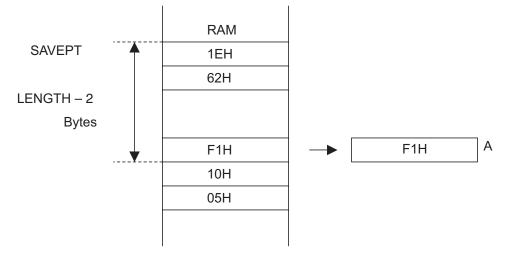

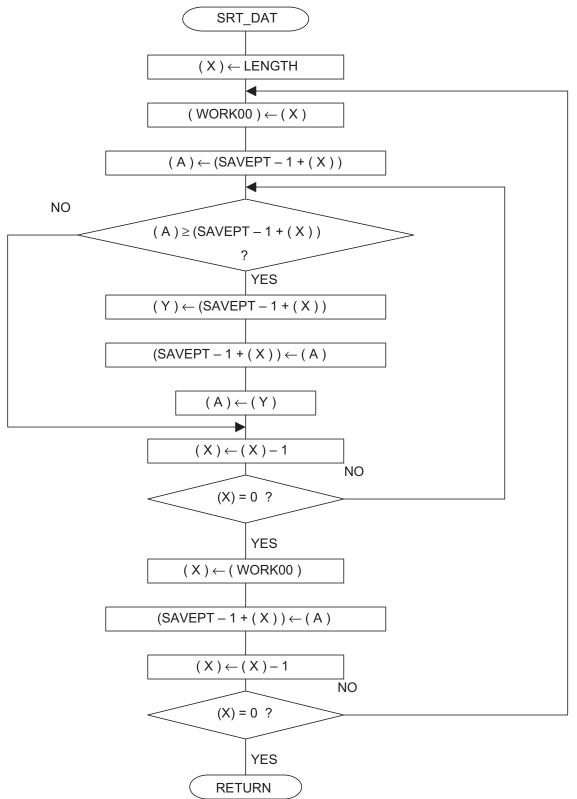

## 3.5 Data Sort

#### (1) Description

The data in the RAM area is sorted in descending order.

#### (2) Explanation

LENGTH bytes of data are sorted in descending order from RAM address SAVEPT. (a) First, the memory contents of the highest address to be sorted are stored in Accumulator A.

(b) Next, the memory contents of the next lower address are compared with the contents of Accumulator A. At this time, if the contents of Accumulator A are equal to or larger than the contents of the lower address, the contents of the memory and the Accumulator A are switched.

(c) The contents of the next lower address are compared with the contents of Accumulator A. At this time, if the contents of Accumulator A are equal to or larger than the contents of the memory, the contents of the memory and the Accumulator A are switched again.

(d) This process is repeated until it reaches the lowest address and the contents of its memory are sorted, after which the lowest value will be stored in Accumulator A. The contents of this Accumulator A will be sent to the highest address in the memory.

(e) Steps (a) through (d) are executed on the sorted area of which the highest address has been decreased, (LENGTH bytes - 1 byte) from SAVEPT.

(f) Again, steps (a) through (d) are executed on the sorted area of which the highest address has been decreased, (LENGTH bytes - 2 bytes) from SAVEPT.

(g) In this manner, steps (a) through (d) are executed until the order of the contents is sorted into descending order, decreasing the highest address until it reaches the lowest address.

In addition, in steps (b) through (c), if the contents are switched when the contents of Accumulator A are smaller than those of the memory, the contents can be sorted into ascending order.

(4) Program List

| ;************************************** |                   |                                       |                                         |  |

|-----------------------------------------|-------------------|---------------------------------------|-----------------------------------------|--|

| ;                                       |                   |                                       |                                         |  |

| ;                                       | So                | rt routine                            |                                         |  |

| ;                                       |                   |                                       |                                         |  |

| ;******                                 | * * * * * * * * * | * * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |  |

| ;                                       |                   |                                       |                                         |  |

| SRT_DAT:                                |                   |                                       |                                         |  |

|                                         | LDX               | #LENGTH                               | ;Data length                            |  |

| SRT_01:                                 | STX               | WORK00                                |                                         |  |

|                                         | LDA               | SAVEPT-1,X                            | ;SAVEPT<>SAVEPT-1+WORK00                |  |

| SRT_02:                                 | CMP               | SAVEPT-1,X                            | ; If use(BCS)                           |  |

|                                         | BCC               | SRT_03                                | ; -then negative                        |  |

|                                         | LDY               | SAVEPT-1,X                            |                                         |  |

|                                         | STA               | SAVEPT-1,X                            |                                         |  |

|                                         | TYA               |                                       | ;Minimum data set                       |  |

| SRT_03:                                 | DEX               |                                       | ; -to A&Y                               |  |

|                                         | BNE               | SRT_02                                |                                         |  |

|                                         | LDX               | WORK00                                |                                         |  |

|                                         | STA               | SAVEPT-1,X                            | ;Minimum data set                       |  |

|                                         | DEX               |                                       | ;Next area                              |  |

|                                         | BNE               | SRT_01                                | ;Sort end ?                             |  |

|                                         | RTS               |                                       | ;Yes                                    |  |

|                                         |                   |                                       |                                         |  |

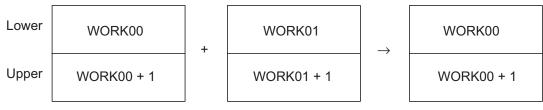

## 3.6 16-Bit Data Add (Binary)

#### (1) Description

Addition of 16-bit binary data is performed.

(2) Explanation

The contents of WORK00 +1 and WORK00 are added to the contents of WORK01 +1 and WORK01, respectively; and the results are stored to WORK00 +1 and WORK00, respectively.

When X Modified Operation Mode Flag T is set to "1", the data is added without destroying the contents of Accumulator A.

Note: M (X) represents the memory of the address indicated by Index Register X.

```

(4) Program List

;

;

16 bits BIN. data addition routine

;

ADD_16:

LDX

#WORK00

CLC

;C flag clear

SET

;T flag set

ADC

WORK01

;(WORK00+1)(WORK00)+

INX

ADC

WORK01+1

;(WORK01+1)(WORK01)

CLT

;T flag clear

RTS

```

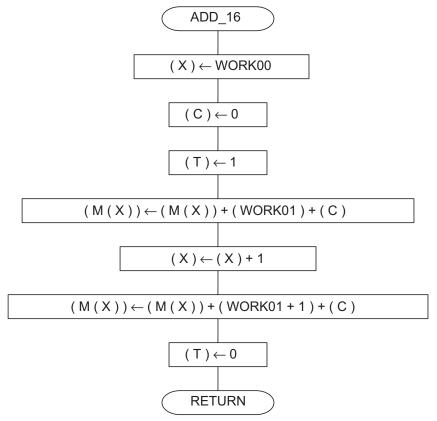

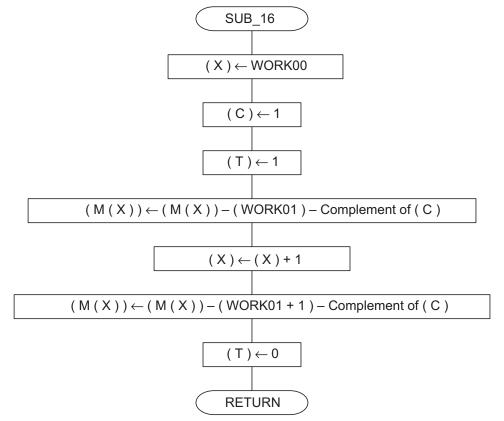

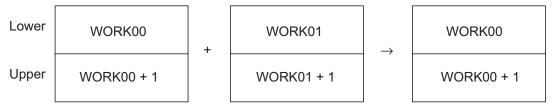

## 3.7 16-Bit Data Subtract (Binary)

#### (1) Description

Subtraction of 16-bit binary data is performed.

(2) Explanation

The contents of WORK01 +1 and WORK01 are subtracted from the contents of WORK00 +1 and WORK00, respectively, and the results are stored to WORK00 +1 and WORK00, respectively.

When X Modified Operation Mode Flag T is set to "1", the data is subtracted without destroying the contents of Accumulator A.

Note: M (X) represents the memory of the address indicated by Index Register X.

```

(4) Program List

;

;

16 bits BIN. data subtraction routine

;

SUB_16:

#WORK00

LDX

SEC

;C flag set

;T flag set

SET

SBC

WORK01

;(WORK00+1)(WORK00)-SBC

INX

WORK01+1

;(WORK01+1)(WORK01)

CLT

;T flag clear

RTS

```

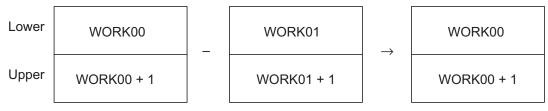

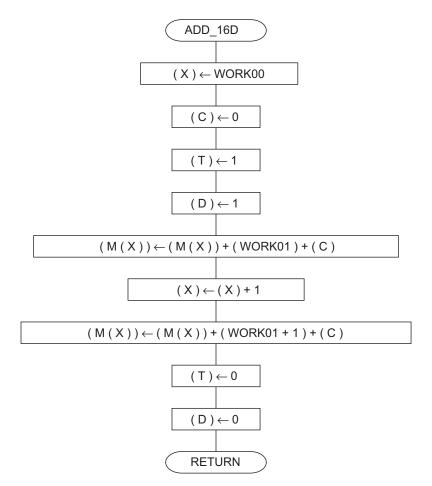

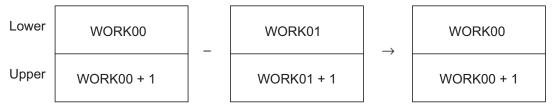

## 3.8 16-Bit Data Add (BCD)

#### (1) Description

Addition of 16-bit BCD data is performed.

(2) Explanation

The contents of WORK00 +1 and WORK00 are added to the contents of WORK01 +1 and WORK01, respectively, and the results are stored to WORK00 +1 and WORK00, respectively.

By setting Decimal Mode Flag D to "1", the ADC instruction can use decimal arithmetic. However, this will delay determination of Carry Flag C, so that make sure the SEC, CLC, and CLD instructions are not executed right after the ADC instruction.

When X Modified Operation Mode Flag T is set to "1", the data is added without destroying the contents of Accumulator A.

Note: M (X) represents the memory of the address indicated by Index Register X.

#### (4) Program List

```

;

;

16 bits BCD data addition routine

ADD_16D:

#WORK00

LDX

CLC

;C flag reset

SET

;T flag set

;Decimal mode set

SED

ADC

WORK01

;(WORK00+1)(WORK00)+

INX

ADC

WORK01+1

;(WORK01+1)(WORK01)

CLT

;T flag reset

CLD

;Decimal mode clear

RTS

```

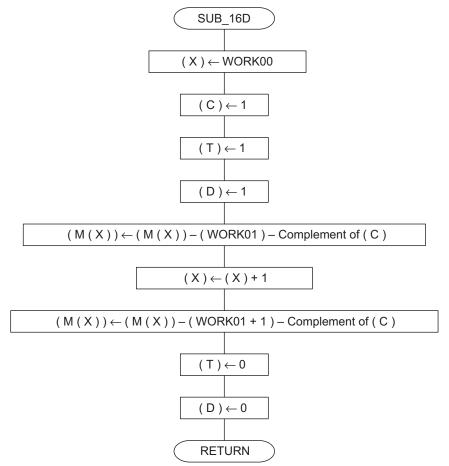

## 3.9 16-Bit Subtract (BCD)

#### (1) Description

Subtraction of 16-bit BCD data is performed.

(2) Explanation

The contents of WORK01 +1 and WORK01 are subtracted from the contents of WORK00 +1 and WORK00, respectively, and the results are stored to WORK00 +1 and WORK00, respectively.

By setting Decimal Mode Flag D to "1", the SBC instruction can use decimal arithmetic. However, this will delay determination of Carry Flag C, so that make sure the SEC, CLC, and CLD instructions are not executed right after the SBC instruction.

When X Modified Operation Mode Flag T is set to "1", the data is subtracted without destroying the contents of Accumulator A.

Note: M (X) represents the memory of the address indicated by Index Register X.

```

(4)Program List

;

;

16 bits BCD data subtraction routine

SUB_16D:

#WORK00

LDX

SEC

;C flag set

SET

;T flag set

SED

;Decimal mode set

SBC

WORK01

INX

;(WORK00+1)(WORK00)-

WORK01+1

SBC

;(WORK01+1)(WORK01)

CLT

;T flag reset

;Decimal mode reset

CLD

RTS

```

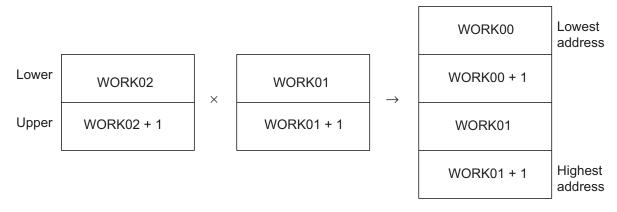

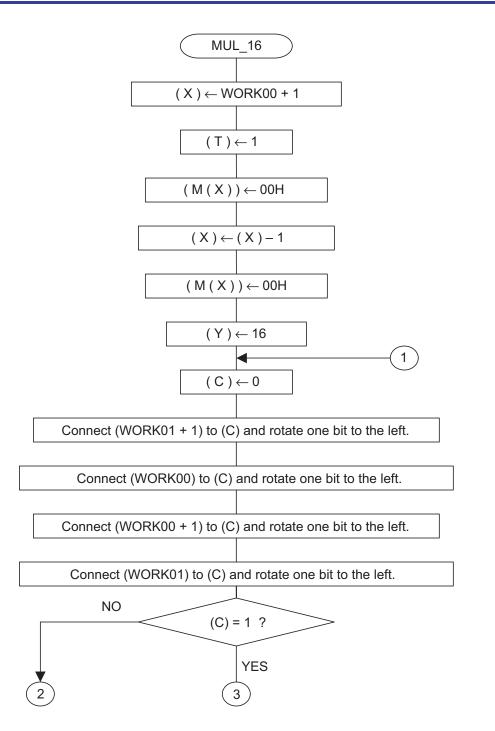

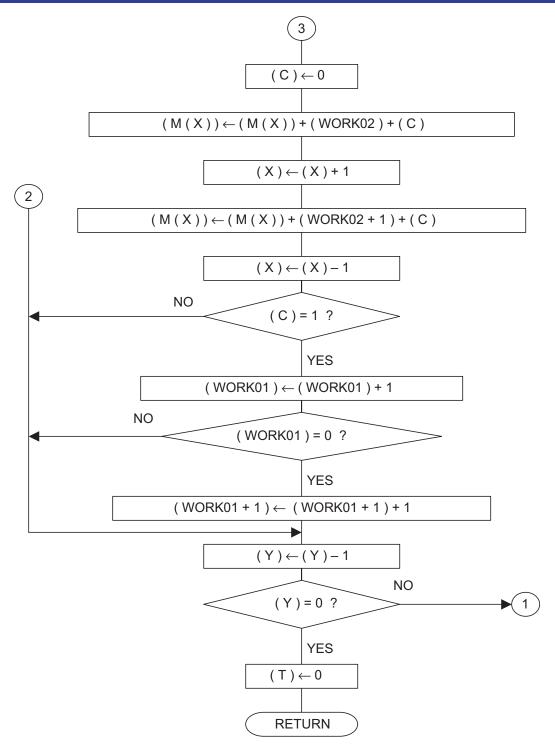

## 3.10 16-Bit Data Multiply (Binary)

#### (1) Description

Multiplication of 16-bit binary data is performed.

(2) Explanation

The contents of WORK02 +1 and WORK02 are multiplied by the contents of WORK01 +1 and WORK01, respectively, and the results are stored to WORK01 +1, WORK01, WORK00 +1 and WORK00. When X Modified Operation Mode Flag T is set to "1", the data is multiplied without destroying the contents of Accumulator A.

Note: M (X) represents the memory of the address indicated by Index Register X.

# RENESAS

| (4) Program L   | list       |                                         |                                       |

|-----------------|------------|-----------------------------------------|---------------------------------------|

| • •             |            | * * * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * |

| ;               |            |                                         |                                       |

| ;               | 16 bits    | BIN. data multiplica                    | tion routine                          |

| ;               |            |                                         |                                       |

| ; * * * * * * * | ******     | * * * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * *   |

| ;               |            |                                         |                                       |

| MUL_16:         |            |                                         |                                       |

|                 | LDX        | #WORK00+1                               | ;Product L addr. set                  |

|                 | SET        |                                         | ;T flag set                           |

|                 | LDA        | #\$00                                   | ;Clear product L                      |

|                 | DEX        |                                         |                                       |

|                 | LDA        | #\$00                                   |                                       |

|                 | LDY        | #16                                     | ;Bit counter set                      |

| ;               |            |                                         |                                       |

| MUL_01:         | CLC        |                                         |                                       |

|                 |            | WORK00                                  | ;Rotate product L                     |

|                 |            | WORK00+1                                |                                       |

|                 | ROL        | WORK01                                  | ;Rotate product H                     |

|                 | ROL        | WORK01+1                                |                                       |

|                 | BCC        | MUL_02                                  | ;C flag 1 ?                           |

|                 | CLC        |                                         | ;Yes                                  |

|                 | ADC        | WORK02                                  | ;Multiplicand + product L             |

|                 | INX        |                                         |                                       |

|                 | ADC        | WORK02+1                                |                                       |

|                 | DEX        |                                         |                                       |

|                 | BCC        | MUL_02                                  | ;Over flow ?                          |

|                 | INC        | WORK01                                  | ;Yes                                  |

|                 | BNE        | MUL_02                                  | ;Over flow ?                          |

|                 | INC        | WORK01+1                                | ;Yes                                  |

| ;               |            |                                         |                                       |

| MUL_02:         | DEY        | MITT 01                                 | Wultiple and O                        |

|                 | BNE        | MUL_01                                  | ;Multiple end ?                       |

|                 | CLT<br>RTS |                                         | ;Yes                                  |

|                 | K12        |                                         |                                       |

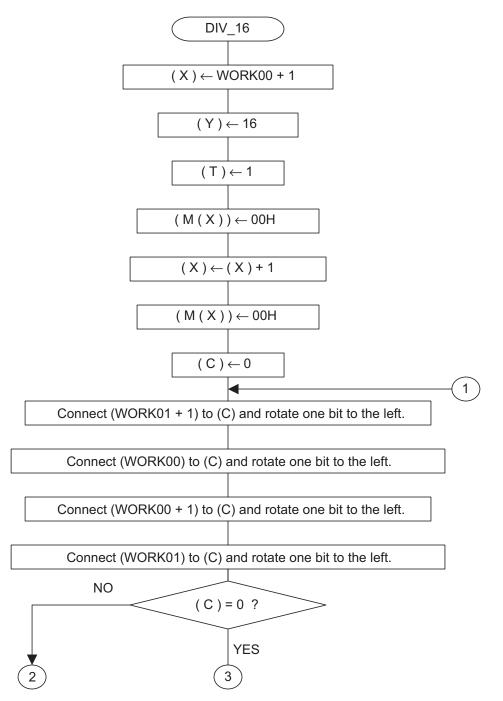

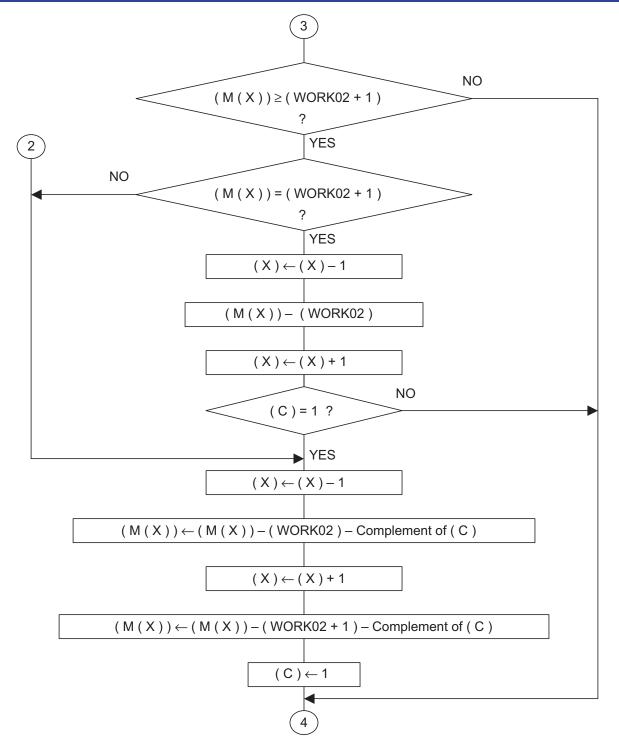

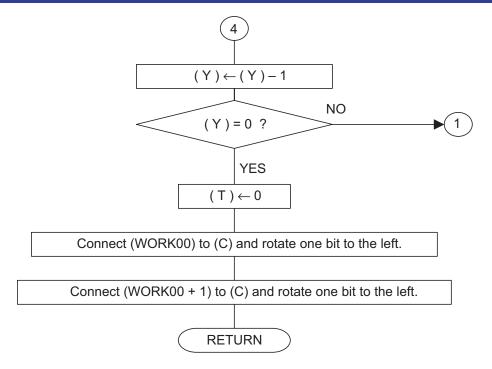

## 3.11 16-Bit Data Divide (Binary)

#### (1) Description

Division of 16-bit binary data is performed.

(2) Explanation

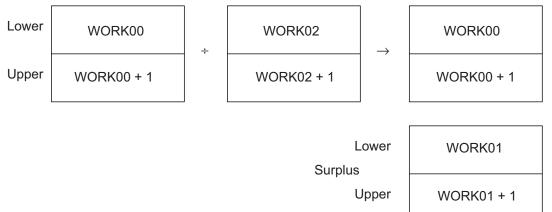

The contents of WORK00 +1 and WORK00 are divided by the contents of WORK02 +1 and WORK02. The quotients are stored to WORK00 +1, and WORK00; and the surpluses are stored to WORK01 +1 and WORK01.

When X Modified Operation Mode Flag T is set to "1", the data is divided without destroying the contents of Accumulator A.

Note: M (X) represents the memory of the address indicated by Index Register X.

| (4) Program L |                     |                                         |                                         |

|---------------|---------------------|-----------------------------------------|-----------------------------------------|

| ,             | * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

| ;<br>;        | 16 bite             | BIN. data division ro                   | uting                                   |

| ;             | IU DIUS             | bin. data division io                   | actile                                  |

|               | * * * * * * * * *   | * * * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * *     |

| ;             |                     |                                         |                                         |

| DIV_16:       |                     |                                         |                                         |

|               | LDX                 | #WORK01                                 | ;Surplus addr. set                      |

|               | LDY                 | #16                                     | ;Bit counter set                        |

|               | SET                 |                                         | ;T flag set                             |

|               | LDA                 | #\$00                                   | ;Clear surplus                          |

|               | INX                 |                                         |                                         |

|               | LDA                 | #\$00                                   |                                         |

| 5 0 1 -       | CLC                 |                                         |                                         |

| DIV_01:       |                     | WORK00                                  | ;Rotate quotient                        |

|               | ROL<br>ROL          | WORK00+1<br>WORK01                      | ;Rotate surplus                         |

|               | ROL                 | WORK01+1                                | Rocace Sulpius                          |

|               | -                   | DIV_02                                  | ;C flag 1 ?                             |

| ;             |                     |                                         |                                         |

|               | CMP                 | WORK02+1                                | ;No                                     |

|               | BCC                 | DIV_03                                  | ;Cannot divide ?                        |

|               | BNE                 | DIV_02                                  | ;No                                     |

|               | DEX                 |                                         |                                         |

|               | CMP                 | WORK02                                  |                                         |

|               | INX                 |                                         |                                         |

|               |                     | DIV_03                                  | ;Cannot divide ?                        |

| •             |                     |                                         |                                         |

| DIV_02:       |                     |                                         | ;No                                     |

|               | SBC<br>INX          | WORK02                                  | ;Surplus - divisor                      |

|               |                     | WORK02+1                                |                                         |

|               | SEC                 | WORROZTI                                |                                         |

| DIV_03:       |                     |                                         |                                         |

| 227_00        |                     | DIV_01                                  | ;Divide end ?                           |

| ;             |                     |                                         |                                         |

|               | CLT                 |                                         | ;Yes                                    |

|               | ROL                 | WORK00                                  | ;Rotate quotient                        |

|               | ROL                 | WORK00+1                                |                                         |

|               | RTS                 |                                         |                                         |

|               |                     |                                         |                                         |

## 4. Application Program Example

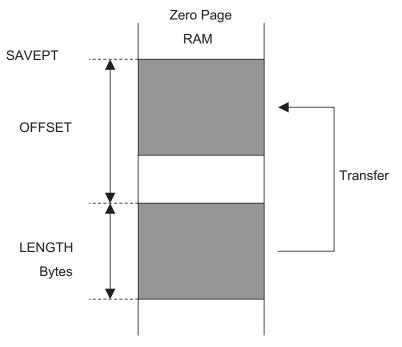

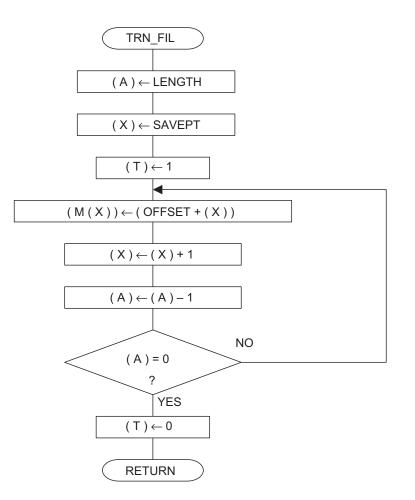

## 4.1 File Handling (transfer)

#### (1) Description

This operation recognizes a part of the zero page RAM as the file memory and executes the data transfer process from one location to another.

#### (2) Explanation

LENGTH bytes of file memory data are transferred from the zero page RAM address SAVEPT + OFFSET to continuous zero page RAM addresses starting at SAVEPT.

X Modified Operation Mode Flag T is set, and then the data is transferred between memories. The pointer is set to single pointer + OFFSET, not double pointer (source/target).

Note: M (X) represents the memory of the address indicated by Index Register X.

#### (4) Program List

| ;*****  | * * * * * * * * * * | * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

|---------|---------------------|-----------------------------------|-----------------------------------------|

| ;       |                     |                                   |                                         |

| ;       | File                | handling (transf                  | er)                                     |

| ;       |                     |                                   |                                         |

| ;*****  | * * * * * * * * * * | * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

| TRN_FIL | :                   |                                   |                                         |

|         | LDA                 | #LENGTH                           | ;File length                            |

|         | LDX                 | #SAVEPT                           |                                         |

|         | SET                 |                                   | ;T flag set                             |

| TRN_01: |                     |                                   |                                         |

|         | LDA                 | OFFSET,X                          | ;Transfer data from                     |

|         | INX                 |                                   | ; -SAVEPT+OFFSET                        |

|         | DEC                 | A                                 | ; -to SAVEPT                            |

|         | BNE                 | TRN_01                            | ;Transfer end ?                         |

|         | CLT                 |                                   | ;Yes                                    |

|         | RTS                 |                                   |                                         |

|         |                     |                                   |                                         |

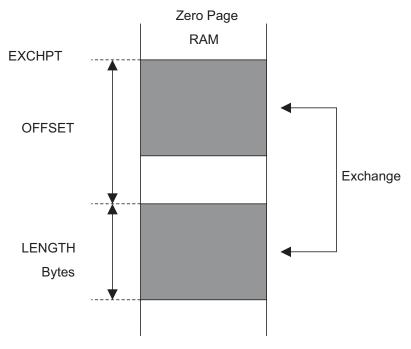

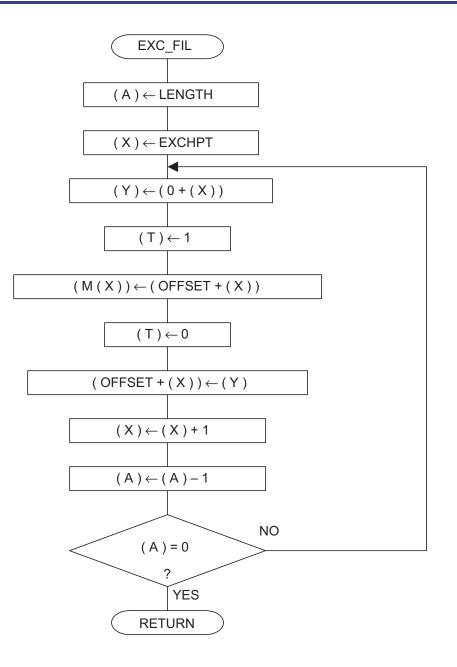

# 4.2 File Handling (exchange)

#### (1) Description

This operation recognizes a part of the zero page RAM as the file memory and executes the data exchange process from one location to another.

(2) Explanation

LENGTH bytes of file memory data from the zero page RAM address EXCHPT + OFFSET are exchanged with the data from zero page RAM address EXCHPT.

X Modified Operation Mode Flag T is set, and then the data is transferred between memories. The pointer is set to single pointer + OFFSET, not double pointer (source/target).

Note: M (X) represents the memory of the address indicated by Index Register X.

(4) Program List ; File handling (exchange) ; ; ; EXC\_FIL: LDA #LENGTH ;File length LDX #EXCHPT EXC\_01: LDY 0,X ;Exchange data of SET ; -EXCHPT+OFFSET ; -with EXCHPT LDA OFFSET,X CLTSTY OFFSET,X INX DEC А EXC\_01 ;Exchange end ? BNE RTS ;Yes

## 4.3 Code Conversion (packed BCD $\rightarrow$ unpacked BCD)

#### (1) Description

Packed BCD data is converted to unpacked BCD data.

(2) Explanation

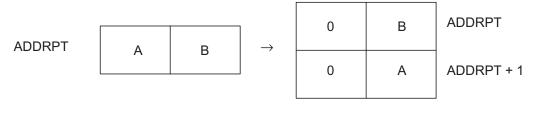

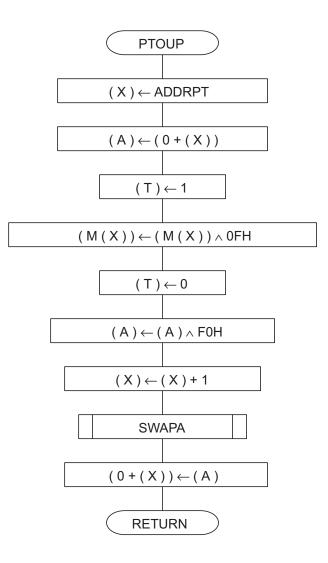

The packed BCD data at zero page RAM address ADDRPT is converted to the unpacked BCD data and stored at ADDRPT and ADDRPT + 1.

A packed BCD consists of two decimal digits in one byte. But packed-to-unpacked conversion results in two unpacked BCD bytes. Each unpacked BCD byte has one digit in the lower four bits and zero filling the upper four bits.

Packed BCD

Unpacked BCD

Note: M (X) represents the memory of the address indicated by Index Register X.

| (4) Program L | List              |                                 |                                         |

|---------------|-------------------|---------------------------------|-----------------------------------------|

| ;******       | ******            | * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

| ;             |                   |                                 |                                         |

| ;             | Packe             | d BCD -> unpacke                | d BCD                                   |

| ;             |                   |                                 |                                         |

| ;******       | * * * * * * * * * | * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

| ;             |                   |                                 |                                         |

| PTOUP:        |                   |                                 |                                         |

|               | LDX               | #ADDRPT                         |                                         |

|               | LDA               | 0,X                             | ;Get packed BCD data                    |

|               | SET               |                                 | ;T flag set                             |

|               | AND               | #0FH                            | ;Unpacked BCD data L                    |

|               | CLT               |                                 | ;T flag clear                           |

|               | AND               | #0F0Н                           |                                         |

|               | INX               |                                 |                                         |

|               | JSR               | SWAPA                           | ;Swap A                                 |

|               | STA               | 0,X                             | ;Unpacked BCD data H                    |

|               | RTS               |                                 |                                         |

| ;******       | ******            | * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

| ;             |                   |                                 |                                         |

| ;             | Swap              | A register                      |                                         |

| ;             |                   |                                 |                                         |

| ;******       | ******            | * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

| ;             |                   |                                 |                                         |

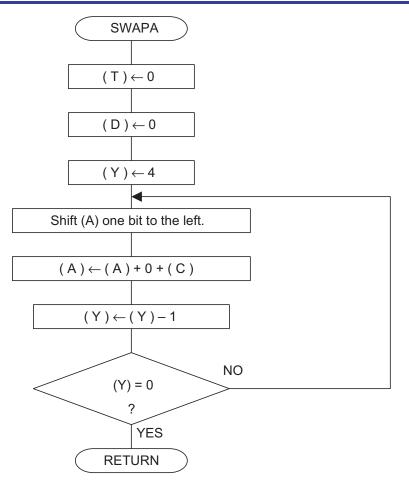

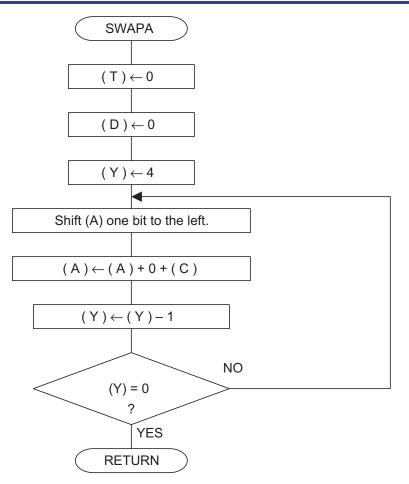

| SWAPA:        |                   |                                 |                                         |

|               | CLT               |                                 | ;T flag clear                           |

|               | CLD               |                                 | ;Decimal mode clear                     |

|               | LDY               | #4                              |                                         |

| SWAPA1:       |                   |                                 |                                         |

|               | ASL               | A                               |                                         |

|               | ADC               | #0                              |                                         |

|               | DEY               |                                 |                                         |

|               | BNE               | SWAPA1                          |                                         |

|               | RTS               |                                 |                                         |

## 4.4 Code Conversion (unpacked BCD $\rightarrow$ packed BCD)

#### (1) Description

Unpacked BCD data is converted to packed BCD data.

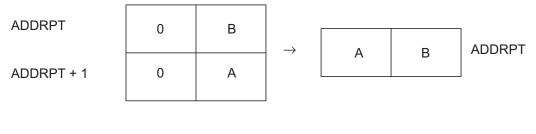

(2) Explanation

The unpacked BCD data at zero page RAM address ADDRPT +1 and ADDRPT are converted to the packed BCD data and stored at ADDRPT.

A packed BCD consists of two decimal digits in one byte. But packed-to-unpacked conversion results in two unpacked BCD bytes. Each unpacked BCD byte has one digit in the lower four bits and zero filling the upper four bits.

Unpacked BCD

Packed BCD

| (4) Program I | List                |                                         |                                     |

|---------------|---------------------|-----------------------------------------|-------------------------------------|

| ;*****        | * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * *   |

| i             |                     |                                         |                                     |

| i             | Unpad               | cked BCD -> packed BCD                  |                                     |

| i             |                     |                                         |                                     |

| ;*****        | * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * |

| i             |                     |                                         |                                     |

| UPTOP:        |                     |                                         |                                     |

|               | LDX                 | #ADDRPT                                 |                                     |

|               | INX                 |                                         |                                     |

|               | LDA                 | 0 , X                                   | ;Get unpacked BCD data H            |

|               | JSR                 | SWAPA                                   | ;Swap A                             |

|               | DEX                 |                                         |                                     |

|               | ORA                 | 0 , X                                   | ;Packed BCD data                    |

|               | STA                 | 0,X                                     |                                     |

|               | RTS                 |                                         |                                     |

| ;*****        | * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * *   |

| ;             |                     |                                         |                                     |

| ;             | Swap                | A register                              |                                     |

| ;             |                     |                                         |                                     |

| ;*****        | * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * *   |

| i             |                     |                                         |                                     |

| SWAPA:        |                     |                                         |                                     |

|               | CLT                 |                                         | ;T flag clear                       |

|               | CLD                 |                                         | ;Decimal mode clear                 |

|               | LDY                 | #4                                      |                                     |

| SWAPA1:       |                     |                                         |                                     |

|               | ASL                 | A                                       |                                     |

|               | ADC                 | # O                                     |                                     |

|               | DEY                 |                                         |                                     |

|               | BNE                 | SWAPA1                                  |                                     |

|               | RTS                 |                                         |                                     |

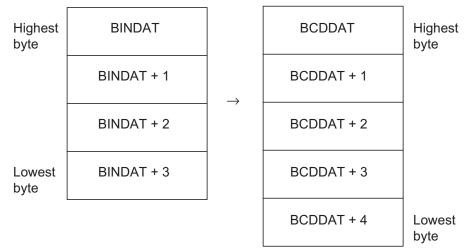

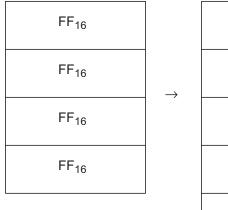

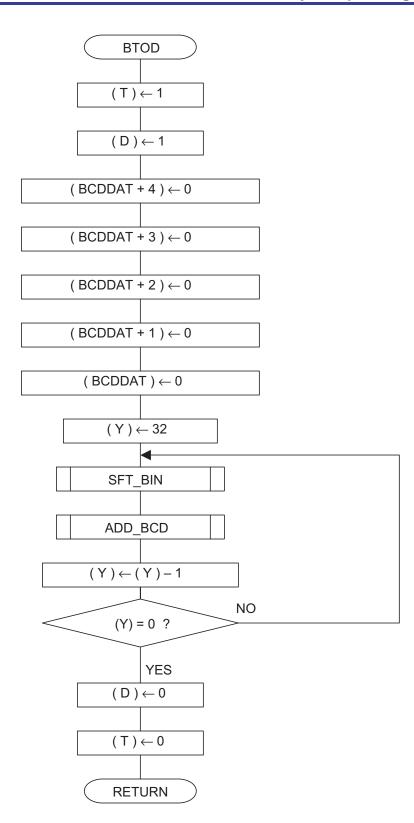

## 4.5 Code Conversion (BIN $\rightarrow$ BCD)

#### (1) Description

4-byte BIN data is converted to 5-byte BCD data.

(2) Explanation

The 4-byte BIN data at zero page RAM address BINDAT, BINDAT +1, BINDAT +2, and BINDAT +3 are converted to 5-byte BCD data and stored at BCDDAT, BCDDAT +1, BCDDAT +2, BCDDAT +3 and BCDDAT +4, respectively.

**Example:** If the BIN data is FFFFFFFH, the BCD data will be 4294967295.

BINDAT

| a | Will be 4294907295. |        |

|---|---------------------|--------|

|   | 42 <sub>10</sub>    | BCDDAT |

|   | 94 <sub>10</sub>    |        |

|   | 96 <sub>10</sub>    |        |

|   | 72 <sub>10</sub>    |        |

|   | 95 <sub>10</sub>    |        |

|   |                     | 1      |

Note: M (X) represents the memory of the address indicated by Index Register X.

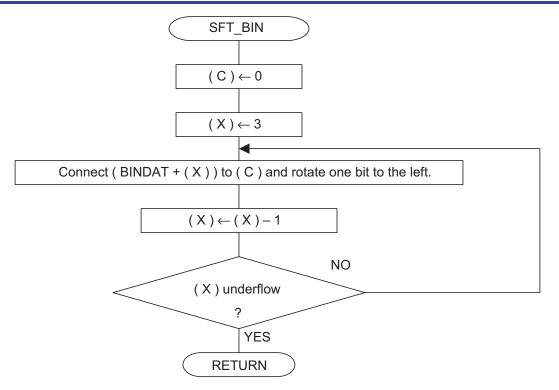

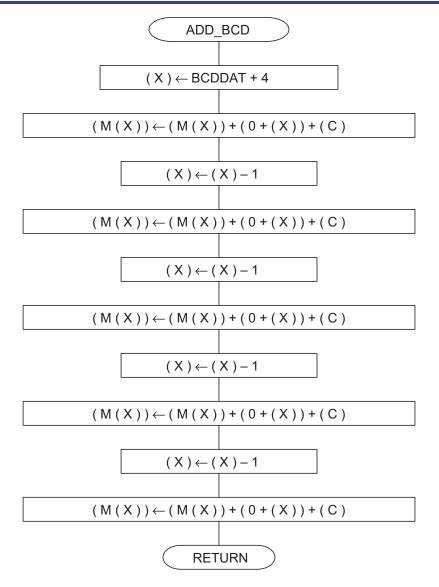

(4) Program List

| ;                         |                                                                    | BIN -> BCD                              |                                         |

|---------------------------|--------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|

| ;                         |                                                                    |                                         |                                         |

| ;*****                    | * * * * * * * *                                                    | * * * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

| BTOD:                     |                                                                    |                                         |                                         |

|                           | SET                                                                |                                         | ;T flag set                             |

|                           | SED                                                                |                                         | ;Decimal mode set                       |

|                           | LDM                                                                | #0,BCDDAT+4                             | ;Clear BCD result area                  |

|                           | LDM                                                                | #0,BCDDAT+3                             |                                         |

|                           | LDM                                                                | #0,BCDDAT+2                             |                                         |

|                           | LDM                                                                | #0,BCDDAT+1                             |                                         |

|                           | LDM                                                                | #0,BCDDAT                               |                                         |

|                           | LDY                                                                | #32                                     | ;Yes                                    |

| BTOD_01:                  |                                                                    |                                         |                                         |

|                           | JSR                                                                | SFT_BIN                                 | ;Left shift BIN data                    |

|                           | JSR                                                                | ADD_BCD                                 | ;2*(BCD)+C -> (BCD)                     |

|                           | DEY                                                                |                                         |                                         |

|                           | BNE                                                                | BTOD_01                                 | ;Convert end ?                          |

|                           | CLD                                                                |                                         | ;Yes                                    |

|                           | CLT                                                                |                                         | ;T flag clear                           |

|                           | RTS                                                                |                                         |                                         |

| ;******                   | ******                                                             | * * * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

| ;                         | T - F                                                              |                                         |                                         |

| <i>i</i>                  | Lei                                                                | t shift BIN data                        |                                         |

|                           |                                                                    | * * * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

| ,                         |                                                                    |                                         |                                         |

| SFT_BIN:                  | CLC                                                                |                                         | ;C flag clear                           |

|                           | LDX                                                                | #3                                      | it may clear                            |

| SFT_01:                   | LDA                                                                | #5                                      |                                         |

| 511_01.                   | ROL                                                                | BINDAT,X                                |                                         |

|                           | DEX                                                                | DINDAI,A                                |                                         |

|                           | BPL                                                                | SFT 01                                  | ;Shift end ?                            |

|                           | RTS                                                                | 511_01                                  | iYes                                    |

|                           |                                                                    | * * * * * * * * * * * * * * * * * * * * | ****                                    |

| :******                   |                                                                    |                                         |                                         |

| ;******                   |                                                                    |                                         |                                         |

| ;                         | 2*(                                                                | $B(D)+C \rightarrow (B(D))$             |                                         |

| ; * * * * * * *<br>;<br>; | 2*(                                                                | BCD)+C -> (BCD)                         |                                         |

| ;<br>;<br>;               |                                                                    |                                         | * * * * * * * * * * * * * * * * * * * * |

| ;<br>;<br>;*****          | * * * * * * * *                                                    |                                         | * * * * * * * * * * * * * * * * * * * * |

| ;<br>;<br>;               | * * * * * * * *                                                    | ****                                    | * * * * * * * * * * * * * * * * * * * * |

| ;<br>;<br>;*****          | *******<br>LDX                                                     | **************************************  | * * * * * * * * * * * * * * * * * * *   |

| ;<br>;<br>;*****          | LDX<br>ADC                                                         | ****                                    | * * * * * * * * * * * * * * * * * * * * |

| ;<br>;<br>;*****          | *******<br>LDX                                                     | **************************************  | ****                                    |

| ;<br>;<br>;*****          | LDX<br>ADC<br>DEX                                                  | **************************************  | * * * * * * * * * * * * * * * * * * * * |

| ;<br>;<br>;*****          | LDX<br>ADC<br>DEX<br>ADC                                           | **************************************  | * * * * * * * * * * * * * * * * * * * * |

| ;<br>;<br>;*****          | LDX<br>ADC<br>DEX<br>ADC<br>DEX<br>DEX                             | **************************************  | ****                                    |

| ;<br>;<br>;*****          | LDX<br>ADC<br>DEX<br>ADC<br>DEX<br>ADC<br>DEX<br>ADC               | **************************************  | ****                                    |

| ;<br>;<br>;*****          | LDX<br>ADC<br>DEX<br>ADC<br>DEX<br>ADC<br>DEX<br>ADC<br>DEX        | **************************************  | ****                                    |

| ;<br>;<br>;*****          | LDX<br>ADC<br>DEX<br>ADC<br>DEX<br>ADC<br>DEX<br>ADC<br>DEX<br>ADC | **************************************  | ****                                    |

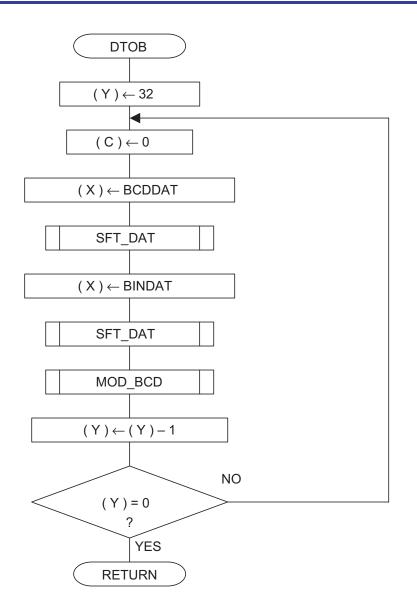

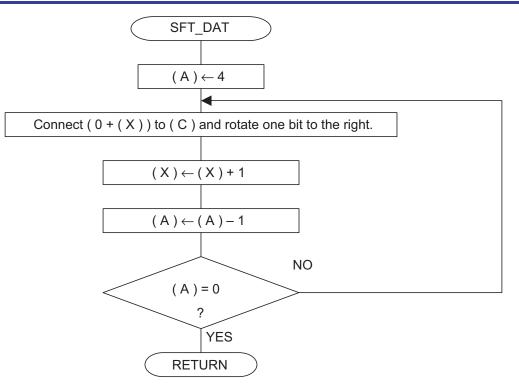

## 4.6 Code Conversion (BCD $\rightarrow$ BIN)

#### (1) Description

4-byte BCD data is converted to 4-byte BIN data.

(2) Explanation

The 4-byte BCD data at zero page RAM addresses BCDDAT, BCDDAT +1, BCDDAT +2, and BCDDAT +3 are converted to 4-byte BIN data and stored at BINDAT, BINDAT +1, BINDAT +2, and BINDAT +3, respectively.

| Highest<br>byte | BCDDAT     |               | BINDAT     | Highest<br>byte |

|-----------------|------------|---------------|------------|-----------------|

|                 | BCDDAT + 1 | $\rightarrow$ | BINDAT + 1 |                 |

|                 | BCDDAT + 2 |               | BINDAT + 2 |                 |

| Lowest<br>byte  | BCDDAT + 3 |               | BINDAT + 3 | Lowest<br>byte  |

Example: If the BCD data is 99999999, the BIN data will be 05F5E0FFH.

| BCDDAT | 99 <sub>10</sub> |               | 05 <sub>16</sub> | BINDAT |

|--------|------------------|---------------|------------------|--------|

|        | 99 <sub>10</sub> | $\rightarrow$ | F5 <sub>16</sub> |        |

|        | 99 <sub>10</sub> |               | E0 <sub>16</sub> |        |

|        | 99 <sub>10</sub> |               | FF <sub>16</sub> |        |

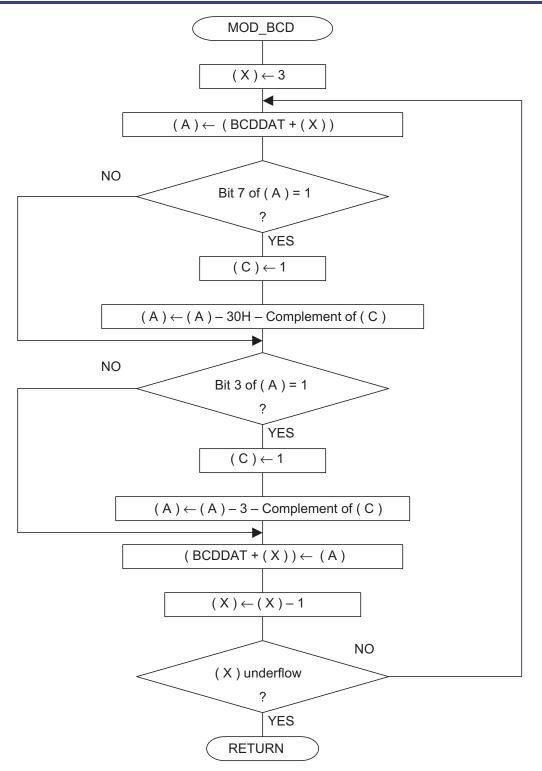

(4) Program List \*\*\*\*\*\*\* \*\*\*\* ; \* \* \* \* \* \* \* \* \* \* \* \* \* \* ; ; BCD -> BIN ; DTOB: #32 LDY DT0B\_01: CLC LDX #BCDDAT ; Point to BCDDAT JSR SFT\_DAT ;Right shift BCD data ; Point to BINDAT LDX #BINDAT JSR SFT\_DAT ;Right shift BIN data MOD\_BCD ;Get modified BCD data JSR DEY BNE DT0B\_01 ;Shift end ? RTS ;Yes ! ; ; Right shift data SFT\_DAT: LDA #4 SFT\_02: ROR 0,X INX DEC А BNE SFT\_02 RTS ; ; Modify BCD data MOD\_BCD: LDX #3 MOD\_01: LDA BCDDAT,X BBC 7,A,MOD\_02 SEC #30H SBC MOD\_02: BBC 3, A, MOD\_03 SEC SBC #3 MOD\_03: STA BCDDAT,X DEX MOD\_01 BPL RTS

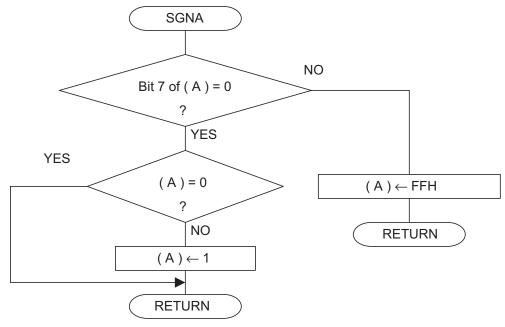

### 4.7 SGN Function

#### (1) Description

This is the SGN function for Accumulator A.

(2) Explanation

The SGN value for the contents of Accumulator A is figured and stored into Accumulator A. Bit 7 of Accumulator A is a sign bit. The SGN function for this operation is as follows:

When (A) > 0, SGN (A) = 1

When (A) = 0, SGN (A) = 0

When (A) < 0, SGN (A) = -1

(3) Flowchart

#### (4) Program List

| ;****** | * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

|---------|---------------------|-----------------------------------------|

| ;       |                     |                                         |

| ;       |                     | SGN(A)                                  |

| ;       |                     |                                         |

| ;****** | * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

| ;       |                     |                                         |

| SGNA:   |                     |                                         |

|         | BBS                 | 7,A,SGN_01                              |

|         | CMP                 | #0                                      |

|         | BEW                 | SGN_02                                  |

|         | LDA                 | #1                                      |

| SGN_02: |                     |                                         |

|         | RTS                 |                                         |

| SGN_01: |                     |                                         |

|         | LDA                 | #\$FF                                   |

|         | RTS                 |                                         |

|         |                     |                                         |

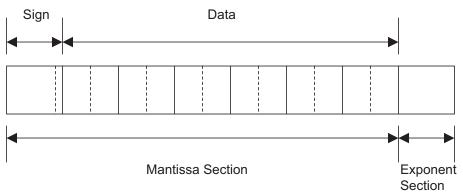

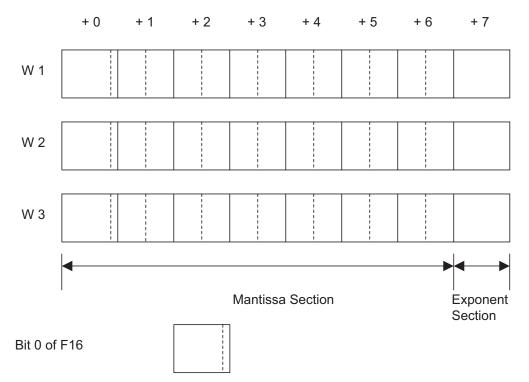

# 4.8 BCD 12-digit Floating Point Arithmetic Calculations

#### (1) Description

Arithmetic calculations for BCD 12-digit floating point numbers are performed.

#### (2) Explanation

The data format, as shown below, consists of two sections: the mantissa (7 bytes: 1 byte of sign bit, 6 bytes of data) and the exponent (one byte). "0" indicates a positive mantissa sign; "1" indicates a negative mantissa sign. The mantissa section data consists of 12 digits of valid numerical numbers (BCD). The exponent section can only handle values ranging from 00H to 0CH; the results of the calculation cannot be guaranteed for values ranging from 0DH to FFH.

The following are examples of numbers expressed in this format.

| 1234              | 0 |     |     |     |   |   | 1 | 2 | 3 | 4 | 0 0 |

|-------------------|---|-----|-----|-----|---|---|---|---|---|---|-----|

| 1.234             | 0 |     |     |     |   |   | 1 | 2 | 3 | 4 | 03  |

| - 15000           | 1 |     |     |     |   | 1 | 5 | 0 | 0 | 0 | 0 0 |

| - 0.9999999999999 | 1 | 9 9 | 9 9 | 9 9 | 9 | 9 | 9 | 9 | 9 | 9 | 0 C |

This format is used by the following three files in the zero page RAM area: W1, W2, and W3.

- W1: Stores the number to be operated and the results.

- W2: Stores the operand. Address is W2 = W1 + 8.

- W3: Uses as a work file for multiply and divide operations. Address is W3 = W2 + 8.

- Bit 0 of F16: Goes to "1" when error occurs.

The following shows the calling sequence for each arithmetic operation. Note that add and subtract are determined by the value in bit 3 of W2.

- Multiply:

- (a) Set the number to be operated in W1.

- (b) Set the operand in W2.

- (c) JSR MULT

• Divide:

Steps (a) & (b) are the same as those in the Multiply operation.(c) JSR DIV

• Add:

Steps (a) & (b) are the same as those in the Multiply operation.

(c) JSR ADSB

• Subtract:

Steps (a) & (b) are the same as those in the Multiply operation.(c) Set bit 3 of W2 to "1".(d) JSR ADSB

After these processes are executed, the results can be checked for errors with the data in bit 0 of zero page RAM address F16. If bit 0 of F16 = "1", an error has occurred. Errors that may occur in these operations are described below.

| Operation | Error                                                      |

|-----------|------------------------------------------------------------|

| Add       | When the result exceeds 999999999999                       |

| Subtract  | When the result exceeds – 9999999999999                    |

| Multiply  | When the result exceeds ± 9999999999999                    |

| Divide    | When it is divided by 0                                    |

|           | <ul> <li>When the result exceeds ± 999999999999</li> </ul> |

| (3) Program I<br>; * * * * * * |                                                                       | * * * * * * * * * * * * * | * * * * * * * | * * * * * * * | * * * * *  | * * * * * * * * * * *                                |         |      |  |  |  |

|--------------------------------|-----------------------------------------------------------------------|---------------------------|---------------|---------------|------------|------------------------------------------------------|---------|------|--|--|--|

| ;                              |                                                                       |                           |               |               |            |                                                      |         |      |  |  |  |

| ;<br>;                         | 12 digits BCD number addition,subtraction<br>,multiplication,division |                           |               |               |            |                                                      |         |      |  |  |  |

| ;                              | ;                                                                     |                           |               |               |            |                                                      |         |      |  |  |  |

| ;******                        | * * * * * * * *                                                       | * * * * * * * * * * * *   | * * * * * * * | * * * * * * * | * * * * *  | * * * * * * * * * * *                                |         |      |  |  |  |

| ;                              |                                                                       |                           |               |               |            |                                                      |         |      |  |  |  |

| ;                              |                                                                       |                           |               |               |            |                                                      |         |      |  |  |  |

| ;                              | RAM ASS                                                               | SIGN                      |               |               |            |                                                      |         |      |  |  |  |

| ;                              | 1                                                                     | 0 0                       | 4             | -             | ~          | -                                                    |         |      |  |  |  |

| ; 0                            | 1<br>L MCD -                                                          | 2 3                       | 4             | 5             | 6<br>T C D | 7<br>TNDX                                            |         |      |  |  |  |

|                                |                                                                       |                           |               |               |            |                                                      |         |      |  |  |  |