# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# アプリケーション・ノート

パワーMOS FETの特徴とスイッチング電源への応用

資料番号 D12971JJ3V0AN00 (第3版) (旧資料番号 TEA-566A) 発行年月 June 2004 N CP(K)

- ◆本資料に記載されている内容は2004年6月現在のもので、今後、予告なく変更することがあります。量 産設計の際には最新の個別データ・シート等をご参照ください。

- 文書による当社の事前の承諾なしに本資料の転載複製を禁じます。当社は,本資料の誤りに関し,一切 その責を負いません。

- 当社は、本資料に記載された当社製品の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、一切その責を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- ●本資料に記載された回路,ソフトウエアおよびこれらに関する情報は,半導体製品の動作例,応用例を 説明するものです。お客様の機器の設計において,回路,ソフトウエアおよびこれらに関する情報を使 用する場合には,お客様の責任において行ってください。これらの使用に起因しお客様または第三者に 生じた損害に関し,当社は,一切その責を負いません。

- 当社は,当社製品の品質,信頼性の向上に努めておりますが,当社製品の不具合が完全に発生しないことを保証するものではありません。当社製品の不具合により生じた生命,身体および財産に対する損害の危険を最小限度にするために,冗長設計,延焼対策設計,誤動作防止設計等安全設計を行ってください。

- 当社は,当社製品の品質水準を「標準水準」,「特別水準」およびお客様に品質保証プログラムを指定していただく「特定水準」に分類しております。また,各品質水準は,以下に示す用途に製品が使われることを意図しておりますので,当社製品の品質水準をご確認ください。

標準水準:コンピュータ, OA機器, 通信機器, 計測機器, AV機器, 家電, 工作機械, パーソナル機器, 産業用ロボット

特別水準:輸送機器(自動車,電車,船舶等),交通用信号機器,防災・防犯装置,各種安全装置, 生命維持を目的として設計されていない医療機器

特定水準: 航空機器, 航空宇宙機器, 海底中継機器, 原子力制御システム, 生命維持のための医療機器, 生命維持のための装置またはシステム等

当社製品のデータ・シート,データ・ブック等の資料で特に品質水準の表示がない場合は,標準水準製品であることを表します。意図されていない用途で当社製品の使用をお客様が希望する場合には,事前に当社販売窓口までお問い合わせください。

#### (注)

- (1)本事項において使用されている「当社」とは、NECエレクトロニクス株式会社およびNECエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいう。

- (2)本事項において使用されている「当社製品」とは,(1)において定義された当社の開発,製造製品をいう。

M8E 02.11

#### 1. **まえがき**

近年,電子機器は,軽薄短小化,省エネ化が図られコストダウンが進展しています。

電子機器ブロックの中で,その電源部の占める割合は,スペース,重量の点で最も大きく,電源部の改善が重要な課題となっています。

このような動向にあって,これまで電源はシリーズレギュレータからスイッチングレギュレータへ移行してきましたが,さらに軽薄短小,高性能化の動向の中でこれに対応したデバイスが要求されています。パワーMOS FETは,スイッチングレギュレータのこれらのニーズに最も適したデバイスとして注目され,すでに実用化がはじまっています。新規の装置設計は従来のバイポーラトランジスタに替りすべてパワーMOS FETで行うところもでてきており,ますますその普及が期待されています。

本資料では、パワーMOS FETの特徴、構造、定格、特性とバイポーラトランジスタからパワーMOS FETへの置き替え回路の例および注意事項について述べます。

注意 2SC2749, 2SC2751, 2SK735, 2SK821, 2SK854は本資料初版発行当時の製品で,現在は廃止品扱いとなっております。本資料の記述は,お客様が仕様検討される際の参考事例としてご覧ください。

#### 2. 特 徵

高利得

電圧ドライブ形デバイスであるため, CMOS等のICによる直接大電力制御が可能です。

高速スイッチング, 低損失

高速スイッチング,低オン抵抗,並列動作が容易です。

スイッチング速度がバイポーラトランジスタの1/10~1/100であり,スイッチング損失を低減できます。 オン時には抵抗特性となるため,小電流域においては,バイポーラトランジスタより低損失化が可能です。

オン抵抗の正の温度係数特性により並列動作が容易であり、この場合の個々の損失は、並列数Nに対して $1/N^2$ になります。

#### 大SOA

バイポーラトランジスタのようにセカンダリブレークダウンがないため,電圧,電流の値は,ほぼ定格電力(一定)の範囲で許容されます。

サステインエネルギがバイポーラトランジスタに対して約1000倍大きく,スイッチングレギュレータの製造 工程や市場での故障を低減できます。

以上の応用ニーズ面での特徴の他に、デバイスとして次のような特徴があります。

#### 確立された基本設計

理論解析が確立しており、理論と実際がよく一致します。

したがって, CADが容易で設計シミュレーションが容易です。

#### 最新の製造プロセス

最新の半導体技術を駆使し,MOS LSI技術の庇護下にあります(CVD技術イオン注入技術,微細加工技術等)。 したがって,今後とも性能改善が期待でき,また再現性の良い安定したプロセス条件が得やすく,均一な品質と 高信頼性が得られます。

#### 3. 構造

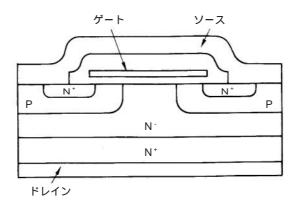

図1 パワーMOS FETの構造

パワーMOS FETは大電流を扱うため, FETセルを数千~数万, 1チップ上に並列に形成したもので, 当社では, 図1の縦形二重拡散構造(DMOS FET = Double diffused MOS FET) を主に採用しています。これは次のような理由によるものです。

#### 容易な高耐圧化

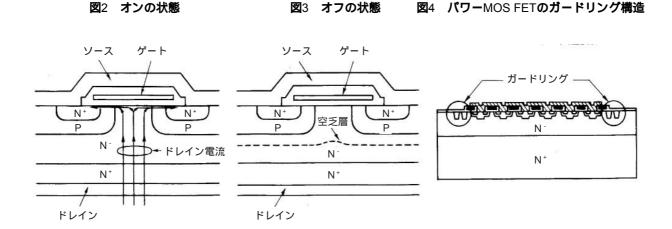

DMOS FETのオン時およびオフ時の動作を図2および図3に示します。

DMOS FETは、シリコン酸化膜を介してゲート電極がドレイン部N・層上をおおっているため、セルよりのびた空乏層は低い電圧でとなりのセルどうし結合し、電位面はチップの表面に平行なプレーンジャンクションとなります。耐圧はセル部でなく多数のセルを囲む外周構造により決まるため、バイポーラトランジスタで採用されている図4のようなガードリング等の既存の構造が適用でき、高耐圧化が容易という利点があります。

#### 低RDS(on)

DMOS FETは縦形構造で基本的にオン抵抗が小さいことに加えて、セルの形成についてもIC, LSI技術の適用が可能であり、セルサイズの微小化により低オン抵抗化をはかることができます。

#### 大サステインエネルギ耐量

前述したようにDMOS FETのオフ時には,多数のセル部はガードリングに囲まれたプレーンジャンクションとなります。このためドレインソース間の耐圧特性は電流集中の起こらない降伏を生じ,チップ全体で均一な電力を生ずるため高サステインエネルギ耐量が得られます。

以上のようにDMOS FETは,MOS FETの中でもスイッチング素子のニーズに合った最適な構造と考えられます。 世界のパワーMOS FETメーカのほとんどがこの構造を採用するようになったこともこれを裏づけています。

#### 4. 定格と特性

パワーMOS FETは,バイポーラトランジスタに比べて多くのすぐれた点があります。

ここでは、パワーMOS FETのサステイン電圧、SOA定格、スイッチング特性について、バイポーラトランジスタ と比較して説明します。

#### 4. 1 VDS(sus)

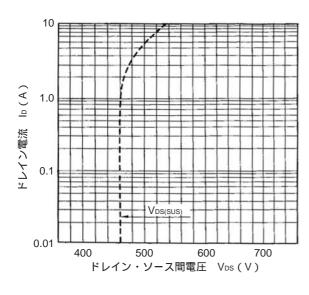

DMOS FETでは、前述のようにセル部に特別な高耐圧構造を付加しなくても、セルの外周部で耐圧が決まり、ブ レークダウン電流は,低電流域ではほとんどこの外周部に,高電流域においてはチップ全面に流れるアバランシェ ブレークダウン特性となり、図5に示すように急峻なVos-los特性を示します。このようにアバランシェダイオードと してチップ全面にブレークダウン電流が流れ、セル部に電流集中することはありません。

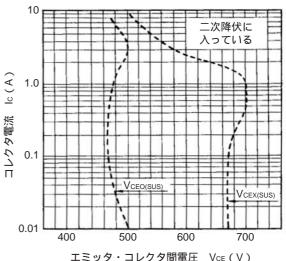

これに対しバイポーラトランジスタでは、hFEが正の温度係数を有しているためブレークダウン電流が流れると増 幅され,局部的に電流集中を生ずる,いわゆるセカンダリブレークダウン現象があります。図6にバイポーラトラン ジスタのサステイン電圧・電流を示します。パワーMOS FETは以上のような二次降伏がないのが大きな特徴です。 パワーMOS FETのサステインエネルギ耐量は,同一チップサイズの同等耐圧のバイポーラトランジスタと比較し

表1に2SK854と2SC2335のサステイン耐量の実験結果を示します。

図5 パワーMOS FETのサステイン電圧 (2SK854の例)

ておよそ1000倍大きくなります(図7参照)。

図6 パイポーラトランジスタのサステイン電圧 (2SC2335の例)

エミッタ・コレクタ間電圧 VcE(V)

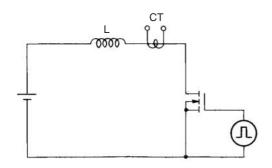

#### 図7 サステインエネルギ耐量試験回路

表1 サステインエネルギの比較

| 品 名     | サンプル | サステイン                 |        | L              |

|---------|------|-----------------------|--------|----------------|

|         |      | エネルギ                  | ( mJ ) | (図7参照)         |

| 2SK854  | NO.1 |                       | 450    | 40 mH          |

|         | NO.2 |                       | 500    |                |

| 2SC2335 | NO.1 | VCEO(sus)             | 1.3    | 100 <i>μ</i> H |

|         |      | V <sub>CEX(sus)</sub> | 0.14   |                |

|         | NO.2 | VCEO(sus)             | 3.2    |                |

|         |      | VCEX(sus)             | 0.2    |                |

# 4.2 SOA**定格**

バイポーラトランジスタは,前述のようにhfeが正の温度係数を有していることからチップの局部的な温度上昇により電流集中し,ついには熱暴走を起こすことになります。この現象はチップのホットスポットで象徴され,セカンダリブレークダウンによる高電圧領域での許容損失低下に結びついています。

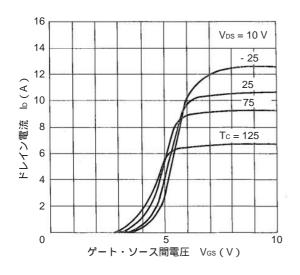

一方,パワーMOS FETはオン抵抗が正の温度係数を有すること,図8に示す伝達特性が大電流領域にて負の温度 依存性を示していることから,電流集中や熱暴走が起こらず等電力線によるSOA定格になります。

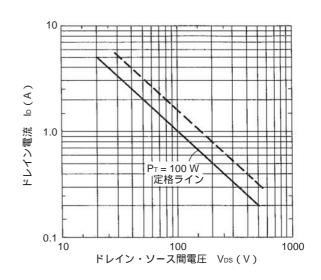

SOA実力値を図9に示します。

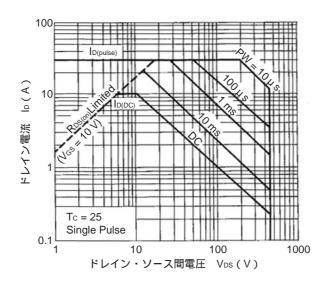

図10は2SK854のSOA定格の例です。図に示すようにパワーMOS FETは電流集中を起こしにくいため,許容できる電力損失内で電流定格を延長できます。

図8 伝達特性 (2SK735)

図9 SOA**の実力値(2SK735の例)**

図10 パルスSOA定格 (2SK735の例)

#### 4.3 スイッチング特性

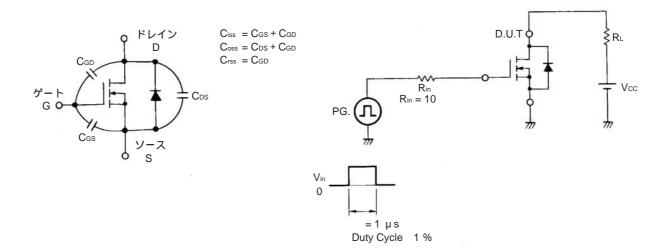

パワーMOS FETは,動作に単一の極性のキャリアのみ関与するデバイスであるため,動作に2つの極性のキャリアの関与するデバイスであるバイポーラトランジスタに比べて,高速スイッチングが可能です。しかし,図11のようにMOS FETの構造上,入力容量 $C_{iss}$ ,出力容量 $C_{oss}$ ,帰還容量 $C_{rss}$ が付加されているため,スイッチング時間は,これらの容量を駆動するインピーダンスにより決まります。

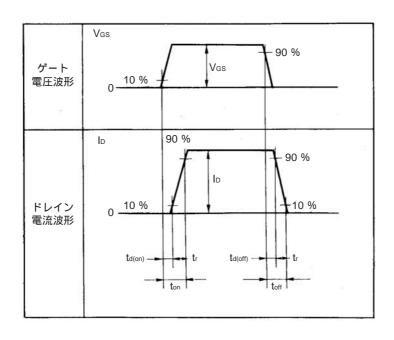

図12,図13にスイッチング時間の試験回路,定義例を,表2に2SK854,2SK735のスイッチング関連特性を示します。

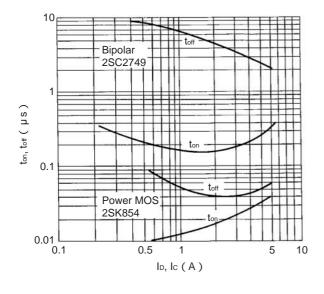

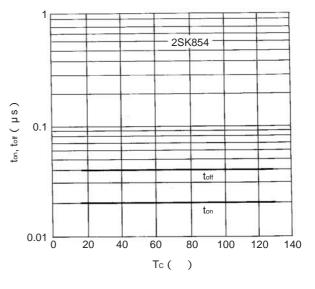

図14,図15はスイッチング時間の電流および温度依存性についてバイポーラトランジスタとパワーMOS FETを比較したものです。パワーMOS FETのスイッチング時間は温度依存性がないので,回路設計が容易です。

図11 パワーMOS FETの寄生容量

図12 スイッチングタイム試験回路例

#### 図13 スイッチングタイムの定義例

表2 2SK854 (5 A, 450 V, TO-220) 2SK735 (10 A, 450 V, MP-88) のスイッチング関連特性

| 項目      | 略号                  | 標準特性   |        | 単位 | 条件                                           |

|---------|---------------------|--------|--------|----|----------------------------------------------|

|         |                     | 2SK854 | 2SK735 |    |                                              |

| 入力容量    | Ciss                | 700    | 1270   | pF | V <sub>DS</sub> = 10 V                       |

| 出力容量    | Coss                | 220    | 320    | pF | V <sub>GS</sub> = 0                          |

| 帰還容量    | Crss                | 75     | 70     | pF | f = 1 MHz                                    |

| オン時遅延時間 | t <sub>d(on)</sub>  | 6      | 15     | ns | V <sub>DD</sub> 150 V V <sub>GS</sub> = 10 V |

| 立ち上がり時間 | tr                  | 15     | 20     | ns | R <sub>in</sub> = 10 Ω                       |

| オフ時遅延時間 | t <sub>d(off)</sub> | 30     | 60     | ns | 2SK854 : ID = 2.5 A, RL = 60 $\Omega$        |

| 下降時間    | tf                  | 7      | 30     | ns | 2SK735 : ID = 5 A, RL = 30 Ω                 |

図14 スイッチング速度の比較

図15 スイッチング速度の温度特性

#### 5. スイッチング電源への応用

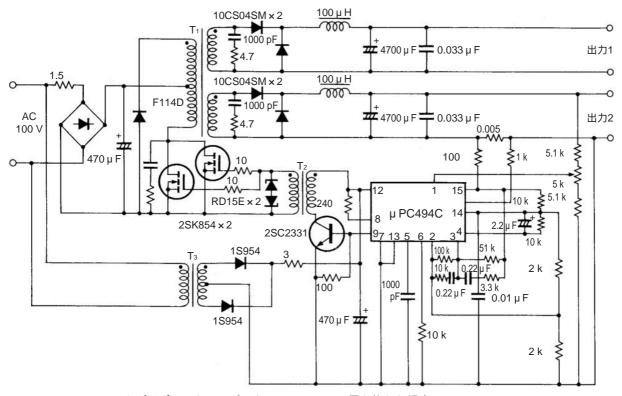

図16 2SK854を用いたセカンダリ方式の電源

(2SK854×2をバイポーラトランジスタ(2SC2751)に置き換えた場合)

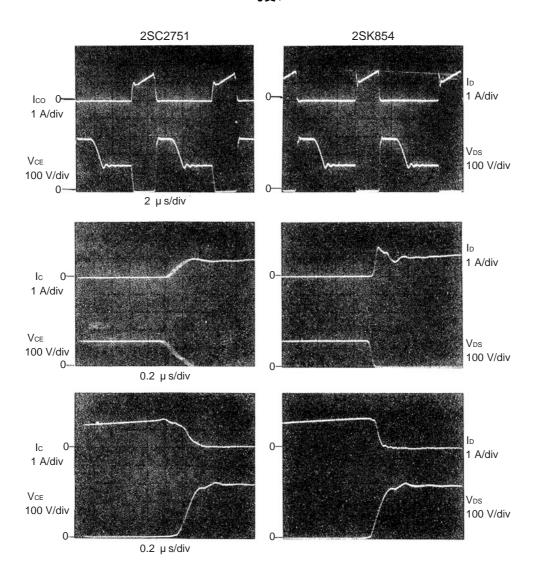

図16は,パワーMOS FET 2SK854を用いたセカンダリ方式の電源回路で,出力容量100 W,スイッチング周波数80 kHzを得ております。

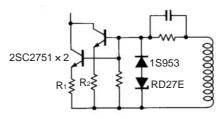

図16のスイッチング電源回路において,パワーMOS FET 2SK854(450 V/5 A, MP-25)を用いた場合と,電流定格で1ランク上のバイポーラトランジスタ2SC2751(400 V/10 A, MP-80)に置き換えた場合の動作波形,素子の温度上昇を比較したものを写真1,および表3に示します。表3からわかるようにパワーMOS FETは,バイポーラトランジスタと比べスイッチングスピードが1桁程度速いため,スイッチング損失が減少し全体の電力損失が低減できます。また,バイポーラトランジスタを図16のように並列接続で使用した場合は,エミッタにバラスト抵抗( $R_1,R_2$ )を接続し電流バランスをとりますが,パワーMOS FETでは,オン抵抗が正の温度特性を有するため,電流抑制作用が起こり電流バランスを保つので,バラスト抵抗が不要となり並列接続が容易にできます。

以上の特徴より、回路の高周波化、簡略化および小形化が可能となります。

# 表3 80 kHzスイッチングレギュレータにおけるスイッチングタイムとケース温度上昇比較

|             | 品 名 | 2SC2751              | 2SC854               |

|-------------|-----|----------------------|----------------------|

| 項目          |     | (バイポーラトランジスタ)        | (パワーMOS FET)         |

| パッケージ       |     | MP-80                | TO-220               |

| スイッチングタイム   | tr  | 0.26 <i>μ</i> s      | $0.05~\mu\mathrm{s}$ |

|             | tf  | $0.30~\mu\mathrm{s}$ | $0.08~\mu\mathrm{s}$ |

| ケース温度上昇⊿ Tc |     | 56                   | 21                   |

写真1

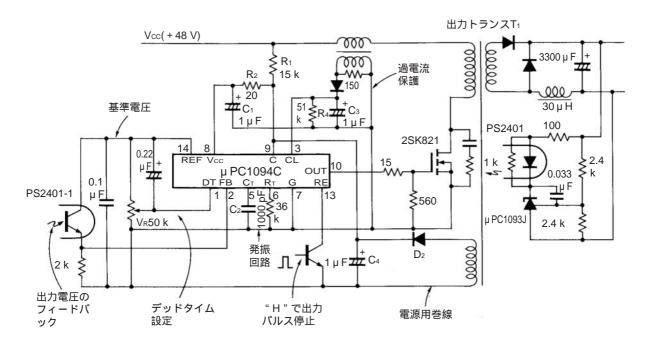

#### 図17 2SK821を用いたプライマリ方式の電源

図17は,2SK821を用いたプライマリ方式の電源回路で,出力容量100 W,スイッチング周波数は200 kHzを得ております。スイッチングレギュレータの小形化,ローコスト化の動向を進展させるためにスイッチング周波数の向上は不可欠であり,今後は図17に示すような方式が主流になるものと思われます。その中でメインスイッチング素子は高速スイッチング動作が可能なパワーMOS FETが以下に示すような特徴を発揮し使用されるものと思われます。

電圧制御形素子であり、図17の方式のようにコントロールICから直接駆動ができ、駆動回路の簡素化が図れ駆動電力が少なくて済みます。

多数キャリアデバイスであり、バイポーラトランジスタのように蓄積効果がなく、高速スイッチングが可能です。

オン抵抗が正の温度係数を有しており、2次降伏現象がなく、並列接続が容易にできます。

特に図2に示す電源のようにスイッチング周波数が100 kHzを超えるものは、パワーMOS FETの独壇場といえます。

# 6. 使用上の注意

パワーMOS FETのオン抵抗は、耐圧が高いほど大きく(およそ耐圧の2乗に比例する)なります。このため耐圧は、オン抵抗が極力小さくなるような分布に設計されていますので、耐圧マージンは図5、図6の比較でわかるようにパワーMOS FETのほうが少なくなっています。バイポーラトランジスタではVcexが定格値のおよそ1.5倍程度まであるため高電圧がVcexに達せず破壊をまぬがれるケースがあります。この点、パワーMOS FETは降伏電流の集中がなく、サステインエネルギ耐量が大きいとはいえ、降伏時の電力損失が容易に定格を越え破壊することがあるので十分注意する必要があります。

# 【発行】

# NECエレクトロニクス株式会社

〒211-8668 神奈川県川崎市中原区下沼部1753

電話(代表): 044(435)5111

----- お問い合わせ先 --

#### 【ホームページ】

NECエレクトロニクスの情報がインターネットでご覧になれます。

URL(アドレス) http://www.necel.co.jp/

#### 【営業関係,技術関係お問い合わせ先】

半導体ホットライン

電話: 044-435-9494

(電話:午前9:00~12:00,午後1:00~5:00)

E-mail : info@necel.com

#### 【資料請求先】

NECエレクトロニクスのホームページよりダウンロードいただくか, NECエレクトロニクスの販売特約店へお申し付けください。