# LOW POWER DUAL-PORTS IN ADVANCED HANDSET APPLICATIONS

## Background

As the demand for high-end wireless handsets continues to rise, the ability for OEMs and ODMs to quickly and cost effectively develop new, increasingly advanced models becomes more and more important. Also, it is equally important that these new models take advantage of the performance supported by emerging wireless data standards so that the value of the "killer apps" they bring to the market is fully realized. This application note discusses one solution that addresses these issues and the value that the IDT70P248 Low Power Dual-Port brings to these types of products.

## **Dual-Processor Architecture**

The high-end, multimedia functions included in today's wireless handsets bring with them more robust processing requirements. As a result, many of the features demanded by consumers out-pace the processing horsepower provided by available baseband processors, including those with integrated ARM cores. In cases such as this, an additional applications processor is required to help off-load some of the processing associated with multimedia applications and the use of a full operating system and application suite.

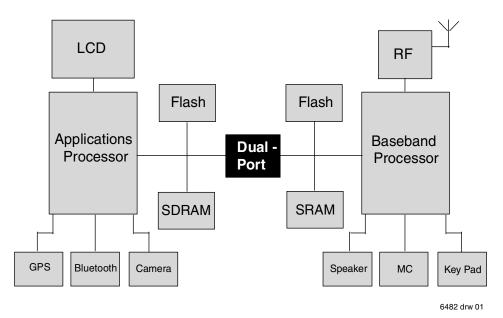

In addition to the higher level of processing it provides, there are two other benefits of adopting the dual-processor approach shown in Figure 1. First, it is a highly modular architecture that allows a single design to be used as the basis for numerous models supporting various peripheral, performance and wireless standard requirements. For example, a fixed applications block, with its supporting peripheral components, can be used in conjunction with a variety of different baseband processors, giving OEMs the ability to quickly target multiple geographies using only a limited amount of design resources. Second, this approach relies primarily of offthe-shelf components, which eliminate the need for long and costly ASIC/ FPGA development cycles.

## Inter-processor Communication

Once a dual-processor architecture has been adopted, a means of inter-processor communication must be established so that data can be transferred back and forth from the air I/F and baseband processor to the applications processor. While a number of methods can be employed to facilitate this communication, the IDT70P248 is the only off-the-shelf solution that provides both the bandwidth necessary to support data rates greater than 1Mbps (see Table 1) and the aggressive power and packaging targets demanded by these kinds of applications (see Table 2). Moreover, the Interrupt functionality provided by the IDT70P248 can be used to aid in software flow control and as a polling mechanism to prevent both ports from being simultaneously accessed, keeping the average power consumed to minimum.

Figure 1. High-end Wireless Handset

### Low Power Operation

The IDT70P248 has been optimized to consume very little power both when operational and when in standby mode (see Table 3). By supporting ultra-low operating and standby currents and a 1.8V core voltage, the IDT70P248 extends both the talk time and the standby time of the handset by limiting the power drawn from the battery under all conditions.

# Advanced Functionality

In addition to providing high-performance, low-power communication between the two processors, the IDT70P248 also features two specialty functions designed specifically for the wireless handset market. The Input Read Register and Output Drive Register allow both of the processors to monitor and/or drive a number of external binary input devices without sacrificing any additional pins. This increases the overall flexibility of the solution by allowing the limited number of controls pins on the two processors to be used for other purposes.

|                  |            | UART | USB1.1 | Dual-Port |  |  |

|------------------|------------|------|--------|-----------|--|--|

| GPRS             | 171.2 kbps |      |        |           |  |  |

| cdma2000 1x      | 307 kbps   |      |        |           |  |  |

| EDGE             | 384 kbps   |      |        |           |  |  |

| cdma2000 3x      | 2 Mbps     |      |        |           |  |  |

| W-CDMA           | 2 Mbps     |      |        |           |  |  |

| cdma2000 1xEV-DO | 2.4 Mbps   |      |        |           |  |  |

| cdma2000 1xEV-DV | 4.8 Mbps   |      |        |           |  |  |

| WCDMA (HSPDA)    | 8-10 Mbps  |      |        |           |  |  |

| 802.11b          | 11 Mbps    |      |        |           |  |  |

|                  |            |      |        |           |  |  |

Table 1. Inter-processor Communication Bandwidth

| Symbol | Description       | IDT70V24VL        | IDT70T24L         | IDT70P248         | USB 2.0<br>Host/Controller | USB1.1<br>Host/Controller |

|--------|-------------------|-------------------|-------------------|-------------------|----------------------------|---------------------------|

| VDD    | Supply Voltage    | 3.0               | 2.5               | 1.8V              | 3.3V                       | 3.3V                      |

| lod    | Operating Current | 75mA              | 50mA              | 15mA              | 345mA                      | 50mA                      |

| Isb3   | Standby Current   | 42uA              | 25uA              | 2uA               | 10.4mA                     | 500uA                     |

| Р      | Operating Power   | 225mW             | 125mW             | 27mW              | 1.14W                      | 165mW                     |

| р      | Standby Power     | 126uW             | 63uW              | 4uW               | 34mW                       | 1.6uW                     |

|        | Package Size      | 64mm <sup>2</sup> | 64mm <sup>2</sup> | 36mm <sup>2</sup> | 64mm <sup>2</sup>          | 100mm <sup>2</sup>        |

Table 2. Package Size and Power Consumption Comparison

6482 tb102

| Symbol | Parameter                                                            | Тур. | Max. | Unit |

|--------|----------------------------------------------------------------------|------|------|------|

| DD     | Dynamic Operating Current<br>(Both Ports Active - CMOS Level Inputs) | 15   | 25   | mA   |

| ISB3   | Standby Current<br>(Both Ports - CMOS Level Inputs)                  | 2    | 8    | uA   |

Table 3. IDT70P248 Operating and Standby Current Levels 6482 tbl03

## Input Read Register

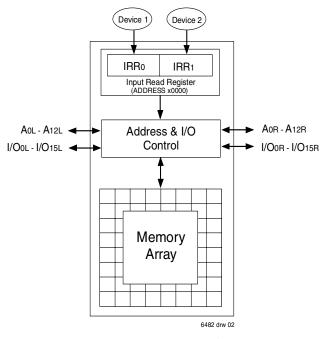

The Input Read Register (IRR) of the IDT70P248 captures the status of two external binary input devices connected to the Input Read pins (e.g. DIP switches). This allows either processor to monitor the status of two external devices using only those pins already used to I/F with the IDT70P248. When access to the IRR is enabled, the contents of the IRR are read from the IDT70P248 as a standard memory access to address x0000 from either port and the data is output via the standard I/Os. The IRR supports inputs up to 3.5V (VIL  $\leq 0.4V$ , VIH  $\geq 1.4V$ ).

Figure 2. IDT70P248 Input Read Register

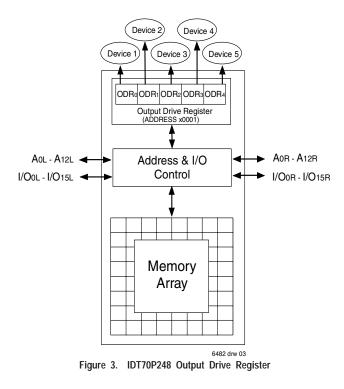

#### Output Drive Register

The Output Drive Register (ODR) of the IDT70P248 determines the state of up to five external binary-state devices by providing a path to Vss

for the external circuit. This gives either processor the ability to control up to five external devices (e.g. LEDs) without sacrificing any additional control signals. The five external devices supported by the ODR can operate at different voltages ( $1.5V \le V_{SUPPLY} \le 3.5V$ ), but the combined current of the devices must not exceed 40mA (8mA lmax for each external device). When the access to the ODR is enabled, the status of the ODR bits is set using standard write accesses to the IDT70P248 from either port to address x0001 with a "1" corresponding to "on" and a "0" corresponding to "off". The status of the ODR bits can also be read (without changing the status of the bits) via a standard read to address x0001.

#### Summary

As shown here, the dual-processor architecture provides OEMs and ODMs with a powerful, flexible, and cost effective approach to high-end handset designs. Using the IDT70P248 as the communication link between the application and baseband processors further optimizes the performance and power consumption of these designs. By taking advantage of this highly specialized device from IDT, the industry's leading supplier of multi-ports, wireless handset manufacturers can shorten their design cycles while still presenting their customers with a wide array of high performance products.

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.